(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년01월07일

(11) 등록번호 10-0792323

(24) 등록일자 2007년12월31일

(51) Int. Cl.

H01L 29/786 (2006.01)

(21) 출원번호 10-2003-7003842

(22) 출원일자 2003년03월17일

심사청구일자 2005년05월23일

번역문제출일자 2003년03월17일

(65) 공개번호 10-2004-0028613

(43) 공개일자 2004년04월03일

(86) 국제출원번호 PCT/JP2002/006981

국제출원일자 2002년07월10일

(87) 국제공개번호 WO 2003/009351

국제공개일자 2003년01월30일

(30) 우선권주장

JP-P-2001-00218370 2001년07월18일 일본(JP)

(56) 선행기술조사문헌

JP06289431 A

JP12082669 A

JP13144296 A

전체 청구항 수 : 총 10 항

심사관 : 구본재

(54) 박막 반도체장치 및 그 제조방법

### (57) 요 약

본 발명의 박막 반도체장치에 있어서는, 박막 반도체장치의 기판은 절연재기층상의 비단결정성 반도체의 박막에, 조사역마다, 조사에너지선의 최대치와 최소치가 규칙적으로 정렬배치된 에너지선강도의 분포형태로 에너지선조사를 함에 따라, 입자지름  $2\mu\text{m}$  이상의 큰 입자지름의 단결정입자가 규칙적으로 정렬배치된 상태의 반도체 박막층을 가진 기판으로서 제조되고, 박막 반도체장치의 단위전극은 상기의 기판을 사용하여, 상기 반도체 박막층의 단결정입자마다 위치 맞춤하여 형성된다. 그에 따라, 게이트전극, 소스전극 및 드레인전극을 가진 단위회로가 반도체 박막내에 형성되어 있는 반도체 단결정 입자마다 정연히 형성배치되어, 장치의 작동에 있어서 입자계에서의 전자산란 등에 의한 악영향을 받는 일없이, 높은 이동도로 작동할 수 있는 박막 반도체장치를 얻을 수 있다.

대표도 - 도4

(72) 발명자

**아베히로유키**

일본국가나가와켄요코하마시도쓰카구요시다초292번

치가부시키가이샤에키쇼센탄기쥬쓰가이하쓰센타내

**야마모토요시타카**

일본국가나가와켄요코하마시도쓰카구요시다초292번

치가부시키가이샤에키쇼센탄기쥬쓰가이하쓰센타내

**고세키히데오**

일본국가나가와켄요코하마시도쓰카구요시다초292번

치가부시키가이샤에키쇼센탄기쥬쓰가이하쓰센타내

**와라비사코미쓰노리**

일본국가나가와켄요코하마시도쓰카구요시다초292번

치가부시키가이샤에키쇼센탄기쥬쓰가이하쓰센타내

(81) 지정국

국내특허 : 중국, 대한민국

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 독일,

덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드,

이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투

칼, 스웨덴, 핀란드, 사이프러스, 터키, 불가리

아, 체코, 슬로바키아, 에스토니아

## 특허청구의 범위

### 청구항 1

절연재로 이루어지는 기층과, 상기 기층상에 형성된 박막 반도체층과, 상기 기층과 상기 박막반도체층의 사이에 형성된 제1의 열전도·결정제어층과, 상기 박막반도체층의 위에 형성된 제2의 열전도·결정제어층을 가진 박막 반도체장치 기판에 있어서, 상기 박막 반도체층 내에는,  $4\mu\text{m}$  이상의 입자지름을 가지는 반도체 단결정 입자가 이차원방향의 규칙적 정렬형태로 형성배치되어 있는 것을 특징으로 하는 박막 반도체장치 기판.

### 청구항 2

절연재로 이루어지는 기층과, 기층상에 형성된 박막 반도체층을 가진 박막 반도체장치에 있어서, 상기 박막 반도체층 내에는,  $4\mu\text{m}$  이상의 입자지름을 가지는 반도체 단결정 입자가 이차원방향의 규칙적 정렬형태로 형성되어 있고, 또한, 상기 반도체 단결정 입자마다 게이트전극을 구비한 단위회로구성이 형성되어 있는 것을 특징으로 하는 박막 반도체장치.

### 청구항 3

절연재로 이루어지는 기층상에 비단결정 반도체층을 형성하고, 상기 비단결정 반도체층에 에너지선을 조사하여 비단결정 반도체를 결정화 또는 재결정화시키는 박막 반도체장치 기판의 제조방법에 있어서,

상기 에너지선의 조사는, 소정의 조사면적내에서, 조사에너지강도가 최대치가 되는 영역과 최대치로부터 연속적으로 저감하여 최소치가 되는 영역이 이차원방향으로 규칙적으로 배열되고, 또한 조사에너지선 강도의 최소치가 상기 비단결정 반도체를 용융시키지 않는 강도인 조사에너지강도 분포형태로 행하는 것을 특징으로 하는 박막 반도체장치 기판의 제조방법.

### 청구항 4

제 3 항에 있어서, 상기 비단결정 반도체층이 비정질 반도체층이고, 상기 에너지선의 조사는 비정질 반도체를 결정화시키도록 행하여지는 것을 특징으로 하는 박막 반도체장치 기판의 제조방법.

### 청구항 5

제 3 항에 있어서, 상기 비단결정 반도체층이 다결정 반도체층이고, 상기 에너지선의 조사는 다결정 반도체를 재결정화시키도록 행하여지는 것을 특징으로 하는 박막 반도체장치 기판의 제조방법.

### 청구항 6

제 3 항에 있어서, 상기 조사에너지선으로서, 엑시머·레이저를 사용하는 것을 특징으로 하는 박막 반도체장치 기판의 제조방법.

### 청구항 7

절연재로 이루어지는 기층상에 비단결정 반도체층을 형성하고, 상기 비단결정 반도체층에 에너지선을 조사하여 비단결정 반도체를 결정화 또는 재결정화시켜 박막 반도체장치기판을 형성하고, 상기 박막 반도체장치 기판에, 게이트전극, 소스전극 및 드레인전극을 가진 전기회로를 형성배치하여 박막 반도체장치로 하는 박막 반도체장치의 제조방법에 있어서,

상기 에너지선의 조사는, 소정의 조사면적내에서, 조사에너지강도가 최대치가 되는 영역과 최대치로부터 연속적으로 저감하여 최소치가 되는 영역이 이차원방향으로 규칙적으로 배열되고, 또한 조사에너지선 강도의 최소치가 상기 비단결정 반도체를 용융시키지 않는 강도인 조사에너지강도 분포형태로 행하여,

상기 형태의 에너지선 조사공정에 의해서 얻어진, 절연재로 이루어지는 기층과, 기층상에 형성되어  $4\mu\text{m}$  이상의 입자지름을 가지는 반도체 단결정 입자가 이차원방향의 규칙적 정렬형태로 배치되어 있는 박막 반도체층을 가지는 박막 반도체장치기판에, 상기 단결정입자마다 게이트전극을 형성하고,

이어서, 상기 단결정입자마다 소스전극 및 드레인전극을 형성함으로써 단결정입자마다 단위회로를 형성하는 것을 특징으로 하는 박막 반도체장치의 제조방법.

**청구항 8**

제 7 항에 있어서, 상기 비단결정 반도체층이 비정질반도체층이고, 상기 에너지선의 조사는, 비정질 반도체를 결정화시키도록 행하여지는 것을 특징으로 하는 박막 반도체장치의 제조방법.

**청구항 9**

제 7 항에 있어서, 상기 비단결정 반도체층이 다결정 반도체층이고, 상기 에너지선의 조사는, 다결정 반도체를 재결정화시키도록 행하여지는 것을 특징으로 하는 박막 반도체장치의 제조방법.

**청구항 10**

제 7 항에 있어서, 상기 조사에너지선으로서, 엑시머·레이저를 사용하는 것을 특징으로 하는 박막 반도체장치의 제조방법.

**청구항 11**

삭제

**청구항 12**

삭제

**청구항 13**

삭제

**청구항 14**

삭제

**청구항 15**

삭제

**명세서****기술분야**

<1> 본 발명은 박막 반도체층을 가진 반도체장치 및 그 기판 및 그들의 제조방법에 관한 것이다.

**배경기술**

<2> 주지한 바와 같이, 박막 반도체장치 내지 박막 트랜지스터(TFT)는 비알칼리유리, 석영유리 등의 절연물질로 이루어진 기층(基層)상에 실리콘과 같은 반도체물질의 박막층이 형성되어 있는 기판을 사용하여, 상기 기판의 반도체 박막층내에 소스영역 및 드레인영역으로 이루어지는 채널영역이 형성되고, 1단위의 채널영역마다, 절연막을 통해 게이트전극이 설치되는 기본구성으로 이루어지는 것이다.

<3> 상기 반도체 박막층은 비정질 실리콘 또는 다결정 실리콘으로 이루어지는 것이지만, 비정질 실리콘의 박막층을 가진 기판을 사용한 TFT는 이동도(移動度)가 매우 낮기( $1\text{cm}^2/\text{V}\cdot\text{sec}$ 정도 이하) 때문에 동작속도가 느리고, 고속 동작을 필요로 하는 장치에는 사용할 수 없다. 이 때문에, 최근에는, 이동도를 높이기 위해서, 다결정 실리콘으로 이루어지는 반도체 박막층을 가진 기판을 사용하는 경우가 많지만, 다결정 실리콘막은 매우 입자지름이 작은 다수의 결정입자로 이루어지는 것이기 때문에, 장치작동시에 결정입자계에 의한 전자의 산란(散亂)이 생기는 등의 이유에 의해, 이동도의 향상에도 한도가 있다.

<4> 이 때문에, 다결정 실리콘막의 결정입자를 크게 함으로써, 이동도가 크고 또한 전자산란 등에 의한 영향이 생기기 어려운 반도체 박막층을 가진 반도체기판을 얻는 것이 검토되고 있다. 예를 들면, 다결정 실리콘막을 고온로(高溫爐)로 가열하여 큰 입자지름화시킴에 따라, 입자지름  $1\mu\text{m}$  정도의 결정입자를 가지며,  $100\text{cm}^2/\text{V}\cdot\text{sec}$  정도의 이동도를 나타낼 수 있는 박막층으로 하는 것도 시도되고 있다. 그러나, 이 큰 입자지름화를 위해서는,  $1000^\circ\text{C}$  이상의 고온에 의한 열처리가 필요하기 때문에, 절연기층재로서, 고온에는 견딜 수 있지만 고가의 석영

유리판을 사용하지 않으면 안되고, 염가인 유리판(예를 들면 소다·유리판)을 사용할 수 없기 때문에, 대화면장치에는 사용하기 어렵다고 하는 난점이 있다.

<5> 따라서, 고온의 가열처리를 사용하지 않고, 비정질 실리콘막 또는 다결정 실리콘막에 엑시머·레이저광선 등의 에너지선을 조사하여 실리콘을 결정화 또는 재결정화시킴에 따라 입자지름이 큰 결정입자로 이루어지는 다결정 실리콘 박막층을 얻고자 하는 몇가지 시도가 제안되어, 실용화되고 있다. 이 방식에 의하면, 염가인 유리판을 기층(基層)으로서 사용하면서, 결정입자를 크게 하는 것이 가능하다.

<6> 그러나, 엑시머·레이저광 등을 사용하는 결정화방식에서도, 얻어지는 결정입자의 입자지름은 최대로 해도  $1\mu\text{m}$  정도로 입자지름도 고르지 않다. 예를 들면, 일본 특개 2001-127301호에는 띠형상의 비정질 실리콘막을 용융재 결정법에 의해서 다결정화시키고, 그 위에 더욱 비정질 실리콘막을 퇴적시켜, 이것을 고상성장법(固相成長法)을 사용하여 결정화시킨다고 하는 일련의 조작을 통하여, 당초의 띠형상 다결정막의 결정을 결정종으로서 결정을 성장시켜, 입자지름이 큰 결정을 가진 다결정막을 얻고자 하는 기술이 제안되어 있다. 그러나, 이 제안에서도, 얻어지는 최대 결정입자지름은 1000nm(즉  $1\mu\text{m}$ )정도이고, 입자지름도 고르지 않은 것이 시사되어 있다(상기 공개 공보의 도 2 내지 도 5 참조).

<7> 또한, 종래의 다결정 반도체장치에서 간과되어 온 문제점으로서, 박막내에서의 결정입자의 배치형태의 문제가 있다. 즉, 종래의 다결정 반도체 박막에 있어서는, 이차원방향에서의 결정입자의 배치형태는 완전히 랜덤(random)하고, 그것을 정렬화시키는 것은 시도되고 있지 않았다. 그러나, 결정입자의 배치가 랜덤한 것은 입자지름이 고르지 않은 점과 아울러, 박막 트랜지스터 사용장치에 큰 난점을 가져온다.

<8> 즉, 당연히, 박막 반도체장치내에서의 트랜지스터회로의 배치는, 다수의 단위회로가 규칙적으로 정연히, 예를 들면 기하학적인 배열형태로 나열되어 있어야 하지만, 회로형성의 기반인 다결정층의 결정입자지름이나 결정배치가 가지런하지 않으면, 단위회로는, 다양한 입자지름이나 배치의 결정입자에 걸쳐 형성되지 않을 수 없다(도 6참조). 이것은 단위회로마다, 이동도나 전자통과 형태가 상이한 결과를 가져와, 박막 반도체장치의 성능에 악영향을 미치게 된다. 예를 들면, 단위회로마다의 특성에 격차가 있으면, 장치 전체적으로 낮은 레벨의 특성을 기초로 한 설계가 되지 않을 수 없다.

#### [발명의 개시]

<10> 본 발명의 과제는, 단위회로가, 입자지름이나 배열이 가지런하지 않은 다수의 결정입자에 걸쳐 배치되는 일없이, 결정입자의 배열형태에 대응한 배치가 되도록 하는 박막 반도체장치 및 그것을 가능하게 할 수 있는 기판 및 그러한 장치나 기판의 제조방법을 제공하는 것이다.

<11> 본 발명의 박막 반도체장치에 있어서는, 반도체 단결정 입자가 규칙적인 정렬상태, 예를 들면 격자형상 배열상태 또는 매트릭스·어레이와 같은 실질적인 기하학적 정렬상태로 배치되어 있는 박막 반도체 기판이 사용된다. 즉, 본 발명의 박막 반도체장치 기판은, 절연재로 이루어지는 기층과, 상기 기층상에 형성된 박막 반도체층을 가지며, 상기 박막 반도체층내에는, 다수의 반도체 단결정 입자가 규칙적 정렬형태로서 형성배치되어 있는 것이며, 또한, 그 입자지름은 크고, 예를 들면  $2\mu\text{m}$  이상이다.

<12> 또한, 본 발명의 박막 반도체장치는, 상기와 같이, 절연물질로 이루어지는 기층과 해당 기층상에 형성되어 다수의 반도체 단결정 입자가 규칙적인 정렬형태로 배치되어 있는 박막 반도체층을 구비한 박막 반도체 기판을 가지며, 상기 반도체 단결정 입자마다 게이트전극을 구비한 단위회로가 형성배치되어 있는 것이다.

<13> 본 발명의 박막 반도체장치 기판의 제조방법에 있어서는, 비(非)단결정 반도체층에 대하여, 조사역(照射域)마다, 조사에너지치가 최대가 되는 부분과 최대치로부터 연속적으로 저감하여 최소가 되는 부분이 규칙적으로 배열되는 강도분포형태로 에너지선조사가 이루어진다. 즉, 본 발명의 박막 반도체장치 기판의 제조방법은, 절연재로 이루어지는 기층상에 비(非)단결정 반도체층을 퇴적하는 공정과, 해당 비단결정 반도체에 에너지선을 조사하여 결정화 또는 재결정화시키는 공정을 가지며, 상기 에너지선 조사공정은, 소정의 조사면적 내에서, 조사에너지선 강도가 최대치가 되는 부분과 최소치가 되는 부분이 규칙적으로 배열되는 강도분포형태로 하는 것을 특징으로 하는 제조방법이다.

<14> 또한, 본 발명의 박막 반도체장치의 제조방법에 있어서는, 상기의 방법에 의해서 박막 반도체장치 기판을 제조한 후, 그 박막 반도체내의 단결정입자마다 회로전극이 형성된다. 즉, 본 발명의 박막 반도체장치의 제조방법은, 상기의 방법에 의해서 박막 반도체장치 기판을 제조하는 공정과, 그것에 의하여 얻어진, 절연재로 이루어지는 기층과 기층상에 형성되어 반도체 단결정 입자가 규칙적 정렬형태로 배치되어 있는 박막 반도체층을 가진 박막 반도체 기판내의 단결정입자마다의 위치 맞춤에 의해서 게이트전극을 형성하는 공정과, 상기 단결정입자마다

소스전극 및 드레인전극을 형성함으로써, 단결정입자마다 단위회로를 형성하는 공정을 가진 것을 특징으로 하는 제조방법이다.

- <15> 본 발명의 박막 반도체장치 기판은, 기판의 박막 반도체층내에, 다수의 큰 입자지름의 반도체 단결정 입자가 규칙적 정렬형태, 예를 들면 격자형상 배열 또는 매트릭스·어레이와 같은 기하학적 정렬상태로 형성배치되어 있기 때문에, 그 각 단결정입자마다 소스영역, 드레인영역 및 게이트전극을 형성배치함으로써, 단위회로가 정연히 배치된 박막 반도체장치를 얻을 수 있다.

- <16> 본 발명의 박막 반도체장치는, 박막 반도체층내에 형성되어 있는 각 단결정입자마다, 소스전극, 드레인전극 및 게이트전극을 가진 단위회로가 정연히 배치되어 있기 때문에, 동작시에 결정입자계에서의 전자산란의 영향을 받는 일이 없는, 높은 이동도의 작동효과를 얻을 수 있다.

- <17> 본 발명의 박막 반도체장치 기판 제조방법은, 비단결정 반도체로 이루어지는 박막 반도체층에 대하여, 조사에너지 강도가 최대치가 되는 부분과 최소치가 되는 부분이 이차원 방향에 있어서 규칙적으로 배열되는 분포형태로, 에너지선조사를 하는 것이기 때문에, 그에 따라, 반도체박막층내에, 다수의 큰 입자지름의(예를 들면 입자지름  $2\mu\text{m}$  이상의)반도체 단결정 입자가 규칙적 정렬형태로 형성배치된 박막 반도체장치 기판을 얻을 수 있다.

- <18> 본 발명의 박막 반도체장치 제조방법은, 박막 반도체층에 다수의 큰 입자지름의 반도체 단결정 입자가 규칙적 정렬형태로 형성배치되어 있는 기판을 사용하여, 상기 반도체 단결정마다, 소스전극, 드레인전극 및 게이트전극을 가진 단위회로를 형성하도록 하였기 때문에, 그에 따라, 이동도가 크고, 또한 전자산란 등의 결함이 없는 박막 반도체장치를 얻을 수 있다.

### 도면의 간단한 설명

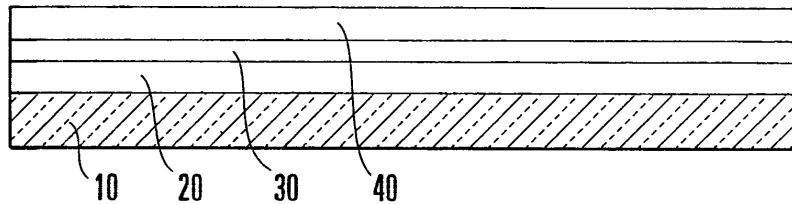

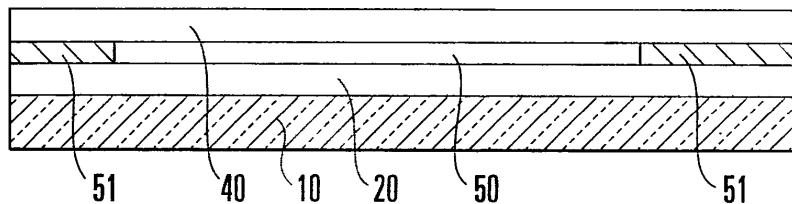

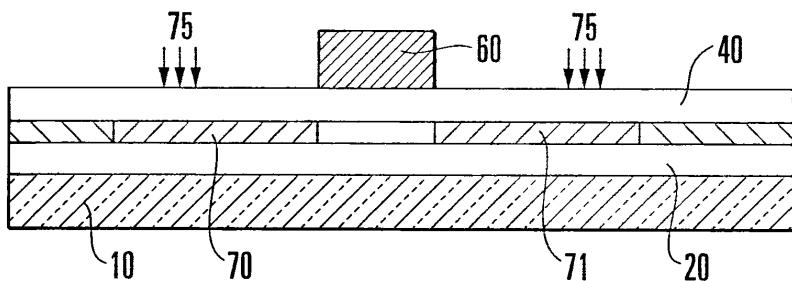

- <19> 도 1은 본 발명의 박막 반도체장치의 제조과정의 일례를 나타내는 모식도이다.

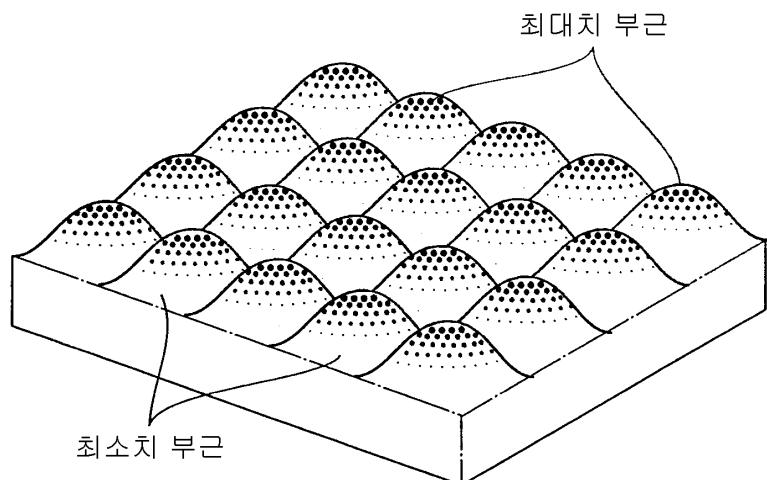

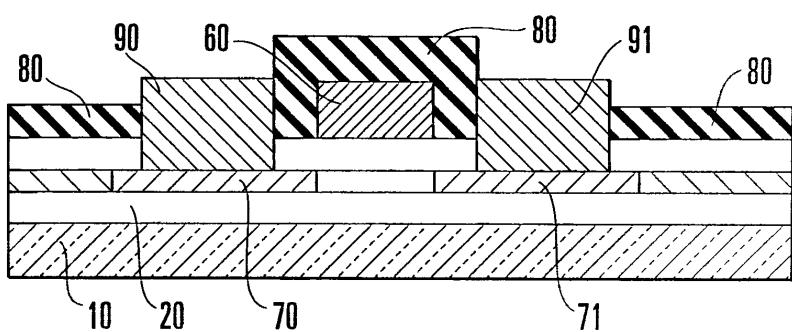

- <20> 도 2는 본 발명방법에 있어서의 에너지선조사시의 에너지선강도의 이차원적 분포상태의 일례를 나타내는 모식도이다.

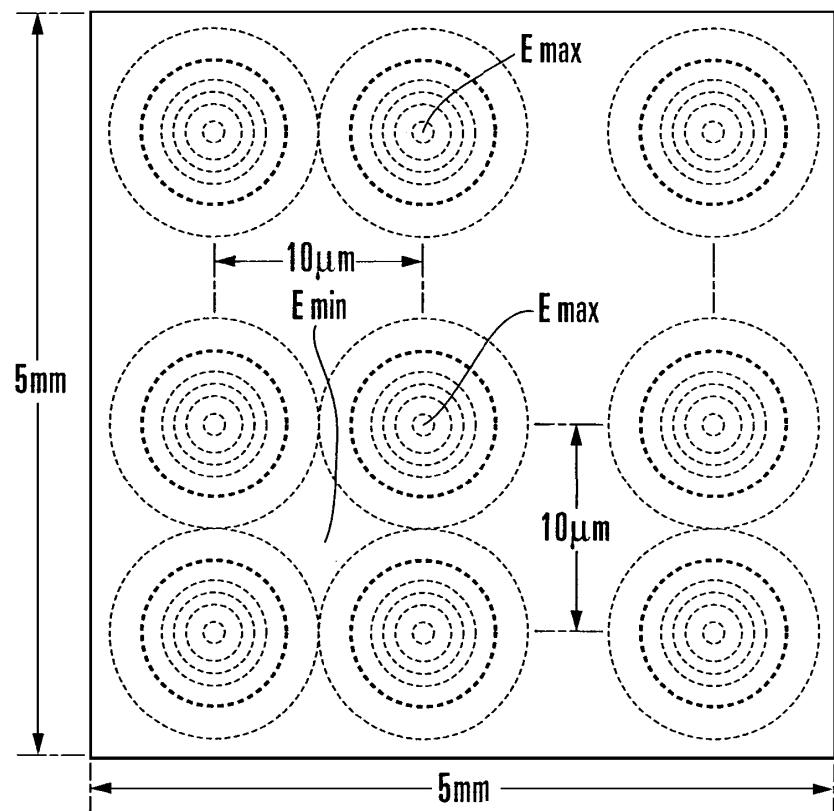

- <21> 도 3은 본 발명방법에 있어서의 조사에너지선 강도의 최대치↔최소치사이의 변화상태의 프로필의 일례를 나타내는 모식도이다.

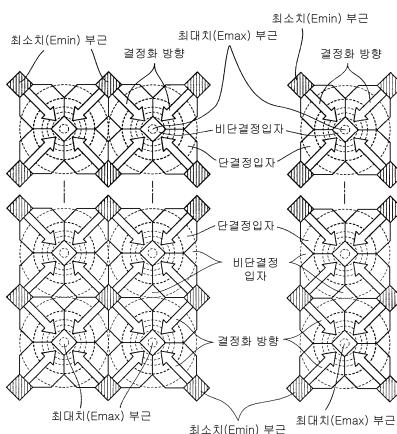

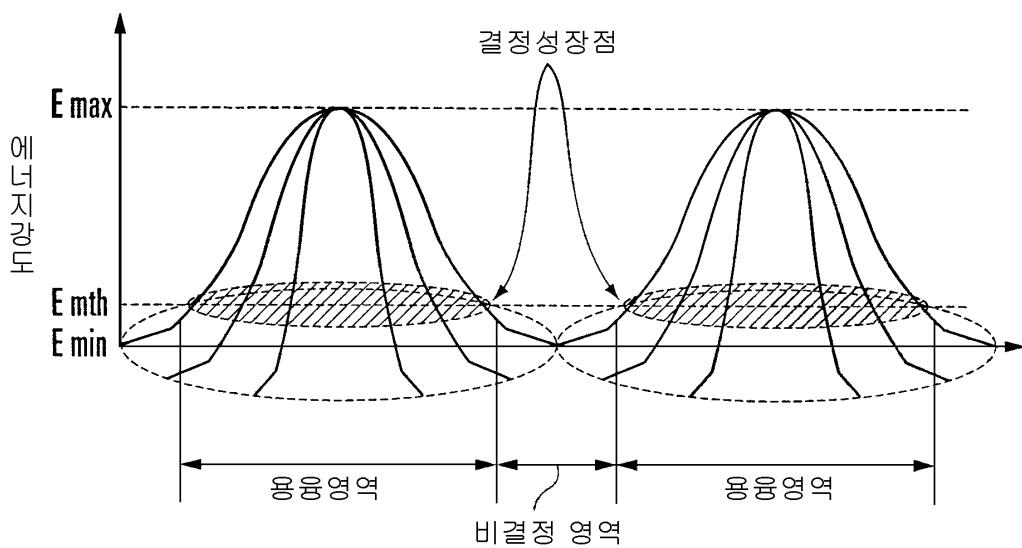

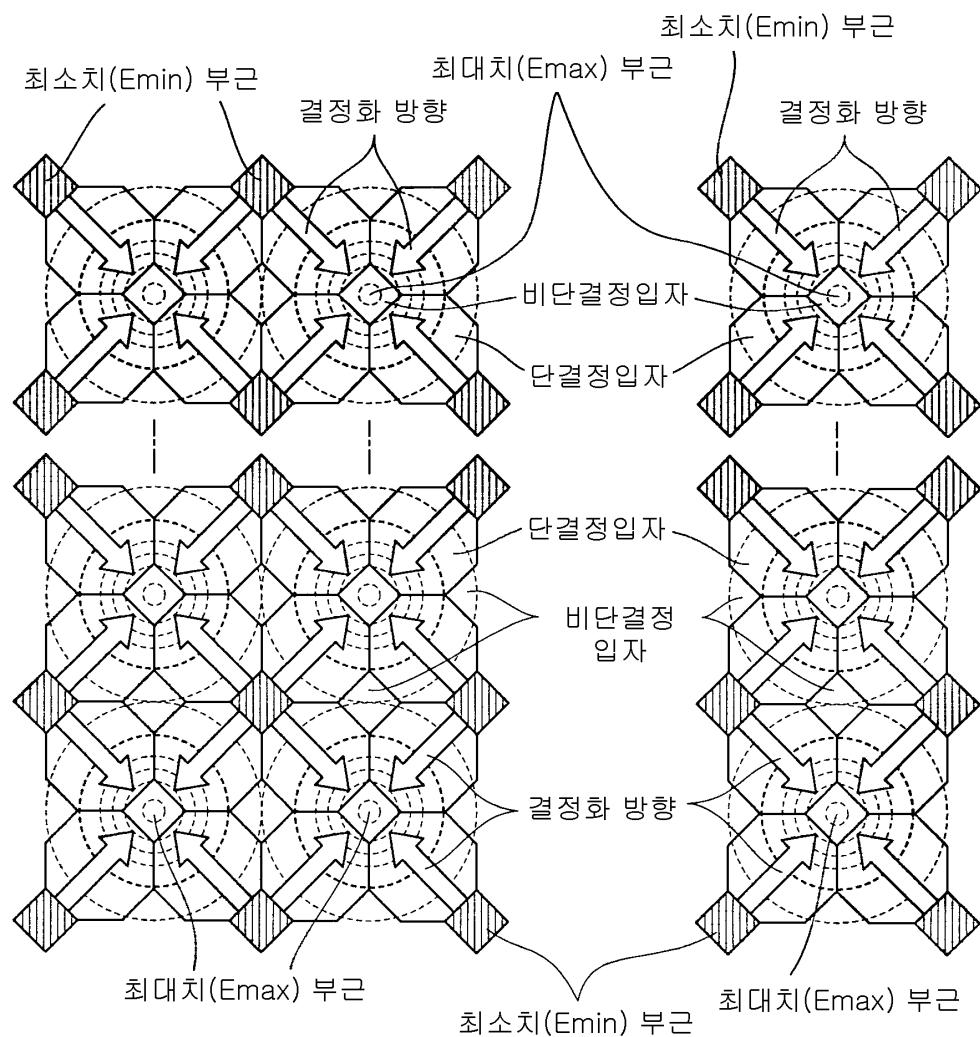

- <22> 도 4는 본 발명방법에 의한 에너지선조사후에 있어서의, 박막 반도체층내의 단결정입자의 규칙적 정렬상태의 일례를 나타내는 모식도이다.

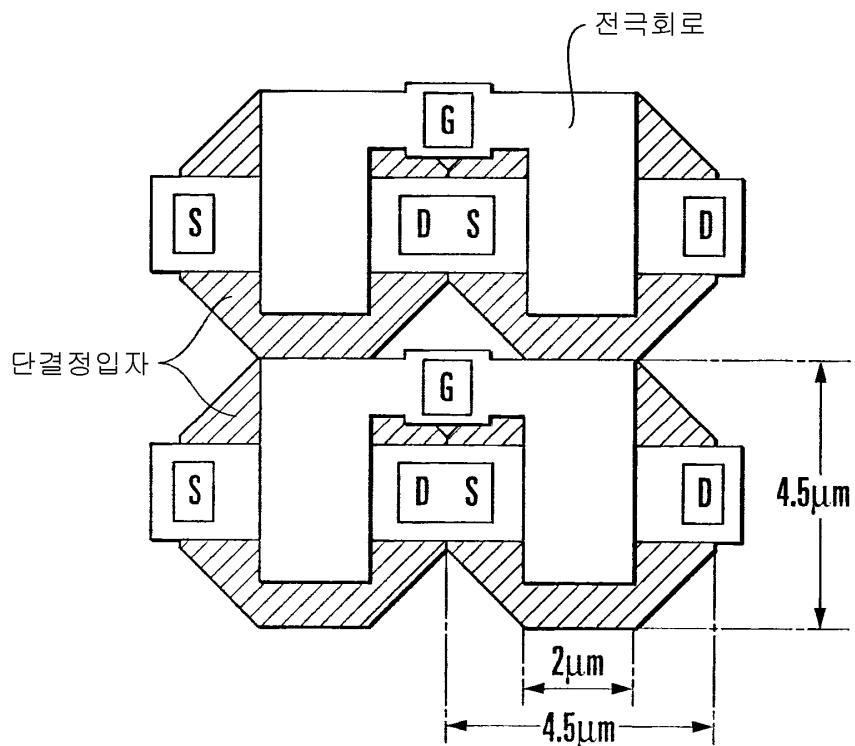

- <23> 도 5는 본 발명의 박막 반도체장치에 있어서의, 결정입자와 전극배치상태의 대응관계의 일례를 나타내는 모식도이다.

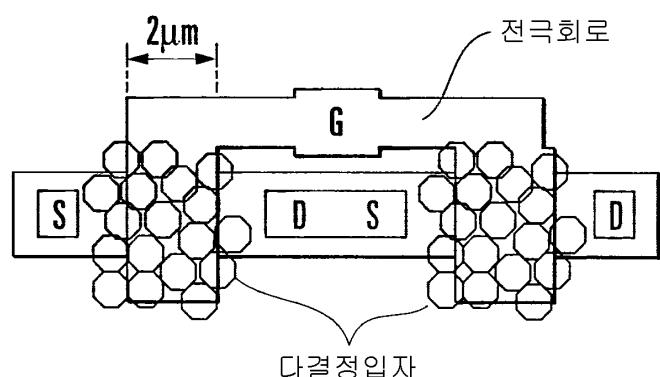

- <24> 도 6은 종래의 다결정 박막 반도체를 사용한 박막 반도체장치에 있어서의, 결정입자와 전극배치상태의 대응관계를 나타내는 모식도이다.

- <25> 도 7은 도 2 및 도 3에 나타낸 에너지선 강도의 최대치와 최소치의 배열상태의 일례를 입체모형적으로 나타낸 모식도이다.

- <26> [발명을 실시하기 위한 최선의 형태]

- <27> 본 발명의 박막 반도체장치에 있어서, 박막 반도체기판의 절연물질기층으로서는, 변형 포인트가  $700^\circ\text{C}$  이하의 유리판을 사용하는 것이 바람직하지만, 유리에 한정되지 않고, 각종 투명 또는 불투명한 절연물질제의 판, 예를 들면 세라믹 혹은 적절한 내열성을 가진 플라스틱필름 등을 사용할 수도 있다.

- <28> 상기의 기층상에, 반도체 단결정 입자가 규칙적인 정렬상태로 배치되어 있는 반도체 박막층이 형성되는 것인데, 이러한 박막층은 기층상에, 비단결정성 반도체의 박막층을 퇴적하여, 그것을, 후술하는 엑시머·레이저 그 밖의 에너지선 조사법에 의해서 입자지름이 큰 단결정으로 이루어지는 다결정 반도체박막으로 함에 따라 이루어진다. 비단결정성 반도체로서는, 비정질 반도체를 사용하여도 좋고, 혹은, 이미 미소 입자지름의 단결정이 형성되어 있는 다결정 반도체를 사용하여, 그것을 재결정시켜 본 발명의 반도체 박막층에 형성하여도 좋다. 박막 반도체 층의 두께는 10 내지  $200\text{nm}$ , 특히 50 내지  $100\text{nm}$ 으로 하는 것이 바람직하다.

- <29> 기층상에 비단결정 반도체층을 형성할 때, 통상적으로는, 기층과 반도체층의 사이에, 제 1 열전도·결정제어층, 예를 들면 산화실리콘, 질화실리콘( $\text{SiNx}$ ) 등의 물질로 이루어지는 박층(薄層)이 형성된다. 이 층은 기층물질(예를 들면 유리)로부터의 불순물을 블록하는 기능과, 조사결정화공정에서 반도체층의 열분포의 균일성이나 결

정의 배향성을 가져오는 기능을 가진 것이며, 그 막두께는 20 내지 1000nm, 특히 200~300nm으로 하는 것이 바람직하다.

<30> 또한, 비단결정 반도체층 위에, 더욱 제 2 열전도 · 결정제어층을 설치하는 것도 통상 이루어지고 있다. 이 층도, 제 1 열전도 · 결정제어층과 마찬가지로, 조사결정화공정에서의 반도체층의 열분포 균일성이나 결정의 배향성을 가져오는 기능을 가진 것으로, 산화실리콘, 질화실리콘, 탄화실리콘(SiC) 등의 물질을 사용할 수 있다. 그 막두께는, 50 내지 500nm, 특히 100~300nm으로 하는 것이 바람직하다.

<31> 상기 제 1 및 제 2 열전도 · 결정제어층이 형성되는 경우에는, 박막 단결정 반도체층은, 상기 두개의 제어층 사이에 개재하여 형성되게 되고, 이 경우에는, 절연물질 기층 위에 제 1 제어층 물질을 박막형상으로 퇴적하고, 그 위에 박막 비단결정 반도체 물질층을 퇴적하고, 더욱 그 위에 제 2 제어층 물질층을 퇴적하여, 그 후에, 위쪽으로부터 에너지선을 조사함으로써 비단결정 반도체층을 단결정화시키게 된다.

<32> 도 1의 (a) 내지 (d)는, 상기한 바와 같이 기층에 각 박막층이 퇴적된 상태로부터 박막 반도체장치가 형성되기 위해 이르기까지의 각 단계의 일례를 나타내는 모식도이다. 먼저, 도 1의 (a)에 나타낸 바와 같이, 유리기판(10) 위에 제 1 열전도 · 결정제어층(20)이 퇴적되고, 그 위에 비단결정층(30)이, 더욱 그 위에 제 2 열전도 · 결정제어층(40)이 퇴적된다. 이어서, (b)에 나타낸 바와 같이, 에너지선의 조사에 의해서, (a)에 있어서의 비단결정층(30)이, (b)에 있어서의 단결정 실리콘역(50)과, 비단결정역(51)으로 변성된다. (b)에 나타나 있는 것은, 1 개의 단결정역의 단면의 모식도로서, 이러한 단결정이 다수 형성됨에 따라, 본 발명의 박막 반도체기판이 되는 것이다.

<33> 다음에, 상기한 바와 같이 형성된 박막 반도체기판상에, (c)에 나타낸 바와 같이, 게이트전극(60)을 형성하고, 또한, 이 게이트전극(60)을 마스크로 하여, 단결정 반도체 박막층에 인이온 등의 전극형성물질(75)을 주입하여, 소스영역(70) 및 드레인영역(71)을 형성한다.

<34> 다음에, (d)에 나타낸 바와 같이, 산화실리콘 등의 절연물질에 의한 층간절연막(80)을 퇴적하고, 더욱, 소스영역(70) 및 드레인영역(71) 상에 위치한 제 2 열전도 · 결정제어층(40) 및 층간절연막(80)에 컨택트홀을 형성한 후, 알루미늄(A1)막을 퇴적하여 소스전극(90) 및 드레인전극(91)을 형성하고, 그에 따라, 본 발명의 박막 반도체장치가 완성하게 된다.

<35> 상기 (b)의 공정에서, 박막 반도체기판에 에너지선조사를 하기 위한 조사수단으로서는, 예를 들면 엑시머 · 레이저광선의 조사를 사용하는 것이 바람직하지만, 반드시 엑시머 · 레이저광선에 한정되는 것이 아니라, 예를 들면, 연속발진의 아르곤 · 레이저광을 펄스화하여 사용할 수 있다.

<36> 에너지선의 조사에 의해서 규칙적인 정렬형태로 단결정 반도체입자가 배치된 박막 반도체층을 얻기 위해서는, 소정의 간격마다 조사에너지강도가 최대치와 최소치의 사이에서 이차원적으로 변화하여, 에너지강도 최대점과 에너지강도 최소점이 규칙적으로, 예를 들면 격자형상 혹은 매트릭스 · 어레이와 같이 정렬된 에너지강도 분포형태로 조사가 이루어지도록 한다. 예를 들면, 도 2, 도 3 및 도 7에 나타낸 바와 같이  $5 \times 5\text{mm}$ 의 사각형 영역내에,  $10\mu\text{m}$ 의 간격마다 조사에너지가 최대치( $E_{\text{max}}$ )  $\rightarrow$  최소치( $E_{\text{min}}$ )  $\rightarrow$  최대치( $E_{\text{max}}$ )의 변화를 이차원적으로(x, y 양방향으로) 반복하는 것과 같은 강도분포형태로 조사하고, 이어서, 조사위치를  $5\text{mm}$ 마다 이동시켜 조사하도록 하면 좋다.

<37> 상기와 같은 조사에너지강도의 변화는, 예를 들면 위상 시프트 · 마스크를 사용하여 조사에너지 강도분포의 변화를 가져옴으로써 가능하고, 또한, 도 3에 나타낸 바와 같이, 최대치와 최소치의 사이의 변화가 실질적으로 연속적 변화인 것이 바람직하다.

<38> 최대치, 최소치를 각각 어느 정도의 값으로 설정할 것인지는, 비단결정 반도체층의 막두께, 상기 제 1, 제 2 제어층의 막두께나 열전도율에 기초하여 조정하면 좋지만, 예를 들어, 최소에너지강도는, 조사시간내에서는 박막 반도체를 용융시키지 않는 조사온도를 가져오는 강도로 하고, 최대치는 박막 반도체를 조사시간내에 용융시키는 데에 필요 또한 충분한 강도로 하여, 도 3에 나타낸 바와 같이, 최대치( $E_{\text{max}}$ )와 최소치( $E_{\text{min}}$ ) 사이에 용융역치( $E_{\text{mth}}$ )가 존재하도록 한다.

<39> 또, 조사유니트의 형상은 상기한 바와 같이  $5 \times 5\text{mm}$ 의 정방형상에 한정되지 않고, 각종 다각형상이어도 되는 것은 물론이고, 또한, 조사에너지의 최대치, 최소치의 배치형상은 방형격자형상에 한정되지 않고, 예를 들면 엘타형 격자형상이라도 좋다.

<40> 상기의 형태에서 박막 반도체에 대하여 에너지선조사를 하면, 조사영역중 조사에너지의 최소치영역[용융역치

(Emth)이하의 영역] 부분은 완전하게는 용융되지 않고, 먼저 Emth에 상당하는 온도이하의 영역에 결정핵이 형성되고, 이어서, 결정핵의 주위에서부터 Emax에 상당하는 온도영역을 향하여 결정이 성장해 나간다(도 4의 화살표가 성장방향을 나타낸다). 한편, 용해온도가 가장 높은 조사에너지 최대치영역이나 결정성장 끝단부근은, 성장방향이 다른 결정이 서로 대향하여, 결과적으로 미결정영역부분 내지는 입자계가 되고, 이렇게 해서, 조사에너지의 용융역치 (Emth) 영역부분을 결정핵으로 하는, 입자지를  $4\mu\text{m}$ 을 넘는 반도체 단결정이 규칙적으로 정렬배치된 박막 반도체기판을 얻을 수 있게 된다(도 4 참조). 조사에너지의 최대치상호간의 간격을 조정함으로써, 단결정의 입자지름을 조정할 수 있는 것은 물론이고, 예를 들어, XeCl 엑시머 · 레이저광에 의한 파장이  $308\text{nm}$ 의 엑시머 · 레이저의 조사인 경우, 최대치 사이의 상호간격을  $12\mu\text{m}$ 로 하는 것에 의해, 입자지를  $5\mu\text{m}$ 의 단결정이 정렬배치한 박막 반도체기판을 얻을 수 있다. 본 발명의 박막 반도체장치에 사용하는 기판으로서는, 입자지를  $2\mu\text{m}$  이상인 것이 바람직하다.

<41> 이렇게 해서 얻어진 박막 반도체기판에 대하여, 예를 들면 각 단결정입자마다 위치맞춤하여, 전극형성물질, 예를 들면 몰리브덴-텅스텐합금(MoW)을 적절한 두께(예를 들면  $300\text{nm}$ )로 퇴적하고, 소정형상으로 패터닝하여 게이트전극을 형성하고, 이 게이트전극을 마스크로 하여 소스영역 및 드레인영역을 각각 형성한 후, 절연물질(예를 들면 산화실리콘)에 의해 게이트전극을 둘러싼 층간절연막을 형성한다. 더욱, 상기 소스영역 및 드레인영역상의 제 2 제어층에 콘택트홀을 형성한 후, 이 홀내에 전극물질(예를 들면 알루미늄)을 퇴적하여 패터닝하고, 소스전극 및 드레인전극을 형성하고, 이에 따라, 예를 들면 도 5의 (a), (b)에 나타낸 바와 같이, 기하학적인 배열형태로 규칙적으로 정렬배치된 각 단결정마다 1단위의 전극회로가 정연히 배치되고, 그에 따라, 종래의 단결정 반도체 박막기판을 사용한 장치의 통상의 이동도를 넘는, 예를 들면  $300\text{cm}^2/\text{V} \cdot \text{sec}$  이상의 이동도를 가진 박막 반도체장치를 얻을 수 있게 된다.

<42> 필요에 따라, 특정한 단결정에는 전극배치를 생략하거나, 1개의 단결정마다 복수의 단위회로를 설치하도록 할 수도 있다. 또한, 상기의 전극배치순서는 N채널형의 박막 트랜지스터제조의 경우이지만, 부분적으로 마스크하여 불순물을 순차 주입함으로써, CMOS 트랜지스터의 구성으로 할 수 있음은 물론이다. 또한, 제 2 제어층을 직접 게이트 절연막으로서 사용하는 대신에, 단결정 정렬층을 형성한 후, 제 2 제어층을 에칭제거하여 그 부분에 새로운 게이트 절연막을 형성하여도 좋다. 또한, 인접한 트랜지스터 사이에 리크전류가 생길 우려가 있는 경우에는, 결정화 전 또는 결정화 후에, 에칭 등에 의해 섬분리(Islands separation)를 실시하여도 좋다.

<43> [실시예]

<44> 외형치수  $400 \times 500\text{mm}$ , 두께  $0.7\text{mm}$ , 변형 포인트  $650^\circ\text{C}$ 의 코닝사제의 비 알카리 유리기판의 표면상에, 제 1 열전도 · 결정제어층으로서,  $200\text{nm}$  두께의 산화실리콘( $\text{SiO}_2$ )막을 플라즈마 CVD법에 의해 성막하고, 그 위에, 비단결정 반도체층으로서  $50\text{nm}$  두께의 비정질 실리콘(a-Si:H)막과, 더욱 그 위에, 제 2 열전도 · 결정제어층으로서  $200\text{nm}$  두께의 산화실리콘막을, 대기에 노출시키는 일 없이 연속적으로 성막하였다.

<45> 다음에, 상기 비정질 실리콘막층을 어닐링하여, 탈수소처리한 후, 위쪽에서부터, 파장  $308\text{nm}$ 의 펄스상태 엑시머 · 레이저광을 조사하여 비정질 실리콘막층을 결정화시켰다. 레이저조사는, 엑시머 · 레이저광을  $5 \times 5\text{mm}$ 의 단형의 레이저광으로 정형하고, 더욱 위상 시프트 마스크에 의해 면내에 강도분포를 갖게 한 레이저광을 1조사유니트로서 행하였다. 강도분포는,  $5 \times 5\text{mm}$ 의 단형영역내에,  $10\mu\text{m}$  간격으로 합계 25만개소의 최대치가 정방형격자형상으로 배열하는 형태인 것으로 하였다. 이 실시예에서는 용융역치가 약  $0.5\text{J}/\text{cm}^2$ , 레이저광 강도의 최대치는  $1.8\text{J}/\text{cm}^2$ , 최소치는  $0.1\text{J}/\text{cm}^2$ 이었다.

<46> 상기의 형태의 엑시머 · 레이저광조사를, 조사마다  $5\text{mm}$ 의 간격으로 단계 이동시켜 수광체 전체면의 조사율을 하였다. 조사완료 후에 Secco 에칭법에 의한 에칭을 실시하여, 주사형 전자현미경에 의한 관찰을 한 바, 입자지를  $4\mu\text{m}$ 의 단결정입자가 격자형상으로 규칙적으로 배열하고 있는 기판을 얻을 수 있는 것을 알 수 있었다.

<47> 이어서, 스파터법에 의해 몰리브덴-텅스텐합금(MoW)막을  $300\text{nm}$  두께로 퇴적하여, 각 단결정입자상에 위치 맞춤하고, 소정형상으로 패터닝하여 게이트전극을 형성하였다. 이 게이트전극을 마스크로 하여 인을 이온주입하여, 소스 및 드레인영역을 형성하였다. 다음에, 층간실리콘막으로서 플라즈마 CVD법에 의해 산화실리콘막을 퇴적하여, 소스 및 드레인영역을 위의 제 2 열전도 · 결정제어층 및 층간절연막에 콘택트홀을 형성하고, 계속해서 알루미늄(Al)막을 형성하여, 박막 트랜지스터장치를 완성시켰다. 이 장치의 이동도의 평균치는  $496\text{cm}^2/\text{V} \cdot \text{sec}$ 였다.

## 도면

## 도면1

(a)

(b)

(c)

(d)

도면2

도면3

도면4

## 도면5

(a)

(b)

## 도면6

도면7