US 20110238900A1

### (19) United States

## (12) Patent Application Publication Heo et al.

#### (54) METHOD OF MANAGING A SOLID STATE DRIVE, ASSOCIATED SYSTEMS AND IMPLEMENTATIONS

(76) Inventors: **Jin Gyu Heo**, Seoul (KR); **Donggi**

Lee, Yongin-si (KR); Seongsik Hwang, Seoul (KR); Dongjin Lee, Seoul (KR); Jeong Woo Lee, Seoul (KR); Wonmoon Cheon, Hwaseong-si (KR); Seungho Lim,

Suwon-si (KR); Jong-Min Kim, Anyang-si (KR); Jae-Hwa Lee, Haeundae-gu (KR); Haeri Lee, Yongsin-si (KR); Woonhyug Jee,

Suwon-si (KR)

(21) Appl. No.: 13/067,436

(22) Filed: Jun. 1, 2011

#### Related U.S. Application Data

(62) Division of application No. 12/585,935, filed on Sep. 29, 2009. (43) **Pub. Date:** Sep. 29, 2011

(10) Pub. No.: US 2011/0238900 A1

(60) Provisional application No. 61/136,822, filed on Oct. 7, 2008.

#### (30) Foreign Application Priority Data

| Sep. 30, 2008 | (KR) | 10-2008-0096117 |

|---------------|------|-----------------|

| Oct. 15, 2008 | (KR) | 10-2008-0101093 |

| Oct. 15, 2008 | (KR) | 10-2008-0101095 |

| Oct. 15, 2008 | (KR) | 10-2008-0101097 |

| Oct. 15, 2008 | (KR) | 10-2008-0101098 |

#### **Publication Classification**

(51) **Int. Cl.** *G06F 12/02* (2006.01)

(52) **U.S. Cl.** ...... 711/103; 711/E12.008

#### (57) ABSTRACT

In one embodiment, the method includes storing, by a status checking module, status information for a solid state drive, and determining a status state of the solid state drive based on the status information. The status state is one of a good state, an intermediate state and a bad state, and the intermediate state is a state between the good state and the bad state.

Fig. 1

Fig. 2

| Value   | Command                                 |

|---------|-----------------------------------------|

| 00h-CFh | Reserved                                |

| D0h     | SMART READ DATA                         |

| D1h     | Obsolete                                |

| D2h     | SMART ENABLE/DISABLE ATTRIBUTE AUTOSAVE |

| D3h     | SMART SAVE ATTRIBUTE VALUES             |

| D4h     | SMART EXECUTE OFF-LINE IMMEDIATE        |

| D5h     | SMART READ LOG                          |

| D6h     | SMART WRITE LOG                         |

| D7h     | Obsolete                                |

| D8h     | SMART ENABLE OPERATIONS                 |

| D9h     | SMART DISABLE OPERATIONS                |

| DAh     | SMART RETURN STATUS                     |

| DBh     | Obsolete                                |

| DCh-DFh | Reserved                                |

| E0h-FFh | Vendor Specific                         |

Fig. 3

| Byte    | F/V | Descriptions                                                                   |  |

|---------|-----|--------------------------------------------------------------------------------|--|

| 0-361   | Х   | Vendor speciifc                                                                |  |

| 362     | ٧   | Off-line data collection status                                                |  |

| 363     | Х   | Self-test execution status byte                                                |  |

| 364-365 | V   | Total time in seconds to complete off-line data collection activite            |  |

| 366     | Х   | Vendor specific                                                                |  |

| 367     | F   | Off-line data collection capability                                            |  |

| 368-369 | F   | SMART capability                                                               |  |

| 370     | F   | Error logging capability<br>7-1 Reserved<br>0 1=Device error logging supported |  |

| 371     | Χ   | Vendor specific                                                                |  |

| 372     | F   | Short self-test routine recommended polling time(in minutes)                   |  |

| 372     | F   | Extended self-test routine recommended polling time(in minutes)                |  |

| 374-385 | R   | Reserved                                                                       |  |

| 386-510 | Х   | Vendor specific                                                                |  |

| 511     | ٧   | Data structure checksum                                                        |  |

#### Key:

F=The content of the byte is fixed and does not change.

V=The content of the byte is variable and may chage depending on the state of the device or the commands executed by the device.

X=The content of the byte is vendor specific and may be fixed or variable

R=The content of the byte is reserved and shall be zero

Fig. 4

| Byte  | F/V | Descriptions              |

|-------|-----|---------------------------|

| 0~1   | Х   | SSD's smart data version  |

| 2~3   | X   | Reserved block count      |

| 4~7   | ٧   | Runtime bad block count   |

| 8~11  | V   | Wear leveling count       |

| 12~15 | Х   | Uncorrectable error count |

| 16~19 | Х   | Program/erase fail count  |

| 20~23 | Χ   | Column fail count         |

| Flash   |                                                         |                                                                                                                          | Parameters                                                                                                              | eters                                    |                          |               |     | Result |      | , o l co : C |

|---------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------|---------------|-----|--------|------|--------------|

| Status  | Ра                                                      | q <sub>d</sub> .                                                                                                         | Pc                                                                                                                      | Pd                                       | Pe                       | Ρf            | Por | Pand   | Psum | urspray      |

| poog    | a1-a2                                                   | b1-b2                                                                                                                    | c1-c2 d1-d2                                                                                                             | d1-d2                                    | e1-e2                    | f1-f2         |     |        |      | uee 19       |

| Warning | a3-a4                                                   | p3-p4                                                                                                                    | c3-c4 d3-d4                                                                                                             | d3-d4                                    | e3-e4                    | f3-f4         |     |        |      | Wellow       |

| Bad     | a5-a6                                                   | 9q-5q                                                                                                                    | b5-b6 c5-c6 d5-d6                                                                                                       | 9p-9p                                    | e5-e6   f5-f6            | f5–f6         |     | ,      |      | Red          |

|         | Pa=Reser<br>Pb=Runti<br>Pc=Wear<br>Pd=Uncor<br>Pe=Progr | · · · _                                                                                                                  | ved block count<br>me bad block count<br>leveling count<br>rectable error count<br>am/Erase fail count<br>in fail count | unt<br>count<br>nt<br>or coun<br>I count | t t                      |               |     |        |      |              |

|         | Por=(Pa<br>Pand=(Pa<br>Psum=F(F                         | Por=(Pa or Pb or Pc or Pd or Pe or Pf)<br>Pand=(Pa and Pb and Pc and Pd and Pe and Pf)<br>Psum=F(Pa, Pb, Pc, Pd, Pe, Pf) | or Pb or Pc or Pd or Pe or Pf)<br>a and Pb and Pc and Pd and Pe a<br>Pa, Pb, Pc, Pd, Pe, Pf)                            | or Pd c<br>Pc and<br>'d, Pe,             | r Pe or<br>Pd and<br>Pf) | Pf)<br>Pe and | Df) |        |      |              |

Determine 'GREEN' displaying good status **S142** \$143 Output good data for 2 S130 displaying intermediate status \$132 **S133** 5131 Output intermediate data for ntermediate status Determine 'YELLOW' Yes 2 **S120** Determine 'RED' displaying bad status \$123 \$122 \$121 Check status information of flash memory Output bad data Bad status Yes Start End for

Fig. 7

Fig. 8

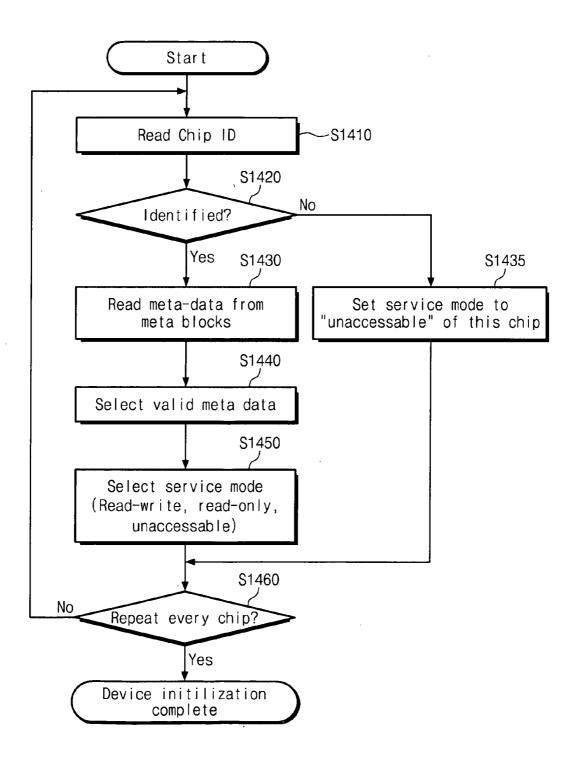

Fig. 11

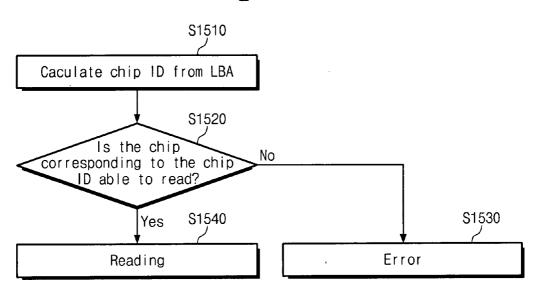

Fig. 12

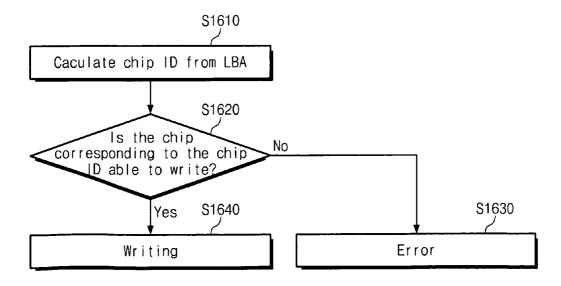

Fig. 13

Fig. 14

Fig. 15

Fig. 16

Fig. 17

|                  | 4KB              | Page             | •                |

|------------------|------------------|------------------|------------------|

| Meta for Chip[1] | Meta for Chip[2] | Meta for Chip[3] | Meta for Chip[4] |

Fig. 18

|                         | 4KB                     | Page                    | •                       |

|-------------------------|-------------------------|-------------------------|-------------------------|

| Smart info. for Chip[1] | Smart info. for Chip[2] | Smart info. for Chip[3] | Smart info. for Chip[4] |

Fig. 19

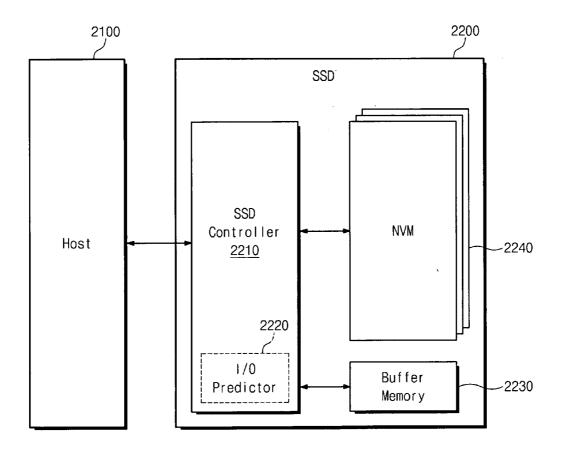

Fig. 20

Fig. 21

Fig. 22

-2222 2220 & FTL Interfaces Replacement DB Pattern DB DB Manager 불 Fig. 23 210 Flash Transition Layer Flash Interface Layer Host Interface Layer

-2260

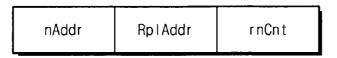

nCnt3 Nex13(2264) LBA\_3 Next nAddr3 nCnt2 LBA\_2 LBA\_2 Next2(2263) Fig. 24A Fig. 24B Read Sequences Next nAddr2 LBA\_b LBA\_1 Pattern DB LBA\_1 nCnt1 Next1(2262) LBA\_0 LBA\_x LBA\_0 LBA\_0 Next nAddr1 RS4 RS1 RS2 RS3 nCnt Current (2261) nAddr

Fig. 24C

Fig. 25

Fig. 26

Fig. 28

# Fig. 29

Fig. 30

Fig. 31

Fig. 32

Fig. 33

Fig. 34

Fig. 35

Fig. 36

Fig. 37

Fig. 38

Fig. 39

Fig. 40

3400 N N SSD Controller 3414 nterface Flash CPU BUS -3411 3413 SRAM Cache CPU 3412 ATA Interface ATA Protocol

Fig. 42

Fig. 43

Fig. 44

Fig. 45

Fig. 46

Fig. 47

Fig. 48

Fig. 49

Fig. 50

Fig. 51

Fig. 52

Fig. 53

Fig. 54

## METHOD OF MANAGING A SOLID STATE DRIVE, ASSOCIATED SYSTEMS AND IMPLEMENTATIONS

# CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This application is a divisional of application Ser. No. 12/585,935, filed Sep. 29, 2009, which claims priority under 35 U.S.C. §119 to Korean Patent Application Nos. 10-2008-0096117, 10-2008-0101093, 10-2008-0101095, 10-2008-0101097 and 10-2008-0101098 in the Korean Intellectual Property Office (KIPO) filed on Sep. 30, 2008, Oct. 15, 2008, Oct. 15, 2008, Oct. 15, 2008 and U.S. Provisional Application No. 61/136,822 filed on Oct. 7, 2008 the entire contents of all of which are herein incorporated by reference.

#### BACKGROUND

[0002] In general, a memory system includes a memory device for storing data and a host for controlling operations of the memory device. The memory device is classified into a volatile memory (such as DRAM, SRAM, and so forth) and a non-volatile memory (such as EEPROM, FRAM, PRAM, MRAM, flash memory, and so forth).

[0003] The volatile memory loses its stored data when power supply is cut off, but the non-volatile memory retains its stored data even when there is no power supply. Among non-volatile memories, the flash memory is widely used as a data storage medium because of advantages such as a high programming speed, lower power consumption, high capacity data storage, and so forth.

[0004] A memory device demanding a high degree of integration causes defective products because of a plurality of limited requirements in manufacturing processes. Various trials have been made in order to resolve yield decrease and defects, which are caused by the factors such as the high degree of integration of a memory device. However, if a memory device is mounted in a memory system and is in operation, it is difficult for a user to determine defectiveness of a memory device.

[0005] A high capacity storage device such as a flash memory card or a solid state disk (SSD) has a typical structure including a plurality of flash memory chips. In general, the SSD is designed to replace a hard disk drive, and therefore, has a significantly larger capacity than a memory card. For example, the SSD may have one or two orders of magnitude greater storage space. Accordingly, the SSD includes many more flash memory chips than a memory card. In some flash memory chips, if the number of bad blocks is drastically increased due to program/erase fails and pre-reserved replacement blocks are all consumed, no more service is available.

**[0006]** A semiconductor memory device is a memory device capable of reading data when necessary after storing the data. The semiconductor memory device is largely classified into a random access memory (RAM) and a read only memory (ROM). Data stored in the RAM disappears when power supply is cut off. This type of a memory is called a volatile memory. On the contrary, data stored in the ROM does not disappear even when there is no power supply. This type of a memory is called a non-volatile memory.

[0007] A kind of the non-volatile memory device includes a flash memory device. The flash memory device is largely

classified into a NOR type and a NAND type. Recently, portable electronic devices such as digital cameras, MP3 players, mobile phones, PDAs, and so forth use flash memories. This is because the flash memory is a non-volatile device having characteristics such as low power consumption and the high degree of integration. Because the flash memory is used in the portable electronic device, the reliability and life cycle of the flash memory are closely related to those of the portable electronic device. Accordingly, it is desirable to improve the reliability and life cycle of the flash memory.

[0008] Other specific volatile memory devices include SRAM, DRAM, and SDRAM. Other non-volatile memory devices include ROM, PROM, EPROM, EEPROM, PRAM, MRAM, RRAM, and FRAM.

[0009] Lately, a semiconductor disk device using a semiconductor memory device has been developed. The semiconductor disk device is better than a hard disk using a rotational disk, in aspects of reliability and speed. Accordingly, a computing system using the semiconductor disk device instead of a hard disk as a storage device has been developed.

## **SUMMARY**

[0010] At least one example embodiment relates to a method of monitoring a status of a solid state drive.

[0011] In one embodiment, the method includes storing, by a status checking module, status information for a solid state drive, and determining a status state of the solid state drive based on the status information. The status state is one of a good state, an intermediate state and a bad state, and the intermediate state is a state between the good state and the bad state.

[0012] At least another embodiment relates to a system.

[0013] In one embodiment, the system includes a solid state drive and a status checking module. The status checking module is configured to access status information on the solid state drive and to determine a status state of the solid state drive based on the accessed status information. The status state is one of a good state, an intermediate state and a bad state, and the intermediate state is a state between the good state and the bad state.

[0014] In another embodiment, the system includes a solid state drive, a status checking module, and a host. The status checking module is configured to store status information on the solid state drive. The host is configured to access the status information and to determine a status state of the solid state drive based on the accessed status information. The status state is one of a good state, an intermediate state and a bad state, and the intermediate state is a state between the good state and the bad state.

[0015] At least one example embodiment relates to a method of monitoring a status of a solid state drive.

[0016] In one embodiment, this method includes receiving, at a status checking module, a hard disk drive protocol command; accessing, by the status checking module, status information on a solid state drive in response to the hard disk drive protocol command; and determining a status of the solid state drive based on the accessed status information.

[0017] Another embodiment of the method includes accessing, by a status checking module, status information on a solid state drive. The status information includes a plurality of status parameters. The method further includes determining a status state associated with each status parameter, and determining a status of the solid state drive by performing an operation on the determined status states.

[0018] With respect to the above embodiments, the intermediate state may be a warning state indicating the solid state drive is approaching the bad state. As another example, the intermediate state may indicate to back-up the solid state drive.

[0019] The status information may include at least one of reserved block information, bad block information, wear leveling information, uncorrectable error information, program and erase cycle information, program/erase fail information and column fail information.

#### BRIEF DESCRIPTION OF DRAWINGS

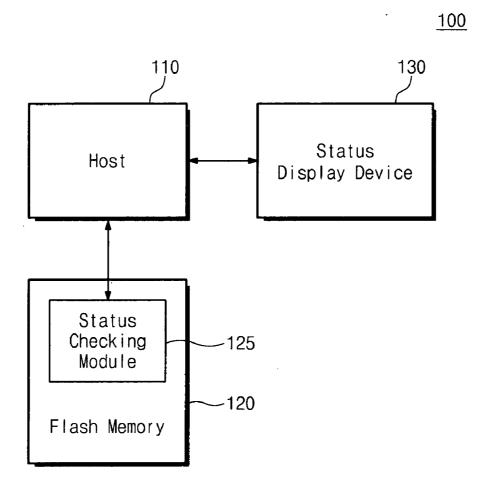

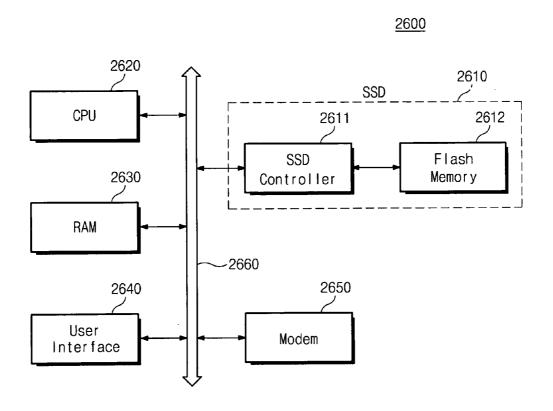

[0020] FIG. 1 is a block diagram illustrating a memory system according an first embodiment.

[0021] FIG. 2 is a table illustrating command formats that are obtained by classifying SMART commands based on a feature register value.

[0022] FIG. 3 is a table illustrating a data structure for a result value of a SMART READ DATA command.

[0023] FIG. 4 is a table illustrating status information of a flash memory through a data area that a manufacturer can use.

[0024] FIG. 5 is a table illustrating a method for determining a status of a flash memory through various parameters representing statuses of the flash memory.

[0025] FIG. 6 is a flowchart illustrating a method of testing a status of the flash memory of FIG. 1.

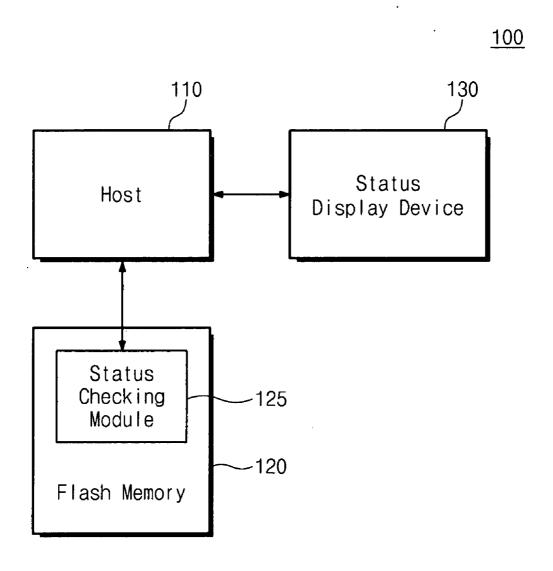

[0026] FIG. 7 is a block diagram illustrating a memory system according to another embodiment.

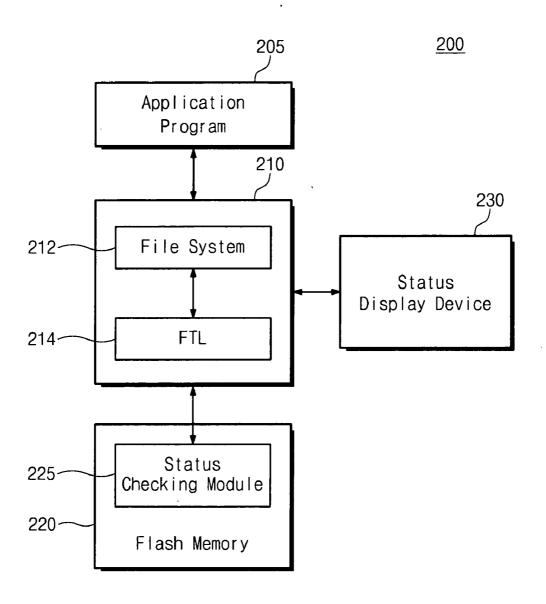

[0027] FIG. 8 is a block diagram illustrating a memory system according to another embodiment.

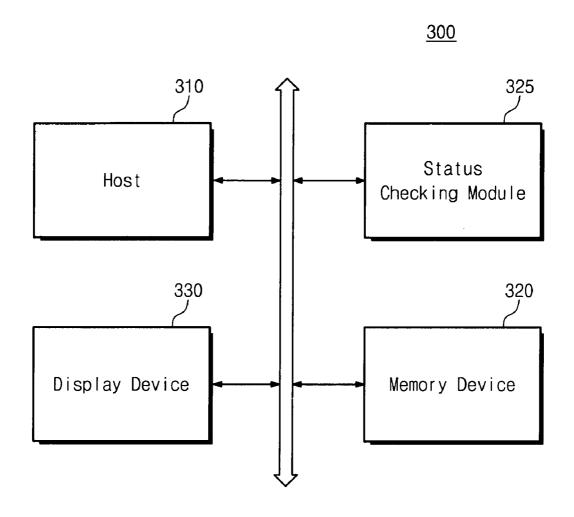

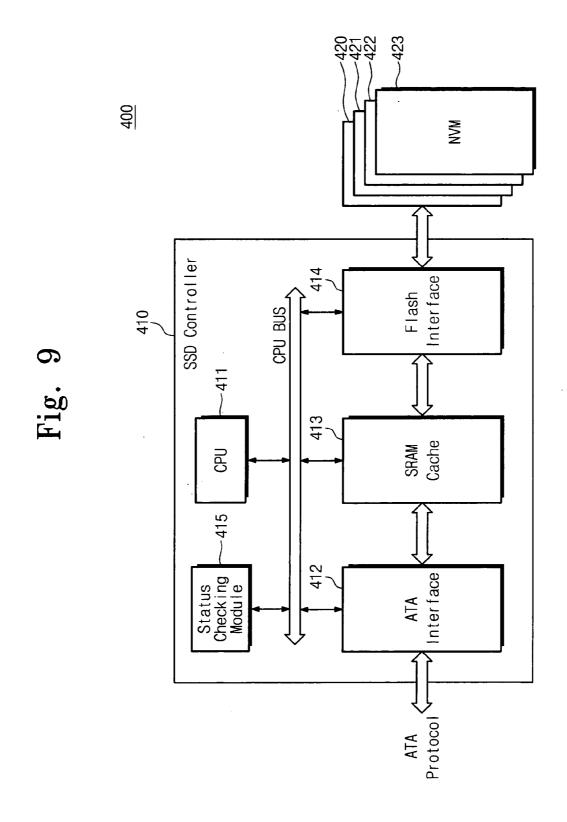

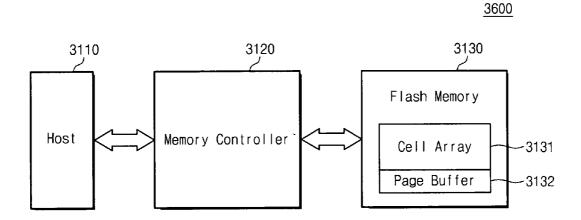

[0028] FIG. 9 is a block diagram illustrating a storage device according to an embodiment.

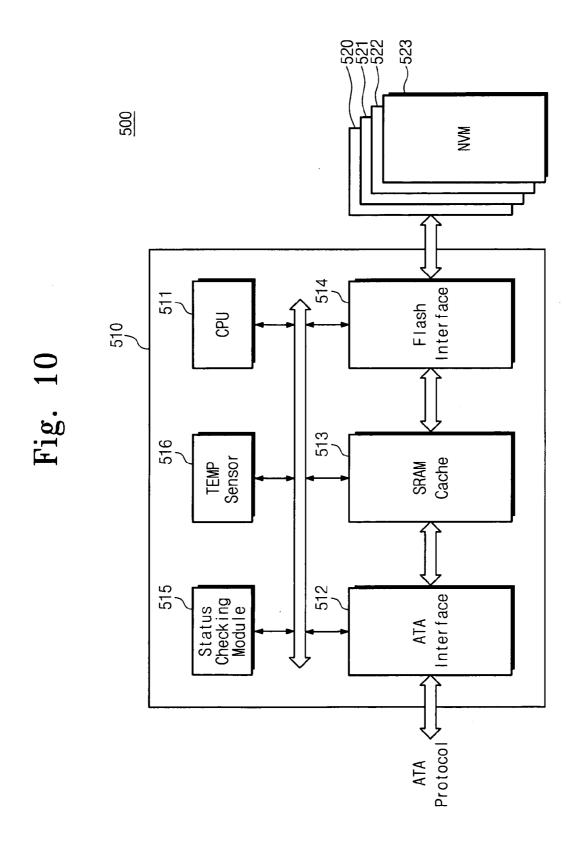

[0029] FIG. 10 is a block diagram illustrating a storage device according to an embodiment.

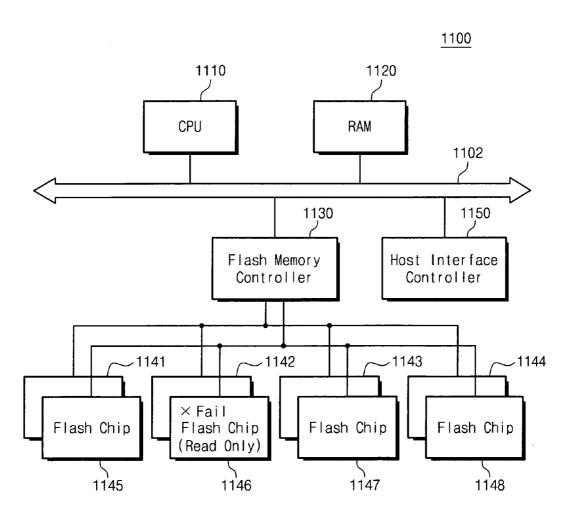

[0030] FIG. 11 is a view illustrating a hardware configuration of a memory storage device according to a second embodiment.

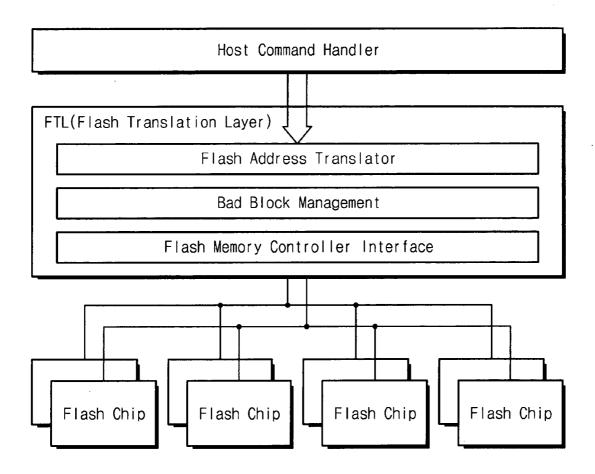

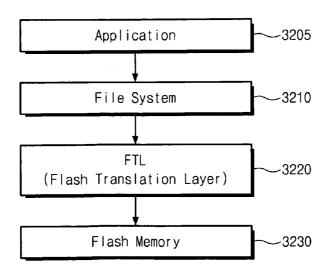

[0031] FIG. 12 is a view illustrating a software module structure of the flash memory storage device according to an embodiment.

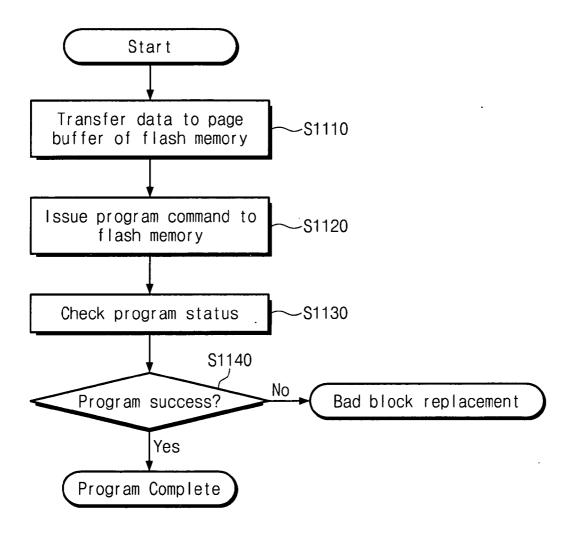

[0032] FIG. 13 illustrates a program flowchart of a flash memory according to an embodiment.

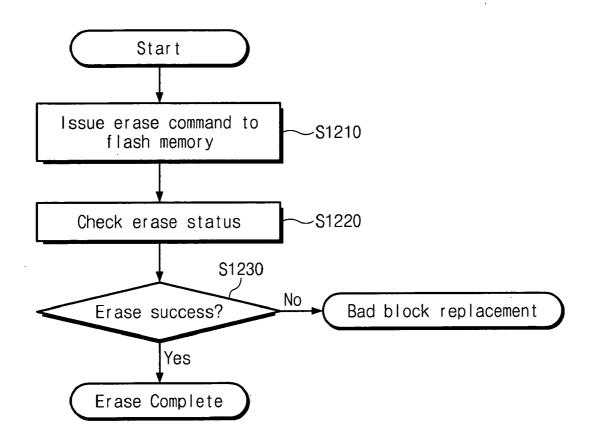

[0033] FIG. 14 illustrates an erase flowchart of a flash memory according to an embodiment.

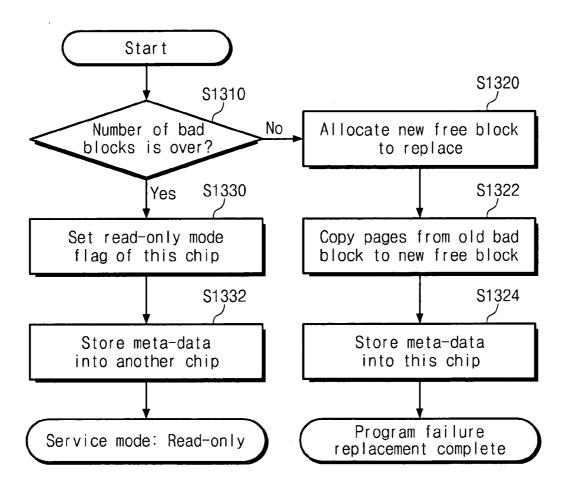

[0034] FIG. 15 illustrates a bad block replacement algorithm during a program fail operation according to an embodiment.

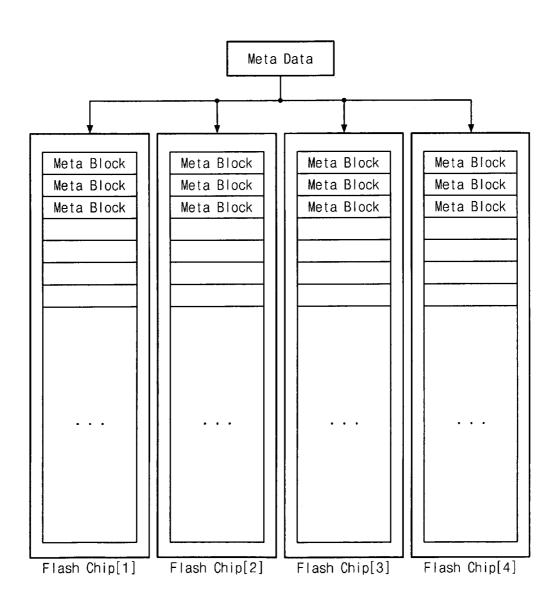

[0035] FIG. 16 illustrates a meta block configuration of a flash memory and a method of storing the same.

[0036] FIG. 17 illustrates a structure of meta data in a page of a flash memory.

[0037] FIG. 18 illustrates a SMART data structure in a page of a flash memory.

[0038] FIG. 19 is a flowchart illustrating an initialization process of the memory storage device of FIG. 11 according to an embodiment.

[0039] FIG. 20 is a flowchart illustrating a read operation of the flash storage device according to an embodiment.

[0040] FIG. 21 is a flowchart illustrating a write operation of the flash storage device according to an embodiment.

[0041] FIG. 22 is a block diagram illustrating technical features of a third embodiment according to inventive concepts of the present invention.

[0042] FIG. 23 is a block diagram illustrating a detailed configuration (or, software) of the SSD controller of FIG. 22.

[0043] FIG. 24A illustrates request sequences and will be

[0043] FIG. 24A illustrates request sequences and will be used to explain the method of creating and updating a pattern database.

[0044] FIG. 24B illustrates an entry in the pattern database. [0045] FIG. 24C illustrates a record in a replacement data-

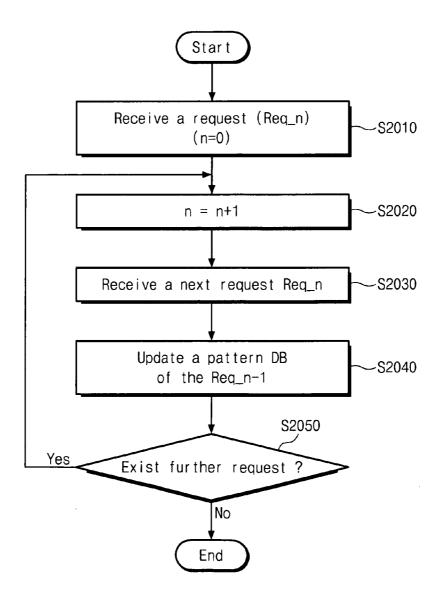

[0046] FIG. 25 is a flowchart illustrating a learning operation.

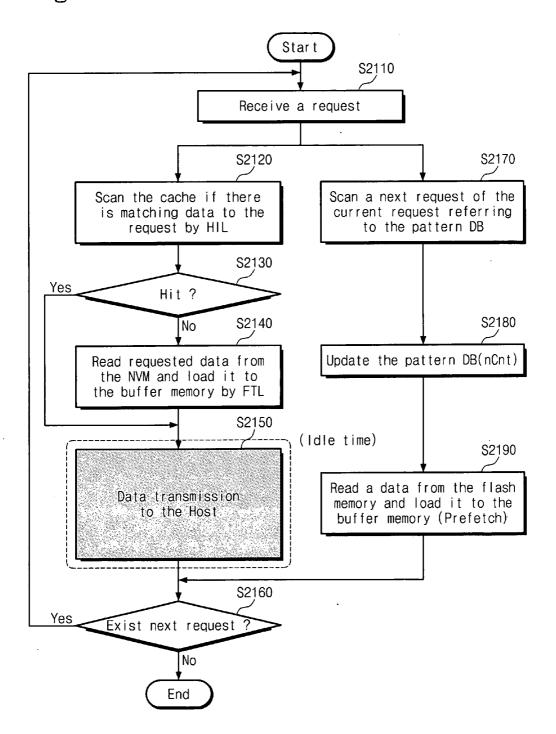

[0047] FIG. 26 is a flowchart illustrating a prediction and a pre-fetch operation with reference to a pattern database accumulated through the learning operation of FIG. 25.

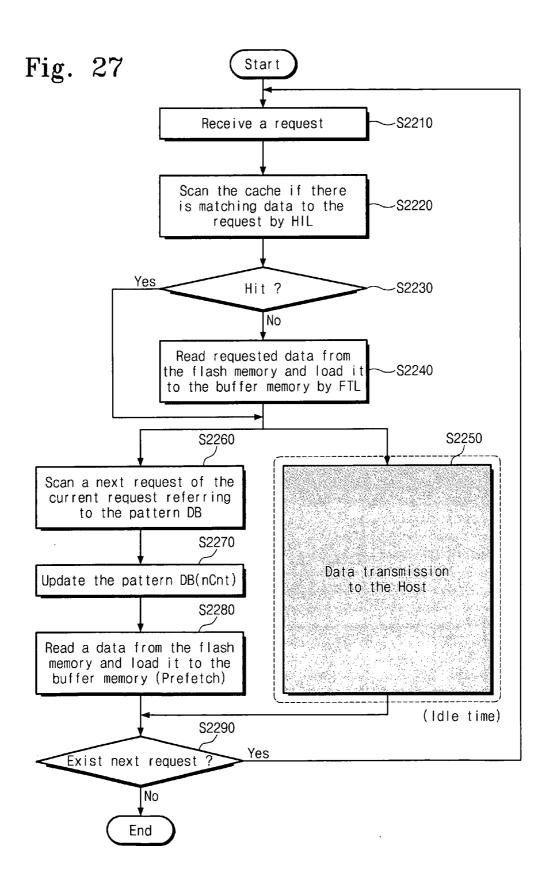

[0048] FIG. 27 is a flowchart illustrating a prediction operation and a pre-fetch operation according to another embodiment.

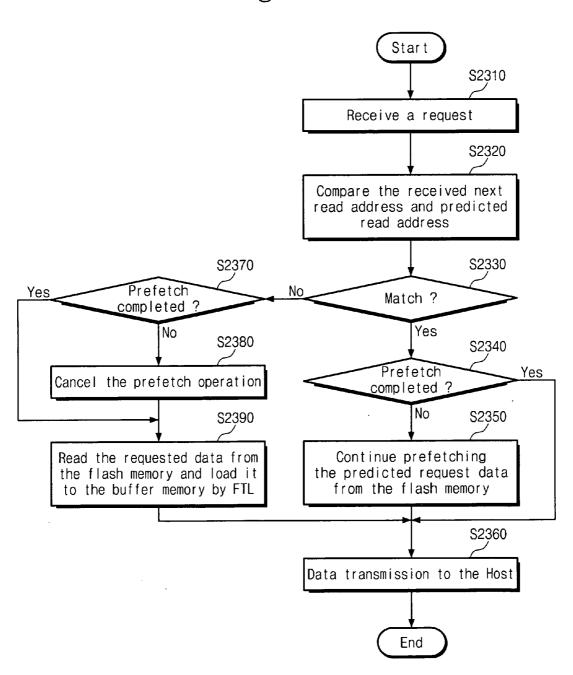

[0049] FIG. 28 is a flowchart illustrating handling of a next read request based on the prediction and pre-fetch operation according to an embodiment.

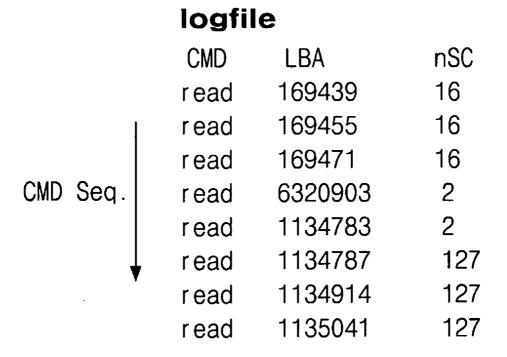

[0050] FIG. 29 is a view illustrating patterns of read requests inputted into SSD.

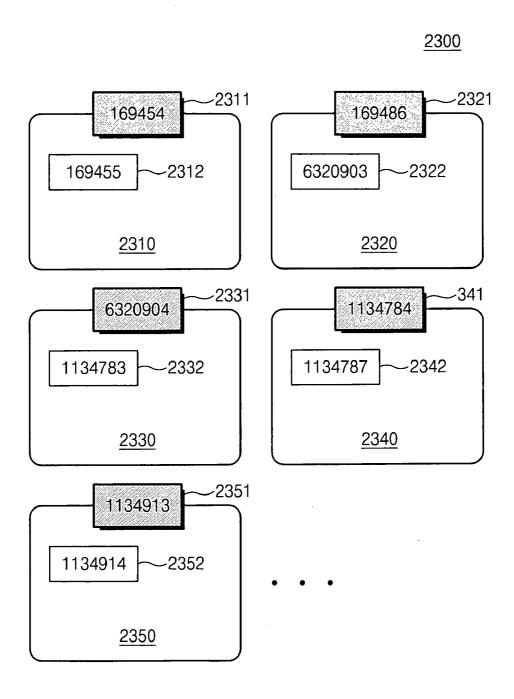

[0051] FIG. 30 is a view illustrating a pattern database configured based on a learning operation when the read requests of FIG. 29 are repeatedly inputted (for example, during a booting operation).

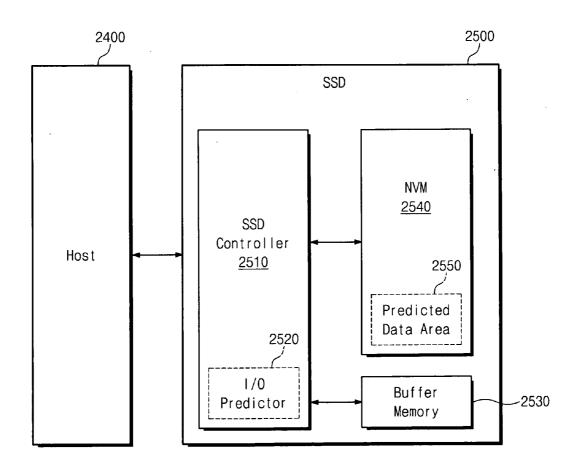

[0052] FIG. 31 is a block diagram illustrating SSD according to another embodiment.

[0053] FIG. 32 is a view illustrating a computing system including a SSD according to an embodiment.

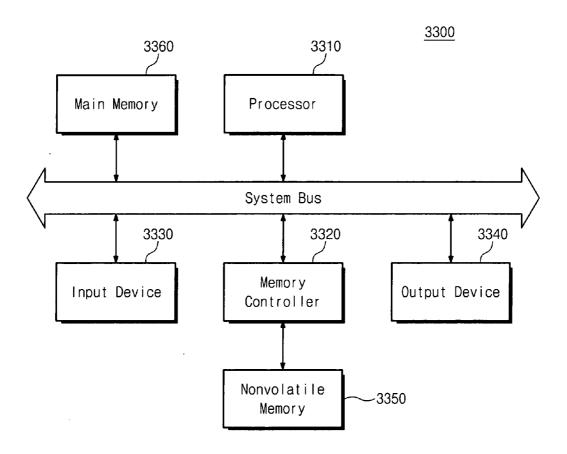

[0054] FIG. 33 is a view illustrating a memory system according to a fourth embodiment according to inventive concepts of the present invention.

[0055] FIG. 34 is a block diagram illustrating a software configuration of the memory system of FIG. 33.

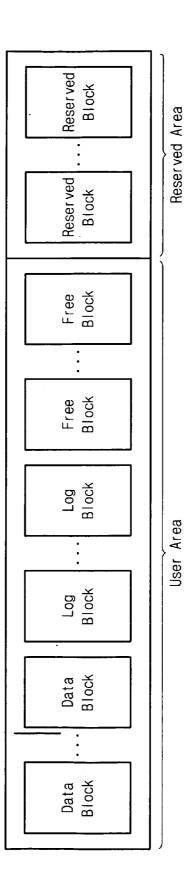

[0056] FIG. 35 is a view illustrating the memory cell array of FIG. 33.

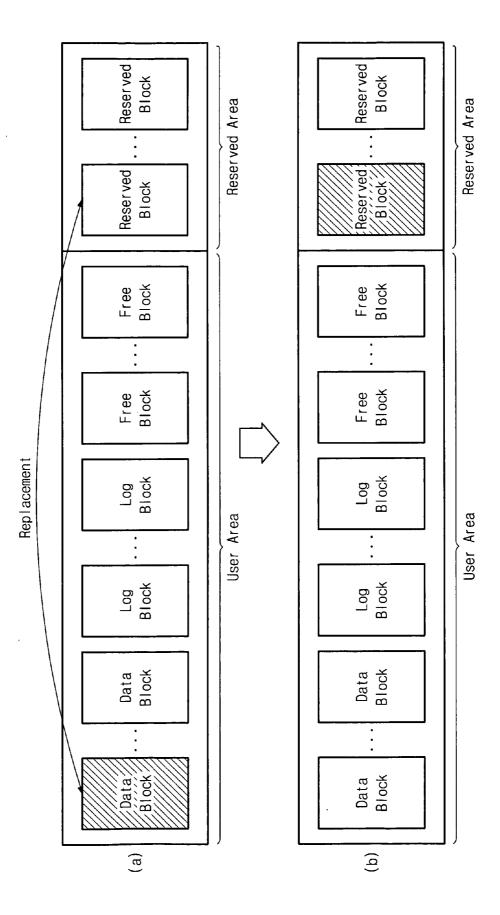

[0057] FIG. 36 is a view illustrating a method of replacing a defective memory block with a reserved block when there is a defective memory block in a user area.

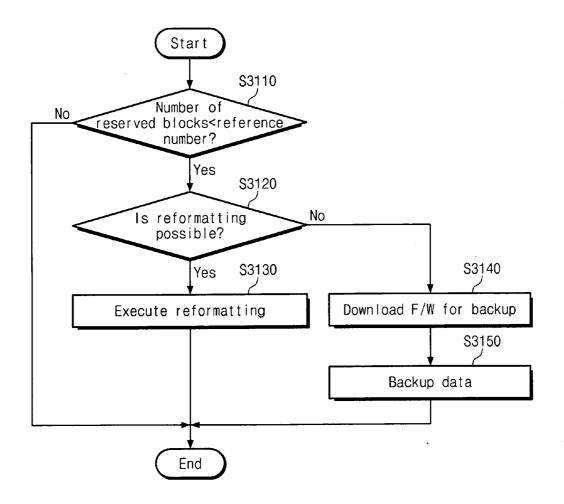

[0058] FIG. 37 is a flowchart illustrating a method of obtaining a reserved area according to an embodiment.

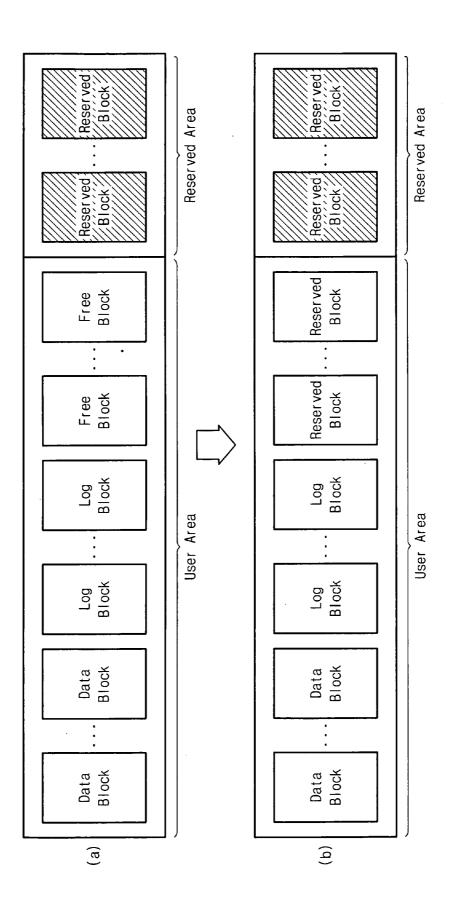

[0059] FIG. 38 is a view illustrating a method of obtaining a reserved area according another embodiment.

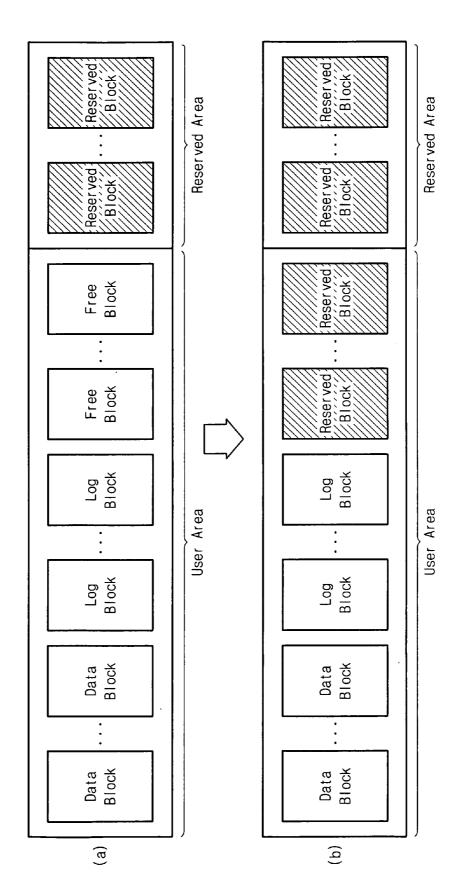

[0060] FIG. 39 is a view illustrating a method of obtaining a reserved area according to a further embodiment.

[0061] FIG. 40 is a block diagram illustrating a computing system including a flash memory according to an embodiment.

[0062] FIG. 41 is a block diagram illustrating a structure of a SSD system according to an embodiment.

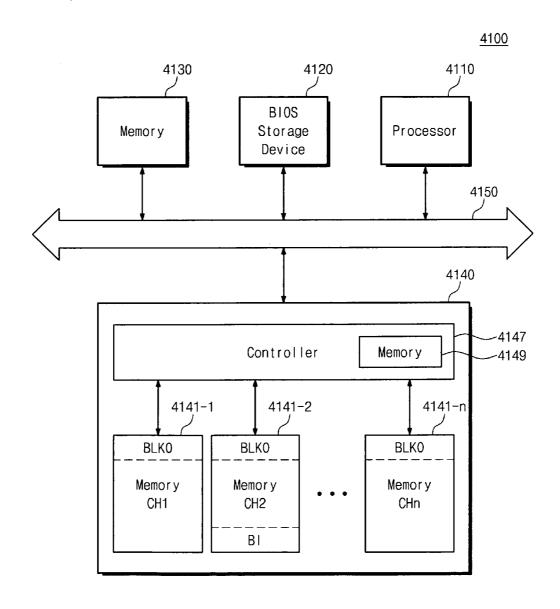

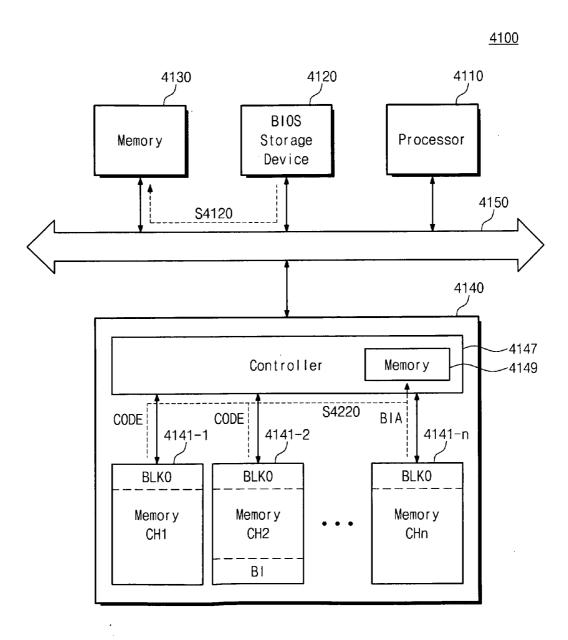

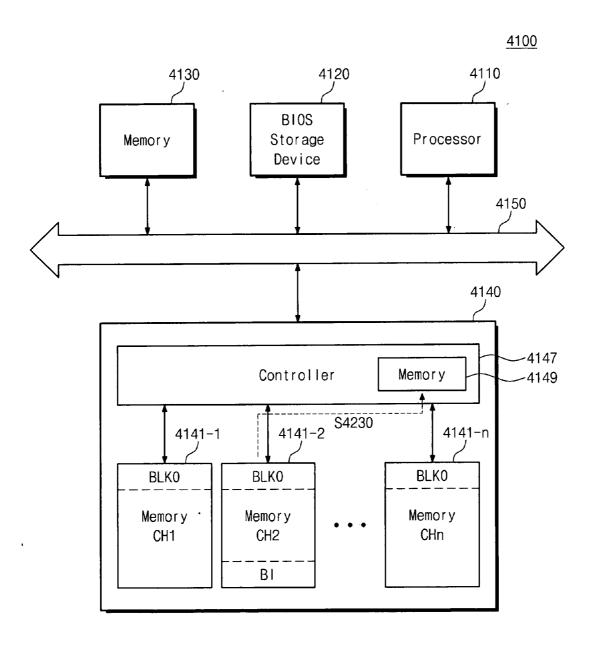

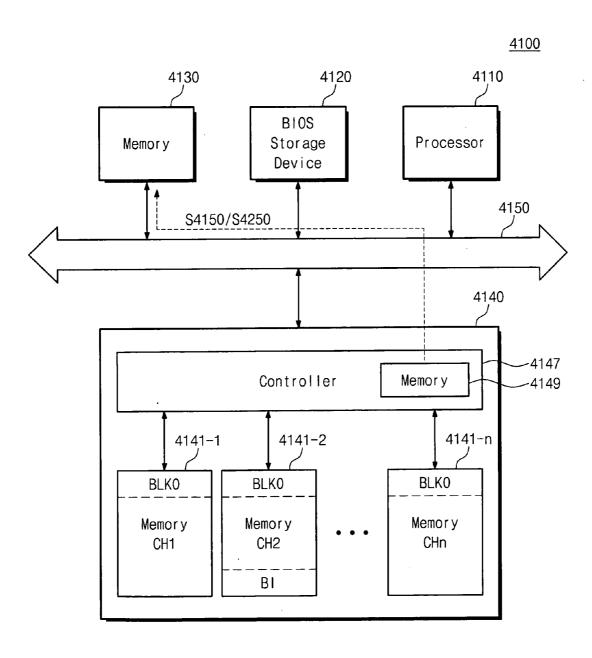

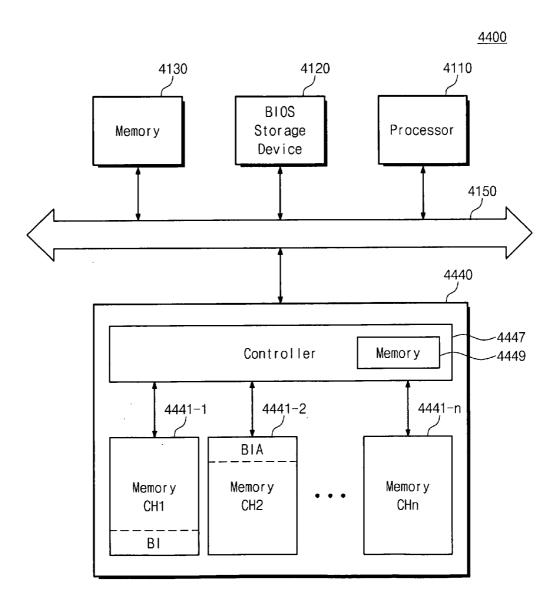

[0063] FIG. 42 is a block diagram illustrating a computing system according to a fifth embodiment of inventive concepts of the present invention.

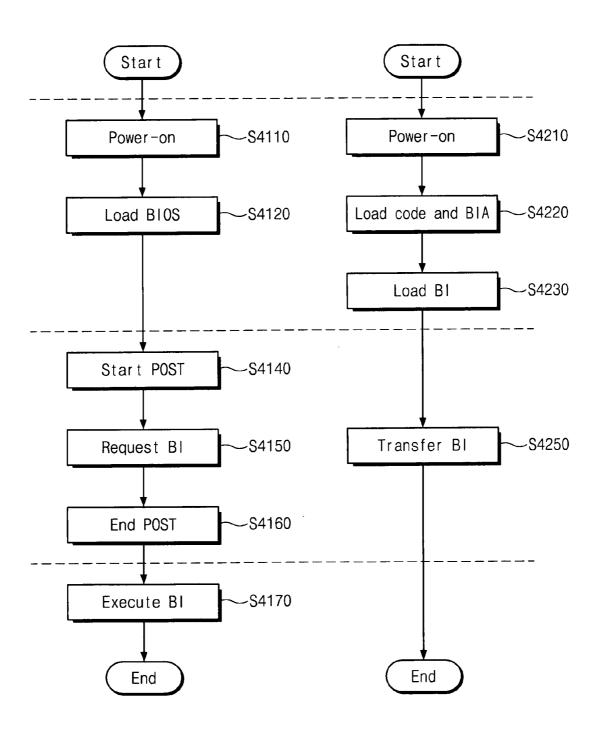

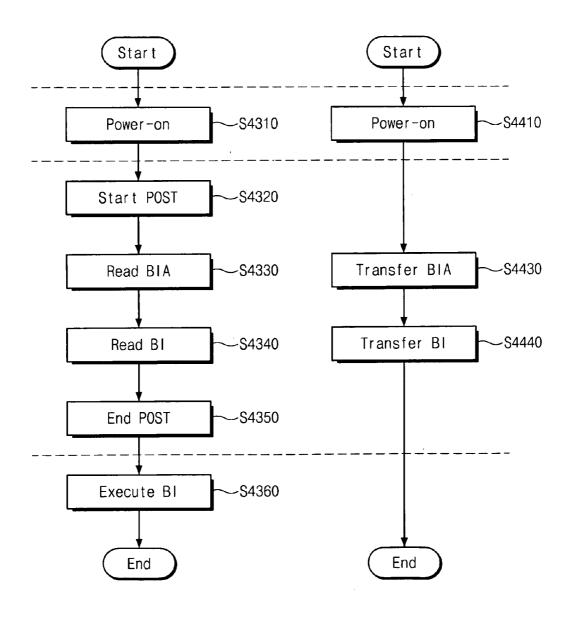

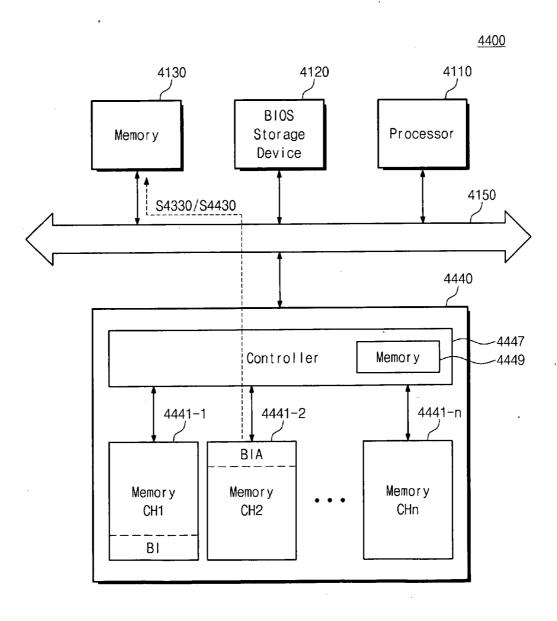

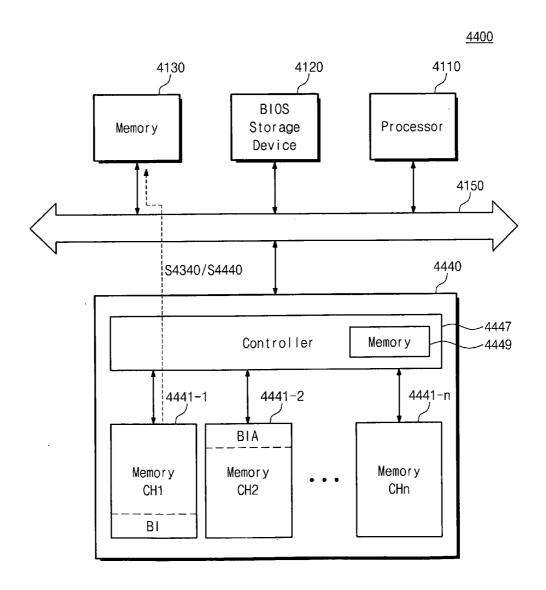

[0064] FIG. 43 is a flowchart illustrating an operation of the computing system of FIG. 42.

[0065] FIGS. 44 to 46 are block diagrams illustrating how the process of FIG. 43 is performed in the computing system of FIG. 42.

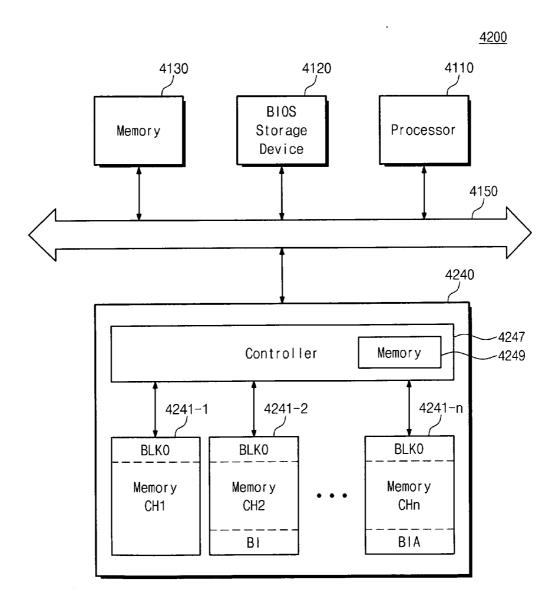

[0066] FIG. 47 is a block diagram illustrating a computing system according to another embodiment.

[0067] FIG. 48 is a block diagram illustrating a computing system according to a further embodiment.

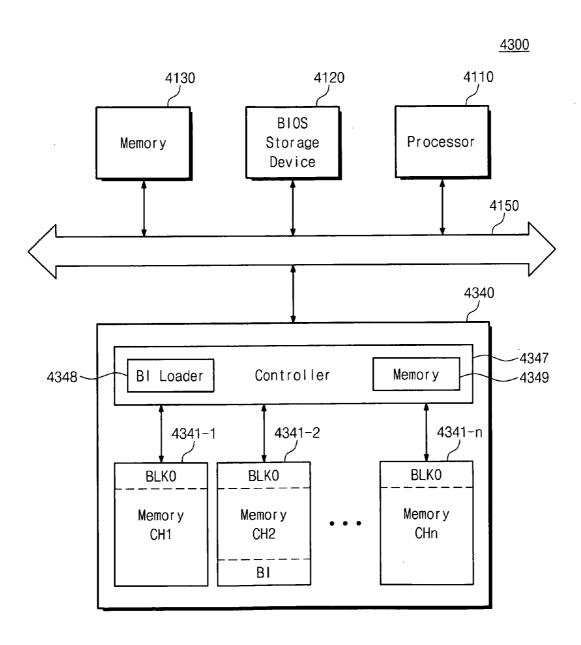

[0068] FIG. 49 is a block diagram illustrating a computing system according to a still further embodiment.

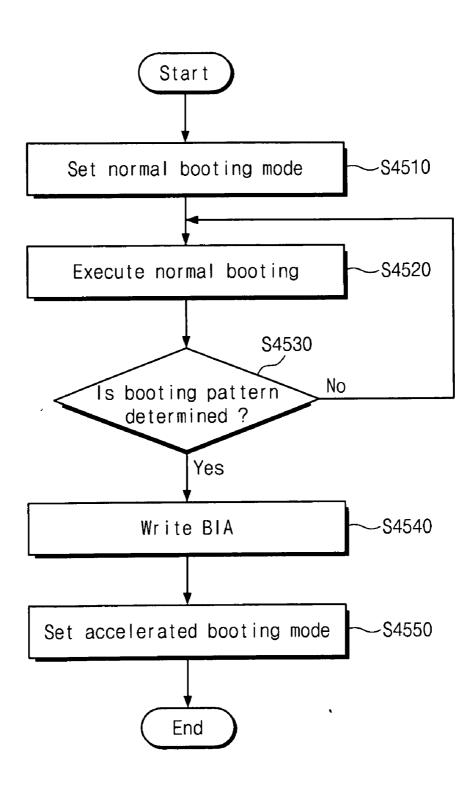

$[0069]\quad {\rm FIG.}\, 50$  is a flowchart illustrating an operation of the computing system of FIG. 49.

[0070] FIGS. 51 and 52 are block diagrams illustrating when the operations of FIG. 50 are performed in the computing system of FIG. 49.

[0071] FIG. 53 is a flowchart illustrating a method in which the computing system according to an embodiment of inventive concepts of the present invention detects a changed address of a boot image.

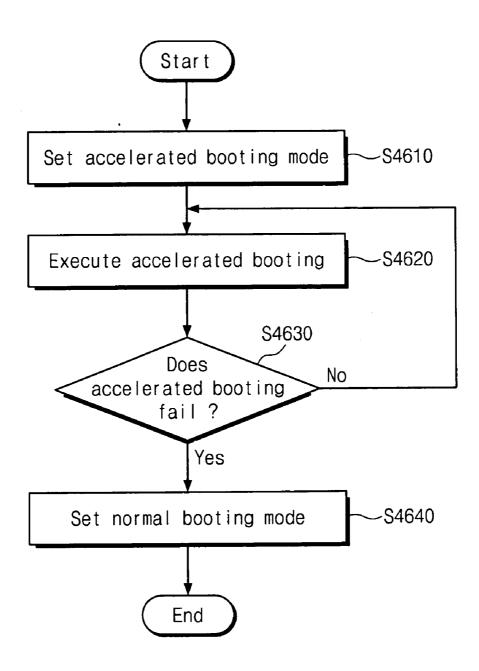

[0072] FIG. 54 is a flowchart illustrating an operation of the computing system according to an embodiment when booting fail occurs during an accelerated booting mode.

## DETAILED DESCRIPTION

[0073] Various example embodiments will now be described more fully with reference to the accompanying drawings in which some example embodiments of the invention are shown. In the drawings, the thicknesses of layers and regions are exaggerated for clarity.

[0074] Specific structural and functional details disclosed herein are merely representative for purposes of describing example. This invention may be embodied in many alternate forms and should not be construed as limited to only the embodiments set forth herein.

[0075] Accordingly, while example embodiments of the invention are capable of various modifications and alternative forms, embodiments thereof are shown by way of example in the drawings and will herein be described in detail. It should be understood, however, that there is no intent to limit example embodiments of the invention to the particular forms disclosed, but on the contrary, example embodiments of the invention are to cover all modifications, equivalents, and alternatives falling within the scope of the invention. Like numbers refer to like elements throughout the description of the figures.

[0076] It will be understood that, although the terms first, second, etc. may be used herein to describe various elements, these elements should not be limited by these terms. These terms are only used to distinguish one element from another. For example, a first element could be termed a second element, and, similarly, a second element could be termed a first element, without departing from the scope of example embodiments. As used herein, the term "and/or" includes any and all combinations of one or more of the associated listed items.

[0077] It will be understood that when an element is referred to as being "connected" or "coupled" to another element, it can be directly connected or coupled to the other element or intervening elements may be present. In contrast, when an element is referred to as being "directly connected" or "directly coupled" to another element, there are no intervening elements present. Other words used to describe the relationship between elements should be interpreted in a like fashion (e.g., "between" versus "directly between", "adjacent" versus "directly adjacent", etc.).

[0078] The terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting of example embodiments of the invention. As used herein, the singular forms "a", "an" and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. It will be further understood that the terms "comprises", "comprising,", "includes" and/or "including", when used herein, specify the presence of stated features, integers, steps, operations, elements, and/or compo-

nents, but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof.

[0079] It should also be noted that in some alternative implementations, the functions/acts noted may occur out of the order noted in the figures. For example, two figures shown in succession may in fact be executed substantially concurrently or may sometimes be executed in the reverse order, depending upon the functionality/acts involved.

[0080] Hereinafter, embodiments according to inventive concepts of the present invention will be described in more detail with reference to the accompanying drawings in order that a person of ordinary skill in the art may easily implement the technical idea of inventive concepts of the present invention.

[0081] Inventive concepts of the present invention relates to a nonvolatile memory device, a memory system (e.g. a solid state drive SSD) including a nonvolatile memory device and a computing system including a memory system having a nonvolatile memory device. Inventive concepts of the present invention provides a nonvolatile memory device, a memory system (e.g. a SSD) and a computing system including a memory system having a nonvolatile memory device having advanced reliabilities and advanced operating speed. For example, a flash memory device, a memory system (e.g. a SSD) including a flash memory device and a computing system including a memory system having a flash memory device are described. However, the technical spirit according to inventive concepts of the present invention is not limited to a flash memory, a memory system including a flash memory device and a computing system including a memory system having a flash memory device. The technical spirit according to inventive concepts of the present invention is able to be applied and modified to a nonvolatile memory device such as a read only memory (ROM), a programmable ROM (PROM), an electrically programmable ROM (EPROM), an electrically programmable and erasable ROM (EEPROM), a flash memory, a magnetic random access memory (MRAM), a ferroelectric RAM (FeRAM or FRAM), a phase-change RAM (PRAM), a resistive RAM (RRAM), etc.

#### Status Monitoring

[0082] Hereinafter, referring to FIG. 1 to FIG. 11, a first embodiment according to inventive concepts of the present invention is described.

[0083] FIG. 1 is a block diagram illustrating a memory system according to the first embodiment of inventive concepts of the present invention. Referring to FIG. 1, a memory system 100 includes a host 110, a flash memory 120 including a status checking module 125, and a status display device 130 for displaying a status of the flash memory 120. The flash memory 120 may be a solid state drive (SSD). The memory system 100 tests status information of the flash memory 120 through the status checking module 125 and displays the test result to the external through the status display device 130.

[0084] The host 110 uses a SMART related command of an advanced technology attachment (ATA) interface in order to provide status information of the flash memory 120. SMART is an acronym for Self-Monitoring, Analysis and Reporting Technology, which can predict possible failure of a disk drive, and is a hard disk drive protocol. The SMART command will be described in more detail with reference to FIG. 2.

[0085] The flash memory 120 includes a plurality of memory cells for storing data. A set of the memory cells is

called a memory cell array. The memory cell array includes a plurality of memory blocks. Each memory block includes a plurality of pages. Each page includes a plurality of memory cells. The flash memory 120 performs an erase operation by a memory block unit and performs a write or read operation by a page unit.

[0086] The flash memory 120 may store one bit data in one memory cell or more than one bit data in one memory cell. In general, a memory cell storing one bit data is called a single level cell (SLC), and a memory cell storing more than one bit data is called a multi level cell (MLC). The SLC has an erase status and a program status according to a threshold voltage. The MLC has an erase status or a plurality of program statuses according to more than one threshold voltage.

[0087] The flash memory 120 includes a status checking module 125. The status checking module 125 for tests a defective status of the flash memory 120 through various status information of the flash memory 120.

[0088] Parameters for detecting status information of the flash memory 120 include a reserved block count, a runtime bad block count, a wear leveling count, an uncorrectable error count, a program/erase fail count, and a column fail count. The reserved block count is the number of reserved blocks. It may be, for example, 2% of all storage capacity. The runtime bad block count is the number of the bad blocks during run time of the flash memory 120 after the flash memory is manufactured. The wear leveling count is the number of Program/ Erase cycles performed during a wear leveling operation; namely, the number of times a wear leveling operation is performed to even out high erase and low erase sections of memory. The program/erase fail count is the number of program/erase fails (e.g., where program or erase of a flash cell has failed). The column fail count is the number of times a column line (bit line) has malfunctioned.

[0089] The status checking module 125 generates status information for displaying a defect status of the flash memory 120 through various parameters. The status checking module 125 combines status information to determine a status of the flash memory 120 and/or provides the status information to the host 110 in order to allow the host 110 to combine the status information and determine a status of the flash memory 120. At this point, the status checking module 125 provides the status information to the host 110 in response to the SMART command.

[0090] Moreover, the status checking module 125 updates periodically a plurality of status information of the flash memory 120 in the cell array of the flash memory 120. This is for preventing the loss of status information of the flash memory 120 during sudden power off of the memory system 100. Here, the sudden power off means a case of when power supply is cut off due to various unwanted reasons such as carelessness during an operation of the memory system 100.

[0091] Furthermore, the status checking module 125 compensates status information for the flash memory 120 with an appropriate value when sudden power off occurs. For example, let's assume a situation where status information is a program/erase cycle. Under the assumption that the updated program/erase cycle count is 1000 and an update period is 10 seconds before sudden power off, the program/erase cycle count is compensated with 1010 during the next update after sudden power off. A compensation value preparing for sudden power off can be obtained through various experimental data.

[0092] Additionally, the memory system 100 according to inventive concepts of the present invention may prepare for sudden power off through an auxiliary battery (not shown). Once sudden power off occurs, the memory system 100 updates status information of the flash memory 120 in the cell array of the memory cell through an auxiliary power supply or battery.

[0093] A status display device 130 displays a status of the flash memory 120 to a user. The status display device 130 displays whether the flash memory 120 is a good status, an intermediate status, or a bad status according to status information of the status checking module 125. Through the status display device 130, a user confirms a status of the flash memory 120 and also performs various operations such as data backup or memory replacement.

[0094] The status display device 130 may be realized with a display device such as an LED. For example, if the flash memory 120 is in a good status, the status display device 130 turns on a green LED. If the flash memory 120 is in the intermediate status, the status display device 130 turns on a yellow LED. If the flash memory 120 is in a bad status, the status display device 130 turns on a red LED. Therefore, a status of the flash memory 120 can be displayed externally.

[0095] Additionally, the status checking device 130 can display a status of the flash memory 120 through an alarm device's alarm sound, a monitor's message box and a graph, an LED's light, etc.

[0096] The memory system 100 of FIG. 1 includes the status checking module 125 for testing a status of the flash memory 120 and the status display device 130 for displaying a status of the flash memory 120 externally. A status of the flash memory 120 used in the memory system 100 can be easily confirmed and operations such as data backup or memory replacement can be performed at an appropriate time.

[0097] FIG. 2 is a table illustrating command formats that are obtained by classifying SMART commands based on a feature register value. Among SMART commands of FIG. 2, nine commands such as SMART READ DATA (D0h), SMART ENABLE/DISABLE ATTRIBUTE AUTOSAVE (D2h), SMART SAVE ATTRIBUTE VALUE (D3h), SMART EXECUTE OFF-LINE IMMEDIATE (D4h), SMART READ LOG (D5h), SMART WRITE LOG (D6h), SMART ENABLE OPERATIONS (D8h), SMART DISABLE OPERATIONS (D9h), and SMART RETURN STATUS (DAh) are designated by standards or protocols.

[0098] In order to provide status information of the flash memory 120 of FIG. 1, the SMART READ DATA command having the feature register value of D0h can be used. That is, when the SMART READ DATA command is provided from the host 110 of FIG. 1, the flash memory 120 generates status information that represents a status of the flash memory 120 through the status checking module 125 and then provides it to the host 110.

[0099] On the other hand, a command (for example, FFh) corresponding to one feature register value among a range of E0h to FFh (i.e., an area of a feature register value), that a manufacturer can use, may be used as a command for providing status information of the flash memory 120. Additionally, one of nine standard commands may be used as the above command.

[0100] FIG. 3 is a table illustrating a data structure for a result value of a SMART READ DATA command. As illustrated in FIG. 3, a data structure of the SMART READ DATA

command may be constituted by 512 bytes. Through a data area (0 byte to 361 byte and 386 byte to 510 byte) that a manufacturer can use among the 512 bytes, status information (such as a reserved block count, a wear leveling count, a program/erase fail count, a column fail count, and a program/erase cycle count) can be provided.

[0101] In FIG. 3, 'F' means that the content of a corresponding byte is fixed and does not change. 'V' means that the content of a corresponding byte is variable and may change. 'R' means that the content of a corresponding byte is reserved and shall be 0. 'X' means that the content of a corresponding byte is vendor specific and may be fixed or variable.

[0102] FIG. 4 is a table illustrating status information of a flash memory through a data area that a manufacturer can use. In FIG. 4, a reserved block count, a runtime bad block count, a wear leveling count, an uncorrectable error count, a program/erase fail count, and a column fail count are provided. Other than those, the status information of the flash memory can include diverse information such as a program/erase cycle count, which indicates the number of program and erase cycles.

[0103] As illustrated in FIG. 4, a byte area 0 to 1 provides information about a SMART data version. A byte area of 2 to 3 provides information about a reserved block count. A byte area of 4 to 7 provides information about a runtime bad block count. A byte area of 8 to 11 provides information about a wear leveling count. A byte area of 12 to 15 provides information about an uncorrectable error count. A byte area of 16 to 19 provides information about a program/erase fail count. A byte area of 20 to 23 provides information about a column fail count. Additionally, the remaining area may provide a reserved block count or other necessary or desired information.

[0104] Status information of the flash memory 120 such as a reserved block count may be stored in a meta block of the flash memory 120. The flash memory 120 provides status information such as a reserved block count in response to the SMART READ DATA command or the SMART RETURN STATUS command. A user can easily confirm a status of the flash memory 120 through the SMART command.

[0105] FIG. 5 is a table illustrating a method for determining a status of a flash memory through various parameters representing statuses of the flash memory. Referring to FIG. 5, a status of the flash memory may be divided into good, intermediate, and bad. The intermediate status is a status state between the good and bad status. The intermediate status may indicate a warning status that the flash memory 120 is transitioning from the good to the bad state. For example, the warning state may indicate the flash memory 120 is approaching the bad state. The intermediate status may indicate to back-up the flash memory 120.

[0106] In one embodiment, the status of the flash memory is determined from six parameters Pa to Pf. Pa represents a reserved block count. Pb represents a runtime bad block count. Pc represents a wear leveling count. Pd represents an uncorrectable error count. Pe represents a program/erase fail count. Pf represents a column fail count. These parameters are just examples and a status of a flash memory can be determined through other parameters, or more or less than these six parameters.

[0107] Each of the parameters has threshold value ranges corresponding to a good status, an intermediate status, and a bad status. For example, if Pa is a value between a1 and a2, it is in a good status. If Pa is a value between a3 and a4, it is in

an intermediate status. If Pa is a value between a5 and a6, it is in a bad status. Likewise, a value of a desired (or, alternatively a predetermined) range is given for Pb, Pc, Pd, Pe, and Pf according to a status. There may be various methods for determining a status of a flash memory through various parameters. Three representative methods are shown in FIG. 5

[0108] First, there is a method for performing an OR operation on parameters (hereinafter, referred as a Por method). For example, the Por method generates an intermediates signal if at least one of several parameters corresponds to an intermediate status and generates a bad signal if at least one corresponds to a bad status. Otherwise, a good signal is generated. If an intermediate signal is generated, a yellow LED is turned on. If a bad signal is generated, a red LED is turned on.

[0109] Second, there is a method for performing an AND operation on parameters (hereinafter, referred to as a Pand method). For example, the Pand method generates an intermediate signal if all parameters correspond to an intermediate status. If all the parameters correspond to a bad status, the Pand method generates a bad signal. If an intermediate signal is generated, a yellow LED is turned on. If a bad signal is generated, a red LED is turned on. Otherwise, a good signal is generated.

[0110] Third, there is a method for combining parameters through operations other than the OR or AND operations (hereinafter, referred to as a function or Psum method). For example, in one embodiment of the Psum method, the status of each parameter is determined according to the table of FIG. 5. In this embodiment, a weight is associated with each status state (e.g., the good status state may have a weight of 0, the intermediate status state may have a weight at 3 and the bad status state may have a weight of 5). Alternatively, each parameter may have its own associated set of weights for the good, intermediate and bad states. The weight for each determined status state of each parameter is summed, and that sum (Psum) is compared to thresholds defining the good, intermediate, and bad states for the flash memory. For example, Psum≤10 is good, 10<Psum≤20 is intermediate, and 20<Psum is bad.

[0111] Alternatively, the weights for less than all of the parameters may be summed. As a still further alternative, some combination of the OR, AND and Psum methods may be used.

[0112] Also, the above parameter operations of FIG. 5 may be performed in the host 110 of FIG. 1, or the status checking module 125 of FIG. 1 in the flash memory 120 of FIG. 1. For example, if the parameter operation is performed in the host 110, the SMART READ DATA command may be used, and if the parameter operation is performed in the status checking module 125, the SMART RETURN STATUS command may be used.

[0113] FIG. 6 is a flowchart illustrating a method of testing a status of the flash memory 120 of FIG. 1. Hereinafter, a method of testing a status of the flash memory 120 in the memory system 100 will be described in more detail with reference to FIGS. 1 and 6. It is assumed that the parameter operation of FIG. 5 is performed in the host 110.

[0114] In operation S110, the status checking module 125 checks status information of the flash memory 120. The status checking module 125 checks various parameters such as a reserved block count in order to a test a status of the flash memory 120. The status checking module 125 provides status

information of the flash memory 120 to the host 110 according to the SMART command of the host 110.

[0115] In operation S120, the host 110 receives the status information of the flash memory 120 and determines whether the flash memory 120 is in a bad status or not. The host 110 performs an operation (for example, an OR, AND, or SUM operation) on various parameters to determine a status of the flash memory 120.

[0116] If the flash memory 120 is determined as a bad status in operation S121, the host 110 determines red for displaying a bad status in operation S122. The host 110 outputs bad data or signal for displaying a bad status to the status display device 130.

[0117] Also, when the bad status in determined, the host may restrict input to and/or output from the flash memory. For example, read only one may be permitted. As another example, input and output may be prevented. Still further, this I/O restriction may be imposed by the host, the status checking module and/or a memory controller of the flash memory. [0118] In operation S130, if the flash memory 120 is not determined as a bad status, whether it is an intermediate status or not is determined and an intermediate data or signals are output. If the intermediate status is determined in operation S131, the host 110 determines yellow for displaying an intermediate status in operation S132. The host 110 outputs intermediate data or signal for displaying an intermediate status to the status display device 130.

[0119] In operation S140, if the flash memory 120 is not determined as an intermediate status, good data or signal are output. If it is not determined as an intermediate status in operation S131, the host 110 determines green for displaying a good status in operation S142. The host 110 outputs good data or signal for displaying a good status to the status display device 130.

[0120] Referring to FIG. 6, if the flash memory 120 is not determined as a bad stairs in operation S121, it is determined whether the flash memory 120 is in an intermediate status or not in operation S131. If it is in an intermediate status, intermediate data are output, and if not, good data are output.

[0121] Here, the memory system 100 determines whether it is in an intermediate status or not in operation S131, and then performs several additional jobs such as an error checking and correcting (ECC) operation, data backup, memory replacement according to the determination result. Therefore, a bad status can be prevented or dealt with in advance.

[0122] Additionally, after operation S110, the memory system 100 may perform operation S120 for determining a bad status, operation S130 for determining an intermediate status, and operation S140 for determining a good status in a different order or concurrently.

[0123] Referring to FIG. 1 again, the memory system 100 tests a status of the flash memory 120 through a status checking module 125, and displays the test result externally through the status display device 130. Such that a user can easily confirm the test result. Accordingly, a good or bad status of the flash memory 120 can be easily identified and jobs such as data backup or memory replacement can be performed at an appropriate time.

[0124] FIG. 7 is a block diagram illustrating a memory system according to another embodiment. Referring to FIG. 7, a memory system 200 includes a host 210 loading an application program 205, a flash memory 220 having a status checking module 225, and a status display device 230 for indicating a status of the flash memory 220.

[0125] The application program 205 includes an algorithm in order to allow a user to request a desired (or alternatively, a predetermined) data operation on the flash memory 220 or to perform a logical operation on a desired (or alternatively, a predetermined file). The host 210 loads the application program 205 in order to perform a desired (or alternatively, a predetermined) data operation on the flash memory 220 upon a user's request.

[0126] The host 210 includes a file system 212 and a flash translation layer (FTL) 214. The file system 212 loads the application program 205. The FTL 214 manages a data operation upon a user's request, that is, a read/write operation of the flash memory 220. The FTL 214 converts a logical address, generated during a write operation by the file system 212, into a physical address.

[0127] The flash memory 220 performs an erase operation before performing a write operation. Additionally, the flash memory 220 performs a write operation by a page unit and performs an erase operation by a block unit. That is, the flash memory 220 is characterized in having a larger erase operation unit than a write operation unit.

[0128] These characteristics may make it difficult for the flash memory 220 to be used as a main memory. Additionally, when the flash memory 220 is used as an auxiliary memory device, those characteristics may make it difficult to utilize a file system for a typical hard disk drive. Accordingly, the memory system 200 uses the FTL 214 between the file system 212 and the flash memory 220 in order to conceal an erase operation of the flash memory 220.

[0129] Due to an address mapping function of the FTL 214, the host 210 recognizes the flash memory 220 as a hard disk, and can access the flash memory 220 using the same method as with a hard disk. If the flash memory 220 is used as a solid state disk or drive (SSD) or a hard disk, the flash memory 220 includes a status checking module 225 and utilizes SMART related commands in order to provide a bad status of the flash memory 220 to a user.

[0130] The status checking module 225 tests an intermediate status of the flash memory 220 through various parameters of the flash memory 220. A method of testing an intermediate status of the flash memory 220 is the same as the above method. The status checking module 225 provides status information to the host 210 through various parameters. The status information is used for displaying status of the flash memory 220 externally.

[0131] The status display device 230 is a device for notifying a user of a status of the flash memory 220. The status display device 230 displays a good status, an intermediate status, or a bad status of the flash memory 220 according to status information of the status checking module 225. A user confirms the status of the flash memory 220 through the status display device 230 and also performs jobs such as data backup or memory replacement.

[0132] The memory system 200 of FIG. 7 uses the application program 205 to recognize a status of the flash memory 220. The application program 205 communicates with the status checking module 225 periodically and determines a status of the flash memory 220. Then, the application program 205 notifies the status display device 230 of the determined result. If the application program 205 is used, the status of the flash memory 220 can be shown in a message box or a graph through a monitor other than an LED.

[0133] The memory system 200 of FIG. 7 updates status information in the flash memory 220 against sudden power

tionally, the memory system 200 may update status information in the flash memory 220 through an auxiliary battery. [0134] FIG. 8 is a block diagram illustrating a memory system according to another embodiment of inventive concepts of the present invention. Referring to FIG. 8, a memory system 300 includes a host 310, a memory device 320, a status checking module 325, and a display device 330. In FIG. 8, the memory device 320 may include volatile memories (for

off, or compensates for status information for update. Addi-

system 300 includes a host 310, a memory device 320, a status checking module 325, and a display device 330. In FIG. 8, the memory device 320 may include volatile memories (for example, DRAM, SRAM, etc.), non-volatile memories (for example, PRAM, MRAM, etc.), a hard disk, SSD, OneNAND, and CD ROM other than the flash memory. Moreover, the status checking module 325 may be placed in the memory device 320. As shown in FIG. 8, the status checking module 325 may be placed outside the memory device 325.

[0135] The status checking module 325 tests a status of the memory device 320 through various parameters of the memory device 320. The status checking module 325 provides status information of the memory device 320 to the host 310. The host 310 determines a status of the memory device 320 comprehensively through status information. The host 310 provides the status result of the memory device 320 to the display device 330. The display device 330 displays the status of the memory device 320 in order for a user to understand it without difficulties.

[0136] The memory system 300 of FIG. 8 updates status information in the flash memory 220 against sudden power off, or compensates for status information for update. Additionally, the memory system 300 may update status information in the flash memory 320 through an auxiliary battery.

[0137] FIG. 9 is a block diagram illustrating a storage device according to an embodiment of inventive concepts of the present invention. Referring to FIG. 9, a storage device 400 includes a memory controller 410 and non-volatile memories 420 to 423. The memory controller 410 includes a CPU 411, an ATA interface 412, a SRAM cache 413, a flash interface 414, and a status checking module 515.

[0138] In FIG. 9, SSD in the storage device 400 is shown as an example. SSD products expected to replace hard disk drive products in the next generation memory market receive considerable attention. The SSD is a data storage device using memory chips such as a flash memory to store data, instead of a rotational disk used in a typical hard disk drive (HDD). Compared to a mechanically moving HDD, the SSD has various advantages such as a fast operating speed, strong resistance against external impact, and low power consumption.

[0139] The CPU 411 receives commands from a host (not shown) and then controls and determines whether to store data from the host in the flash memory or to read stored data of the flash memory in order to transmit them to the host.

[0140] The ATA interface 412 exchanges data with the host according to a control of the CPU 411. The ATA interface 412 fetches a command and an address from the host and delivers them to the CPU 411 through a CPU bus. Data inputted from the host or data to be transmitted to the host, via ATA interface, are delivered through the SRAM cache 413 not the CPU bus according to a control of the CPU 411. Here, the ATA interface 412 may be realized with a SATA or PATA interface. [0141] The SRAM cache 413 temporarily stores transmitted data between the host and the flash memories 420 to 423. Additionally, the SRAM cache 413 may be used for storing a program that will be operated by the CPU 411. The SRAM

cache 413 may be regarded as a kind of a buffer memory, and may be realized with other types of memory than an SRAM. [0142] The flash interface 414 exchanges data with the non-volatile memories 420 to 423. The flash interface 414 may be configured to support a NAND flash memory, an One-NAND flash memory, or a multi-level flash memory.

One-NAND flash memory, or a multi-level flash memory. The flash interface 414 and the non-volatile memories 420 to 423 exchange control signals and data.

[0143] The status checking module 415 tests statuses of the non-volatile memories 420 to 423 through various parameters. An operating principle of the status checking module 415 is the same as the above. The status checking module 415 provides status information to the host through the ATA interface 412. The host analyzes or evaluates status information, and delivers its analyzed result to a display device (not shown) through the ATA interface 412. Additionally, the status checking module 415 combines a plurality of status information to test a status of the non-volatile memory. At this point, the SSD controller 410 provides the combined result of the plurality of status information to the host or the display device.

[0144] The storage device 400 of FIG. 9 updates status information in the flash memories 420 to 423 against sudden power off, or compensates for status information for update. Additionally, the storage device 400 may update status information in the flash memories 420 to 423 through an auxiliary battery.

[0145] FIG. 10 is a block diagram illustrating a storage device according to an embodiment of inventive concepts of the present invention. Referring to FIG. 10, a storage device 500 includes SSD controller 510 and non-volatile memories 520 to 523. The SSD controller 510 includes a CPU 511, an ATA interface 512, a SRAM cache 513, a flash interface 514, a status checking module 515, and a temperature sensor 516.

[0146] The storage device 500 of FIG. 10 has the same structure and operating principle as FIG. 9 except for the temperature sensor 516. The temperature sensor 516 measures a temperature of the storage device 500, and provides the measured result to the status checking module 515. If the measured temperature is above or below the standard, the status checking module 515 adjusts the upper value and the lower value of the parameters of FIG. 5 to be appropriate for the measured temperature.

[0147] The memory system or the storage device according to the embodiments may be used as a mobile storage device. Accordingly, they may be used as a storage device of an MP3, a digital camera, a PDA, and an e-book. Additionally, they may be used as a storage device of a digital TV or a computer.

[0148] The memory system or the storage device according to inventive concepts of the present invention may be mounted through various kinds of packages. For example, the memory system or the storage device may be mounted through various packages such as PoP (Package on Package), Ball grid arrays (BGAs), Chip scale packages (CSPs), Plastic Leaded Chip Carrier (PLCC), Plastic Dual In-Line Package (PDIP), Die in Waffle Pack, Die in Wafer Form, Chip On Board (COB), Ceramic Dual In-Line Package (CERDIP), Plastic Metric Quad Flat Pack (MQFP), Thin Quad Flatpack (TQFP), Small Outline (SOIC), Shrink Small Outline Package (SSOP), Thin Small Outline (TSOP), Thin Quad Flatpack (TQFP), System In Package (SIP), Multi Chip Package (MCP), Wafer-level Fabricated Package (WFP), and Wafer-Level Processed Stack Package (WSP).

[0149] As described above referring to FIG. 1 to FIG. 10, a status of a SSD is able to be determined based on the LED. Thus, when a SSD is defected, it is able to be replaced with a normal SSD in times. That is, reliabilities of a nonvolatile memory device, a memory system including a nonvolatile memory device and a computing system including a memory system having a nonvolatile memory device are advanced.

#### I/O Restriction

[0150] A memory storage device according to a second embodiment of inventive concepts of the present invention is configured to set a read only mode for a memory chip where defects occur. Therefore, it is possible to backup important user data of a defective memory chip. Hereinafter, referring to FIG. 11 to FIG. 21, the second embodiment of inventive concepts of the present invention is described.

[0151] FIG. 11 is a view illustrating a hardware configuration of a memory storage device 1100 according to the second embodiment of inventive concepts of the present invention. Referring to FIG. 11, the memory storage device 1100 includes a system bus 1102, a CPU 1110, a RAM 1120, a flash memory controller 1130, memory chips 1141 to 1148, and a host interface controller 1150. The memory storage device 1100 of inventive concepts of the present invention is realized to allow each of a plurality of memory chips 1141 to 1148 to operate in any one of a write/read mode, a read only mode, and an inaccessible mode. Although the memory storage device 1100 of FIG. 11 includes a plurality of the flash memory chips 1141 to 1148, it may not be necessarily constituted by the flash memory chips. The memory storage device of inventive concepts of the present invention may be constituted by volatile chips or nonvolatile memory chips.

[0152] The memory storage device 1100 of inventive concepts of the present invention may be a memory card or SSD. The RAM 1120 is a volatile memory device and may be a DRAM or a SRAM.

[0153] The flash memory controller 1130 controls the plurality of memory chips 1141 to 1148. The flash memory controller 1130 examines each mode status of the memory chips 1141 to 1148, and according thereto, controls the memory chips 1141 to 1148 upon a read or write request from the host. Additionally, the flash memory controller 1130 includes an ECC engine for correcting errors of the memory chips 1141 to 1148.

[0154] The memory chips 1141 to 1148 store data. The memory chips 1141 to 1148 of FIG. 11 are eight, but the number of memory chips may not be necessarily limited thereto. The memory chips 1141 to 1148 may instead be memory packages including two or more memory chips. The reason of using a plurality of memory chips 1141 to 1148 in the memory storage device 1100 is to achieve a high capacity and also improve performance. That is, a read/write request of the host can be processed faster by operating the plurality of memory chips 1141 to 1148 concurrently. Moreover, the memory chips 1141 to 1148 may be configured with various memories other than the flash memory. The memory chips 1141 to 1148 may be realized with volatile memories or non-volatile memories (for example, MRAM, PRAM, and FRAM).

[0155] The host interface controller 1150 may be a secure digital (SD) card interface or a multi media card interface in a case of a memory card and may be a PATA, a SATA, or a PCI-express in a case of SSD. This interface defines a communication channel with a host (not shown).

[0156] In a typical memory storage device, if any one of memory chips is defective, the entire memory storage device becomes unavailable. However, in the memory storage device 1100, even if any one of the memory chips 1141 to 1148 becomes unavailable for normal read/write service, the memory storage device 1100 still can be available by operating a defective memory chip 1148 in a read only mode. A mode change service of a memory chip is performed in the flash memory controller 1130. For convenience of description, it will be described under the assumption that a memory chip is a flash memory.

[0157] FIG. 12 is a view illustrating a software module structure of the flash memory storage device 1100 according to an embodiment. A host command handler analyzes a host command and is in charge of buffer management, which will be received from or transmitted into the host. A read or write position that the host requested does not match with a physical address of a flash memory in one to one correspondence. Accordingly, it is necessary to convert a logical address into a physical address of a flash memory. A software module responsible for this conversion is called a flash translation layer (FTL). The FTL includes an address translator and a bad block management module. The address translator converts a logical address to a physical address of the flash memory. The bad block management module registers a bad block where erase fail occurs and is responsible for replacing the bad block.

**[0158]** Additionally, the FTL includes a flash memory controller interface for performing a read, program, or erase operation on each flash memory chip. The FTL uses a software method for managing a situation of when normal services cannot be provided due to a defective specific memory block. This method, for example, includes a service mode setting method for each flash memory.

[0159] FIG. 13 illustrates a program flowchart of a flash memory according to an embodiment of inventive concepts of the present invention. Referring to FIG. 13, a program operation of a flash memory will progress as follows. In operation S1110, data to be programmed will be transmitted to a page buffer of a flash memory. In operation S1120, a program command is issued for the flash memory. Based on the issued program command, a program operation of the flash memory is performed. Next, a program status is checked or verified in operation S1130. Then, it is determined whether the program operation is successful or not through the checked result in operation S1140. At this point, if the program operation is successful, it is terminated. On the contrary, if the program operation is not successful, a bad block replacement operation is performed. A detailed description for the bad block replacement operation will be made with reference to FIG.

[0160] FIG. 14 illustrates an erase flowchart of a flash memory according to inventive concepts of the present invention. Referring to FIG. 14, an erase operation of the flash memory will progress as follows. An erase command is issued to the flash memory in operation S1210. Based on the issued erase command, an erase operation of the flash memory will be performed. Then, an erase operation status is checked or verified in operation S1220. It is determined that the erase operation is successful or not through the checked result in operation S1230. At this point, if the erase operation is successful, it is terminated. On the contrary, if the erase operation is not successful, a bad block replacement opera-

tion is performed. A detailed description for the bad block replacement operation will be made with reference to FIG. **15**.

[0161] FIG. 15 illustrates a bad block replacement algorithm during a program fail operation according to inventive concepts of the present invention. Referring to FIG. 15, a bad block replacement operation will progress as follows. Once program fail occurs, the memory controller 1130 determines whether the number of occurred bad blocks is over that of reserved blocks for replacement or not in operation S1310. If the number of bad blocks does not exceed that of reserved blocks, the memory controller 1130 allocates new free blocks from the reserve blocks to replace the bad blocks in operation S1320. Next, the memory controller 1130 copies previous data from a previous bad block to a new free block in operation S1322, and then updates a block mapping table. The data corresponding to the updated mapping table are stored in the flash memory in operation S1324. Therefore, the block replacement operation is completed during program fail.

[0162] On the contrary, if the number of bad blocks exceeds that of reserved bocks, no more block replacement operation is possible. Accordingly, the memory controller 1130 sets a read only flag in meta data for displaying a mapping status of a flash memory that is no longer used for block replacement. This updated meta data cannot be stored in a flash memory where block replacement is impossible. This is because no more write operation can be performed on the flash memory where no block replacement is possible. Accordingly, the updated meta data are stored in another flash memory where block replacement is possible in operation S1332. Therefore, the flash memory where no block placement is possible can be used for a read only mode service.

[0163] All the meta data of the flash memories according to inventive concepts of the present invention are realized to be stored in each of the flash memories. FIG. 16 illustrates a meta block configuration of a flash memory and a method of storing the same. Referring to FIG. 16, the meta data of the flash memories are stored in the meta blocks of the flash memories. Therefore, even when any one of the flash memories cannot be read or written due to defect occurrence, a service mode can be adjusted with respect to the defective flash memory by using the meta data stored in another flash memory. For example, if the flash memory 1146 cannot provide a read/write mode service, it can be adjusted to a read only mode service through the meta information of another flash memory.

[0164] If the memory storage device of inventive concepts of the present invention is applied to SSD, drive status information such as SMART may be stored and managed in a plurality of chips as illustrated in FIG. 16. Accordingly, since the SMART information is not stored in a specific chip, reporting of bad status information of a drive is possible even when some chips are defective.

[0165] An age value is increased in each flash memory each time a meta block is updated. That is, the age value is increased according to the updated number. The memory controller 1130 determines meta data, of which age value is high among a plurality of meta data read from the flash memory, as valid meta data. The reason is that a meta value having the highest age value is the latest updated meta data.

[0166] FIG. 17 illustrates a structure of meta data in a page of a flash memory. As illustrated in FIG. 17, meta data of four

flash memories are stored in a meta block of one flash memory. Here, meta data of each flash memory is stored in a page of 4 KByte.

[0167] Meta data are stored in a meta block of each flash memory such that meta data having bad block status information about flash memories can be included. That is, each flash memory has meta data information about itself. Accordingly, later on, even when any one of the flash memories becomes defective, status information of the defective flash memory can be extracted from the meta data of another flash memory.

[0168] FIG. 18 illustrates a SMART data structure in a page of a flash memory. Because the SMART information stores information about a plurality of chips in one page, even when unrecognizable chip occurs, information about the unrecognizable chip can be extracted from another chip.

[0169] FIG. 19 is a flowchart illustrating an initialization process of the memory storage device 1100 of FIG. 11 according to inventive concepts of the present invention. Referring to FIG. 19, an initialization operation of the memory storage device 100 is as follows. First, the memory controller 1130 reads an identification (ID) of each of the chips 1141 to 1148 in operation S1410. At this point, the memory controller 1130 determines whether the read chip is identified or not in operation S1420. If the memory chip is not identified, the memory controller 1130 updates meta data to set a corresponding memory chip to be in an inaccessible mode in operation S1435. Then, it proceeds to operation S1460

[0170] If the memory chip is identified, the memory controller 1130 reads meta data from a meta block of a memory chip. The highest age value among the read meta data is determined as valid meta data in operation S1440. Here, the age value of the meta data is increased each time update is performed. A service mode of a memory chip is selected from the valid meta data in operation S1450. The service mode is one of a read/write mode, a read only mode, and an inaccessible mode.

[0171] The memory controller 1130 determines whether the initialization process repeats on all the memory chips or not in operation S1460. If the initialization process is not performed on every memory chips, it proceeds to operation S1410. If the initialization process is performed on every memory chips, it is terminated.

[0172] FIG. 20 is a flowchart illustrating a read operation of the flash storage device 1100 according to inventive concepts of the present invention. Referring to FIG. 20, after the initialization process is performed, a read operation of the flash storage device 1100 is as follows. The memory controller 1130 calculates a corresponding chip ID according to a logical block address (LBA) delivered from the host in operation S1510. The memory controller 1130 determines whether a read operation on the calculated chip ID is possible or not through valid meta data in operation S1420. If a read/write mode service or a read only mode service cannot be provided on the calculated chip ID, the read operation is processed as an error in operation S1530. If a read/write mode service or a read only mode service is provided on the calculated chip ID, the read operation is performed on a corresponding memory chip in operation S1540.

[0173] FIG. 21 is a flowchart illustrating a write operation of the flash storage device 1100. Referring to FIG. 21, after an initialization process is performed, a write operation of the flash storage device 1100 is as follows. The memory control-

ler 1130 calculates a corresponding chip ID according to a logical block address (LBA) delivered from the host in operation S1610. The memory controller 1130 determines whether a write operation on the calculated chip ID is possible or not through valid meta data in operation S1620. If a read/write mode service cannot be provided on the calculated chip ID, the write operation is processed as an error in operation S1630. If a read/write mode service is provided on the calculated chip ID, the write operation is performed on a corresponding memory chip in operation S1640.

[0174] Although not illustrated in the drawing, it is apparent to those skilled in the art that an application chipset, a camera image processor (CIS), a mobile DRAM, and so forth may be use the memory storage device of the example embodiments. The memory controller and the flash memory may include SSD for storing data through a non-volatile memory device, for example.

[0175] The flash memory and/or the memory controller according to inventive concepts of the present invention may be mounted through various kinds of packages. For example, the flash memory device and/or the memory controller may be mounted through various packages such as PoP (Package on Package), Ball grid arrays (BGAs), Chip scale packages (CSPs), Plastic Leaded Chip Carrier (PLCC), Plastic Dual In-Line Package (PDIP), Die in Waffle Pack, Die in Wafer Form, Chip On Board (COB), Ceramic Dual In-Line Package (CERDIP), Plastic Metric Quad Flat Pack (MQFP), Thin Quad Flatpack (TQFP), Small Outline (SOIC), Shrink Small Outline Package (SSOP), Thin Small Outline (TSOP), Thin Quad Flatpack (TQFP), System In Package (SIP), Multi Chip Package (MCP), Wafer-level Fabricated Package (WFP), and Wafer-Level Processed Stack Package (WSP).

[0176] As described above referring to FIG. 11 to FIG. 21, a bad block is set as a read only service mode when any reserved block to be replaced with a bad block does not exist. Thus, data stored in a block can be read even though it is determined as a bad block. That is, reliabilities of a nonvolatile memory device, a memory system including a nonvolatile memory and a computing system including a memory system having a nonvolatile memory device are advanced.

#### Prediction

[0177] Hereinafter, a memory system according to a third embodiment of inventive concepts of the present invention is described referring to FIG. 22 to FIG. 32. A semiconductor disk device will be used as a non-volatile memory system in order to describe features and functions in the third embodiment of inventive concepts of the present invention. Additionally, a read request is mainly described as expected requests in the third embodiment of inventive concepts of the present invention, but the example embodiments are not limited thereto. However, those skilled in the art can easily understand other advantages and performances according to the listed contents. Additionally, a flash memory is described as one example of a storage medium, but other non-volatile memory devices can be also used. For example, PRAM, MRAM, ReRAM, and FRAM may be used as a storage medium, and also different kinds of memory devices may be applied to a hybrid memory system.

[0178] FIG. 22 is a block diagram illustrating technical features of the third embodiment according to inventive concepts of the present invention. Referring to FIG. 22, SSD 2200 of inventive concepts of the present invention exchanges data with an external host 2100 through an input/output port.

The SSD 2200 stores or reads data in or from a non-volatile memory 2240 in response to a read/write request from the host 2100. The SSD 2200 of inventive concepts of the present invention predicts a pattern of a request provided from the host 2100. Accordingly, the SSD 2200 can improve a response speed with respect to a read request of the host 2100. [0179] The host 2100 requests the SSD 2200 to write data. The host 2100 provides a corresponding address and data upon a data write request. Additionally, the host 2100 provides a data read request to the SSD 2200. In a computing system, the read request of the host 2100 is typically divided into a sequential request and a random request. The sequential request is for reading data sequentially. During the sequential request, continuous data next to the currently requested data are pre-fetched and then are transmitted to the host 2100, such that a read speed can be improved. On the contrary, in a case of the random request, it is difficult for the host 2100 to predict data for the continuous next read request. However, a pattern may frequently exist in the random request. If the SSD 2200 can recognize the pattern, the next read request associated with a current read request can be predicted. This means that performance of the SSD 2200 can be improved.