(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-48025

(P2004-48025A)

(43) 公開日 平成16年2月12日(2004.2.12)

(51) Int.CI.<sup>7</sup>H01L 21/3205

H01L 21/768

H01L 21/82

H01L 21/822

H01L 21/8242

F 1

H01L 21/88

H01L 21/90

H01L 27/04

H01L 21/82

H01L 27/10

テーマコード(参考)

S 5FO33

C 5FO38

D 5FO64

W 5FO83

H01L 621C

審査請求 有 請求項の数 5 O L (全 32 頁) 最終頁に続く

(21) 出願番号 特願2003-207585 (P2003-207585)

(22) 出願日 平成15年8月14日 (2003.8.14)

(62) 分割の表示 特願平10-33388の分割

原出願日 平成10年2月16日 (1998.2.16)

(31) 優先権主張番号 特願平9-81013

(32) 優先日 平成9年3月31日 (1997.3.31)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 河渕 靖

東京都小平市上水本町五丁目20番1号

株式会社日立製作所半導体事業部内

(72) 発明者 長沢 幸一

東京都小平市上水本町五丁目20番1号

株式会社日立製作所半導体事業部内

(72) 発明者 茂庭 昌弘

東京都小平市上水本町五丁目20番1号

株式会社日立製作所半導体事業部内

最終頁に続く

(54) 【発明の名称】半導体集積回路装置

## (57) 【要約】

【課題】C M P法により研磨される絶縁膜の平坦性を向上する。

【解決手段】半導体基板1の主面上に形成されたM I S F E T Q 1を覆う層間絶縁膜9の上層に配線10を形成するとともに、その配線10間の間隔が広い領域にダミー配線11を配置する。また、ダミー配線11はスクラップ領域にも配置される。さらに、ダミー配線11は、ボンディングパッドの周辺領域およびマーカの周辺領域には、配置されない。また、M I S F E Tのゲート電極と同層にダミーゲート配線を設ける。また、浅溝素子分離領域にダミー領域を向ける。これらダミー部材を設けた後に、C M P法で絶縁膜を平坦化する。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

半導体基板の活性領域上に形成された M I S F E T のゲート電極と、前記ゲート電極と同層で構成されるとともに、前記ゲート電極間の距離が離れて形成されている空隙領域に配置されたダミーゲート配線と、前記ゲート電極およびダミーゲート配線を覆い、かつ C M P 法により平坦化された被膜を含む絶縁膜とを有する半導体集積回路装置において、前記活性領域は、素子分離領域で分離され、前記ダミーゲート配線は、前記素子分離領域上に形成されることを特徴とする半導体集積回路装置。

## 【請求項 2】

請求項 1 記載の半導体集積回路装置であって、さらに、前記活性領域およびダミー領域を規定する溝と、前記溝に C M P 法により平坦化された被膜を含む絶縁膜が埋込まれた素子分離絶縁膜とを含み、前記素子分離領域は、前記ダミー領域および素子分離絶縁膜で構成され、前記ダミーゲート配線は、前記素子分離領域において、前記ダミー領域および素子分離絶縁膜上に配置されることを特徴とする半導体集積回路装置。

## 【請求項 3】

半導体基板の活性領域およびダミー領域と、前記活性領域に形成された半導体素子と、前記活性領域およびダミー領域を規定する溝と、前記溝に C M P 法により平坦化された被膜を含む絶縁膜が埋込まれた素子分離絶縁膜と、前記活性領域および素子分離絶縁膜上に形成されたゲート配線とを有する半導体集積回路装置であって、前記活性領域を規定する素子分離領域は、前記ダミー領域および素子分離絶縁膜で構成され、前記ゲート配線は、前記ゲート配線の下部には前記ダミー領域が形成されないように、前記素子分離絶縁膜上に延在し、ダミーゲート配線が、前記ゲート配線と同層で構成され、前記ダミーゲート配線は、前記素子分離領域において、前記ダミー領域および素子分離絶縁膜上に配置されることを特徴とする半導体集積回路装置。

## 【請求項 4】

請求項 1 または 2 記載の半導体集積回路装置であって、前記ゲート電極は、D R A M のメモリセルの選択 M I S F E T のゲート電極を構成することを特徴とする半導体集積回路装置。

## 【請求項 5】

半導体基板の活性領域上に形成された M I S F E T のゲート電極と、前記ゲート電極と同層で構成されるとともに、前記ゲート電極間の距離が離れて形成されている空隙領域に配置されたダミーゲート配線と、前記ゲート電極およびダミーゲート配線を覆い、かつ C M P 法により平坦化された被膜を含む絶縁膜とを有する半導体集積回路装置において、前記活性領域は、素子分離領域で分離され、前記ダミーゲート配線は、前記素子分離領域上に形成され、また前記ダミーゲート配線はスクライプ領域上に形成されていることを特徴とする半導体集積回路装置。

## 【発明の詳細な説明】

## 【0 0 0 1】

## 【発明の属する技術分野】

本発明は、半導体集積回路装置に関し、特に、その製造工程に C M P ( C h e m i c a l M e c h a n i c a l P o l i s h i n g ) 法を用いた平坦化工程を含む半導体集積

10

20

30

40

50

回路装置に適用して有効な技術に関するものである。

【0002】

【従来の技術】

半導体集積回路装置の最小加工寸法の減少に伴ってステッパーの高性能化が必要となり、レンズ開口径の増大と露光波長の短波長化が進んでいる。その結果、露光光学系の焦点深度が浅くなり、被加工表面の僅かな凹凸も問題となる。この結果、被加工表面の平坦化はデバイスプロセス上重要な技術課題となっている。しかも上記の平坦化は、段差上に形成される配線の断線を防止するために必要とされる段差形状の緩和を目的とした平坦化ではなく、グローバルな平坦化つまり完全平坦化が要求されるものである。

【0003】

表面平坦化の技術としては、SOG (Spin On Glass) 膜あるいは低融点ガラスの塗布および溶融による塗布法、ガラスフローによる熱処理法、CVD (Chemical Vapor Deposition) の表面反応メカニズムを適用して自己平坦化させる方法等が知られているが、表面の状態や適用する熱処理等の条件あるいはそれらの加工上の制約から、完全な平坦化すなわちグローバル平坦化を行うことができない場合が多い。そこで、完全平坦化が実用的に可能な技術としてエッチバック法およびCMP法が有望視されている。

【0004】

エッチバック法は、フォトレジストを犠牲膜にしたもの、SOG膜を用いたもの、自己平坦化CVD膜を用いたもの等が知られているが、プロセスの複雑さ、コスト、パーティクルによる歩留まり低下が問題となり、一方、CMP法は前記エッチバック法に生ずる問題は比較的少なく、エッチバック法との比較において総合的に優れたプロセスであるとの認識が一般に形成されつつある。つまり、完全平坦化を実現しうる実用的な技術としては、CMP法が最も有望であると考えられる。

【0005】

なお、CMP技術を詳しく記載している例としては、たとえば、特開平7-74175号公報、特開平6-196551号公報、平成8年5月1日、工業調査会発行、「電子材料」1996年5月号、p22~p27がある。

【0006】

【発明が解決しようとする課題】

しかし、CMP法を適用したデバイス表面の完全平坦化技術を検討する過程において、公知の技術ではないが、本発明者は以下のような問題点があることを認識した。

【0007】

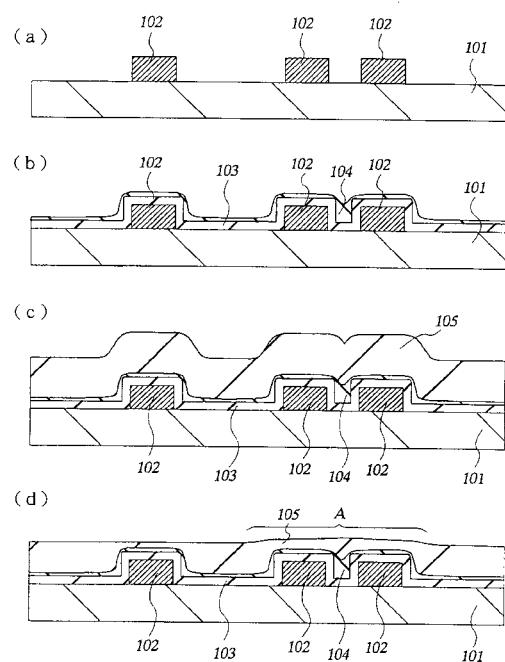

図29(a)~(d)は、本発明者が検討したCMP法による平坦化技術を説明するための断面図である。配線を絶縁膜により被覆し、その絶縁膜を平坦化する方法としては、まず、層間絶縁膜101上に配線102を形成し(図29(a))、次に、TEOS (Tetraethoxysilane: (C<sub>2</sub>H<sub>5</sub>O)<sub>4</sub>Si)を用いたプラズマCVD法等により第1絶縁膜103およびSOG等の第2絶縁膜104を堆積して凹部を埋め込み(図29(b))、TEOSプラズマCVD法等により第3絶縁膜105を堆積し(図29(c))、さらに、第3絶縁膜105をCMP法により研磨して平坦化することができる(図29(d))。

【0008】

この際、配線102のパターンは、機能設計および論理設計に基づくレイアウト設計において、通常のレイアウトルールにしたがっているか否かに主眼が置かれ、特にCMP工程での研磨特性が考慮されることはない。

【0009】

そのため、配線パターンは、場所により疎密が発生し、上記の検討図面(図29(d))においては、A部において配線102が密に形成され、その他の領域では、配線102は疎に形成されることとなる。

【0010】

10

20

30

40

50

このように、配線 102 に疎密のある状態で CMP 研磨を行うと、第 3 絶縁膜 105 の表面を完全に平坦化することができず、配線 102 が密に形成された A 部領域で 0.2 ~ 0.7  $\mu\text{m}$  の標高差が生じ、表面に大きなうねりが残ってしまう。

#### 【0011】

このようなうねりの存在する表面では、その後のフォトリソグラフィ工程あるいはエッチング工程でプロセスマージンが低下し、微細な加工および高集積化の対応が困難となり、半導体集積回路装置の信頼性の向上および歩留まりの改善を図ることができない。

#### 【0012】

また、うねりのある状態でのリソグラフィおよびエッチングを良好に行うためにプロセス条件の最適化を行う必要があり、うねりを最小限に抑制するための CMP 工程の最適化も必要となる。このような最適化に要する期間により量産プロセスの立ち上げ時期が遅れるという問題もある。

#### 【0013】

さらに、配線 102 が疎な領域では、第 2 絶縁膜 104 によって配線 102 間が十分に埋め込まれず、そのような凹部を完全に埋め込むために第 3 絶縁膜 105 の膜厚を厚くせざるを得ない。その結果、第 3 絶縁膜 105 の堆積時間が長くなる等の工程負荷が大きくなるのみならず、第 3 絶縁膜 105 の研磨量も多くなり、CMP 工程での工程負荷も大きくなるという問題が生じる。

#### 【0014】

本発明の目的は、CMP 法による研磨後の部材表面を完全に平坦化することにある。

#### 【0015】

また、本発明の目的は、フォトリソグラフィ工程およびエッチング工程等でのプロセスマージンを向上し、微細な加工および高集積化に対応することができる技術を提供するとともに、半導体集積回路装置の信頼性および歩留まりを向上することにある。

#### 【0016】

また、本発明の目的は、プロセス立ち上げを容易にすることにある。

#### 【0017】

また、本発明の目的は、CMP 法により研磨される部材の研磨量を低減し、工程負荷の低減および工程時間の短縮によるコスト競争力の向上を図ることにある。

#### 【0018】

また、本発明の目的は、CMP 法により完全平坦化が可能な部材パターンの設計方法を提供することにある。

#### 【0019】

また、本発明の目的は、完全平坦化を実現するための対策により生ずる配線等の寄生容量の増加を抑制し、半導体集積回路装置の性能を確保することにある。

#### 【0020】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

#### 【0021】

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

#### 【0022】

(1) 本発明の半導体集積回路装置は、半導体基板の主面上または層間絶縁膜上に形成された半導体集積回路素子を構成する配線と、その配線を覆い、CMP 法により平坦化された被膜を含む絶縁膜とを有する半導体集積回路装置であって、その配線の形成された配線層において、配線間の距離が離れて形成されている空隙領域に、配線と同一の材料からなり素子として機能しないダミー配線が形成されているものである。

#### 【0023】

また、本発明の半導体集積回路装置は、半導体基板の主面に形成された浅溝と、浅溝に C

10

20

30

40

50

MP 法により平坦化された被膜を含む絶縁膜が埋め込まれた素子分離領域と、素子分離領域により分離された半導体集積回路素子の活性領域とを含む半導体集積回路装置であって、活性領域間の距離が離れて形成されている半導体基板の空隙領域に、半導体集積回路素子として機能しない半導体基板の正面のダミー領域が形成されているものである。

## 【0024】

このような半導体集積回路装置によれば、空隙領域にダミー配線あるいはダミー領域が形成されているため、疎の部分が発生しないように配線を覆う絶縁膜の表面あるいは半導体基板の正面を完全に平坦化することができる。

## 【0025】

すなわち、ダミー配線あるいはダミー領域（ダミー部材）が形成されず配線あるいは活性領域（素子構成部材）のみが形成されている場合には、素子構成部材間の距離が大きく離れた空隙領域が生じ、このような空隙領域が存在したままで絶縁膜を堆積した場合、空隙領域周辺での絶縁膜表面の形状は、素子構成部材の形状を忠実に反映した凹凸形状となる。このような凹凸形状は図29に示したように完全平坦化を阻害する要因となる。

## 【0026】

そこで、本発明では、このような空隙領域にダミー部材を配置し、絶縁膜の凹凸形状を緩和して、CMP研磨後の絶縁膜の表面を完全に平坦化するものである。

## 【0027】

このように絶縁膜の表面が完全に平坦化されるため、その後のフォトリソグラフィ工程あるいはエッチング工程においてプロセスマージンを増加することができ、その結果、半導体集積回路装置の製造歩留まりを向上し、プロセス立ち上げ時間を短縮することが可能となる。

## 【0028】

なお、配線としては、層間絶縁膜上に形成された金属配線、MISFET（Metal-Insulator-Semiconductor Field Effect Transistor）のゲート配線、DRAM（Dynamic Random Access Memory）のピット線を例示することができる。金属配線およびゲート配線については、DRAM等のメモリ素子のものに限らず、ロジック素子のものについても含まれることはいうまでもない。特に、ロジック素子の配線が一般に3層以上の多層配線であることから、このような配線に本発明を適用すれば顕著な効果が得られる。

## 【0029】

(2) また、本発明の半導体集積回路装置は、前記した半導体集積回路装置において、ダミー配線および配線の部材相互間の間隔、あるいは、ダミー領域および活性領域の部材相互間の間隔を、リソグラフィの分解能から要求される最小スペース幅以上とし、かつ、配線の高さあるいは浅溝の深さの2倍以下とする条件を満足する高密度部材形成領域を含み、その面積はチップ面積の95%以上とするものである。

## 【0030】

このようにダミー配線および配線、あるいは、ダミー領域および活性領域の部材間の間隔を配線の高さあるいは浅溝の深さの2倍以下とすることにより、それら部材上に形成される絶縁膜のCMP研磨速度に部材パターンのパターン依存性が生じなくなり、CMP研磨速度が均一となって絶縁膜の表面平坦性をほぼ完全なものとすることができます。

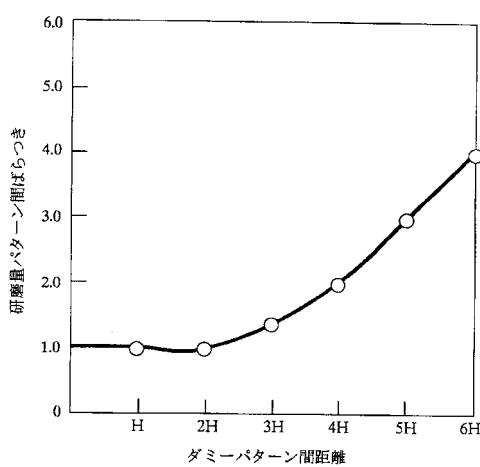

## 【0031】

図30は、本発明者の実験検討により得られた知見を示すデータであり、パターン間距離に対するCMP研磨量のばらつきの値を示したグラフである。横軸は、パターン高さで規格化されたパターン間距離を示し、縦軸は基準パターン（ベタパターン）に対するパターン上絶縁膜のCMP研磨量を示す。図30より明らかな様に、パターン高さの2倍程度までパターンが離れてても絶縁膜のCMP研磨量は変化しない。すなわち、ダミー配線および配線、あるいは、ダミー領域および活性領域の部材間の間隔を配線の高さあるいは浅溝の深さの2倍以下にすれば、これらの部材上に形成された絶縁膜のCMP速度はパターンによらず一定となり、絶縁膜を完全に平坦化することが可能となる。

10

20

30

40

50

## 【0032】

上記のように完全平坦化が実現できる領域つまり高密度部材形成領域は、できるだけ広い方がチップ全体を平坦化できるため好ましいが、チップ面積の全てが高密度部材形成領域である必要はない。すなわち、完全平坦化が実現できる高密度部材形成領域はチップ面積の95%以上であれば実用的に十分平坦な表面を得ることが可能である。

## 【0033】

また、これらの部材間の間隔をリソグラフィの分解能から要求される最小スペース幅以上とする条件は、部材加工を良好に行うためには最小加工寸法以上の加工スペースが必要とされるためであり、この条件を満足することにより配線あるいはダミー配線、または、活性領域あるいはダミー領域の加工を良好に行うことができる。なお、最小スペース幅としては、KrFエキシマレーザを露光源に用いた場合には0.2μmを例示することができる。10

## 【0034】

なお、高密度部材形成領域でない残りの5%の領域では、ダミー配線および配線またはダミー領域および活性領域の部材相互間の間隔が配線の高さまたは浅溝の深さの4倍以下の距離で配置されていることが好ましい。このように、パターン間隔が配線の高さまたは浅溝の深さの4倍以下の距離で配置されている領域つまり低密度部材形成領域の絶縁膜は、図30に示すように約2倍の研磨量ばらつきを示すが、低密度部材形成領域の面積がチップ面積の5%以下であるため、その寄与は無視することができる。

## 【0035】

また、本発明の半導体集積回路装置は、前記半導体集積回路装置において、ダミー配線またはダミー領域を、その幅がリソグラフィの分解能から要求される最小ライン幅以上、または、その長さが最小ライン幅の2倍以上であり、また、スクライプ領域においてはダミー配線またはダミー領域の幅および長さは、ボンディングパッド間の間隔以下である。なお、最小スペース幅および最小ライン幅は、0.2μm、ボンディングパッド間の距離は、10μmとすることができる。20

## 【0036】

このような半導体集積回路装置によれば、ダミー配線またはダミー領域の幅をリソグラフィの分解能から要求される最小ライン幅以上とすることによりダミー配線またはダミー領域の加工を確実に行うことができ、また、ダミー配線またはダミー領域の長さを最小ライン幅の2倍以上とすることにより、それら部材の解像度を確実に保持することができる。つまり、最小加工寸法の幅および長さを有するパターンでは、正確に解像できない恐れがあるが、本発明では、ダミー配線またはダミー領域の長さをその2倍とするため、その恐れを回避することができる。ダミー配線またはダミー領域の幅および長さは、30μm以下で構成されるが、20μm以下が多用され、好ましくは10μm以下で構成される。30

## 【0037】

また、ダミー配線またはダミー領域の幅および長さを30μm以下とすることにより、配線等の寄生容量を低減し、また、ボンディングパッド間のショート不良を低減することができる。すなわち、ダミー配線またはダミー領域の幅あるいは長さが大きくなれば、それらダミー部材が大きくなり、半導体集積回路素子として機能する配線等の寄生容量を大きくすることとなり、半導体集積回路装置の高速応答性能等の性能を損なうこととなるが、それら幅あるいは長さが30μm以下であれば配線等の寄生容量を実用上問題が生じない程度に抑制することができる。また、ダミー配線がスクライプ領域に配置された場合には、スクライプにより発生する切り屑は導電性の塵になる可能性がある。しかし、導電性の塵ではあっても、それによりショートする可能性のある部分は、ボンディングパッドの間に限られるため、ダミー配線の幅および長さをボンディングパッド間の間隔以下としておけば、たとえ導電性の塵になったとしてもショート不良を発生することはない。これらの効果により、半導体集積回路装置の性能および歩留まりを低下することを防止することができる。40

## 【0038】

10

20

30

40

50

また、本発明の半導体集積回路装置は、ダミー配線またはダミー領域がスクライプ領域にも形成されているものである。

【0039】

このような半導体集積回路装置によれば、スクライプ領域においても完全平坦性が確保でき、ウェハ全体の完全平坦性を実現することができる。

【0040】

また、本発明の半導体集積回路装置は、ダミー配線および配線からなる配線のパターン密度またはダミー領域および活性領域からなる領域のパターン密度を、半導体基板の全領域においてほぼ均一とするものである。

【0041】

このような半導体集積回路装置によっても、それらパターン上の絶縁膜の完全平坦性を実現することができる。すなわち、パターン上絶縁膜の平坦性が阻害されるのは、パターンの密度に不均一が存在するためであることは前記したとおりであり、このようなパターンの密度に不均一性が発生しないようにダミー部材を設けることによっても絶縁膜の均一性は向上する。

【0042】

(3) また、本発明の半導体集積回路装置は、前記した半導体集積回路装置であって、ダミー配線が、半導体基板上に設けられたボンディングパッド部またはフォトリソグラフィのためのマーカ部と同一の配線層においてボンディングパッド部またはマーカ部の周辺に形成されていないものである。

【0043】

このような半導体集積回路装置によれば、ワイヤボンディングする際のボンディングパッドの自動検出およびフォトリソグラフィの際のマスク合わせに用いるマーカの自動検出をスムーズに行うことが可能となる。すなわち、ボンディングパッドあるいはマーカの周辺にそれらと同一材料のダミー部材が形成されている場合には、ボンディングパッドあるいはマーカの検出の際にダミー部材がノイズとなってうまく検出されない可能性があるが、本発明ではそのような恐れがない。

【0044】

なお、ダミー配線が形成されていない領域は、ボンディングパッド部から 20 μm の領域またはマーカ部から 60 μm の領域とすることができる。

【0045】

また、本発明の半導体集積回路装置は、絶縁膜として、SOG 法もしくは高密度プラズマ CVD 法により形成されたシリコン酸化膜、リフロー法により形成された BPSG ( Boron-doped Phospho-Silicate Glass ) 膜もしくは PSG ( Phospho-Silicate Glass ) 膜またはポリシラザン膜を含むものとすることができる。

【0046】

このような半導体集積回路装置によれば、SOG 法もしくは高密度プラズマ CVD 法により形成されたシリコン酸化膜、リフロー法により形成された BPSG 膜もしくは PSG 膜またはポリシラザン膜が段差被覆性に優れ、また凹部を埋め込む特性を有するものであるため、配線およびダミー配線あるいは活性領域およびダミー領域により形成される凹部を良好に埋め込み、CMP 法により研磨される絶縁膜の膜厚を薄くすることができる。このような CMP 研磨膜の薄膜化は、CMP 研磨膜の堆積工程の負荷低減のみならず、CMP 工程の負荷低減をも図ることができ、工程時間の短縮等半導体集積回路装置のコスト競争力を向上することもできる。

【0047】

本発明の半導体集積回路装置の製造方法は、前記した半導体集積回路装置の製造方法であって、(a) 半導体基板の正面または層間絶縁膜上に多結晶シリコンまたは金属を含む導電膜を堆積し、導電膜をパターニングして配線およびダミー配線を形成する工程、(b) 配線およびダミー配線により形成される凹部の内面を含む配線およびダミー配線の上層に

10

20

30

40

50

、SOG法もしくは高密度プラズマCVD法により形成されたシリコン酸化膜、リフロー法により形成されたBPSG膜もしくはPSG膜、またはポリシリコン膜からなる第1の絶縁膜を堆積し、凹部を埋め込む工程、(c)第1の絶縁膜上に第2の絶縁膜を堆積する工程、(d)第2の絶縁膜の表面をCMP法により研磨する工程、を有し、第2の絶縁膜の膜厚を第1の絶縁膜の表面の凹凸を平坦化するに十分な膜厚とするものである。

【0048】

このような半導体集積回路装置の製造方法によれば、第2の絶縁膜の堆積膜厚を薄くすることができ、第2の絶縁膜の堆積時間を短縮するのみならず、CMP研磨工程における第2の絶縁膜の研磨量も少なくすることができる。このため、工程自体は従来の工程を踏襲しつつ、工程時間の短縮を図り、工程負荷を低減して半導体集積回路装置のコスト競争力を向上することができる。

【0049】

すなわち、本発明の製造方法では、配線およびダミー配線により形成された凹部をSOG法もしくは高密度プラズマCVD法により形成されたシリコン酸化膜、リフロー法により形成されたBPSG膜もしくはPSG膜、またはポリシリコン膜からなる第1の絶縁膜により埋め込むため、第2の絶縁膜の表面に残存する凹凸は、被膜形成前の凹凸に比較して緩和されたものとなる。そのため、第2の絶縁膜の膜厚は、第1の絶縁膜の表面の凹凸を平坦化するに十分な膜厚とすること、つまり、薄い膜厚でも十分に第2の絶縁膜の表面を平坦化することが可能となる。

【0050】

(4) なお、このCMP研磨の際、硬質パッドを用いることができる。

【0051】

また、第1および第2の絶縁膜により配線およびダミー配線に起因する表面の凹凸をほぼ平坦化し、CMP法による研磨は表面の仕上げ研磨にのみ用いることもできる。この表面仕上げに用いる研磨手段はCMP法に限られず、ドライベルト研磨、ラッピング等その他の研磨手法であってもよい。

【0052】

また、本発明の半導体集積回路装置は、前記した半導体集積回路装置の製造方法であって、(a)半導体基板の主面にシリコン窒化膜を堆積し、活性領域およびダミー領域以外の領域のシリコン窒化膜および半導体基板をパターニングして浅溝を形成する工程、(b)浅溝の内面を含む半導体基板および配線およびシリコン窒化膜上に、シリコン酸化膜からなる絶縁膜を堆積し、浅溝を埋め込む工程、(c)絶縁膜をCMP法により研磨し、シリコン窒化膜を露出する工程、を含むものである。

【0053】

このような半導体集積回路装置の製造方法によれば、素子分離領域にもダミー領域を形成するため、素子分離領域のディッキングすなわち窪みを防止し、半導体基板表面を完全平坦化することができる。また、CMP研磨膜である絶縁膜と半導体基板の活性領域との間に、シリコン酸化膜よりもCMP研磨速度の遅いシリコン窒化膜を形成しているため、シリコン窒化膜がCMP研磨のストップ層となり、さらに完全な平坦性を確保することができる。

【0054】

なお、(c)工程におけるCMP法で用いるスラリをシリコン酸化物を研磨剤とするアルカリ性スラリとし、(c)工程の後に、浅溝に形成された絶縁膜をウェットエッチングまたはドライエッチングによりエッチングして、絶縁膜の表面の高さを半導体基板の主面と同一または半導体基板の主面より低くする工程を含むことができる。スラリをシリコン酸化物を研磨剤とするアルカリ性スラリとする場合には、シリコン酸化膜とシリコン窒化膜との研磨速度の比は3ないし4対1となり、シリコン窒化膜の膜厚を厚くする必要がある。このような場合、シリコン窒化膜を除去した後の半導体基板主面すなわち活性領域の高さと素子分離領域であるシリコン酸化膜の高さとの関係は、シリコン酸化膜の方が高いという状態になる。よって、さらにウェットエッチングあるいはドライエッチングによりシ

10

20

30

40

50

リコン酸化膜をエッティングし、絶縁膜の表面の高さを半導体基板の正面と同一または半導体基板の正面より低くするものである。これにより、微細なゲート加工を行うことが可能となる。

【0055】

また、(c)工程におけるCMP法で用いるスラリを酸化セリウムを研磨剤とするスラリとすることができます。この場合のシリコン酸化膜とシリコン窒化膜との研磨速度の比は30ないし50対1となり、シリコン窒化膜の膜厚を厚くする必要はない。よって、シリコン窒化膜の膜厚は、プロセス上無視し得る程度たとえば50nm以下とすることができ、シリコン窒化膜を除去した後のシリコン酸化膜のエッティングは必要ではない。

【0056】

(5) 本発明の設計方法は、半導体集積回路素子を構成する部材の加工に用いるマスクのマスクパターンを生成する工程を含む設計方法であって、マスクパターンには、部材の部材パターンと、ダミー配置禁止領域には配置されないダミーパターンとが含まれ、部材パターンおよびダミーパターンのパターン相互間のパターン間隔がリソグラフィの分解能から要求される最小スペース幅または0.2μm以上である第1の条件、パターン間隔が、チップ面積の95%以上の領域においては部材の高さの2倍以下であり、チップ面積の5%以下の領域においては部材の高さの4倍以下である第2の条件、ダミーパターンの幅が、リソグラフィの分解能から要求される最小ライン幅または0.2μm以上である第3の条件、ダミーパターンの幅が、半導体集積回路装置に設けられるボンディングパッド間の間隔または10μm以下である第4の条件、ダミーパターンの長さが、最小ライン幅の2倍または0.2μm以上である第5の条件、ダミーパターンの長さが、ボンディングパッド間の間隔または10μm以下である第6の条件、の何れの条件をも満足するようにマスクパターンが生成されるものである。

【0057】

このような設計方法によれば、前記した半導体集積回路装置の製造に必要な部材パターンのマスクを設計することが可能である。前記各条件は、前記した半導体集積回路装置の効果を実現するためのものである。

【0058】

なお、ダミーパターンは、半導体基板のスクライプ領域にも配置できることはいうまでもない。

【0059】

また、ダミー配置禁止領域は、ボンディングパッドとなるパターンの端部から20μmの範囲、フォトリソグラフィのマーカとなるパターンの端部から60μmの範囲、接続孔が形成される領域から0.5μmの範囲、または、フューズ領域とすることができます。このような場合、ワイヤボンディングあるいはフォトリソグラフィの際のボンディングパッドあるいはマスク合わせのためのマーカの検出が容易となり、異層間の配線相互あるいは配線および半導体基板間の接続孔の形成を行うことができる。

【0060】

また、部材がビット線の上層に形成される蓄積容量とほぼ同一層に形成される金属配線の場合には、蓄積容量が形成される領域をダミー配置禁止領域とすることができます。このような場合、第1金属配線層をDRAMの蓄積容量と同一層に形成することができ、第1金属配線層の領域についてはダミー配線を配置することができる。

【0061】

また、部材が半導体基板の正面に形成される活性領域の場合には、半導体基板の正面にゲート配線が形成される領域はダミー配置禁止領域とすることができます。このような場合、ゲート配線の下層にはダミー領域が形成されないため、ゲート配線と半導体基板との間の容量を低減することができる。すなわち、半導体基板正面のダミー領域は見かけ上半導体基板の活性領域と同一の構造となるため、ダミー領域上にゲート配線が形成された場合には、ゲート配線の容量が増加することとなる。このため、ゲート配線の下にはダミー領域を形成しないこととしたものである。これにより半導体集積回路装置の高速応答性能等

10

20

30

40

50

の性能を向上することができる。

【0062】

また、本発明の設計方法は、ダミーパターンにより形成されるダミー部材によって増加する部材の浮遊容量が最小となるようにダミーパターンを配置するものである。これにより、半導体集積回路装置の高速応答性能等の性能を向上することができる。なお、このような配置は、前記設計方法の条件を満足した上で、ダミーパターンの面積を最小にし、ダミーパターンの数を最小にするように最適化することにより行うことができる。また、このような最適化は、レイアウトパターンを生成するコンピュータ等の情報処理装置により自動的に計算することも可能である。

【0063】

【発明の実施の形態】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

【0064】

(実施の形態1)

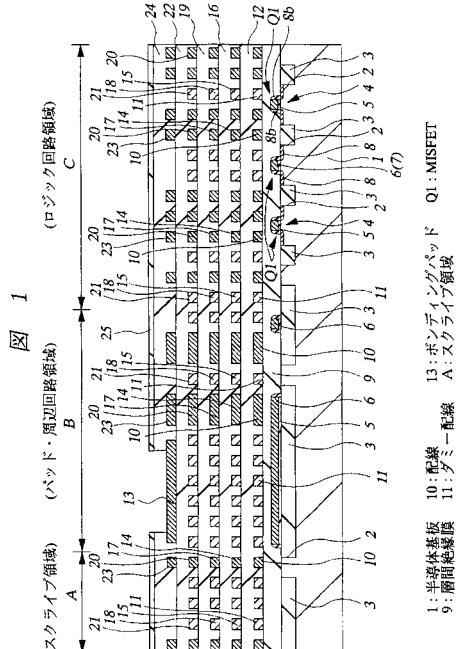

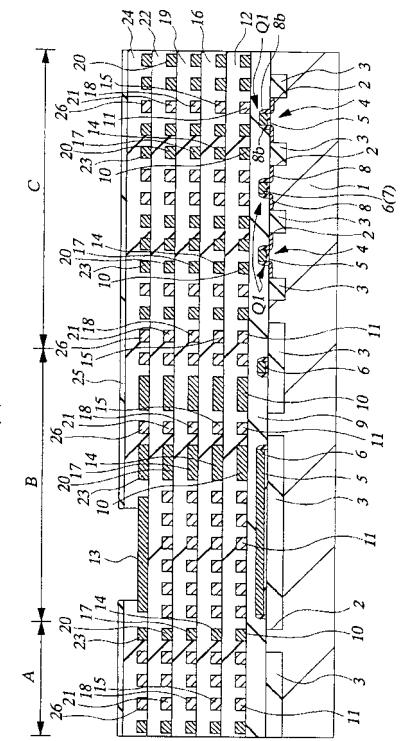

図1は、本発明の半導体集積回路装置の一実施の形態であるロジック集積回路装置の一例を示した断面図である。図1において、Aはスクライプ領域、Bはパッド・周辺回路領域、Cはロジック回路領域である。

【0065】

本実施の形態1のロジック集積回路装置は、半導体基板1の主面に浅溝(Shallow trench)2が形成され、浅溝2に絶縁膜であるシリコン酸化膜が埋め込まれた素子分離領域3を有するものである。この素子分離領域3によって、半導体基板1の主面に形成された活性領域4が規定される。なお、ここでは素子分離として浅溝素子分離構造を例示するが、LOCOS(Local Oxidation of Silicon)法により形成されたフィールド絶縁膜による素子分離構造であってもよい。また、ここでは図示していないが半導体基板の主面にはp型およびn型のウェル領域が形成されていてもよい。

【0066】

活性領域4にはMISFETが形成される。半導体基板の主面上にはMISFETのゲート絶縁膜5を介してゲート配線6が形成されている。ゲート絶縁膜5はたとえば熱酸化法等により形成されたシリコン酸化膜とすることができる、ゲート配線6はたとえばCVD法により形成された多結晶シリコン膜とすることができる。多結晶シリコン膜の表面には、電気抵抗低減のためのシリサイド層が形成されていてもよい。

【0067】

ゲート配線6の一部は、素子分離領域3上を延在するように形成され、他の部分は、半導体基板1の活性領域4に形成されたMISFETQ1のゲート電極7となるものである。ゲート電極7の両側の半導体基板1の主面である活性領域4には不純物半導体領域8が形成されている。不純物半導体領域8は、MISFETQ1のソース・ドレイン領域として機能するものであり、いわゆるLDD(Lightly Doped Drain)とすることもできる。また、ゲート配線6の側面にはサイドウォールスペーサ8bが形成されている。サイドウォールスペーサ8bはたとえばシリコン酸化膜またはシリコン窒化膜とすることができる。

【0068】

ロジック回路領域Cに形成されたMISFETQ1は、ロジック回路の能動素子として機能する。また、図示はされていないが、パッド・周辺回路領域Bに形成されたMISFETは、周辺回路の能動素子として機能する。なお、上記ロジック回路領域Cおよびパッド・周辺回路領域Bに形成されたトランジスタとしてMISFETを例示しているがバイポーラトランジスタあるいはBi-CMOSトランジスタであってもよい。

【0069】

10

20

30

40

50

ゲート配線 6 は層間絶縁膜 9 で覆われ、層間絶縁膜 9 上には、第 1 層目の配線層で構成された配線 10 およびダミー配線 11 が形成されている。

【 0 0 7 0 】

層間絶縁膜 9 は、たとえば PSG 膜、BPSG 膜、あるいは SOG 膜等のシリコン酸化膜とすることができます。また、不純物の拡散を防止するために TEOS シリコン酸化膜等との積層膜とすることもできる。また、層間絶縁膜 9 の表面は CMP 法あるいはエッチバッく法等により平坦化されていることが好ましい。

【 0 0 7 1 】

配線 10 およびダミー配線 11 は同一の材料からなり同一工程（同層）で形成されるものである。材料としては、たとえばアルミニウム（Al）、銅（Cu）等の金属を例示することができるが、不純物が高濃度にドープされた多結晶シリコン膜であってもよい。多結晶シリコン膜の場合その表面がシリサイド化されていてもよい。

【 0 0 7 2 】

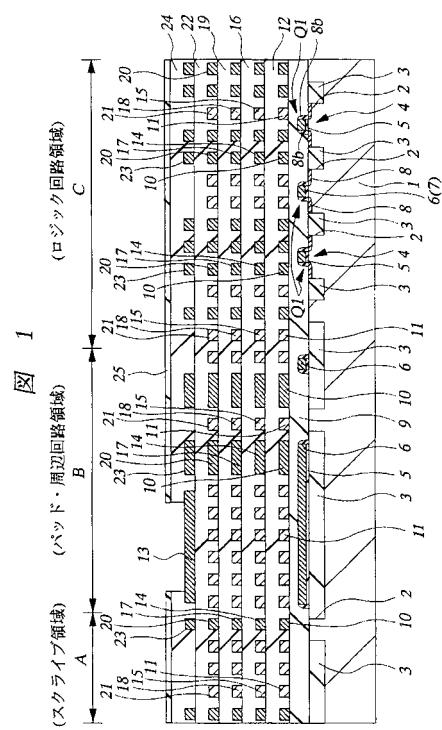

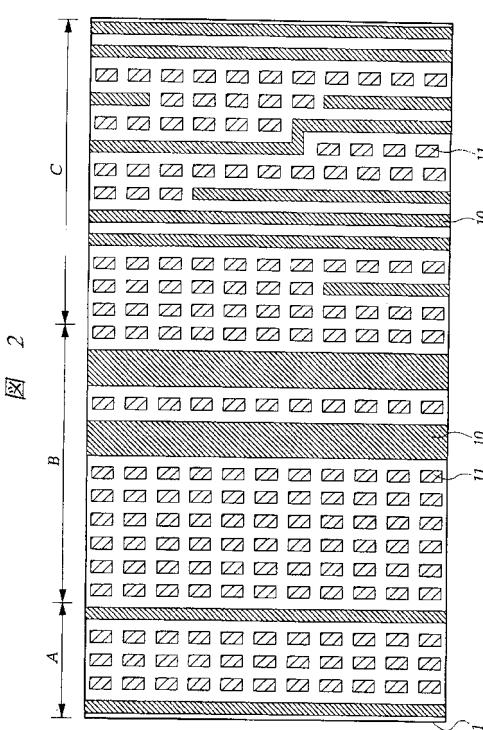

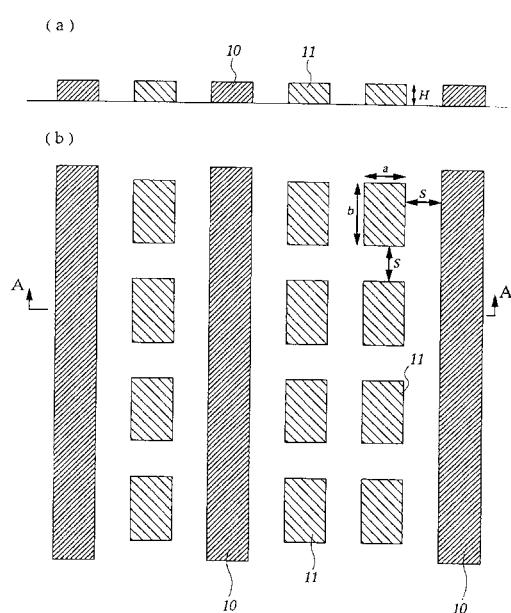

図 2 は、第 1 層における配線 10 およびダミー配線 11 の配置を示す平面図である。

【 0 0 7 3 】

ダミー配線 11 は、配線 10 間の間隔が広い領域（空隙領域）に形成される。その結果、ダミー配線 11 は、配線 10 の形成されていない領域にまんべんなく敷き詰められ、ダミー配線 11 および配線 10 からなる部材間の間隔は狭く、ダミー配線 11 が密に充填されたように配置されることとなる。

【 0 0 7 4 】

また、ダミー配線 11 は、スクライプ領域 A にも形成される。これにより、半導体基板 1 の全面にわたって後に説明する絶縁膜 12 の平坦性が確保される。スクライプ領域 A に形成されるダミー配線 11 の幅および長さは、ボンディングパッド間の間隔以下になるよう構成される。

【 0 0 7 5 】

図 3 (b) は、配線 10 およびダミー配線 11 の配置に適用されるレイアウトルールを説明する平面図であり、図 3 (a) は、図 3 (b) の A - A 線に沿った断面図である。

【 0 0 7 6 】

配線 10 とダミー配線 11 との間隔およびダミー配線 11 相互間の間隔である部材間隔 S は、ダミー配線 11 および配線 10 の配線高さ H の 2 倍以下となっている。このように部材間隔 S を配線高さ H の 2 倍以下とすることにより、先に説明した図 3 (a) の説明のとおり、絶縁膜 12 の CMP 研磨量を均一とすることができる、絶縁膜 12 の表面を完全に平坦化することができる。ただし、チップ面積の 5 % 以下の領域においては部材間隔 S が配線高さ H の 4 倍以下まで許容される。この場合、絶縁膜 12 の研磨量ばらつきは約 2 倍となるがその面積がチップ面積の 5 % 以下であるため、全体としては無視することができ、絶縁膜 12 全体としてはほぼ平坦性が確保できる。

【 0 0 7 7 】

また、部材間隔 S は、リソグラフィツールで要求される最小スペース幅以上の間隔が必要である。この条件により配線 10 およびダミー配線 11 の確実な加工が確保され、部材を設計通りに加工することが可能となる。なお、最小スペース幅としては、KrF エキシマーレーザを光源として用いた露光装置の場合 0.2 μm を例示することができる。

【 0 0 7 8 】

ダミー配線 11 の幅 a は、リソグラフィツールで要求される最小ライン幅以上とする。幅 a を最小ライン幅以上とすることによりダミー配線 11 の加工を確実なものとすることができます。また、スクライプ領域において、ダミー配線 11 の幅 a は、ボンディングパッド 13 間の距離以下とする。ボンディングパッド 13 間の距離以下とすることによりダミー配線 11 がダイシング等により剥離し切り欠きとなって導電性の塵になった場合にもボンディングパッド 13 間をショートすることなく、不良発生の原因を無くすことができる。また、ダミー配線 11 の幅 a は、たとえば 30 μm 以下で構成され、20 μm 以下が多用され、好ましくは 10 μm 以下であり、ボンディングパッド 13 間の距離はたとえば 10

10

20

30

40

50

$\mu\text{m}$ 程度とすることができますが、この程度の大きさのダミー配線11が形成されても配線10の寄生容量は大きくならず、配線10に伝送される信号を遅延させる問題は生じない。この結果、ロジック集積回路装置の性能を低下させることもない。

【0079】

ダミー配線11の長さbは、最小ライン幅の2倍以上とし、スライプ領域においては、ボンディングパッド13間の距離はたとえば10 $\mu\text{m}$ 以下とする。ダミー配線11の長さbを、幅aよりも大きく、かつ最小ライン幅の2倍以下とすることにより、ダミー配線11の幅および長さがともに最小ライン幅である場合には、ダミー配線11が解像しない可能性があるが、長さbを、最小ライン幅の2倍以上とすることにより、幅aが最小ライン幅であってもダミー配線11を確実に解像することができ、その加工を確実なものにすることが可能となる。また、長さbをボンディングパッド13間の距離はたとえば10 $\mu\text{m}$ 以下とするのは、幅aの場合と同様な理由による。

10

【0080】

また、ダミー配線11の長さbは、幅aと同様に、たとえば30 $\mu\text{m}$ 以下で構成され、20 $\mu\text{m}$ 以下が多用され、好ましくは10 $\mu\text{m}$ 以下である。

【0081】

なお、本実施の形態1では、ダミー配線11の形状を長方形としているが、上記の条件を満足する限り、三角形、台形、円あるいは他の多角形としてもよい。また、配線10の寄生容量を最小にするためには、ダミー配線11の形状はできるだけ小さいことが好ましく、その数もできるだけ少ないことが好ましい。よって、上記条件を満足する範囲内で配線10の寄生容量を最小にするためには、部材間隔Sを配線高さHの2倍とし、ダミー配線の幅aを最小ライン幅とし、ダミー配線の長さbを最小ライン幅の2倍(以上)とするのが最も好ましい。本実施の形態では、たとえば幅aは0.6~1 $\mu\text{m}$ で、長さbは10~20 $\mu\text{m}$ で構成される。

20

【0082】

配線10およびダミー配線11は絶縁膜12により覆われる。絶縁膜12の表面はCMP法により研磨されたものであり、その表面は完全平坦化されている。

【0083】

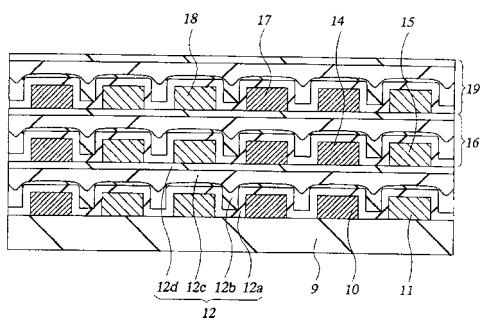

図4は、図1における配線部分を拡大して示した断面図である。

30

【0084】

絶縁膜12は、配線10およびダミー配線11に接する側から絶縁膜12a、絶縁膜12b、絶縁膜12cおよび絶縁膜12dの積層膜となっている。

【0085】

絶縁膜12aは、たとえばTEOSを用いたCVD法により形成されたシリコン酸化膜とすることができます。図示するように、絶縁膜12aは段差に忠実な表面形状で形成される。膜厚はたとえば300nmとすることができます。

【0086】

絶縁膜12bは、たとえば無機SOG膜、高密度プラズマCVD法によるシリコン酸化膜あるいはポリシラザン膜とすることができます。凹部を埋め込む特性を有する膜を用いることができる。よって、図示するように凹部に埋め込まれ、凸部の膜厚は薄くなるように形成される。このように絶縁膜12bによって凹部を埋め込むことができるのは、前記したダミー配線11が前記の条件により形成されているためであり、ダミー配線11により形成された凹部の間隔が絶縁膜12bを埋め込むに必要な間隔以下となっているためである。膜厚は凸部においてたとえば125nmとすることができます。

40

【0087】

絶縁膜12cは、たとえばTEOSを用いたCVD法により形成されたシリコン酸化膜とすることができます。CMP法によりその表面が研磨されているものである。この研磨面は、ダミー配線11が形成されているため、完全平坦面が実現されている。膜厚は凸部においてたとえば500nmとすることができます。

【0088】

50

絶縁膜 12d は、たとえば T E O S を用いた C V D 法により形成されたシリコン酸化膜とすることができる。膜厚はたとえば 200 nm とすることができる。なお、絶縁膜 12d は省略することも可能である。この場合には絶縁膜 12c の堆積の際に絶縁膜 12d の膜厚分だけ上乗せする必要がある。

【 0 0 8 9 】

絶縁膜 12 の上層には、第 2 配線層の配線 14、ダミー配線 15 および絶縁膜 16 が形成され、さらに第 3 配線層の配線 17、ダミー配線 18 および絶縁膜 19、第 4 配線層の配線 20、ダミー配線 21 および絶縁膜 22 が形成されている。配線 14, 17, 20、ダミー配線 15, 18, 21、および絶縁膜 16, 19, 22 の各配線層および絶縁膜は、第 1 配線層の配線 10、ダミー配線 11、絶縁膜 12 と同様に構成されている。 10

【 0 0 9 0 】

また、第 5 配線層の配線 23 および絶縁膜 24 が第 4 配線層の上層の形成され、パッシベーション膜 25 が形成されている。パッシベーション膜 25 は、たとえばシリコン窒化膜とすることができる。また、配線 23 にはボンディングパッド 13 が含まれる。

【 0 0 9 1 】

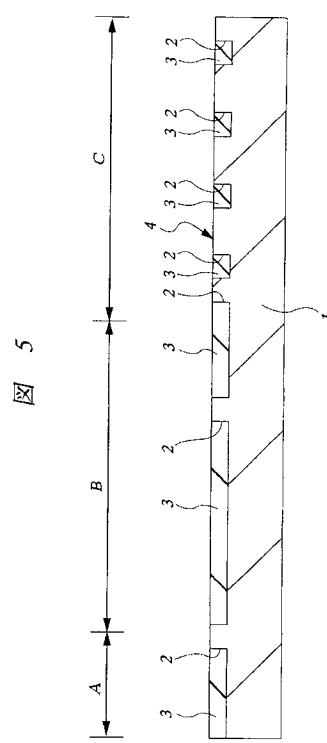

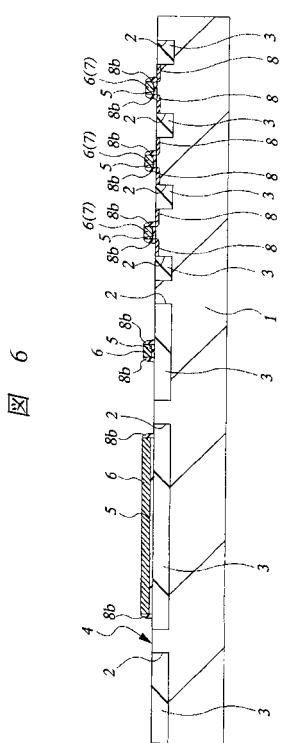

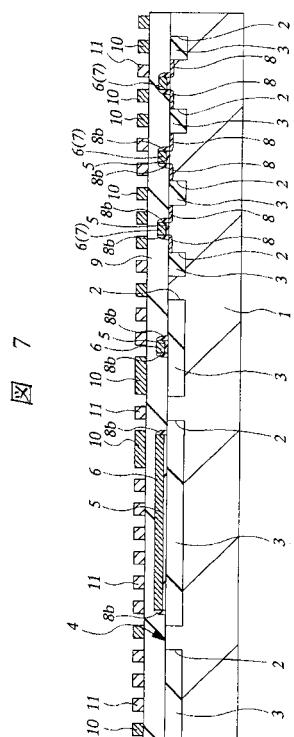

次に、本実施の形態 1 のロジック集積回路装置の製造方法を図 5 ~ 図 11 を用いて説明する。

【 0 0 9 2 】

図 5 ~ 図 11 は、本実施の形態 1 のロジック集積回路装置の製造方法の一例を工程順に示した断面図である。 20

【 0 0 9 3 】

まず、図 5 に示すように、半導体基板 1 を用意し、浅溝 2 をフォトリソグラフィおよびエッチング技術を用いて形成する。その後、浅溝 2 を含む半導体基板 1 の正面にシリコン酸化膜を堆積し、そのシリコン酸化膜を C M P 法等を用いて研磨し、素子分離領域 3 を形成する。その後、n 型および p 型のウェル領域を形成してもよい。

【 0 0 9 4 】

次に、図 6 に示すように、ゲート絶縁膜 5 となるシリコン酸化膜を熱酸化または熱 C V D 法により形成し、さらに C V D 法により多結晶シリコン膜を堆積する。多結晶シリコン膜は、フォトリソグラフィおよびエッチング技術を用いてパターニングされ、ゲート配線 6 ( ゲート電極 7 ) が形成される。その後、ゲート電極 7 をマスクにしてゲート電極 7 に対して自己整合的に不純物をイオン注入し、不純物半導体領域 8 を形成する。さらにシリコン酸化膜を堆積後異方性エッチングを行ってサイドウォールスペーサ 8b を形成する。この後、さらに高濃度の不純物をイオン注入して不純物半導体領域 8 をいわゆる L D D 構造としてもよい。 30

【 0 0 9 5 】

次に、図 7 に示すように、P S G 膜を形成し、エッチバック法あるいは C M P 法を用いて平坦化し、層間絶縁膜 9 を形成する。その後、アルミニウム膜をスパッタ法あるいは蒸着法を用いて堆積する。さらに、アルミニウム膜をフォトリソグラフィおよびエッチング技術を用いてパターニングし、配線 10 およびダミー配線 11 を形成する。これらのパターニングは、前記したダミー配線 11 の条件に従う。 40

【 0 0 9 6 】

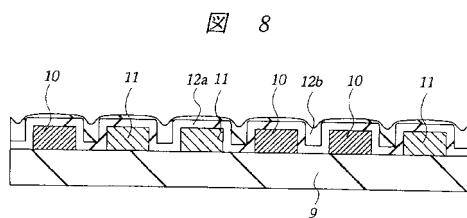

次に、図 8 に示すように、T E O S を用いた C V D 法により絶縁膜 12a を形成する。C V D 法としてはたとえばプラズマ C V D 法を用いることができるが、オゾンを併用した熱 C V D 法でもよい。絶縁膜 12a の膜厚は 300 nm とする。なお、図 8 ~ 図 11 では、配線層のみを示した断面図であり、その下層は省略している。

【 0 0 9 7 】

その後、無機 S O G 膜を用いて絶縁膜 12b を形成するか、有機 S O G 膜を塗布後エッチバックして、配線 10 およびダミー配線 11 により形成されたギャップを埋め込む。無機 S O G 膜の形成は、無機 S O G の塗布およびそのベーク処理により行うことができる。絶縁膜 12b の膜厚は、凸部において 125 nm とする。なお、絶縁膜 12b は、高密度プ 50

ラズマ C V D 法によるシリコン酸化膜あるいはポリシラザン膜であってもよい。

【 0 0 9 8 】

絶縁膜 1 2 b でギャップを埋め込む際に、ダミー配線 1 1 が形成されているためギャップの幅が小さく、ギャップ内を絶縁膜 1 2 b で良好に埋め込むことが可能となる。すなわち、凹部の膜厚を凸部に比較して厚くすることができる。その結果、絶縁膜 1 2 b の表面の凹凸は緩和され、その高低差が小さいものとすることができます。

【 0 0 9 9 】

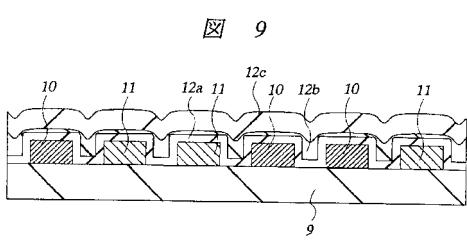

次に、図 9 に示すように、T E O S を用いた C V D 法により絶縁膜 1 2 c を形成する。絶縁膜 1 2 c の膜厚は 7 0 0 n m とすることができる。たとえば、ダミー配線 1 1 を設けない図 2 9 のような場合には、絶縁膜 1 2 c の膜厚は 1 7 0 0 n m 程度必要となるが、本実施の形態 1 では、ダミー配線 1 1 を設けているため、膜厚を 7 0 0 n m と薄くすることができる。その結果、絶縁膜 1 2 c の堆積工程を短縮し、工程負荷を低減することができる。

【 0 1 0 0 】

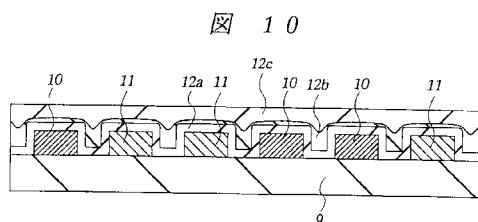

次に、図 1 0 に示すように、絶縁膜 1 2 c の表面を C M P 法により研磨して平坦化する。本実施の形態 1 では、絶縁膜 1 2 c の表面形状は配線 1 0 およびダミー配線 1 1 の形状を、さらに絶縁膜 1 2 b の形状を反映するため、場所によらずほぼ均一な高さとなっている。その結果、研磨速度は場所によらずほぼ均一となり、絶縁膜 1 2 c の表面をほぼ完全に平坦化することが可能である。また、絶縁膜 1 2 c の膜厚が 7 0 0 n m と薄いため、C M P 研磨量を少なくすることができ、C M P 研磨工程の工程負荷を低減することも可能である。なお、研磨量は 2 0 0 n m とすることができます。

【 0 1 0 1 】

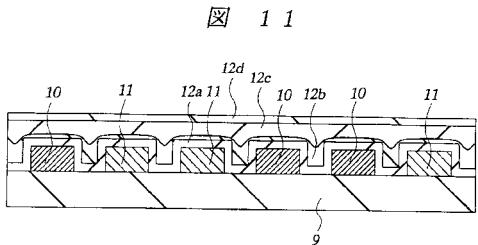

次に、C M P 研磨後の表面洗浄を行い、図 1 1 に示すように、T E O S を用いた C V D 法により絶縁膜 1 2 d を形成する。絶縁膜 1 2 d の膜厚は 2 0 0 n m とすることができる。なお、絶縁膜 1 2 d を省略し、絶縁膜 1 2 c の膜厚を 9 0 0 n m とすることも可能である。

【 0 1 0 2 】

このようにして第 1 層の配線層が完成する。この後、第 1 層配線層と同様にして第 2 層～第 4 層の配線層を形成し、さらに第 5 配線層を同様に形成することができる。その後、パッセーション膜 2 5 を形成して図 1 に示すロジック集積回路装置がほぼ完成する。

【 0 1 0 3 】

本実施の形態 1 の製造方法によれば、絶縁膜 1 2 , 1 6 , 1 9 , 2 2 の表面が完全に平坦化されるとともに、C M P 研磨される絶縁膜の堆積工程およびC M P 研磨の工程を短縮し、工程負荷を低減することができる。このような効果は、ロジック素子のように一般に 3 層以上の多層配線とされる場合に特に顕著となる。

【 0 1 0 4 】

なお、本実施の形態 1 では、配線層が 5 層の場合を例示したが、それよりも多い層あるいは少ない層に適用してもよく、配線層の層数は任意である。

【 0 1 0 5 】

( 実施の形態 2 )

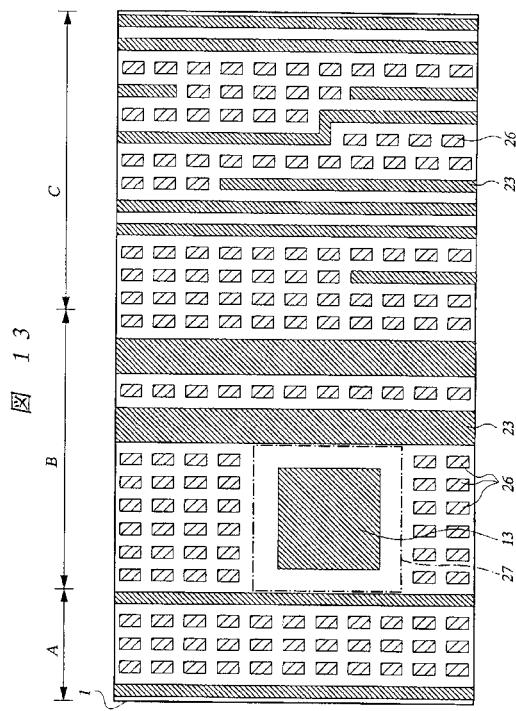

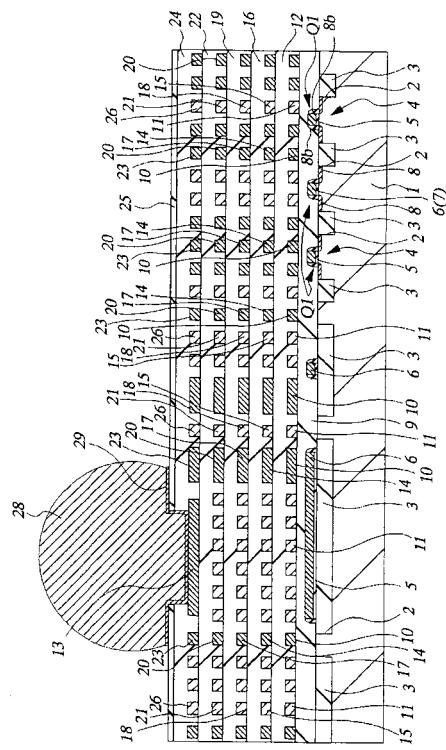

図 1 2 は、本発明の他の実施の形態であるロジック集積回路装置の一例を示した断面図である。

【 0 1 0 6 】

本実施の形態 2 のロジック集積回路装置は、実施の形態 1 で説明したロジック集積回路装置と第 5 層目の配線層を除きほぼ同一である。したがって、以下の説明では、同一の部分の説明を省略し、異なる部分についてのみ説明する。

【 0 1 0 7 】

本実施の形態 2 のロジック集積回路装置は、第 5 配線層に配線 2 3 の他にダミー配線 2 6 を有する。ダミー配線 2 6 が配置される条件は、実施の形態 1 で説明したダミー配線 1 1 の条件とほぼ同様である。ただし、第 5 配線層の配線 2 3 にはボンディングパッド 1 3 が

10

20

30

40

50

含まれるため、ボンディングパッド 13 の周辺については、ダミー配線 26 の配置条件が相違する。

【0108】

図13は、第5配線層の配線23およびダミー配線26の配置を示した平面図である。ボンディングパッド13の周辺には、ダミー配線26が配置されない禁止領域27が設かれている。禁止領域27は、ボンディングパッド13の端部から20μmの範囲とすることができる。

【0109】

このようなロジック集積回路装置によれば、第5配線層にもダミー配線26が形成されているため、パッシベーション膜25の表面も完全平坦化することが可能となる。その結果、図14に示すようにバンプ28の下地膜となるBLM(Ball Limiting Metalization)膜29の加工を精密に行なうことが可能となる。また、ボンディングパッド13の周辺に禁止領域27を設けることにより、ワイヤボンディング装置によるボンディングパッド13の自動検出を確実に行なうことが可能となる。

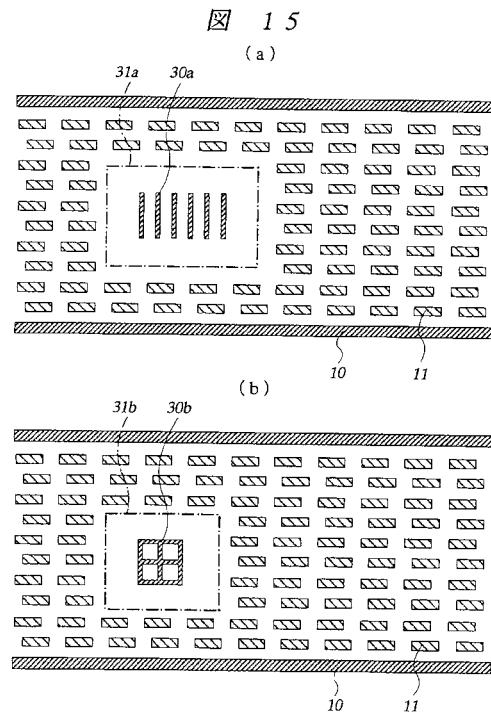

【0110】

なお、本実施の形態2および前記した実施の形態1において、ダミー配線11, 15, 18, 21, 26は、スクライブ領域Aにも形成することができるが、スクライブ領域Aあるいはその他の領域に、図15(a)および図15(b)に示すようなフォトリソグラフィ用のマーカ30a, 30bが形成されている場合には、その周辺にダミー配線11, 15, 18, 21, 26が配置されない禁止領域31a, 31bを設けることができる。また、禁止領域31a, 31bはマーカ30a, 30bの端部から60μmの範囲とすることができる。

【0111】

このような禁止領域31a, 31bを設けることにより、フォトリソグラフィに用いる露光装置においてマーカ30a, 30bの自動検出を良好に行なうことが可能となる。

【0112】

なお、禁止領域31a, 31bは、少なくとも最上層の配線層で構成されるダミー配線26のみに適用し、下層の配線であるダミー配線11, 15, 18には適用しなくてもよいし、ダミー配線自身を設けないようにしてもよい。

【0113】

(実施の形態3)

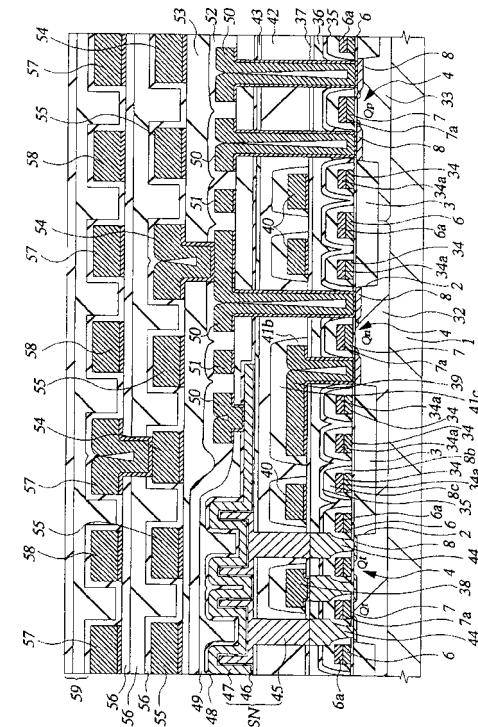

図16は、本発明の他の実施の形態であるDRAMの一例を示した断面図である。

【0114】

本実施の形態3のDRAMの半導体基板1、浅溝2、素子分離領域3および活性領域4については実施の形態1と同様である。また、半導体基板1の正面にはp型ウェル領域32およびn型ウェル領域33が形成されている。

【0115】

p型ウェル領域32の活性領域4には、DRAMのメモリセルMを構成する選択MISFETQ<sub>t</sub>と周辺回路のMISFETQ<sub>n</sub>が形成され、n型ウェル領域33の活性領域4には周辺回路のMISFETQ<sub>p</sub>が形成されている。

【0116】

なお、図16において、左側はメモリセル形成領域であり、中央部および右側は周辺回路形成領域である。DRAMのメモリセルMは、選択MISFETQ<sub>t</sub>と容量素子である蓄積容量SNとを有する。

【0117】

MISFETQ<sub>t</sub>, Q<sub>n</sub>, Q<sub>p</sub>のゲート電極7はたとえば多結晶シリコン膜からなり、その表面にはシリサイド層7aが形成されている。MISFETQ<sub>t</sub>, Q<sub>n</sub>, Q<sub>p</sub>のゲート電極7の両側の活性領域4には不純物半導体領域8が形成され、MISFETのソース・ドレイン領域を構成する。不純物半導体領域8の導電形はMISFETの導電形により異なり、MISFETQ<sub>t</sub>, Q<sub>n</sub>についてはn型、MISFETQ<sub>p</sub>についてはp型となる

10

20

30

40

50

。なお、周辺回路の M I S F E T Q n , Q p については不純物半導体領域 8 は L D D 構造となるよう図示されているが、 L D D でなくてもよい。

【 0 1 1 8 】

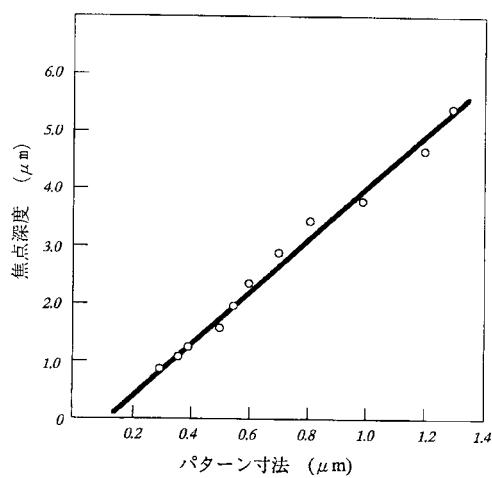

ゲート電極 7 の同一層には、ゲート配線 6 およびダミーゲート配線（ダミー部材）3 4 が形成されている。ゲート電極 7 はゲート配線 6 の一部でもある。なお、ゲート配線 6 およびダミーゲート配線 3 4 はゲート電極 7 と同時（同層で）に形成されるため、その表面にシリサイド層 6 a 、 3 4 a が形成されている。ゲート配線 6 およびダミーゲート配線 3 4 の側面および上面には各々シリコン酸化膜からなるサイドウォールスペーサ 8 b およびキャップ絶縁膜 8 c が形成され、その上層には絶縁膜 3 5 が形成される。絶縁膜 3 5 はたとえば T E O S シリコン酸化膜とすることができる。絶縁膜 3 5 の上層には、 C M P 法により平坦化された絶縁膜 3 6 が形成される。絶縁膜 3 6 はたとえば B P S G 膜とすることができる。本実施の形態 3 ではダミーゲート配線 3 4 が設けられているため、絶縁膜 3 6 をほぼ完全に平坦化することができる。このように完全平坦化することにより、図 1 7 に示すようにリソグラフィの焦点深度が浅くなっても、 0 . 2  $\mu$  m レベルの微細パターンを施した製品の量産化が可能となる。

【 0 1 1 9 】

ダミーゲート配線 3 4 の配置は、実施の形態 1 で説明したダミー配線 1 1 の条件と同様の条件に従う。なお、ダミーゲート配線 3 4 は、接続孔が形成された領域には配置されない。これにより、接続孔の開口を問題なく行うことができる。また、ダミーゲート配線 3 4 は、主に素子分離領域 3 上に形成される。

【 0 1 2 0 】

絶縁膜 3 6 の上層にはたとえば T E O S シリコン酸化膜からなる絶縁膜 3 7 を形成することができるが、省略することも可能である。

【 0 1 2 1 】

絶縁膜 3 7 の上層には、 D R A M のビット線 3 8 、それと同層に形成される配線 3 9 およびダミー配線 4 0 が形成される。これらの配線はたとえば C V D タングステン膜を接着層とする多結晶シリコン膜とすることができる。ダミー配線 4 0 は、実施の形態 1 で説明したダミー配線 1 1 の条件と同様の条件に従う。ただし、接続孔が形成された領域には配置されない。これにより、接続孔の開口を問題なく行うことができる。また、ビット線 3 8 、配線 3 9 およびダミー配線 4 0 の側面および上面には各々シリコン酸化膜からなるサイドウォールスペーサ 4 1 b およびキャップ絶縁膜 4 1 c が形成され、その上層には絶縁膜 4 2 が形成される。絶縁膜 4 2 は、たとえば B P S G 膜とすることができる、 C M P 法により研磨され平坦化されているものである。なお、絶縁膜 4 2 の上層にはたとえば T E O S シリコン酸化膜からなる絶縁膜 4 3 を形成することができるが、省略することも可能である。本実施の形態 3 ではダミー配線 4 0 が設けられているため、絶縁膜 4 2 をほぼ完全に平坦化することができる。

【 0 1 2 2 】

絶縁膜 4 3 の上層には D R A M の蓄積容量 S N と第 1 層の金属配線層が形成されている。蓄積容量 S N は、プラグ 4 4 を介して M I S F E T Q t の不純物半導体領域 8 に接続される下部電極 4 5 と、容量絶縁膜 4 6 を介して下部電極 4 5 に対向して形成されるプレート電極 4 7 とから構成される。また、蓄積容量 S N は絶縁膜 4 8 により覆われている。さらに、蓄積容量 S N は、たとえば高密度プラズマ法により形成されたシリコン酸化膜からなる絶縁膜 4 9 により覆われ、絶縁膜 4 9 の上層に第 1 層の配線 5 0 およびダミー配線 5 1 が形成される。配線 5 0 は、接続孔を介してプレート電極 4 7 あるいは半導体基板 1 の正面の不純物半導体領域 8 に接続される。配線 5 0 およびダミー配線 5 1 は、同時に形成され、たとえば C V D タングステンを接着層とするタングステン膜あるいはアルミニウム膜とすることができます。ダミー配線 5 1 は、実施の形態 1 に説明したダミー配線 1 1 と同様の条件で配置される。ただし、蓄積容量 S N の形成されるメモリマット領域には配置されない。

【 0 1 2 3 】

10

20

30

40

50

配線 5 0 およびダミー配線 5 1 は、たとえば高密度プラズマ C V D 法によるシリコン酸化膜あるいはポリシラザン膜からなる絶縁膜 5 2 により覆われ、さらに、たとえば T E O S シリコン酸化膜からなる絶縁膜 5 3 が形成されている。絶縁膜 5 3 は C M P 法により研磨され平坦化されている。絶縁膜 5 3 の平坦性は、ダミー配線 5 1 が形成されているためほぼ完全な平坦性とすることができます。

【 0 1 2 4 】

絶縁膜 5 3 の上層には、第 2 層の配線 5 4 、ダミー配線 5 5 および絶縁膜 5 6 、さらに第 3 層の配線 5 7 、ダミー配線 5 8 および絶縁膜 5 9 が形成されている。配線 5 4 、ダミー配線 5 5 、絶縁膜 5 6 、配線 5 7 、ダミー配線 5 8 および絶縁膜 5 9 については、実施の形態 1 における配線 1 0 、ダミー配線 1 1 および絶縁膜 1 2 と同様とすることができます。

10

【 0 1 2 5 】

本実施の形態 3 の D R A M によれば、ゲート配線 6 、ビット線 3 8 、第 1 層の配線 5 0 、第 2 層の配線 5 4 および第 3 層の配線 5 7 の各層にダミーの部材 3 4 、4 0 、5 1 、5 5 、5 8 を設けているため、各層の絶縁膜の平坦性を完全なものとすることができる。また、ダミーゲート配線 3 4 、ダミー配線 4 0 、5 1 、5 5 、5 8 をメモリセル形成領域と周辺回路領域との間に配置することにより、各層の絶縁膜を平坦化できる。

【 0 1 2 6 】

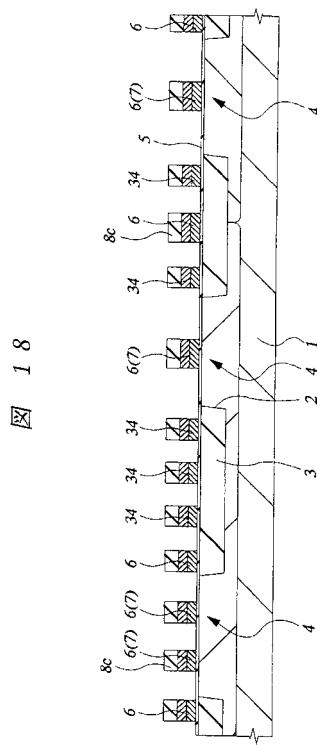

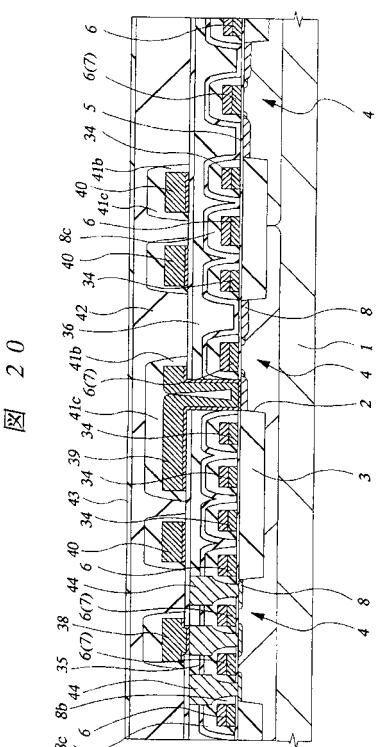

次に、本実施の形態 3 の D R A M の製造方法を図 1 8 ~ 図 2 1 を用いて説明する。図 1 8 ~ 図 2 1 は、本実施の形態 3 の D R A M の製造方法の一例を工程順に示した断面図である。

20

【 0 1 2 7 】

半導体基板 1 の主面への素子分離領域 3 の形成までは実施の形態 1 と同様であるため省略する。

【 0 1 2 8 】

次に、図 1 8 に示すように、ゲート絶縁膜 5 となるシリコン酸化膜を形成し、ゲート配線 6 、ゲート電極 7 およびダミーゲート配線 3 4 となる多結晶シリコン膜を堆積し、さらに、キャップ絶縁膜 8 c となるシリコン酸化膜を堆積した後、これらの積層膜をパターニングしてゲート配線 6 、ゲート電極 7 およびダミーゲート配線 3 4 を形成する。ゲート配線 6 ( ゲート電極 7 ) は通常のレイアウトルールに従いパターニングされ、ダミーゲート配線 3 4 は、通常のレイアウトルールの他に実施の形態 1 で説明したダミー配線 1 1 の条件をほぼ満足して、かつ素子分離領域 3 上に配置されるようにパターニングされる。

30

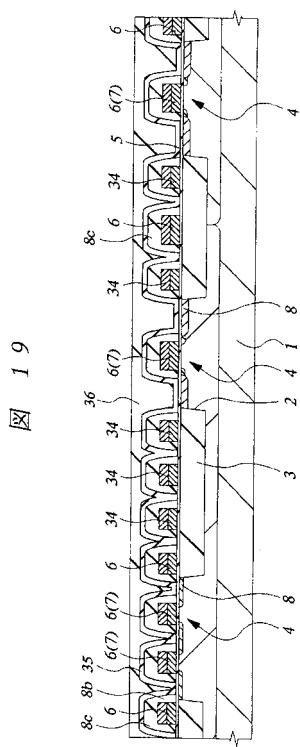

【 0 1 2 9 】

次に、図 1 9 に示すように、サイドウォールスペーサ 8 b を形成し、絶縁膜 3 5 を堆積した後、B P S G 膜を堆積する。その後、B P S G 膜を C M P 法により研磨して絶縁膜 3 6 を形成する。B P S G 膜の膜厚は 8 0 0 n m とすることができる、C M P 研磨量は 4 0 0 n m とすることができる。これは、ダミーゲート配線 3 4 を形成しない場合にはさらに厚いB P S G 膜を堆積する必要があり、C M P 研磨量も増すのに対して、B P S G 膜の膜厚を薄く、C M P 研磨量を少なくすることができ、工程負荷を低減することができるという効果を有する。なお、B P S G 膜の他に、P S G 膜あるいは高密度プラズマ C V D 法によるシリコン酸化膜を用いることができる。

40

【 0 1 3 0 】

なお、サイドウォールスペーサ 8 b およびキャップ絶縁膜 8 c はシリコン窒化膜とすることもできる。シリコン窒化膜を用いた場合には、接続孔を開口する際のエッチングをセルフアラインで行うことが可能となる。

【 0 1 3 1 】

次に、図 2 0 に示すように、C M P 研磨後の洗浄を行った後に、絶縁膜 3 7 を 1 0 0 n m の膜厚で堆積する。絶縁膜 3 7 は省略することも可能である。その後、ビット線 3 8 および蓄積容量 S N の下部電極 4 5 に接続されるプラグ 4 4 を形成した後、ビット線 3 8 、配線 3 9 およびダミー配線 4 0 を形成する。ダミー配線 4 0 は、実施の形態 1 のダミー配線 1 1 の条件と同様の条件により配置される。さらに、サイドウォールスペーサ 4 1 b およ

50

びキャップ絶縁膜41cを形成した後、BPSG膜を堆積し、BPSG膜をCMP法により研磨して絶縁膜42を形成する。なお、BPSG膜の他に、PSG膜あるいは高密度プラズマCVD法によるシリコン酸化膜を用いることができる。ここで、ダミー配線40が形成されているため、絶縁膜42の表面を完全平坦化できると同時に、BPSG膜の膜厚を薄くし、CMP研磨量を減少することができる。さらに、CMP研磨後の洗浄を行い、TEOSプラズマCVD法等により絶縁膜43を堆積する。絶縁膜43は省略することが可能である。

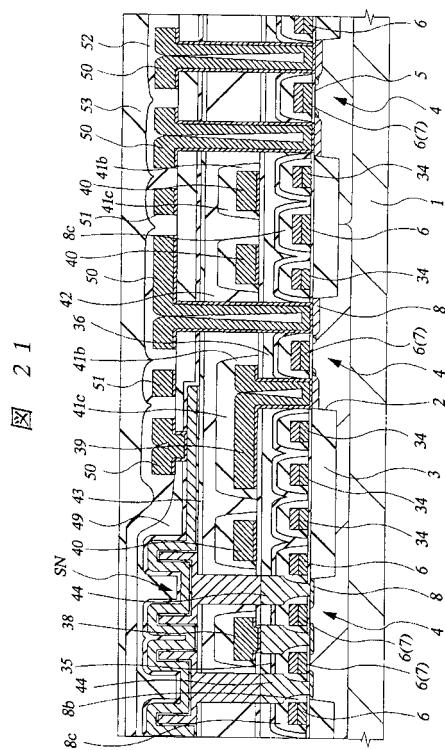

#### 【0132】

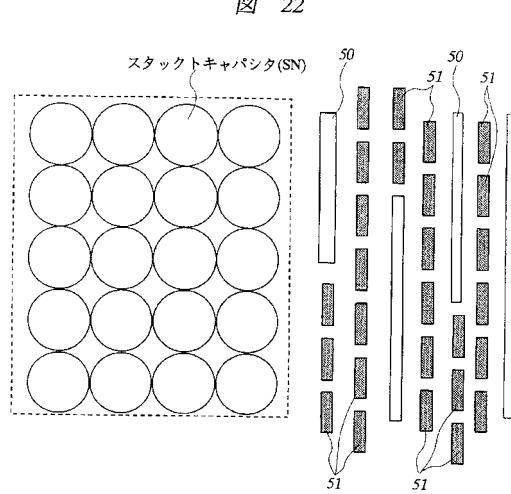

次に、図21に示すように、蓄積容量SNを形成し、BPSG膜を堆積してベーク処理を行い絶縁膜49を形成する。絶縁膜49の膜厚は500nmとすることができる。さらに、接続孔を開口した後、第1層の配線となるタンゲステン膜をCVD法により形成し、アルミニウム膜をスパッタ法により形成する。その後、アルミニウム膜およびタンゲステン膜をパターニングして配線50およびダミー配線51を形成する。ダミー配線51の配置は、実施の形態1のダミー配線11の条件と同様であるが、さらに、蓄積容量SNの配置されたメモリマット領域には配置されないという条件が加重される。図22にこの状況を示す平面図を示す。さらに、BPSG膜を堆積して絶縁膜52を形成した後、たとえばTEOSシリコン酸化膜を堆積してこれをCMP法により研磨し、絶縁膜53を形成する。なお、BPSG膜の他に、PSG膜あるいは高密度プラズマCVD法によるシリコン酸化膜を用いることができる。ここで、ダミー配線51が形成されているため、絶縁膜53の表面を完全平坦化できると同時に、TEOSシリコン酸化膜の膜厚を薄くし、CMP研磨量を減少することができる。

#### 【0133】

その後、実施の形態1と同様に第2層配線層および第3層配線層を形成して実施の形態3のDRAMがほぼ完成する。

#### 【0134】

本実施の形態3の製造方法によれば、各層の絶縁膜が完全平坦化されると同時に、工程負荷を低減することができる。

#### 【0135】

なお、本実施の形態3においても、実施の形態1、2に示すように、ダミー部材をスライプ領域に形成することができ、ポンディングパッドの周辺およびマーカの周辺にダミー部材を配置しないようにすることができる。

#### 【0136】

また、フューズが形成された領域の周辺にもダミー部材を配置しないようにすることもできる。

#### 【0137】

また、実施の形態3のようなダミーゲート配線34を、実施の形態1、2に示した半導体集積回路装置に設けてもよいことは勿論である。

#### 【0138】

##### (実施の形態4)

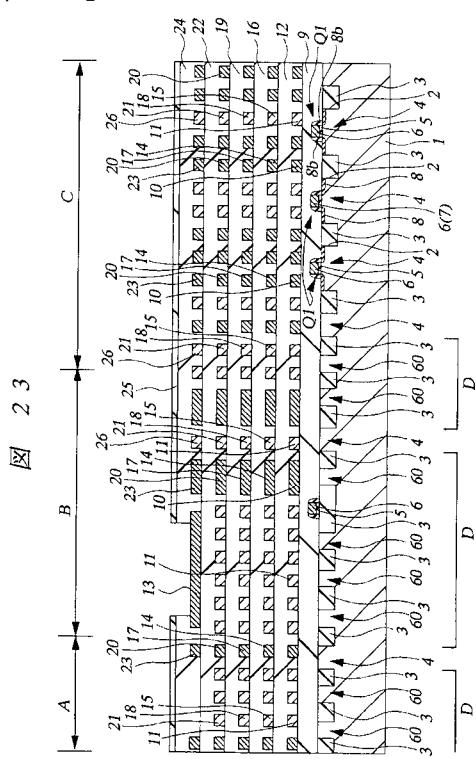

図23は、本発明の他の実施の形態である半導体集積回路装置の一例を示した断面図である。

#### 【0139】

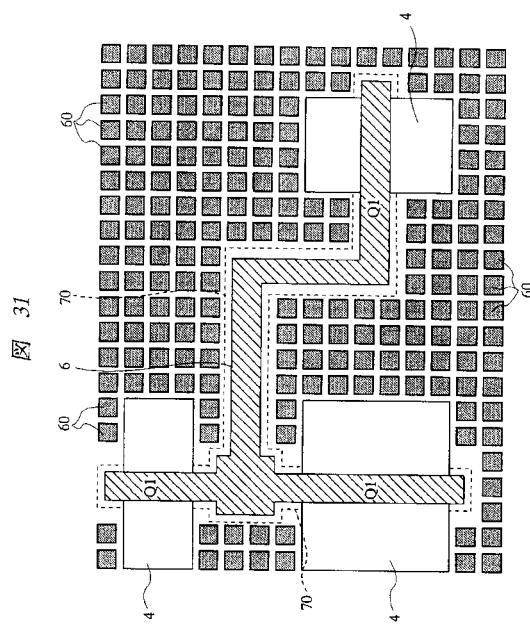

本発明の半導体集積回路装置は、半導体基板1の活性領域4を規定する素子分離領域D、3にダミー領域60が形成されたものである。すなわち、広い素子分離領域Dにおいて、ダミー領域(ダミー部材)60を形成する。素子分離構造以外の半導体基板上の素子および配線等については、実施の形態1と同様であるため説明を省略する。ダミー領域60はスライプ領域にも形成されてよく、実施の形態1のダミー配線11の条件と同様に条件で配置される。このようにダミー領域60が形成されているため、CMP法を用いて素子分離領域D、3を形成する時に、素子分離領域D、3にディッキングが発生せず、半導体基板1の表面を平坦化することが可能となる。また、ダミー領域60の大きさが小さく、

その数を最適化することにより、ダミー領域 6 0 による寄生容量の増加を防止し、半導体集積回路装置の性能を保持することが可能となる。

【 0 1 4 0 】

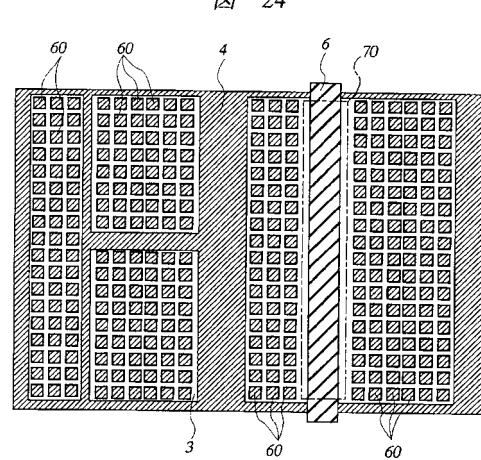

なお、半導体基板 1 の正面にゲート配線 6 が形成される領域には、ダミー領域 6 0 を配置しない方がよい。すなわち、ゲート配線 6 の下部は、ダミー領域 6 0 が配置されない禁止領域 7 0 が設けられる。その状況を図 2 4 および図 3 1 に示す。ダミー領域 6 0 は、半導体基板 1 の活性領域 4 と同様の作用を持つため、その直上にゲート配線 6 が形成されれば、ゲート配線 6 をゲート絶縁膜 5 を介して活性領域 4 と向き合うこととなり、ゲート配線 6 の寄生容量が大きくなるが、このように、ゲート配線 6 が形成される領域には、ダミー領域 6 0 を配置しない場合には、ゲート配線 6 の寄生容量が増加する事がない。この結果、半導体集積回路装置の性能を低下させることがない。10

【 0 1 4 1 】

本実施の形態においては、ダミー領域 6 0 は、幅 a および長さ b が、たとえばともに 15 ~ 20  $\mu\text{m}$  程度の正方形で構成されるが、これに限定されず長方形他の形状であってもよい。

【 0 1 4 2 】

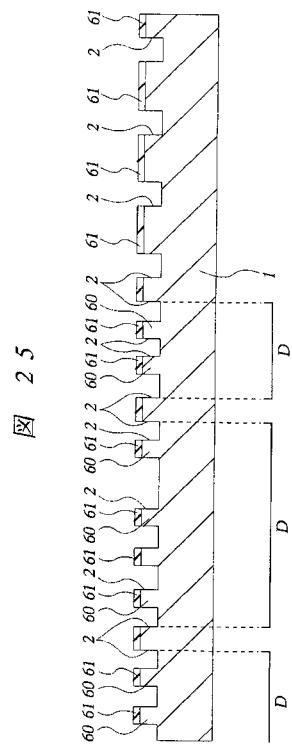

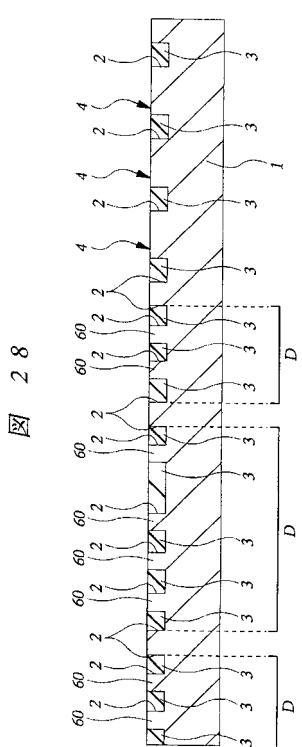

次に、本実施の形態 4 の半導体集積回路装置の製造方法を図 2 5 ~ 図 2 8 を用いて説明する。

【 0 1 4 3 】

まず、図 2 5 に示すように、半導体基板 1 の正面にシリコン窒化膜 6 1 を堆積し、シリコン窒化膜 6 1 および半導体基板 1 をパターニングして浅溝 2 を形成する。浅溝 2 は、素子分離領域 3 となるものおよびダミー領域 6 0 となるものの両方が含まれる。すなわち、活性領域 4 を規定する素子分離領域 D、3 にダミー領域 6 0 が形成されるように浅溝 2 を形成する。20

【 0 1 4 4 】

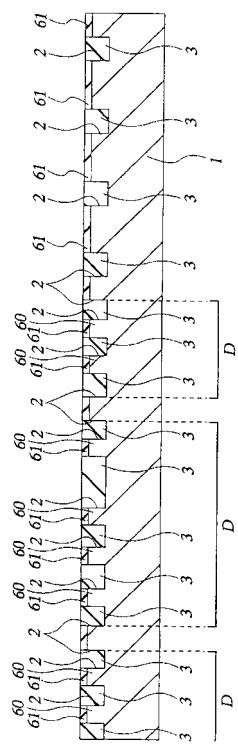

次に、図 2 6 に示すように、たとえば CVD 法によりシリコン酸化膜を堆積し、1 次研磨としてシリコン酸化膜を CMP 法により研磨して、浅溝 2 にシリコン酸化膜を埋め込むことにより素子分離領域 D、3 およびダミー領域 6 0 を形成する。1 次研磨には、シリコン酸化物粒子を研磨剤とするアルカリ性のスラリを用いることができる。この場合、シリコン酸化膜とシリコン窒化膜との研磨速度の比が 3 ~ 4 対 1 となるためシリコン窒化膜の膜厚をある程度厚くする必要がある。30

【 0 1 4 5 】

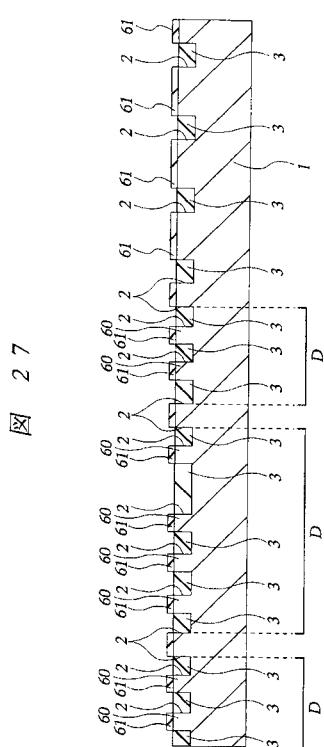

次に、図 2 7 に示すように、さらに 2 次研磨を行い、異物およびダメージ層の除去を行うことができる。なお、2 次研磨は、柔らかいパッドを用いて行うことができ、薬液を用いてもよいが、純水を用いても構わない。その後、半導体基板 1 の両面をスクラブおよびフッ酸洗浄し、さらにアンモニア洗浄および塩酸洗浄を行った後、素子分離領域 3 およびダミー領域 6 0 のエッチバックを行う。エッチバックは、ドライエッチングあるいはウェットエッティングにより行うことができる。このように素子分離領域 3 およびダミー領域 6 0 のエッチバックを行うことにより、素子分離領域 3 およびダミー領域 6 0 の高さを活性領域 4 の高さと等しくするかあるいはそれより低くすることが可能である。これにより、微細なゲート配線の加工が可能となる。なお、このエッチバックプロセスは省略することができる。40

【 0 1 4 6 】

最後にシリコン窒化膜 6 1 を除去して図 2 8 に示す活性領域 4 を規定する素子分離領域 D、3 が形成された半導体基板 1 が用意される。この後の工程は実施の形態 1 と同様であるため省略する。

【 0 1 4 7 】

なお、1 次研磨を酸化セリウムを研磨剤とするスラリを用いて行うことができる。この場合、シリコン酸化膜とシリコン窒化膜との研磨速度の比は 30 ~ 50 対 1 となり、シリコン窒化膜 6 1 の膜厚を 50 nm 以下にすることができる。このような膜厚はプロセス設計50

上無視することができるため、上記の素子分離領域3およびダミー領域60のエッチバッくを省略することが可能となる。これにより、工程を簡略化することが可能となる。

#### 【0148】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

#### 【0149】

たとえば、上記実施の形態1～4では、CMP工程を絶縁膜の研磨工程として用いたが、本発明を用いれば、CMP研磨前に既にある程度の平坦性が確保できるため、CMP研磨を仕上げ工程として用いることも可能である。この場合、仕上げ工程は、CMP法に限られず、ドライベルト研磨あるいはラッピング法等を用いることができる。

#### 【0150】

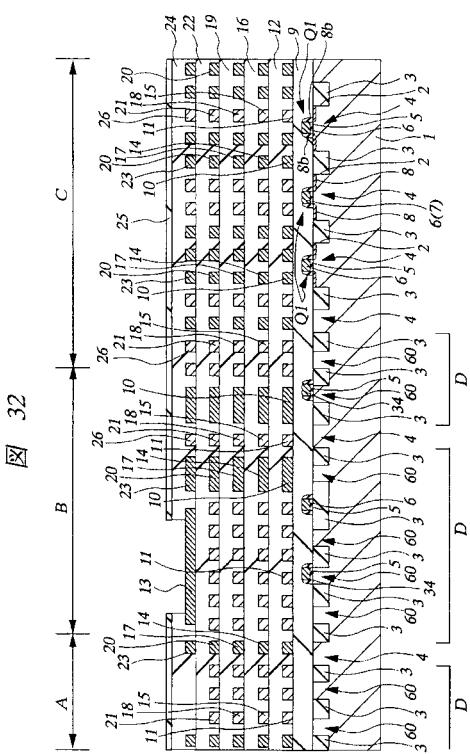

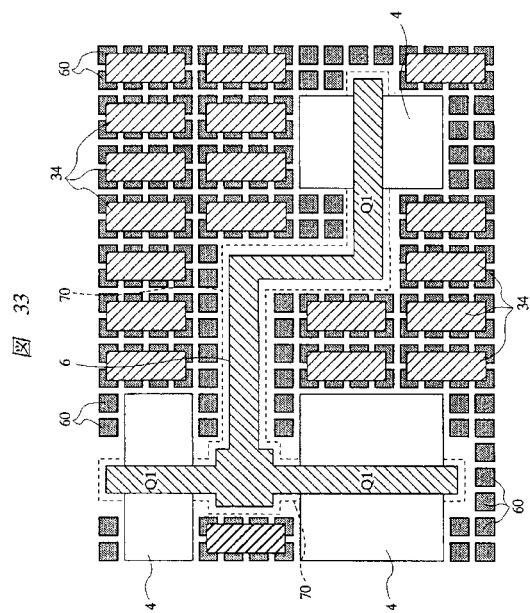

また、図32に示すように、実施の形態4において、実施の形態3に示したダミーゲート配線34を設けてもよい。図33は、図32の要部平面図である。ダミーゲート配線34は素子分離領域D、3およびダミー領域60上を延在するように構成される。また、ダミーゲート配線34は、電気的にフローティングの状態で構成され、ゲート絶縁膜5を介してダミー領域60上に形成される。

#### 【0151】

なお、MISFETQ1のソース・ドレイン領域である半導体領域8を形成する時、素子分離領域D、3上を覆うレジスト膜をマスクにしてイオン注入することにより、ダミー領域60に半導体領域8が形成されない。

#### 【0152】

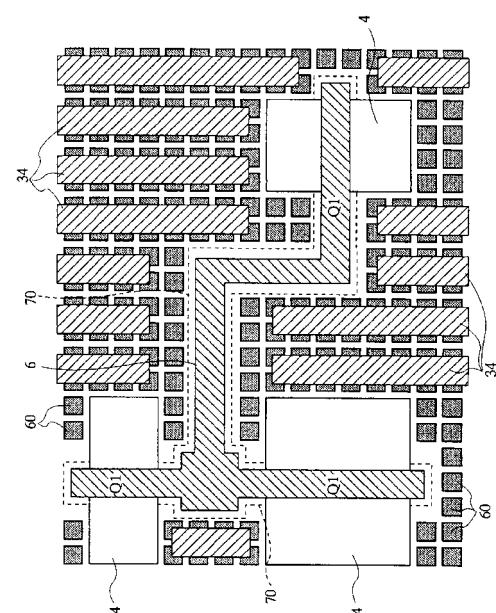

また、図34に示すように、ダミーゲート配線34を配線状に長く形成してもよい。これにより絶縁膜9の表面の平坦性を向上することができる。

#### 【0153】

また、実施の形態3において、実施の形態4に示すダミー領域60を設けてもよいことは勿論である。

#### 【0154】

#### 【発明の効果】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

#### 【0155】

CMP法による研磨後の部材表面を完全に平坦化することができる。

#### 【0156】

フォトリソグラフィ工程およびエッチング工程等でのプロセスマージンを向上し、微細な加工および高集積化に対応することができ、半導体集積回路装置の信頼性および歩留まりを向上することができる。

#### 【0157】

プロセス立ち上げを容易にすることができる。

#### 【0158】

CMP法により研磨される部材の研磨量を低減し、工程負荷の低減および工程時間の短縮によるコスト競争力の向上を図ることができる。

#### 【0159】

CMP法により完全平坦化が可能な部材パターンの設計方法を提供することができる。

#### 【0160】

完全平坦化を実現するための対策により生ずる配線等の寄生容量の増加を抑制し、半導体集積回路装置の性能を確保することができる。

#### 【図面の簡単な説明】

【図1】実施の形態1のロジック集積回路装置の一例を示した断面図である。

【図2】図1における第1配線層の配線およびダミー配線の配置を示す要部平面図である

10

20

30

40

50

。【図3】(b)は、配線およびダミー配線の配置に適用されるレイアウトルールを説明する平面図であり、(a)は、図3(b)におけるA-A線に沿った方向の断面図である。【図4】図1における配線部分を拡大して示した断面図である。

【図5】実施の形態1のロジック集積回路装置の製造方法の一例を工程順に示した断面図である。

【図6】実施の形態1のロジック集積回路装置の製造方法の一例を工程順に示した断面図である。

【図7】実施の形態1のロジック集積回路装置の製造方法の一例を工程順に示した断面図である。

【図8】実施の形態1のロジック集積回路装置の製造方法の一例を工程順に示した断面図である。

【図9】実施の形態1のロジック集積回路装置の製造方法の一例を工程順に示した断面図である。

【図10】実施の形態1のロジック集積回路装置の製造方法の一例を工程順に示した断面図である。

【図11】実施の形態1のロジック集積回路装置の製造方法の一例を工程順に示した断面図である。

【図12】実施の形態2のロジック集積回路装置の一例を示した断面図である。

【図13】実施の形態2における第5配線層の配線およびダミー配線の配置を示した平面図である。

【図14】実施の形態2のロジック集積回路装置の一例を示した断面図である。

【図15】(a)および(b)は、実施の形態2のロジック集積回路装置の他の例を示した平面図である。

【図16】実施の形態3のDRAMの一例を示した断面図である。

【図17】パターン寸法とリソグラフィの焦点深度との関係を示すグラフである。

【図18】実施の形態3のDRAMの製造方法の一例を工程順に示した断面図である。

【図19】実施の形態3のDRAMの製造方法の一例を工程順に示した断面図である。

【図20】実施の形態3のDRAMの製造方法の一例を工程順に示した断面図である。

【図21】実施の形態3のDRAMの製造方法の一例を工程順に示した断面図である。

【図22】実施の形態3のDRAMの製造方法の一例を工程順に示した平面図である。

【図23】実施の形態4の半導体集積回路装置の一例を示した断面図である。

【図24】実施の形態4の半導体集積回路装置の一例を示した平面図である。

【図25】実施の形態4の半導体集積回路装置の製造方法の一例を工程順に示した断面図である。

【図26】実施の形態4の半導体集積回路装置の製造方法の一例を工程順に示した断面図である。

【図27】実施の形態4の半導体集積回路装置の製造方法の一例を工程順に示した断面図である。

【図28】実施の形態4の半導体集積回路装置の製造方法の一例を工程順に示した断面図である。

【図29】(a)～(d)は、本発明者が検討したCMP法による平坦化技術を説明するための断面図である。

【図30】パターン間距離に対するCMP研磨量のばらつきの値を示したグラフである。

【図31】実施の形態4の半導体集積回路装置の一例を示した平面図である。

【図32】本発明の他の実施の形態である半導体集積回路装置の一例を示した断面図である。

【図33】図32に示す半導体集積回路装置の要部平面図である。

【図34】図32に示す半導体集積回路装置の要部平面図である。

【符号の説明】

|                         |               |    |

|-------------------------|---------------|----|

| 1                       | 半導体基板         |    |

| 2                       | 浅溝            |    |

| D、3                     | 素子分離領域        |    |

| 4                       | 活性領域          |    |

| 5                       | ゲート絶縁膜        |    |

| 6                       | ゲート配線         |    |

| 6 a                     | シリサイド層        |    |

| 7                       | ゲート電極         |    |

| 7 a                     | シリサイド層        |    |

| 8                       | 不純物半導体領域      | 10 |

| 8 b                     | サイドウォールスペーサ   |    |

| 8 c                     | キャップ絶縁膜       |    |

| 9                       | 層間絶縁膜         |    |

| 10、14、17、20、23          | 配線            |    |

| 11、15、18、21、26          | ダミー配線         |    |

| 12、12 a ~ d             | 絶縁膜           |    |

| 13                      | ボンディングパッド     |    |

| 16、19、22、24             | 絶縁膜           |    |

| 25                      | パッシベーション膜     |    |

| 27                      | 禁止領域          | 20 |

| 28                      | バンプ           |    |

| 29                      | B L M膜        |    |

| 30 a, 30 b              | マーカ           |    |

| 31 a, 31 b              | 禁止領域          |    |

| 32                      | p型ウェル領域       |    |

| 33                      | n型ウェル領域       |    |

| 34                      | ダミーゲート配線      |    |

| 35 ~ 37                 | 絶縁膜           |    |

| 38                      | ビット線          |    |

| 39、50、54、57             | 配線            | 30 |

| 40、51、55、58、60          | ダミー配線         |    |

| 41 b                    | サイドウォールスペーサ   |    |

| 41 c                    | キャップ絶縁膜       |    |

| 42、43、48、49、52、53、56、59 | 絶縁膜           |    |

| 44                      | プラグ           |    |

| 45                      | 下部電極          |    |

| 46                      | 容量絶縁膜         |    |

| 47                      | プレート電極        |    |

| 61                      | シリコン窒化膜       |    |

| 101                     | 層間絶縁膜         | 40 |

| 102                     | 配線            |    |

| 103                     | 第1絶縁膜         |    |

| 104                     | 第2絶縁膜         |    |

| 105                     | 第3絶縁膜         |    |

| A                       | スクライブ領域       |    |

| B                       | パッド・周辺回路領域    |    |

| C                       | ロジック回路領域      |    |

| Q t                     | 選択M I S F E T |    |

| Q n                     | M I S F E T   |    |

| Q p                     | M I S F E T   | 50 |

## Q 1      M I S F E T

## S 部材間隔

### S N 蓄積容量

a 幅

b 長さ

【 図 1 】

【 図 2 】

【図3】

図3

【図4】

図4

【図5】

【図6】

【図7】

7

【 四 8 】

四 8

【 四 9 】

四 9

【 図 1 0 】

図 10

【 図 1 1 】

図 11

【図 1 2】

四 12

【 図 1 3 】

【 図 1 5 】

【 図 1 4 】

【 図 1 6 】

【図 17】

図 17

【図 18】

【図 19】

【図 20】

【 図 2 1 】

【 図 2 2 】

【 図 2 3 】

【 図 2 4 】

【 図 25 】

【 図 2 6 】

【図27】

【 図 28 】

【図29】

図29

【図30】

図30

【図31】

【図32】

【図33】

【図34】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>H 01 L 27/04

H 01 L 27/108

F I

H 01 L 27/10 6 8 1 F

H 01 L 21/88 K

テーマコード(参考)

(72)発明者 山田 洋平

東京都小平市上水本町五丁目20番1号 株式会社日立製作所半導体事業部内

(72)発明者 竹田 敏文

東京都小平市上水本町五丁目20番1号 株式会社日立製作所半導体事業部内

F ターム(参考) 5F033 HH04 HH08 HH11 HH19 JJ01 JJ08 JJ19 KK01 LL04 MM05

MM07 NN06 NN07 PP06 QQ09 QQ31 QQ48 RR04 RR06 RR09

RR14 RR15 RR25 SS04 SS11 SS15 SS22 TT08 UU04 VV02

VV07 VV16 XX01 XX24

5F038 AV06 CA10 CA13 CD10 CD13 DF05 EZ11 EZ20

5F064 BB01 BB14 BB35 CC09 DD10 EE08 EE09 EE14 EE15 EE23

EE32 EE33 EE35 EE36 EE43 EE51 EE56 GG03

5F083 AD24 AD48 AD49 GA27 JA35 JA36 JA39 JA53 JA56 KA20

LA12 MA06 MA17 MA20 NA01 PR10 PR21 PR40 PR43 PR44

PR45 PR46 PR53 PR54 PR55 PR56 ZA28 ZA29