## (19) 대한민국특허청(KR)

## (12) 특허공보(B1)

(51) Int. Cl.<sup>4</sup>

G05B 19/405

G11C 19/08

(45) 공고일자 1988년03월22일

(11) 공고번호 특 1988-0000421

(21) 출원번호

특 1981-0003369

(65) 공개번호

특 1983-0008288

(22) 출원일자

1981년09월10일

(43) 공개일자

1983년11월18일

(30) 우선권주장

80-133305 1980년09월25일 일본(JP)

(71) 출원인

후지쓰후아낙크 가부시끼가이샤 이나바 세이우에몽

일본국 도오꼬도 히노시 아사히가오까 3 쪽메 5 반찌 1

(72) 발명자

노자와 료이찌로

일본국 도오꼬도 시부 야꾸 사루 가꾸쪼 12-1-2105

끼야 노부유끼

일본국 도오꼬도 하찌오오지시 요꼬까와쪼 108 요꼬까와쪼 쥬따꾸

13-106

(74) 대리인

이준구, 백락신

심사과 : 서장관 (책자공보 제1378호)(54) 카세트 메모리의 데이터 서입 및 독출 제어방법 및 장치**요약**

내용 없음.

**대표도****도1****영세서**

[발명의 명칭]

카세트 메모리의 데이터 서입 및 독출 제어방법 및 장치

[도면의 간단한 설명]

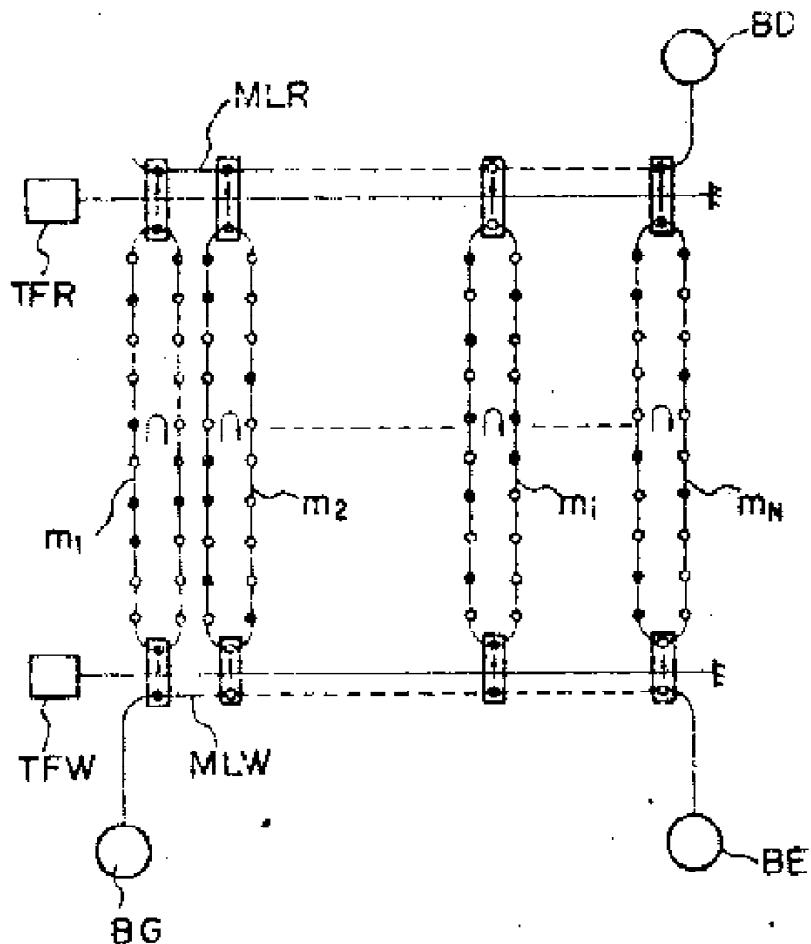

제1도는 메이지·마이너 루우프로 구성된 자기 버블 메모리의 정보 독출 동작을 설명하는 설명도.

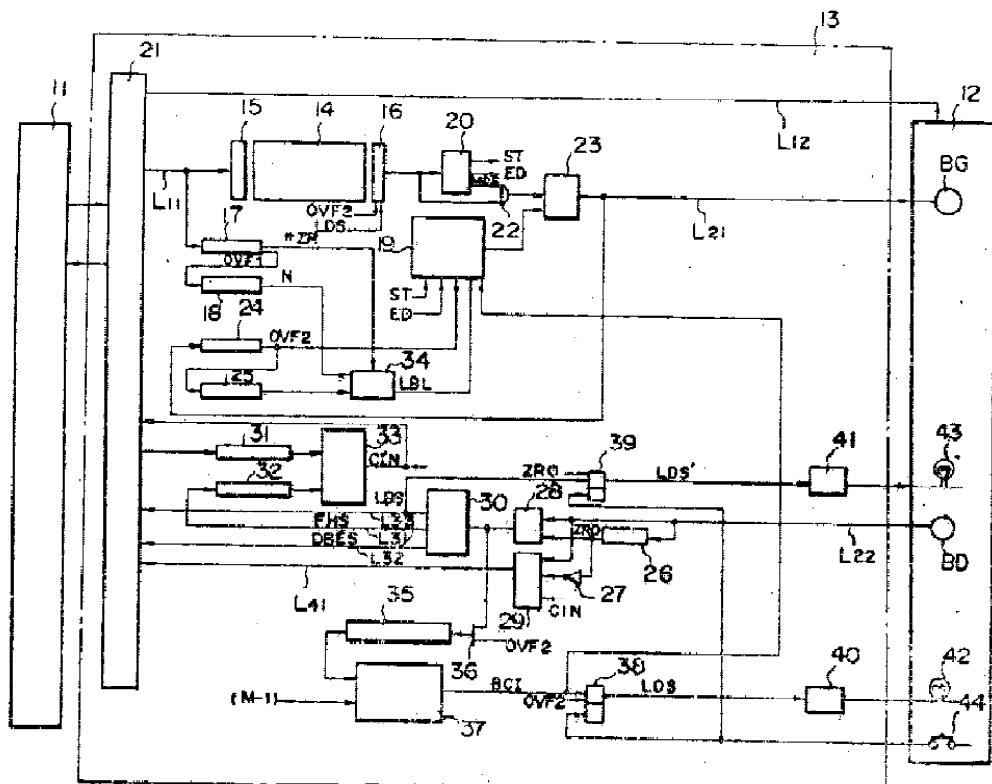

제2도는 본 발명에 따라 카세트 메모리의 데이터 서입과 독출 동작을 제어하는 서입 독출 제어장치의 블럭도.

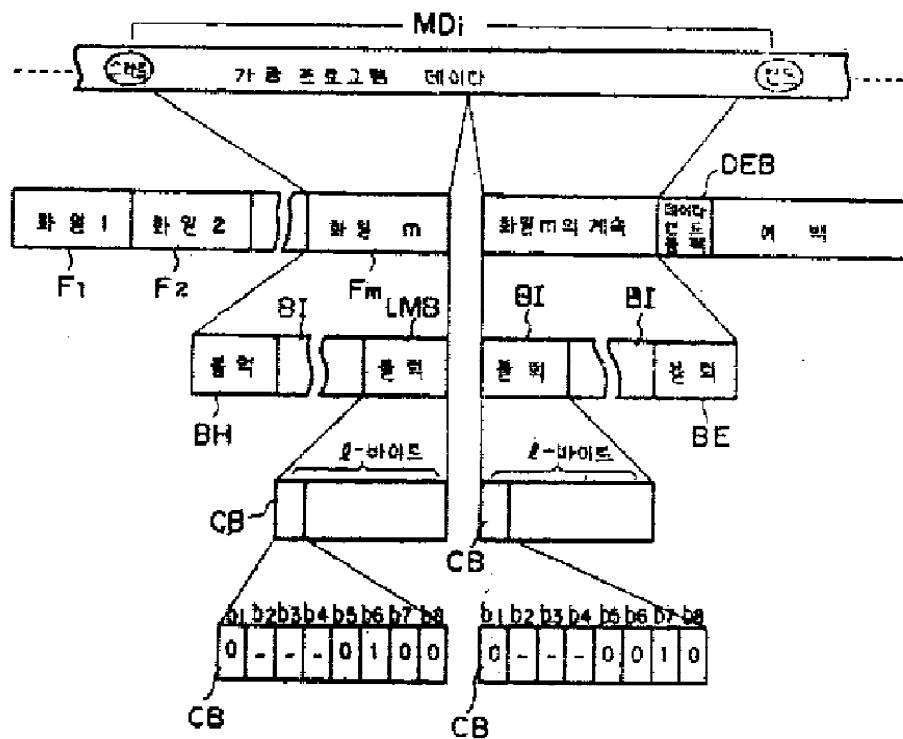

제3도는 데이터의 구성을 설명하는 설명도.

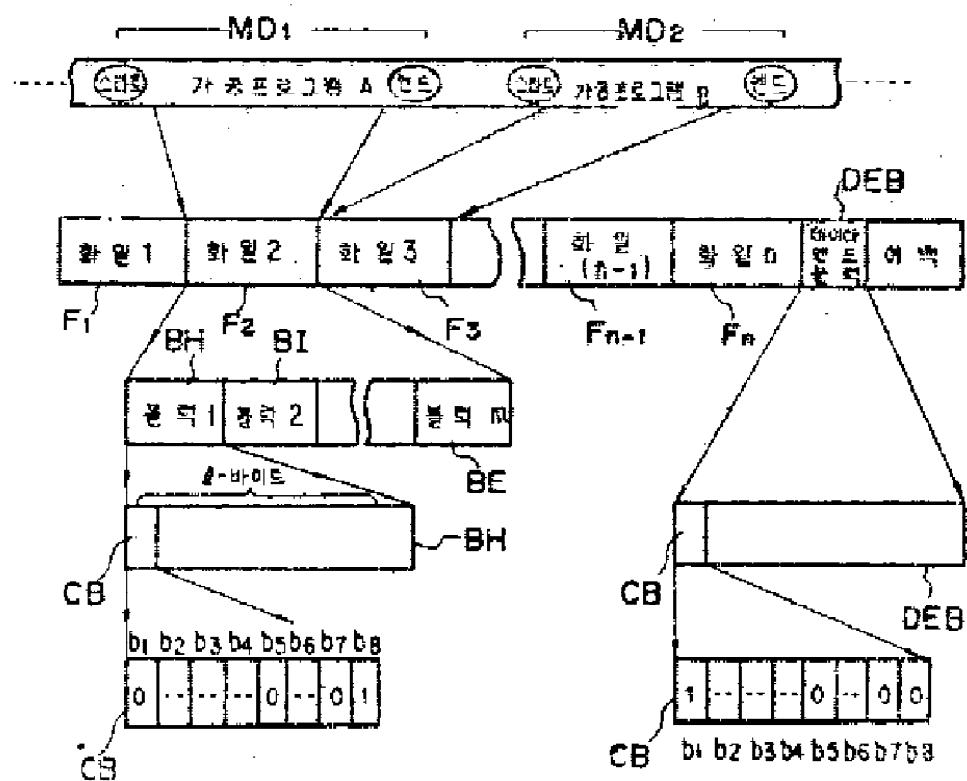

제4도는 본 발명에 따라 데이터의 구성을 설명하는 설명도.

[발명의 상세한 설명]

본 발명은 카세트 메모리의 데이터 서입과 독출을 제어하는 방법 및 장치에 관한 것으로, 특히 버블 카세트 메모리와 관련된 수치제어 데이터를 서입 및 독출하는 방법 및 장치에 관한 것이다.

부분 프로그램(part program)을 기억하기 위한 내부 기억장치를 갖는 수치제어 장치에서, 부분 프로그램을 메모리에 서입하고 메모리에 기억된 정보를 보존하기 위해 기억 매체로서 종이 테이프를 사용하는 것이 종래의 실시예였다. 테이프 판독기와 테이프 천공기는 수치제어 장치에 접속되며 테이프 판독기는 테이프 천공기에 의하여 데이터를 테이프에서 내부 메모리로 전송한다. 종이 테이프는 비교적 수명이 짧기 때문에 종이 테이프 기억 매체에 의한 이런 형의 시스템은 충분히 만족할만한 것이 못되며, 다른 기도 어렵고 판독 착오가 가끔 일어나기 때문에 신뢰도가 떨어진다.

최근 자기 버블과 반도체 등에 의한 형의 카세트 메모리가 기억 매체로 개발되어 구형의 테이프를 대체하고 있다. 또 기억 매체로 그런 카세트 메모리를 사용하는 수치제어 시스템이 발표되어 실용화되고 있다. 그러한 형으로 반도체 카세트 메모리를 이용하는 수치제어 시스템의 예는 미국 특허 번호 4, 229, 804에 발표되었다.

카세트 메모리는 충분히 효과적인 방법으로 이용될 수 없다는 것이 카세트 메모리 기억 매체를 갖는 종래의 수치제어 시스템에서 당연한 단점이다. 예를 들어 가공 작업을 하기 위한 프로그램 등의 데이터를 카세트 메모리의 여백에 기억시키려 할 때, 여백이 전체 프로그램을 기억하는데 불충분한 크기를 갖는 경우 가공프로그램은 독자적인 또는 새로운 카세트 메모리에 기억되어야 하고, 상기 메모리

의 여백에 어떤 것도 서입되지 못한다. 그러므로 카세트 메모리는 여백이 다 소모되어 효과적으로 이용될 수 없고 비용이 많이 들게 된다.

상기의 관점에서 볼때 한개의 가공 프로그램을 전체로 기억시킬 수 없다 하더라도 여백을 다 소모하지 않는 카세트 메모리의 독출과 서입 동작을 제어하는 방법 및 장치가 필요하다. 즉 데이터를 상기 여백으로 서입함으로써 카세트 메모리를 전체적으로 이용할 수 있는 상기 설명한 방법 및 장치를 종래의 기술은 아직 보유하고 있지 않다.

자기 테이프가 컴퓨터 시스템에서 기억 매체로 사용될 때, 복수개의 화일이 한개의 자기 테이프를 즉, 소위 한개의 볼륨을 구성하는 한개의 자기 테이프(아마다 마사유끼의 1980년 7월 25일 발행의 "화일 편집개론(Introduction to File Compilation)"의 페이지 9~11)에 기억될 수 있는 화일 편집 방법이 존재한다. 그럼에도 불구하고, 한개의 볼륨이 여백을 갖고 있지만 화일은 전체로 여백에 서입될 수 없을 때, 데이터는 거기에 기억될 수 없으며, 여백도 다 소모된다.

따라서 본 발명의 목적은 데이터 서입 및 독출 동작을 제어하는 방법 및 장치를 구비하여 메모리의 이용을 효과적으로 하며, 특히 전체의 가공 프로그램이 여백 부분에 기억될 수 없는 때라도 카세트 메모리의 여백부분의 소모를 피하는 것이다.

본 발명의 또 다른 목적은 데이터를 기억하는 여백이 이미 카세트 메모리에서 이용될 수 없을 때, 템프등의 수단에 의해, 카세트 메모리에 과부하를 걸지 않고 더 이상의 데이터를 서입하기 위한 새로운 카세트메모리로 교체하도록 조작자에게 알리는, 데이터의 서입 및 독출 동작을 제어하는 방법 및 장치를 제공하는 것이다.

본 발명의 또 다른 목적은 카세트 메모리에서 여백이 이미 사용될 수 없을 때 쉽게 검출할 수 있는 데이터 서입 및 독출 동작을 제어하는 방법 및 장치를 제공하는 것이다.

본 발명의 또 다른 목적은 카세트 메모리로부터 데이터를 독출할 때 최종 데이터의 독출을 쉽게 검출하고, 이 때 카세트 메모리의 교환을 지시할 수 있는 데이터의 서입 및 독출 동작을 제어하는 방법 및 장치를 제공하는 것이다.

본 발명의 또 다른 목적은 그 방법 및 장치가 버블 카세트 메모리에 응용하는데 가장 적합한 데이터 서입 및 독출 동작을 제어하는 방법 및 장치를 제공하는 것이다.

본 발명의 다른 특징과 이점은 첨부 도면과 함께 취해진 하기 설명에서 명백하게 될 것이다.

본 발명은 제1도의 자기 버블 메모리에 관련해서 설명될 것이다. 버블 메모리는 공지된 것으로 후지쓰리미티드에 의해 출판된 1979년도 책자 "Fujitsu Bubble Memory Technical Information"에 발표되었다. 제1도에서  $m_1, m_2, m_3 \dots m_N$ 은 전부 N개인 마이너 루프의 번호를 나타낸다. 각 마이너 루프는 2M비트의 버블 도메인 전송 트랙을 갖는 폐루프이다. 예를들면 T바야 패턴의 연속적인 루프이다. BG는 버블 메모리 발생기, BE는 버블 흡수기, MLR은 판독 전용의 메이저 라인이며 MLW는 서입 전용의 메이저 라인이다. 마이너루프  $m_1, m_2 \dots m_N$ 의 일단은 메이저 라인 MLR, MLW와 접하고 있으며, 전송 지령이 트랜스퍼 TFR에 의해 내려지면, 즉시 독출 전용의 메이저 라인 MLR의 전송 영역에 있는 마이너 루프의 비트 위치에 있는 버블 도메인(원으로 표시됨)이 메이저 라인 MLR에 전송된다. 한편 전송 지령이 트랜스퍼 TFW에 의해 발해지면, 서입 전용 라인 MLW로 서입된 버블 도메인(원으로 다시 표시됨)은 메이저 라인 MLW에 인접한 영역의 마이너 루프  $m_1, m_2 \dots m_N$ 에 전송된다.

독출 동작의 처리는 하기와 같이 일어난다. N비트로 이루어진 한 액세스 단위의 기억정보를 독출할 때 마이너 루프  $m_1, m_2 \dots m_N$ 의 N개의 버블 도메인이 전송 지령에 응답하여 독출전용의 메이저 라인 MLR에 병렬로 전송된다. 제1도의 자기 버블 메모리에서, 한 액세스 단위의 기억정보는, 각 마이너 루프  $m_i$  ( $i=1, 2, \dots N$ )에 기억된 2M비트의 정보를  $b(i, 1), b(i, 2) \dots b(i, 2M-1), b(i, 2M)$ 라고 할 때,  $b(1, j), b(2, j), \dots b(N, j)$  ( $j=1, 2, \dots, 2M$ )로 이루어지는 N비트 정보를 의미하게 된다.

독출 전용의 메이저 라인 MLR에 전송된 버블 도메인은 한 비트씩 차례로 독출 전용의 메이저 라인 MLR내에서 쉬프트되어 직렬 데이터를 출력한다. 따라서 예를들어 자기저항 효과형의 버블 검출기 BD가 독출 전용의 메이저 라인 MLR의 출력단에 제공되면, 출력 데이터는 버블 도메인의 유무를 검출함으로써 독출될 수 있다. 독출 동작에 있어서는, 마이너 루프  $m_1, m_2, \dots, m_N$  중의 한개의 액세스 단위의 버블 도메인이 소실되는 파괴 독출과 소실되지 않는 비파괴 독출이 있는데, 보통은 비파괴 독출이 행해진다.

그러므로 상기 설명에 따라 기억된 정보는 독출 전용 메이저 라인 MLR에 의해 판독되며, 데이터는 서입 전용 메이저 라인 MLW에 의해 마이너 루프로 서입된다. 버블 도메인은 각 마이너 루프  $m_i$  중을 화살표 방향으로 쉬프트하여, 한개의 액세스 단위의 정보가 독출전용 메이저 라인 MLR, 혹은 서입 전용 메이저 라인 MLW에 도달했을 때 독출 혹은 서입된다. 따라서 버블 메모리로부터 데이터를 독출할 때 독출될 데이터를 기억하는 마이너 루프  $m_i$ 의 비트 위치는 독출전용 메이저 라인 MLR과 마이너 루프 사이의 트랜스퍼 위치에 있어야 하며, 데이터를 버블 메모리로 서입할 때는 새 정보가 서입될 마이너 루프  $m_i$ 의 비트 위치는 서입 전용 메이저 라인 MLW와 마이너 루프  $m_i$  사이의 트랜스퍼 위치에 있어야 한다.

본 발명은 제2도~제4도를 참조하여 설명될 것이다. 제2도는 서입 독출 제어장치의 블럭도이며, 제3도는 데이터의 구성을 보인 것이며, 제4도는 한개의 데이터 화일이 두개의 카세트 메모리로 기억될 경우 데이터의 구성도이다.

우선 제2도를 참조하면, 수치 제어장치(11), 제1도의 메이저 · 마이너 루프 구성을 갖는 자기 버블 메모리를 구비한 카세트 메모리(12)와, 데이터를 카세트 메모리(12)로 서입 및 독출하며 수치 제어장치(11)와 카세트 메모리 사이의 데이터의 전송을 제어하는 서입 독출 제어장치 (13)가 주어지고

있다. 버퍼 메모리(14)는 일련의 가공 데이터 즉 가공 프로그램(한개의 화일이라 함)을 일시적으로 기억하며, 그 데이터는 수치 제어장치(11)에 의해 연속적으로 출력된다. 제3도에서  $MD_i$  ( $i=1, 2, \dots$ )로 표시된 가공 데이터의 한개의 화일은 스타트 바이트, 다수의 가공 프로그램 바이트, 그리고 엔드 바이트로 구성된다. 데이터의 한개의 블럭은 후술하는 바와같이 1개의 바이트로 구성된다. 15는 서임제어 회로, 16은 독출 제어회로를 나타낸다. (1-1)바이트의 용량을 갖는 바이트 계수기(17)은 수치 제어장치(11)로부터 전송된 가공 데이터를 한바이트마다 카운트업한다. 이와함께 그 계수기 내용이 영이 아닐때 신호  $*ZR=1$ "을 출력한다. 계수기(18)는 바이트 계수기(17)의 출력인 오버플로우 펄스  $OVF_1$ 을 계수하는데, 바이트 계수기(17)의 출력  $*ZR=0$ "이면 계수기(18)의 계수값  $NOI$  한 화일의 블럭수를 나타내고,  $*ZR=1$ "이면  $(NOI+1)$ 이 한화일의 블럭수를 나타낸다. 이는 하기에서 좀더 상세히 설명될 것이다. 19는 제어 바이트 발생회로인데, 한 화일의 가공 데이터  $MD_i$ 를 (1-1) 바이트 씩의 다수의 블럭으로 각각 분할할때, 제어 바이트 발생회로(19)는 제3도에 보인 바와같이 각 블럭의 개시 또는 선두에 한개의 제어 바이트 CB를 삽입하고, 1개의 블럭을 1바이트로하여 카세트 메모리(12)에 기억한다. 이 제어 바이트 CB는 제3도에 보인  $b_1 \sim b_8$ 의 8개의 비트로 구성된다. 한개의 화일에서, 선두 블럭 BH의 제어 바이트의 8번째 비트  $b_8$ 에는 "1"이 기억되며, 최종 블럭 BE의 제어 바이트의 5번째 비트  $b_5$ 에는 "1"이 기억되고, 중간 블럭 BI의 제어 바이트의 7번째 비트  $b_7$ 에는 "1"이 기억된다. 카세트 메모리(12)에는 다수의 화일  $F_i$  ( $i=1, 2, \dots$ )가 기억되지만 최종화일  $F_n$  이후에는 데이터 엔드 블럭 DEB가 카세트 메모리에 서입된다. 데이터 엔드 블럭 DEB의 제어 바이트 CD의 첫번째 비트  $b_1$ 에는 "1"이 서입된다. 또한 카세트 메모리(12)에 1바이트의 블럭형태로 각각 일련의 가공 데이터를 기억하는 과정에 있어서, 카세트 메모리에 단 한 블럭의 여백이 남아 있을 때에는 제4도에 보인 바와같이 상기 블럭의 제어 바이트의 6번째 비트  $b_6$ 에 "1"이 서입된다. 그러므로 블럭이 화일의 선두에 있으면 블럭의 제어 바이트의 8번째 비트  $b_8$ 에 "1"이 서입되고, 블럭이 화일의 최종 블럭이면 제어 바이트의 5번째 비트  $b_5$ 에는 "1"이 서입되며, 블럭이 중간 블럭이면 7번째 비트  $b_7$ 에 "1"이 서입되고 블럭이 데이터 엔드 블럭이면 첫번째 비트  $b_1$ 에 "1"이 서입되며, 카세트 메모리(12)의 최후의 1블럭메모리 영역에 기억될 블럭이라면 6번째 비트  $b_6$ 에 "1"이 서입된다.

20은 디코우더로서 버퍼 메모리(14)에서 독출된 데이터가 스타트 데이터 START이면 데이터 스타트 신호  $ST=1$ "을 발생하고, 엔드 데이터 END이면 데이터 엔드 신호  $ED=1$ "을 발생하며, 또 스타트 데이터도 엔드 데이터도 아니면 가공 데이터 신호  $MDS=1$ "를 출력한다. 제어회로(21)은 카세트 메모리서입 독출 제어장치(13)의 전체를 제어하는 제어회로이며, 22는 엔드 게이트, 23은 데이터 합성회로로서 버퍼 메모리(14)의 독출 가공 데이터와 제어 바이트 발생회로(19)의 출력인 제어 데이터를 합성하여 라인  $L_{21}$ 을 통해 카세트 메모리(12)의 버블 발생기(BG)에 이 합성 데이터를 입력한다. 1바이트의 용량을 갖는 바이트 계수기(24)는 합성회로(23)에서 1바이트의 데이터가 출력될 때마다 +1카운트업 한다. 25는 바이트 계수기(24)에서 발생하는 오버플로우 펄스  $OVF_2$ 를 계수하고 1화일의 블럭수를 지시하는 계수기이며, 용량이 1인 바이트 계수기(26)는 카세트 메모리(12)의 버블 검출(BD)기에서 라인  $L_{22}$ 을 통해 독출된 데이터를 1바이트씩 계수하고, 그 내용이 영이면 영신호  $ZRO(=1)$ 를 출력한다. 27은 NOT게이트이며, 28은 영신호  $ZRO=1$ "이면 개방되는 게이트 회로로서, 제어 데이터를 출력한다. 29는, 후술할 화일 검색완료를 지시하는 일치신호  $CIN=1$ "이고 동시에 영신호  $ZRO=0$ "이면 개방되는 게이트 회로이며, 가공데이터(제어 데이터를 제외)를 출력한다. 게이트 회로(28)의 출력단에 접속된 판별회로(30)는 제어 바이트의 제8번째 비트  $b_8$ 이 "1"이면 라인  $L_{31}$ 에 "1"을 출력하고, 제1비트  $b_1$ 이 "1"이면 라인  $L_{32}$ 에 "1"을 출력하며, 제6번째 비트  $b_6$ 이 "1"이면 라인  $L_{33}$ 에 "1"을 출력한다. 판별회로(30)는 게이트 회로(28)를 통하여 입력된 제어 데이터를 검사하여, 화일의 선두 블럭 BH(제3도)가 독출되면 라인  $L_{31}$ 에 화일 선두신호  $FHS(=1)$ 를 출력하고, 데이터 엔드 블럭 DEB가 독출되면 라인  $L_{32}$ 에 데이터 엔드 블럭신호  $DBES(=1)$ 를 출력하며, 카세트 메모리(12)의 최후의 1블럭 기억 영역에 기억된 블럭이 독출되면 최종블럭 신호  $LBS(=1)$ 를 출력한다. 31은 원하는 화일의 위치(선두 화일로부터 몇번째의 화일인가를 의미한다. 즉 선두 화일에서 두번째, 세번째……)를 기억하기 위한 지령 화일 위치 레지스터이다. 예를들면 수치 제어장치(11)에서 제  $i$  번째의 화일을 꺼내라는 화일 검색 지령을 출력하면 수치  $i$ 가 지령 화일 위치레지스터(31)에 기억된다. 또한 직전에 입출력된  $F_i$ 의 다음의 화일  $F_{i+1}$ 의 선두 부분을 검색하라는 화일검색 지령이 출력되면, 제어회로(21)는 직전에 입출력된 화일위치  $i$ 에 1을 합산하고 그 연산 결과( $i+1$ )가 지령 화일 위치 레지스터(31)에 기억된다. 현재 화일 위치 레지스터(32)는 라인  $L_{31}$ 에 "1"이 출력될 때마다 +1 카운트업하고 현재 독출된 화일의 위치를 기억한다. 비교회로(33)은 지령 화일 위치와 현재 화일 위치가 일치할 때 일치신호  $CIN=1$ "을 제어회로(21)과 게이트 회로(29)에 출력한다. 비교회로(34)는 계수기(18, 25)의 내용을 비교하고 내용이 일치하면 일치신호  $LBL$ 을 출력한다.

용량  $M$ 을 갖는 블럭 계수기(35)는 현재 데이터를 서입시킨 카세트 메모리(12)의 기억 영역이 선두에서 몇번째의 블럭인가를 지시한다. 즉 데이터 엔드 블럭 DEB가 검색되면 블럭계수기(35)는 게이트 회로(28)에서 제어 데이터가 출력될 때마다 +1카운트업하고 수치 제어장치에서의 데이터가 카세트 메모리(12)로 서입될 때 블럭 계수기는 1블럭이 서입될 때마다(오버플로우 펄스  $OVF_2$ 가 발생될 때마다) +1만큼씩 증가된다. 데이터 엔드 블럭 DEB가 검색될 때까지 계수된 제어 데이터항의 수는 카세트 메모리로 이미 서입된 총 블럭의 수를 나타내며, 결국 블럭 계수기(35)의 내용은 현재 독출 서입된 카세트 메모리(12)의 위치가 선두에서 몇번째의 블럭 위치에 있는가를 지시한다. 36은 오아(OR) 게이트이다.

비교회로(37)는 블럭 계수기(35)의 내용을 값  $M-1$ 과 비교하고(여기서  $M$ 은 카세트 메모리(12)에 기억될 수 있는 총 블럭의 수이다),  $M-1$ 과 계수기 내용이 일치하면 일치신호  $BCI$ 를 출력한다. 38은 플립플롭을 나타낸다. 데이터 서입 과정중 카세트 메모리(12)에 여백의 1블럭이 남아 있으면 비교회로

(37)는 일치 신호 BCI를 발생하고, 이 일치 신호에 의하여 플립플롭(38)은 세트된다. 39는 다른 플립플롭이며 독출중 카세트 메모리(12)에서 최종 블록 LMB(제4도)가 독출되면, 판별회로(30)는 최종 블럭신호 LBS를 출력하고 플립플롭(39)을 세트한다. 40과 41은 각각 드라이버를 나타내고 42와 43은 램프, 44는 리세트버튼을 나타낸다.

다음에 본 발명의 동작을 설명한다. 우선 1화일의 가공 데이터 MD<sub>1</sub> (제3도)이 수치 제어장치(11)에서 출력되어 카세트 메모리(12)에 기억되는 경우에 대해 설명한다.

수치 제어장치(11)에서 새화일 서입 지령이 제어회로(21)에 보내지면, 제어회로(21)는 라인 L<sub>12</sub>를 통하여 카세트 메모리(12)에 판독지령을 보내므로, 카세트 메모리(12)의 선두에서 순차로 데이터를 라인 L<sub>22</sub>를 통해 독출한다. 바이트 계수기(26)의 내용은 블럭의 최초의 바이트(제어 바이트)를 독출할 때만 영이되기 때문에(ZR0="1"), 제어 데이터는 게이트 회로(28)를 통하여 판별회로(30)에 입력된다. 판별회로(30)는 독출된 데이터의 1바이트마다 입력된 제어 데이터의 제1비트 b<sub>1</sub>이 "1"인가 아닌가를 판별한다. 즉 판별회로(30)는 입력된 제어 데이터가 데이터 엔드 블럭 DEB에 속하는가를 판별한다. 제어 데이터가 제1비트에서 "1"임을 알게되면 판별회로(30)는 데이터 블럭 엔드신호 DBES(논리 "1")를 라인 L<sub>32</sub>를 통해 제어회로(21)에 입력한다. 이 신호 DBES에 의해 제어회로(21)는 즉시 데이터 독출을 정지한다. 이상에 의해 새 가공 데이터 MD<sub>1</sub>을 서입하는 카세트 메모리의 작성 과정이 완료된다. 즉 상기 과정에 따라, 새 정보가 서입되는 마아너루프의 비트 위치가 트랜스퍼 위치에 있게 된다.

한편 상기 처리와 병행하여 혹은 그전에 수치 제어장치(11)에서 출력된 1개의 화일의 가공 데이터는 버퍼 메모리(14)에 기억된다. 또한 가공 데이터 MD<sub>1</sub>이 제어회로(21)를 통해 한 바이트씩 연속적으로 출력되면 서입 제어회로(15)에 의해 버퍼 메모리(14)에 데이터가 기억된다. 이와 병행하여 바이트 계수기(17)는 1바이트의 가공 데이터(스타트 데이터와 엔드 데이터는 제외)가 라인 L<sub>11</sub>에 출력될 때마다 1만큼 카운트업되고, (1-1) 바이트의 가공데이터의 발생에 의해 오버플로우 펄스 OVF<sub>1</sub>을 출력한다. 또 계수기(18)는 이 오버플로우 펄스 OVF<sub>1</sub>을 계수하고 1화일의 블럭수를 지시한다. 즉 ; 엔드 바이트가 발생하는 시점에 있어서 바이트 계수기(17)의 내용이 영 (\*ZR="0")이 되면 계수기(18)의 계수값 NOI 1화일의 총 블럭수가 되며, \*ZR="1"이면 (N+1)이 1화일의 총 블럭수가 된다.

1화일의 총 가공 데이터가 버퍼 메모리에 기억되면 이후 판독 제어회로(16)의 제어에 의하여 가공 데이터가 순차로 1바이트씩 버퍼메모리(14)에서 독출됨과 동시에 디코우더(20)에 입력된다. 최초의 데이터가 스타트 데이터 START이기 때문에 디코우더(20)로부터의 데이터 스타트 신호 ST는 논리 "1"이 되며 그 반면 가공 데이터 신호 MDS와 데이터 엔드 신호 ED는 모두 논리 "0"이 된다. 그 결과 앤드 게이트(22)는 폐쇄되어 스타트 데이터 START는 데이터 합성회로(23)에 출력될 수 없다. 한편 데이터 스타트신호 ST는 "1"이기 때문에 제어 바이트 발생회로 (19)는 제8번째 비트가 "1"로 서입되는 제어 데이터를 발생하고, 합성회로(24)와 라인 L<sub>21</sub>을 통하여 카세트 메모리(12)의 버블 발생기(BG)에 제어 데이터를 입력하며, 그 데이터는 상기의 트랜스퍼 위치에 있는 마이너, 루프의 비트 위치로부터 카세트 메모리로 순차로 서입된다. 그런데 스타트 데이터 이후의 데이터는 가공 데이터이므로 디코우더(20)의 가공 데이터 신호 MDS는 "1"이 되며 엔드 데이터 END가 출력될때까지 "1"이 된다. 그 결과 (1-1)바이트의 가공 데이터가 앤드 게이트(22), 데이터 합성회로(23) 및 라인 L<sub>21</sub>을 통해 카세트 메모리(12)에 기억된다. 즉 가공 데이터의 선두 블럭 BH가 카세트 메모리에 서입된다. 결국 1블럭의 크기를 버블 메모리의 1액세스 단위라고 하면, 그 1블럭의 데이터가 한번에 카세트 메모리로 서입되는 셈이 된다.

바이트 계수기(24)는 1바이트의 데이터가 데이터 합성회로(23)에 의해 출력될 때마다 1만큼씩 카운트업된다. 따라서, 데이터 합성회로(23)가 1바이트 가공 데이터와 (1-1)바이트 가공데이터를 출력하면 즉 데이터 합성회로(23)이 바이트(1블럭)의 데이터를 출력하면, 바이트 계수기(24)는 오버플로우 펄스 OVF<sub>2</sub>를 발생한다. 이에 의하여 계수기(25)는 1만큼 카운트업 됨과 함께, 독출 제어회로(16)은 버퍼 메모리(14)에서의 데이터의 독출을 일시적으로 정지한다. 한편 오버플로우 펄스 OVF<sub>2</sub>의 발생에 의하여 제어 바이트 발생회로(19)는 제7비트 b<sub>7</sub>에 "1"을 서입시킨 제어 데이터를 출력하고, 합성회로(23) 및 라인 L<sub>21</sub>을 통해 카세트 메모리(12)에 입력하여 기억한다. 독출 제어회로(16)는 그후 다시 버퍼 메모리(14)로부터의 (1-1)바이트의 가공 데이터를 다시 독출하고, 앤드 게이트(22), 데이터 합성회로(23)와 라인 L<sub>21</sub>을 통해 카세트 메모리에 입력하여 기억한다. 즉 제2블럭의 데이터가 카세트 메모리에 서입된다. 그후 상기 방법으로 제7번째 비트에 "1"을 서입시킨 제어 데이터가 (1-1)바이트의 가공 데이터마다 카세트 메모리(12)에 서입되며 3번째 블럭의 기억을 행한다.

상기 동작이 반복되고 순차의 블럭의 가공 데이터가 서입된다. 그러면 1화일의 최종 블럭 BE(제3도)의 직전의 블럭이 카세트 메모리(12)에 서입된 시점에서 계수기(25)의 계수값은 NOI 된다. 또한 이 경우 총 블럭의 수는 N+1, 바이트 계수기(17)의 내용이 영이 아니기 때문에 (\*ZR="1") 계수기(18)의 계수값은 NOI 된다. 따라서 최종블럭 BE의 직전의 블럭이 카세트 메모리(12)에 서입되는 시점에서, 계수기(18, 25)의 내용은 모두 NOI 되고 비교회로(34)는 일치신호LBL("1")을 출력한다. 이에 의하여 제어바이트 발생회로(19)는 제5비트 b<sub>5</sub>에 "1"을 서입시킨 제어 데이터를 발생하고, 이 데이터는 데이터 합성회로(23)과 라인 L<sub>21</sub>을 통해 카세트 메모리(12)에 기억된다. 최종블럭의 BE의 가공 데이터가 앤드 게이트(22), 데이터 합성회로(23)와 라인 L<sub>21</sub>을 통해 카세트 메모리(12)에 기억된다.

엔드 데이터 END가 버퍼 메모리(14)에서 독출되면 디코우더(20)는 엔드 데이터신호 ED="1"을 출력한다. 이 신호에 의하여 앤드 게이트(22)는 폐쇄되고 제어 바이트 발생회로(19)는 제1비트 b<sub>1</sub>에 "1"을 서입시킨 제어 데이터를 발생하며 이 데이터는 카세트 메모리(13)에 기억된다(데이터 엔드 블럭 DEB

의서입).

그러므로 상기 일련의 동작에 따라 1화일의 가공 데이터는 각 블럭으로 분할되고 1바이트의 제어 데이터를 가공 데이터가 카세트 메모리(12)에 기억되기 전에 각 블럭의 선두에 삽입된다. 또한 데이터 엔드블럭 DEB는 최신의 화일이 기억된 후 카세트 메모리에 서입된다. 다음 화일이 카세트 메모리에 서입되면 데이터 엔드 블럭이 기억되어야 할 위치에서 그 다음의 화일이 기억되며 이와같이 하여 다시 데이터엔드 블럭이 기억된다.

1화일의 가공 데이터가 카세트 메모리(12)에서 어떻게 독출되어 수치 제어장치에 전달되는 가를 설명한다.

수치 제어장치(11)가 화일 위치  $i$ 를 가진 화일을 꺼내라는 검색 지령이 내려지면, 지령화일 위치  $i$ 는 제어회로(21)의 제어하에 지령화일 위치 레지스터(31)에 세트된다.

이와 병행하여 제어회로(21)는 라인  $L_{12}$ 로 카세트 메모리(12)에 출력되는 독출 지령을 출력하여, 데이터가 카세트 메모리의 선두부터 판독된다. 즉 데이터는 선두 화일부터 순차로 판독된다. 바이트 계수기(26)의 내용은 영(영신호  $ZR0="1"$ )이기 때문에, 최초 바이트의 블럭이 독출되면, 제어 데이터 만이 게이트회로(28)를 통해 판별회로(30)에 입력된다. 판별회로(30)는 제8비트  $b_8$ 에 "1"이 서입된 제어 데이터가 인가될 때마다, 라인  $L_{31}$ 에 "1"을 출력하고, 화일 현재위치 레지스터(32)의 내용을 +1 카운트업한다. 이후 마찬가지로 선두 블럭의 제어 데이터가 독출될 때마다 라인  $L_{31}$ 에 "1"이 나타나고 화일 현재 위치 레지스터(32)의 내용은 +1 카운트업된다.

한편 비교회로(22)는 지령 화일 위치  $i$ 와 화일 현재위치를 비교하고 일치되면 일치신호 CIN을 제어 회로(21)에 출력한다. 이 일치신호 CIN에 의하여 제어회로(21)는 즉시 데이터의 독출을 정지한다(지령화일의 검색 종료). 이상에 의하여 데이터를 독출하고자 하는 화일의 선두를 서어치하는 처리가 종료한다.

상기 과정에 따라, 독출된 데이터를 기억하는 마이너 루프의 비트 위치는 트랜스퍼 위치에 있게 된다.

1 화일의 가공 데이터는 카세트 메모리(12)에서 라인  $L_{22}$ 를 통하여, 제1화일의 1바이트 제어 데이터 와(1-1) 바이트의 가공 데이터의 제1블럭, 1바이트의 제어 데이터와(1-1) 바이트의 가공 데이터의 제2블럭의 순서로 독출한다.

제어 데이터의 독출시 바이트 계수기(26)의 내용이 영( $ZR0="1"$ ) 되므로 게이트 29는 폐쇄되고 가공 데이터는 수치 제어회로에 출력될 수 없다. 한편(1-1) 바이트의 가공 데이터가 판독될 때 바이트 계수기(26)의 내용은 1~(1-1)에 있으므로  $ZR0="0"$ 이 되며, 게이트 회로(29)는 개방되고 일치신호 CIN="1"을 발생한다. 이로 인해 가공 데이터는 라인  $L_{41}$ 과 제어회로(21)를 통해 수치 제어장치(11)에 전송된다. 그러므로 카세트 메모리(12)에서 독출된 데이터는 가공 데이터를 제거하여 수치제어장치(11)에 전송된다.

데이터는 상기 방법으로 카세트 메모리(12)로 서입 및 독출된다. 서입 동작 과정중 화일이 메모리에 전부 기억되기 전에 카세트 메모리(12)의 용량이 다 차는 경우가 있다. 그런 경우 데이터가 메모리에 어떻게 서입될 수 있는가를 설명한다.

데이터가 카세트 메모리(12)에 서입될 때 블럭 계수기(35)의 내용은 이미 메모리로 서입된 총 블럭의 수를 나타낸다. 즉 데이터 서입 동작에 앞서 행해지는 준비과정(데이터 엔드 블럭 DEB의 검색)에서 블럭계수기(35)의 내용은 1 바이트의 제어 데이터가 게이트 회로(28)에 도달할 때마다 +1 카운트업 된다. 또한 데이터가 수치 제어장치(11)에서 카세트 메모리(12)로 서입될 때, 블럭 계수기(35)의 내용은 1 블럭의 데이터가 서입될 때마다, 즉 오버플로우 펄스 OVF<sub>2</sub>가 발생될 때마다 +1만큼 카운트업된다.

비교회로(37)는 항상 블럭 계수기(35)의 내용과( $M-1$ )값( $M$ 은 카세트 메모리(12)에 기억될 수 있는 블럭의 총수)를 비교하여, 계수 내용과( $M-1$ )이 일치하면 일치신호 BCI를 발생한다. 즉 카세트 메모리(12)의 기억 영역의 나머지 부분이 1 블럭과 일치하면 일치신호 BCI가 출력된다. 일치신호 BCI에 의하여 제어 바이트 발생회로(19)는 제어 바이트의 6번째 비트  $b_6$ 에 "1"이 서입된 제어 데이터를 발생한다. 이데이터는 데이터 합성회로(23)와 라인  $L_{21}$ 을 통하여 카세트 메모리(12)에 입력되고, 카세트 메모리의 최종블럭 기억 영역에 서입된다. (1-1) 바이트의 가공 데이터는 버퍼 메모리(14)에서 독출되고 앤드 게이트(22), 데이터 합성회로(23)와 라인  $L_{21}$ 을 통해 송출되어 카세트 메모리의 상기 최종 블럭 기억 영역에 기억된다. 이때 바이트 계수기(24)는 오버플로우 펄스 OVF<sub>2</sub>를 발생하기 때문에 블럭 계수기(35)의 내용은 영으로 회복되고 플립플롭(38)은 세트되며 플립플롭은 드라이버(40)를 통해 램프 드라이브신호 LDS("1")을 출력한다. 카세트 메모리(12)를 하우징하는 케이스에 장착된 카세트 교환 지시 램프는 드라이브신호 LDS에 의하여 점등된다. 점등된 램프를 보고 조작자가 카세트를 새로 교체하게 한다. 조작자가 새 카세트로 교체하고 리세트 버튼 44를 누르면 플립플롭(38)은 리세트되고 램프(42)는 소등되며 램프 드라이브신호 LDS는 "0"이 된다. 나머지 데이터의 서입 과정이 새 카세트 메모리의 선두로 부터 시작될 수 있다.

한편 카세트 메모리(12)의 데이터 독출에서 제6비트  $b_6$ 에 "1"이 서입된 제어 데이터(제어 데이터의 제6비트에 "1"이 설정되어 있으면 다음 카세트로 쉬프트 하라는 의미이다)가 판별회로(30)에 의하여 검출되면, 이 판별회로(30)는 라인  $L_{33}$ 에 신호 LBS("1")을 출력한다. 이 신호 LBS가 발생하고 바이트 계수기(26)의 영신호  $ZR0$ 가 "1"이 되면(제어 데이터에 속하는 최종 블럭 LMB(제4도)가 독출되면) 제어회로(21)는 카세트 메모리(12)에서 데이터의 독출을 정지한다. 동시에 플립플롭(39)은 세트되고 램프 드라이브신호 LDS는 드라이버(41)를 통해 출력된다. 드라이브 신호는 카세트 메모리 교환 지

시 램프(43)를 점등하여 조작자가 그 다음의 카세트로 교체하게 한다.

조작자가 카세트를 교체하고 리세트 버튼(44)를 누르면 플립플롭(39)은 리세트되며 램프(43)는 소등된다. 제어회로(21)는 새 카세트 메모리의 선두로부터 독출을 시작한다. 상술한 두개의 램프(42, 43)들이 사용되는 대신 한개의 램프만이 사용될 수도 있다.

본 발명에 의하면 카세트 메모리의 전 영역에 데이터를 기억할수 있도록 메모리의 효과적 이용을 극대화할 수 있다. 또 1 카세트에 들어갈 수 없는 데이터가 메모리 제어장치측에서 처리될 수 있으므로 NC측에서의 처리는 간단해지고, 다른 I/O장치(테이프 판독기와 테이프 천공기등)와 동일하게 제어할 수 있다. 또한 외부에 제공된 램프는 카세트 메모리가 데이터 서입 또는 독출 동작중 교환되어야 할 때 지시하도록 점등되므로 조작자의 작업이 용이해진다.

상기 설명된 실시예에서, 수치 제어장치에서 카세트 메모리까지 전송된 데이터는 일시적으로 버퍼 메모리에 기억된다. 이것은 반드시 필연적인 것은 아니며, 카세트 메모리로 데이터가 직접 입력될 수도 있다.

본 발명의 정신과 범위를 이탈함이 없이 본 발명의 다른 실시예가 있을 수 있음을 명백하기 때문에, 하기 특허청구범위에 한정된 것 이외의 특수한 실시예에 본 발명이 적용될 수 있음을 이해할 수 있을 것이다.

## (57) 청구의 범위

### 청구항 1

(정정) 수치 제어장치와 카세트 메모리, 그리고 수치 제어장치와 카세트 메모리 사이에 설치되어 수체 제어 데이터를 카세트 메모리로 서입하며 수치 제어 데이터를 카세트 메모리에서 독출하는 서입 독출제어장치를 내장한 수치 제어 시스템의, 카세트 메모리의 데이터 서입 및 독출 동작을 제어하는 방법에 있어서, 데이터를 카세트 메모리로 서입하는 동작에서 한개의 화일을 소정수의 바이트로 이루어진 복수개의 블럭으로 분할하는 과정이 행해지며, 한 화일이 수치 제어장치에서 카세트 메모리로 서입된 데이터의 한 입력단위로 구성되는 단계, 상기 복수개의 블럭의 각각의 선두에 제어 바이트를 부가하는 단계, 카세트 메모리의 나머지 기억 영역의 양이 데이터의 한 블럭의 양이 되는가를 검출하는 단계, 카세트 메모리의 나머지 기억 영역의 양이 데이터의 한 블럭의 양이 되는가를 검출하는 단계, 카세트 메모리의 나머지 기억양이 한 블럭의 양에 상당한 때에는 카세트 메모리에 기억된 최후의 제어 바이트에 다음의 카세트 메모리로 이전하는 것을 지시하는 부호를 서입하는 단계를 구비한 것을 특징으로 하는, 카세트 메모리의 데이터 서입 및 독출 제어방법.

### 청구항 2

(정정) 제1항에 있어서, 카세트 메모리의 나머지 기억 영역의 양이 영이면 카세트 메모리가 교체되어야 하는 것을 외부에 지시하는 단계를 구비한 것을 특징으로 하는, 카세트 메모리의 서입 및 독출 제어방법.

### 청구항 3

(정정) 제1항 또는 제2항에 있어서, 상기 데이터의 한개의 입력 단위가 한개의 수치 제어 프로그램인 것을 특징으로 하는 카세트 메모리의 서입 및 독출 제어방법.

### 청구항 4

(정정) 제1항 또는 제2항에 있어서, 카세트 메모리로부터 데이터를 독출하는 동작에서, 상기 그 다음의 카세트 메모리로 이전하라는 지시를 하는 부호를 검출하는 단계와, 상기 부호가 검출되면 카세트메모리를 교환할 것을 외부에 지시하는 단계를 구비하고 있는 것을 특징으로 하는 카세트 메모리의 서입 및 독출 제어방법.

### 청구항 5

(정정) 제1항 또는 제2항에 있어서, 수치 제어 데이터가 한 블럭 단위로 카세트 메모리에 서입되는 것을 특징으로 하는 카세트 메모리의 서입 및 독출 제어방법.

### 청구항 6

(정정) 수치 제어장치와 카세트 메모리 사이에 설치되어, 수치 제어 데이터를 카세트 메모리로 서입하고 수치 제어 데이터를 카세트 메모리에서 독출하는 데이터 서입 독출 제어장치에 있어서, 수치 제어장치에서 카세트 메모리로 서입된 한 입력장치의 데이터를 각각 소정수의 바이트로 이루어진 복수개의 블럭으로 분할하는 수단과, 제어 바이트를 상기 복수개의 블럭의 각각의 선두에 부가하는 수단과, 카세트 메모리의 나머지 기억 영역의 양이 데이터의 한 블럭과 일치하는가를 판별하는 수단과, 최종 블럭의 제어바이트에 그 다음의 카세트 메모리로의 이전을 지시하는 부호를 서입하는 수단을 구비한 것을 특징으로 하는 데이터의 서입 및 독출 제어장치.

### 청구항 7

(정정) 제6항에 있어서, 카세트 메모리의 나머지 기억 영역의 양이 영이라는 사실을 검출하면 램프를 점등하는 수단을 구비한 것을 특징으로 하는 데이터의 서입 및 독출 제어장치.

### 청구항 8

(정정) 제6항 또는 제7항에 있어서, 카세트 메모리로부터 데이터를 독출할 때 다음의 카세트 메모리로 이전을 지시하는 부호를 검출하는 수단과, 카세트 메모리가 상기 부호의 검출에 의하여 교체되어

야할 것을 외부에 지시하는 수단을 구비한 것을 특징으로 하는 데이터 서입 및 독출 제어장치.

### 청구항 9

(정정) 제6항 또는 제7항에 있어서, 카세트 메모리가 버블 카세트 메모리임을 특징으로 하는 데이터의 서입 및 독출 제어장치.

### 도면

#### 도면1

도면2

도면3

## 도면4