# United States Patent

Glugos et al.

[15] 3,692,988

[45] Sept. 19, 1972

[54] **PARCEL POSTAGE METERING SYSTEM**

[72] Inventors: Daniel F. Glugos, Huntington; Gerald C. Freeman, Norwalk; Peter N. Piotroski, Stamford, all of Conn.

[73] Assignee: Pitney-Bowes Inc., Stamford, Conn.

[22] Filed: Jan. 18, 1971

[21] Appl. No.: 107,223

[52] U.S. Cl.....235/151.33, 177/25

[51] Int. Cl.....G06f 15/20, G01g 19/413

[58] Field of Search .....235/151.33, 177; 177/25, 58, 177/61, DIG. 1, DIG. 3; 340/146.2, 173 LM

[56] **References Cited**

UNITED STATES PATENTS

3,594,735 7/1971 Furlong et al.....340/173 LM

3,290,491 12/1966 Wahlberg .....235/151.33 X

3,315,067 4/1967 Bell et al.....235/151.33

3,167,740 1/1965 King et al. ....235/177

3,057,547 10/1962 Adler et al.....235/151.33 X

*Primary Examiner*—Eugene G. Botz

*Assistant Examiner*—Edward J. Wise

*Attorney*—William D. Soltow, Jr., Albert W. Scribner, Martin D. Wittstein and Louis A. Tirelli

[57] **ABSTRACT**

A parcel postage metering system comprises a scale for providing a parcel weight reading which is used in conjunction with the parcel destination (postal zone) to enter a postage memory and obtain the appropriate postage. The thus obtained postage controls apparatus for setting a postage meter to issue a stamp imprinted with the appropriate parcel postage. A zip code to zone conversion memory is incorporated to provide the appropriate zone entry into the postage rate memory, given the zip code of the parcel destination.

23 Claims, 20 Drawing Figures

PATENTED SEP 19 1972

3,692,988

SHEET 01 OF 14

INVENTORS

DANIEL F. DLUGOS

GERALD C. FREEMAN

PETER N. PIOTROSKI

PETER N. PIOTRO

BY

Albert W. Scribner

ATTORNEY

FIG. 3

PATENTED SEP 19 1972

3,692,988

SHEET 04 OF 14

FIG. 4

PATENTED SEP 19 1972

3,692,988

SHEET 05 OF 14

FIG. 5

FIG. 20

FIG. 6

FIG. 7

FIG. 8

## POSTAGE MEMORY 52

FIG. 9

## ZIP-ZONE MEMORY 90

FIG. 10

PATENTED SEP 19 1972

3,692,988

SHEET 09 OF 14

FIG.

FIG. 13

OVERSIZE

LOGIC 100

FIG. 18

POSTAGE DIGIT SELECTION APPARATUS 30

PATENTED SEP 19 1972

3,692,988

SHEET 12 OF 14

FIG. 14

POSTAGE

DIGIT

SELECTION

APPARATUS 30

PATENTED SEP 19 1972

3,692,988

SHEET 13 OF 14

FIG. 15

FIG. 16

FIG. 17

PATENTED SEP 19 1972

3,692,988

SHEET 14 OF 14

FIG. 19

## PARCEL POSTAGE METERING SYSTEM

## BACKGROUND OF THE INVENTION

There have been a number of proposals for parcel postage systems to be used in the processing of parcels for mailing or shipping. A comprehensive or universal system must be sufficiently flexible to handle a number of variables which are involved in mailing or shipping parcels. The weight of each parcel must be determined with reasonable accuracy and speed. The distances between the original and the various parcel destinations must be determined in order to identify the appropriate postal zone for each parcel. Then, the postage applicable to each parcel must be determined on the basis of its weight and destination or postal zone. Having determined the applicable postage, a postage meter or the like is then set up and controlled to issue a stamp imprinted with that postage; the stamp being adhered to the parcel.

There are other factors or variables which a truly universal system should be equipped to handle. For example, the United States Post Office offers various classes of parcel post service, such as surface parcel post and air parcel post, each with different postage rate schedules based according to weight and postal zone. Also, there is United Parcel Service which offers parcel shipping services. It would thus be desirable to have a system which can be selectively controlled to compute postage or shipping charges for each of these different services.

In addition, there are factors such as insurance, special handling, special delivery, etc., which are often times desired and preferably should be capable of system implementation. Also, the special situation involving the computation of postage or shipping charges for oversize parcels should be considered in the design of a universally flexible parcel postage system.

When dealing with United Parcel Service, there are special shipping situations which require an additional charge, such as when shipping from west to east. Moreover, United Parcel Service (UPS) does not have authorized land routes between a number of geographical locations and must resort to so-called "drop shipping," which presents a special shipping charge situation. In some areas UPS has different rate schedules for intrastate and interstate shipments. All of these various situations should be accounted for.

Heretofore, some of the proposed parcel postage computing systems have been essentially "special purpose" and thus inflexible machines adapted to handle only a single class of postage service. Attempts to provide "general purpose" machines have resulted in extreme complexity; such systems being unwieldy from both the operator standpoint and the servicing standpoint.

From a practical standpoint, such systems cannot operate without human intervention. At the very least, an operator must be on hand to determine the postal zone of each parcel destination. This determination must then be introduced into the system as an operator input. Other operator inputs manifesting selections of service, class of service, insurance, etc., are called for if the system is to be applicable to diverse mailings. An oversize parcel situation must also be entered into the system by the operator if the correct postage is to be computed. Thus, operational simplicity is a most im-

portant consideration in the design of a truly flexible parcel postage system if the use of highly skilled and thus highly paid operating personnel is to be avoided.

It is accordingly an object of the present invention to provide an improved system for automatically determining parcel postage or shipping charges for various selected types and classes of postal services.

An additional object is to provide a system of the above character which is capable of rapidly processing 10 a large number of parcels pursuant to automatically determining the postage of each and controlling a postage meter accordingly.

Still another object is to provide a system of the 15 above character which is selectively controllable to accommodate special situations requiring additional postage or shipping charges, such as oversize parcels, insurance, special handling, etc.

An additional object is to provide a system of the 20 above character which is adapted to automatically determine the postal zone from the zip code of the parcel destination address.

Another object is to provide apparatus for mechanically positioning the postage digit selectors of a postage 25 meter in accordance with the postage determined by the system.

A further object is to provide a system of the above character which is reliable, accurate, and readily operated by relatively unskilled personnel.

Other objects of the invention will in part be obvious 30 and in part appear hereinafter.

## SUMMARY OF THE INVENTION

In accordance with the present invention, there is 35 provided a system for weighing a parcel to be mailed or shipped and automatically determining the postage or shipping charges therefor. Having done this, the system automatically controls a printing device, such as a postage meter, to issue a stamp imprinted with the appropriate postage or shipping charge to be applied to the parcel. The consecutively executed functions of weighing, postage determination, and stamp issuance are performed rapidly, accurately and reliably without 45 operator intervention except to identify the parcel destination and for special circumstances.

More specifically, the present invention provides a scale for weighing successive parcels. The weight of each parcel is translated into encoded weight data, 50 which is stored in a register. The operator enters the geographical zone to which the parcel is destined, i.e., the mailing or shipping distance. This zone entry and the stored weight data are used to enter a postage memory which stores the postage or shipping charges 55 for the various combinations of parcel weight and mailing distance (zone). The appropriate postage is read from the postage memory and stored in a register where it is used to condition a postage meter or the equivalent to print out the appropriate postage, typically on a stamp to be adhered to the parcel.

In many instances, the operator is not given the parcel destination zone but rather the postal zip code of the parcel destination address. As an important feature of the invention, the system includes a zip-to-zone 65 memory which is adapted to convert a zip code entry by the operator to the appropriate zone for entry into the postage memory.

The system of the present invention is also adapted to compute the proper postage or shipping charge applicable to oversize parcels. When the operator determines that a parcel is oversized, he initiates an oversize designation input which automatically conditions the system to determine if the oversize parcel weight is less or greater than an established minimum weight and determine the postage accordingly.

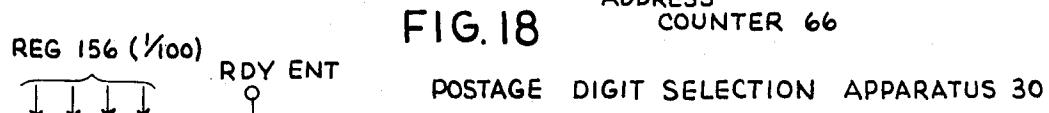

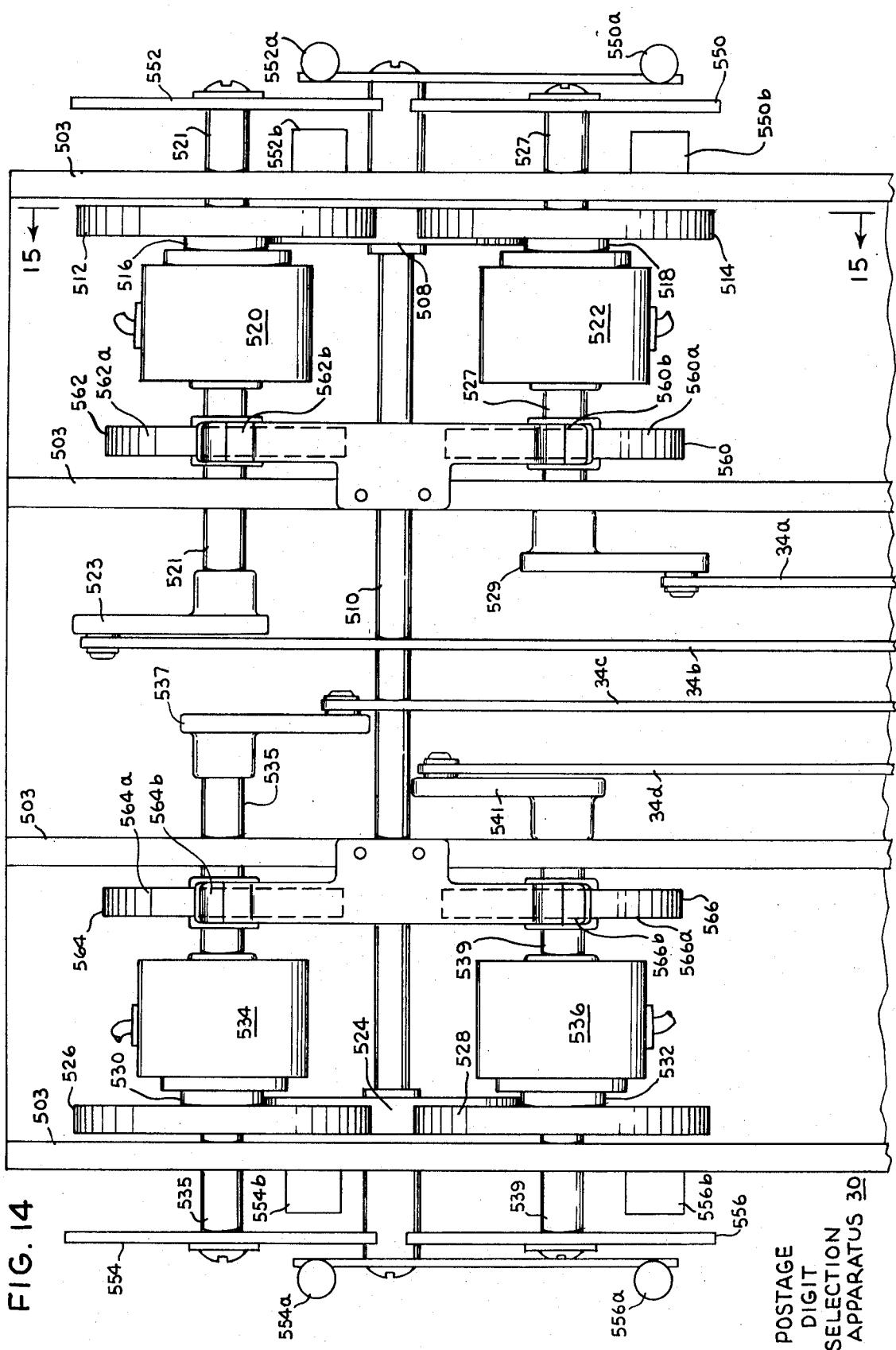

The system includes apparatus for interfacing the postage register, which is the system output register, with a conventional postage meter. Separate position encoders translate the digit positions of the various postage digit selector arms of the postage meter into coded digits which are compared with the corresponding postage digits stored in the postage register, as read from the postage memory. The postage digit selector arms are separately driven through their various digit positions, and as each assumes the digit positions corresponding to the associated digits in the postage register, they are decoupled from their respective drives. When all have been positioned to set up a digit by digit comparison with the postage held in the postage register, the postage meter is triggered to issue a postage imprinted stamp.

The invention accordingly comprises the features of construction, combinations of elements, and arrangement of parts which will be exemplified in the constructions hereinafter set forth, and the scope of the invention will be indicated in the claims.

#### DESCRIPTION OF THE DRAWINGS

For a fuller understanding of the nature and objects of the invention, reference should be had to the following detailed description taken in connection with the accompanying drawings, in which:

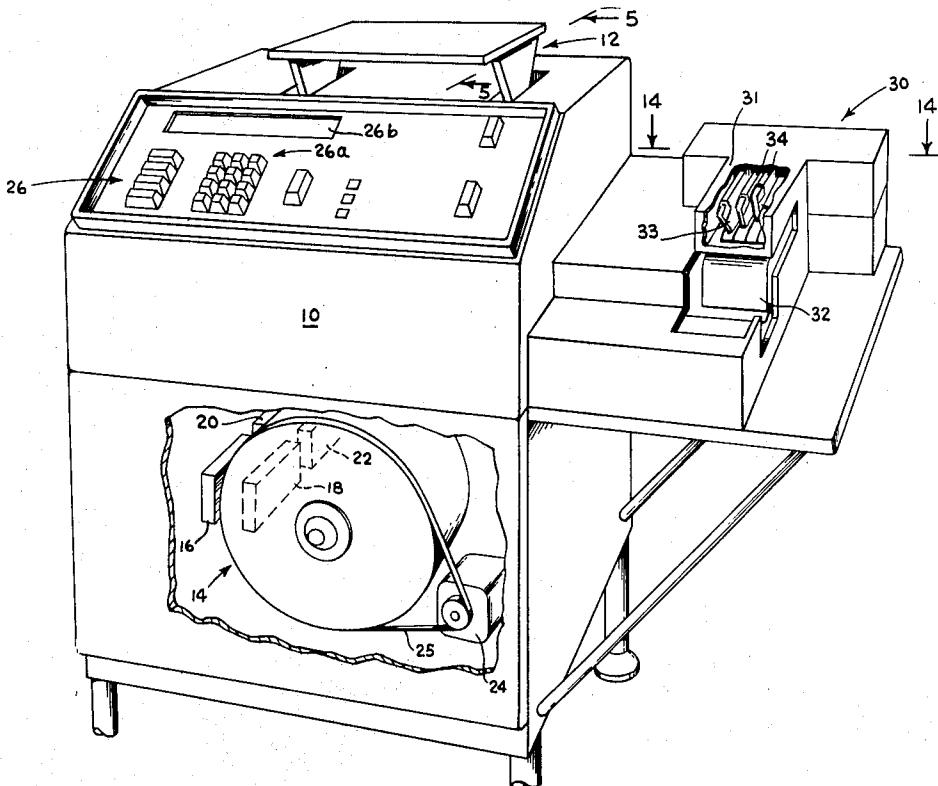

FIG. 1 is a perspective view of a parcel postage metering system constructed in accordance with the invention;

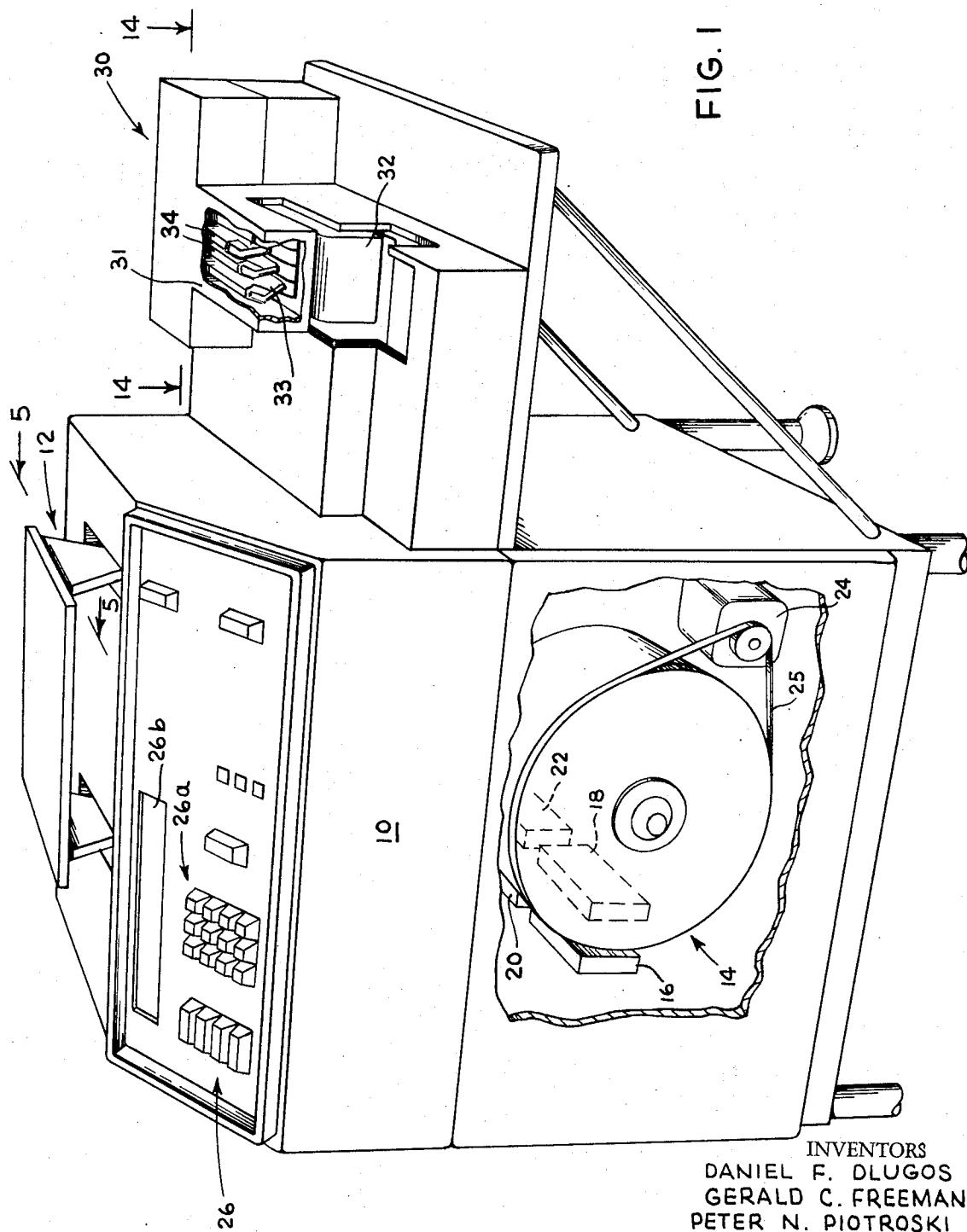

FIG. 2 is an overall functional block diagram of the parcel postage metering system of FIG. 1;

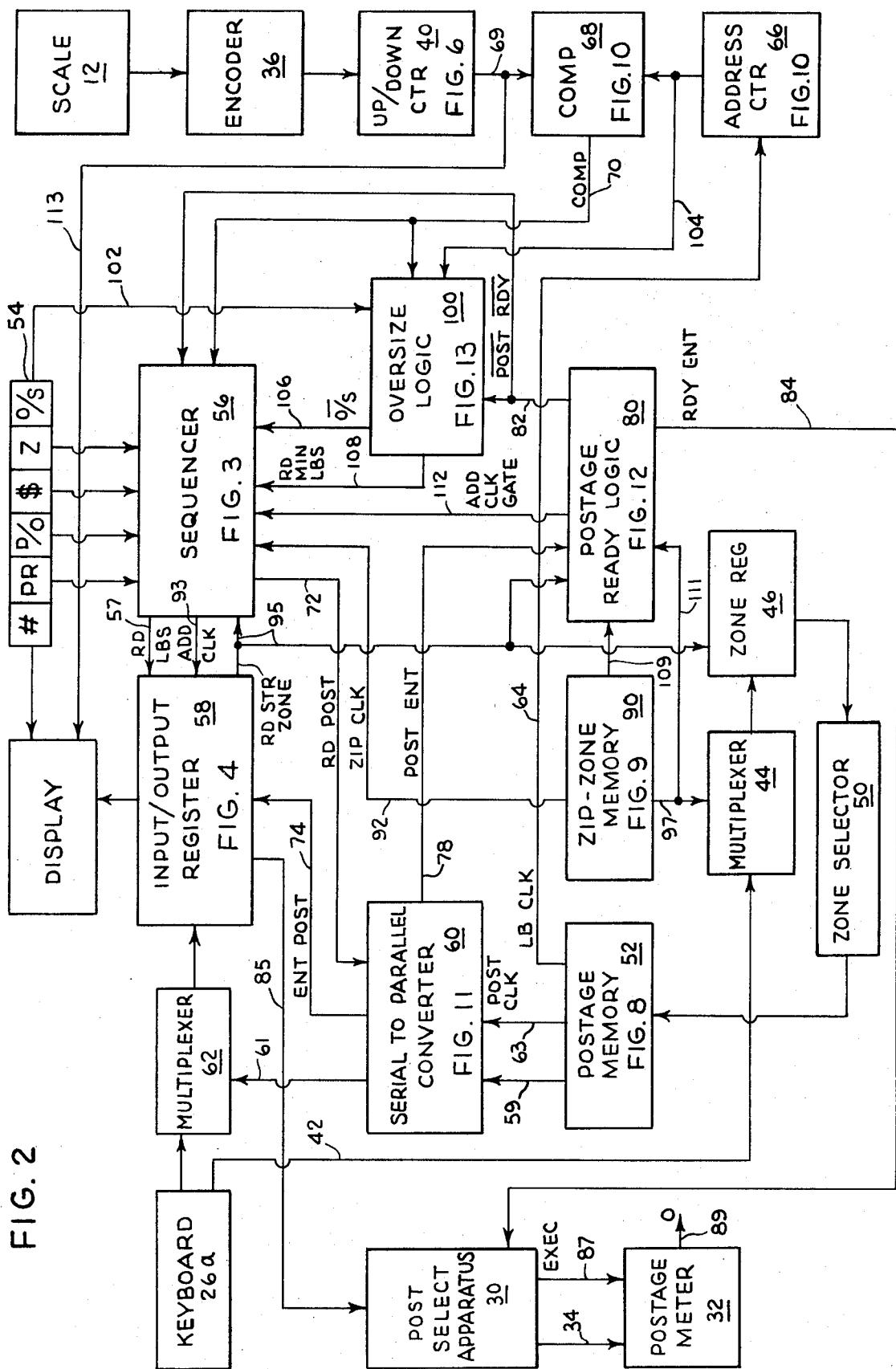

FIG. 3 is a detailed logic block diagram of the sequencer of FIG. 2;

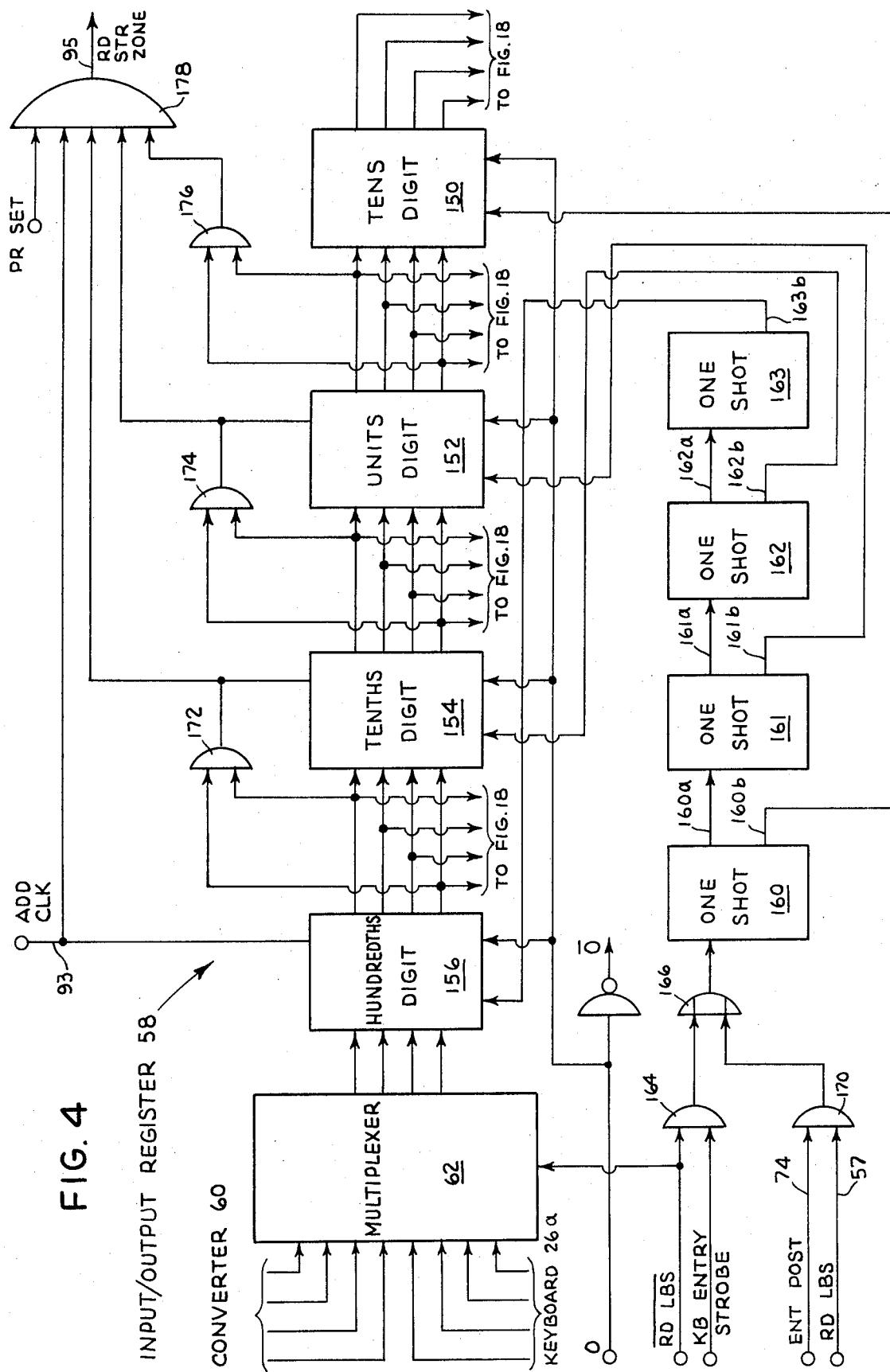

FIG. 4 is a detailed logic block diagram of the input/output register of FIG. 2;

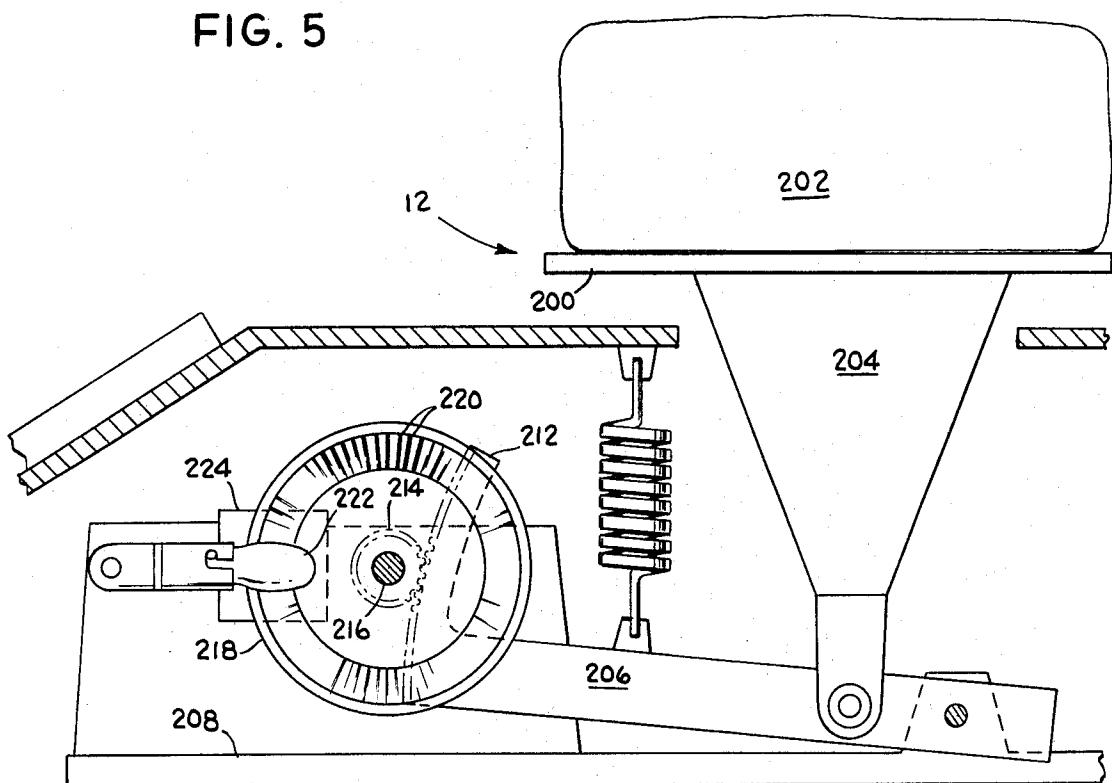

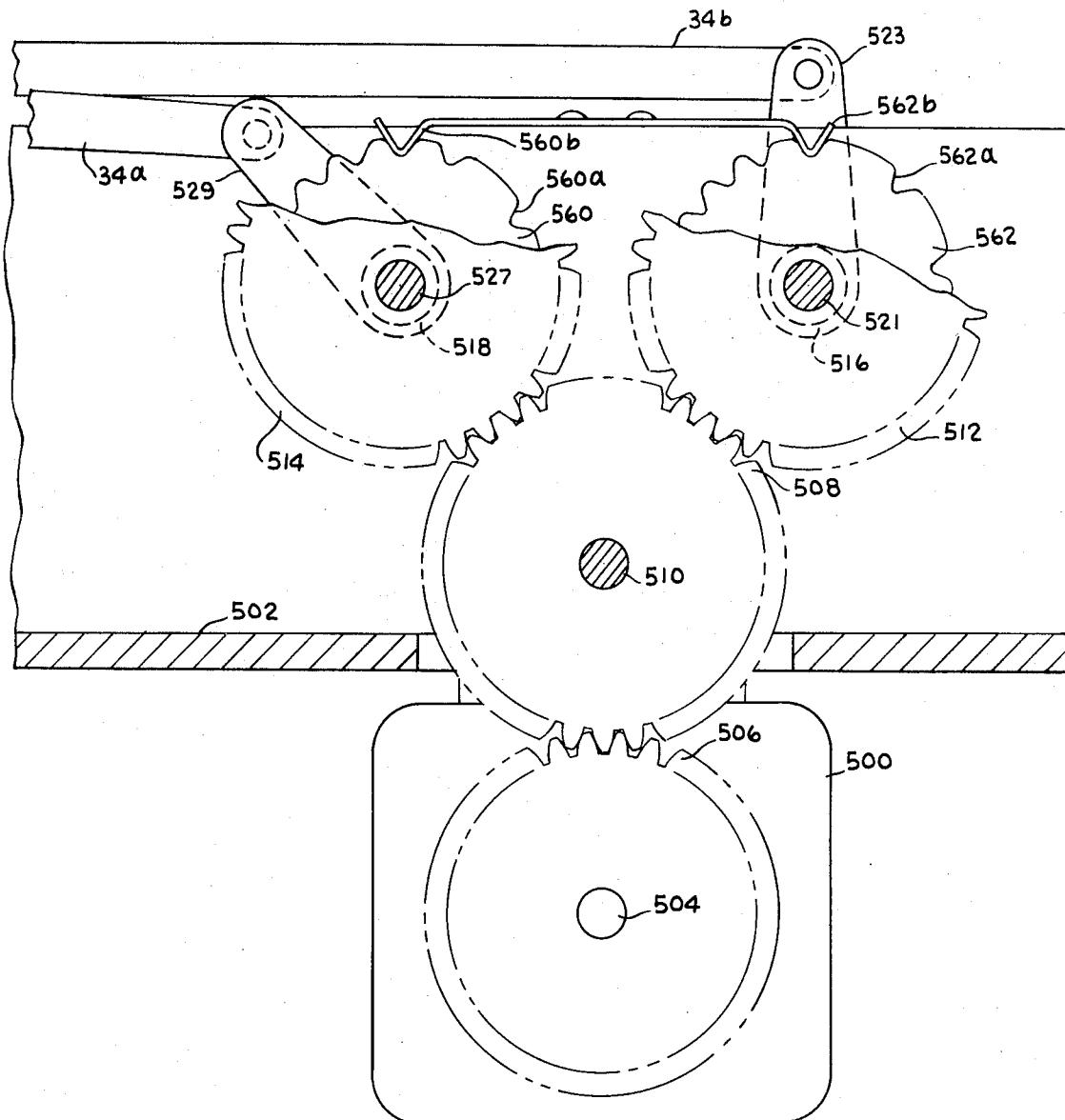

FIG. 5 is a sectional view taken along line 5—5 of FIG. 1 to show the scale and encoder of FIG. 2;

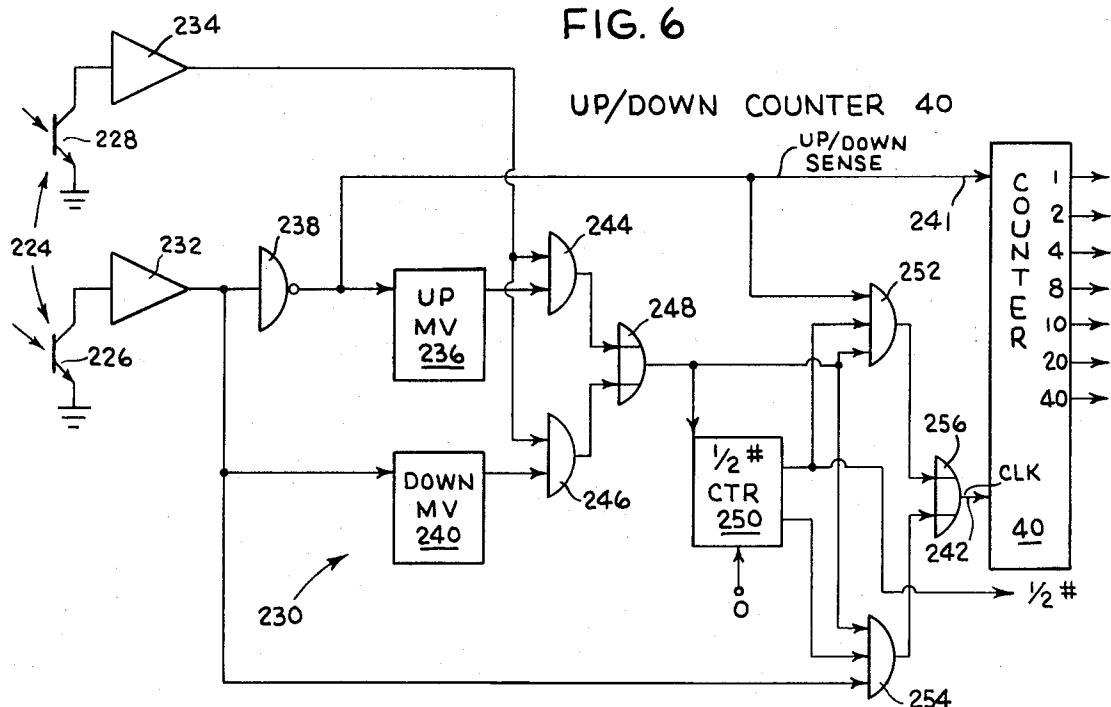

FIG. 6 is a detailed logic block diagram of the up/down counter of FIG. 2;

FIG. 7 is a timing diagram illustrating the operation of the up/down counter of FIG. 6;

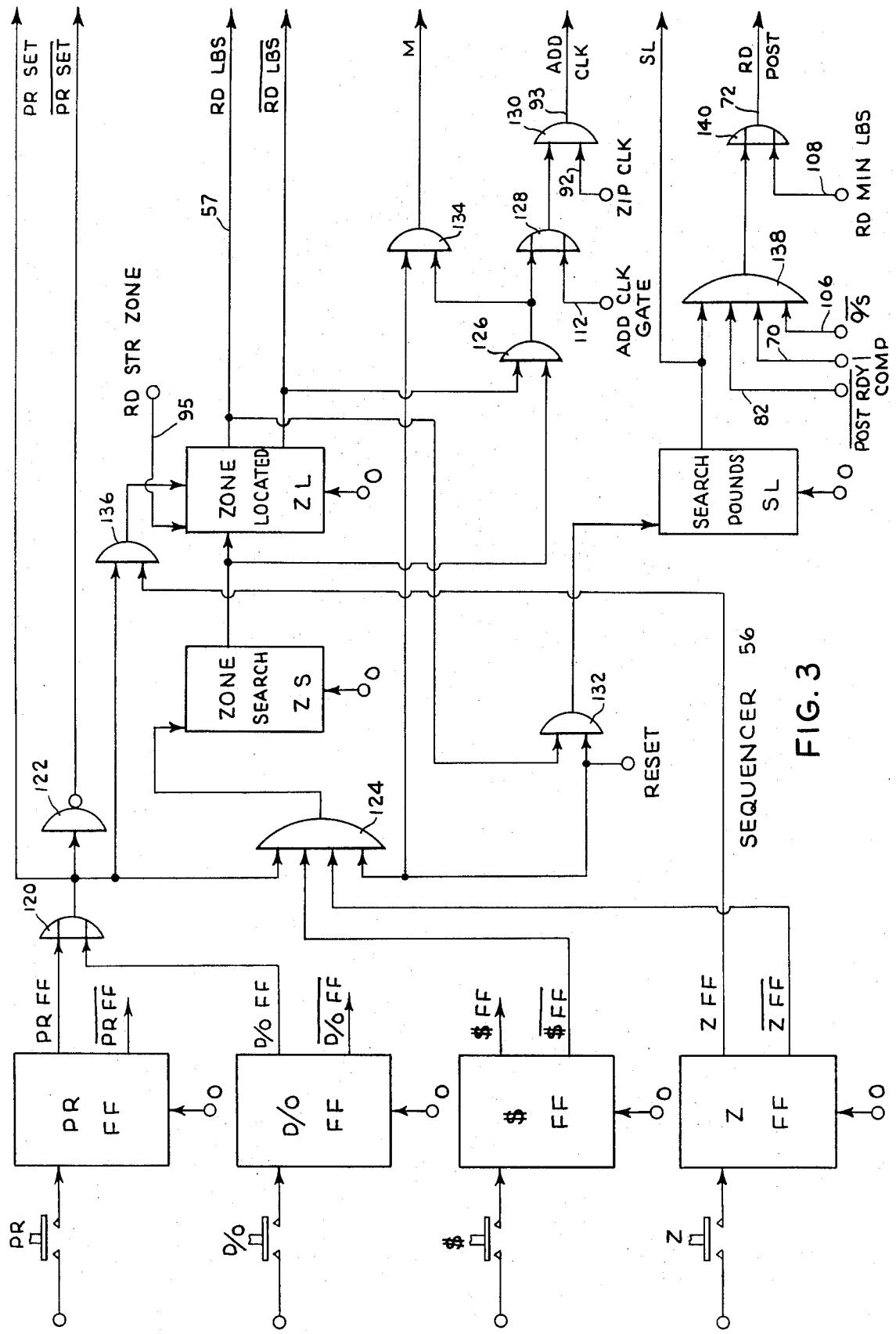

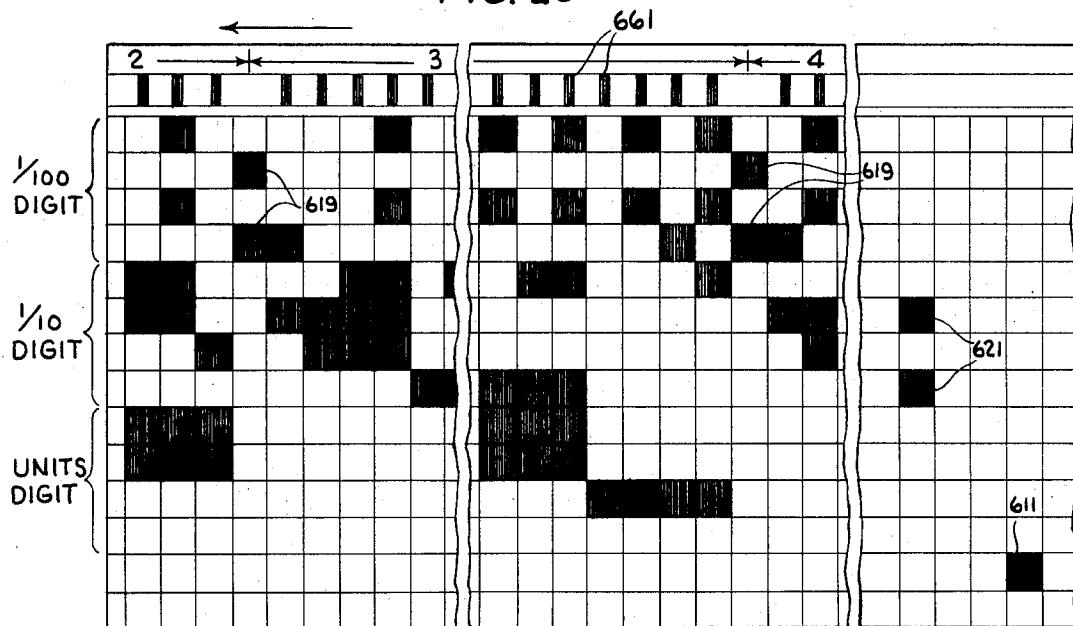

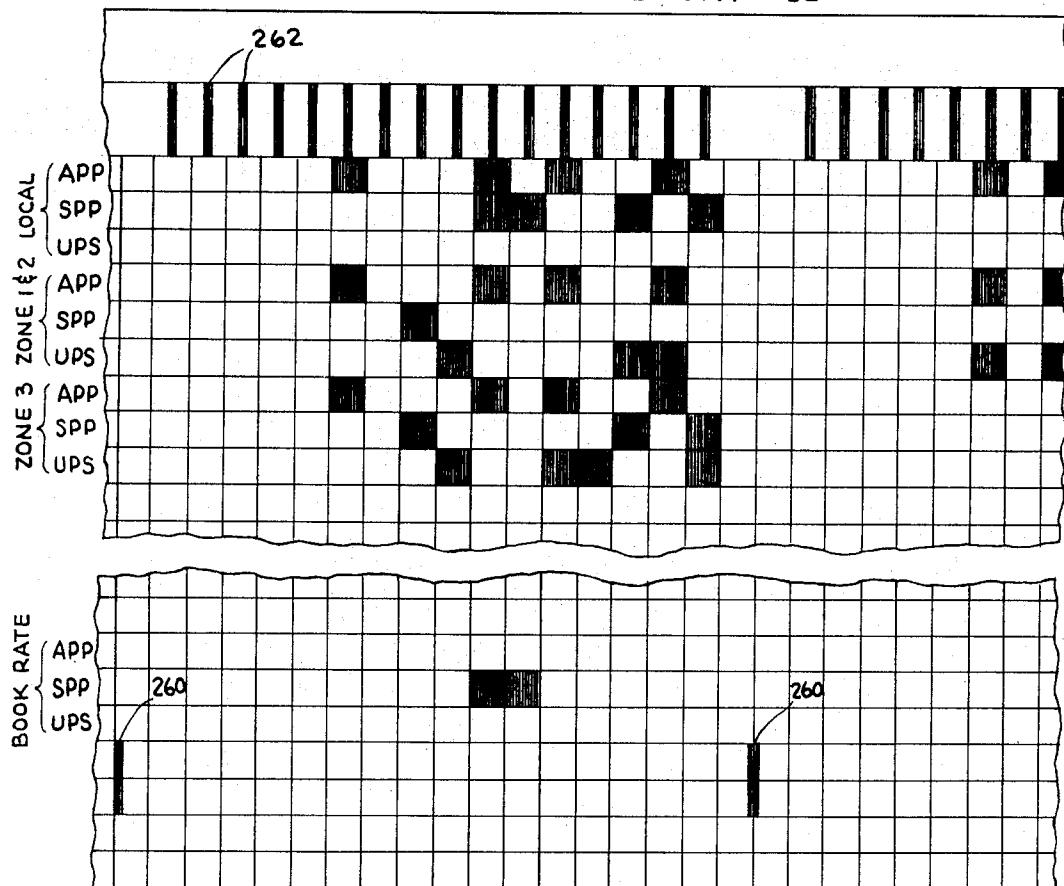

FIG. 8 is a plan view of a portion of a pounds to postage conversion table as stored in the postage memory of FIG. 2;

FIG. 9 is a plan view of a portion of a zip code to postal zone conversion table as stored in the zip-zone memory of FIG. 2;

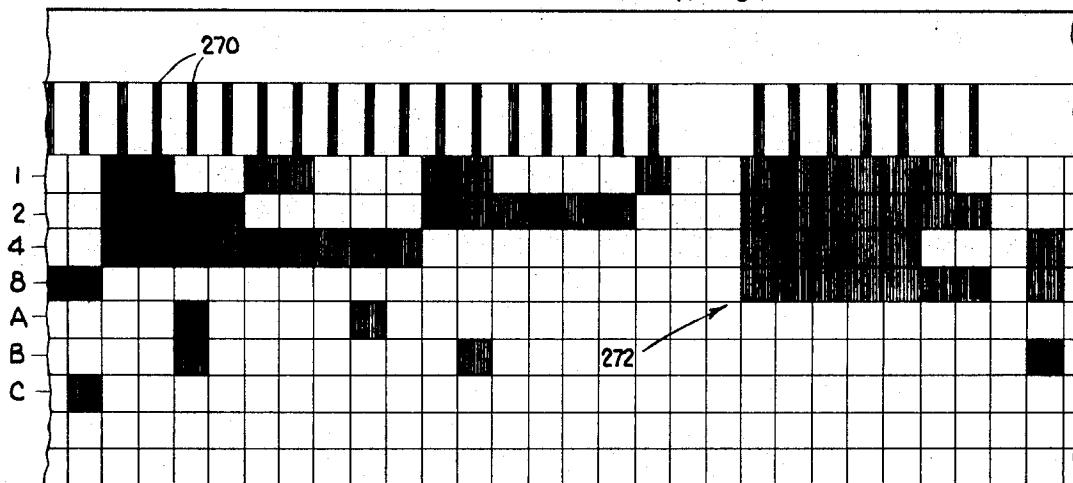

FIG. 10 is a logic block diagram of the address counter and comparator of FIG. 2;

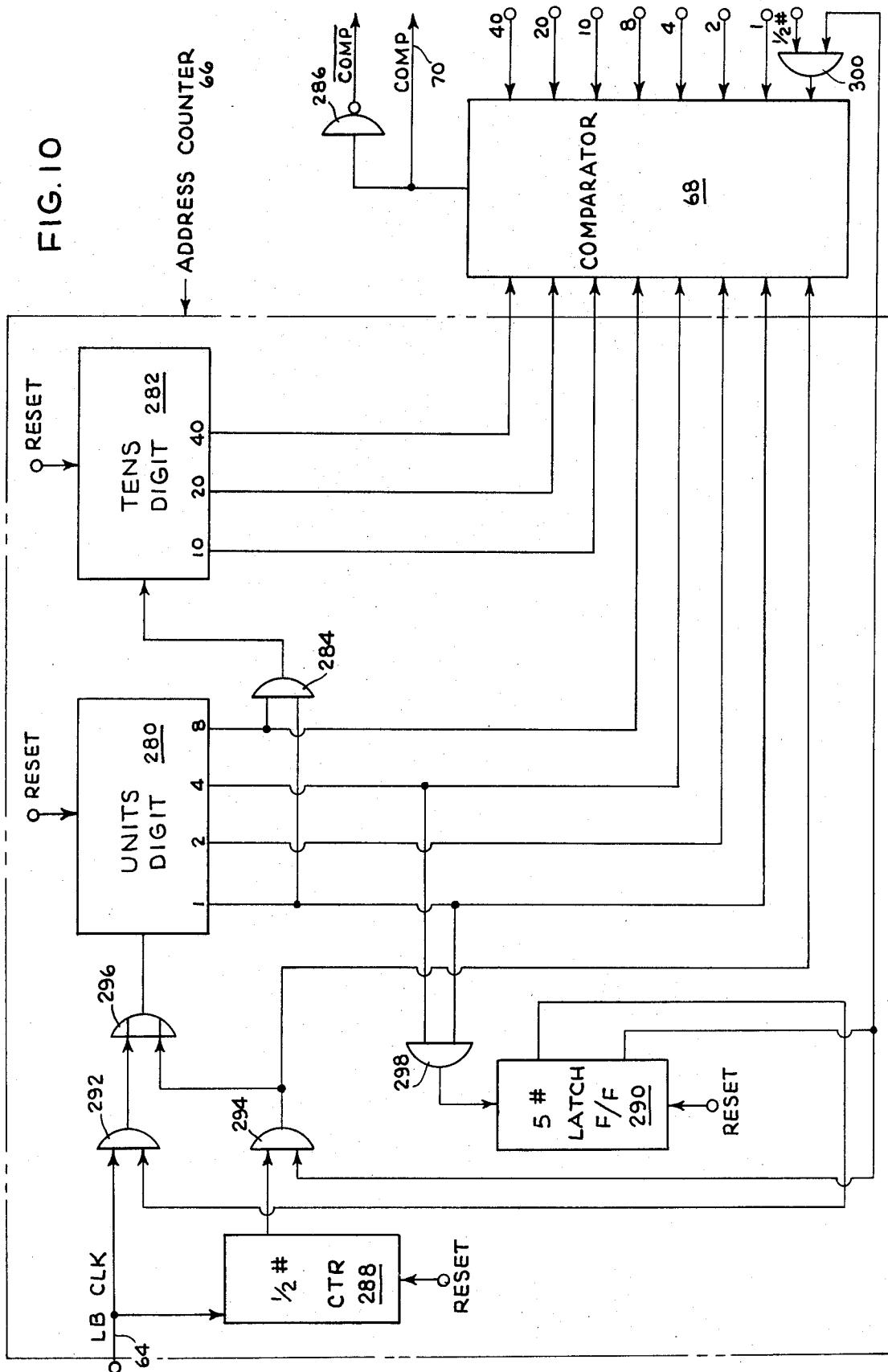

FIG. 11 is a detailed block diagram of the serial to parallel converter of FIG. 2;

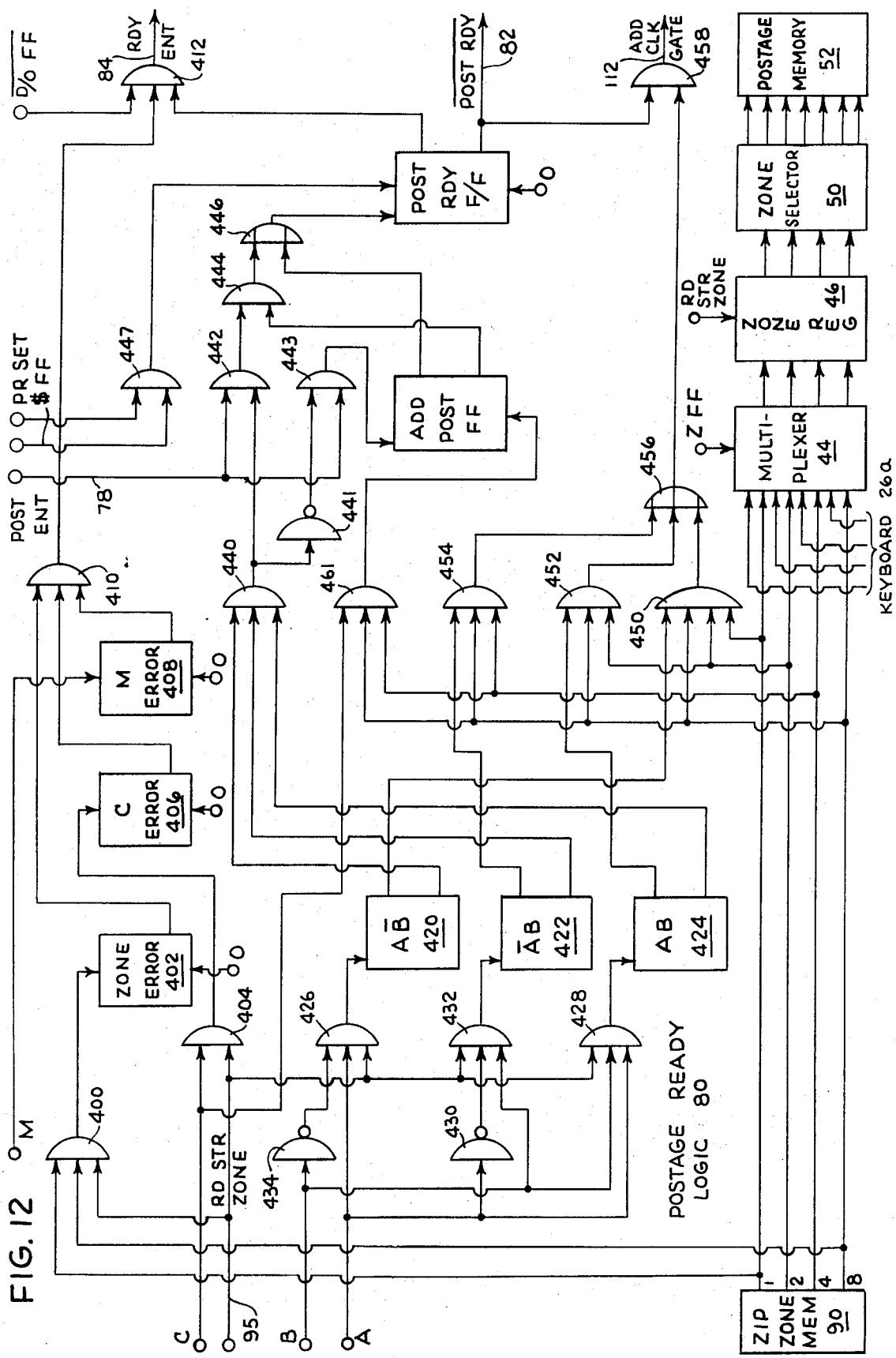

FIG. 12 is a detailed logic block diagram of the postage ready logic of FIG. 2;

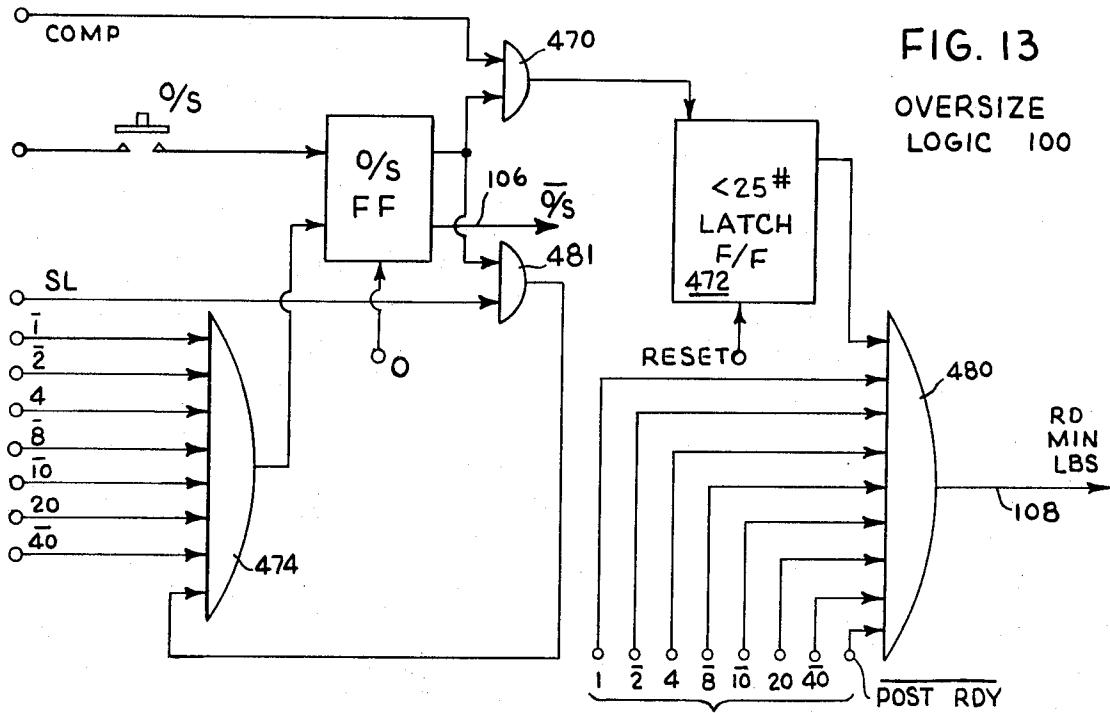

FIG. 13 is a detailed logic block diagram of the oversize logic of FIG. 2;

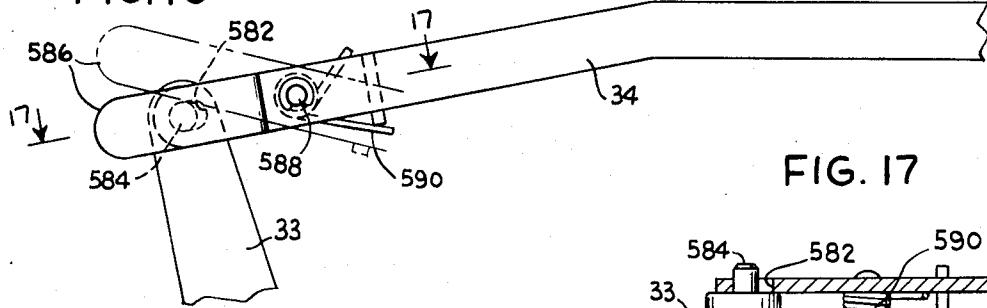

FIG. 14 is a sectional view taken along line 14—14 of FIG. 1;

FIG. 15 is a sectional view taken along line 15—15 of FIG. 14;

FIG. 16 is a side elevational view of one end portion of one of the links interconnecting the postage digit selection apparatus of FIG. 14 and the postage meter of FIG. 1;

FIG. 17 is a sectional view taken along line 17—17 of FIG. 16;

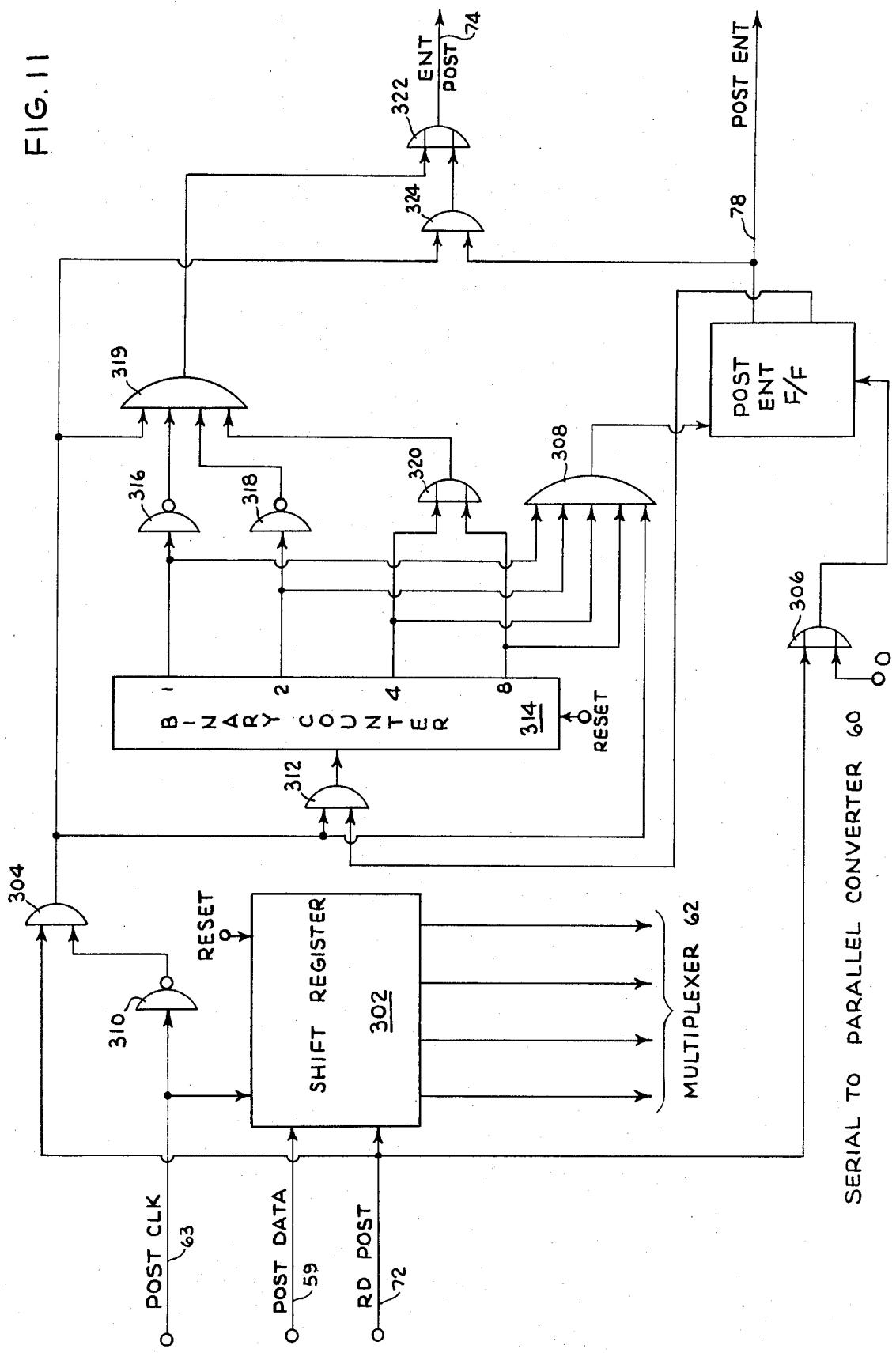

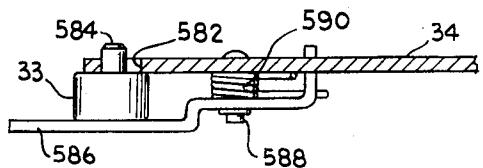

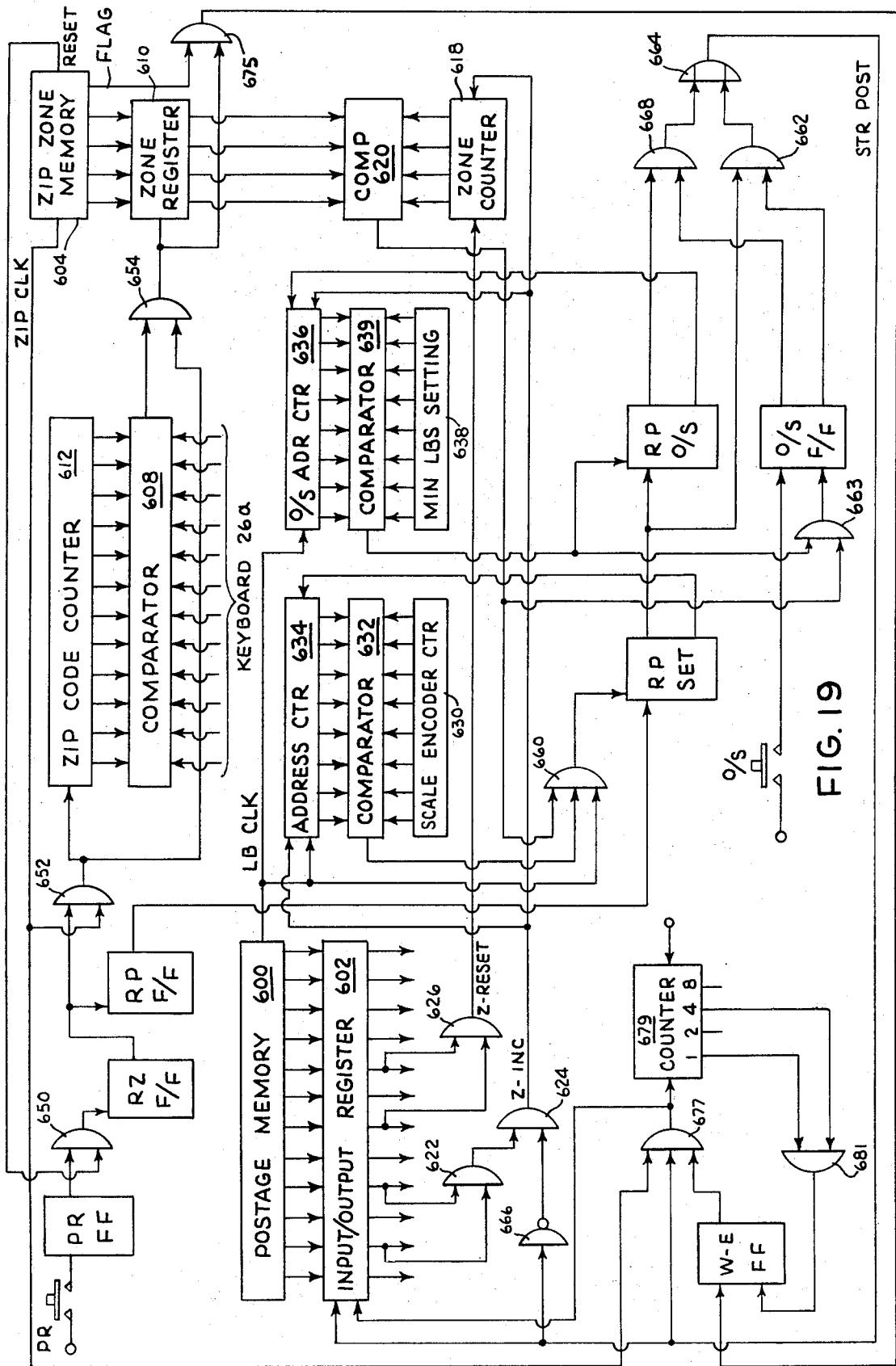

FIG. 18 is a detailed logic block diagram of the postage data handling portion of the postage digit selection apparatus;

FIG. 19 is an overall functional block diagram of an alternative embodiment of the console portion of the postage metering system of FIG. 1; and

FIG. 20 is a plan view of a portion of a pounds to postage conversion table as stored in the postage memory of FIG. 19.

Like reference notations refer to corresponding parts throughout several views of the drawings.

#### DETAILED DESCRIPTION

Referring now to the drawings, and first to FIG. 1, the parcel postage system of the present invention includes a console, generally indicated at 10, which contains, among other things, electronic circuitry for processing weight and postage data. Parcel weight data is obtained from a scale, generally indicated at 12, incorporated in console 10, while postage data is primarily obtained from a memory drum, generally indicated at 14 and also accommodated within the console. As will be seen, memory drum 14 has two separate memory banks; one storing a postage rate schedule and the other storing a zip code to postal zone conversion table. The data stored on memory drum 14 is optically encoded as opaque and transparent binary bits which are sensed by optical readout stations. As seen in FIG. 1, a light emitter 16 shines light through the postage rate memory bank peripheral portion of the memory drum 14 to a receiver 18, consisting of an array of suitable photosensors such as phototransistors. Similarly, the zip to zone memory bank peripheral portion of the memory drum is read out using a light emitter 20 and a receiver 22. Memory drum 14 is rotated by a motor 24 and an interconnecting belt drive 25.

It will readily occur to those in the art that other forms of data memories may be employed in the system of the present invention. For example, the postage and zone data may be optically encoded on one or more transparent discs. Moreover, suitable data memories may be provided in the form of magnetically encoded discs and drums, or even magnetic core matrices, although it is preferred to use a cyclical memory wherein the data is revolved past readout stations, thus simplifying accessing from a component standpoint.

The console 10 also includes a control panel, generally indicated at 26 in FIG. 1, which contains a plurality of mode keys selectively depressed by an operator to initiate various system operating modes to be described. The control panel also includes numerical entry keys accommodating the manual input of data pursuant to the invention. Space is also provided in the control panel 26 to accommodate a display panel 26b where data is displayed; such data being system derived postage and weight data, as well as data entered from the control panel 26.

The console 10 is electrically linked to electromechanical postage selection apparatus, generally indicated at 30. The selection apparatus, as will be seen, is mechanically linked to a postage meter 32 of known construction, such as a Pitney-Bowes 5300 Series Postage Meter. Parcel postage data derived at the console on the basis of the parcel weight is fed to the selection apparatus 30, which operates to mechanically position the various postage digit selector arms, jointly indicated at 33 in FIG. 1, by way of interconnecting links, jointly indicated at 34, so as to set up the postage meter 32 for the proper postage. The postage meter is then signaled to issue a stamp printed with the value of the postage received from console 10.

At this point, it should be pointed out that the system of the present invention is applicable to United States Post Office parcel post service and United Parcel Service (UPS). As is well known, a parcel can be sent either by parcel post (PP) or UPS. Thus, when reference is made to determining the applicable postage, this is intended to mean either the postage charged by the Post Office or the shipping charges applicable to the parcel if sent by UPS. Each service has its own rate schedule determined on the basis of the parcel weight, and, generally speaking, the distance the parcel is to be sent, and, in fact, the present invention contemplates storing both rate schedules on memory drum 14.

In practice, parcels would be separated into groups depending upon whether they are to be sent by PP or UPS. One group of parcels, for example, those to be sent by Parcel Post would be successively weighed on a scale 12 to obtain the parcel postage stamps from postage meter 32; the postage values being automatically deducted from a prepaid postage amount entered by postal officials. The parcel postage meter 32 would then be removed; the cover 31 being opened and the links 34 readily disconnected from the postage digit selector arms 33. A UPS meter is substituted, and the console 10 is conditioned to determine the shipping charges for the parcels to be sent by UPS.

Alternatively, separate selection apparatus 30 and mechanically interlinked meters 32 can be provided for each service. They would be separately electrically linked to the console and would be individually selected from the control panel 26 by the operator according to which service is to be employed, either PP or UPS, for each parcel being weighed on scale 12.

#### Overall System Block Diagram

The basic operation of the system of FIG. 1 will be more readily understood from the system block diagram seen in FIG. 2. With the exception the postage meter 32 and the electromechanical selection apparatus 30, all of the components seen in FIG. 8 are functionally and physically located within console 10. When a parcel is placed on scale 12, its mechanical response is coupled to a scale encoder 36 adapted to convert the parcel weight into a proportional number of pulses which are accumulated in a counter 40. As will be seen, counter 40 is an up/down pulse counter, enabling it to accurately follow the scale response as it oscillates about and ultimately settles down to a final weight reading.

The operator, upon reading the parcel address destination, determines the appropriate postal zone on the basis of the distance between his geographical loca-

tion and the parcel destination. The operator enters the postal zone by depression of the appropriate key of a numerical entry keyboard 26a included in control panel 26 (FIG. 1). This zone entry is supplied by connection 42 and a multiplexer or switch 44 to a zone register 46. Prior to the entry of a zone from numerical entry keyboard 26a, the operator presses a mode key Z included in a mode key group 54, which has as one of its functions the conditioning of multiplexer 44 to route the keyboard zone entry through to zone register 46. The zone digit entry held in zone register 46 conditions a zone selector 50 to effect appropriate zone entry into the postage memory 52 which, as previously noted, comprises one of the memory banks carried by memory drum 14 (FIG. 1). In physical terms, zone entry into the postage memory 52 is effective by selecting one of a plurality of phototransistors, or the equivalent, included in the receiver array 18 generally illustrated in FIG. 1. As will be subsequently described, the postage memory 52 includes a series of side by side zone channels in which postage data is serially recorded by parcel weight. Thus, the zone selector 50 effects selection of the appropriate phototransistor of the receiver array 18 which is aligned with the channel of the postage memory 52 assigned to the particular zone entered into the zone register 46 from the keyboard 26a.

The next operator function, and in most situations the only remaining operator function required for each parcel, is to depress a postage request key PR included in mode key group 54 in control panel 26. This generates an input over lead 55 to a sequencer 56 which operates to organize the system operating functions pursuant to determining the applicable parcel postage.

Since the appropriate zone has already been entered into zone register 46, thereby accessing postage memory 52 for all postage data, regardless of parcel weight, for that particular zone, the sequencer 56 generates a signal RD LBS over lead 57 to an input/output register 58. This signal conditions register 58 for acceptance of the appropriate postage data read from the postage memory 52 over connection 59 to a serial to parallel converter 60 and thence over connection 61 and multiplexer 62 to the input/output register. As will be described, the postage data is stored and read out from postage memory in serial binary coded decimal, while the input/output register 58 is designed to accept the postage data in serial digit, parallel bit fashion.

Thus, the serial to parallel converter 60 is necessary to accept the digit bits serially from postage memory 52 and successively pass the bits of each postage digit in parallel to the input/output register 58. The memory 52 also includes a postage clock bit channel which is read out to provide postage clock pulses POST CLK over lead 63 to converter 60 for synchronizing the serial to parallel conversion.

Having accessed the postage memory 52 for the appropriate zone, it now remains to further access the postage memory for the appropriate parcel weight, held in up/down counter 40, in order to obtain the applicable postage for entry into input/output register 58. To this end, the postage memory is provided with a pound clock pulse channel in which are recorded a series of pound clock bits located in predetermined relation to the stored postage data. These pound clock pul-

ses LB CLK, read out during each revolution of the drum memory 14 (FIG. 1), are applied over lead 64 to an address counter 66. The pound clock pulse count accumulating in address counter 66 is continuously compared in a comparator 68 with the parcel weight stored in the up/down counter 40 supplied over connection 69. When a comparison is reached between the pulse counts in address counter 66 and up/down counter 40, comparator 68 generates a compare signal COMP over lead 70 to the sequencer 56. Due to the arrangement of the postage data in postage memory 52, the generation of compare signal COMP signals that the postage data applicable to the parcel weight registered in the up/down counter 40 is about to be read out to the serial to parallel converter 60. The sequencer circuit 56, in response to the compare signal COMP generates a read postage command signal RD POST over lead 72 to the serial to parallel converter 60. This signal conditions the converter 60 to perform the serial to parallel bit conversion on a digit by digit basis for the next four postage digits read from the postage memory 52. The four bits of each postage digit are assembled and then transferred in parallel, digit by digit, to the input/output register 58. Each postage digit is shifted into the input/output register in response to an enter postage signal ENT POST generated over lead 74.

When the last of the four postage digits, in the illustrated embodiment of the invention, has been assembled in parallel bit fashion and shifted into the input/output register 58, the serial to parallel converter 60 generates a postage entered signal POST ENT over line 78 to a postage ready logic circuit 80. Prior to receipt of this signal the postage ready logic circuit 80 provides a postage not ready signal POST RDY over lead 82 to the sequencer 56 effective to enable the various sequence control functions of the sequencer. When the postage not ready signal POST RDY goes false in response to receipt of the postage entered signal POST ENT, signifying that the postage has been fully entered into the input/output register 58, the sequencer 56 is effectively disabled.

Assuming that no additional postage over and above the postage value held in the input/output register is applicable to the particular parcel on scale 12, the postage ready circuit 80 generates a ready enter signal RDY ENT which is supplied over lead 84 to the electromechanical postage selection apparatus 30. This apparatus then looks at the postage digits registered in the input/output register 58 communicated over connection 85 and operates to mechanically position the postage digit selector arms 33 of postage meter 32 accordingly via the interconnecting links, diagrammatically indicated at 34 in FIG. 2. After all the postage levers have been approximately positioned by the selection apparatus 30, an execute signal EXEC issues over lead 87, signaling the postage meter to execute a print cycle and issue an appropriately imprinted postage stamp which may then be applied to the parcel. After the postage meter 32 has issued the stamp, it issues a cycle complete signal 0 which is fed back over lead 89 to the console for the purpose of resetting the console components preparatory for the next parcel.

In some of the cases, it is contemplated that the operator will not be supplied with the postal zone or the parcel destination, but will be able to readily obtain the

zip code of the parcel destination typically recorded on the parcel address. In these cases, the operator enters the first three digits of the zip code into the input/output register 58 via numerical keyboard 26a and multiplexer 62. It is only when key Z is depressed preparatory to a direct zone entry, that the keyboard is connected by multiplexer 44 to the zone register 46.

With the entry of a zip code into the input/output register and the depression of the postage request key 10 PR, the sequencer 56 initiates a zone search through a zip to zone memory 90, included as the other memory bank carried by memory drum 14 (FIG. 1). As will be seen, the zip-zone memory 90 includes a zip clock bit 15 channel, with each zip clock bit storage position aligned with a binary coded decimal zone storage position. As will become apparent, the zip-zone memory is specially encoded on the basis of the geographical location of each particular system installation, since the applicable postal zone in each case is determined by the distance to the parcel destination. These zip clock bits are read as zip clock pulses ZIP CLK from the zip-zone 20 memory 90 during each memory drum revolution and are fed over lead 92 to sequencer 56 during a zone 25 search. These zip clock pulses are gated through as add clock pulses ADD CLK over lead 93 to the input/output register 58.

As will be seen, the input/output register is adapted 30 not only as a binary coded decimal (BCD) digit shift register, but also as a BCD counter. Thus, each zip clock pulse ZIP CLK gated through as an add clock pulse ADD CLK to the input/output register increments the zip code number registered therein by one. The input/output register is incremented until it overflows, 35 i.e., goes from 999 to 000. When overflow occurs, the input/output register 58 generates a read store zone signal RD STR ZONE on output lead 95 to zone register 46. The zone register responds by accepting and holding the zone number coincidentally read from the zip-zone memory 90 and supplied over connection 97 and multiplexer 44.

From this general description, it is seen that by serially arranging the zone data in the zip-zone memory 90 in accordance with the distance between the various zip code designated geographical locations and the system installation location, where the zone data is located in the memory by counting up to the complement of the zip code held in the input/output register, 45 the appropriate zone can be entered into the zone register 46 from the zip-zone memory 90, thereby effecting a zip to zone conversion.

The read store zone signal RD STR ZONE on output lead 95 is also supplied to the sequencer 56 to indicate 50 that the appropriate zone has been located and entered into the zone register 46 and that a search of the postage memory 52 for the applicable postage may now be performed in the manner previously generally described.

Occasionally, the system of the present invention 55 may be called upon to determine the postage applicable to an oversize package. Under both the PP and UPS rate schedules, the postage applicable to an oversized package is determined as follows. If the oversize package is less than an established minimum weight, 25 pounds for UPS and 10 pounds for PP, the applicable postage is determined on the basis of the established

minimum weight. However, if the oversize parcel weights more than the established minimum weight, the applicable postage is determined by its actual weight.

Still referring to FIG. 2, when the operator determines that a parcel placed on scale 12 is oversized, an oversize key O/S is depressed, conditioning an oversize logic circuit 100 over lead 102. During the searching of the postage memory 52 for the applicable postage, the accumulating count of the pound clock pulses LB CLK read from the postage memory 52 into the address counter 66 is applied over connection 104 to the oversize logic circuit 100, as well as the comparator 68. The oversize logic circuit also receives the compare output COMP from comparator 68. As will be seen, the count content of the address counter 66 is continuously decoded to detect when it is incremented to the established minimum pound value. Until this minimum pound value is reached in the search of the postage memory 52, the oversize logic circuit 100 supplies a signal O/S over lead 106 to the sequencer 56, in effect telling the sequencer to disregard the compare signal COMP issuing from the comparator 68 over lead 70, which would occur if the oversized package weighs less than the established minimum. In this case, when the address counter increments to the established minimum weight value, the oversize logic circuit 100 supplies a read minimum pounds signal RD MIN LBS over lead 108 to the sequencer 56, which responds by issuing the read postage signal RD POST over lead 72 to the serial to parallel converter 60. The postage applicable to the established minimum weight is thus entered into the input/output register.

On the other hand, if the established minimum weight value is achieved in the address counter 66 before a compare signal COMP issues from comparator 68, the oversize logic circuit 100 is converted to its inoperative state as though it had not been conditioned in the first instance by oversize key O/S. The disabling effect of the signal O/S is removed, and the sequencer awaits the receipt of the compare signal COMP from comparator 68 pursuant to retrieval from the postage memory 52 of the postage value based on the actual weight of the oversized parcel.

In certain situations dealing with the UPS system, a nominal additional postage charge is required in shipping parcels between certain locations. These special situations can be conveniently handled in accordance with the present invention by providing recorded flag bits in the zip-zone memory 90 which are read out as flag pulses into the postage ready logic 80 over lead 109 under the control of the read store zone signal RD STR ZONE at the same time that the zone is read into the zone register 46. After the postage applicable to the parcel weight has been located in the postage memory 52 and entered into the input/output register 58, the postage ready logic 80 determines whether it received on or more flag pulses over lead 109 from the zip-zone memory 90 at the time the proper zone was located and entered into the zone register 46. If flag pulses had been received, the postage ready logic circuit 80 is conditioned to accept over connection 111 from the zip-zone memory 90 uniquely coded bits in effect designating the amount of additional postage to be added to the postage already registered in the input/output register 58. The postage

ready logic circuit 80 generates an add clock gate pulse ADD CLK GATE over lead 112 to the sequencer 56 effective to gate through to the input/output register a predetermined number of zip clock pulses ZIP CLK as add clock pulses ADD CLK to the input/output register 58. The input/output register is thus incremented accordingly so as to register the original postage plus the additional postage.

10 The various entries into the input/output register 58, such as zip code numbers and postage are displayed at the display panel 26b. In addition, a key # in group 54 may be depressed to condition the display panel to display the parcel weight in the up/down counter 40 communicated over connection 113.

15 Sequencer

The sequencer 56 of FIG. 2, as seen in detail in FIG. 3, operates to initiate various system operating modes and insures that the various operating steps involved in each mode are performed in the appropriate sequence. Specifically, the sequencer 56 is conditioned by various mode keys of the group 54 to initiate a particular operating mode. As seen in FIG. 3, the postage request key PR, postage display/only key D/O, additional 20 postage key \$ and the zone entry key Z, upon depression, provide separate inputs directly to the sequencer 56. The oversize key O/S of the group 54, as seen in FIG. 2, applies its input to the oversize logic 100 which, in turn, provides signal O/S to the sequencer. The mode 25 of function keys PR, D/O, \$ and Z, upon depression are effective to set respective flip-flops PREF, D/OFF, \$FF and ZFF. These flip-flops serve as latches for their respective keys, and thus a key need only be momentarily depressed to register the fact that a particular operating mode has been called for. These flip-flops are set by depressions of their respective keys and are reset by the cycle complete signal O issued by the postage meter 32.

30 Depression of the postage request key PR initiates the system operation culminating in the issuance of a postage imprinted stamp by postage meter 32 applicable to the parcel placed on scale 12. Postage display only key D/O initiates essentially the same operation as the postage request key PR, except that the applicable postage is merely displayed at the display panel 115 (FIG. 2). Thus, the postage display only function is largely a test function performed to check the operating accuracy of the system. The additional postage key \$ is employed in the situation where additional postage, over the above the postage applicable to the parcel weight, is to be applied to a parcel. Thus, key \$ is depressed prior to the entry of numerical postage data from keyboard 26a into the input/output register 58 to cover the cost of, for example, insurance, special handling, etc. Upon depression of postage request key PR, the postage selection apparatus 30 is immediately actuated by the signal RDY ENT to set up the postage meter 32 to the addition postage value in register 58 and issue an additional postage imprinted stamp.

35 The zone entry key Z is depressed preparatory to the entry of the zone of the parcel destination directly from the keyboard 26a into the zone register 46 (FIG. 2). As will be seen, the system is normally conditioned to accept the parcel destination keyboard entry into the input/output register in the form of a zip code number. The system then proceeds to search the zip-zone

memory 90 for the postal zone corresponding to the zip code entry; the located postal zone then being entered into the zone register 46, as previously generally described. Thus, depression of the zone key Z in effect causes the system to skip the zone search operation, since the appropriate zone has already been entered into the zone register 46 directly from the keyboard 26a.

The set outputs of the postage request flip-flop PRFF and the postage display only flip-flop D/OFF are gated together in an OR gate 120 to provide a common output, identified as PR SET and, through inverter 122, the complement PR SET. As will be seen, these signals are used as controls elsewhere in the system. The output PR SET is applied as one input to an AND gate 124. The remaining inputs to this gate are the reset output \$FF of the additional postage flip-flop \$FF and the reset output ZFF of the zone entry flip-flop ZFF. The last remaining input to AND gate 124 is a reset pulse read from the zip-zone memory 90 at the beginning of each revolution of the memory drum 14 (FIG. 1). This reset pulse issues at the beginning of each revolution of the zip to zone conversion table stored in the memory 90 passed its readout station. Actually, this reset pulse is common to both the zip-zone memory and the postage memory 52, and, in the latter case, signals the start of each revolution of the pounds to postage conversion table stored in the postage memory passed its readout station.

Assuming either the postage request key PR or the postage display only key D/O is depressed and the additional postage key \$ and the zone entry key Z are not depressed, the output of AND gate 124 goes to a logical ONE upon the receipt of the next occurring reset pulse. Upon the termination of the reset pulse, the gate output goes to a logical ZERO, which is effective to trigger a zone search flip-flop ZS from its reset state to its set state. The set output of the flip-flop is connected to the set input of a zone located flip-flop ZL and also is in an AND gate 126 with the reset output RD LBS of a zone located flip-flop ZL. While the zone search flip-flop is set and until the zone located flip-flop is set, AND gate 126 provides a logical ONE output which is passed through an OR gate 128 to enable an AND gate 130. The other input to AND gate 130 consists of zip clock pulses ZIP CLK read from the zip-zone memory 90, which feed through this gate, while enabled, as add clock pulses ADD CLK on lead 93 to the input/output register 58. The input/output register, as will be seen, functions both as a binary coded decimal BCD shift register and a BCD counter. These add clock pulses serve to increment the zip code number entered in register 58 from keyboard 26a prior to depression of either the postage request key PR or the postage display only key D/O.

The arrangement of the zone data stored in the zip-zone memory 90 is such that when the number of zip clock pulses read from the stored zip-zone conversion table after the occurrence of a reset pulse equals the complement of the zip code number held in the input/output register 58, the zone applicable to the zip code number entered from keyboard 26a has arrived at the readout station. When the input/output counter has been incremented to the complement of the zip code number previously entered therein, it spills over or is

zeroed, and this event is decoded to provide the read store zone signal RD STR ZONE. This signal is returned to the sequencer 56 over lead 95 to trigger the zone located flip-flop ZL to its set state, signifying that the zone applicable to the zip code entered into input/output register 58 has been located in the zip-zone memory 90. AND gate 130 is disabled via AND gate 126, thereby terminating the application of add clock pulses ADD CLK to the input/output register.

If, upon the occurrence of the next reset pulse after the zone search flip-flop ZS have been set, the zone located flip-flop ZL has not been set by a read store zone signal, the output of AND gate 126 remains a logical ONE, enabling the passage of this next occurring reset pulse through AND gate 134 as an error signal M.

As will be seen, the postage ready logic 80 supplies an enabling input ADD CLK GATE through OR gate 128 to AND gate 130, thus enabling the application of a selected number of additional add clock pulses ADD CLK to the input/output register to increment a postage value previously entered therein from postage memory 52.

Assuming that the appropriate zone has been located in the zip-zone memory 90, AND gate 132 is enabled from the set output RD LBS of flip-flop ZL, and upon the next occurring reset pulse a search pounds flip-flop SL is triggered to its set condition. This has the controlling effect of initiating a search of the postage memory 52 (FIG. 2). As previously noted, each reset pulse read from the zip-zone memory 90 is also common to the postage memory 52, and thus signals the arrival of the start of the stored pounds to postage conversion table at its readout station. The logical ONE set output of the search pounds flip-flop, indicated as SL, enables an AND gate 138, whose other inputs are POST RDY from the postage ready logic 80, COMP from the comparator circuit 68, and O/S from the oversize logic 100. Assuming that the postage has not been located in the postage memory and entered into the input/output register (POST RDY a logical ONE) and the parcel is not oversized (O/S a logical ONE), AND gate 138 passes the compare signal COMP through to the output of an OR gate 140 and a read postage command signal RD POST, which is fed over lead 72 to the serial to parallel converter 60. This signal announces the arrival of the applicable postage in the pounds to postage conversion table at the readout station, and conditions the converter 60 to effect the requisite serial to parallel digit bit conversion and the transfer of the postage digits serially into the input/output register via the multiplexer 61 (FIG. 2).

As will be seen from the details of the oversize logic circuit 100 to be described, if the package is oversized and the operator signals this fact by depression of the oversize key O/S, AND gate 138 is disabled by the signal O/S, and the read postage command signal RD POST is derived from the read minimum pounds signal RD MIN LBS supplied from the oversize logic circuit over lead 108.

Still referring to FIG. 3, if the zone is to be entered into the zone register 46 directly from the keyboard 26a, key Z is depressed to set flip-flop ZFF. The appropriate zone number is then entered into the zone register. The set output of flip-flop ZFF enables an AND gate 136, and, upon depression of postage request key

PR (or key D/O), the zone located flip-flop is forced to its set state just as though the zone had been located from the zip-zone memory. The next reset pulse sets the search pounds flip-flop SL to enable a search of the postage memory 52.

As shown in FIG. 3, the various flip-flops in the sequencer 56 all receive the cycle complete signal O from the postage meter 32 as a forced reset input, insuring that they are all reset preparatory for the system operating cycle.

#### Input/Output Register

The input/output register 58, as seen in detail in FIG. 4, may be considered as comprising four digit registers, namely, a tens digit register 150, a units digit register 152, a tenths digit register 154 and a hundredths digit register 156. Each digit register consists of four bit stages, enabling it to store a decimal digit in binary coded decimal format. The input/output register 58 is loaded from the left via multiplexer 62 from either the postage memory 52 and converter 60 or the numerical keyboard 26a (FIG. 2). The digits, parallel by bit, enter serially and are shifted through the digit registers to their ultimate register positions under the control of a series of one shot multivibrators 160-163. During digit entry from the keyboard 26a, the system has to be conditioned to search the postage memory 52, since the zone located flip-flop ZL in the sequencer (FIG. 3) is still in its reset state. Its reset output RD LBS, a logical ONE, is applied to the multiplexer 62, conditioning it to connect the input/output register to the numerical keyboard 26a. The output RD LBS also conditions an AND gate 164 to pass a keyboard entry strobe pulse, which accompanies each keyboard digit entry, to the first one shot multivibrator 160 via an OR gate 166. The one shot multivibrator 160 is triggered to execute a pulse cycle. The multivibrator output pulse appears both on its set output lead 160a and, in complemented form, on its reset output lead 160b. The leading edge of the output pulse of multivibrator 160 on lead 160b, in effect, clears the tens digit register 150 by accepting the contents of the units register 152, while the trailing edge on lead 160a triggers the next one shot multivibrator 161 into a pulse cycle. The leading edge of its output pulse on reset output lead 161b is used to condition the units digit register 152 to accept the contents of the tenths digit register 154. The trailing edge of the pulse output of one shot multivibrator 161, appearing on its set output lead 161a, triggers one shot multivibrator 162 into a pulse cycle. The reset output of this multivibrator, on lead 162b, conditions the tenths digit register 154 to accept the content of the hundredths digit register 156, while the trailing edge of its output pulse on lead 162a triggers the last one shot multivibrator 163. The leading edge of the output pulse of this multivibrator on lead 163b, is applied to the hundredths digit register 156 to accept the digit entry in parallel bit, binary coded decimal form from the keyboard 26a via multiplexer 62.

It is thus seen that in response to each keyboard entry strobe pulse, the one shot multivibrators 160-163 fire in succession to effect the shifting of the digits content of the input/output register 58 to the right one digit position. As will be seen, a zip code entry from the numerical keyboard 26a requires only the first three digits of the zip code of the parcel destination.

Thus, a zip code entry encompasses three digit entries, each entry accompanied by a keyboard entry strobe pulse, and the zip code, once entered into the input/output register 58, is held in the first three digit registers 152, 154 and 156.

During the time that the system is to read a postage value from the postage memory 52 via serial to parallel converter 60, the zone located flip-flop ZL in the sequencer 56 (FIG. 3) is set, and its set output RD LBS, a logical ONE, enables an AND gate 170 in FIG. 4 to pass enter postage strobe pulses ENT POST from the serial to parallel converter 60 through to one short multivibrator 160 via OR gate 166. The reset output RD LBS from the zone located flip-flop ZL, being a logical ZERO, conditions the multiplexer 62 to accept postage digit entries from the postage memory 52 by way of a serial to parallel converter, rather than keyboard 26a. The postage digits, in parallel bit, binary coded decimal form, are shifted into the input/output register most significant digit first in the same manner as described for digit entries from the numerical keyboard 26a.

During a zone search, as previously described in connection with the sequencer of FIG. 3, add clock pulses ADD CLK are gated over lead 93 to the input/output register. As seen in FIG. 4, these clock pulses are applied to increment the hundredths digit register 156, which contains the least significant digit of the zip code entry. Each add clock pulse increments the hundredths digit register one count. The outputs of the one and eight bit stages of the hundredths digit register 156 are gated in an AND gate 172 to generate carry pulses for incrementing the tenths digit register 154. Similarly, the outputs of the one and eight bit stages of the tenths digit register are gated together in an AND gate 174 to generate carry pulses for the units digit register 152. These outputs of the one and eight bit stages of the units digit register are gated together in an AND gate 176 to generate a carry pulse which is gated in an AND gate 178 with the carry pulse outputs from gates 172 and 174, the add clock pulses arriving over lead 93, and the output PR SET from sequencer 56 (FIG. 3).

From this detailed description, it is seen that a zip code entry in the hundredths, tenths and units digit registers of the input/output register is incremented by the add clock pulses to 999. Upon the next add clock pulse, simultaneous carry pulses will be applied to AND gate 178 from AND gates 172, 174 and 176. This signifies that the input/output register has overflowed, i.e., counted to the complement of the zip code number originally entered therein, and the read store zone signal RD STR ZONE issues on lead 95 at the output of AND gate 178 for transmittal to the sequencer 56, the zone register 46 and the postage ready logic 80, all as seen generally in FIG. 2.

#### Scale And Weight Encoder

The scale unit 12, as seen in FIG. 5, includes a platform 200 on which a parcel 202 is placed to be weighted. The platform 200 is mounted by a pair of laterally spaced supports 204 pivotally linked at their lower ends to a lever 206, which, in turn, is pivotally mounted by a base 208. It is thus seen that upon placement of parcel 202 on the scale platform 200, the parcel weight forces the scale platform 200 downward, causing a counterclockwise pivotal movement of lever 206 against the restraining force of a spring 210 through an angle proportional to the parcel weight.

The free end of lever 206 carries a rack gear sector 212 which engages a pinion 214 keyed on a shaft 216 which also mounts an encoder disc 218. By virtue of this construction, it is seen that the pivotal movement of lever 206 in response to the parcel weight is translated into a proportional increment of angular rotation of the encoder disc 218. The encoder disc carries a series of opaque bars 220 which, upon rotation of the encoder disc, cause interruptions of a light beam between a source 222 and a receiver 224. Thus, the increment of rotation of the encoder disc 218 in response to the parcel weight is translated into a proportionate number of electrical pulses at the receiver 224.

#### Up/Down Scale Counter

The up/down counter 40 of FIG. 2 is seen in detail in FIG. 6. The receiver 224 noted in FIG. 5, comprises a pair of phototransistors 226 and 228. The use of two photosensors in the receiver 224 is for the purpose of conditioning steering logic circuitry, generally indicated at 230, pursuant to controlling the up/down counter 40 to count either up or down in response to movement theremitted of the bars 220 on encoder disc 218. As seen in FIG. 7, the phototransistors 226 and 228 of receiver 224 are positioned such that the response of the former to the bars 220 leads that of the latter for counting up in pounds, and vice versa for counting down in pounds. Thus, in FIG. 7, the encoder disc may be assumed to be moving to the left during countup and to the right during countdown. The phototransistors 226 and 228 are spaced apart by a distance equal to approximately one-half the width of a single opaque bar 220 on encoder disc 218. When the bars 220 are moving to the left passed the phototransistors, phototransistor 226 sees a dark to light transition while the phototransistor 228 is obscured by a bar. As will be seen, each time this occurs, a countup pulse is generated. On the other hand, a countdown pulse is generated when the phototransistor 226 sees a light to dark transition while the phototransistor 228 sees a light to dark transition while the phototransistor 228 is obscured by a bar 220 of the encoder disc 218. As was previously noted, the up/down capability of counter 40 is necessary to resolve any bounce of the scale platform 200 into an accurate registration of the weight of parcel 202.

Returning to FIG. 6, the emitter of phototransistor 226 is grounded, while its collector is connected to the input of an amplifier 232. Similarly, phototransistor 228 has its emitter grounded and its collector connected to the input of an amplifier 234. For purposes of the present description, it will be assumed that when the phototransistors are illuminated, they apply a logical ZERO input to their respective amplifiers, and when they are not illuminated, they develop logical ONE inputs.

The output of amplifier 232 is connected through an inverter 238 to the triggering input of an up multivibrator 236 and directly to the triggering input of a down multivibrator 240. The output of inverter 238 is also connected to the up/down sense input 241 of counter 40. It will be further seen that the counter will count up in response to clock pulses received at its clock input 242 as long as its sense input is a logical ONE, and will count down in response to those clock pulses received while its sense input is a logical ZERO.

Up multivibrator 236 is triggered in response to each logical ZERO to ONE transition, which through inverter 238 corresponds to each dark to light transition sensed by phototransistor 226. Since down multivibrator 240 is connected directly to the output of amplifier 232, it is triggered in response to each light to dark transition sensed by phototransistor 226. The pulse outputs of the up and down multivibrators are separately gated in AND gates 244 and 246, respectively. These 5 AND gates are enabled only during the time that the output from amplifier 234 is a logical ONE, which corresponds to the times that phototransistor 228 is obscured by bars 220. The output of AND gates 244 and 10 246 are connected as separate inputs to an OR gate 248, whose output is connected to the toggling input of a flip-flop 250 which, in the present application, serves as a half-pound counter since the encoder disc 218 is assumed to be graduated in half-pound increments. 15 The set output of flip-flop 250 is gated with the output of OR gate 248 and the output of inverter 238 in an AND gate 252. The reset output of flip-flop 250 is gated with the output of OR gate 248 and the output of amplifier 232 in an AND gate 254. The outputs of gates 20 252 and 254 are gated together in an OR gate 256, whose output is connected to the clock input 242 of counter 40.

The operation of the steering logic 230 of FIG. 6 will now be described in conjunction with the timing diagram of FIG. 7. Assuming that the counter 40 is counting up from 0 pounds, the first dark to light transition sensed by phototransistor 226 triggers up multivibrator 236. Its pulse output is passed by AND gate 244 since it is enabled by the logical ONE output from amplifier 234 due to the fact that phototransistor 228 senses no light. Flip-flop 250 is triggered on the trailing edge of the up multivibrator pulse from its original reset condition to its set condition. Counter 40 is not however pulsed on its clock input 242 from gate 252 since the up multivibrator pulse terminates as flip-flop 250 is set and gate 254 is disabled by the now prevailing logical ZERO output from amplifier 232. In response to the next dark to light transition the up multivibrator 45 generates another pulse and flip-flop 250 is reset by its trailing edge. However during the interval of this pulse, AND gate 254 is enabled since flip-flop 250 is still set and the output of inverter 238 is a ONE. Thus, this up multivibrator output pulse passes through gates 252 50 and 256 to the clock input of counter 40. Since the sense input 241 receives a ONE from inverter 238, counter 40 is incremented.

It is thus seen that with alternate dark to light transitions sensed by phototransistor 226, counter 40 is incremented to progressively register the angular displacement of the encoder disc 218 in response to the parcel weight.

If at any time, the encoder disc 218 rotates in the opposite or downward direction, down multivibrator 240 60 will be triggered by light to dark transitions sensed by phototransistor 226 during the time that phototransistor 228 senses no light. AND gate 246 is thus enabled to pass a pulse to reverse the state of flip-flop 250 on its trailing edge. Assuming that the flip-flop 250 has previously been triggered to its reset state at the conclusion of an up clock pulse to counter 40, the first increment of reverse or downward movement of

half-pound counter 288 to its set state. At this time, AND gate 292 is disabled from the 5 pound latch 290, and the units digit stage is not incremented. With the next occurring pound clock pulse LB CLK, the half-pound counter is triggered to its reset state, producing a logical ONE to ZERO transition at its set output which passes through AND gate 294 and OR gate 296 to increment the units digit stage 280 of the address counter 66. It is thus seen that the address counter 66 is incremented with every other pound clock pulse LB CLK read from postage memory 52.

The one and four bit outputs of the units digit stage 280 are gated together in an AND gate 298, such that when the units digit stage has been incremented to a 5 pound count, the 5 pound latch 290 is forced to its set state, thereby enabling AND gate 292 and disabling AND gate 294. Thereafter, each pound clock pulses passes through AND gate 292 to increment the units digit stage 280 of the address counter 66.

Prior to achieving a 5 pound count in the address counter 66, the content of the half-pound counter 288, appearing at the output of AND gate 294, is compared with the output of the half-pound counter 250 of the up/down counter 40 (FIG. 6). Thus, the output of AND gate 294 is applied to comparator 66 for comparison with the output of an AND gate 300 which receives as inputs the set output of half-pound counter 250 and the reset output of the 5 pound latch 290 of FIG. 10. It is thus seen that prior to the achievement of a 5 pound count in the address counter 66 the comparator 68 compares the content of the address counter and the up/down counter by half-pound increments. Above 5 pounds, both AND gates 294 and 300 are disabled by the 5 pound latch 290, and thus the content of the half-pound counters 250 and 288 are effectively ignored by comparator 68.

#### Serial to Parallel Converter

The serial to parallel converter 60, seen in FIG. 2, is shown in detail in FIG. 11. The operation of the serial to parallel converter begins with the read postage command signal RD POST supplied over lead 72 from the output of OR gate 140 in the sequencer 56 (FIG. 3). It will be recalled that the read postage command signal, except for oversized parcel situations, is derived from the comparison signal COMP issuing from comparator 68. As the read postage command signal goes to a logical ONE, a four bit shift register 302 is enabled to shift in the four bits of a postage digit read serially from the postage memory 52 over line 59. The read postage command signal RD POST is also supplied as one input to an AND gate 304 and as one input to an OR gate 306, whose output is connected to the forced reset input of a postage enter flip-flop POST ENT. The cycle complete signal O is supplied to the other input of OR gate 306, thus assuring that the postage enter flip-flop POST ENT is reset preparatory to the receipt of postage data by converter 60. As will be seen, the postage enter flip-flop is triggered to its set condition from the output of AND gate 308 to generate a postage enter signal POST ENT signifying that the last postage digit has been entered into the input/output register 58 from converter 60.

The postage clock pulses POST CLK read from postage memory 52 over lead 63 are used to shift the postage digit bits into shift register 302 and are also in-

verted in an inverter 310 for application to the other input of AND gate 304. The output of AND gate 304 is applied to one input of an AND gate 312 which is enabled from the reset output of the postage enter flip-flop

5 POST ENT. Thus, as long as this flip-flop is in its reset state, AND gate 312 passes clocking pulses from the output of AND gate 304 to increment a four bit binary counter 314. The one and two bit stages of binary counter 314 are inverted in inverters 316 and 318, whose outputs are connected as separate inputs to an AND gate 319, together with the output of AND gate 304. The fourth input to AND gate 316 originates from an OR gate 320 whose inputs come from the four and eight bit stages of the binary counter 314.

15 It is seen that gate 319, as controlled by inverters 316, 318 and OR gate 320, provides an output pulse when the count of the binary counter 314 reaches four, eight and 12. This pulse output is supplied through an

20 OR gate 322 as the enter postage shift or strobe pulse ENT POST to the input/output register 58, causing the first three digits of the postage data to be successively shifted into the input/output register from the shift register 302 of the serial to parallel converter. When the 25 binary counter 314 reaches a count of 16, AND gate 308 is fully enabled to trigger the postage enter flip-flop POST ENT to its set position. The set output of this flip-flop enables an AND gate 324, whose other input is obtained from AND gate 304. The output of gate 324 is 30 connected as the other input to OR gate 322, such that the last enter postage shift pulse ENT POST effecting the shift in of the last postage digit comes from gate 324, rather than gate 319.

35 The purpose of gating the complement of the postage clock pulses POST CLK with the read postage command signal RD POST in AND gate 304 is to derive a train of clock pulses for clocking binary counter 314 which is effectively shifted ahead in time relative to the 40 postage clock pulse train. In this way, the binary counter is incremented one count just prior to the shifting of the corresponding postage digit bit into shift register 302.

45 Specifically, when the read postage command signal RD POST appears, line 72 goes from a logical ZERO to a logical ONE, and the output of AND gate 304 goes to a ONE. When the first postage clock pulse POST CLK appears, the output of AND gate 304 goes to a logical ZERO and this ONE to ZERO transition passes 50 through AND gate 312 to increment the binary counter 314. As each postage clock pulse terminates, the shift register 302 is shifted to accept the postage digit bit being read from the postage memory 52. On the leading edge of the fourth postage clock pulse, the binary counter 314 is incremented to four, and the fourth bit of the first postage digit is shifted into the shift register 302 on the termination of the fourth postage clock pulse. At this point, the output of the AND gate 304 goes to a logical ONE, which passes through AND gate 55 317 as the enter postage shift pulse ENT POST to the input/output register 58. This shift pulse terminates with the leading edge of the fifth postage clock pulse, which is also effective through AND gate 312 to increment the binary counter to five. When the binary counter reaches the counts of eight and 12, the same operation occurs to shift the second or third postage digits into the input/output register.

the encoder disc 218 triggers the down multivibrator and its output pulse is passed by gate 254 before flip-flop 250 is set. This pulse is effective to decrement counter 40 since its up/down sense input 241 is now a logical ZERO as seen in FIG. 7.

#### Postage and Zip-Zone Memories

The postage memory 52, actually a read-only memory, stores a pounds to postage conversion table, which may take the form of a film strip secured on the periphery of the memory drum 14 (FIG. 1). It will be appreciated that, in the event of a postage rate change, a film strip bearing the new rate table may be readily substituted. A typical arrangement of the postage data for a portion of the conversion chart of postage memory 52 is shown in FIG. 8. The postage memory includes a series of opaque pound bars, of which two are shown in FIG. 8 at 260. These pound bars are read out as pound clock pulses LB CLK, which are accumulated in the address counter 56, as generally described in connection with FIG. 2. The postage data is stored in a series of channels according to postal zone and carrier service. For example, each postal zone may be allotted three separate channels of postage data according to the carrier desired. Thus, one channel of each zone is devoted to the postage for air parcel post (APP), a second for surface parcel post (SPP) and the third for United Parcel Service (UPS). The postage data is stored in binary coded decimal form, most significant digit and most significant bit first. It is assumed that the left pound bar 260 shown in FIG. 8 corresponds to the 9 pound clock pulse and the one to the right the 10 pound clock pulse, the postage data stored therebetween is applicable to a parcel weighing 9, but less than 10, pounds. Each block of postage data is accompanied by a series of 16 postage clock bits 262 which are read out as postage clock pulses POST CLK to the serial to parallel converter 60 (FIG. 2) to synchronize the handling of the serially read four bits of each postage digit for parallel bit transmission of successive postage digits to the input/output register 58.

It is apparent from FIG. 8, that when the appropriate postal zone has been determined and entered into the zone register 46 (FIG. 8), and the desired carrier APP, SPP or UPS has been selected by the operator, the postage memory readout station is conditioned to serially read out the postage data in only one of the various postage data channels in the postage memory 52.

The zip-zone memory 90, seen in FIG. 9, is also a read-only memory storing an optically encoded zip code to postal zone conversion table carried as a film strip on the periphery of the memory drum 14 (FIG. 1). The array of opaque timing bits 270 are read out to provide the zip clock pulses ZIP CLK which are applied, as previously discussed, as add clock pulses ADD to the input/output register 58, pursuant to counting to the complement of the zip code number entered therein. Aligned with each bar 270 are four bit positions for storing the appropriate zone number in binary coded decimal; the bits being read out in parallel.

The zip-zone memory also includes three additional channels A, B and C which contain flag bits for designating special situations, as will be described in connection with the postage ready logic circuitry 80, generally disclosed in FIG. 2 and detailed in FIG. 12. Any flag bits aligned with the appropriate zone are read

out with the zone number in response to the read store zone signal RD STR ZONE and used in conjunction with add-on control data, generally indicated at 272 and stored at the end of the zip to zone conversion table. As will be seen, this add-on data, together with any flag bits read from channels A, B and C is utilized by the postage ready logic 80 to augment the postage data read from the postage memory 52 into the input/output register 58.

#### 10 Address Counter and Comparator

The address counter 56 of FIG. 2 is shown in detail in FIG. 10 and operates to count the pound clock pulses LB CLK read from the postage memory 52 starting from the beginning of the pound to postage conversion table stored therein. The units digits of the pounds address are accumulated in binary coded decimal form in a units digit stage 280 of the address counter 66. The one and eight bit outputs of the units digit stage 280 are gated together in an AND gate 284 to provide carry pulses which are accumulated in a tens digit stage 282 of the address counter 66. The content of the address counter 66 is continuously compared in comparator 68 with the parcel weight held in the up/down counter 40 (FIGS. 2 and 6). When the address counter 66 has been incremented to a pound count comparable to that held in the up/down counter 40, comparator 66 generates the output COMP on lead 70 and its complement  $\overline{\text{COMP}}$  through inverter 286.

30 As was previously noted, the pound encoder 218 of FIG. 6 is graduated in half-pound increments, thus the up/down counter 40 counts in half-pound increments by virtue of flip-flop 250 in FIG. 6. Since the rate schedule for APP is based on half-pound increments for parcel weights up to 5 pounds and pound increments above 5 pounds, the address counter 66 must be initially adapted to interpret the pound clock pulses LB CLK as half-pound increments up to 5 pounds and pound increments thereafter. To this end, the control logic for the address counter 66 includes two flip-flops 288 and 290, the former serving as a half-pound counter for the pound clock pulses LB CLK and the latter as a 5 pound latch for disabling the half-pound counter when the address counter 66 has been incremented to 5 pounds.

Specifically, as seen in FIG. 10, the pound clock pulses LB CLK from the postage memory 52 arriving over lead 64 are applied to one input of an AND gate 292 50 and also to the triggering input of the half-pound counter 288. The set output of the half-pound counter is connected as one input to an AND gate 294, whose output is gated with the output of AND gate 292 in an OR gate 296. The output of this OR gate is connected 55 to the clock input of the units digit stage 280 of the address counter 66.

The other input to AND gate 292 is obtained from the set output of the 5 pound latch 290, while the other input to AND gate 294 is obtained from the reset output of the 5 pound latch. Initially, the 5 pound latch is reset by the reset pulse issuing at the beginning of each revolution of the pounds to postage conversion table passed its readout station. Thus, AND gate 292 is disabled, while AND gate 294 is enabled. Similarly, the half-pound counter 288 is also initially in its reset state. The first pound clock pulse LB CLK read from the postage memory 52 after each reset pulse triggers the

When the binary counter 314 goes from a count of 15 to 16 on the leading edge of the 16th postage clock pulse, the output of AND gate 308 goes from ONE to ZERO, triggering postage enter flip-flop POST ENT to its one state. On the trailing edge of the sixteenth postage clock pulse, the last postage digit is shifted into the shift register 302 and the output of AND gate 304 goes to a ONE, which passes through AND gate 324 and OR gate 322 as the fourth enter postage shift pulse ENT POST. This shift pulse terminates as the read postage command signal RD POST goes to ZERO, which occurs when the address counter 66 is incremented and the comparator 68 senses that there is no longer a comparison between the address counter 66 and the up/down counter 40. Shift register 302 is disabled, as is the binary counter 314 by the reset output of the postage enter flip-flop POST ENT.

#### Postage Ready Logic

The postage ready logic 80 of FIG. 2, seen in detail in FIG. 12, generally handles special situations which affect the postage data entered into the input/output register 58. In addition, the postage ready logic handles various error situations identified by a flag bit stored in the channel C of the zip-zone memory (FIG. 9). Ultimately, the postage ready logic is responsible for generating the ready enter signal RDY ENT over lead 84 enabling the postage digit selection apparatus 30 to initiate the setting up of the postage meter 32 to the postage value registered in the input/output register 58.

Referring to FIG. 12, the four zone data bits in channels 1, 2, 4 and 8 of the zip-zone memory 90 (FIG. 9) in parallel to multiplexer 44 for entry into the zone register 46 upon issuance of the read store zone command signal RD STR ZONE from the input/output register 58. If the zone is to be entered from the numerical keyboard 26a, depression of the key Z sets flip-flop ZFF in the sequencer 56 (FIG. 3), and the set output ZFF conditions multiplexer 44 to connect the zone register 46 to the numerical keyboard 26a for direct zone entry.

In certain situations, there may not be an appropriate zone conversion for a zip code entered into the input/output register 58. To handle these situations, the zone number which would be read out in response to the read store zone command signal RD STR ZONE is coded as a decimal nine. Since the postage rate schedules under the parcel post and the United Parcel Service systems only contemplates eight postal zones, a nine readout may be used to identify a zone error. Thus, channels 1 and 8 of the zip-zone memory are applied to an AND gate 400, together with the read store zone signal RD STR ZONE. If, when the read store zone signal issues, the number 9, in binary coded decimal, is read from the zip-zone memory, AND gate 400 is enabled to set a zone error flip-flop 402. The set output of this flip-flop may be used to initiate energization of a suitable error light at the control panel 26.

In certain situations, particularly with respect to the UPS system, United Parcel Service does not have authorized land routes between the mailing site and certain parcel destinations. For these situations, UPS resorts to so-called "drop shipping," requiring special shipping charges which the present system is not equipped to handle. However, it is necessary to identify these special situations, and the present system is

equipped to do so. To this end, a flag bit is encoded in channel C in the zip-zone memory (FIG. 9) aligned with storage locations of those zones for which "drop shipping" must be employed. The coincidence of a readout of a flag bit from channel C and the issuance of a read store zone signal is detected by AND gate 404, whose output is connected to set a flip-flop 406 to register the occurrence of a C error. The set output of this flip-flop may be used to initiate energization of an appropriate error light to notify the operator that, for example, a "drop shipping" situation has arisen.

Returning briefly to the sequencer of FIG. 3, it will be recalled that error signal M issues from AND gate 134 if the system fails to locate a zone on the basis of a zip code entry into the input/output register 58. Returning to FIG. 12, this error signal M is applied to set an M error flip-flop 408. It will be noted that the reset outputs of flip-flops 402, 406 and 408 are gated together in an AND gate 410, whose output is connected as one input to an AND gate 412 from which the ready enter signal RDY ENT issues. As a consequence, if an error situation is detected, AND gate 412 is disabled to inhibit the ready enter signal and thus prevent the postage digit selection apparatus 30 from setting the postage meter 32 to any postage value registered in input/output register 58. In addition, if the postage value in the input/output register is to be displayed only, the display only key D/O (FIG. 3) is depressed to set the display only flip-flop D/OFF, and its reset output D/OFF disables AND gate 412 to inhibit the ready enter signal.

Flag bits encoded in the channels A and B of the zip-zone memory 90 and read out during the occurrence of a read store zone signal RD STR ZONE are used in conjunction with the add-on postage control data 272 (FIG. 9) stored at the end of the zip-zone conversion table stored in the zip-zone memory. As seen in FIG. 12, the readout of flag bits stored in channels A and B are used to set one of three flip-flops 420, 422 and 424. Specifically, the readout of channel A is applied to AND gates 426 and 428, and, through an inverter 430, to AND gate 432. The readout of channel B is applied to AND gate 428, AND gate 432, and through an inverter 434, to AND gate 426. The read store signal RD STR ZONE is applied as a third input to each of these gates. If a flag bit is read from channel A when the read store zone signal issues, an output issues from AND gate 426 to set the flip-flop 420, labeled AB. If a flag bit is read from channel B when the read store zone command signal issues, the resulting output from AND gate 432 sets flip-flop 422, labeled  $\overline{AB}$ . If a flag bit is read from both channels A and B when the read store zone signal issues, AND gate 428 provides an output to set flip-flop 424, labeled AB.

Assuming that no additional postage function is to be executed, and thus neither of the flip-flops 420, 422 and 424 is set, their reset outputs, all logical ONES, enable an AND gate 440, whose output enables an AND gate 442. Thus, AND gate 442 is conditioned to pass the postage entered signal POST ENT generated by the postage entered flip-flop in the serial to parallel converter 60 (FIG. 11) through to one input of a normally enabled AND gate 444. It will be recalled that the postage entered signal POST ENT issues as the last postage digit is shifted into the input/output register 58.

The AND gate 444 is normally enabled from the reset output of an add postage flip-flop ADD POST, and thus the postage entered signal is passed through to OR gate 446 to set a postage ready flip-flop POST RDY. Assuming no error and that the postage is not merely to be displayed, the logical ONE at the set output of the postage ready flip-flop is passed through AND gate 412 as the ready enter signal RDY ENT for transmission over lead 84 to the postage digit selection apparatus 30 (FIG. 2).

On the other hand, if one of the flip-flops 420, 422 and 426 has been set during the issuance of the read store zone signal RD STR ZONE, the output of AND gate 440 is a logical ZERO, which is inverted by an inverter 441 to a ONE to enable an AND gate 443. Thus, the postage entered signal POST ENT passes through AND gate 443 to set add postage flip-flop ADD POST. Since AND gate 442 is disabled from the output of AND gate 440, the postage entered signal is inhibited from setting the postage ready flip-flop POST RDY.

Still referring to FIG. 12, the set output of the AB flip-flop 420 is connected to an AND gate 450 together with the readout of channels 1, 2 and 8 of the zip-zone memory. The set output of AB flip-flop 424 is gated in AND gate 452 with the readout of channels 2 and 8 of the zip-zone memory, while the set output of AB flip-flop 422 is gated in AND gate 454 with the readout of channels 4 and 8. The outputs of AND gates 450, 452 and 454 are gated together in an OR gate 456, whose output is gated with the reset output POST RDY of the postage ready flip-flop in an AND gate 456 to provide an add clock gate signal ADD CLK GATE. It will be recalled that the add clock gate signal is used in the sequencer 56 of FIG. 3 to enable AND gate 130 to pass zip clock pulses ZIP CLK as add clock pulses ADD CLK over lead 93 to input/output register 58.