(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-333166

(P2005-333166A)

(43) 公開日 平成17年12月2日(2005.12.2)

(51) Int.CI.<sup>7</sup>

H 01 L 21/60

F 1

H 01 L 21/60

3 1 1 Q

テーマコード(参考)

5 F O 4 4

審査請求 有 請求項の数 1 O L (全 16 頁)

|            |                                   |          |                                                   |

|------------|-----------------------------------|----------|---------------------------------------------------|

| (21) 出願番号  | 特願2005-240361 (P2005-240361)      | (71) 出願人 | 000005223<br>富士通株式会社<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 |

| (22) 出願日   | 平成17年8月22日 (2005.8.22)            | (74) 代理人 | 100070150<br>弁理士 伊東 忠彦                            |

| (62) 分割の表示 | 特願2002-49394 (P2002-49394)<br>の分割 | (72) 発明者 | 安藤 史彦<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内       |

| 原出願日       | 平成14年2月26日 (2002.2.26)            | (72) 発明者 | 高島 晃<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内        |

|            |                                   | (72) 発明者 | 西村 隆雄<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内       |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】 本発明は半導体チップに設けられた突起電極を被実装部材に設けられたパッドに接合する半導体装置の製造方法に関し、バンプ間ピッチが狭ピッチ化してもバンプ間で短絡が発生することを防止することを課題とする。

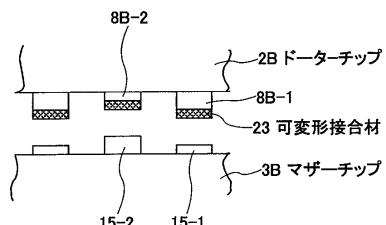

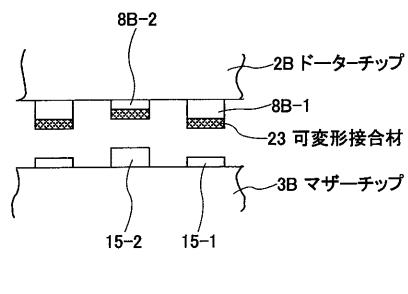

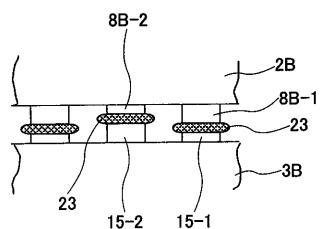

【解決手段】 ドータチップ2Bに設けられた突起電極8B-1,8B-2を、該ドータチップ2Bが実装されるマザーチップ3Bに設けられたパッド15-1,15-2に接合する工程を有する半導体装置の製造方法において、隣接する突起電極8B-1,8B-2及びこの突起電極8B-1,8B-2に対応するパッド15-1,15-2とはそれぞれ互いに高さが異なるよう設けられ、突起電極8B-1,8B-2、またはパッド15-1,15-2の少なくとも一方に突起電極8B-1,8B-2及びパッド15-1,15-2よりも軟質で接合時に変形可能とされた可変形接合材23を配設しておき、突起電極8B-1,8B-2とパッド15-1,15-2とを可変形接合材23を介して接合する。

【選択図】 図12

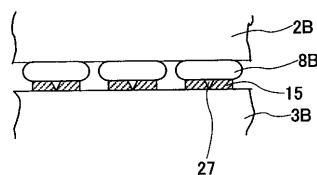

本発明の第2実施例である半導体装置の製造方法の変形例を説明するための図であり、チップ接合前の状態を示す図

**【特許請求の範囲】****【請求項 1】**

半導体チップに設けられた突起電極を、該半導体チップが実装される被実装部材に設けられたパッドに接合する工程を有する半導体装置の製造方法において、

隣接する前記突起電極及び該突起電極に対応する前記パッドとは、それぞれ互いに高さが異なるよう設けられ、

前記突起電極、または前記パッドの少なくとも一方に、前記突起電極及び前記パッドよりも軟質で前記接合時に変形可能とされた可変形接合材を配設しておき、

前記突起電極と前記パッドとを前記可変形接合材を介して接合することを特徴とする半導体装置の製造方法。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は半導体装置の製造方法に係り、特に半導体チップに設けられた突起電極を被実装部材に設けられたパッドに接合する半導体装置の製造方法に関する。

**【0002】**

近年、携帯端末装置に代表される電子機器の小型化の要求に伴い、それらに搭載される半導体装置の小型化・軽量化が強く要求されている。この要求を満たすために、半導体チップの実装方法としてフリップチップ接合を用い、また複数の半導体チップを1パッケージ内にスタック(積層)する構造が採用されている。

20

**【背景技術】****【0003】**

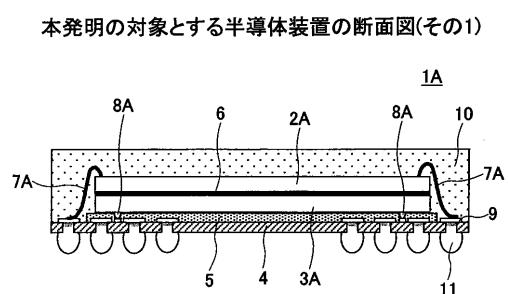

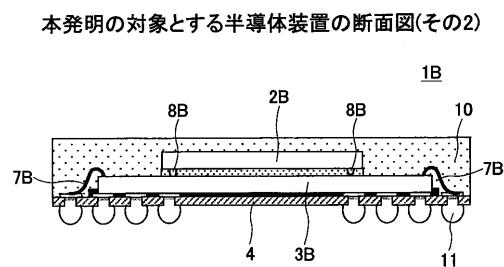

図1及び図2は、小型化の要求に対応した半導体装置の一例を示している。図1及び図2に示す半導体装置1A, 1Bは、いずれもドーターチップ2A, 2Bとマザーチップ3A, 3Bを一つの封止樹脂10内にスタック(積層)した構造とされている。

**【0004】**

図1に示される半導体装置1Aは、マザーチップ3Aをインターポーザ4にフリップチップ接合した構成とされている。即ち、マザーチップ3Aに形成されたバンプ8Aが、インターポーザ4に形成された電極部9にフリップチップ接合された構成とされている。また、マザーチップ3Aとインターポーザ4との間には、ダイ付け樹脂5が配設されている。

30

**【0005】**

ドーターチップ2Aは、マザーチップ3A上に接着剤6を用いて搭載された構成とされている。また、ドーターチップ2Aとインターポーザ4は、ワイヤー7Aを用いて接続されている。

**【0006】**

上記のワイヤー7A及びバンプ8Aは、インターポーザ4に形成されている電極部9に接続される。この電極部9の形成位置にはスルーホールが形成されており、外部接続端子となる半田ボール11はこのスルーホールを介して電極部9に接続した構成とされている。

40

**【0007】**

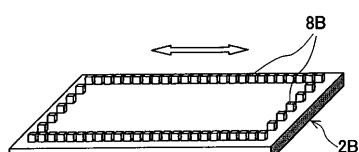

一方、図2に示される半導体装置1Bは、ドーターチップ2Bをマザーチップ3Bにフリップチップ接合した構成とされている。即ち、ドーターチップ2Bに形成されたバンプ8Bが、マザーチップ3Bに形成された電極(図示せず)にフリップチップ接合された構成とされている。

**【0008】**

マザーチップ3Bは、インターポーザ4上に接着剤を用いて固定された構成とされている。また、マザーチップ3Bとインターポーザ4は、ワイヤー7Bを用いて接続されている。更に、上記のワイヤー7B及びバンプ8Bは、図1に示した半導体装置1Aと同様に

50

、インターポーラ 4 に形成されたスルーホールを介して外部接続端子となる半田ボール 1 1 と接続した構成とされている。

【0009】

上記したように、図 1 に示す半導体装置 1 A はマザーチップ 3 A (下部に位置する半導体チップをマザーチップという) をインターポーラにフリップチップ接合し、また図 2 に示す半導体装置 1 B はドーターチップ 2 B (上部に位置する半導体チップをドーターチップという) をマザーチップ 3 B にフリップチップ接合している。このフリップチップ接合を行う装置及び方法については、例えば特許文献 1 ~ 5 に示されるように、各種提案されている。

【0010】

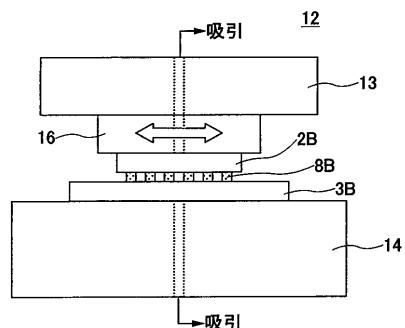

図 3 は、フリップチップ接合を行う装置の一例である半導体製造装置 1 2 を示している。尚、図 3 は、半導体装置 1 B の製造過程において、ドーターチップ 2 B とマザーチップ 3 B とをフリップチップ接合する例を示している。

【0011】

半導体製造装置 1 2 は、大略すると超音波ホーン 1 3 とチップ吸着ステージ 1 4 とにより構成されている。超音波ホーン 1 3 は超音波振動を発生させるものであり、その下部には吸着チャック 1 6 が配設されている。

【0012】

この吸着チャック 1 6 は、超音波ホーン 1 3 と一体的な構成されており、よって超音波振動を行なう。図 3 に示す矢印は、超音波振動の振幅方向を示している。また、吸着チャック 1 6 は図示しない吸引手段に接続されており、よってこの吸引力によりドーターチップ 2 B は吸着チャック 1 6 に吸着される構成とされている。

【0013】

一方、チップ吸着ステージ 1 4 は吸着チャック 1 6 の下部に配設されており、その上部にマザーチップ 3 B が載置される。チップ吸着ステージ 1 4 は図示しない吸引手段に接続されており、よってこの吸引力によりマザーチップ 3 B はチップ吸着ステージ 1 4 に吸着される構成とされている。

【0014】

そして、ドーターチップ 2 B を吸着チャック 1 6 に吸着し、マザーチップ 3 B をチップ吸着ステージ 1 4 に吸着した状態でドーターチップ 2 B とマザーチップ 3 B を近接させる。そして、バンプ 8 B がマザーチップ 3 B に当接した状態で、超音波ホーン 1 3 を駆動する。これにより、超音波振動はバンプ 8 B に印加され、バンプ 8 B は溶融してマザーチップ 3 B に接合される。

【特許文献 1】特開 2001-338941 号公報

【特許文献 2】特開平 11-284028 号公報

【特許文献 3】特開平 10-125734 号公報

【特許文献 4】特開 2001-308141 号公報

【特許文献 5】特開 2001-291742 号公報

【発明の開示】

【発明が解決しようとする課題】

【0015】

ところで、半導体装置の小型化・軽量化及び高速化、高機能化に伴い、半導体チップ 2 B , 3 A に形成されるバンプ 8 A , 8 B は微細化し、またその配設ピッチは狭ピッチ化する傾向にある。このように、バンプ 8 A , 8 B の狭ピッチ化が進むと、ドーターチップ 2 A , 2 B とマザーチップ 3 A , 3 B との超音波接合時において、バンプ 8 A , 8 B が潰れ、隣接するバンプ 8 A , 8 B 間で短絡(ショート)が発生するという問題点がある。

【0016】

図 4 を用いて、具体例について説明する。尚、同図では、バンプ 8 B を超音波接合する例を示している。

【0017】

10

20

30

40

50

バンプ 8 B を超音波接合する際、その超音波の振幅方向が図中矢印で示すように長手方向に沿った方向であったとすると、超音波振動の印加により溶融したバンプ 8 B は、図 5 に示すように超音波の振幅方向（図中、矢印で示す方向）に延出した形状となる。換言すると、超音波接合時において、バンプ 8 B は超音波の振幅方向に長径を有した橢円形状となる。

#### 【 0 0 1 8 】

このため、図 6 に示すように、ドーターチップ 2 B とマザーチップ 3 B とを接合した際、隣接するバンプ 8 B 同士で、詳細には超音波の振幅方向に隣接するバンプ 8 B 同士で短絡が発生してしまう。この現象は、図 1 に示した半導体装置 1 A においても同様に発生する。このような隣接するバンプ 8 A, 8 B で短絡が発生するのは、バンプ間ピッチが 60  $\mu\text{m}$  以下となった場合に重大な問題となる。10

#### 【 0 0 1 9 】

本発明は上記の点に鑑みてなされたものであり、突起電極間のピッチが狭ピッチ化しても突起電極間で短絡が発生することのない半導体装置の製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【 0 0 2 0 】

上記の課題を解決するために本発明では、

半導体チップに設けられた突起電極を、該半導体チップが実装される被実装部材に設けられたパッドに接合する工程を有する半導体装置の製造方法において、20

隣接する前記突起電極及び該突起電極に対応する前記パッドとは、それぞれ互いに高さが異なるよう設けられ、20

前記突起電極、または前記パッドの少なくとも一方に、前記突起電極及び前記パッドよりも軟質で前記接合時に変形可能とされた可変形接合材を配設しておき、20

前記突起電極と前記パッドとを前記可変形接合材を介して接合することを特徴とするものである。

#### 【 0 0 2 1 】

上記発明によれば、突起電極とパッドとを可変形接合材を介して接合される。この際、可変形接合材は、突起電極及びパッドよりも軟質であり、接合時に変形可能な構成である。このため、突起電極とパッドとを接合する際、突起電極とパッドは変形せずに可変形接合材のみが変形し接合が行われる。このように、接合時において突起電極及びパッドが変形しないことにより、狭ピッチ化しても隣接する突起電極間及び隣接するパッド間で短絡が生じることを防止することができる。30

#### 【 0 0 2 2 】

また、隣接する突起電極の高さを異ならせたことにより、可変形接合材の配設される高さも隣接する突起電極間で異なる。可変形接合材は、突起電極とパッドとを接合した際、変形して側部にはみ出る可能性があるが、上記のように隣接する可変形部材の高さが異なることにより、上記のようにみ出しが生じても可変形部材間で短絡が発生することを防止することができる。

#### 【発明の効果】

#### 【 0 0 2 3 】

上述の如く本発明によれば、突起電極とパッドとを接合する際、突起電極とパッドは変形せずに可変形接合材のみが変形し接合が行われるため、狭ピッチ化しても隣接する突起電極間及び隣接するパッド間で短絡が生じることを防止することができる。また、隣接する可変形部材の高さが異なることにより、接合時に可変形接合部材がはみ出したとしても、可変形部材間で短絡が発生することを防止することができる。40

#### 【発明を実施するための最良の形態】

#### 【 0 0 2 4 】

次に、本発明を実施するための最良の形態について図面と共に説明する。

#### 【 0 0 2 5 】

10

20

30

40

50

図7乃至図9は、本発明の第1実施例である半導体製造装置及び半導体装置の製造方法を説明するための図である。尚、以下の各実施例の説明では、図2に示した半導体装置1Bを製造する例について説明するが、本発明の適用は図2に示す半導体装置1Bの製造に限定されるものではなく、突起電極（バンプ等）を用いた実装処理に広く適用できるものである。

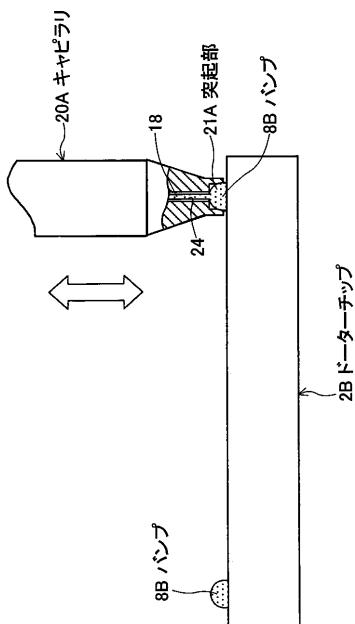

#### 【0026】

本実施例に係る半導体製造装置は、ドーターチップ2Bにバンプ8Bを形成するものである。また、本実施例ではバンプ8Bはスタッダードバンプとされており、ワイヤーボンディング技術を利用してバンプ8Bが形成される。

#### 【0027】

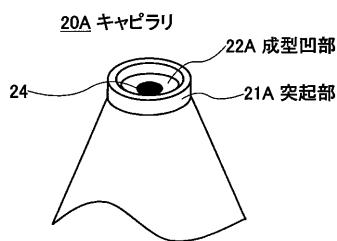

半導体製造装置は、図7に示すキャピラリ20Aを有している。このキャピラリ20Aは、図示しない超音波発生装置に接続されており、超音波振動を行なう構成とされている。また、キャピラリ20Aは、内部に金ワイヤー18を挿通する挿通孔24が形成されている。

#### 【0028】

更に、本実施例に係る半導体製造装置は、キャピラリ20Aの先端部に突起部21Aが形成されている。この突起部21Aは同一高さを有した円状の突起であり、よって相対的にキャピラリ20Aの先端部には凹部（以下、この凹部を成形用凹部22Aという）が形成された構成とされている。この成形用凹部22Aは、後述するように、バンプ8Bを成形するときの型として機能する。

#### 【0029】

上記構成とされた半導体製造装置を用いてバンプ8Bをドーターチップ2B上に形成するには、先ず金ワイヤー18をキャピラリ20Aから延出させ、その先端に図示しない電気トーチによる放電処理により金ボールを形成する。そして、キャピラリ20Aを移動させることにより、この金ボールをドーターチップ2B上のバンプ形成位置に位置決めする。

#### 【0030】

続いて、キャピラリ20Aを超音波振動させることにより、金ボールをドーターチップ2Bに超音波接合する。この際、キャピラリ20Aの先端に形成された突起部21Aは、ドーターチップ2Bに押圧された状態で超音波接合が実施される。このように、突起部21Aは、ドーターチップ2Bに押圧されることにより、超音波接合時において成形用凹部22Aは閉空間となる。また、金ボールは、この閉空間とされた成形用凹部22Aの内部で超音波により溶融することとなる。

#### 【0031】

従って、溶融した金ボールは、突起部21Aによりキャピラリ20Aの外部にはみ出す（漏れ出す）ことを防止することができる。即ち、キャピラリ20Aにより形成されるバンプ8Bは、全て成形用凹部22Aの形状に対応した同一の形状となる。これにより、キャピラリ20Aにより形成されるバンプ8Bの形状を既定形状に高精度に揃えることができ、よって隣接するバンプ8B間で短絡が発生することを防止することができる。

#### 【0032】

また本実施例では、上記したようにバンプ8Bを形成するキャピラリ20Aに突起部21Aを一体的に形成することにより、キャピラリ20Aにバンプ8Bを成形する成形治具としての機能をも持たせた構成としている。これにより、成形治具とキャピラリ20Aを別個とする構成に比べ、半導体製造装置の構成の簡単化を図ることができる。また、バンプ8Bの形成処理と、バンプ8Bの成形処理を同時に行なうことができるため、処理時間の短縮を図ることができる。

#### 【0033】

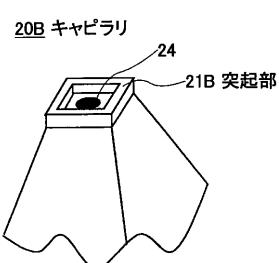

尚、本実施例では、突起部21Aを図8に示すように円形状としたが、突起部の形状は円形に限定されるものではない。具体的には、図9に示すように、キャピラリ20Bの先端に矩形状の突起部21Bを形成した構成としてもよく、また図示しないが楕円形等の他

の形状とすることも可能である。

【0034】

次に、本発明の第2実施例である半導体装置の製造方法について説明する。

【0035】

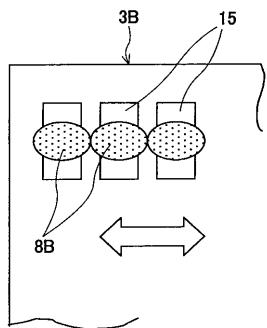

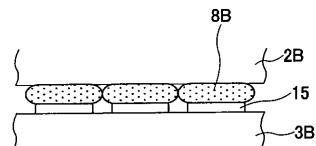

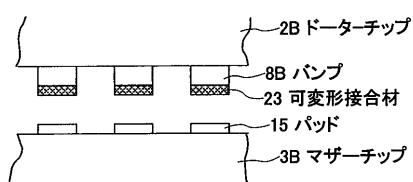

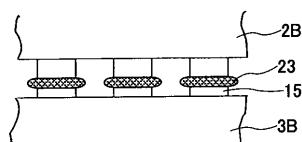

図10及び図11は、第2実施例である半導体装置の製造方法を説明するための図である。本実施例では、ドーターチップ2Bに形成されたバンプ8Bと、マザーチップ3Bに形成されたパッド15Bとを超音波接合するのに、バンプ8Bに可変形接合材23を配設し、この可変形接合材23を介してバンプ8Bとパッド15を超音波接合したことを特徴とするものである。

【0036】

可変形接合材23は、バンプ8B及びパッド15よりも軟質で、かつ超音波接合時に変形可能な材質が選定されている。具体例としては、バンプ8B及びパッド15をニッケルで形成した場合、可変形接合材23としてニッケルよりも軟質で変形可能な金を用いることが考えられる。

【0037】

図11は、バンプ8Bがパッド15に接合された状態を示している。同図に示すように、バンプ8Bとパッド15は、可変形接合材23を介して接合される。この際、前記のように可変形接合材23はバンプ8B及びパッド15よりも軟質であり、かつ接合時に変形可能な構成であるため、接合時にバンプ8Bとパッド15は変形せず、可変形接合材23のみが変形して接合が行われる。

【0038】

このように、本実施例による製造方法では、超音波接合時においてバンプ8B及びパッド15は変形しないため、狭ピッチ化しても隣接するバンプ8B及びパッド15間で短絡が生じることはない。

【0039】

この接合の際、可変形接合材23は超音波接合時に押圧されるため、若干外部にはみ出しがある。しかしながら、可変形接合材23の配設量はバンプ8Bの体積に対して少なく、よってはみ出し量も少ないため、隣接する可変形接合材23間で短絡が発生することもない。

【0040】

尚、上記した実施例では可変形接合材23をバンプ8Bに配設した構成としたが、可変形接合材23はパッド15に設けた構成としてもよく、またバンプ8Bとパッド15との双方に設けた構成としてもよい。

【0041】

次に、本発明の第3実施例である半導体装置の製造方法について説明する。

【0042】

図12及び図13は、第3実施例である半導体装置の製造方法を説明するための図である。本実施例では、前記した第2実施例と同様に、ドーターチップ2Bに形成されたバンプ8Bと、マザーチップ3Bに形成されたパッド15Bとを超音波接合するのに、可変形接合材23を介して超音波接合する構成としている。但し、第2実施例では複数形成されたバンプ8B及びパッド15を同一高さとしていたのに対し、本実施例では、隣接するバンプ8Bの高さを異ならせたことを特徴とするものである。

【0043】

具体的には、図12に示すように、バンプ8B-1は、これと隣接したバンプ8B-2に対して高い構成とされている。これに対応して、バンプ8B-1と接合されるパッド15-1は、バンプ8B-2と接合されるパッド15-2に対して低い構成とされている。このように、隣接するバンプ8B-1, 8B-2の高さを異ならせたことにより、図13に示すように、超音波接合後における可変形接合材23の高さも各バンプ8B-1, 8B-2間で異なった高さとなる。

【0044】

10

20

30

40

50

前記したように、可変形接合材 23 は、バンプ 8B（バンプ 8B-1, 8B-2）とパッド 15（パッド 15-1, 15-2）とを接合した際、変形して側部にはみ出る可能性がある。しかしながら、本実施例のように、隣接するバンプ 8B の高さを変化させ、これに伴い可変形部材 23 の高さを異ならせることにより、上記のようにはみ出しが生じても可変形接合材 23 間で短絡が発生することを防止することができる。よって、本実施例の構成とすることにより、更にバンプ 8B の狭ピッチ化を図ることが可能となる。

次に、本発明の第4実施例である半導体装置の製造方法について説明する。

#### 【0045】

図14乃至図16は、第4実施例である半導体装置の製造方法を説明するための図である。本実施例では、バンプ 8B とパッド 15 との位置決め精度を向上させることにより、10 バンプ 8B の狭ピッチ化を可能としたものである。

#### 【0046】

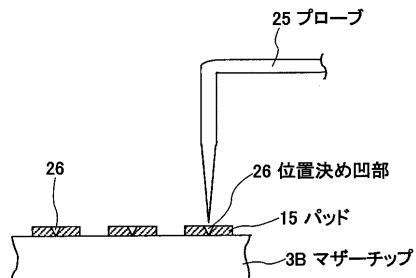

通常、半導体装置 1A, 1B は、半導体チップ 2A, 2B, 3A, 3B を実装する前に所定の信頼性試験が実施される。この信頼性試験は、図14に示すように、複数プローブ 25（図では、便宜上1本のみ示している）を用いて実施される。このプローブ 25 は、図示しない試験装置に接続されており、所定の試験信号を供給する構成とされている。

#### 【0047】

マザーチップ 3B に対して上記信頼性試験を実施するには、プローブ 25 をマザーチップ 3B のパッド 15 に突き刺し、これによりプローブ 25 とパッド 15 とを電気的に接続して試験を実施する。このプローブ 25 をパッド 15 に突き刺す際、パッド 15 には凹部が形成される。

#### 【0048】

このプローブ 25 がパッド 15 と接続する位置は、従来では特に精度を持たせておらず、プローブ 25 が必ずパッド 15 に接続するのに足る比較的低い精度とされていた。これに対して本実施例では、プローブ 25 がパッド 15 と接続される位置を高精度に位置決めする構成としている。

#### 【0049】

具体的には、プローブ 25 が移動する構成の場合には、プローブ 25 の移動装置の移動精度を高く設定し、またマザーチップ 3B を支持しているステージが移動する場合には、この移動ステージの移動精度を高く設定した構成としている。この構成とすることにより、プローブ 25 をパッド 15 上の既定位置に高精度に接続（突き刺す）ことができる。またこれに伴い、プローブ 25 を突き刺すことによりパッド 15 に形成される凹部の位置精度を向上させることができる。尚、このように高い位置精度を持って形成された凹部を、以下位置決め凹部 26 というものをとする。

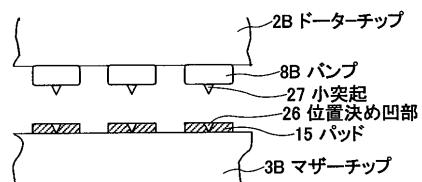

#### 【0050】

図15は、ドーターチップ 2B とマザーチップ 3B とを接合させるため、バンプ 8B とパッド 15 とを対向させた状態を示している。バンプ 8B はスタッドバンプであり、前記のようにワイヤーボンディング技術を利用して形成されたものである。このスタッドバンプは、その先端位置にワイヤーを切断するときに形成される小突起 27 を有している。

#### 【0051】

本実施例では、バンプ 8B に形成された小突起 27 と、パッド 15 に形成された位置決め凹部 26 とを位置決めして超音波接合を行なうことを行なうことを特徴としている。図16は、小突起 27 が位置決め凹部 26 に嵌入し、ドーターチップ 2B とマザーチップ 3B とが位置決めされた状態を示している。

#### 【0052】

前記したように、パッド 15 に形成される位置決め凹部 26 の位置精度は高精度とされている。また、小突起 27 もバンプ 8B の中央位置に精度よく形成されるものである。よって、位置決め凹部 26 と小突起 27 を位置決めして超音波接合処理を行なうことにより、バンプ 8B とパッド 15 の位置決めを精度よく行なうことができる。これにより、バンプ 8B とパッド 15 との位置ずれに起因して、隣接するバンプ 8B 間で短絡が発生するこ

10

20

30

40

50

とを防止することができる。よって、本実施例によつても、バンプ 8 B の狭ピッチ化を実現することができる。

#### 【0053】

尚、位置決め凹部 26 の位置精度に比較して、小突起 27 の位置精度は低くなることが考えられる。これは、小突起 27 の形成位置がバンプ 8 B の形状精度に影響を受けるからである。しかしながら、前記した図 7 乃至図 9 に示した半導体製造装置（キャピラリ 20 A, 20 B）を用いることにより、形成されるバンプ 8 B の形状精度を高めることができ、よつて高精度の位置決めを行なうことができる。

#### 【0054】

次に、本発明の第 5 実施例である半導体装置の製造方法について説明する。

10

#### 【0055】

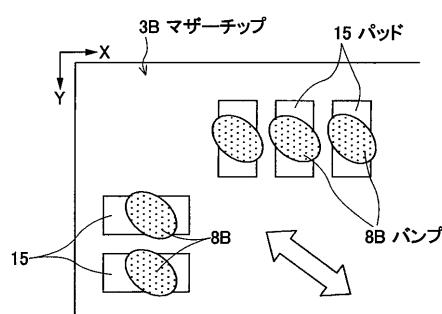

図 17 は、第 5 実施例である半導体装置の製造方法を説明するための図である。本実施例では、バンプ 8 B とパッド 15 とを接合する際に印加する超音波振動の振幅方向に特徴を有するものである。即ち、本実施例では、バンプ 8 B とパッド 15 とを超音波接合する際、超音波の振幅方向をバンプ 8 B 或いはパッド 15 の並び方向（図中、矢印 X, Y で示す方向）と異なる方向となるよう設定した。

#### 【0056】

同図に示す例では、超音波の振幅方向は X 方向から約 45° の角度となるよう設定されている。しかしながら、この超音波の振幅方向の角度は、これに限定されるものではなく、任意に設定することができるものである。

20

#### 【0057】

本実施例のように、超音波の振幅方向とバンプ 8 B, パッド 15 の並び方向（X, Y 方向）と異なる方向とすることにより、隣接するバンプ 8 B 間で短絡が発生するのを防止することができる。即ち、超音波振動によりバンプ 8 B が溶融すると、超音波の振幅方向にバンプ 8 B が延出する（変形する）現象が発生するが、超音波の振幅方向とバンプ 8 B の並び方向（X, Y 方向）と同一方向であると、隣接するバンプ間で短絡が生じるおそれがある（図 5 参照）。

#### 【0058】

しかしながら、本実施例のように超音波の振幅方向をバンプ 8 B の並び方向（X, Y 方向）と異ならせることにより、バンプ 8 B が溶融して延出したとしても、その延出方向は隣接するバンプ 8 B が近接する方向とは異なる方向となる。具体的には、図 17 に示すように、各バンプ 8 B が X, Y 方向に対して斜め方向に平行に列設した構成となる。このため、バンプ 8 B のピッチが狭ピッチ化しても、隣接するバンプ 8 B 間で短絡が発生するのを防止することができる。

30

#### 【0059】

次に、本発明の第 6 実施例である半導体装置の製造方法について説明する。

#### 【0060】

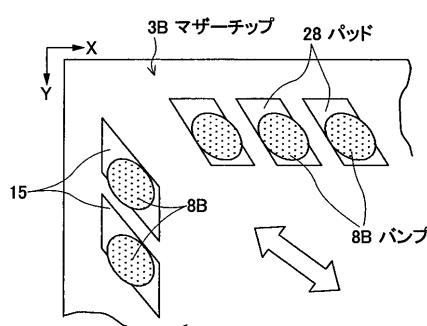

図 18 は、第 6 実施例である半導体装置の製造方法を説明するための図である。本実施例では、第 7 実施例と同様に、バンプ 8 B とパッド 28 とを超音波接合する際の超音波の振幅方向を、バンプ 8 B 或いはパッド 28 の並び方向（図中、矢印 X, Y で示す方向）と異なる方向となるよう設定している。これに加えて本実施例では、パッド 28 の延在方向が超音波の振幅方向と同一方向となるよう構成したことの特徴としている。

40

#### 【0061】

この構成とすることにより、前記した第 7 実施例の構成で実現できる効果に加え、バンプ 8 B とパッド 28 との接合面積を増大することができる。これにより、バンプ 8 B とパッド 28 との接合強度を向上させることができる。また、バンプ 8 B は、いわゆる濡れ性の高いパッド 28 に沿って延出するため、隣接方向（X, Y 方向）に対する変形量が小さくなる。よつて、本実施例の構成とすることによつても、バンプ 8 B が狭ピッチ化しても、隣接するバンプ 8 B 間で短絡が発生することを防止できる。

#### 【0062】

50

次に、本発明の第7実施例である半導体装置の製造方法について説明する。

【0063】

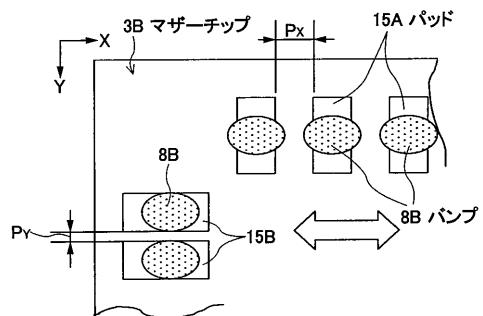

図19は、第7実施例である半導体装置の製造方法を説明するための図である。本実施例においては、超音波の振幅方向と同一方向（図中、矢印X方向）に延在するパッド15Aの配設ピッチ $P_x$ が、超音波の振幅方向と直交する方向（図中、矢印Y方向）に延在するパッド15Bの配設ピッチ $P_y$ に対して長く設定したこと（ $P_x > P_y$ ）を特徴としている。

【0064】

前記したように、バンプ8Bが超音波振動により溶融すると、超音波の振幅方向に延出する現象が発生する。このため、超音波の振幅方向と同一方向（本実施例ではX方向）に配設されたパッド15Aの配設ピッチ $P_x$ が狭いと、超音波接合の際に隣接するバンプ8B間で短絡が発生するおそれがある。これに対し、超音波の振幅方向と直交する方向（本実施例ではY方向）に配設されたパッド15Bは、その配設方向が溶融したバンプ8Bの延出方向と異なるため、配設ピッチ $P_y$ を狭ピッチとしても短絡のおそれはない。

10

【0065】

従って、本実施例のように超音波の振幅方向と同一方向（X方向）に配設されたパッド15Aの配設ピッチ $P_x$ を、超音波の振幅方向と直交する方向（Y方向）に配設されたパッド15Bの配設ピッチ $P_y$ に対して長く設定することにより、半導体装置の小型化（本実施例では、特にY方向の小型化）を図りつつ、隣接するバンプ8B間で短絡が発生するのを防止することができる。

20

【0066】

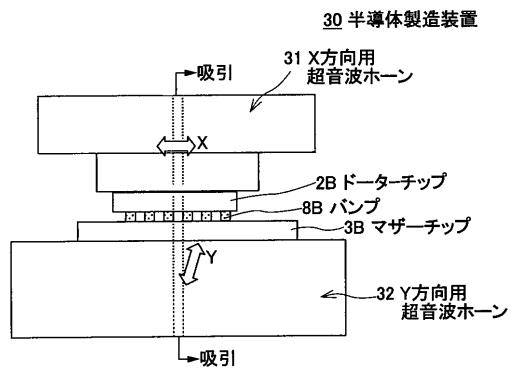

次に、本発明の第2実施例である半導体製造装置について説明する。

【0067】

図20は、第2実施例である半導体製造装置30を説明するための図である。前記した各実施例に係る半導体製造装置及び半導体装置の製造方法では、超音波振動を一方向にのみ印加してバンプ8Bをパッド15に超音波接合する構成とされていた。

20

【0068】

これに対して本実施例に係る半導体製造装置30は、バンプ8Bとパッド15とを超音波接合する際、異なる2方向に超音波振動を印加できる構成としたことを特徴とするものである。本実施例では、超音波振動の振幅方向が直交するX方向とY方向となるよう構成されている。このため、半導体製造装置30は、振幅方向がX方向である超音波振動を発生させるX方向超音波ホーン31と、振幅方向がY方向である超音波振動を発生させるY方向超音波ホーン32とを有した構成とされている。

30

【0069】

X方向超音波ホーン31は図示しない吸着手段に接続されており、よってドーターチップ2BはX方向超音波ホーン31に吸着される構成とされている。また、Y方向超音波ホーン32も図示しない吸着手段に接続されており、よってマザーチップ3BはY方向超音波ホーン32に吸着される構成とされている。

【0070】

そして、ドーターチップ2BをX方向超音波ホーン31に吸着し、マザーチップ3BをY方向超音波ホーン32に吸着した状態でドーターチップ2Bとマザーチップ3Bを近接させる。そして、バンプ8Bがマザーチップ3Bに当接した状態で、各超音波ホーン31, 32を駆動する。これによりドーターチップ2BはX方向超音波ホーン31によりX方向の振幅を有する超音波振動を行い、またマザーチップ3BはY方向超音波ホーン32によりY方向の振幅を有する超音波振動を行なう。

40

【0071】

このように、本実施例ではX方向超音波ホーン31による超音波振動の方向と、Y方向超音波ホーン32による超音波振動の方向とが異なるため、各方向（X, Y方向）への超音波振動の振幅を小さくしてもバンプ8Bとパッド15とを確実に接合することができる。このように、超音波振動の振幅を小さくできることにより、接合処理時にバンプ8B及

50

びパッド 15 が振動される振動量（移動量）も小さくできるため、バンプ 8B が狭ピッチ化しても、隣接する突起電極間で短絡が発生することを防止することができる。

#### 【0072】

特に本実施例では、各超音波ホーン 31, 32 が発生する超音波振動の振幅方向が直交するよう構成しているため、超音波接合処理時における各振動方向への振動量を最も小さくすることができ、隣接するバンプ 8B 間での短絡をより確実に防止することができる。

#### 【0073】

以上の説明に関し、更に以下の項を開示する。

(付記 1) 半導体チップに突起電極を形成する半導体製造装置において、

前記突起電極を所定形状に成形する成形治具を設けると共に、

該成形治具の前記突起電極を形成する位置に、該突起電極が形成治具の外部にはみ出すことを防止する突起部を形成したことを特徴とする半導体製造装置。

(付記 2) 付記 1 記載の半導体製造装置において、

前記突起電極をスタッドバンプとすると共に、

前記成形治具と前記スタッドバンプを形成するキャピラリとを一体化したことを特徴とする半導体製造装置。

(付記 3) 付記 1 または 2 記載の半導体製造装置において、

前記突起部の形状を円形、橢円形、及び矩形から選定される一の形状としたことを特徴とする半導体製造装置。

(付記 4) 半導体チップに設けられた突起電極を、該半導体チップが実装される被実装部材に設けられたパッドに接合する半導体製造装置において、

前記半導体チップを一の方向に超音波振動させる第 1 の超音波振動印加手段と、

前記被実装部材を前記半導体チップの超音波振動と異なる方向に超音波振動させる第 2 の超音波振動手段とを具備することを特徴とする半導体製造装置。

(付記 5) 付記 4 記載の半導体製造装置において、

前記半導体チップの超音波振動方向と、前記被実装部材の超音波振動方向が直交するよう構成したことを特徴とする半導体製造装置。

(付記 6) 半導体チップに設けられた突起電極を、該半導体チップが実装される被実装部材に設けられたパッドに接合する工程を有する半導体装置の製造方法において、

前記半導体チップに設けられた突起電極、または前記被実装部材に設けられたパッドの少なくとも一方に、前記接合時に変形可能な構成とされた可変形接合材を配設しておき、

前記突起電極と前記パッドとを前記可変形接合材を介して接合することを特徴とする半導体装置の製造方法。

(付記 7) 付記 6 記載の半導体装置の製造方法において、

隣接する前記突起電極の高さを異ならせたことを特徴とする半導体装置の製造方法。

(付記 8) 半導体チップに設けられた突起電極を、該半導体チップが実装される被実装部材に設けられたパッドに超音波接合する工程を有する半導体装置の製造方法において、

前記突起電極と前記パッドとを超音波接合する際、前記半導体チップへの超音波の振幅方向を前記突起電極の並び方向と異なる方向としたことを特徴とする半導体装置の製造方法。

(付記 9) 半導体チップに設けられた突起電極を、該半導体チップが実装される被実装部材に設けられたパッドに超音波接合する工程を有する半導体装置の製造方法において、

前記突起電極と前記パッドとを超音波接合する際、前記半導体チップへの超音波の振幅方向と、前記パッドの延在方向を同一方向としたことを特徴とする半導体装置の製造方法。

(付記 10) 半導体チップに設けられた突起電極を、該半導体チップが実装される被実装部材に設けられたパッドに超音波接合する工程を有する半導体装置の製造方法において、

超音波の振幅方向と同一方向に延在する前記パッドの配設ピッチが、前記超音波の振幅方向と直交する方向に延在する前記パッドの配設ピッチに対して長く設定したことを特徴とする半導体装置の製造方法。

10

20

30

40

50

(付記 11) 半導体チップに設けられたスタッドバンプを、該半導体チップが実装される被実装部材に設けられたパッドに接合する工程を有する半導体装置の製造方法において、

更に、プローブを前記パッドに刺すことにより電気的に接続し、該プローブを介して被実装部材の試験を行なう工程を設けると共に、

前記スタッドバンプを前記パッドに接合する際、前記被実装部材の試験を行なう工程で前記プローブにより前記パッドに形成された凹部と、前記スタッドバンプの先端部に形成された小突起とを位置決めして前記接合を行なうことを特徴とする半導体装置の製造方法。

(付記 12) 付記 6 乃至 11 記載の半導体装置の製造方法において、

前記被実装部材が、半導体チップであることを特徴とする半導体装置の製造方法。 10

#### 【図面の簡単な説明】

#### 【0074】

【図 1】図 1 は、本発明の対象とする半導体装置の断面図である（その 1）。

【図 2】図 2 は、本発明の対象とする半導体装置の断面図である（その 2）。

【図 3】図 3 は、従来の一例である半導体製造装置を示す図である。

【図 4】図 4 は、従来の問題点を説明するための図であり、ドーターチップの底面を示す図である。

【図 5】図 5 は、従来の問題点を説明するための図であり、隣接したバンプが短絡した状態を示す図である（その 1）。

【図 6】図 6 は、従来の問題点を説明するための図であり、隣接したバンプが短絡した状態を示す図である（その 2）。 20

【図 7】図 7 は、本発明の第 1 実施例である半導体装置の製造方法及び半導体製造装置を説明するための図である。

【図 8】図 8 は、本発明の第 1 実施例である半導体製造装置に設けられるキャピラリを拡大して示す図である。

【図 9】図 9 は、図 8 に示すキャピラリの変形例を示す図である。

【図 10】図 10 は、本発明の第 2 実施例である半導体装置の製造方法を説明するための図であり、チップ接合前の状態を示す図である。

【図 11】図 11 は、本発明の第 2 実施例である半導体装置の製造方法を説明するための図であり、チップ接合後の状態を示す図である。 30

【図 12】図 12 は、本発明の第 3 実施例である半導体装置の製造方法の変形例を説明するための図であり、チップ接合前の状態を示す図である。

【図 13】図 13 は、本発明の第 3 実施例である半導体装置の製造方法の変形例を説明するための図であり、チップ接合後の状態を示す図である。

【図 14】図 14 は、本発明の第 4 実施例である半導体装置の製造方法を説明するための図であり、チップに対し試験を行っている状態を示す図である。

【図 15】図 15 は、本発明の第 4 実施例である半導体装置の製造方法を説明するための図であり、チップ接合前の状態を示す図である。

【図 16】図 16 は、本発明の第 5 実施例である半導体装置の製造方法を説明するための図であり、チップ接合後の状態を示す図である。 40

【図 17】図 17 は、本発明の第 6 実施例である半導体装置の製造方法を説明するための図であり、マザーチップ上のパッドとバンプとの接合状態を示す図である。

【図 18】図 18 は、本発明の第 7 実施例である半導体装置の製造方法を説明するための図であり、マザーチップ上のパッドとバンプとの接合状態を示す図である。

【図 19】図 19 は、本発明の第 8 実施例である半導体装置の製造方法を説明するための図であり、マザーチップ上のパッドとバンプとの接合状態を示す図である。

【図 20】図 20 は、本発明の第 2 実施例である半導体製造装置を説明するための図である。

#### 【符号の説明】

#### 【0075】

- 1A, 1B 半導体装置

2A, 2B ドーテーチップ

3A, 3B マザーチップ

8A, 8B バンプ

15, 28 パッド

16 振動体

20A, 20B キャピラリ

21A, 21B 突起部

22A, 22B 成型凹部

23 可変形接合材

25 プローブ

26 位置決め凹部

27 小突起

30 半導体製造装置

31 X方向超音波ホーン

32 Y方向超音波ホーン

10

【図1】

【図2】

【図3】

従来の一例である半導体製造装置を示す図

【図4】

従来の問題点を説明するための図であり、ドーテーチップの底面を示す図

【図5】

従来の問題点を説明するための図であり、隣接したバンプが短絡した状態を示す図(その1)

【図6】

従来の問題点を説明するための図であり、隣接したバンプが短絡した状態を示す図(その2)

【図7】

本発明の第1実施例である半導体装置の製造方法及び半導体製造装置を説明するための図

【図8】

本発明の第1実施例である半導体製造装置に設けられるキャピラリを拡大して示す図

【図9】

図8に示すキャピラリの変形例を示す図

【図10】

本発明の第2実施例である半導体装置の製造方法を説明するための図であり、チップ接合前の状態を示す図

【図11】

本発明の第2実施例である半導体装置の製造方法を説明するための図であり、チップ接合後の状態を示す図

【図12】

本発明の第2実施例である半導体装置の製造方法の変形例を説明するための図であり、チップ接合前の状態を示す図

【図13】

本発明の第2実施例である半導体装置の製造方法の変形例を説明するための図であり、チップ接合後の状態を示す図

【図14】

本発明の第3実施例である半導体装置の製造方法を説明するための図であり、チップに対し試験を行なっている状態を示す図

【図15】

本発明の第3実施例である半導体装置の製造方法を説明するための図であり、チップ接合前の状態を示す図

【図16】

本発明の第3実施例である半導体装置の製造方法を説明するための図であり、チップ接合後の状態を示す図

【図17】

本発明の第4実施例である半導体装置の製造方法を説明するための図であり、マザーチップ上のパッドとバンプとの接合状態を示す図

【図18】

本発明の第5実施例である半導体装置の製造方法を説明するための図であり、マザーチップ上のパッドとバンプとの接合状態を示す図

【図19】

本発明の第6実施例である半導体装置の製造方法を説明するための図であり、マザーチップ上のパッドとバンプとの接合状態を示す図

【図20】

本発明の第2実施例である半導体製造装置を説明するための図

---

フロントページの続き

(72)発明者 埼本 隆司

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 夏秋 昌典

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

F ターム(参考) 5F044 KK17 KK18 LL00 LL13 QQ03