(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-284551

(P2006-284551A)

(43) 公開日 平成18年10月19日(2006.10.19)

(51) Int.C1.

GO1C 19/56 (2006.01)

GO1P 9/04 (2006.01)

F1

GO1C 19/56

GO1P 9/04

テーマコード(参考)

2F105

審査請求 未請求 請求項の数 23 O L (全 65 頁)

(21) 出願番号 特願2005-374325 (P2005-374325)

(22) 出願日 平成17年12月27日 (2005.12.27)

(31) 優先権主張番号 特願2005-47802 (P2005-47802)

(32) 優先日 平成17年2月23日 (2005.2.23)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2005-50962 (P2005-50962)

(32) 優先日 平成17年2月25日 (2005.2.25)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2005-66051 (P2005-66051)

(32) 優先日 平成17年3月9日 (2005.3.9)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100072350

弁理士 飯阪 泰雄

(72) 発明者 稲熊 輝往

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 高橋 和夫

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 佐々木 伸

宮城県登米郡中田町宝江新井田字加賀野境

30番地 ソニー宮城株式会社内

最終頁に続く

(54) 【発明の名称】振動型ジャイロセンサ

## (57) 【要約】

【課題】簡易な構成によって小型化と高Q値を得ることで特性の向上を図る。

【解決手段】本発明の振動型ジャイロセンサ1は、回路素子が実装されるとともに複数個のランド4を有する配線パターンが形成された支持基板2と、この支持基板の表面2-1に実装された振動素子20とを備え、振動素子20は、上記ランドに接続される複数の端子部25が形成された実装面22-2を有する基部22と、この基部22の側周部から片持ち梁状に一体に突設され基部22の実装面と同一面を構成し第1電極層27とこの第1電極層の上に積層された圧電層28とこの圧電層の上に積層された第2電極層29, 30とがそれぞれ形成された基板対向面を有する振動子部23とを有するとともに、振動素子20は、各端子部25が金属凸部26を介してランド4に接合されることによって支持基板2上に実装されている。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

回路素子が実装されるとともに複数個のランドを有する配線パターンが形成された支持基板と、この支持基板の表面に実装された振動素子とを備えた振動型ジャイロセンサにおいて、

前記振動素子は、

前記ランドに接続される複数の端子部が形成された実装面を有する基部と、

この基部の側周部から片持ち梁状に一体に突設され前記基部の実装面と同一面を構成し第1電極層とこの第1電極層の上に積層された圧電層とこの圧電層の上に積層された第2電極層とがそれぞれ形成された基板対向面を有する振動子部とを有するとともに、

前記振動素子は、前記各端子部が金属凸部を介して前記ランドに接合されることによって前記支持基板上に実装されている

ことを特徴とする振動型ジャイロセンサ。

**【請求項 2】**

前記金属凸部は、前記各端子部に設けられて前記ランドに溶着される金バンプであることを特徴とする請求項1に記載の振動型ジャイロセンサ。

**【請求項 3】**

前記金バンプは多段バンプからなる

ことを特徴とする請求項2に記載の振動型ジャイロセンサ。

**【請求項 4】**

前記基部の実装面には、ダミーバンプが設けられている

ことを特徴とする請求項1に記載の振動型ジャイロセンサ。

**【請求項 5】**

前記振動子部の上面は、前記基部の上面から傾斜部を介して段落ち形成されており、前記金属凸部は、前記傾斜部の非形成領域に対応する前記実装面上の領域に設けられている

ことを特徴とする請求項1に記載の振動型ジャイロセンサ。

**【請求項 6】**

前記基部の実装面には、前記振動子部の基端部位と、前記複数の端子部のうち少なくとも前記振動子部側に位置する端子部との間を跨ぐように、溝部が形成されている

ことを特徴とする請求項1に記載の振動型ジャイロセンサ。

**【請求項 7】**

前記溝部の一端部は、前記基部の側周部に臨んでいる

ことを特徴とする請求項6に記載の振動型ジャイロセンサ。

**【請求項 8】**

前記支持基板には、前記振動子部の基板対向面と対向する領域に、前記振動子部の厚み方向に自由振動させる空間部を構成する凹部が形成されている

ことを特徴とする請求項1に記載の振動型ジャイロセンサ。

**【請求項 9】**

前記凹部は、前記振動子部の振動動作によって生じる空気流のダンピング効果に対して前記振動子部の変位減衰割合を所期値に保持する高さをもって形成されている

ことを特徴とする請求項8に記載の振動型ジャイロセンサ。

**【請求項 10】**

前記支持基板には、前記回路素子が実装されるとともに、複数の前記振動素子が、各々の振動子部を互いに異なる軸方向に向けて実装されている

ことを特徴とする請求項1に記載の振動型ジャイロセンサ。

**【請求項 11】**

前記回路素子はIC部品であり、前記複数の振動素子の実装領域間を結ぶ直線の中間領域が当該IC部品の主要実装領域とされている

ことを特徴とする請求項10に記載の振動型ジャイロセンサ。

10

20

30

40

50

**【請求項 1 2】**

回路素子が実装されるとともに複数個のランドを有する配線パターンが形成された支持基板と、この支持基板の表面に実装された振動素子とを備えた振動型ジャイロセンサにおいて、

前記振動素子は、

前記ランドに接続される複数の端子部が形成された実装面を有する基部と、

この基部の側周部から片持ち梁状に一体に突設され前記基部の実装面と同一面を構成し第1電極層とこの第1電極層の上に積層された圧電層とこの圧電層の上に積層された第2電極層とがそれぞれ形成された基板対向面を有する振動子部とを有するとともに、

前記振動素子は、前記各端子部が金属凸部を介して前記ランドに接合されることによって前記支持基板上に実装されており、

前記支持基板は、前記振動素子及び前記回路素子が実装される第1主面と、外部の制御基板と電気的に接続される複数の外部接続端子部が形成された第2主面とを備えていることを特徴とする振動型ジャイロセンサ。

**【請求項 1 3】**

前記支持基板の第1主面及び第2主面のうち少なくとも一方の主面には、外部負荷を緩衝する負荷緩衝溝が形成されている

ことを特徴とする請求項1 2に記載の振動型ジャイロセンサ。

**【請求項 1 4】**

前記負荷緩衝溝は、前記振動素子の実装領域を囲むようにして形成されている

20

ことを特徴とする請求項1 3に記載の振動型ジャイロセンサ。

**【請求項 1 5】**

前記負荷緩衝溝は、前記回路素子の実装領域を囲むようにして形成されている

ことを特徴とする請求項1 3に記載の振動型ジャイロセンサ。

**【請求項 1 6】**

前記負荷緩衝溝は、100 μm以上の深さ寸法をもって形成されている

ことを特徴とする請求項1 3に記載の振動型ジャイロセンサ。

**【請求項 1 7】**

前記振動素子は、前記外部接続端子部の形成領域よりも前記支持基板の外周側に実装されている

30

ことを特徴とする請求項1 2に記載の振動型ジャイロセンサ。

**【請求項 1 8】**

前記複数の外部接続端子部は、前記支持基板の第2主面上の同一円周上を各々の主要形成領域とされている

ことを特徴とする請求項1 7に記載の振動型ジャイロセンサ。

**【請求項 1 9】**

前記複数の外部接続端子部は、前記支持基板の第2主面上の同一円周上を各々の主要形成領域とされており、前記振動素子は、当該円周上の前記外部接続端子部の非形成領域に実装されている

ことを特徴とする請求項1 2に記載の振動型ジャイロセンサ。

40

**【請求項 2 0】**

前記支持基板の第1主面は、遮光性のカバー部材で覆われている

ことを特徴とする請求項1 2に記載の振動型ジャイロセンサ。

**【請求項 2 1】**

前記外部接続端子部と前記制御基板との間には、負荷緩衝層が設けられている

ことを特徴とする請求項1 2に記載の振動型ジャイロセンサ。

**【請求項 2 2】**

前記負荷緩衝層は、異方性導電フィルムである

ことを特徴とする請求項2 1に記載の振動型ジャイロセンサ。

**【請求項 2 3】**

50

前記負荷緩衝層は、前記外部接続端子部と前記制御基板との間に配置されたフレキシブル配線基板である

ことを特徴とする請求項21に記載の振動型ジャイロセンサ。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、例えば、ビデオカメラの手振れ検知やバーチャルリアリティ装置における動作検知、カーナビゲーションシステムにおける方向検知などに用いられる角速度センサに関する。 10

##### 【背景技術】

##### 【0002】

従来より、民生用の角速度センサとしては、片持ち梁の振動子を所定の共振周波数で振動させておき、角速度の影響によって生じるコリオリ力を圧電素子などで検出することによって角速度を検出する、いわゆる振動型のジャイロセンサが広く用いられている。

##### 【0003】

振動型ジャイロセンサは、単純な機構、短い起動時間、安価で製造可能といった利点を有しており、例えば、ビデオカメラ、バーチャルリアリティ装置、カーナビゲーションシステムなどの電子機器に搭載され、それぞれ手振れ検知、動作検知、方向検知などをする際のセンサとして活用されている。 20

##### 【0004】

従来の振動型ジャイロセンサは、振動素子が適宜の圧電材料を機械加工によって切り出し所定の形状に整形して製作されていた。振動型ジャイロセンサとしては、搭載される本体機器の小型軽量化、多機能高性能化に伴って、更なる小型化や高性能化が要求されているが、機械加工による加工精度の限界によって小型で高精度の振動素子を作製することが困難であった。

##### 【0005】

そこで、近年、半導体プロセスに適用される薄膜技術を用いて、シリコン基板上に圧電薄膜層を挟んで一対の電極層を積層形成することによって、片持ち梁形状の振動素子を備えたものが提案されている（例えば特許文献1参照）。かかる振動型ジャイロセンサは、小型薄型化が図られることによって、他用途のセンサ等と組み合わせて複合化や高機能化が図られる。 30

##### 【0006】

#### 【特許文献1】特開平7-113643号公報

##### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0007】

ところで、振動型ジャイロセンサにおいては、搭載機器の小型軽量化、多機能高性能化に伴って、更なる小型化や高性能化が要求されている。例えば各種センサと組み合わせて多機能化が図られており、振動素子を支持基板に実装して振動型ジャイロセンサを構成し、更にこの振動型ジャイロセンサを各種センサとともに本体機器側の制御基板に搭載することによって全体として小型化が図られている。 40

##### 【0008】

しかしながら、従来の振動型ジャイロセンサにおいては、振動素子の各電極と支持基板側の端子部とが一般にワイヤボンディング法によって接続されており、振動素子の周囲にワイヤを引き回すためのスペースが必要で、これが小型化の実現を阻害する要因となっている。

##### 【0009】

また、振動型ジャイロセンサは、小型化に伴って外部の振動等の影響を大きく受けるよ 50

うになり、振動素子の支持構造等の複雑化に伴いコストがアップするといった問題が生じる。振動型ジャイロセンサにおいては、設置の状態が機器の仕様によって決定されることから、あらゆる状態で用いられる場合でも所定の特性が安定して得られるように構成されなければならない。振動型ジャイロセンサにおいては、高感度で安定した特性を得るために、振動素子の共振状態を定義する機械品質係数Q値(Q factor)を高くする必要がある。機械品質係数Q値は、振動素子の材料や固定構造によって決定される。

#### 【0010】

本発明は上述の問題に鑑みてなされ、簡易な構成によって小型化と高Q値を得ることで特性の向上を図った振動型ジャイロセンサを提供することを課題とする。

#### 【課題を解決するための手段】

#### 【0011】

以上の課題を解決するに当たり、本発明の振動型ジャイロセンサは、回路素子が実装されるとともに複数個のランドを有する配線パターンが形成された支持基板と、この支持基板の表面に実装された振動素子とを備えた振動型ジャイロセンサにおいて、上記振動素子は、上記ランドに接続される複数の端子部が形成された実装面を有する基部と、この基部の側周部から片持ち梁状に一体に突設され上記基部の実装面と同一面を構成し第1電極層とこの第1電極層の上に積層された圧電層とこの圧電層の上に積層された第2電極層とがそれぞれ形成された基板対向面を有する振動子部とを有するとともに、上記振動素子は、上記各端子部が金属凸部を介して上記ランドに接合されることによって上記支持基板上に実装されている。

#### 【0012】

本発明の振動型ジャイロセンサにおいては、各金属凸部が例えば金パンプや、振動素子の基部から一体に突出された凸部等によって形成される。これら金属凸部を介して振動素子の各端子部が支持基板上のランドに接合されることによって、振動素子が支持基板に対して電気的接続が行われるとともに機械的に固定されることで、実装スペースの効率化が図れるようになる。

#### 【0013】

本発明の振動型ジャイロセンサにおいては、支持基板側から振動素子に対して所定周波数の交流電界を印加することにより振動子部を固有振動を生じさせ、手振れ等により振動子部に生じたコリオリ力を電気的に検出しその検出信号を出力する。本発明では、振動素子が基部から振動子部を片持ち梁状に一体に形成した片持ち梁状に構成されているとともに、金属凸部を介して支持基板から浮かせた状態で固定されることから、振動子部の変位減衰割合が低減されて高Q値化が図られる。

#### 【0014】

一方、振動型ジャイロセンサにおいては、外部から加えられる振動や衝撃、更に本体機器側の制御基板への接合時に発生する熱応力等の外部負荷の影響を強く受ける。このような外部負荷によって支持基板に発生する歪みや応力を吸収あるいは緩和する負荷緩衝構造があると好ましい。

#### 【0015】

負荷緩衝構造としては、例えば、支持基板上の振動素子実装領域を囲むようにして形成した負荷緩衝溝や、振動素子の基部の実装面に対し振動子部の基端部位と各端子部との間を跨ぐようにして形成した溝部、あるいは、支持基板と本体機器側の制御基板との間に設けた負荷緩衝層等が該当する。この負荷緩衝構造を設けることにより、振動素子の安定した振動動作を確保して検出精度の向上が図れるようになる。

#### 【発明の効果】

#### 【0016】

本発明の振動型ジャイロセンサによれば、振動素子は、金属凸部を介して支持基板上に実装されているので、小型化とともに高Q値化が図られて高感度で安定した特性を得ることができる。

#### 【0017】

10

20

30

40

50

また、負荷緩衝構造を設けることで外部負荷からの影響を緩和することが可能となり、これにより、振動素子の安定した検出動作と高い検出精度を得ることができる。

#### 【発明を実施するための最良の形態】

##### 【0018】

以下、本発明の実施の形態として図面に示した振動型ジャイロセンサについて、詳細に説明する。

なお、本発明はこれに限定されることなく、本発明の技術的思想に基づいて種々の変形が可能である。また、本明細書においては、以下に説明するように構成部材の各部位について具体的な寸法値を挙げて説明しているが、各寸法値は中心基準値である。各部位は、この中心基準値に限定された寸法値で形成されることに限定されず、一般的な公差範囲の寸法値をもって形成されることは勿論である。また、振動型ジャイロセンサは、かかる寸法値の形状に限定されず、特性仕様に応じて各部が適宜形成される。

##### 【0019】

###### (第1の実施の形態)

###### [振動型ジャイロセンサの概略構成]

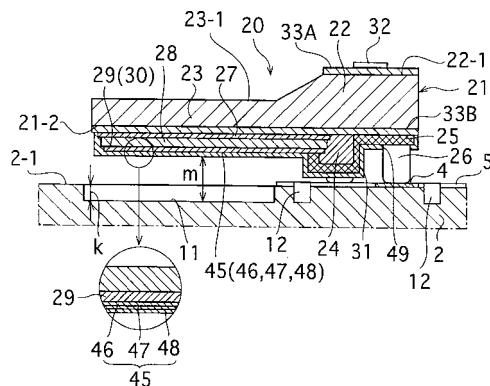

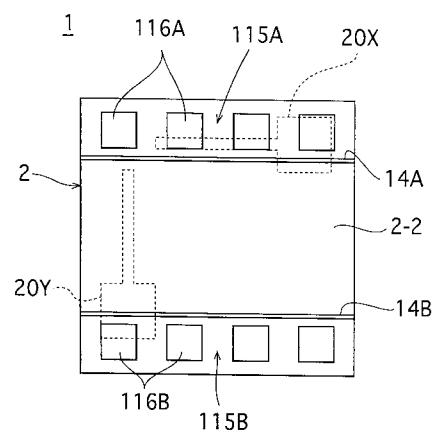

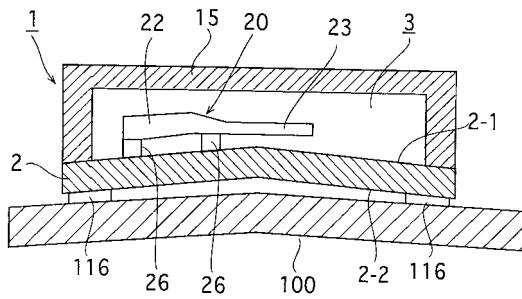

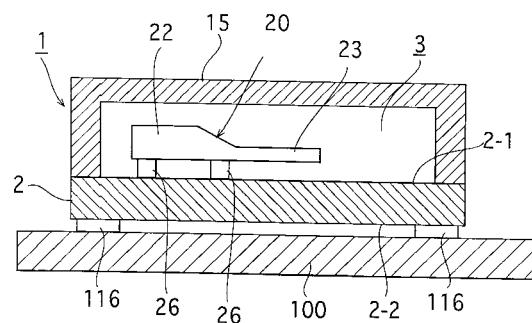

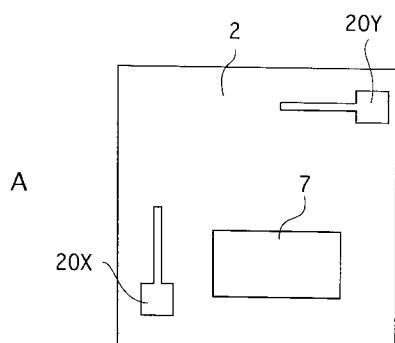

振動型ジャイロセンサ1は、図1に示すように支持基板2と、この支持基板2の第1主面2-1上に組み付けられて部品実装空間部3を構成するカバー部材15とにより外観部材を構成し、例えばビデオカメラに搭載されて手振れ補正機構を構成する。また、振動型ジャイロセンサ1は、例えばバーチャルリアリティ装置に用いられて動作検知器を構成し、或いはカーナビゲーション装置に用いられて方向検知器を構成する。

##### 【0020】

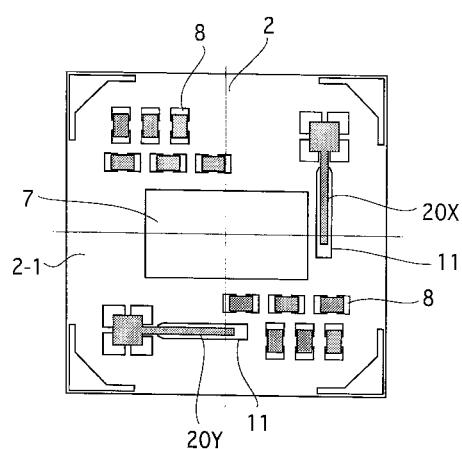

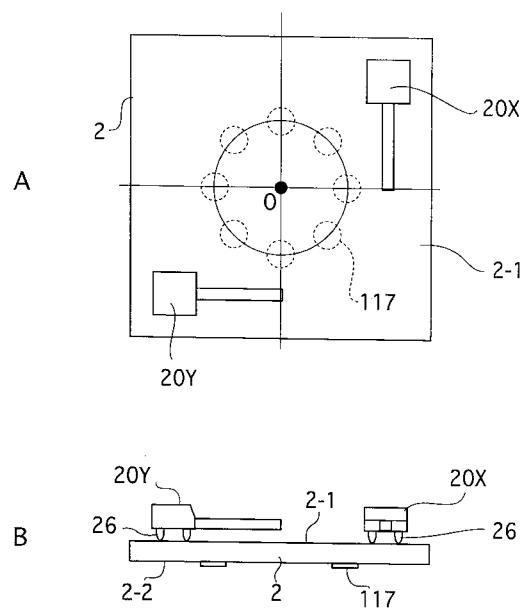

振動型ジャイロセンサ1は、支持基板2に例えばセラミック基板やガラス基板等が用いられている。支持基板2の第1主面2-1上には複数個のランド4等を有する所定の配線パターン5が形成されて部品実装領域6が構成されている。部品実装領域6には、詳細を後述する互いに異なる軸方向の振動を検出するように搭載される第1、第2の一対の振動素子20X、20Y(以下、個別に説明する場合を除いて振動素子20と総称する。)、IC回路素子7、更には外付け用の多数個のセラミックコンデンサや適宜の電子部品8が混載されている。

##### 【0021】

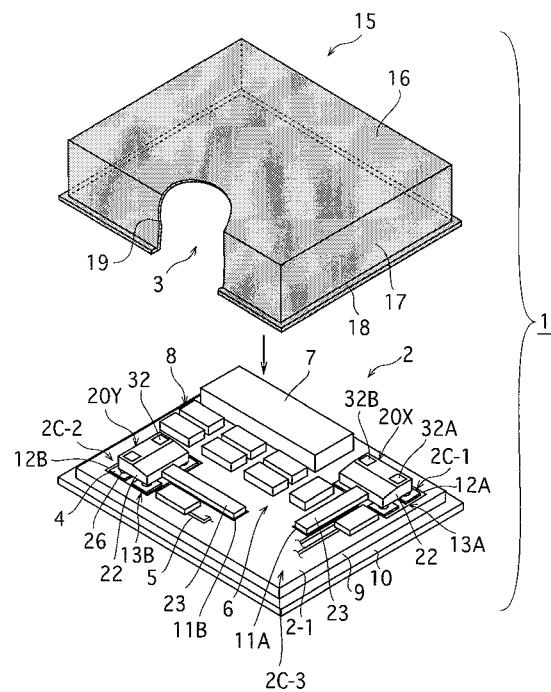

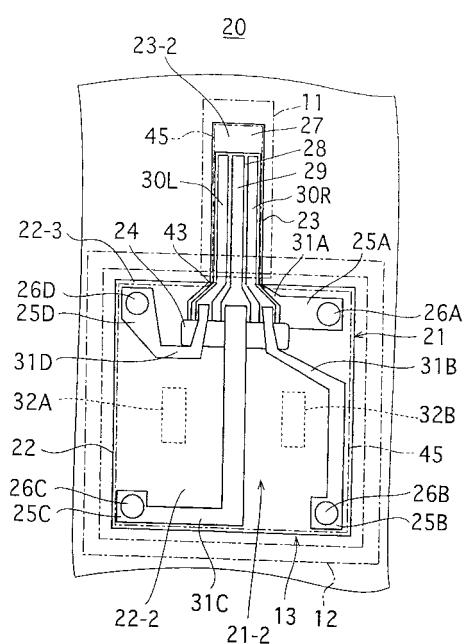

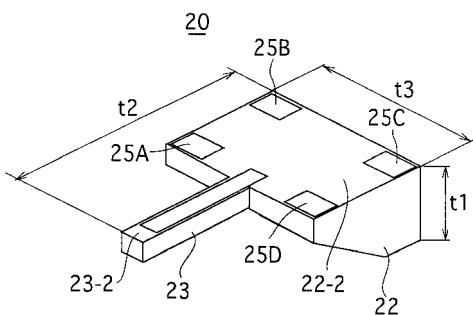

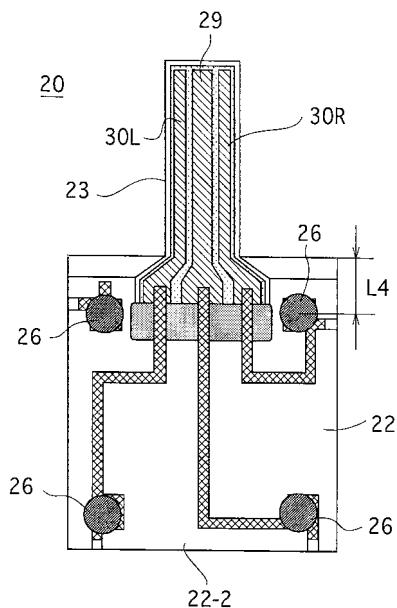

支持基板2の部品実装領域6には、IC回路素子7や電子部品8とともに振動素子20が適宜の実装機を用いてそれぞれフリップチップ法等の表面実装法によって実装されている。同一形状に形成された一対の振動素子20X、20Yは、支持基板2の第1主面2-1の相対するコーナ部位2C-1、2C-2に位置して互いに軸線を異にして実装されている。振動素子20は、図2に示すように、金パンプ26を介してランド4に接続される複数の端子部25が形成された実装面を有する基部22と、この基部22の一側周部から片持ち梁状に一体に突設された振動子部23とを有する。なお、振動素子20の構成の詳細は後述する。

##### 【0022】

図1に示すように、一方の第1振動素子20Xは、支持基板2のコーナ部位2C-1において部品実装領域6に構成した浮島状の第1振動素子実装領域13Aに基部22が固定され、この基部22から一体に突設された振動子部23が支持基板2の側縁に沿って隣り合うコーナ部位2C-3に向けられる。他方の第2振動素子20Yは、支持基板2のコーナ部位2C-2において部品実装領域6に構成した浮島状の第2振動素子実装領域13Bに基部22が固定され、この基部22から一体に突設された振動子部23が支持基板2の側縁に沿って隣り合うコーナ部位2C-3に向けられる。

##### 【0023】

すなわち、第1振動素子20X及び第2振動素子20Yは、各々の振動子部23をコーナ部位2C-3に向けて互いに90°の角度を付されて支持基板2にそれぞれ実装されている。なお、振動型ジャイロセンサ1は、一対の振動素子20X、20Yにより直交する2軸の振動検出を行うようとするが、本体機器の仕様に応じて適宜の角度差をもって振動

10

20

30

40

50

素子 20 X, 20 Y を支持基板 2 に実装するようにしてもよいことは勿論である。

【0024】

振動型ジャイロセンサ 1 は、振動素子 20 の振動子部 23 を共振させた状態において、振動子部 23 に加えられた長手方向の周りの角速度を検出する。振動型ジャイロセンサ 1 においては、第 1 振動素子 20 X と第 2 振動素子 20 Y とを支持基板 2 に角度を異にして搭載することによって、X 軸方向と Y 軸方向の角速度を同時に検出し、例えばビデオカメラの手振れによる振動状態に基づく制御信号を出力して手振れ補正機構を構成する。

【0025】

次に、支持基板 2 の構成の詳細について説明する。

【0026】

【負荷緩衝構造】

振動型ジャイロセンサ 1 は、支持基板 2 を薄厚とすることによって小型、薄型化が図られていることから、外部から加えられる振動や衝撃等の外部負荷によって支持基板 2 に歪みや応力が発生することがある。そこで、本実施の形態では、支持基板 2 に外部負荷の緩衝構造が設けられることによって、歪みや応力が生じた場合でも支持基板 2 に搭載した振動素子 20 への影響が低減されるように構成されている。

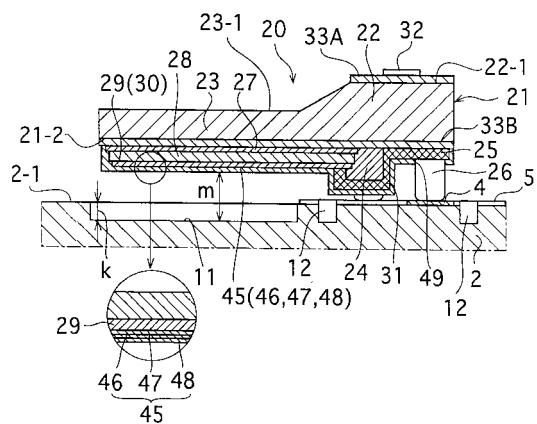

【0027】

支持基板 2 には、図 1 から図 3 に示すように第 1 主面 2-1 の各コーナ部位 2C-1, 2C-2 に第 1 負荷緩衝溝部 12A, 12B (以下、個別に説明する場合を除いて第 1 負荷緩衝溝部 12 と総称する。) が形成されている。上述の振動素子実装領域 13A, 13B (以下、個別に説明する場合を除いて振動素子実装領域 13 と総称する。) は第 1 負荷緩衝溝部 12 によって囲まれた領域に構成されており、各振動素子実装領域 13 に振動素子 20 が実装される。

【0028】

また、支持基板 2 には、図 3 に示すように、本体機器等の外部の制御基板 100 に実装される第 2 主面 2-2 側に第 2 負荷緩衝溝部 14 が形成されている。この第 2 負荷緩衝溝部 14 は、図 5 に示すように第 2 負荷緩衝溝部 14A と第 2 負荷緩衝溝部 14B とからなり、以下個別に説明する場合を除いて第 2 負荷緩衝溝部 14 と総称する。第 2 負荷緩衝溝部 14 によって囲まれた領域は、図 5 に示すように端子形成領域 115A, 115B (以下、個別に説明する場合を除いて端子形成領域 115 と総称する。) として構成されている。

【0029】

第 1 負荷緩衝溝部 12 は、図 4 に示すように振動素子 20 の基部 22 の外形寸法よりも大きな振動素子実装領域 13 を構成する全体枠状の有底溝によって構成されている。第 1 負荷緩衝溝部 12 は、例えばダイサー等による機械的溝加工やウェットエッティング法による化学的溝加工或いはレーザ等によるドライエッティング法により形成される。第 1 負荷緩衝溝部 12 は、支持基板 2 の機械的強度を損なわない範囲で溝の深さを 100  $\mu\text{m}$  以上にして形成される (詳細は図 5-2 を参照して後述する)。

【0030】

第 2 負荷緩衝溝部 14A, 14B は、図 5 に示すように、それぞれ支持基板 2 の外周側縁部に沿って平行に形成されている。これら第 2 負荷緩衝溝部 14A, 14B と外周側縁部との間の領域には、端子形成領域 115A, 115B としてそれぞれに外部接続用端子部として複数個の実装端子部 116A, 116B (以下、個別に説明する場合を除いて実装端子部 116 と総称する。) が適宜に配列して形成されている。支持基板 2 は、各実装端子部 116 にそれぞれ設けたバンプ 117 を介して実装端子部 (外部接続端子部) 116 が相対する制御基板 100 側のランドと接続されることによって、制御基板 100 に実装される。

【0031】

第 2 負荷緩衝溝部 14 は、第 1 負荷緩衝溝部 12 と同様に、例えばダイサー等による機械的溝加工やウェットエッティング法による化学的溝加工或いはレーザ等によるドライエッ

10

20

30

40

50

チング法等によって支持基板2の第2主面2-2に所定の深さをもって形成される。第2負荷緩衝溝部14は、支持基板2の第2主面2-2において浮島状の端子形成領域115を構成し、この端子形成領域115に外周側縁部に沿って複数個の実装端子部116が配列して形成されるようとする。なお、第2負荷緩衝溝部14は、外周側縁部に沿った直線溝に限定されず、例えば実装端子部116を囲む枠状や両端を外周側縁部に開放された略コ字状に形成するようとしてもよい。

#### 【0032】

なお、支持基板2には、第1主面2-1と第2主面2-2とを貫通して多数個のビアが形成されており、これらビアを介して第1主面2-1側の配線パターン5と第2主面2-2側の実装端子部116とが適宜接続される。

10

#### 【0033】

振動型ジャイロセンサ1は、本体機器に衝撃等が加えられると、制御基板100を介して支持基板2に歪みや応力が発生する。本実施の形態では、上述したように第1負荷緩衝溝部12によって囲まれて浮島状態とされた振動素子実装領域13上に振動素子20を実装したことで、外部負荷により支持基板2に生じた歪みや応力が第1負荷緩衝溝部12によって吸収される。したがって、第1負荷緩衝溝部12は一種のダンパー作用を奏することで振動素子実装領域13上に実装した振動素子20に対する外部負荷の影響を低減し、振動素子20が安定した状態で検出動作を行うようとする。

#### 【0034】

一方、振動型ジャイロセンサ1においては、上述したように第2負荷緩衝溝部14を設けて浮島状態とした端子形成領域115に設けられた実装端子部116が制御基板100との固定部を構成する。本実施の形態では、制御基板100を介して伝達される外部負荷が第2負荷緩衝溝部14によって吸収される。したがって、第2負荷緩衝溝部14は一種のダンパー作用を奏することで振動素子実装領域13上に実装した振動素子20に対する外部負荷の影響を低減し、振動素子20が安定した状態で検出動作を行うようとする。

20

#### 【0035】

なお、第1負荷緩衝溝部12は、全周に亘って連続した断面コ字状の溝部によって構成されるが、これに限定されない。第1負荷緩衝溝部12は、所定の特性を満たすことを条件に、例えば多数個の溝部を全体として枠状に配列して構成するようとしてもよい。また、第2負荷緩衝溝部14も、連続した溝部によって構成される必要はなく、例えば多数個の溝部を配列して構成するようとしてもよい。更に、支持基板2の第1主面2-1に第1負荷緩衝溝部12を形成するとともに第2主面2-2に第2負荷緩衝溝部14を形成して表裏主面の負荷緩衝構造を構成するようにしたが、所定の特性を有することを条件に第1負荷緩衝溝部12のみ又は第2負荷緩衝溝部14のみによって負荷緩衝構造を構成するようとしてもよい。

30

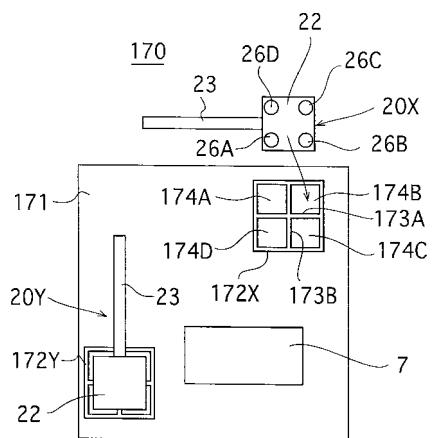

#### 【0036】

なお、上述したように支持基板2の第1主面2-1に振動素子実装領域13を囲む枠状の第1負荷緩衝溝部12を形成したが、この第1負荷緩衝溝部12の構成はこれに限定されるものではない。図6に示した振動型ジャイロセンサ170は、支持基板171に枠状の第1負荷緩衝溝部172X, 172Yを形成しているが、さらにこの第1負荷緩衝溝部172内に十字状の区割り溝173A, 173Bを形成して4つの個別実装領域174A~174Dを構成している。

40

#### 【0037】

すなわち、振動型ジャイロセンサ170は、各個別実装領域174がそれぞれ振動素子20の基部22に形成した端子部25と対応して個別に区割りされており、図示しないがそれぞれに実装端子部が設けられている。振動型ジャイロセンサ170においては、かかる構造によって、金パンプ26を介して相対する実装端子部に各端子部25を固定されて支持基板171に実装される振動素子20が、全体を第1負荷緩衝溝部172によって囲まれた第1浮島内において各固定部毎に区割り溝173によって区割りされた第2浮島内に個別に固定されて実装される。したがって、振動型ジャイロセンサ170においては、

50

振動素子 20 が、外部負荷により発生する支持基板 171 の歪みや応力の影響をより確実に低減されて安定した角速度の検出動作が行われるようにする。

【0038】

[間隔構成凹部]

次に、支持基板 2 には、振動素子 20X, 20Y に対応して部品実装領域 6 に、振動子部 23 をその厚さ方向に自由振動させる空間部を構成する凹部 11A, 11B (以下、個別に説明する場合を除いて間隔構成凹部 11 と総称する。) が形成されている。間隔構成凹部 11 は、支持基板 2 の第 1 主面 2-1 に対して例えばエッチング加工や溝切り加工を施すことで所定の深さと開口寸法を有する矩形の有底溝状に形成される。

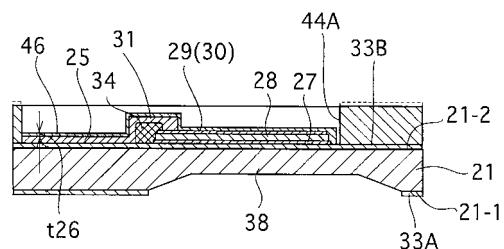

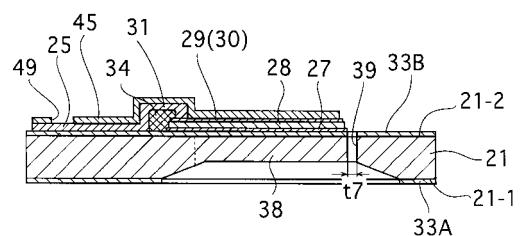

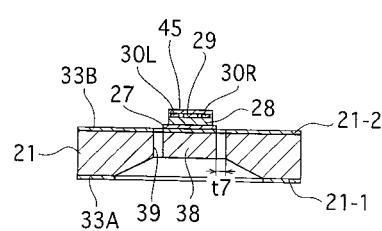

【0039】

振動型ジャイロセンサ 1 は、基部 22 と片持ち梁状の振動子部 23 とが一体に形成された振動素子 20 が、金バンプ 26 を介して支持基板 2 の第 1 主面 2-1 上に実装される。振動素子 20 は、金バンプ 26 の厚みにより振動子部 23 と支持基板 2 の第 1 主面 2-1 との対向間隔が規定されて全体の薄型化が図られているが、金バンプ 26 の加工限界によって充分な間隔を保持し得ない場合がある。

【0040】

振動素子 20 は、振動子部 23 の振動動作に伴って支持基板 2 の第 1 主面 2-1 との間に空気流を生じさせる。この空気流は、支持基板 2 の第 1 主面 2-1 に当たって振動子部 23 を押し上げるダンピング効果を発生させる。本実施の形態では、支持基板 2 の第 1 主面 2-1 に間隔構成凹部 11 を形成することにより、図 2 に示すように支持基板 2 と振動子部 23 との間に充分な間隔 m を保持して振動素子 20 に作用するダンピング効果の影響を低減する。

【0041】

振動型ジャイロセンサ 1 は、支持基板 2 の第 1 主面 2-1 上に振動素子 20 を実装した状態において振動子部 23 が間隔構成凹部 11 と対向して延在されることで、薄型化を保持しながら図 2 に示すように振動子部 23 と支持基板 2 との間に充分な間隔が保持されるようになる。これにより、振動子部 23 が厚み方向に振動動作した際に、詳細を図 5 3 を参照して後述するようにダンピング効果の作用が低減され、振動素子 20 の安定した検出動作が確保される。

【0042】

間隔構成凹部 11 は、振動素子 20 の振動子部 23 の寸法に合わせて最適化されて支持基板 2 に形成される。本実施の形態では、振動素子 20 が後述する寸法値で形成されるとともに振動子部 23 の最大振幅量を p とした場合、間隔構成凹部 11 の開口寸法は  $2.1 \text{ mm} \times 0.32 \text{ mm}$  とされ、深さ寸法 k (図 2 参照) は、 $k = p / 2 + 0.05 \text{ (mm)}$  に形成される。支持基板 2 にかかる構成の間隔構成凹部 11 が形成されることによって、高さ寸法が抑制されて薄型化が図られるとともに、振動素子 20 に対するダンピング効果の影響が低減されて高 Q 値化が保持され高感度で安定した手振れ等の検出動作が行えるようになる。

【0043】

続いて、振動素子 20 の構成の詳細について説明する。

【0044】

[金バンプ]

振動素子 20 は、後述するようにシリコン基板 21 の第 2 主面 21-2 によって構成される基部 22 の第 2 主面 (22-2) が支持基板 2 に対する固定面 (実装面) を構成して上述した振動素子実装領域 13 上に実装される。図 4 に示すように基部 22 の実装面 22-2 には、第 1 端子部 25A ~ 第 4 端子部 25D (以下、個別に説明する場合を除いて端子部 25 と総称する。) が形成されるとともに、これら端子部 25 上にそれぞれ金属凸部として第 1 金バンプ 26A ~ 第 4 金バンプ 26D (以下、個別に説明する場合を除いて金バンプ 26 と総称する。) が形成されている。

【0045】

10

20

30

40

50

振動素子 20 の各端子部 25 は、それぞれ支持基板 2 側の配線パターン 5 に形成した各ランド 4 に対応して形成されている。各端子部 25 は、対応するランド 4 と位置合わせされて支持基板 2 に組み合わされる。そして、この状態で振動素子 20 を支持基板 2 に押し当たながら超音波を印加し、金バンプ 26 を介して各端子部 25 とランド 4 とを溶着接合させる。これにより振動素子 20 は支持基板 2 上に実装される。このように振動素子 20 を所定高さの金バンプ 26 を介して実装することにより、振動子部 23 がその第 2 主面(基板対向面) 23-2 を支持基板 2 の第 1 主面 2-1 に対して所定の高さ位置に保持された状態で所定の振動動作を行えるようとする。

#### 【0046】

本実施の形態においては、表面実装法で振動素子 20 を支持基板 2 へ実装することによって実装工程の効率化を図っている。表面実装法における接続子としては、上述した金バンプ 26 に限定されることはなく、半導体プロセスにおいて一般に採用される半田ボールや銅バンプ等の各種の他の金属凸部を用いることもできる。本実施の形態では、本体機器の製造工程においてリフロー半田処理等が施されて、支持基板 2 の実装端子部 116 がバンプ 117 を介して制御基板 100 の各ランドと接続固定されることから、耐熱性が大きくかつ作業性の高い金バンプ 26 が接続子として採用している。

#### 【0047】

振動型ジャイロセンサにおいては、支持基板に対する振動素子の固定構造によって機械品質係数 Q (Q factor) が決定される。本実施の形態では、振動素子 20 が基部 22 を金バンプ 26 を介して支持基板 2 の第 1 主面 2-1 から浮かした状態で実装されることによって、例えば接着層を介して基部全面を支持基板に接合した場合と比較して振動子部 23 の先端部の減衰割合が大きくなり良好な Q 値が得られる。また、基部 22 を支持基板 2 の第 1 主面 2-1 に対して 1箇所で固定するよりも複数箇所で固定する構造の方が良好な Q 値特性が得られることから、基部 22 を支持基板 2 に対して四隅の位置を固定することによって良好な Q 値特性を得るようにしている。

#### 【0048】

なお、各金バンプ 26 は振動子部 23 の長手方向の中心軸線に対して幅寸法  $t_6$  (図 9 参照) の範囲内の領域において全体の重心を位置させるようにして設けることができる。このように金バンプ 26 を配置することによって、厚み方向に振動動作する振動子部 23 は左右のバランスを崩すことなく安定した状態で振動動作することが可能となる。

また、各金バンプ 26 を基部 22 から突出される振動子部 23 の基端部位から振動子部 23 の幅寸法  $t_6$  の 2 倍を半径とする領域の外側領域に位置して形成することにより、金バンプ 26 による振動子部 23 の振動動作を吸収する作用を低減して高 Q 値を保持することが可能となる。

さらに、少なくとも 1 個の金バンプ 26 が、振動子部 23 の基端部から基部 22 の厚み寸法  $t_1$  (図 8 参照) の 2 倍の範囲の領域内に形成されることで、振動子部 23 の振動動作が基部 22 に伝達されて共振周波数のズレを生じさせることが防止されるようになる。

#### 【0049】

なおまた、金バンプ 26 はいわゆる 2 段バンプによって形成されるようにしてもよい。更に、基部 22 の第 2 主面上に電気的接続を行わない、いわゆるダミーの第 5 の金バンプを形成するようにしてもよい。この場合は勿論、支持基板 2 側には、この第 5 金バンプが溶着固定されるダミー端子部が形成される。

#### 【0050】

##### [素子形状]

さて、本実施の形態の振動素子 20 は、図 8 に示すように、振動子部 23 が、基部 22 の第 2 主面(実装面) 22-2 と同一面を構成する第 2 主面(基板対向面) 23-2 を有し、一端部を基部 22 に一体化されて片持ち梁状に突設されている。振動子部 23 は、その上面 23-1 が図 2 に示すように基部 22 の第 1 主面(上面) 22-1 から段落ちされることによって所定の厚みとされる。振動子部 23 は、所定の長さと断面積を有して基部 22 の一側周部と一体に形成された断面矩形の片持ち梁によって構成される。

10

20

30

40

50

## 【0051】

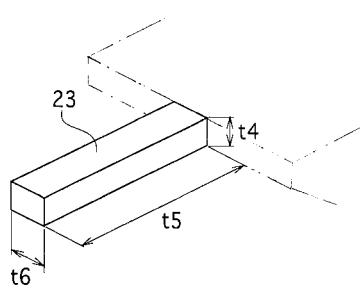

振動素子20の基部22は、図8に示すように、厚み寸法t1を300μm、振動子部23の先端部までの長さ寸法t2を3mm、幅寸法t3を1mmの大きさをもって形成される。振動素子20の振動子部23は、図9に示すように、厚み寸法t4を100μm、長さ寸法t5を2.5mm、幅寸法t6を100μmに形成される。振動素子20は、詳細を後述するように駆動検出回路部50から印加される所定周波数の駆動電圧により振動動作するが、上述した形状から40kHzの共振周波数で振動する。なお、振動素子20は、かかる構成に限定されるものではなく、使用する周波数や目標とする全体形状に応じて種々設定される。

## 【0052】

なお、基部22と振動子部23の各部が次の条件を満足して振動素子20を形成することができる。すなわち、基部22は、その幅寸法t3を振動子部23の幅寸法t6の2倍よりも大きな幅寸法とされるとともに、重心位置を振動子部23の長手方向の中心軸線に対して振動子部23の幅寸法t6の2倍の領域内に位置して形成される。かかる構成によって振動子部23が左右のバランスを崩すことなく良好な状態で振動動作が行われるようになる。また、基部22の厚み寸法t1を振動子部23の厚み寸法t4の1.5倍で形成することによって、基部22の機械的強度が保持されて振動子部23の振動動作による振動動作の発生を抑制でき、共振周波数のズレが生じないようになる。

## 【0053】

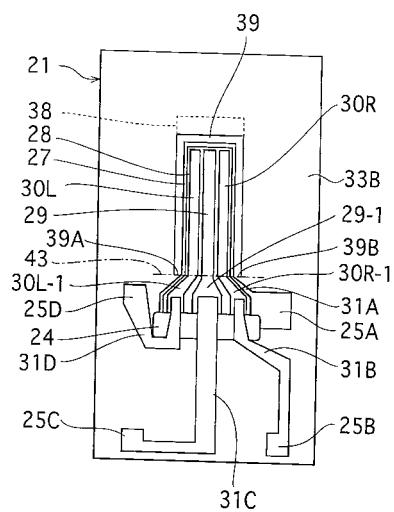

## [圧電膜・各種電極層]

振動素子20には、後述する振動素子製造工程により、図4に示すように振動子部23の第2正面(基板対向面)23-2上に長さ方向の略全長に亘って、基準電極層(第1電極層)27と、圧電薄膜層28と、駆動電極層(第2電極層)29とが積層形成されている。振動子部23の第2正面(基板対向面)23-2上には、駆動電極層29を挟んで一对の検出電極30R、30L(以下、個別に説明する場合を除いて検出電極30と総称する。)が形成されており、これら駆動電極層29と検出電極30とにより第2電極層が構成されている。

## 【0054】

振動子部23の第2正面(基板対向面)23-2には、第1層として基準電極層27が形成され、この基準電極層27上にはほぼ同長の圧電薄膜層28が積層形成される。圧電薄膜層28上には、これとほぼ同長でかつ幅狭の駆動電極層29が幅方向の中央部に位置して積層形成されるとともに、この駆動電極層29を挟んで圧電薄膜層28上に一对の検出電極30R、30Lが積層形成される。

## 【0055】

## [リード・端子部]

振動素子20には、図4に示すように基部22の第2正面(実装面)22-2上に、基準電極層27と第1端子部25Aとを接続する第1リード31Aが形成されるとともに、駆動電極層29と第3端子部25Cとを接続する第3リード31Cが形成されている。同様に、基部22の実装面22-2上には、第1検出電極30Rと第2端子部25Bとを接続する第2リード31Bが形成されるとともに、第2検出電極30Lと第4端子部25Dとを接続する第4リード31Dが形成されている。なお、各リード31A～31Dについては、以下、個別に説明する場合を除いてリード31と総称する。

## 【0056】

第1リード31Aは、振動子部23に形成した基準電極層27の基端部から基部22側に一体に延長され、図4に示すように基部22の第2正面(実装面)22-2上に振動子部23を一体に形成した側の一方コーナ部に位置して形成された第1端子部25Aと一体化される。駆動電極層29と検出電極30は、それぞれの基端部が振動子部23から基部22までやや幅広の部位で一体に延長され、これら幅広部位が平坦化層24によって被覆される。

## 【0057】

10

20

30

40

50

第2リード31Bは、一端部が平坦化層24を乗り越えるようにして形成され、基部22の一側部に沿って第1端子部25Aと対向する後方側のコーナ部へと導かれることにより、このコーナ部に形成された第2端子部25Bと接続される。第3リード31Cは、一端部が平坦化層24を乗り越えるようにして形成され、基部22の略中央部を横切って後方側へと導かれるとともに後端側に沿って第2端子部25Bと対向するコーナ部へと導かれることにより、このコーナ部に形成された第3端子部25Cと接続される。第4リード31Dも、一端部が平坦化層24を乗り越えるようにして形成され、基部22の他側部に沿って第3端子部25Cと対向する前方側の他方コーナ部へと導かれることにより、このコーナ部に形成された第4端子部25Dと接続される。

## 【0058】

なお、振動素子20には、上述した構成にかかわらず、端子部25が基部22の第2主面(実装面)22-2上に最適化される適宜の位置でかつ適宜の個数をもって形成される。また、振動素子20は、各電極層のリード31と端子部25との接続パターンが上述した構成に限定されるものではないことは勿論であり、端子部25の位置や個数に応じて基部22の第2主面上に適宜に形成される。

## 【0059】

## [絶縁保護層]

振動素子20には、図2及び図4に示すように、第2主面21-2側において基部22と振動子部23を被覆する絶縁保護層45が形成されている。絶縁保護層45は、第1層の第1アルミナ(酸化アルミニウム:  $Al_2O_3$ )層46と、第2層の酸化シリコン(SiO<sub>2</sub>)層47と、第3層の第2アルミナ層48とからなる3層構造によって構成される。

## 【0060】

絶縁保護層45には、図2に示すように、各端子部25の形成領域に対応して端子開口部49が形成されており、これらの端子開口部49を介して各端子部25が外方に臨んでいる。振動素子20は、図2に示すように端子開口部49から突出されるようにして各端子部25に金バンプ26が形成される。

## 【0061】

絶縁保護層45は、図4に示すように、基部22と振動子部23の各々の外周縁と、基準電極層27や端子部25の最外周部位との間においてシリコン基板21の第2主面21-2が枠状に露出されるようにして形成される。絶縁保護層45は、外周部位に第2主面21-2の露出部位を残すことによって、後述する振動素子20の切り出し工程に際して外周部位から剥離が生じることが防止されている。なお、絶縁保護層45は、幅寸法t6が100μmとされた振動子部23において、例えば98μmの幅寸法をもって形成される。

## 【0062】

絶縁保護層45は、第1アルミナ層46が例えば50nmの厚み寸法をもって形成される。第1アルミナ層46は、基部22や振動子部23の主面との密着性を向上させる下地密着層として作用し、振動動作する振動子部23上に絶縁保護層45が強固に成膜形成されないようにして剥離等の発生が防止されるようにする。

## 【0063】

酸化シリコン層47は、空気中の水分等を遮断して各電極層等への付着を防止するとともに、各電極層の酸化抑制、各電極層の電気的絶縁或いは薄膜の各電極層や圧電薄膜層28の機械的保護を図る機能を奏する。最上層の第2アルミナ層48は、シリコン基板21に後述する外形溝形成工程を施して振動子部23を形成する際に形成されるレジスト層との密着性を向上させる作用を奏し、エッチング剤による酸化シリコン層47の損傷を防止する。

## 【0064】

酸化シリコン層47は、第2電極層42の少なくとも2倍の厚みで、1μm以下の厚みで形成されている。また、酸化シリコン層47は、0.4Pa以下のアルゴンガス雰囲気中でスパッタ法によって第1アルミナ層46上に成膜される。絶縁保護層45は、酸化シリ

10

20

30

40

50

リコン層 47 を上述した膜厚とすることによって、十分な絶縁保護機能を奏するとともに成膜時のバリ発生が防止される。また、酸化シリコン層 47 は、上述したスパッタ条件で成膜することによって、高膜密度で形成される。

#### 【 0 0 6 5 】

##### [ 位置合わせ用マーク ]

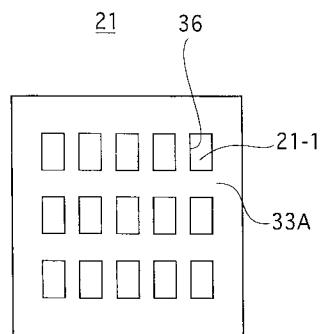

振動型ジャイロセンサ 1 においては、同一形状の第 1 振動素子 20 X と第 2 振動素子 20 Y とを支持基板 2 に対して精密に位置決めして実装するために、支持基板 2 が各ランド 4 の位置を実装機側に認識される。振動素子 20 には、実装機によって認識された各ランド 4 に対して位置決めされて実装されるようにするために、基部 22 の第 1 主面（上面）22-1 に位置合わせ用マーク 32 A, 32 B（以下、位置合わせ用マーク 32 と総称する。）が設けられている。10

#### 【 0 0 6 6 】

位置合わせ用マーク 32 は、図 1 及び図 4 に示すように、基部 22 の第 1 主面（上面）22-1 上に幅方向に離間して形成された金属箔等からなる一対の矩形部によって構成される。振動素子 20 は、実装機によって位置合わせ用マーク 32 が読み取られ、支持基板 2 に対する位置や姿勢の実装データが生成された後、この実装データと上述したランド 4 のデータとに基づいて、支持基板 2 に対して精密に位置決めされて実装される。

#### 【 0 0 6 7 】

振動素子 20 は、位置合わせ用マーク 32 を基部 22 の第 1 主面上に形成したが、かかる構成に限定されるものではない。位置合わせ用マーク 32 は、基部 22 の第 2 主面（実装面）22-2 に、例えば配線工程と同一工程で導体部からなる位置合わせ用マークを端子部 25 やリード 31 を避けた適宜の位置に形成するようにしてもよい。位置合わせ用マーク 32 は、詳細を後述するように振動素子 20 の電極層や振動子部 23 を形成する外形溝形成工程において用いられる誘導結合型プラズマ装置による反応性イオンエッチング処理に際して用いられる基準マーカに合わせて、位置決めされて形成されることが好ましい。位置合わせ用マーク 32 は、ステッパー露光装置を用いることによって、振動子部 23 に対して 0.1  $\mu\text{m}$  以下の精度で形成することが可能である。20

#### 【 0 0 6 8 】

位置合わせ用マーク 32 は、適宜の方法によって形成される。例えば基部 22 の第 2 主面（実装面）22-2 に後述するようにチタン層と白金層とからなる第 1 電極層 40 のパターニングによって形成した場合に、実装工程に際して読み取りが行われて画像処理を施す際に良好なコントラストが得られて実装精度の向上が図られるようになる。30

#### 【 0 0 6 9 】

##### [ カバー ]

続いて、支持基板 2 の第 1 主面 2-1 を外部から遮蔽するカバー 15 の詳細について説明する。

#### 【 0 0 7 0 】

振動型ジャイロセンサ 1 は、手振れ等により生じるコリオリ力による振動素子 20 の変位を、詳細を後述するようにこの振動素子 20 に形成した圧電薄膜層 28 と検出電極 30 とにより検出して検出信号を出力する。そして、圧電薄膜層 28 に光が照射されると焦電効果により電圧が発生し、この焦電圧が検出動作に影響を及ぼして検出特性が低下する。40

#### 【 0 0 7 1 】

振動型ジャイロセンサ 1 においては、支持基板 2 とカバー部材 15 とによる部品実装空間部 3 の遮光対応が図られ、外部光の影響による特性低下の防止が図られている。支持基板 2 には、図 1 に示すように部品実装領域 6 を縁取りるようにして外周部位が全周に亘って第 1 主面 2-1 から段落ちされて垂直壁からなる遮光段部 9 を構成することでカバー固定部 10 が形成されている。そして、支持基板 2 に対して金属薄板によって形成したカバー部材 15 を、カバー固定部 10 上に樹脂接着によって全周に亘って接合することによって、部品実装空間部 3 を密閉して防塵、防湿するとともに遮光空間部として構成する。

#### 【 0 0 7 2 】

カバー部材 15 は、図 1 に示すように支持基板 2 の部品実装領域 6 を被覆するに足る外形寸法を有する主面部 16 と、この主面部 16 の外周部に全周に亘って一体に折曲形成された外周壁部 17 とからなる全体箱状に形成されている。カバー部材 15 は、外周壁部 17 が、支持基板 2 に組み付けられた状態において振動素子 20 の振動子部 23 が振動動作を可能とする部品実装空間部 3 を構成する高さ寸法をもって形成されている。カバー部材 15 には、外周壁部 17 の開口縁に全周に亘って、支持基板 2 に形成したカバー固定部 10 よりもやや小幅とされた外周フランジ部 18 が一体に折曲形成されている。なお、図示せずとも外周フランジ部 18 はアース凸部を形成し、振動型ジャイロセンサ 1 が制御基板 100 に実装された際に制御基板 100 上のグランド端子に接続される。

## 【0073】

10

カバー部材 15 は、金属薄板によって形成されることで振動型ジャイロセンサ 1 の小型軽量化を保持しているが、赤外波長の外部光に対する遮光性が低下して充分な遮光機能を奏し得ないこともある。そこで本実施の形態では、主面部 16 と外周壁部 17 の表面全体に例えれば赤外波長の光を吸収する赤外線吸収塗料を塗布して遮光層 19 を形成し、部品実装空間部 3 内への赤外波長の外部光の放射を遮蔽して振動素子 20 が安定した動作を行うようにする。なお、遮光層 19 は、赤外線吸収塗料溶液中にディップして表裏主面に形成したり、黒色クロムめっき処理や黒染め処理或いは黒色陽極酸化処理を施して形成してもよい。

## 【0074】

20

上述のように、振動型ジャイロセンサ 1 においては、支持基板 2 に対してカバー部材 15 が、外周フランジ部 18 をカバー固定部 10 上に重ね合わせて接着剤によって接合されることによって組み付けられ、密閉かつ遮光された部品実装空間部 3 を構成する。ところが、重ね合わされたカバー固定部 10 と外周フランジ部 18 との間の隙間に介在する接着剤層を透過して外部光が部品実装空間部 3 内に進入する場合がある。そこで本実施の形態においては、上述したように支持基板 2 が主面 2-1 に対して遮光段部 9 を介してカバー固定部 10 を段落ち形成したことにより、接着剤層を透過した外部光が遮光段部 9 によって遮光されるようにしている。

## 【0075】

30

本実施の形態においては、支持基板 2 に対してカバー部材 15 も他の構成部材と同様に表面実装法によって組み付けるようにすることで、組立工程の合理化が図られている。振動型ジャイロセンサ 1 においては、カバー部材 15 を支持基板 2 の段落ちされたカバー固定部 10 上に固定することから薄型化が図られるとともに、接着剤の部品実装領域 6 への流れ込みも防止される。また、部品実装空間部 3 が防塵、防湿空間部として構成されるとともに遮光空間部として構成されることで、振動素子 20 における焦電効果の発生を抑制して安定した手振れ等の検出動作を行うことを可能とする。

## 【0076】

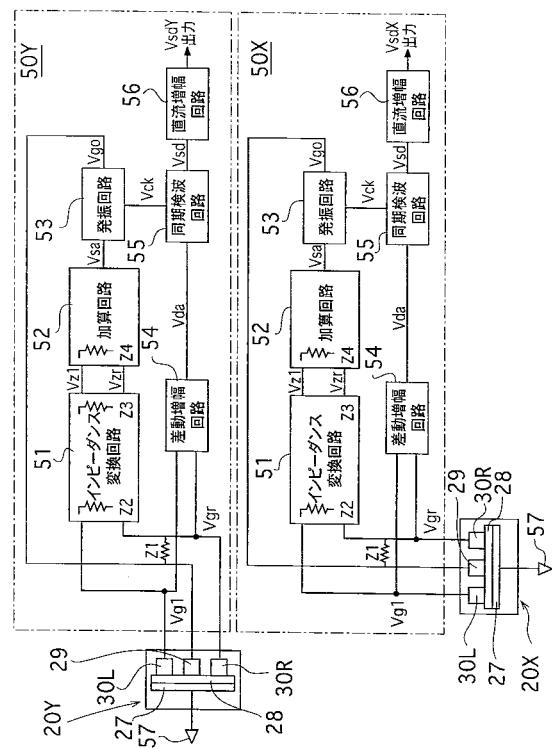

## [回路構成]

次に、振動型ジャイロセンサ 1 を駆動する回路構成について図 7 を参照して説明する。

## 【0077】

40

振動型ジャイロセンサ 1 は、第 1 振動素子 20X と第 2 振動素子 20Y とにそれぞれ接続され I C 回路素子 7 や電子部品 8 等によって構成された第 1 駆動検出回路部 50X と第 2 駆動検出回路部 50Y とを備えている。これら第 1 駆動検出回路部 50X と第 2 駆動検出回路部 50Y とは互いに同一の回路構成とされることから、以下、駆動検出回路部 50 と総称して説明する。駆動検出回路部 50 は、インピーダンス変換回路 51 と、加算回路 52 と、発振回路 53 と、差動增幅回路 54 と、同期検波回路 55 と、直流增幅回路 56 等を備えている。

## 【0078】

50

駆動検出回路部 50 は、図 7 に示すように振動素子 20 の第 1 検出電極 30R と第 2 検出電極 30L に対してインピーダンス変換回路 51 と差動增幅回路 54 とが接続される。インピーダンス変換回路 51 には加算回路 52 が接続され、この加算回路 52 に接続され

た発振回路 5 3 が駆動電極層 2 9 と接続される。差動増幅回路 5 4 と発振回路 5 3 とには同期検波回路 5 5 が接続され、この同期検波回路 5 5 に直流増幅回路 5 6 が接続される。なお、振動素子 2 0 の基準電極層 2 7 は、支持基板 2 側の基準電位 5 7 と接続される。

#### 【 0 0 7 9 】

駆動検出回路部 5 0 は、振動素子 2 0 とインピーダンス変換回路 5 1 と加算回路 5 2 と発振回路 5 3 とによって自励発振回路を構成する。そして、発振回路 5 3 から駆動電極層 2 9 に対して所定周波数の発振出力  $V_{g0}$  を印加することによって振動素子 2 0 の振動子部 2 3 に固有振動を生じさせる。振動素子 2 0 の第 1 検出電極 3 0 R からの出力  $V_{gr}$  と第 2 検出電極 3 0 L からの出力  $V_{g1}$  とはインピーダンス変換回路 5 1 に供給され、これらの入力に基づいてインピーダンス変換回路 5 1 から加算回路 5 2 に対してそれぞれ出力  $V_{zr}$  と  $V_{z1}$  を出力する。加算回路 5 2 は、これらの入力に基づいて発振回路 5 3 に対して加算出力  $V_{sa}$  を出力する。

#### 【 0 0 8 0 】

振動素子 2 0 の第 1 検出電極 3 0 R からの出力  $V_{gr}$  と第 2 検出電極 3 0 L からの出力  $V_{g1}$  とは差動増幅回路 5 4 に供給される。駆動検出回路部 5 0 は、後述するように振動素子 2 0 が手振れを検出するとこれら出力  $V_{gr}$  と出力  $V_{g1}$  とに差異が生じることから、差動増幅回路 5 4 によって所定の出力  $V_{da}$  が得られる。差動増幅回路 5 4 からの出力  $V_{da}$  は、同期検波回路 5 5 に供給される。同期検波回路 5 5 は出力  $V_{da}$  を同期検波することで直流信号  $V_{sd}$  に変換して直流増幅回路 5 6 に供給し、所定の直流増幅を行った直流信号  $V_{sd}$  を出力する。

#### 【 0 0 8 1 】

同期検波回路 5 5 は、差動増幅回路 5 4 の出力  $V_{da}$  を、発振回路 5 3 から駆動信号に同期して出力されるクロック信号  $V_{ck}$  のタイミングで全波整流した後で積分して直流信号  $V_{sd}$  を得る。駆動検出回路部 5 0 は、上述したようにこの直流信号  $V_{sd}$  を直流増幅回路 5 6 において増幅して出力することにより、手振れにより生じる角速度信号の検出が行われる。

#### 【 0 0 8 2 】

駆動検出回路部 5 0 は、インピーダンス変換回路 5 1 がハイ・インピーダンス入力  $Z_2$  の状態でロー・インピーダンス出力  $Z_3$  を得るようになっており、第 1 検出電極 3 0 R と第 2 検出電極 3 0 L 間のインピーダンス  $Z_1$  と加算回路 5 2 の入力間のインピーダンス  $Z_4$  とを分離する作用を奏する。インピーダンス変換回路 5 1 を設けることによって、これら第 1 検出電極 3 0 R と第 2 検出電極 3 0 L とから大きな出力差異を得ることが可能となる。

#### 【 0 0 8 3 】

駆動検出回路部 5 0 においては、上述したインピーダンス変換回路 5 1 が入力と出力とのインピーダンス変換機能を奏するだけで信号の大きさに影響を与えることはない。したがって、第 1 検出電極 3 0 R からの出力  $V_{gr}$  とインピーダンス変換回路 5 1 の一方側の出力  $V_{zr}$ 、及び第 2 検出電極 3 0 L からの出力  $V_{g1}$  とインピーダンス変換回路 5 1 の他方側の出力  $V_{z1}$  とはそれぞれ同一の大きさである。駆動検出回路部 5 0 においては、振動素子 2 0 によって手振れ検出が行われて第 1 検出電極 3 0 R からの出力  $V_{gr}$  と第 2 検出電極 3 0 L からの出力  $V_{g1}$  とに差があっても、加算回路 5 2 からの出力  $V_{sa}$  に保持される。

#### 【 0 0 8 4 】

駆動検出回路部 5 0 においては、例えばスイッチング動作等によってノイズが重畠されることがあっても、発振回路 5 3 の出力  $V_{g0}$  に重畠されたノイズ成分が振動素子 2 0 におけるバンドフィルタと同等の働きによって共振周波数以外の成分が除去されることで、差動増幅回路 5 4 からノイズ成分が除去された高精度の出力  $V_{da}$  を得ることが可能となる。なお、振動型ジャイロセンサ 1 は、上述した駆動検出回路部 5 0 に限定されるものではなく、固有振動する振動子部 2 3 の手振れ動作による変位を圧電薄膜層 2 8 と一対の検出電極 3 0 とによって検出し、適宜の処理を行って検出出力を得るように構成されればよ

10

20

30

40

50

い。

【0085】

振動型ジャイロセンサ1においては、上述したようにX軸方向の角速度を検出する第1振動素子20XとY軸方向の角速度を検出する第2振動素子20Yとを備えている。第1振動素子20Xに接続された第1駆動検出回路部50XからはX軸方向の検出出力VsdXが得られるとともに、第2振動素子20Yに接続された第2駆動検出回路部50YからはY軸方向の検出出力VsdYが得られる。振動型ジャイロセンサ1においては、第1振動素子20Xと第2振動素子20Yとが、それぞれ数kHzから数百kHzの範囲で動作周波数の設定が可能である。そして、第1振動素子20Xの動作周波数fxと第2振動素子20Yの動作周波数fyとの周波数差(fx-fy)を1kHz以上とすることで、クロストークが低減されて精密な振動検出が行われるようになる。

【0086】

[振動型ジャイロセンサの製造方法]

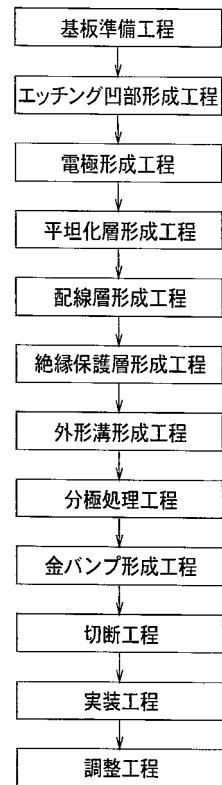

以下、本実施の形態の振動型ジャイロセンサ1の製造方法について説明する。図10は振動型ジャイロセンサ1の製造方法を説明する主要工程フロー図である。

【0087】

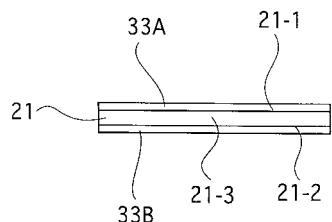

振動型ジャイロセンサ1においては、上述した振動素子20が、例えば図11及び図12に示すように、正面21-1の方位面が(100)面、側面21-3の方位面が(110)面となるように切り出されたシリコン基板21を基材にして多数個が一括して形成された後に、切断工程を経て1個ずつに切り分けられる。

【0088】

[基板準備工程]

シリコン基板21は、外形寸法が、工程に用いられる設備仕様に応じて切り出し寸法が適宜決定され、例えば300×300(mm)とされる。シリコン基板21は図11に示すように平面視矩形状の基板に限らず、平面視円形のウェーハ形状でもよい。シリコン基板21は、作業性やコスト等によって厚み寸法を決定されるが、少なくとも振動素子20の基部22の厚み寸法よりも大きな厚みであればよい。シリコン基板21は、上述したように基部22の厚みが300μmであるとともに振動子部23の厚みが100μmであることから、300μm以上の基板が用いられる。

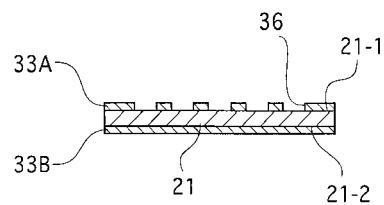

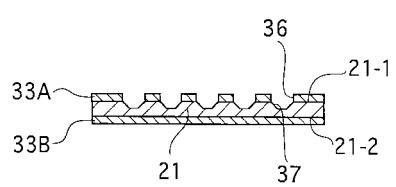

【0089】

シリコン基板21には、熱酸化処理が施されて、図12に示すように第1正面21-1上及び第2正面21-2上にそれぞれシリコン酸化膜(SiO<sub>2</sub>膜)33A, 33B(以下、個別に説明する場合を除いてシリコン酸化膜33と総称する。)が全面に亘って形成されている。シリコン酸化膜33は、後述するようにシリコン基板21に結晶異方性エッティング処理を施す際に保護膜として機能する。シリコン酸化膜33は、保護膜機能を奏すればよく適宜の厚みをもって形成されるが、例えば0.3μm程度の厚み寸法で形成される。

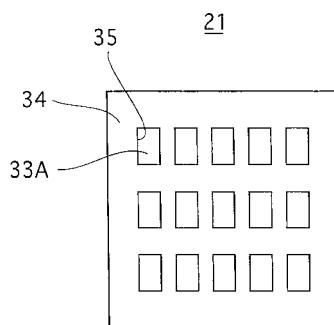

【0090】

[エッティング凹部形成工程]

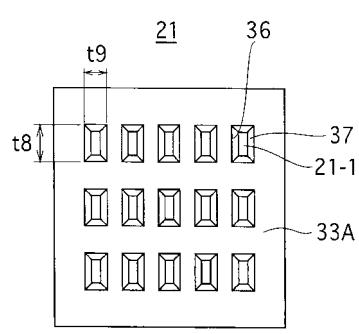

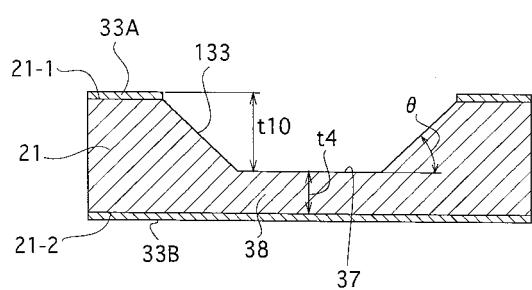

振動素子製造工程は、半導体プロセスの薄膜工程と同様の工程からなり、シリコン基板21の第1正面21-1側から各振動素子20の振動子部23を形成する部位を所定の厚み寸法とする上述したエッティング凹部37を形成するエッティング凹部形成工程を有する。

【0091】

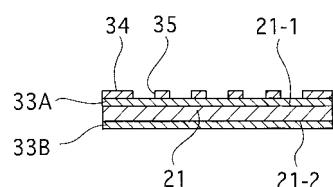

エッティング凹部形成工程は、図13～図19に示すように、シリコン基板21の第1正面21-1に、フォトレジスト層34を形成するフォトレジスト層形成工程と、エッティング凹部37の形成部位に対応してフォトレジスト層34にフォトレジスト層開口部35を形成するフォトレジストパターニング工程と、フォトレジスト層開口部35に臨むシリコン酸化膜33Aを除去してシリコン酸化膜開口部36を形成する第1エッティング処理工程と、シリコン酸化膜開口部36内にエッティング凹部37を形成する第2エッティング処理工程等を有する。

10

20

30

40

50

## 【0092】

フォトレジスト層形成工程は、シリコン基板21の第1主面21-1に形成したシリコン酸化膜33A上に全面に亘ってフォトレジスト材を塗布してフォトレジスト層34を形成する。フォトレジスト層形成工程は、フォトレジスト材として例えば東京応化社製の感光性フォトレジスト材「O F P R - 8 6 0 0」が用いられ、このフォトレジスト材を塗布した後にマイクロ波で加熱して水分を除去するプレベーキング処理を施してシリコン酸化膜33A上にフォトレジスト層34を形成する。

## 【0093】

フォトレジストパターニング工程は、フォトレジスト層34上に各シリコン酸化膜開口部36を形成する部位を開口部としたマスキング処理を施し、フォトレジスト層34に対して露光、現像処理を施す。フォトレジストパターニング工程は、各シリコン酸化膜開口部36の対応部位のフォトレジスト層34を除去して、図13及び図14に示すようにシリコン酸化膜33Aを外方に臨ませる多数個のフォトレジスト層開口部35を一括して形成する。なお、シリコン基板21には、図13に示すように3×5個のフォトレジスト層開口部35が形成されることで、後述する各工程を経て15個の振動素子20が一括して製造されるようとする。

## 【0094】

第1エッティング処理工程は、フォトレジスト層開口部35を介して外部に臨むシリコン酸化膜33Aを除去する工程である。第1エッティング処理は、シリコン基板21の界面の平滑性を保持するために、シリコン酸化膜33Aのみを除去する湿式エッティング法を採用するが、この方法に限定されるものではなく例えばイオンエッティング法等の適宜のエッティング処理であってもよい。

## 【0095】

第1エッティング処理には、エッティング液として例えばフッ化アンモニウム溶液を用い、シリコン酸化膜33Aを除去してシリコン酸化膜開口部36を形成する。これにより、図15及び図16に示すように、シリコン基板21の第1主面21-1を外部に臨ませる。なお、第1エッティング処理は、長時間に亘ってエッティングを行った場合にシリコン酸化膜開口部36の側面からエッティングが進行するいわゆるサイドエッティング現象が生じることから、シリコン酸化膜33Aがエッティングされた時点で終了するようにエッティング時間を正確に管理することが好ましい。

## 【0096】

第2エッティング処理は、シリコン酸化膜開口部36を介して外部に臨むシリコン基板21の第1主面21-1にエッティング凹部37を形成する工程である。第2エッティング処理工程は、シリコン基板21の結晶方向にエッティング速度が依存する性質を利用した結晶異方性の湿式エッティング処理によって、シリコン基板21を振動子部23の厚みまでエッティングする。

## 【0097】

第2エッティング処理工程には、エッティング液として例えばTMAH(水酸化テトラメチルアンモニウム)やKOH(水酸化カリウム)或いはEDP(エチレンジアミン-ピロカルコール-水)溶液が用いられる。第2エッティング処理は、具体的にはエッティング液として表裏面のシリコン酸化膜33A, 33Bのエッティングレートの選択比がより大きくなるTMAH20%溶液を用い、このエッティング液を攪拌しながら温度を80℃に保ち、6時間のエッティングを行って図17及び図18に示すエッティング凹部37を形成する。

## 【0098】

第2エッティング処理工程においては、基材として用いるシリコン基板21の第1主面21-1や第2主面21-2に対して側面21-3の対エッティング性が小さい特性を利用して、(100)面に対して約55°の角度の面方位となる(110)面が出現するエッティングが行われる。これにより、開口部から底面に向かって約55°の傾斜角度をもって次第に開口寸法が小さくなり、内周壁に約55°の傾斜角度のエッティング斜面133を有するエッティング凹部37が形成される。

## 【0099】

エッティング凹部37は、後述する外形切り抜き工程が施されて振動子部23を形成するダイヤフラム部38を構成する。エッティング凹部37は、図17に示すように長さ寸法t8、幅寸法t9の開口寸法を有し、図19に示すように深さ寸法t10をもって形成される。エッティング凹部37は、図19に示すように、第1主面21-1から第2主面21-2側に向かって次第に開口寸法が小さくなる断面が台形の空間部によって構成される。

## 【0100】

エッティング凹部37は、内周壁が上述したように内方下がりに55°の傾斜角度を付されて形成される。ダイヤフラム部38は、後述するように、振動子部23の幅寸法t6と長さ寸法t5及びその外周部を切り抜くようにしてシリコン基板21に形成する外形溝39の幅寸法t7(図36及び図37参照)とによって規定する。外形溝39の幅寸法t7は、(深さ寸法t10×1/tan55°)で求められる。

10

## 【0101】

したがって、エッティング凹部37は、ダイヤフラム部38の幅を規定する開口幅寸法t9が、(深さ寸法t10×1/tan55°)×2+t6(振動子部23の幅寸法)+2×t7(外形溝39の幅寸法)から求められる。エッティング凹部37は、開口部位の幅寸法t9が、t10=200μm、t6=100μm、t7=200μmとすると、t9=780μmとなる。

## 【0102】

また、エッティング凹部37は、上述した第2エッティング処理を施すことによって長さ方向についても幅方向と同様にその内周壁がそれぞれ傾斜角度が55°の傾斜面として構成される。したがって、エッティング凹部37は、ダイヤフラム部38の長さを規定する長さ寸法t8が、(深さ寸法t10×1/tan55°)×2+t5(振動子部23の長さ寸法)+t7(外形溝39の幅寸法)から求められる。エッティング凹部37は、長さ寸法t8が、t10=200μm、t5=2.5mm、t7=200μmとすると、t8=2980μmとなる。

20

## 【0103】

## [電極形成工程(成膜)]

上述したエッティング凹部形成工程により、シリコン基板21にエッティング凹部37の底面と第2主面21-2との間に、所定の厚みを有する矩形のダイヤフラム部38が構成される。ダイヤフラム部38は、振動素子20の振動子部23を構成する。エッティング凹部形成工程の後、ダイヤフラム部38の第2主面21-2側を加工面として電極形成工程が施される。

30

## 【0104】

電極形成工程は、例えばマグнетロンスパッタ装置によって、エッティング凹部37の形成部位と対向する第2主面21-2上に、シリコン酸化膜33Bを介して各電極層を形成する。電極形成工程は、図20に示すようにシリコン酸化膜33Bを介して基準電極層27を構成する第1電極層40を形成する第1電極層形成工程と、圧電薄膜層28を構成する圧電膜層41を形成する圧電膜層形成工程と、駆動電極層29及び検出電極30を構成する第2電極層42を形成する第2電極層形成工程とを有する。

40

## 【0105】

なお、振動素子製造工程においては、振動子部23に対する上述した第1電極層40の形成工程と第2電極層42の形成工程に合わせて、基部22の形成部位に各リード31や端子部25を形成するための導体層の形成工程も同時に行われるようとする。

## 【0106】

第1電極層形成工程は、図20に示すように、振動子部23の構成部位に対応するシリコン酸化膜33B上に全面に亘ってチタンをスパッタリングしてチタン薄膜層を形成する工程と、このチタン薄膜層上にプラチナ(白金)をスパッタリングしてプラチナ層を形成して2層構成の第1電極層40を積層形成する工程とからなる。チタン薄膜層形成工程は、例えばガス圧0.5Pa、RF(高周波)パワー1kWのスパッタ条件でシリコン酸化

50

膜33B上に膜厚が50nm以下(例えば5nm~20nm)のチタン薄膜層を成膜する。プラチナ層形成工程は、例えばガス厚0.5Pa、RFパワー0.5kWのスパッタ条件でチタン薄膜層上に膜厚が200nm程度のプラチナ薄膜層を成膜する。

【0107】

第1電極層40は、チタン薄膜層がシリコン酸化膜33Bとの密着性を向上させる作用を奏するとともに、プラチナ層が良好な電極として作用する。第1電極層形成工程は、上述した第1電極層40の形成と同時にダイヤフラム部38から基部22の形成領域へと延長して第1リード31Aと第1端子部25Aとを構成する導体層も形成する。

【0108】

圧電膜層形成工程は、上述した第1電極層40上に全面に亘って、例えばチタン酸ジルコン酸鉛(PZT)をスパッタリングして所定の厚みの圧電膜層41を積層形成する。圧電膜層形成工程は、 $Pb_{(1+x)}(Zr_{0.53}Ti_{0.47})O_{3-y}$ 酸化物をターゲットとして用いて、例えばガス圧0.7Pa、RFパワー0.5kWのスパッタ条件で第1電極層40上に膜厚が1μm程度のPZT層からなる圧電膜層41を積層形成する。圧電膜層形成工程は、電気炉により圧電膜層41をベーキングすることによって、結晶化熱処理を施す。ベーキング処理は、例えば酸素雰囲気下で、700、10分間の条件で行う。なお、圧電膜層41は、上述した第1電極層40から延長された基部22の形成領域に形成された電極層の一部を被覆して形成される。

【0109】

第2電極層形成工程は、上述した圧電膜層41上に全面に亘って、プラチナをスパッタリングしてプラチナ層を形成することによって第2電極層42を積層形成する。第2電極層形成工程は、ガス圧0.5Pa、RFパワー0.5kWのスパッタ条件で圧電膜層41上に膜厚が200nm程度のプラチナ薄膜層を成膜する。

【0110】

[電極形成工程(パターニング)]

次に、最上層に形成された第2電極層42に対してパターニング処理を施す第2電極層パターニング工程が行われる。第2電極層パターニング工程では図21及び図22に示すように所定形状の駆動電極層29と一対の検出電極30R, 30Lとを形成する。

【0111】

駆動電極層29は、上述したように振動子部23を駆動させる所定の駆動電圧が印加される電極であり、振動子部23の幅方向の中央領域に所定の幅をもって長さ方向のほぼ全域に亘って形成される。検出電極30は、振動子部23に発生したコリオリ力を検出する電極であり、駆動電極層29の両側に位置して長さ方向のほぼ全域に亘って互いに絶縁を保持されて平行に形成される。

【0112】

第2電極層パターニング工程は、第2電極層42に対してフォトリソグラフ処理を施して図21に示すように圧電膜層41上に駆動電極層29と検出電極30とを形成する。第2電極層パターニング工程は、駆動電極層29と検出電極30との対応部位にレジスト層を形成し、不要な部位の第2電極層42を例えばイオンエッチング法等によって除去した後にレジスト層を除去する等の工程を経て、駆動電極層29と検出電極30とをパターン形成する。第2電極層パターニング工程は、かかる工程に限定されず、半導体プロセスにおいて採用されている適宜の導電層形成工程を利用して駆動電極層29や検出電極30を形成するようにしてもよいことは勿論である。

【0113】

駆動電極層29と検出電極30とは、図21に示すように先端部とともに振動子部23の根元となる根元部位43においても同一となるようにして形成される。この第2電極層パターニング工程においては、根元部位43において一致された駆動電極層29と検出電極30との基端部に、それぞれ幅広とされたリード接続部29-1, 30R-1, 30L-1が一体にパターン形成される。

【0114】

10

20

30

40

50

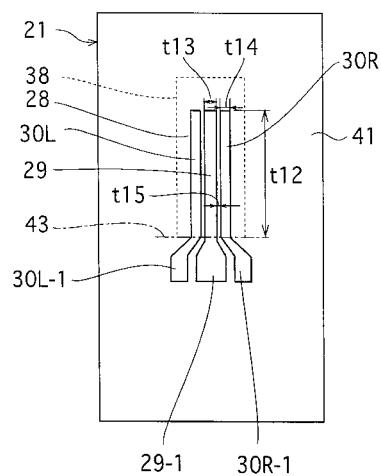

第2電極層パターニング工程においては、第2電極層42をパターニングして例えば長さ寸法t12が2mm、幅寸法t13が50μmの駆動電極層29を形成する。そして、この駆動電極層29を挟んで、図21に示すようにそれぞれ幅寸法t14が10μmの第1検出電極30Rと第2検出電極30Lとを、5μmの間隔寸法t15をもってパターン形成する。また、第2電極層パターニング工程は、長さ寸法がそれぞれ50μm、幅寸法もそれぞれ50μmとしたリード接続部29-1, 30R-1, 30L-1をパターン形成する。なお、駆動電極層29と検出電極30とは上述した寸法値に限定されるものではなく、振動子部23の第2主面上に形成することが可能な範囲で適宜形成される。

#### 【0115】

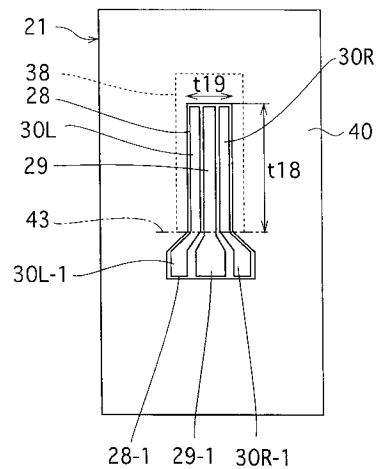

続いて、上述した圧電膜層41に対してパターニング処理を施す圧電膜層パターニング工程によって、図23及び図24に示す所定形状の圧電薄膜層28を形成する。圧電薄膜層28は、圧電膜層41に対して上述した駆動電極層29と検出電極30よりも大きな面積の部位を残すようにパターニング処理を施して形成される。圧電薄膜層28は、振動子部23に対して、その幅よりもやや小幅であり基端部から先端部の近傍位置に亘って形成される。

#### 【0116】

圧電膜層パターニング工程は、圧電膜層41に対してフォトリソグラフ処理を施して圧電薄膜層28の対応部位にレジスト層を形成し、不要な部位の圧電膜層41を例えばフッ硝酸溶液を用いた湿式エッチング法等によって除去した後に、レジスト層を除去する等の工程を経て、図23及び図24に示す圧電薄膜層28を形成する。なお、上記の例では圧電膜層41を湿式エッチング法によってエッチング処理を施すようにしたが、かかる方法に限定されるものではなく、例えばイオンエッチング法や反応性イオンエッチング法(RIE: Reactive Ion Etching)等の適宜の方法を施すことにより圧電薄膜層28を形成するようにしてもよいことは勿論である。

#### 【0117】

圧電膜層パターニング工程においては、圧電薄膜層28の基端部が図23に示すように振動子部23の根元となる根元部位43において駆動電極層29と検出電極30とほぼ同形となるようにして形成される。そして、圧電薄膜層28は、基端部から駆動電極層29や検出電極30のリード接続部29-1, 30R-1, 30L-1よりもやや大きな面積を有して端子受け部28-1が一体にパターン形成される。

#### 【0118】

圧電膜層パターニング工程は、長さ寸法t18が駆動電極層29や検出電極30よりもやや長い2.2mm、幅寸法t19が90μmの圧電薄膜層28をパターン形成する。圧電薄膜層28の基端部に形成される端子受け部28-1は、駆動電極層29や検出電極30のリード接続部29-1, 30R-1, 30L-1の周囲に5μmの幅寸法を有してパターン形成される。なお、圧電薄膜層28は上述した寸法値に限定されるものではなく、駆動電極層29や検出電極30よりも大きな面積をもって振動子部23の第2主面23-2上に形成することが可能な範囲で適宜形成される。

#### 【0119】

そして、第1電極層40に対して、上述した第2電極層パターニング工程と同様のパターニング処理を施す第1電極層パターニング工程によって、図25及び図26に示すように基準電極層27をパターン形成する。第1電極層パターニング工程は、基準電極層27の対応部位にレジスト層を形成し、不要な部位の第1電極層40を例えばイオンエッチング法等によって除去した後にレジスト層を除去する等の工程を経て、基準電極層27をパターン形成する。なお、第1電極層パターニング工程は、かかる工程に限定されず、半導体プロセスにおいて採用されている適宜の導電層形成工程を利用して基準電極層27を形成するようにしてもよいことは勿論である。

#### 【0120】

第1電極層パターニング工程においては、振動子部23の第2主面上においてその幅よりもやや小幅で圧電薄膜層28よりも大きな幅を有する基準電極層27を形成する。基準

10

20

30

40

50

電極層 27 の基端部は、図 25 に示すように振動子部 23 の根元となる根元部位 43 において駆動電極層 29 と検出電極 30 及び圧電薄膜層 28 とほぼ同形となるようにして形成される。この第 1 電極層パターニング工程においては、基端部から側方へと一体に引き出されて基部 22 の形成部位上に第 1 リード 31A とその先端部の第 1 端子部 25A とが同時にパターン形成される。

#### 【0121】

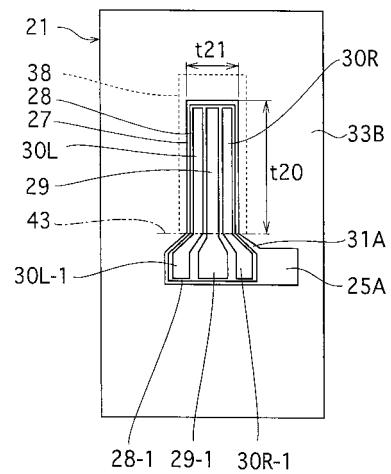

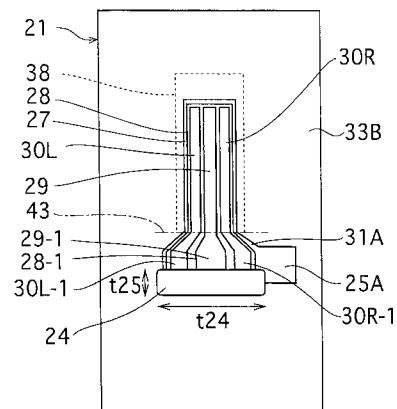

第 1 電極層パターニング工程においては、長さ寸法  $t_{20}$  が  $2.3\text{ mm}$ 、幅寸法  $t_{21}$  が  $94\text{ }\mu\text{m}$  とされ、圧電薄膜層 28 の周囲に  $5\text{ }\mu\text{m}$  の幅寸法をもって基準電極層 27 を形成する。なお、第 1 電極層パターニング工程は、基準電極層 27 が上述した寸法値に限定されるものではなく、振動子部 23 の第 2 主面上に形成することが可能な範囲で適宜形成される。

#### 【0122】

##### [平坦化層形成工程]

振動素子製造工程においては、上述した各工程を経て基部 22 の形成部位に対応して、駆動電極層 29 と検出電極 30 のリード接続部 29-1, 30R-1, 30L-1 及び端子部 25B ~ 25D を形成するとともに、これら各端子部 25 と一体化されるリード 31B ~ 31D を形成する。この際、リード 31B ~ 31D をリード接続部 29-1, 30R-1, 30L-1 と円滑に接続するために、図 27 及び図 28 に示す平坦化層 24 を形成する。

#### 【0123】

リード接続部 29-1, 30R-1, 30L-1 と端子部 25B ~ 25D とを接続するリード 31B ~ 31D は、図 29 及び図 30 に示すように、圧電薄膜層 28 の端子受け部 28-1 や基準電極層 27 の端部を通過して基部 22 の形成部位を引き回すようにして形成される。上述したように圧電薄膜層 28 は圧電膜層 41 に湿式エッティング処理を施してパターニングされることから、エッティング箇所の端部がシリコン基板 21 の第 2 主面 21-2 側に向かって逆テープ或いは垂直な段部となっている。従って、基部 22 の形成部位にリード 31B ~ 31D を直接形成した場合に、上記段部において断線を生じさせことがある。また、基部 22 の形成部位に引き回されている第 1 リード 31A とリード 31B ~ 31D との絶縁を保持する必要もある。

#### 【0124】

平坦化層形成工程は、基部 22 の形成部位に形成したレジスト層にフォトリソグラフ処理を施して、リード接続部 29-1, 30R-1, 30L-1 と第 1 リード 31A とを被覆するレジスト層をパターン形成する。パターン形成されたレジスト層は、例えば  $160\text{ }\sim 300$  程度の加熱処理が施されることで硬化し平坦化層 24 を構成する。平坦化層形成工程は、幅寸法  $t_{24}$  が  $200\text{ }\mu\text{m}$ 、長さ寸法  $t_{25}$  が  $50\text{ }\mu\text{m}$ 、厚み寸法が  $2\text{ }\mu\text{m}$  (図 28 では強調して示している。) の平坦化層 24 を形成する。なお、平坦化層形成工程は、かかる工程に限定されるものではなく、半導体プロセス等に実施される適宜のレジスト層形成工程や適宜の絶縁性材料を用いて平坦化層 24 を形成するようにしてよい。

#### 【0125】

##### [配線層形成工程]

次に、基部 22 の形成部位に上述した第 2 端子部 25B ~ 第 4 端子部 25D 及び第 2 リード 31B ~ 第 4 リード 31D を形成する配線層形成工程が施される。配線層形成工程は、基部 22 の形成部位に全面に亘って感光性のフォトレジスト層を形成するとともに、このフォトレジスト層に対してフォトリソグラフ処理を施して第 2 端子部 25B ~ 第 4 端子部 25D や第 2 リード 31B ~ 第 4 リード 31D に対応する開口パターンを形成し、さらにスパッタリングによって各開口部内に導体層を形成して配線層を形成する。配線層形成工程は、所定の導体部を形成した後に、フォトレジスト層を除去して図 29 及び図 30 に示す第 2 端子部 25B ~ 第 4 端子部 25D 及び第 2 リード 31B ~ 第 4 リード 31D をパターン形成する。

#### 【0126】

10

20

30

40

50

この配線層形成工程においては、シリコン酸化膜33Bに対する密着性の向上を図るチタン層やアルミナ層が下地層として形成された後に、このチタン層上に電気抵抗が低く低コストの銅層が形成される。この例では、例えばチタン層が20nmの厚みで形成され、銅層が300nmの厚みで形成される。なお、配線層形成工程は、かかる工程に限定されず、例えば半導体プロセスで汎用される各種の配線パターン形成技術によって配線層を形成するようにしてもよい。

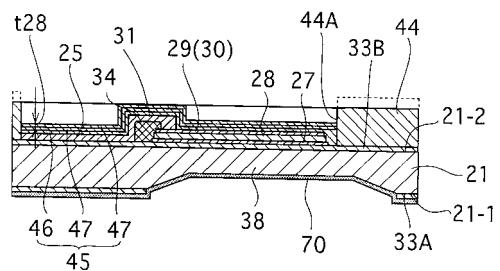

【0127】

[絶縁保護層形成工程]

続いて、上述した工程を経て主面上に端子部25とリード31とを形成した基部22と、各電極層と圧電薄膜層28とを形成した振動子部23の主面上に3層構成の絶縁保護層45を形成する絶縁保護層形成工程が施される。絶縁保護層形成工程は、レジスト層形成工程と、レジスト層パターニング形成工程と、第1アルミナ層形成工程と、酸化シリコン層形成工程と、第2アルミナ層形成工程と、レジスト層除去工程とを有する。

【0128】

絶縁保護層形成工程は、レジスト層形成工程とレジスト層パターニング形成工程とを経て、図31に示すようにシリコン基板21の第2主面上に絶縁保護層45の形成部位を開口したレジスト層44を形成する。レジスト層形成工程は、シリコン基板21上に全面に亘って感光性レジスト剤を塗布してレジスト層44を形成する。レジスト層パターニング形成工程は、レジスト層44に対してフォトリソグラフ処理を施して絶縁保護層45の形成領域に対応する部位を開口して絶縁保護層形成開口部44Aを形成する。なお、レジスト層44は、図示を省略するが端子部25の対応部位がそれぞれ円形に残される。

【0129】

絶縁保護層形成工程は、スパッタ法によって第1アルミナ層46と酸化シリコン層47と第2アルミナ層48とを積層形成するとともに、不要なスパッタ形成膜をレジスト層44とともに除去してレジスト層44の絶縁保護層形成開口部44A内に3層構造のスパッタ形成層を残すいわゆるリフトオフ法によって所望の絶縁保護層45を形成する。なお、図32～図34においては、絶縁保護層形成開口部44Aに形成される各スパッタ膜のみを図示しているが、この絶縁保護層形成開口部44Aを構成するレジスト層44上にも同様にしてスパッタ膜が形成されることは勿論であり、これらスパッタ膜はレジスト層除去工程によってレジスト層44とともに一括して除去される。

【0130】

第1アルミナ層形成工程は、アルミナのスパッタリングを施して、図32に示すように上述した絶縁保護層形成開口部44Aの内部に第1アルミナ層46を形成する。第1アルミナ層46は、50nm程度の厚み寸法t26をもって形成され、絶縁保護層形成開口部44A内において上述したようにシリコン基板21や駆動電極層29或いは検出電極30との密着性を向上させる下地金属層として機能する。

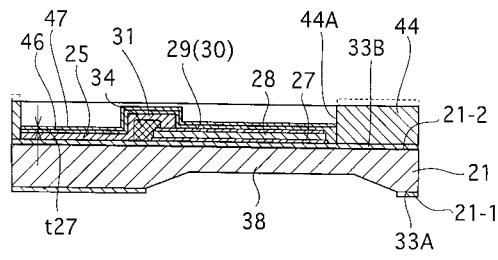

【0131】

酸化シリコン層形成工程は、酸化シリコンのスパッタリングを施して、図33に示すように上述した第1アルミナ層46上に酸化シリコン層47を形成する。酸化シリコン層形成工程は、スパッタ槽内におけるアルゴン圧が0.35Paを放電限界の下限とすることから、アルゴン圧を下限値よりもやや高圧とした0.4Paに設定して酸化シリコンのスパッタリングを行って、高密度の酸化シリコン膜47を形成する。酸化シリコン膜形成工程は、駆動電極層29や検出電極30の少なくとも2倍の厚みを有することで充分な絶縁保護機能を奏し、かつリフトオフ法においてバリ発生率が小さい範囲の厚みである1μm以下の厚み寸法t27を有する酸化シリコン層47を形成する。酸化シリコン層47は、具体的には750nmの厚み寸法t27に形成される。

【0132】

第2アルミナ層形成工程は、アルミナのスパッタリングを施して、図34に示すように上述した酸化シリコン層47上に第2アルミナ層48を全面に亘って形成する。第2アルミナ層48は、50nm程度の厚み寸法t28をもって形成され、後述する外形溝形成工

10

20

30

40

50

程に際して形成されるレジスト層との密着性を向上させることで、エッティング剤による酸化シリコン層 47 の損傷を防止する。

【0133】

[外形溝形成工程]

次に、シリコン基板 21 の第 1 主面 21-1 上に、図 34 に示すようにエッティングストップ層 70 を形成する工程が施される。エッティングストップ層 70 は、後述する外形溝形成工程をシリコン基板 21 に対して施す際に、第 1 主面 21-1 側にプラズマ集中が生じて所定のエッジ形状が形成されない形状不良の発生を抑制する機能を奏する。エッティングストップ層形成工程は、例えばシリコン基板 21 の第 1 主面 21-1 上に、スパッタ法によって全面に亘って厚みが 500 nm 程度の酸化シリコンを形成する。

10

【0134】

外形溝形成工程は、ダイヤフラム部 38 を貫通して振動子部 23 の外周部を構成する外形溝 39 を形成する。外形溝形成工程においては、図 35 ~ 図 37 に示すように、ダイヤフラム部 38 と対向するシリコン基板 21 の第 2 主面 21-2 側から、上述した各電極層を積層形成したシリコン基板 21 の振動子部 23 の一方側の根元部位 43 を始端 39A とし、振動子部 23 を囲むように他方側の根元部位 43 を終端 39B とする略コ字状の貫通溝からなる外形溝 39 が形成される。外形溝 39 は、上述したように 200 μm の幅寸法  $t_7$  をもって形成される。

20

【0135】

外形溝形成工程は、具体的にはシリコン酸化膜 33B を所定形状のコ字状に除去してシリコン基板 21 の第 2 主面 21-2 を露出させる第 1 エッティング処理工程と、露出されたシリコン基板 21 に対して外形溝 39 を形成する第 2 エッティング処理工程とからなる。

【0136】

第 1 エッティング工程においては、シリコン酸化膜 33B 上に全面に亘って感光性のフォトレジスト層を形成するとともに、このフォトレジスト層に対してフォトリソグラフ処理を施して上述した各電極層の形成領域を囲み振動子部 23 の外形寸法と等しい開口寸法を有するコ字状の開口パターンを形成する。第 1 エッティング処理工程は、開口パターンを介して露出されたシリコン酸化膜 33B をイオンエッティングによって除去する。なお、第 1 エッティング処理工程は、例えば湿式エッティングによってシリコン酸化膜 33B をコ字状に除去することも可能であるが、サイドエッティングによる寸法誤差の発生を考慮すると、イオンエッティングが好適に実施される。

30

【0137】

第 2 エッティング工程においては、残されたシリコン酸化膜 33B がレジスト膜（エッティング保護膜）として利用される。第 2 エッティング処理工程は、レジスト膜（シリコン酸化膜 33B）との選択比が得られ、かつ振動子部 23 の外周部が高精度の垂直面によって構成されるようにするために、シリコン基板 21 に対して例えば反応性イオンエッティングが施される。

【0138】

第 2 エッティング処理工程には、高密度なプラズマを生成する誘導結合型プラズマ（ICP : Inductively Coupled Plasma）を生成する機能を有する反応性イオンエッティング（RIE）装置が用いられる。第 2 エッティング処理工程は、エッティング箇所に SF<sub>6</sub> ガスを導入するエッティング処理と、C<sub>4</sub>F<sub>8</sub> ガスを導入してエッティングした箇所に外周壁を保護するための保護膜形成工程とを繰り返す Bosch ( Bosch 社 ) プロセスが用いられ、毎分 10 μm 程度の速度で垂直な内壁を有する外形溝 39 をシリコン基板 21 に形成する。

40

【0139】

第 2 エッティング処理工程の後、シリコン基板 21 の第 1 主面 21-1 に形成されたエッティングストップ層 70 を除去する工程が施される。エッティングストップ層の除去工程は、例えばフッ化アンモニウムを用いた湿式エッティング処理によって酸化シリコンからなるエッティングストップ層 70 を除去する。なお、エッティングストップ層除去工程は、上述した外形溝形成工程で形成したフォトレジスト層を除去してしまうと絶縁保護層 45 も除去さ

50

れてしまうから、エッティングストップ層 70 を除去した後に当該フォトレジスト層の除去が行われるようにする。

#### 【0140】

##### [分極処理工程]

続いて、シリコン基板 21 上に形成される各振動素子 20 の圧電薄膜層 28 を一括して分極処理する分極処理工程が行われる。分極処理ための分極用配線には Cu 配線が用いられる。Cu 配線は、後述する分極処理を行った後に湿式エッティング処理によって容易に溶解することで、各振動素子 20 にダメージを与えることなく除去することが可能である。なお、分極用配線については、Cu 配線に限定されず、上述した機能を奏する適宜の導電体によって形成してもよいことは勿論である。

10

#### 【0141】

Cu 配線の形成には、例えばフォトリソグラフ処理によって所望の形状を開口部とするレジスト層をシリコン基板 21 の第 2 主面 21-2 上にパターン形成した後に、Cu 層をスパッタ法により成膜するとともに不要な部位に付着した Cu 層をレジスト層とともに除去するリフトオフ法が用いられる。Cu 配線は、分極処理時の導通を確保するために、例えば幅寸法が 30  $\mu\text{m}$  以上、厚みが 400 nm 程度とする。

#### 【0142】

分極処理工程は、Cu 配線に形成された印加側パッドとグランド側パッドとを介して各振動素子 20 を外部電源に一括して接続することによって、効率よく行うことが可能である。なお、分極処理工程は、例えばワイヤボンディング法によって各パッドと外部電源との接続を行うとともに、20 V - 20 min の条件で通電を行って分極処理を施す。分極処理工程は、かかる条件に限定されず、適宜の接続方法や分極条件によって分極処理を施すようにしてもよいことは勿論である。

20

#### 【0143】

##### [金バンプ形成工程]

次に、金バンプ形成工程が行われる。振動素子 20 は、上述したように支持基板 2 に表面実装されることから、各端子部 25 上に金バンプ 26 が形成される。金バンプ形成工程は、各端子部 25 に金ワイヤのボンディングツールを押し当てて所定形状のスタッドバンプを形成する。金バンプ形成工程においては、必要に応じて基部 22 上にいわゆるダミーバンプも形成される。なお、金バンプ 26 の他の形成方法としては、後述するめっきバンプ法がある。

30

#### 【0144】

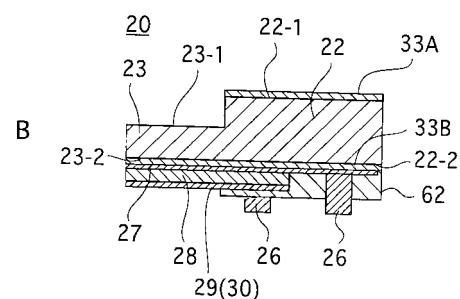

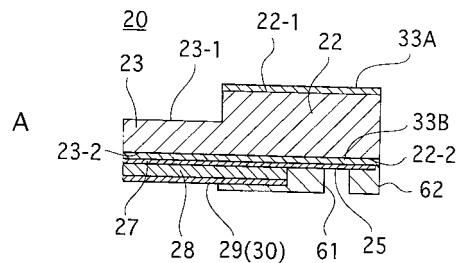

めっきバンプ法は、図 38 A に示すように端子部 25 上に所定の開口部 61 を有するめっきレジスト層 62 を形成する工程と、図 38 B に示すように金めっき処理により各開口部 61 内に金めっき層 26 を所定の高さまで成長させる金めっき工程と、めっきレジスト層 62 を除去する工程とを有する。なお、金バンプ形成工程においては、めっき処理の条件によって形成される金バンプ 26 の厚み(高さ)に限界があり、所望の高さを有する金バンプ 26 が形成し得ないこともある。金バンプ形成工程においては、1 回のめっき処理によって所望の金バンプ 26 を得られない場合に、第 1 層の金めっき層を電極とする 2 回めっき処理を施していわゆる段付き金バンプ 26 を形成するようにしてもよい。

40

#### 【0145】

なお、バンプ形成工程について、上述した方法に限定されず、半導体プロセスで実施されている例えば蒸着法や転写法等によってバンプ形成を行うようにしてもよい。また、振動素子製造工程においては、詳細を省略するが、金バンプ 26 と端子部 25 との密着性を向上させるために、TiW、TiN 等のいわゆるバンプ下地金属層が形成される。

#### 【0146】

##### [切断工程]

続いて、シリコン基板 21 から各振動素子 20 を切り分ける切断工程が実施される。切断工程においては、例えばダイヤモンドカッタ等によって基部 22 の対応部位を切り分けることによって、各振動素子 20 の切り分けが行われる。切断工程では、ダイヤモンドカ

50

ツタによって切断溝を形成した後に、シリコン基板21を折って切り分けが行われる。なお、切断工程は、砥石や研削によりシリコン基板21の面方位を利用して切断を行うようにしてもよい。

【0147】

上述した振動素子製造工程においては、例えば基部22を共通とし、この基部22の隣り合う側面に振動子部をそれぞれ一体に形成することによって2軸の検出信号を得る2軸一体型振動素子との比較において、シリコン基板(ウェーハ)21からの取り数を大幅に向上させることを可能とする。

【0148】

[実装工程]

以上の工程を経て製造された振動素子20は、シリコン基板21の第2主面21-2側を実装面として、支持基板2の第1主面2-1上に表面実装法によって実装される。振動素子20は、各端子部25に設けられた金バンプ26を支持基板2側の相対するランド4に位置合わせされる。この際、振動素子20は、上述したように位置合わせ用マーク32が読み取られて、実装機により位置と向きを高精度に位置決めされる。

【0149】

振動素子20は、支持基板2に押圧された状態で超音波が印加され、各金バンプ26が相対するランド4に溶着されることで支持基板2の第1主面2-1上に実装される。支持基板2には、第1主面2-1上にIC回路素子7や電子部品8が実装され、振動素子20に対して後述する調整工程が行われた後、カバー部材15が取り付けられることで、振動型ジャイロセンサ1が完成する。

【0150】

以上のように、本実施の形態においては、基部22に振動子部23を一体に形成してなる多数個の振動素子20をシリコン基板21に一括して製作し、それぞれを個々に切り分けるようにしている。そして、支持基板2の第1主面2-1上に、同一形状の第1振動素子20Xと第2振動素子20Yとを90°異なる2軸上に実装することで、当該2軸の検出信号を得る振動型ジャイロセンサ1が作製される。

【0151】

[調整工程]

振動素子製造工程においては、上述したように誘導結合型プラズマを用いたエッチング処理を施してシリコン基板21から各振動素子20の振動子部23をそれぞれ高精度に切り抜くようとするが、材料取りの歩留まり等の条件によって各振動子部23がプラズマの出射中心線上に対して全て左右対称に位置して形成されることが困難である。このため、各振動素子20の位置ずれやその他種々の工程条件等によって各振動子部23の形状にバラツキが生じることがある。振動素子20は、例えば振動子部23の断面形状が台形状又は平行四辺形状に形成された場合に、正規の矩形形状の振動子部23との比較で垂直な上下振動からずれて中心軸線に対して質量が小さな側に傾いた状態で振動動作を行うようになる。

【0152】

そこで、振動子部23の所定箇所にレーザ加工を施して質量の大きな側を研削することによって振動状態を矯正する調整工程が施される。調整工程は、微細な大きさで形成される振動子部23の断面形状を直接視認することが困難であることから、切断した個々の振動素子20について所定の縦共振周波数で振動子部23を振動動作させて左右の検出信号の大きさを比較する方法によって、振動子部23の断面形状のバラツキを確認する。調整工程は、左右の検出信号に差異が生じている場合に、レーザ加工によって小さな検出信号を出力する側の振動子部23の一部を研削する。

【0153】

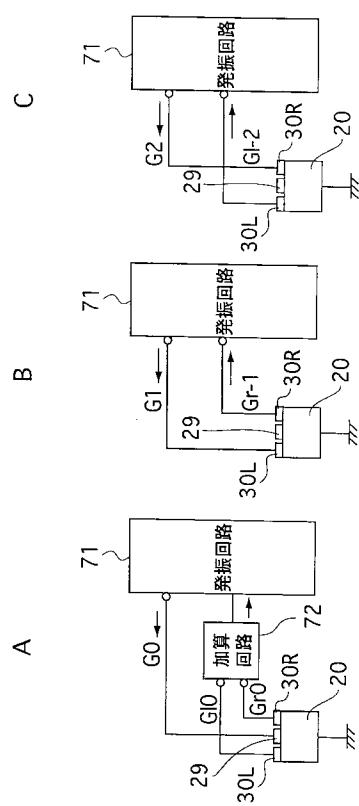

調整工程は、例えば対象とする振動素子20について、調整前に図39Aに示すように、発振回路71の発振出力G0を駆動電極層29に印加することによって振動素子20を縦共振状態で駆動させる。調整工程は、一対の検出電極層30L, 30Rから得る検出信

号 G<sub>1</sub>0, G<sub>r</sub>0 を加算回路 72 によって加算し、その加算信号を発振回路 71 に帰還させる。そして、検出電極 30L, 30R から得る検出信号 G<sub>1</sub>0, G<sub>r</sub>0 に基づいて、発振回路 71 の発振周波数を縦共振周波数 f<sub>0</sub> として測定するとともに検出信号 G<sub>1</sub>0, G<sub>r</sub>0 の差を差分信号として測定する。

【0154】

また、調整工程は、図 39B に示すように、発振回路 71 の発振出力 G<sub>1</sub> を検出電極 30L に印加することによって振動素子 20 を横共振状態で駆動させる。調整工程は、検出電極 30R から得る検出信号 G<sub>r</sub>-1 を発振回路 71 に帰還させるとともに、検出信号 G<sub>r</sub>-1 に基づいて、発振回路 71 の発振周波数を横共振周波数 f<sub>1</sub> として測定する。なお、横共振周波数は、検出信号 G<sub>r</sub>-1 から得る横共振周波数 f<sub>1</sub> と検出信号 G<sub>1</sub>-1 から得る横共振周波数 f<sub>2</sub> とは等しいことから、検出電極 30L, 30R のいずれか一方の接続状態で行うようにすればよい。

10

【0155】

さらに、調整工程は、図 39C に示すように、発振回路 71 の発振出力 G<sub>2</sub> を検出電極 30R に印加することによって振動素子 20 を横共振状態で駆動させる。調整工程は、検出電極 30L から得る検出信号 G<sub>1</sub>-2 を発振回路 71 に帰還させるとともに、検出信号 G<sub>1</sub>-2 に基づいて、発振回路 71 の発振周波数を横共振周波数 f<sub>2</sub> として測定する。調整工程は、上述した各測定によって得た縦共振周波数 f<sub>0</sub> と横共振周波数 f<sub>1</sub>, f<sub>2</sub> の周波数差を離調度とし、離調度が所定の範囲であるか否かを判定する。また、調整工程は、検出電極 30L, 30R から検出される差分信号が所定の範囲であるか否かを判定する。

20

【0156】

調整工程は、上述した離調度や差分信号の判定結果に基づいて、その大きさから振動子部 23 に対する調整加工位置を決定してレーザ照射を行って一部を研削して調整を行う。調整工程は、以下同様の測定・レーザ加工を、離調度と差分信号とが目標値に達成するまで施す。

【0157】

調整工程には、スポット径を調整可能な波長 532 nm のレーザを出射するレーザ装置が用いられる。調整工程は、振動素子 20 の振動子部 23 に対して、例えば側面と第 1 主面 23-1 に跨る稜線部位に対して長さ方向の適宜の場所にレーザを照射することにより調整を行う。振動素子 20 は、振動子部 23 の基端部から先端部に向かうほどレーザ照射による調整の変化量が、周波数差、検出信号バランスとともに小さいことから、基端部側において粗調整を行い、先端部側で微調整を行うことが可能である。

30

【0158】

そして、この調整工程は振動素子 20 が支持基板 2 に実装された状態で行われるので、実装前に当該調整を行った際の実装後における再調整が不要となり、振動型ジャイロセンサ 1 の生産性を高められる。この場合、調整用レーザが照射される領域は振動子部 23 の上面 23-2 側であるため、実装後の調整作業性に優れている。また、この振動子部 23 の上面 23-2 は圧電層や電極層が形成されていない面であるため、レーザ加工時に発生する熱により圧電薄膜層 28 の特性が変化したり、分極状態が変化する等の影響を最大限防ぐことが可能である。

40

【0159】

ところで、振動型ジャイロセンサ 1 は、振動素子 20 が、駆動電極層 29 に対して駆動検出回路部 50 から所定周波数の交流電圧が印加されることによって、振動子部 23 が固有の振動数をもって振動する。振動子部 23 は、厚み方向である縦方向に縦共振周波数で共振するとともに幅方向である横方向にも横共振周波数で共振する。振動素子 20 は、縦共振周波数と横共振周波数との差である離調度が小さいほど高感度特性を有する。振動型ジャイロセンサ 1 は、上述したように結晶異方性エッチング処理や反応性イオンエッチング処理を施して振動子部 23 の外周部を精度よく形成することで高離調度化が図られている。

【0160】

50

振動素子 20 は、振動子部 23 の長さ寸法  $t_5$  の精度によって縦共振周波数特性に大きな影響が生じる。振動素子 20 は、上述したように振動子部 23 の長さ寸法  $t_5$  を規定する根元部位 43 が、結晶異方性エッティング処理を施すことによって形成されるダイヤフラム部 38 の (100) 面及び 55° の角度をなすエッティング傾斜面 133 である (111) 面と、平坦面である境界線とに「ずれ」が生じた場合に、この「ずれ」量に応じて離調度が大きくなってしまう。

#### 【0161】

すなわち、振動素子 20 は、かかる「ずれ」量が、結晶異方性エッティング処理時のシリコン酸化膜 33B 上に形成するレジスト膜パターンと、反応性イオンエッティング処理時のレジスト膜パターンの位置ずれが原因となる。したがって、振動素子 20 は、例えば工程中でシリコン基板 21 の第 1, 第 2 主面 21-1, 21-2 を同時に観察可能な両面アライナー装置により位置決めする対応を図るようにしてもよい。また、振動素子 20 は、シリコン基板 21 の第 1 主面 21-1 上や第 2 主面 21-2 上に適宜の位置決め用パターンやマークを形成し、これらを基準として他方主面の位置規制を行うアライメント装置によって位置決めする対応を図るようにしてもよい。振動素子 20 は、かかる位置決めの対応が支持基板 2 への実装工程に際しても適用可能である。

#### 【0162】

なお、振動素子 20 は、上述した「ずれ」量が約  $30 \mu m$  程度よりも小さな範囲であれば、縦共振周波数と横共振周波数とがほぼ一致する。したがって、振動素子 20 は、やや精度の高いエッティング工程を施すことによって実質的な「ずれ」量による離調度特性の低下を抑制することが可能であり、上述したアライメント装置を用いた対応を不要として製造される。

#### 【0163】

##### [バンプ接合の効果]

振動素子 20 は、支持基板 2 に対する固定方法や材料によって Q 値が決定される。振動型ジャイロセンサ 1 は、上述したように振動素子 20 が基部 22 に形成したそれぞれ所定の高さを有する複数個の金バンプ 26 によって支持基板 2 に実装したことにより、安定かつ高感度で振動子部 23 の振動動作が行われて高 Q 値化が図られている。

#### 【0164】

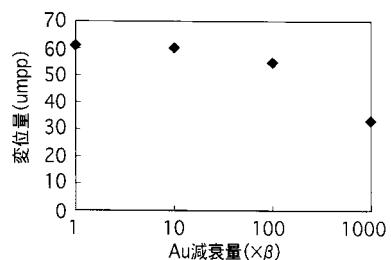

振動型ジャイロセンサ 1 について、以下、振動素子 20 の支持基板 2 に対する固定方法による Q 値特性の影響を、F E M (Finite-Element Method: 有限要素法) 解析法によって解析する。解析は、振動子部 23 をシリコン材によって製作するとともに支持基板 2 に対して金接合層 (金バンプ 26) によって固定した場合の、固定部分の減衰による振動子部 23 の先端部位における変位量 (この例では上振幅のピークと下振幅のピーク間の変位量 ( $\mu m p p$ )) を計算することによって固定方法の違いによる特性変化を解析した。シリコンの材料減衰 =  $3.54 \times 10^{-8}$ 、金接合層の材料減衰 =  $3.54 \times 10^{-8}$  を基準にした値をパラメータにして代入する。

#### 【0165】

振動素子 20 が基部 22 を支持基板 2 に対して金接合層を介して全面に亘って接合された場合の第 1 の解析を行った。この第 1 の解析により、図 40 に振動子部 23 の変位量の変動結果が得られた。振動素子 20 は、同図から明らかなように、A u の減衰量が大きくなるにしたがって振動子部 23 の先端部の変位が次第に減衰する。

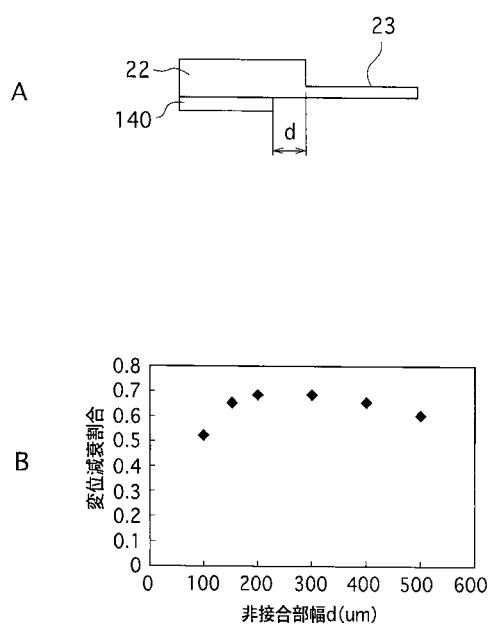

#### 【0166】

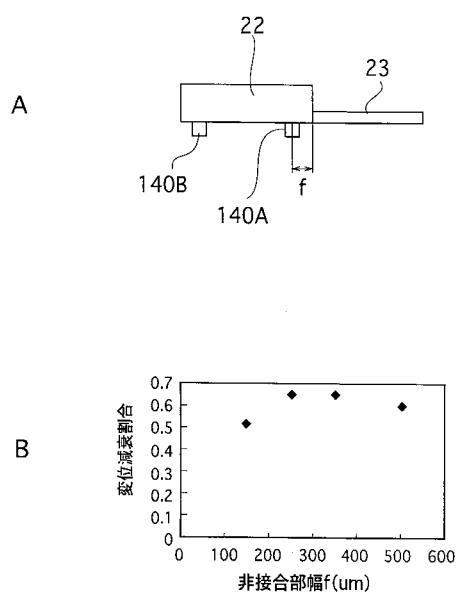

また、振動素子 20 が基部 22 を支持基板 2 に対して金接合層 140 を介して接合される場合の第 2 の解析を行った。この第 2 の解析は、具体的には、図 41A に示したように、振動子部 23 の基端部位において設けた幅  $d$  の非接合部の変化による振動子部 23 の変位減衰割合の変化を解析するものであり、図 41B に示す結果が得られた。振動素子 20 は、図 41B から明らかなように金接合層 140 の非接合部の幅が  $200 \mu m \sim 300 \mu m$  の範囲で変位減衰割合が大きくなる結果が得られた。ここで、変位減衰割合は、振動子の機械品質係数 Q 値に相当する値であり、数値が大きいほど優れており特定周波数において

10

20

30

40

50

て高い強度で発振する。以下、同様の意味で用いるものとする。

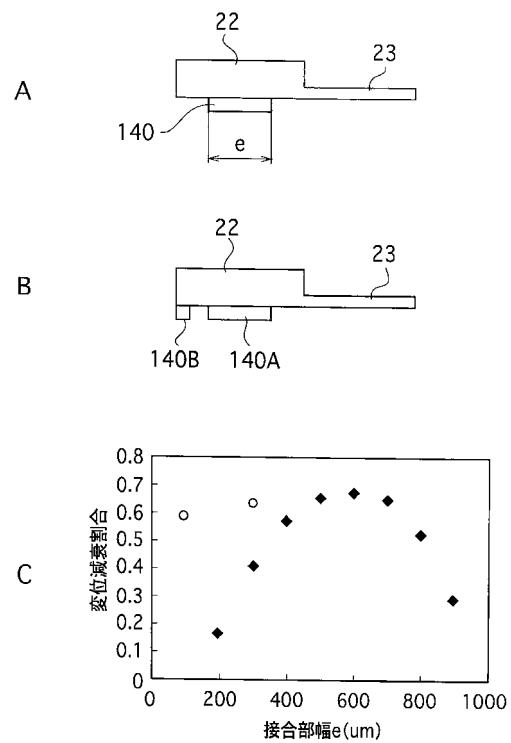

【0167】

さらに、振動素子20が基部22に対して金接合層140を介して接合する場合の第3の解析を行った。この第3の解析は、具体的には図42Aに示すように金接合層140の幅eの変化による振動子部23の変位減衰割合の変化を解析するものであり、図42Cに示す結果が得られた。また、第3の解析において、図42Bに示すように振動素子20が基部22に対して第1金接合層140Aと第2金接合層140Bとを介して接合される場合における解析も行った。

【0168】

図42Cは、1個の金接合層140による幅eの変化による振動子部23の変位減衰割合の解析結果を黒色四角印で示すとともに、第2金接合層140Bを追加した場合の解析結果を白色丸印で示している。振動素子20は、金接合層140の幅eが500μm~700μmの範囲で減衰割合が大きくなる結果を得る。また、振動素子20は、2箇所で固定することによって、金接合層140の幅eが小さい場合でも大きな減衰割合が得られるようになる。

【0169】

振動素子20においては、上述した第1~第3解析の結果から明らかのように、金接合層140により支持基板2上に接合される基部22が、全面で接合されるよりも第1金接合層140Aと第2金接合層140Bとの2箇所で接合されることが良好な特性を示す解析結果が得られる。第4の解析は、かかる解析結果に基づいて、図43Aに示すように基部22を第1金接合層140Aと第2金接合層140Bとの2箇所で支持基板2上に接合し、上述した第2の解析と同様に振動子部23の基端部位において設けた非接合部の幅fをパラメータとして振動子部23の変位減衰割合の変化を解析することによって第1金接合層140Aの最適位置を求めた。振動素子20は、図43Bに示すように第1金接合層140Aを振動子部23の根元位置から非接合部の幅fをほぼ250μmとして基部22を固定することによって、最適化が図られるとの解析結果が得られた。

【0170】

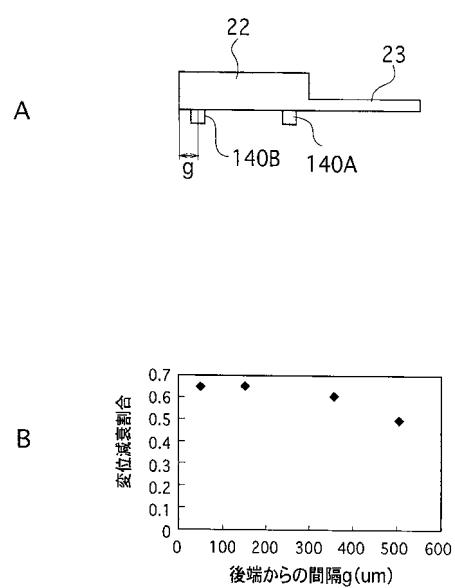

第5の解析は、上述した第4の解析に対して、図44Aに示すように基部22を第1金接合層140Aと第2金接合層140Bとの2箇所で支持基板2上に接合するが、第2金接合層140Bの最適位置を解析したものである。振動素子20は、第1金接合層140Aを基部22に対して上述した振動子部23の根元から250μmの最適位置を固定し、第2金接合層140Bについて基部22の後端部からの間隔gをパラメータとして振動子部23の変位減衰割合の変化を解析して最適位置を求めた。振動素子20は、図44Bに示すように、第2金接合層140Bが振動子部23の根元と対向する基部22の後端部から次第に振動子部23側へ近づくにしたがってこの振動子部23の変位減衰割合が小さくなる結果が得られた。したがって、振動素子20は、支持基板2に対して基部22を第1金接合層140Aと第2金接合層140Bの2箇所で固定する場合に、振動子部23の根元から250μmの位置とより後端部に近い位置とにおいて固定することによって最適化が図られるとの解析結果が得られる。

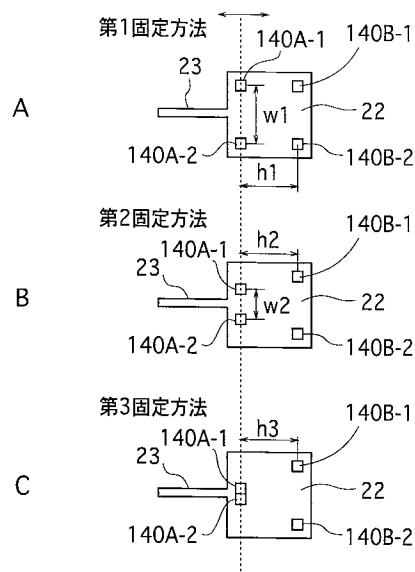

【0171】

振動素子20は、上述した第1~第5解析から、支持基板2に対する基部22の固定方法が全面固定よりも部分固定、1箇所固定よりも複数箇所固定である方が良好なQ値特性を得ることができることが明らかとなった。第6の解析は、支持基板2に対する基部22の固定方法を、図45Aに示すように振動子部23の根元側を幅方向に離間した一対の第1金属層140A-1, 140A-2によって固定するとともに基部22の後端側において幅方向に離間した一対の第2金属層140B-1, 140B-2によって固定する4点固定構造とした場合の解析である。第6の解析では、第2金属層140B-1, 140B-2を固定するとともに、第1金属層140A-1, 140A-2の相対する間隔wと第2金属層140Bとの間隔hとをパラメータとして振動子部23の変位減衰割合の変化を解析することによって最適な固定位置の解析を行った。

10

20

30

40

50

## 【0172】

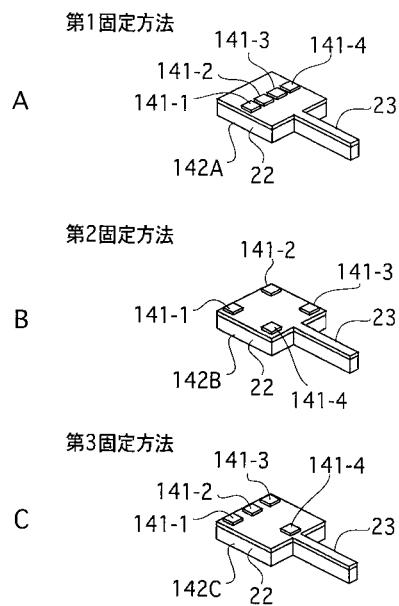

第6の解析は、図45Aに示すように、第1金属層140A-1, 140A-2を基部22の幅方向の両側に設けて相対する間隔をw1として支持基板2に固定する方法を第1固定方法とし、図45Bに示すように、第1金属層140A-1, 140A-2を中央部に近づけて相対する間隔をw2として支持基板2に固定する方法を第2固定方法とし、図45Cに示すように第1金属層140A-1, 140A-2を振動子部である中心部位において一体化して相対する間隔をw3=0として支持基板2に固定する方法を第3固定方法とする。

## 【0173】

振動素子20は、図46A及び図46Bに示すように支持基板2に対して基部22が第1金属層140A-1, 140A-2によって、振動子部23の根元に近い位置で基部22の幅方向の両側で固定される固定方法により最適化が図られるとの解析結果が得られる。なお、振動素子20は、第3固定方法によって支持基板2に対して基部22を固定した場合に極大をもつ。

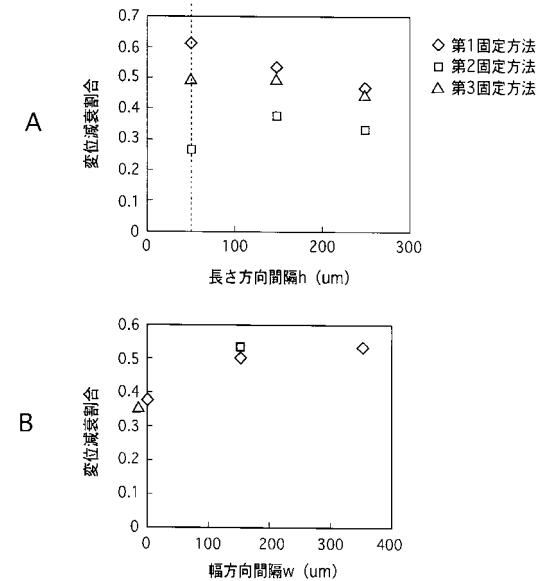

## 【0174】

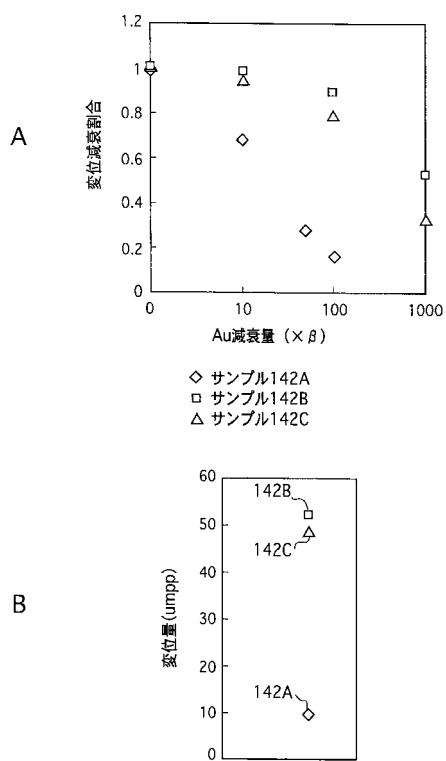

第7の解析は、図47Aに示すように、4個の金バンプ141-1~141-4によって支持基板2に対して基部22を固定した場合のFEM計算結果と測定結果とを解析したものである。第1の固定方法は、図47Aに示すように基部22の略中央部に4個の金バンプ141-1~141-4を横方向に1列に並べて固定した方法である。第2の固定方法は、図47Bに示すように基部22の四隅に4個の金バンプ141-1~141-4を配置して固定した方法である。第3の固定方法は、図47Cに示すように基部22の後端側に3個の金バンプ141-1~141-3を横方向に並べるとともに振動子部23の根元で幅方向の中央部に位置して1個の金バンプ141-4を配置して固定した方法である。

## 【0175】

図48Aは、横軸にAuの減衰量を、縦軸に振動子部23の変位減衰割合を示したFEM計算結果を示した図である。また、図48Bは、各固定方法を採用した振動素子142A~142Cの変位量(μmpp)の測定結果を示した図である。振動素子20は、図48A及び同図Bから明らかのように固定部位におけるAuの材料減衰が大きい場合でも四隅を金バンプ141-1~141-4によって固定したサンプル142Bが減衰に強い固定方法を構成している。

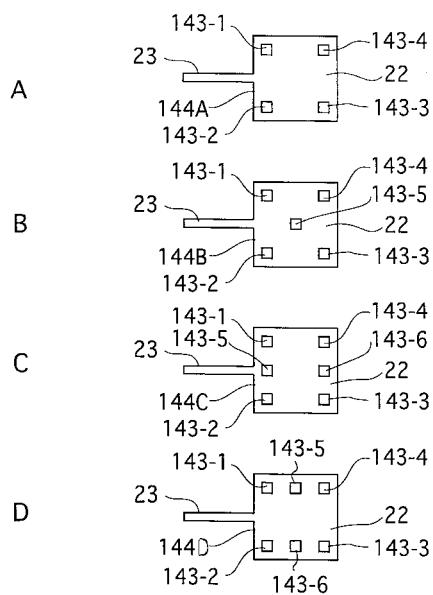

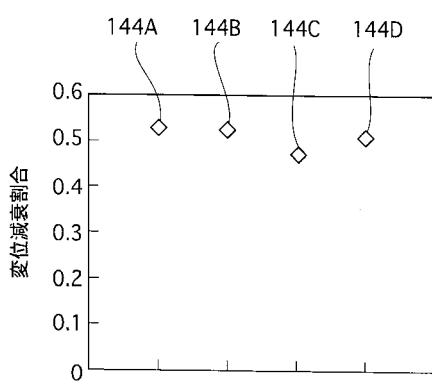

## 【0176】

第8の解析は、上述した第1解析~第7解析の解析結果を踏まえて、さらに多点箇所で振動素子20を支持基板2に対して固定する場合の優位性を検討した解析である。第8の解析では、図49に示すように、基部22に対して金バンプ143の数を異にして配置した第1サンプル振動素子144A~第4サンプル振動素子144Dについて、振動子部23の変位減衰割合の解析を行って図50に示す結果を得た。

## 【0177】

第1サンプル振動素子144Aは、基部22の四隅に配置された4個の金バンプ143-1~143-4を有している。第2サンプル振動素子144Bは、基部22の四隅に配置された4個の金バンプ143-1~143-4と、中央部に配置された1個の金バンプ143-5との合計5個の金バンプ143-1~143-5を有している。第3サンプル振動素子144Cは、基部22の四隅に配置された4個の金バンプ143-1~143-4と、振動子部23の延長線上で両側の金バンプ143の中央部に位置することによってそれぞれ横方向に3個ずつが配列された合計6個の金バンプ143-1~143-6を有している。第4サンプル振動素子144Dは、基部22の幅方向の両側に沿って縦方向に3個ずつが配列された合計6個の金バンプ143-1~143-6を有している。

## 【0178】

上述した第1サンプル振動素子144A~第4サンプル144Dにおいては、図50に示すように振動子部23の変位減衰割合について大きな差異はない。したがって、振動素

10

20

30

40

50

子 2 0 においては、支持基板 2 に対して基部 2 2 を多点で固定しても特性がさほど向上されないとの解析結果が得られた。

### 【 0 1 7 9 】

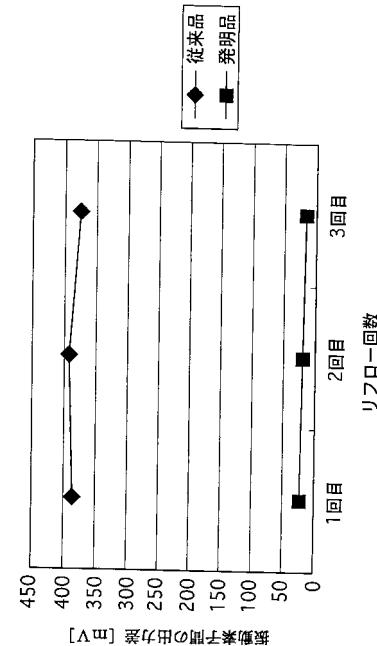

#### [ 負荷緩衝溝部の効果 ]

上述したように振動型ジャイロセンサ 1 , 1 7 0 においては、支持基板 2 , 1 7 1 に第 1 負荷緩衝溝部 1 2 , 1 7 2 や第 2 負荷緩衝溝部 1 4 からなる外部負荷の緩衝構造を形成して振動素子 2 0 による安定した角速度の検出動作が行われるように構成される。振動型ジャイロセンサ 1 においては、振動の角度方向により出力信号が基準値よりも大小の値を示すために、出力信号に予めオフセット電圧が印加されている。

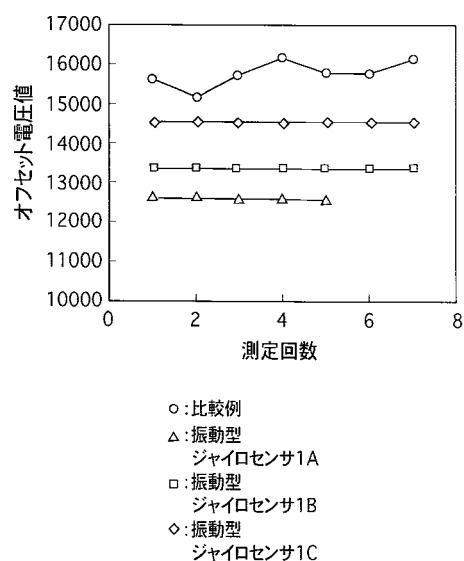

### 【 0 1 8 0 】

図 5 1 は、上述した緩衝構造の作用効果について、出力電圧の変動を測定した結果を示したグラフであり、この変動が小さいほど振動型ジャイロセンサ 1 が安定した状態で検出動作を行うことが裏付けられる。同図において、縦軸がオフセット電圧値 ( × 1 0 E - 4 V ) とし、横軸が測定回数である。比較例として示す支持基板 2 に第 1 負荷緩衝溝部 1 2 や第 2 負荷緩衝溝部 1 4 を設けずに振動素子 2 0 を実装した振動型ジャイロセンサは、印で示す変動状態となつた。

### 【 0 1 8 1 】

これに対して、支持基板 2 に枠状の第 1 負荷緩衝溝部 1 2 のみを形成した振動型ジャイロセンサ 1 A は、印の結果であった。また、第 1 負荷緩衝溝部 1 7 2 と区割り溝 1 7 3 とによって構成された個別実装領域 1 7 4 に端子部 2 5 をそれぞれ固定した振動型ジャイロセンサ 1 B は、印の結果であった。さらに、支持基板 2 の第 2 主面 2 - 2 に第 2 負荷緩衝溝部 1 4 を形成した振動型ジャイロセンサ 1 C は、印の結果であった。

### 【 0 1 8 2 】

図 5 1 から明らかなように、比較例振動型ジャイロセンサは、測定する毎にオフセット電圧値が大きく変動しており、外部負荷が振動素子 2 0 の検出動作に影響を与えて、検出精度が低下する。一方、支持基板 2 に第 1 負荷緩衝溝部 1 2 や第 2 負荷緩衝溝部 1 4 を形成した振動型ジャイロセンサ 1 A ~ 1 C は、いずれもオフセット電圧値の変動がほとんどなく、安定した特性が得られることが確認される。なお、第 1 負荷緩衝溝部 1 2 と第 2 負荷緩衝溝部 1 4 とを形成した振動型ジャイロセンサについても、同様にオフセット電圧値の変動がほとんどなく、安定した特性を有することは明らかである。

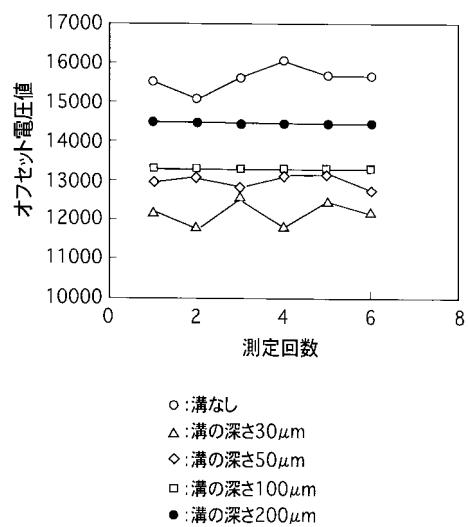

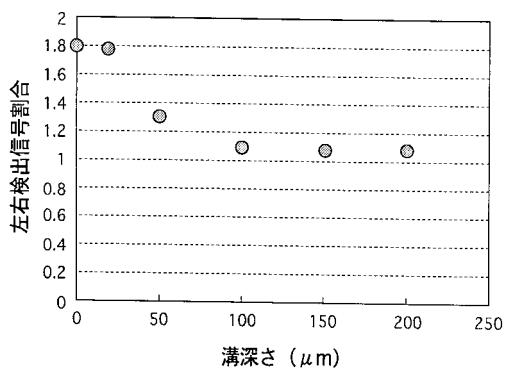

### 【 0 1 8 3 】

図 5 2 は、支持基板 2 に溝の深さを異にする枠状の第 1 負荷緩衝溝部 1 2 を形成し、同様にしてオフセット電圧値の変化を測定した結果を示したグラフである。同図において、印は、溝の深さが 0  $\mu$ m 、すなわち第 1 負荷緩衝溝部 1 2 が形成されていない振動型ジャイロセンサの測定結果を示す。同図において、印は第 1 負荷緩衝溝部 1 2 の溝の深さを 3 0  $\mu$ m とした振動型ジャイロセンサの測定結果を示す。また、同図において、印は第 1 負荷緩衝溝部 1 2 の溝の深さを 5 0  $\mu$ m とした振動型ジャイロセンサの測定結果を示し、印は第 1 負荷緩衝溝部 1 2 の溝の深さを 1 0 0  $\mu$ m とした振動型ジャイロセンサの測定結果を示し、印は第 1 負荷緩衝溝部 1 2 の溝の深さを 2 0 0  $\mu$ m とした振動型ジャイロセンサの測定結果を示す。

### 【 0 1 8 4 】

振動型ジャイロセンサにおいては、図 5 2 から明らかなように、第 1 負荷緩衝溝部 1 2 が 5 0  $\mu$ m 以下の深さではオフセット電圧値に変動が生じて安定した特性が得られない結果となつた。一方、振動型ジャイロセンサにおいては、第 1 負荷緩衝溝部 1 2 が 1 0 0  $\mu$ m を超える深さではオフセット電圧値の変動がほとんど無く、安定した特性を有することは明らかである。

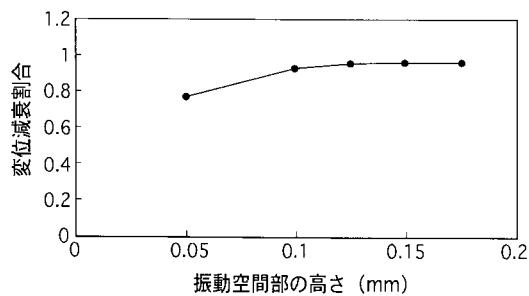

### 【 0 1 8 5 】

#### [ 間隔構成凹部の効果 ]

振動型ジャイロセンサ 1 においては、上述したように振動素子 2 0 の振動子部 2 3 に対して支持基板 2 の主面 2 - 1 に深さ k の間隔構成凹部 1 1 を形成することによって、振

10

20

30

40

50

動子部 23 と支持基板 2 との間に高さ  $m$  ( 図 2 参照 ) の振動空間部が構成される。振動型ジャイロセンサ 1 においては、上述したように振動素子 20 に駆動電圧が印加されることによって振動子部 23 が振動動作する。この振動素子 20 の縦方向と横方向との振動動作によって、振動空間部内に縦方向と横方向との空気流を生じさせる。縦方向の空気流は、間隔構成凹部 11 の底面に当たって反射して振動素子 20 の振動子部 23 側へと流れるようになる。縦方向の空気流は、振動素子 20 に対してその縦振動動作に抵抗するいわゆるダンピング効果を振動子部 23 に対して作用させる。

#### 【 0186 】

振動型ジャイロセンサ 1 においては、振動子部 23 が、上述したように金バンプ 26 の高さと間隔構成凹部 11 の深さ  $k$  とを加えた高さ  $m$  の振動空間部において振動動作することで、ダンピング効果の影響を低減されて高  $Q$  値をもって振動する。したがって、振動型ジャイロセンサ 1 においては、高  $Q$  値化が保持された振動素子によって高感度で安定した手振れ検出が行われるようになる。

#### 【 0187 】

振動型ジャイロセンサ 1 においては、例えば振動素子 20 が基部 22 の厚み寸法を 0.3 mm、振動子部 23 の厚み寸法を 0.1 mm に形成し、支持基板 2 に開口寸法が 2.1 mm × 0.32 mm であり深さ寸法  $k$  を変化させた間隔構成凹部 11 を形成した場合に、振動空間部の高さ  $m$  の変化と振動子部 23 の変位減衰割合の変化とが図 53 に示す特性を得る。振動素子 20 は、同図から明らかのように振動空間部の高さ  $m$  が 0.05 mm と極めて狭い場合に、振動子部 23 に対して大きなダンピング効果の影響が生じて変位減衰割合が 0.8 程度となる。振動素子 20 は、所定の  $Q$  値が得られない状態となり、特性が低下する。

#### 【 0188 】

振動素子 20 は、振動空間部の高さ  $m$  が大きくなるにしたがって振動子部 23 に対するダンピング効果の影響が低減されることによって、振動子部 23 の変位減衰割合が次第に大きくなる。振動素子 20 は、振動空間部の高さ  $m$  が 0.1 mm 程度になると振動子部 23 に対してダンピング効果の影響がほとんど作用しない状態となり、所期の  $Q$  値が得られるようになる。

#### 【 0189 】

勿論、振動空間部は、高さ  $k$  が振動素子 20 の最大振幅量、すなわち振動子部 23 の先端部における最大変位量の 1/2 よりも大きく、振動素子 20 を自由振動させることが条件である。振動空間部は、上述した特性図から、振動子部 23 の最大振幅量を  $p$  とすると、 $k = p/2 + 0.05$  ( mm ) の条件を満たす振動空間部を構成することによって振動素子 20 が所期の  $Q$  値によって駆動されることを可能とする。

#### 【 0190 】

上述した実施の形態においては、支持基板 2 の主面 2-1 に深さ  $k$  の間隔構成凹部 11 を形成することによって主面 2-1 と振動子部 23 の第 2 主面 ( 基板対向面 ) 23-2 との間に全体として高さ  $m$  の振動空間部を構成するようにしたが、本発明はかかる構成に限定されるものではない。振動型ジャイロセンサ 1 は、例えば間隔構成凹部 11 を支持基板 2 を貫通する矩形溝によって構成してもよい。振動型ジャイロセンサ 1 は、かかる構成によって金バンプ 26 を一般的な大きさで形成することを可能とし、全体としてさらに薄型化が図られるようになる。

#### 【 0191 】

##### [ 一対の振動素子の効果 ]

振動素子製造工程においては、上述したように基部 22 に振動子部 23 を一体に形成してなる多数個の振動素子 20 をシリコン基板 21 に一括して製作してそれぞれを切り分けるようとする。振動素子製造工程においては、支持基板 2 の主面上に 2 軸上に位置して実装されて 2 軸の検出信号を得る振動型ジャイロセンサ 1 に備えられる同一形状の第 1 振動素子 20X と第 2 振動素子 20Y とを製作する。

#### 【 0192 】

10

20

30

40

50

振動素子製造工程においては、例えば基部 2 2 を共通とし、この基部 2 2 の隣り合う側面に振動子部をそれぞれ一体に形成することによって 2 軸の検出信号を得る 2 軸一体型振動素子との比較において、シリコン基板（ウェーハ）2 1 からの取り数を大幅に向上させることを可能とする。各部が上述した寸法値を有する振動素子 2 0 と、同等の機能を有する 2 軸一体型振動素子とを製作した場合の取り数の比較を図 5 4 に示す。

【 0 1 9 3 】

振動素子 2 0 は、図 5 4 から明らかなように 3 cm 角のシリコン基板を用いた場合に総計 60 個（2 個使いとなることから振動型ジャイロセンサ 1 が 30 個分）が製作され、半導体プロセスの量産工程で一般に用いられる 4 インチ径のウェーハを用いた場合に総計 1 200 個（同 600 個分）が製作され、さらに 5 インチ径のウェーハを用いた場合には総計 4 000 個（同 2 000 個分）が製作される。一方、2 軸一体型振動素子は、3 cm 角のシリコン基板を用いた場合に総計 20 個が製作され、4 インチ径のウェーハを用いた場合に 300 個が製作され、さらに 5 インチ径のウェーハを用いた場合には総計 800 個が製作される。振動素子 2 0 は、材料の歩留まりを大幅に向上させて、コスト低減が図られるようになる。

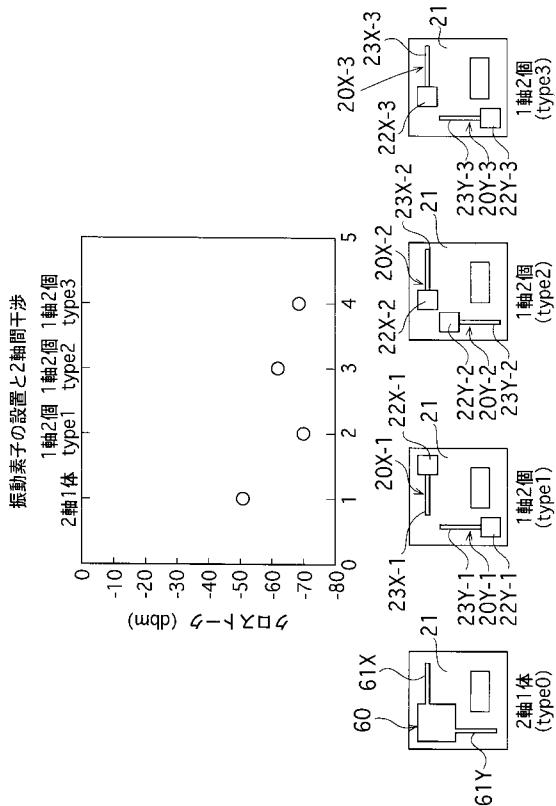

【 0 1 9 4 】

振動型ジャイロセンサにおいては、上述したように支持基板 2 に 2 軸の検出信号を得る第 1 振動素子 2 0 X と第 2 振動素子 2 0 Y とを直交する 2 軸上に位置して実装する。振動型ジャイロセンサ 1 においては、一方の振動素子の振動動作が他方の振動素子に影響を及ぼしていわゆる 2 軸間干渉の発生が考慮される。図 5 5 は、第 1 振動素子 2 0 X と第 2 振動素子 2 0 Y とを向きを変えて支持基板 2 に実装した場合に、クロストークを測定した結果を示す。

【 0 1 9 5 】

図 5 5においてタイプ 1 は、第 1 振動素子 2 0 X - 1 と第 2 振動素子 2 0 Y - 1 とが、それぞれの振動子部 2 3 X - 1 , 2 3 Y - 1 を互いに向き合うようにして支持基板 2 の対角位置のコーナ部に基部 2 2 X - 1 , 2 2 Y - 1 を固定されて実装される。タイプ 2 は、第 1 振動素子 2 0 X - 2 と第 2 振動素子 2 0 Y - 2 とが、同一コーナ部においてそれぞれの基部 2 2 X - 2 , 2 2 Y - 2 を固定するとともに振動子部 2 3 X - 2 , 2 3 Y - 2 を互いに直交する側縁に沿って延在させるようにして支持基板 2 に実装される。タイプ 3 は、第 1 振動素子 2 0 X - 3 があるコーナ部に基部 2 2 X - 3 を固定して振動子部 2 3 X - 3 を隣り合う一方のコーナ部に向けて支持基板 2 に実装するとともに、第 2 振動素子 2 0 Y - 3 が隣り合うコーナ部に基部 2 2 Y - 3 を固定して振動子部 2 3 Y - 3 を第 1 振動素子 2 0 X - 3 に向けて支持基板 2 に実装する。なお、同図には比較例として、上述した 2 軸一体型の振動素子（タイプ 0 ）60 についてのクロストーク値を示す。クロストークの単位は、d b m（デシベル実効値）である。

【 0 1 9 6 】

図 5 5 に示すように、タイプ 0 の振動素子 60 のクロストーク値は - 50 d b m、タイプ 1 の振動素子 2 0 X - 1 , 2 0 Y - 1 のクロストーク値は - 70 d b m、タイプ 2 の振動素子 2 0 X - 2 , 2 0 Y - 2 のクロストーク値は - 60 d b m、タイプ 3 の振動素子 2 0 X - 3 , 2 0 Y - 3 のクロストーク値は - 72 d b m であった。

【 0 1 9 7 】

本発明に係るタイプ 1 ~ 3 の振動型ジャイロセンサにおいては、タイプ 0 の 2 軸一体型の振動素子 60 に対して、実装状態にかかわらず最小でも - 10 d b m 程度の改善が図られる。振動型ジャイロセンサ 1 は、独立した 2 個の振動素子 2 0 を備えることによって、検出信号に対する 2 軸間の干渉信号が 1 mV 程度に抑えることができる。これに対して、2 軸一体型の振動素子を備えた振動型ジャイロセンサにおいては、検出信号に対する 2 軸間の干渉信号が 10 mV 程度となり、検出特性を低下させる。

【 0 1 9 8 】

また、本実施の形態の振動型ジャイロセンサ 1 においては、第 1 振動素子 2 0 X と第 2 振動素子 2 0 Y とをタイプ 1 のように配置して支持基板 2 に実装することによって、2 軸

10

20

30

40

50

間干渉が最も小さい結果を得た。振動型ジャイロセンサ1においては、支持基板2に対してもよいかなる位置に第1振動素子20Xと第2振動素子20Yとを搭載するようにしてもよいが、小型のIC回路素子7や多数個の電子部品8の実装や配線パターン5の引き回しを考慮すると、上述した各タイプのように支持基板2のコーナ部に基部22を固定して実装することが最も実装効率の向上が図られる。

### 【0199】

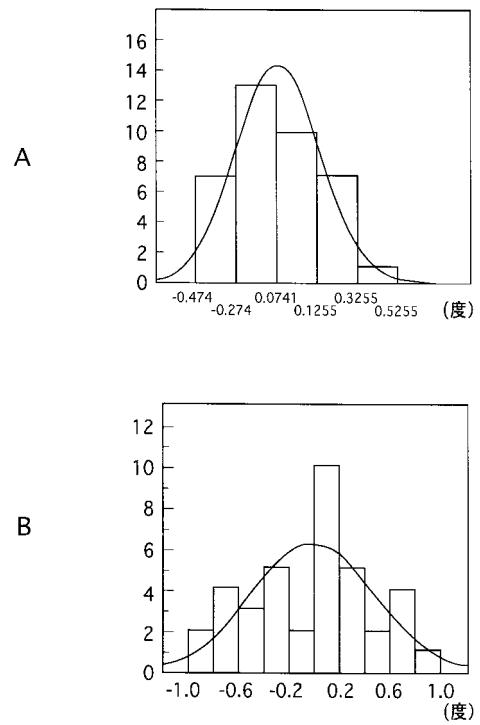

振動型ジャイロセンサ1においては、各振動素子20にそれぞれ位置合わせ用マーク32を設け、この位置合わせ用マーク32を認識して2個の第1振動素子20Xと第2振動素子20Yとを実装機によって支持基板2の直交する2軸上に互いに向き合う姿勢で実装する。振動型ジャイロセンサ1においては、各振動素子20の振動子部23が位置ずれを生じないようにして支持基板2に実装する必要がある。図56は、各振動素子20の位置ずれ（中心軸に対するずれ角度の分布）を表したヒストグラムであり、横軸はずれ角度（deg）、縦軸は数量である。位置合わせ用マーク32を認識して実装を行った場合を同図Aに、振動素子20の外形形状で認識して実装を行った場合を同図Bに示す。振動型ジャイロセンサ1においては、同図から明らかなように位置合わせ用マーク32によって高度の認識が行われることによって、各振動素子20が支持基板2に対して角度ずれ発生のバラツキも少なくかつずれ角度も小さい範囲で高精度に実装される。したがって、振動型ジャイロセンサ1においては、各振動素子20によって高精度かつ安定した手振れの検出動作が行われるようになる。

### 【0200】

#### [クロストーク]

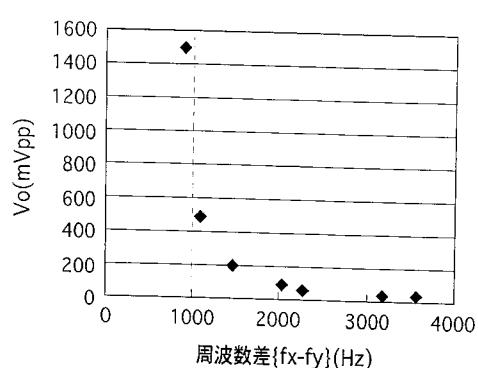

振動素子20の動作周波数は数kHzから数百kHzの範囲で設定可能であり、この2軸角速度センサ（振動型ジャイロセンサ1）では、2個の振動素子20X, 20Yの動作周波数（fx, fy）を変えて周波数差（fx - fy）による干渉信号の大きさを測定したところ、図57に示す結果が得られた。図57において、横軸は振動素子20X, 20Yの動作周波数差（fx - fy）、縦軸はセンサ出力（直流）に重畠される交流のノイズ成分Vo（ノイズを表す交流波形の上振幅ピークと下振幅ピーク間の大きさ）を示しており、ここでは軸間クロストークと称する。

### 【0201】

周波数差（fx - fy）が1kHz未満ではクロストーク値は1500mVpp以上に達して安定した角速度検出が行えなくなる。これに対して、周波数差を1kHz付近でクロストーク値は500mVppと著しく低減し始め、周波数差1.4kHzで200mVpp、2kHz以上で100mVpp以下にまで低下させることができる。図57の結果から、周波数差（fx - fy）を1kHz以上とすることにより軸間クロストークが顕著に低減することがわかる。2個の振動素子20X, 20Yの動作周波数（fx, fy）を1kHz離した2種類のサンプルを作製したところ、極めて安定に動作する2軸角速度センサを得ることができた。

サンプル1 第1振動素子20Xの動作周波数37kHz

第2振動素子20Yの動作周波数36kHz

サンプル2 第1振動素子20Xの動作周波数40kHz

第2振動素子20Yの動作周波数39kHz

### 【0202】

また、図57に示したように、周波数差（fx - fy）を2kHzから3kHzに設定することで、一対の振動素子20X, 20Y間のクロストークによる影響を回避することができる。従って、2kHz以上の周波数差をもって各振動素子20X, 20Yを駆動することで、センサ出力の更なる高精度化を図ることができる。

### 【0203】

また、本実施の形態の振動型ジャイロセンサは、これら振動素子20と本体機器側に内蔵される他の電子部品（センサ等）との間のクロストークによる影響も受ける場合があるが、このような影響が出ない周波数を振動素子の駆動周波数として選定できるように、駆

10

20

30

40

50

動周波数の異なる複数の振動素子を予め用意しておくのが好ましい。具体的には、駆動周波数が例えば35 kHz以上60 kHz以下の範囲で振動素子を複数種用意しておき、一对の振動素子間は勿論、本体機器に内蔵される他の電子部品とのクロストークを回避できる互いに1 kHz以上(好ましくは2 kHz以上)離れた2つの動作周波数の素子を選択する。

【0204】

次に、本発明の他の実施の形態について説明する。

【0205】

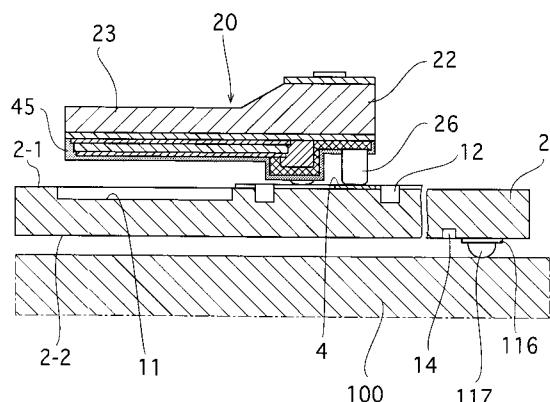

本発明に係る振動型ジャイロセンサ1は、図58に模式的に示すように、支持基板2の第1正面2-1に対して振動素子20が金バンプ26を介して実装されるとともに、この支持基板2の第1正面2-1にカバー部材15が組み込まれて部品実装空間部3が外部から遮蔽されている。このようにして作製された振動型ジャイロセンサ1は、支持基板2の第2正面2-2に形成された外部接続端子部としての実装端子部116を介して本体機器側の制御基板100に実装される。

10

【0206】

ここで、制御基板100の構成や物性等は、本体機器の種類によって異なるのが通常である。振動型ジャイロセンサにおいては、制御基板100の種類に限らず、常に所定の特性が得られる必要がある。また、制御基板100には他の様々な電子部品が搭載されるため、これら電子部品の実装時に振動型ジャイロセンサ1には少なからず歪みや応力が加えられる。特に、電子部品の実装にリフローはんだ付けが用いられる場合、制御基板100に加わる熱応力が原因で、図59にやや誇張して示すように、制御基板100側から振動型ジャイロセンサ1へ負荷が加わり、振動素子20と支持基板2との間の接合部に歪みや応力が加わる可能性が高い。こうなると、振動素子20は所期の接合構造が確保されなくなることから振動特性や検出感度が不安定となり、安定した角速度検出が困難になる。なお、本体機器側に作用する衝撃等の外部応力によっても上述と同様な問題が発生し得る。

20

【0207】

そこで、以下の各実施の形態では、制御基板100への他の電子部品のリフロー実装時や外部から加えられる衝撃等によって、振動素子20の振動特性が影響を受けにくい振動型ジャイロセンサの幾つかの構成例について説明する。なお、振動素子20の各部の寸法は上述の第1の実施の形態において説明したとおりである。

30

【0208】

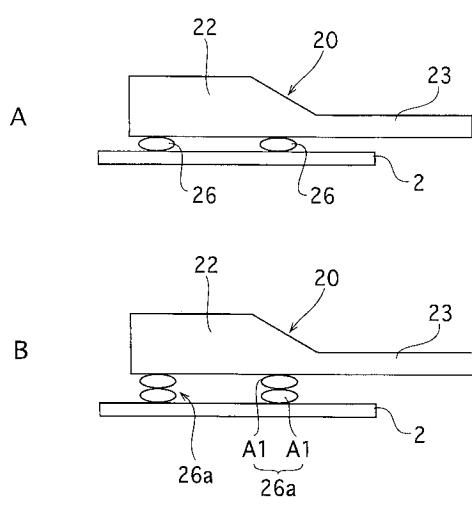

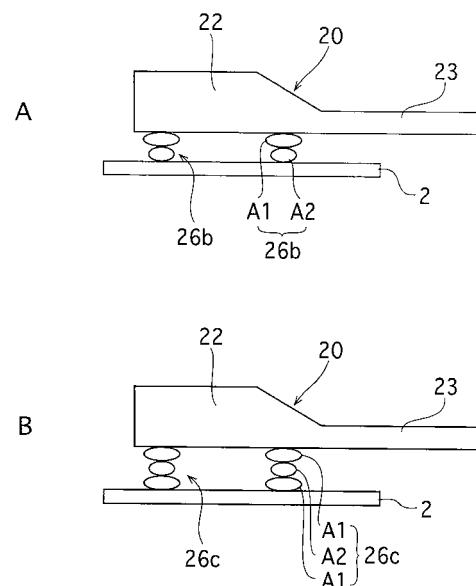

(第2の実施の形態：多段バンプ)

上述の第1の実施の形態では主に、図60Aに示すように振動素子20が単段の金バンプ26を介して支持基板2に実装される形態について説明した。本実施の形態では図60B及び図61A,Bに示すように、上記金バンプを複数段のバンプ構造として、接合強度を確保しながら振動素子に加わる応力を低減し、安定した振動特性と信頼性の高い検出精度が得られるようにしている。

40

【0209】

図60Bは、同一径のバンプA1を2段積み上げて金バンプ26aを構成した例を示している。この2段構造の金バンプ26aは単段の金バンプ26に比べて、振動素子20を支持基板2から更に高い位置に保持される。これにより、支持基板に伝達された外部応力が多段の金バンプ26aで減衰されて振動素子20へ伝えられることになる。このため、振動素子20は、外部応力の影響を受けにくくなり、安定した振動特性が確保されて信頼性の高い検出精度を得ることができる。

40

【0210】

多段バンプを構成する各バンプは径が同一のもので構成される場合に限らない。図61Aは、互いに径の異なる2つのバンプA1,A2を積み上げた金バンプ26bの構成を示している。この例では、バンプA1よりも小径のバンプA2を支持基板2側に配置した例を示している。各層のバンプ径は、要求される振動特性や接合強度等に応じて適宜設定することができる。また、多段バンプを構成する各バンプは2段構造に限らない。図61B

50

は、3段構造の金パンプ26cの構成を示している。この例では、小径パンプA2を一对の大径パンプA1で挟んだ構成となっている。

【0211】

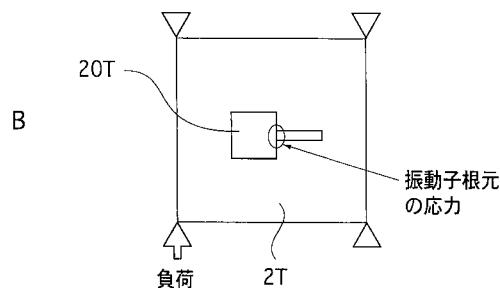

ここで、図60及び図61に示した構造の金パンプを介して振動素子が実装された支持基板モデルを作製し、支持基板に一定の負荷を与えたときの振動素子の挙動変化に加わる応力をシミュレーションにより計算した。

【0212】

各パンプA1,A2は、一般的なワイヤボンディングツールを用いて作製される。パンプA1,A2の径は、図62Aに示すように用いられるワイヤ(金線)の径(線幅)で決まり、線幅38μmの金線で径130μmのパンプA1が得られ、線幅25μmの金線で径90μmのパンプA2が得られた。試験条件は図62Bに示すように、厚さ0.5mmで一辺が7mmの正方形支持基板2Tの中央に振動素子20Tを実装し、支持基板2Tの3点の隅部を固定し、残る1点に基板厚み方向に一定量(ここでは10μm)変位させて振動子の根元に加わる応力を計算した。使用した応力解析ソフトは「ANSYS5.7」である。

【0213】

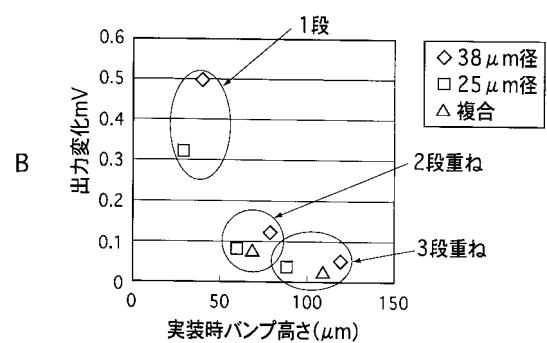

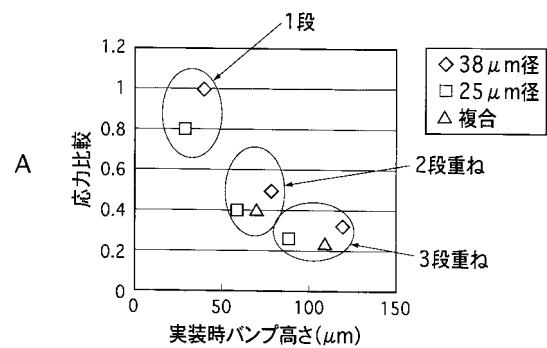

実装時のパンプ高さと振動子の根元に加わる応力との関係を図63Aに示す。パンプ段数が多く実装高さが高いほど、振動子根元部に作用する応力が低く、パンプ接合部での応力減衰効果が高いことがわかる。また、各段のパンプ径の異同は特に差異は特に認められなかった。

【0214】

また、実装時のパンプ高さと振動素子の出力変化との関係を図63Bに示す。ここでいう出力変化とは、本体機器側の制御実装に対する実装前後の基準出力の変動量を意味する。パンプ段数が多段になるほど出力変動が小さく、実装前後で安定した検出精度が得られている。特に、パンプ高さ50μm以上でセンサの出力変化が大幅に改善されている。パンプ高さを高くするが特性面では安定するが、逆に接合強度が低下するので使用範囲としては例えば100μm程度までが好ましい。

【0215】

(第3の実施の形態：パンプ位置)

上述の第1の実施の形態で説明したように、振動素子20は金パンプ26を介して支持基板2上に実装されている。しかしながら、金パンプ26を形成する位置によっては、本体機器側の制御基板から受ける応力で支持基板2に反りが生じた場合、この反りが振動素子20に大きく影響して振動モードが変化し、特性が低下するおそれがある。

【0216】

そこで本実施の形態では、振動素子20に形成される金パンプ26の位置を規定することにより、外部歪みが加えられても振動素子の安定な振動モードを維持し出力精度の低下を抑制するようにしている。

【0217】

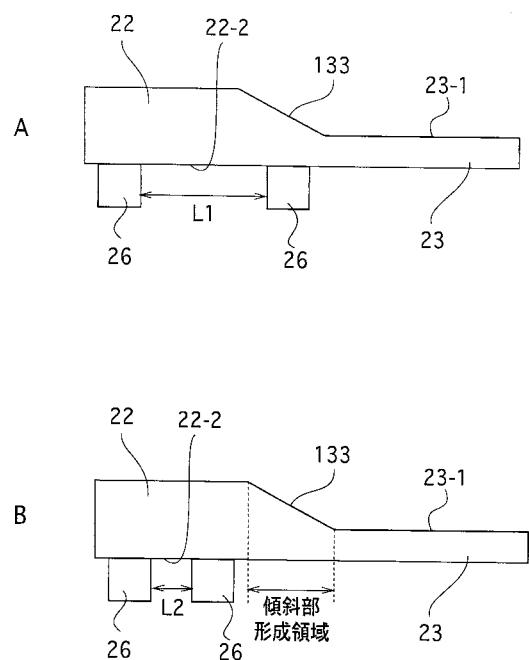

上述の第1の実施の形態で説明した振動素子は、図64Aに模式的に示すように、基部22の実装面22-2の四隅位置にそれぞれ金パンプ26が形成されていた。支持基板側から振動素子へ伝わる歪みや応力の大きさは、金パンプ26の配置間隔Lの大きさに依存し、Lが大きくなるほど振動素子に加わる歪みや応力は大きくなる。

【0218】

本実施の形態では、図64Bに示すように、金パンプ26の配置間隔L2が、図64Aに示した振動素子の配置間隔L1よりも短くしている。具体的には、本発明に係る振動素子は、振動素子23の上面23-1が基部22の上面22-1から傾斜部133(図19参照)を介して段落ち形成されているが、図64Aの例では、振動子部23側に位置する金パンプ26が基部22の実装面22-2において傾斜部133の形成領域に対応する領域に設けられている。これに対して本実施の形態では、図64Bに示すように、振動子23側に位置する金パンプ26は、基部22の実装面22-2において傾斜部133の非形

10

20

30

40

50

成領域に対応する領域に設けられている。

【0219】

また、上記のように振動子部23側に位置する金パンプ26を傾斜部133の非形成領域に対応する実装面22-2上の領域に設けることで、段階的に厚さが小さくなる傾斜部133の形成領域に対応する領域に比べて、歪みや応力が振動子部23に伝達されにくくすることができる。これにより、振動子部23の根元部位における応力集中を抑制して、振動子部23の振動特性の安定化を図ることが可能となる。

【0220】

以上のように、振動子部23に外部歪みや応力の影響を少なくするには、金パンプ26が振動子部23からできるだけ離れた位置に設けられることが好ましい。また、各金パンプ26の配置間隔を互いにできる限り近づけることで、外部からの歪みを振動子部23の先端まで伝播させないようにすることができる。

10

【0221】

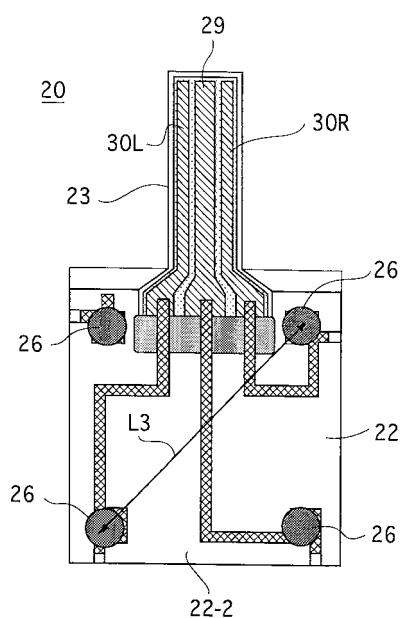

次に、図65に示すように、実装面22-2上において互いに対角位置にある金パンプ26間の距離（パンプ中心間距離）L3と、支持基板に荷重を加えたときの振動素子20の挙動の変化の様子を調べたところ、図66に示す結果が得られた。図66は、互いに対角位置にある金パンプ26間の距離L3に対する、振動素子20の左右の検出電極30L, 30Rから出力される検出信号の出力比を示している。測定方法は、制御基板として5cm角ガラスエポキシ基板中央に当該振動型ジャイロセンサをリフローはんだ付け法により実装した後、制御基板の3点を固定し残りの1点に対して加重を行い歪みを発生させたときの、左右検出信号の割合（出力が同一の場合は1）を測定した。

20

【0222】

図66に示されているように、対角線上の距離L3が750μm以上になると急激に外部歪みに対して敏感となり、振動モードが本来の垂直方向から変化させ左右の検出信号に差が出ることが確認される。これに対して、対角線上の距離L3が600μm以下の場合は、外部歪みに対して変化の度合が少ないことが確認される。

【0223】

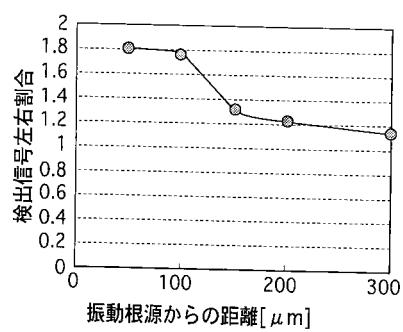

また、図67に示すように、実装面22-2上において振動子部23側に位置する金パンプ26の振動子部23の根元部位からの距離L4に対する、振動素子20の左右の検出信号の出力比を上述と同様な方法で測定したところ図68に示す結果が得られた。図68に示されるように、振動子部23の根元部位からの距離L4が150μmを超える範囲で外部歪みに対して検出信号の変化が起こりにくくなっていることが確認される。なお、この実験では、互いに対角位置にある金パンプ26間の距離は600μmに固定した。

30

【0224】

以上の結果より、本実施の形態の振動型ジャイロセンサが外部歪みの影響を少なくして本来の特性を維持するために必要な振動素子20上の金パンプ26の形成位置としては、互いに対角位置にある金パンプ26間の距離は600μm以下であること、あるいは、振動子部23の根元部位から150μm以上離して金パンプ26を配置することが重要である。

40

【0225】

（第4の実施の形態：負荷緩衝層）

上述の第1の実施の形態で説明したように、振動素子20は金パンプ26を介して支持基板2上に実装されている。しかしながら、本体機器側の制御基板から受ける応力で支持基板2に反りが生じた場合、この反りが振動素子20に大きく影響して振動モードが変化し、特性が低下するおそれがある。

【0226】

そこで本実施の形態では、支持基板2と制御基板100との間、あるいは振動素子20と支持基板2との間に、外部歪みが加えられても振動素子の安定な振動モードを維持することができる負荷緩衝層が設けられている。この負荷緩衝層は、外部歪みを吸収して振動素子20への伝播を抑制できるバッファ機能を有するものであれば、特に構成は限定され

50

ない。

【0227】

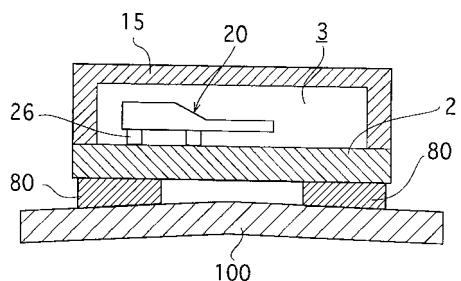

例えば図69に示す構成例は、振動型ジャイロセンサ1と制御基板100との間の電気的接続及び機械的接合を異方性導電層80を介して行うようにしている。この異方性導電層80としては、異方性導電フィルムが好適であるが、異方性導電ペーストあるいは異方性導電接着剤等でもよい。異方性導電材料は、樹脂母材中に導電粒子を分散させ加圧方向に導電性を発現させる機能性材料である。樹脂母材は固化後においても適度な弾性を有するとともに、制御基板100に実装される部品のリフロー温度（例えば250）に対して一定の耐熱性をもっているものが好ましい。

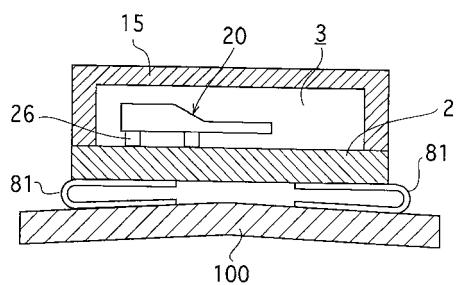

【0228】

一方、図70に示す構成例は、振動型ジャイロセンサ1と制御基板100との間の電気的接続及び機械的接合をフレキシブル配線基板81を介して行うようにしている。この種のフレキシブル配線基板には、ポリイミド等の耐熱性樹脂フィルム表面（又は表裏面）に配線層が形成された可撓性のあるプリント配線基板が用いられる。このフレキシブル配線基板81の可撓性を利用して制御基板100に作用した外部歪みを吸収し振動型ジャイロセンサ1の所期の特性維持を図ることができる。

【0229】

フレキシブル配線基板81は、同一表面に振動型ジャイロセンサ1及び制御基板100と接合される各々の接続端子が形成されており、裏面側に折り返されて両者間を接続している。これにより、振動型ジャイロセンサ1の実装面積の低減が図られている。これに対して、図71に示したフレキシブル配線基板82のように、一方の面に振動型ジャイロセンサ1を接続し、他方の面に制御基板100を接続してもよい。この場合、制御基板100に対する振動型ジャイロセンサ1の実装高さを低く抑えることができる。

【0230】

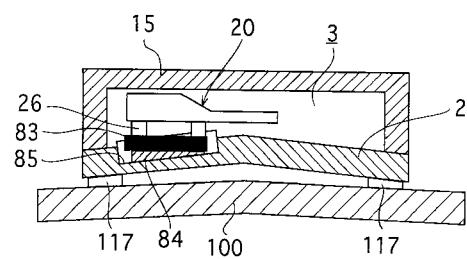

更に、図72に示す構成例は、支持基板2に対する振動素子20の実装形態が上述の各例と異なっており、振動素子20を一旦金パンプ26を介して支持板83に実装し、この支持板83を異方性導電層84を介して支持基板2に電気的かつ機械的に接合することで、支持基板2上に振動素子20を浮島状に実装している。支持板83としてはアルミニウム等の金属製基板やセラミック製基板など振動素子のQ値が充分得られるものであれば特に構成は限定されない。異方性導電層84は上述の例と同様に、支持基板2側から振動素子20側への歪みの伝播を吸収する機能を有する。なお、図示の例では、支持基板2に対する振動素子20の実装高さを抑えるため、支持基板2の実装領域には所定深さの凹所83が形成されている。

【0231】

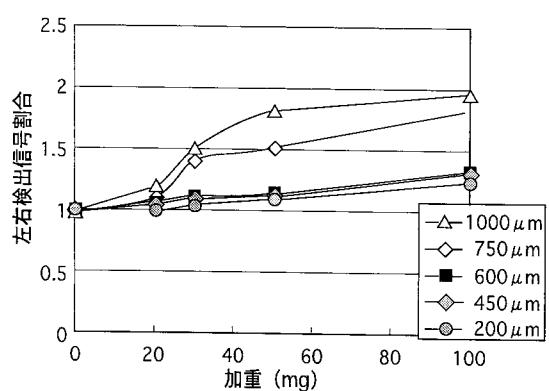

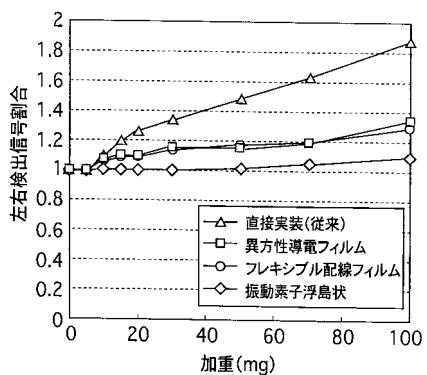

図73は、本実施の形態の構成の一実験結果を示している。実験は、制御基板100として5cm角ガラスエポキシ基板の4隅のうち3点は固定し残りの1点に対して加重を行って歪みを発生させたときの、振動素子20の左右検出信号の出力比を測定した。図73から、支持基板2に直接振動素子20を実装した場合には、荷重を加えて制御基板に歪みを加えると振動モードが変化して左右の検出信号バランスが大きく変化する。

【0232】

これに対して、振動型ジャイロセンサ1を異方性導電フィルムやフレキシブル配線基板を介して制御基板100に実装したり、支持基板2に対して振動素子20を浮島状に実装する場合の方が、信号の変化が小さいか殆ど認められず、制御基板100に与えた歪みが振動素子20に伝播しにくくなっていることが確認される。

【0233】

（第5の実施の形態：振動素子に溝形成）

上述の第1の実施の形態で説明したように、振動素子20は金パンプ26を介して支持基板2上に実装されている。しかしながら、本体機器側の制御基板から受ける応力で支持基板2に反りが生じた場合、この反りが振動素子20に大きく影響して振動モードが変化し、特性が低下するおそれがある。

10

20

30

40

50

## 【0234】

そこで本実施の形態では、振動素子20の実装面22-2に歪みの伝播を抑制する溝を形成することで、外部歪みが加えられても振動子部23の安定な振動モードを維持し、高い検出精度が得られるようにしている。

## 【0235】

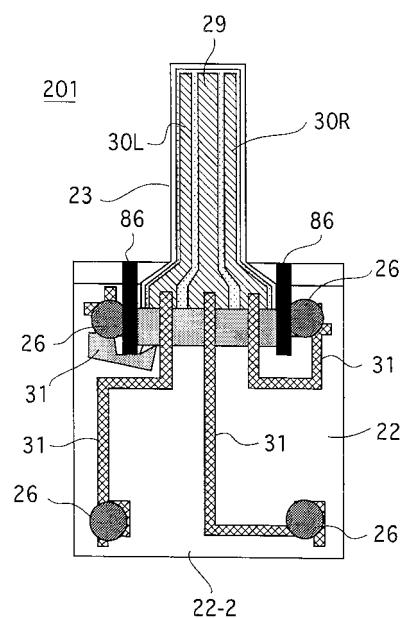

図74に示すように、振動素子201は、上述の第1の実施の形態と同様に、金バンプ26が形成される基部22と、この基部22から片持ち梁状に突出形成された振動子部23とを有している。基部22の実装面には、振動子部23に形成された基準電極や駆動電極29、左右の検出電極30L, 30Rと各端子部上の金バンプ26との間を電気的に接続するリード31がそれぞれ形成されている。

10

## 【0236】

そこで、本実施の形態の振動素子201においては、基部22の実装面22-2において振動子部23側に配置される一対の金バンプ26の形成位置（端子部形成位置）と、振動子部23の根元部位（基端部位）との間に、支持基板に接合された金バンプ26から振動子部23への外部歪みの伝播を抑制する溝86がそれぞれ形成されている。これらの溝86により、振動子部23を基部22から分離して外部歪みの影響を少なくし十分なS/N比（信号ノイズ比）を確保することができる。

20

## 【0237】

基部22に形成される溝86は、振動子部23側に配置される一対の金バンプ26の形成位置と、振動子部23の根元部位との間を結ぶ直線を跨ぐようにして、リード31や各種電極層が形成されない領域に形成される。図75は、支持基板に歪みを加えたときの振動素子の挙動の変化を測定したときの実験結果である。上述の第3の実施の形態と同様な測定方法で、溝86の形成深さと左右検出信号の出力比との関係を測定した。図75の結果から、溝深さが50μm以上、更に好ましくは100μm以上で左右検出信号差がなくなり、安定した垂直振動を維持できることが確認された。なお、溝深さ100μmは即ち、振動子部23の厚み寸法に相当する。

30

## 【0238】

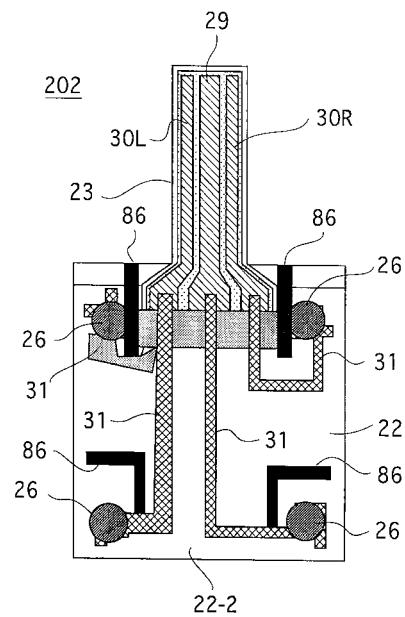

溝86の形成位置は、図74のように振動子部23側に位置する一対の金バンプ26の近傍にのみ形成される場合に限らず、図76に示す振動素子202のように、振動子部23側に位置した他の一対の金バンプ26にも同様に、振動子部23の根元部位と結ばれる直線を跨ぐ位置に同様な溝86が形成されてもよい。溝86の形状は、直線状に限らず、屈曲形状や湾曲形状等であってもよい。また、例えば図74に示したように溝86の一端部が基部22の側周部に臨むように形成することで、当該溝86による外部歪みの伝播抑制効果をより一層高めることができる。

30

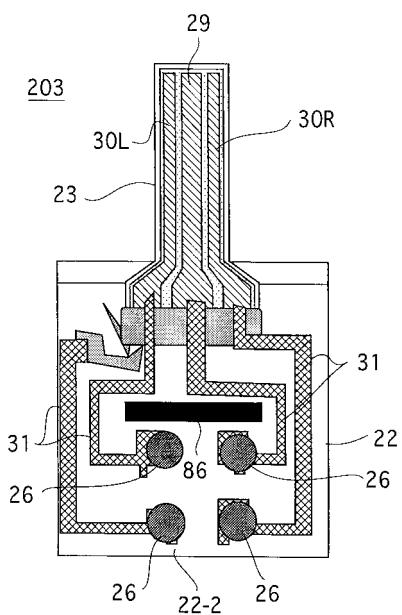

## 【0239】

そして、図77に示す振動素子202は、基部22の実装面22-2上に形成される金バンプ26の形成位置が互いに近接配置された例を示している。この例では、歪み伝播抑制用の溝86は、各々の金バンプ26と振動子部23の根元部位とを結ぶ直線を同時に跨ぐ位置に一箇所のみ直線状に形成されており、このような構成によつても図74及び図76に示した構成と同様な効果を得ることができる。

40

## 【0240】

（第6の実施の形態：IC回路素子の実装領域に溝形成）

上述の第1の実施の形態で説明したように、振動素子20は金バンプ26を介して支持基板2上に実装されている。図78A, Bに示すように、支持基板2は、振動素子20(20X, 20Y)のほかIC回路素子7等が混載され、これらの部品はリフローはんだ付け法によって実装される場合が多い。

## 【0241】

したがって、振動素子20のフリップチップ実装後にIC回路素子7等の多足部品がリフロー実装される際、支持基板2が熱応力で反りが生じ、振動素子20に影響を及ぼして振動モードを変化させ特性を低下させるおそれがある。また、振動素子20が搭載された

50

支持基板 2 を本体機器側の制御基板上にリフロー実装される場合、支持基板 2 上の I C 回路素子 7 の接合部が再度リフローし、その実装過程で生じる支持基板 2 の反り等が影響して振動素子 20 に影響を及ぼすことが考えられる。

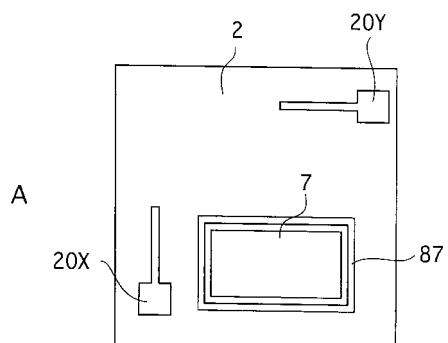

#### 【 0 2 4 2 】

そこで、本実施の形態では、図 7 9 A, B に示すように、支持基板 2 上の I C 回路素子 7 の実装領域を囲むように溝 8 7 を形成して、I C 回路素子 7 のリフロー実装時や支持基板 2 のリフロー実装時に発生する熱応力や歪が振動素子 20 の実装領域に伝播するのを抑制することで、振動素子 20 の振動特性の低下を阻止するようにしている。なお、この種の溝 8 7 は、I C 回路素子 7 の実装領域だけでなく、他の多足部品の実装領域にも同様に形成してもよい。

#### 【 0 2 4 3 】

図 8 0 は、溝 8 7 の形成深さの相違による支持基板 2 のリフロー回数と振動素子 20 の左右検出信号間の出力値変化との関係を示している。縦軸の出力値変化は歪みの伝播により振動素子の振動モードが変動して左右検出信号間の出力値変化（リフロー前は 0）の絶対値を示している。図 8 0 の結果より、I C 回路素子 7 の実装領域の周囲を囲むように溝 8 7 を 50  $\mu\text{m}$  以上の深さで形成することで、当該溝を形成しない場合に比べて、振動素子の出力値変化を抑えることができ、特に、溝 8 7 の形成深さを 100  $\mu\text{m}$  以上とすることで、振動素子 20 の出力値変化を抑制できる。

#### 【 0 2 4 4 】

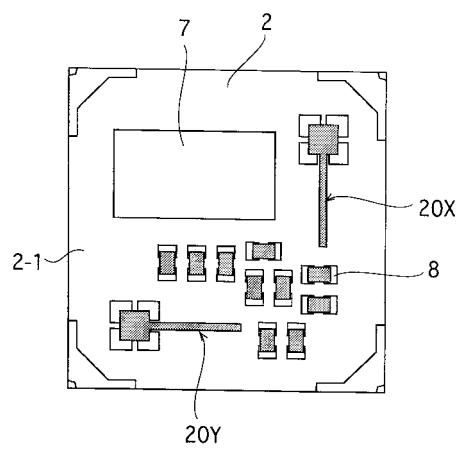

（第 7 の実施の形態：I C 回路素子の実装位置）

上述の第 6 の実施の形態に関連して、本実施の形態では I C 回路素子 7 の実装領域について検討する。

#### 【 0 2 4 5 】

上述の第 1 の実施の形態では、図 8 1 に示すように、I C 回路素子 7 は振動素子 20 (20 X, 20 Y) が実装される支持基板 2 のコーナー部とは異なるコーナー部近傍に実装されていた。また、支持基板 2 上に実装される他の電子部品 8 も偏った領域に集中していた。したがって、リフロー時における熱応力や熱歪みが支持基板 2 の面内に不均一に発生し、これが原因で一対の振動素子 20 X, 20 Y の実装領域に均等な熱応力等が作用しなくなることから、振動素子間ににおいて検出精度にバラツキが発生するおそれがある。

#### 【 0 2 4 6 】

そこで、本実施の形態では、図 8 2 に示すように、一対の振動素子 20 の実装領域間を結ぶ直線の中間領域に I C 回路素子の主要実装領域を定めている。これにより、I C 回路素子 7 のリフロー実装過程あるいは制御基板上の支持基板 2 のリフロー実装過程において支持基板 2 に作用する熱応力を、一対の振動素子 20 に対して均等に作用させることができとなり、振動素子間の特性差の発生を抑制することが可能となる。

#### 【 0 2 4 7 】

ここで、I C 回路素子 7 の実装領域は、図 8 2 に示すように平面視矩形状の I C 回路素子が一対の振動素子 20 の中間点（対称位置）に設定されることが好ましいが、実際的には、図示する I C 回路素子 7 の実装領域を中心とする一定の領域内に設定することができる。ここでいう一定の領域内としては、支持基板 2 の面内を第 1 ~ 第 4 の 4 つの象限に分けたときに、少なくとも各象限に I C 回路素子 7 の実装領域の一部が属する領域内であればよい。

#### 【 0 2 4 8 】

また、I C 回路素子 7 の実装領域とともに、その他の電子部品 8 についても図 8 2 に示すように各振動素子 20 に対して均等あるいは対称な位置に部品数及び部品実装領域を各自分散して設定するのが好ましい。これにより、I C 回路素子 7 だけでなく、他の電子部品 8 のリフロー過程において発生する応力をも、各振動素子 20 に対して均等に作用させることができとなる。

#### 【 0 2 4 9 】

図 8 3 は、I C 回路素子 7 の実装領域の相違による支持基板 2 のリフロー回数と一対の

10

20

30

40

50

振動素子間の出力差との関係を示している。振動素子間の出力差が小さいほど各振動素子に伝播する歪み量が一様であり、出力差が大きいほど各振動素子に伝播する歪み量の差が大きいことを意味している。なお、リフロー前は出力差は0である。IC回路素子7が支持基板2のコーナー部に偏って配置された比較例の構成(図81)の構成に比べて、図82に示した本発明の実施の形態の効果は歴然であり、振動素子間の出力差はほとんど認められなかった。

#### 【0250】

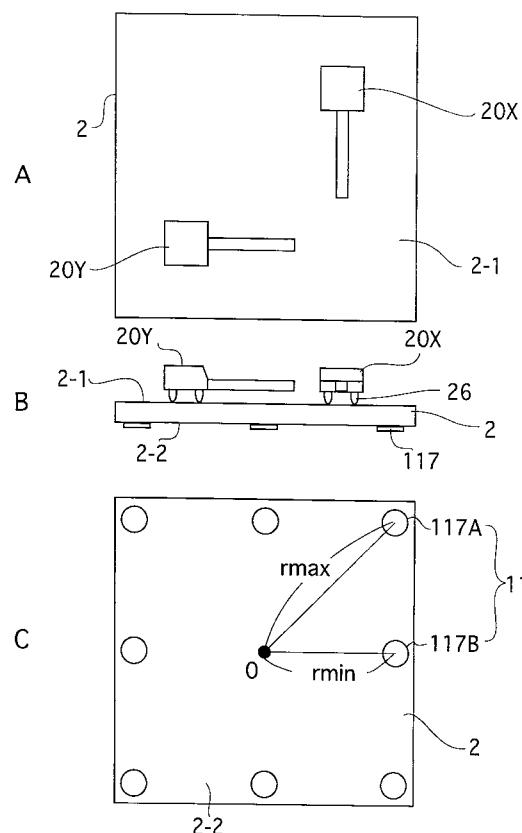

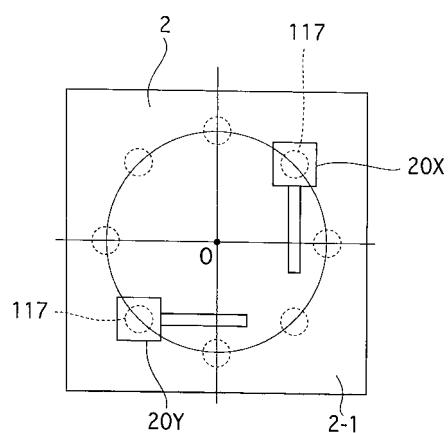

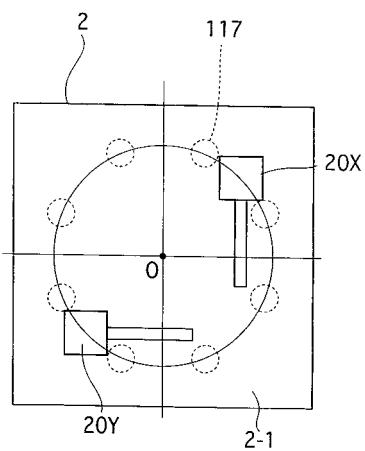

(第8の実施の形態：外部接続端子及び振動素子の配置領域)

振動型ジャイロセンサ1を構成する支持基板2は、図84A～Cに模式的に示すように、その第1主面2-1上に振動素子20(20X, 20Y)やIC回路素子等の電子部品(図示略)が実装され、反対側の第2主面2-2上には本体機器側の制御基板に実装される複数の外部接続端子部(実装端子部)117が設けられている。通常、支持基板2の中央部は内部回路の配線引き回し領域として用いる方が配線効率が良いため、外部接続端子部117は支持基板2の最外周に沿って配置される。

#### 【0251】

しかし、このような外部接続端子部117の配置構成では、支持基板2の中心部Oから各外部接続端子部117間の距離が大きくなり、支持基板2のリフロー実装過程での歪み量が大きくなる。また、図84Cに示すように、支持基板2の隅部に位置する外部接続端子部117Aの方が、支持基板2の各辺の中間部に位置する外部接続端子部117Bよりも、支持基板2の中心部Oからの距離が長い。このため、上記リフロー実装時において支持基板2の面内に作用する歪み分布が不均一となり、特に対角位置(四隅)付近の外部接続端子部117Aには歪みが集中することになる。

#### 【0252】

このように、図84に示す外部接続端子部117の配置例では、支持基板2のリフロー実装時に大きな歪みが発生し易く、支持基板2上の振動素子20に影響を及ぼすこととなっていた。

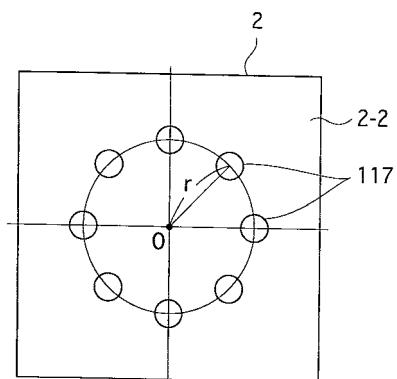

#### 【0253】

そこで、本実施の形態では、図85に示すように、支持基板2の第2主面2-2上に形成される複数の外部接続端子部117が、支持基板2上の同一円周上をそれぞれの主要形成領域とされている。特に図85の例では、支持基板2の中心Oを中心とする半径rの円周上に各外部接続端子部117が等角度間隔で形成されている。

#### 【0254】

このように、各外部接続端子部117を支持基板2の中心Oから等距離上に配置することで、支持基板2のリフロー実装時において支持基板2に発生する歪み分布を均一化できるとともに、支持基板に発生する歪み量の低減を図ることができる。これにより、支持基板2上の振動素子20に与える影響を少なくて、安定した振動検出を確保することができる。

#### 【0255】

なお、外部接続端子部117が配置される円周の半径rは、要求される実装精度(実装後の平行度、端子間距離)等を勘案し、可能な限り小さく設定するのが好ましい。

#### 【0256】

振動素子20は、図86A, Bに示すように、外部接続端子部117の形成領域よりも支持基板2の外周側に実装するのが好ましい。支持基板2に作用する歪み量は、外部接続端子部117の形成領域よりも内周側よりも外周側の方が小さいからである。これにより、振動素子20への影響を少なくすることができる。この場合、外部接続端子部117は同一円周上に配置されているのが好ましいが、これに限られない。

#### 【0257】

また、振動素子20は、各々の外部接続端子部117が配置される円周上に配置される構成でも構わない。但し、図87に示すように、振動素子20は外部接続端子部117の直上位置に実装されるよりも、図88に示すように、外部接続端子部117の非直上位置

10

20

30

40

50

に実装される方が好ましい。外部衝撃等を受けた際、これら外部接続端子部 117 を介して支持基板 2 に伝播されるため、外部接続端子部 117 の直上位置に振動素子 20 が実装されていると、振動素子 20 が受ける歪み量が大きくなり振動モードの安定化が困難となるおそれがあるからである。

【図面の簡単な説明】

【0258】

【図 1】本発明の第 1 の実施の形態による振動型ジャイロセンサのカバー部材を取り外して見たときの全体斜視図である。

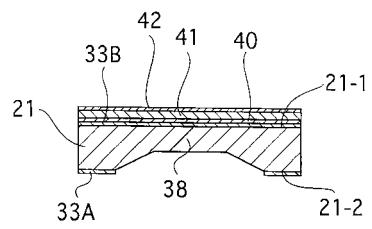

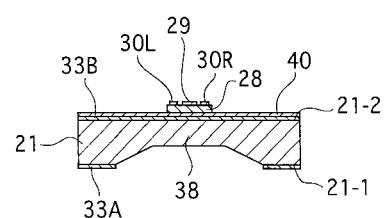

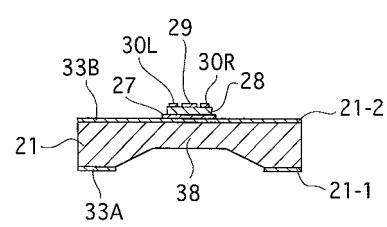

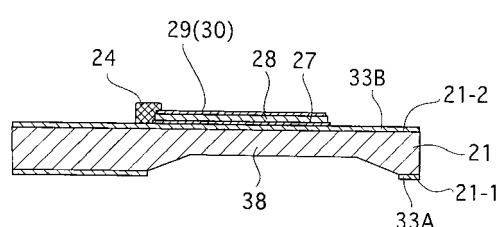

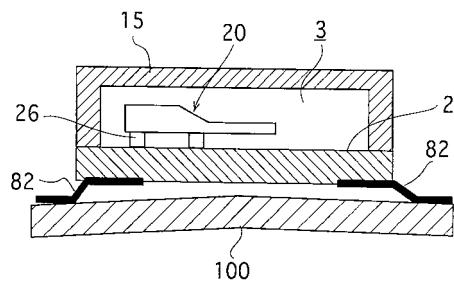

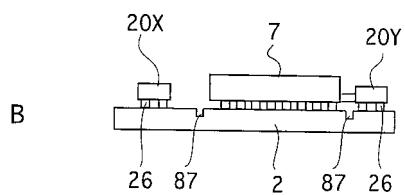

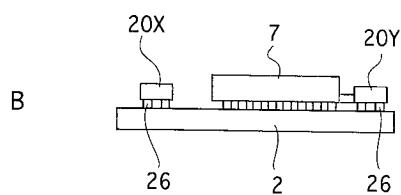

【図 2】振動型ジャイロセンサの振動素子の要部断面図である。

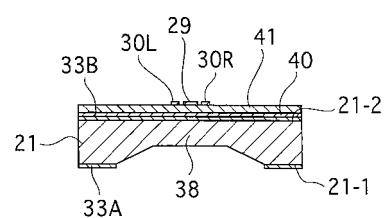

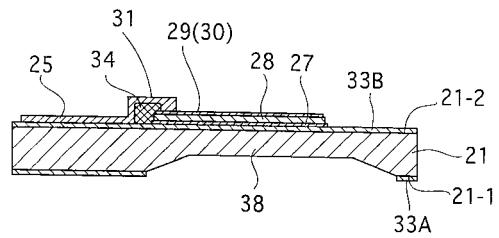

【図 3】振動型ジャイロセンサを制御基板へ実装したときの状態を示す振動素子の要部断面図である。 10

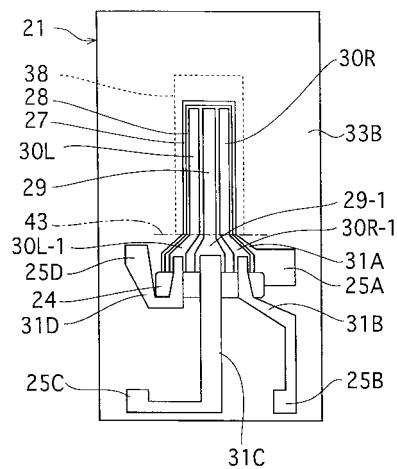

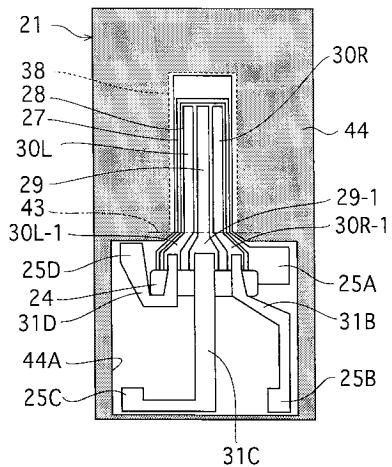

【図 4】振動素子の底面図である。

【図 5】振動型ジャイロセンサの底面図である。

【図 6】負荷緩衝溝部の構成の変形例を示す支持基板の平面図である。

【図 7】振動型ジャイロセンサの回路構成図である。

【図 8】振動素子の底面側から見た全体斜視図である。

【図 9】振動素子の振動子部の斜視図である。

【図 10】振動型ジャイロセンサの製造方法を説明する主要工程フロー図である。

【図 11】振動素子の製造工程に用いるシリコン基板の平面図である。

【図 12】同シリコン基板の断面図である。 20

【図 13】フォトレジスト層に振動素子形成部位をパターニングしたシリコン基板の平面図である。

【図 14】同シリコン基板の断面図である。

【図 15】シリコン酸化膜に振動素子形成部位をパターニングしたシリコン基板の平面図である。

【図 16】同シリコン基板の断面図である。

【図 17】振動子部の厚みを規定するダイヤフラム部を構成するエッチング凹部を形成したシリコン基板の平面図である。 30

【図 18】同シリコン基板の断面図である。

【図 19】エッチング凹部の拡大断面図である。

【図 20】ダイヤフラム部に第 1 電極層と圧電膜層と第 2 電極層とを積層形成した状態の要部断面図である。

【図 21】第 2 電極層に駆動電極層と検出電極とをパターニングした状態の要部平面図である。

【図 22】同要部断面図である。

【図 23】圧電膜層に圧電薄膜層をパターニングした状態の要部平面図である。

【図 24】同要部断面図である。

【図 25】第 1 電極層に基準電極層をパターニングした状態の要部平面図である。

【図 26】同要部断面図である。

【図 27】平坦化層を形成した状態の要部平面図である。 40

【図 28】同要部断面図である。

【図 29】基部形成領域にリードを形成した状態の要部平面図である。

【図 30】同要部断面図である。

【図 31】絶縁保護層形成用のフォトレジスト層を形成した状態の要部平面図である。

【図 32】絶縁保護層の第 1 アルミナ層を形成した状態の要部断面図である。

【図 33】絶縁保護層の酸化シリコン層を形成した状態の要部断面図である。

【図 34】絶縁保護層の第 2 アルミナ層及びエッチングストップ層を形成した状態の要部断面図である。

【図 35】振動子部の外形を形成する外形溝を形成した状態の要部平面図である。

【図 36】同振動子部の長手方向と垂直な方向から見た要部断面図である。 50

【図37】同振動子部の長手方向から見た要部断面図である。

【図38】めっきバンプの形成方法を説明する振動素子の側断面図である。

【図39】振動素子の調整工程の説明図である。

【図40】振動素子の支持基板に対する固定方法のFEM解析図であり、金バンプの減衰量と振動子部の変位量との関係を示す特性図である。

【図41】非接合部の幅と振動子部の変位減衰割合との関係を示す解析モデル図及び特性図である。

【図42】金接合層の幅と振動子部の変位減衰割合との関係を示す解析モデル図及び特性図である。

【図43】振動子側における金接合層の固定位置と振動子部の変位減衰割合との関係を示す解析モデル図及び特性図である。 10

【図44】基部の後端側における金接合層の固定位置と振動子部の変位減衰割合との関係を示す解析モデル図及び特性図である。

【図45】4箇所固定における金接合層の配置位置の解析モデル図である。

【図46】図45に示した各モデル図の特性図である。

【図47】4箇所固定構造を採用したサンプル振動素子における金接合層の配置位置を示す解析モデル図である。

【図48】図47に示した各モデル図の特性図である。

【図49】多点固定における金接合層の配置位置の解析モデル図である。

【図50】図49に示した各モデル図の特性図である。 20

【図51】負荷緩衝溝部によるオフセット電圧値の変動抑制作作用の特性図である。

【図52】負荷緩衝溝部の溝の深さによるオフセット電圧値の変動抑制作作用の特性図である。

【図53】間隔構成凹部により形成される振動空間部の高さと振動子部の変位減衰割合との関係を示す特性図である。

【図54】シリコン基板からの素子の取り数の比較図である。

【図55】振動素子の配置状態による2軸間干渉の特性図である。

【図56】実装工程における振動素子の角度ずれのヒストグラムであり、Aは位置合わせ用マークを認識して実装した場合、Bは外形認識により実装した場合を示す。

【図57】2個の振動素子の動作周波数を変えて周波数差による干渉信号の大きさを測定した結果を示す特性図である。 30

【図58】振動型ジャイロセンサが制御基板に実装された状態を示す断面模式図である。

【図59】図58において制御基板に外部歪みが加わったときの振動型ジャイロセンサの様子を説明する断面模式図である。

【図60】本発明の第2の実施の形態において説明する振動素子を模式的に示す側面図であり、Aは従来の振動素子を示し、Bは第2の実施の形態の振動素子を示す。

【図61】金バンプの構成の変形例を示す図である。

【図62】本発明の第2の実施の形態において説明する実施例の測定原理図である。

【図63】図62の実施例の結果を示す特性図である。

【図64】本発明の第3の実施の形態において説明する振動素子を模式的に示す側面図であり、Aは従来の振動素子を示し、Bは第3の実施の形態の振動素子を示す。 40

【図65】本発明の第3の実施の形態において説明する一実施例の説明図であり、振動素子の底面図である。

【図66】本発明の第3の実施の形態において説明する一実施例の測定結果を示す特性図である。

【図67】本発明の第3の実施の形態において説明する他の実施例の説明図であり、振動素子の底面図である。

【図68】本発明の第3の実施の形態において説明する他の実施例の測定結果を示す特性図である。

【図69】本発明の第4の実施の形態による振動型ジャイロセンサの概略側断面図である。 50

【図 7 0】本発明の第 4 の実施の形態による振動型ジャイロセンサの概略側断面図である。

【図 7 1】本発明の第 4 の実施の形態による振動型ジャイロセンサの概略側断面図である。

【図 7 2】本発明の第 4 の実施の形態による振動型ジャイロセンサの概略側断面図である。

【図 7 3】本発明の第 4 の実施の形態において説明する各実施例の測定結果を示す特性図である。

【図 7 4】本発明の第 5 の実施の形態による振動素子の底面図である。

【図 7 5】本発明の第 5 の実施の形態において説明する実施例の測定結果を示す特性図である。

【図 7 6】本発明の第 5 の実施の形態の変形例を説明する振動素子の底面図である。

【図 7 7】本発明の第 5 の実施の形態の変形例を説明する振動素子の底面図である。

【図 7 8】本発明の第 6 の実施の形態において説明する従来の振動型ジャイロセンサの要部の平面図及び側面図である。

【図 7 9】本発明の第 6 の実施の形態による振動型ジャイロセンサの要部の平面図及び側面図である。

【図 8 0】本発明の第 6 の実施の形態において説明する実施例の測定結果を示す特性図である。

【図 8 1】本発明の第 7 の実施の形態において説明する従来の振動型ジャイロセンサの要部平面図である。

【図 8 2】本発明の第 7 の実施の形態による振動型ジャイロセンサの要部平面図である。

【図 8 3】本発明の第 7 の実施の形態において説明する実施例の測定結果を示す特性図である。

【図 8 4】本発明の第 8 の実施の形態において説明する従来の振動型ジャイロセンサの要部の平面図、側面図及び底面図である。

【図 8 5】本発明の第 8 の実施の形態による支持基板の底面図である。

【図 8 6】本発明の第 8 の実施の形態による振動型ジャイロセンサの要部の平面図及び側面図である。

【図 8 7】本発明の第 8 の実施の形態において説明する振動素子の配置構成例を示す要部平面図である。

【図 8 8】本発明の第 8 の実施の形態において説明する振動素子の他の配置構成例を示す要部平面図である。

#### 【符号の説明】

##### 【0259】

1 … 振動型ジャイロセンサ、 2 … 支持基板、 2 - 1 … 第 1 主面、 2 - 2 … 第 2 主面、 4 … ランド、 5 … 配線パターン、 7 … I C 回路素子、 8 … 電子部品、 11 … 間隔構成凹部、 12, 14 … 負荷緩衝溝部、 15 … カバー部材、 20 … 振動素子、 21 … シリコン基板、 22 … 基部、 22 - 2 … 実装面、 23 … 振動子部、 23 - 2 … 基板対向面、 25 … 端子部、 26 … 金パンプ、 27 … 基準電極層、 28 … 圧電薄膜層、 29 … 駆動電極層、 30 … 検出電極、 31 … リード、 32 … 位置合わせ用マーク、 33 … シリコン酸化膜、 37 … エッティング凹部、 38 … ダイヤフラム部、 39 … 外形溝、 45 … 絶縁保護層、 46, 48 … アルミナ層、 47 … 酸化シリコン層、 50 … 駆動検出回路部、 80, 84 … 異方性導電層、 81, 82 … フレキシブル配線基板、 86, 87 … 溝、 100 … 制御基板、 133 … エッティング傾斜面

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図17】

【図16】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図3-3】

【図3-4】

【図3-5】

【図3-6】

【図37】

【図38】

【図39】

【図40】

【図4-1】

【図4-2】

【図4-3】

【図4-4】

【図45】

【図46】

【図47】

【図48】

【図49】

【図50】

【図51】

【図52】

【図53】

【図54】

|          | 3cm角基板 | 4in $\phi$ 基板 | 5in $\phi$ 基板 |

|----------|--------|---------------|---------------|

| 1軸振動素子   | 60(30) | 1200(600)     | 4000(2000)    |

| 2軸合体振動素子 | 20     | 300           | 800           |

【図55】

【図56】

【図57】

【図59】

【図58】

【図60】

【図61】

【図62】

A

|                           | 大 (A1) | 小 (A2) |

|---------------------------|--------|--------|

| 金線幅 ( $\mu\text{m}$ )     | 38     | 25     |

| ポール形状直径 ( $\mu\text{m}$ ) | 130    | 90     |

【図63】

【図64】

【図65】

【図66】

【図67】

【図68】

【図69】

【図70】