(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

19 March 2009 (19.03.2009)

PCT

(10) International Publication Number

WO 2009/034113 A1(51) International Patent Classification:

H01L 21/762 (2006.01)

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BI, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(21) International Application Number:

PCT/EP2008/062018(22) International Filing Date:

11 September 2008 (11.09.2008)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

0757511 12 September 2007 (12.09.2007) FR(71) Applicant (for all designated States except US):

S.O.I.TEC SILICON ON INSULATOR TECHNOLOGIES [FR/FR]; Parc Technologique des Fontaines, Chemin des Franques, F-38190 Bernin (FR).

(72) Inventors; and

(75) Inventors/Applicants (for US only): SOULIER BOUCHET, Brigitte [FR/FR]; 15 rue Lakanal, F-38000 Grenoble (FR). KERDILES, Sébastien [FR/FR]; 281, Impasse de Pageonièvre, F-38330 Saint-Ismier (FR). SCHWARZENBACH, Walter [FR/FR]; 19, Chemin du Mollard, F-38330 Saint Nazaire Les Eymes (FR).

(74) Agent: CABINET REGIMBEAU; 20, rue de Chazelles, F-75847 Paris Cedex 17 (FR).

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

## Declaration under Rule 4.17:

— of inventorship (Rule 4.17(iv))

## Published:

— with international search report

— before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

(54) Title: METHOD OF PRODUCING A STRUCTURE BY LAYER TRANSFER

FIG. 4

(57) **Abstract:** This invention relates to a method of producing a semiconductor structure by transferring a layer (32) of a donor substrate (30) to a receiver substrate (10), comprising the following stages : (a) creation of an embrittlement zone (31) in the donor substrate (30) so as to define the aforementioned layer (32), (b) treatment of the surface of the donor substrate (30) and/or the receiver substrate (10), so as to increase the bonding strength between the two substrates (c) direct wafer bonding of the donor substrate (30) to the receiver substrate (10), (d) detachment of the donor substrate (30) in the embrittlement zone (31), so as to form said semiconductor structure, in which the surface of the receiver substrate, except for a peripheral crown, is covered with the transferred layer (32). This method is notable in that at stage (b) treatment of the substrate surface is controlled, so that the increase in bonding strength between the donor substrate and the receiver substrate is lower in a peripheral area of these substrates than the increase in bonding strength in the central area of said substrates and in that said peripheral area has a width at least equal to the that of the crown and lower than 10 mm.

WO 2009/034113 A1

## METHOD OF PRODUCING A STRUCTURE BY LAYER TRANSFER

### FIELD OF THE INVENTION

5 This invention relates to a method of producing a structure by layer transfer. This method is especially used in the manufacture of SOI (silicon-on-insulator) structures using a SmartCut <sup>TM</sup> technique.

### BACKGROUND TO THE INVENTION

10 Smart Cut <sup>TM</sup> enables a fine layer of a donor substrate to be transferred to a receiver substrate and initiates the following stages:

a) Implantation of atomic species within the donor substrate, in order to create an embrittlement zone of the same depth as the thickness of the fine layer to be transferred.

15 b) Bringing into contact of the substrates and direct wafer bonding.

The entire surface of the substrates is bonded, except for the periphery, as the wafers exhibit edge roll-off (ERO) and are not therefore in contact around their periphery, as can be seen in Figure 1.

c) Detachment of the donor substrate in the embrittlement zone and transfer 20 of the fine layer to the receiver substrate.

The substrates generally occur in the form of circular wafers; for example, 300 mm wafers are currently in use.

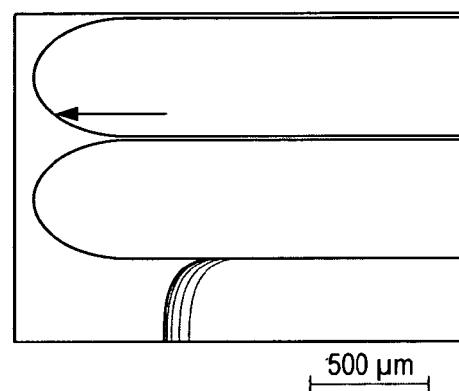

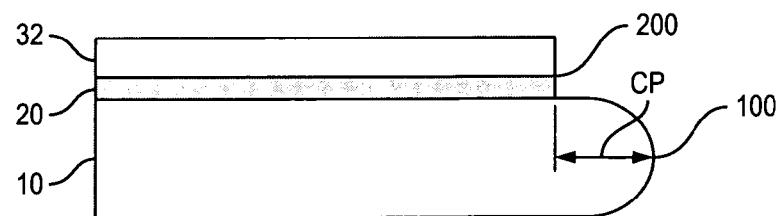

The peripheral area in which transfer of the fine layer has not taken place is called the crown. In relation to Figure 2, which shows a top view of four 25 peripheral areas of an SOI wafer, the crown CP is located between the perimeter 100 of the receiver substrate (outer edge of the crown) and the perimeter 200 of the transferred layer (inner edge). On the wafer in Figure 2, the crown CP is even, in other words the SOI perimeter is even.

Prior to direct wafer bonding, it is possible to bring about plasma activation 30 of the surface of at least one of the substrates. This activation enables the bonding strength to be improved significantly.

The bonding strength can also be improved by adapted cleaning prior to bonding, for example a type O<sub>3</sub>/SC1/SC2 sequence in which the SC1 is carried out at a temperature of under 50 °C.

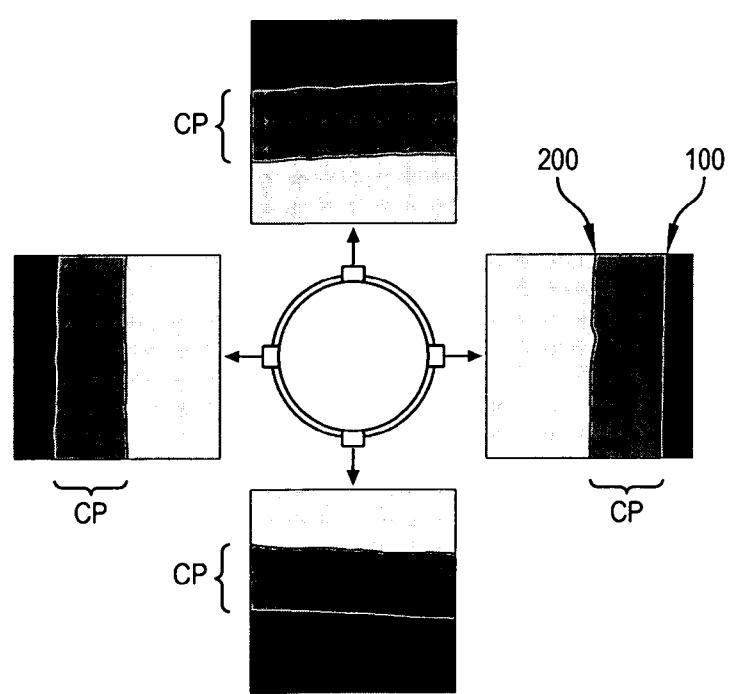

However, it has been found that improving the bonding strength can produce an uneven crown width (referred to in the jargon as a “jagged edge”) in the final product, in other words, the SOI obtained following detachment. What happens here is that following detachment, the crown also includes small 5 isolated zones that have also been transferred.

The width of the crown is therefore made uneven by the random, local enlargement of the transferred zone over several hundreds of micrometres towards the edge of the receiver substrate. The enlargement of the transferred zone is visible in the photos in Figure 3, where the lighter area represents the 10 transferred layer and the darker layer is the crown.

Document WO2007/06145 discloses a method for preventing the formation of edge voids in an SOI, which are non-transferred zones located preferentially at the periphery of the SOI.

One of the aims of the invention is therefore to improve the method of 15 producing a structure by layer transfer, so as to guarantee that the edge of the transferred layer is even, without any local enlargement.

## BRIEF DESCRIPTION OF THE INVENTION

A first object of the invention is a method of producing a semiconductor 20 structure by transferring a layer of a donor substrate to a receiver substrate, including the following stages:

- (a) creation of an embrittlement zone in the donor substrate, so as to define the aforementioned layer,

- (b) treatment of the surface of the donor and/or receiver substrate, so as 25 to increase the bonding strength between the two substrates,

- (c) direct wafer bonding of the donor substrate to the receiver substrate,

- (d) detachment of the donor substrate in the embrittlement zone, so as to form said semiconductor structure, in which the surface of the receiver substrate, except for a peripheral crown, is covered with the 30 transferred layer (32),

the aforementioned method being characterised in that at stage (b) treatment of the substrate surface is controlled, so that the increase in bonding strength between the donor substrate and the receiver substrate is lower in a peripheral area of these substrates than the increase in bonding strength in the central

area of said substrates and in that said peripheral area has a width at least equal to the that of the crown and lower than 10 mm.

According to other possible features of the invention:

- the bonding strength between the substrates is not increased in the peripheral area;

- 5 - the bonding strength in the peripheral area is at least 15% lower than the bonding strength in the central area of the substrates;

- said peripheral area has a width of between 0.2 and 10 mm;

- 10 - the method includes, prior to stage (b), the experimental determination of the width of the crown;

- experimental determination of the width of the crown involves producing a semiconductor reference structure by transferring a layer of donor substrate to a receiver substrate, comprising the following stages:

- a) creation of an embrittlement zone in a donor substrate, so as to define said layer,

- 15 b) treatment of the surface of the donor and/or receiver substrate, so as to increase the bonding strength between the two substrates

- c) direct wafer bonding of the donor substrate on the receiver substrate

- d) detachment of the donor substrate in the embrittlement zone, so as to 20 measure the width of the receiver substrate crown on said reference structure.

- according to a first embodiment of the invention, the treatment at stage (b) involves plasma activation wherein the peripheral area is not exposed to the plasma;

- 25 - according to a variant of the invention, stage (b) includes plasma activation or cleaning (preferably an SC1 cleaning carried out at a temperature of below 50°C) of the entire substrate surface followed by deactivation of the peripheral area, said deactivation being carried out by chemical etching of the peripheral area; for this purpose, an etching solution is dispensed by a jet onto the 30 peripheral area of the substrate while the substrate is rotated.

#### **BRIEF DESCRIPTION OF THE FIGURES**

Other features and advantages of the invention will emerge from the detailed description that follows in relation to the attached figures in which:

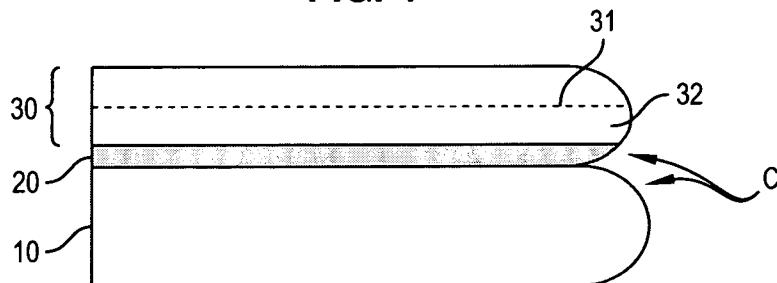

- Figure 1 is a photo of a section through two wafers showing the edge roll-off of the wafers at the start of the SOI crown

- Figure 2 is a top view of the edge of an SOI wafer showing an even crown

- 5 - Figure 3 is a photograph of the crown of a wafer displaying the jagged edge phenomenon

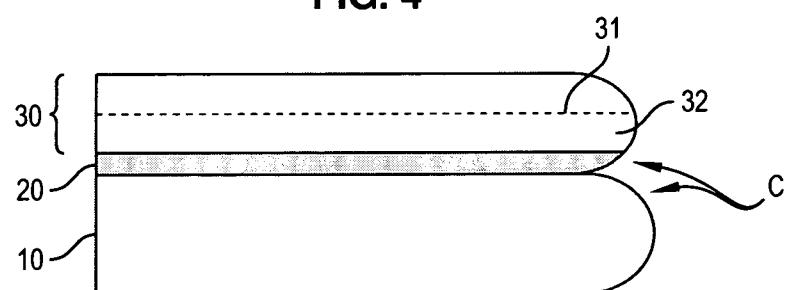

- Figure 4 is a sectional view of a structure after a donor substrate has been bonded onto a receiver substrate in the production of an SOI;

- Figure 5 is a sectional view of the above structure following the 10 detachment and transfer of a fine layer;

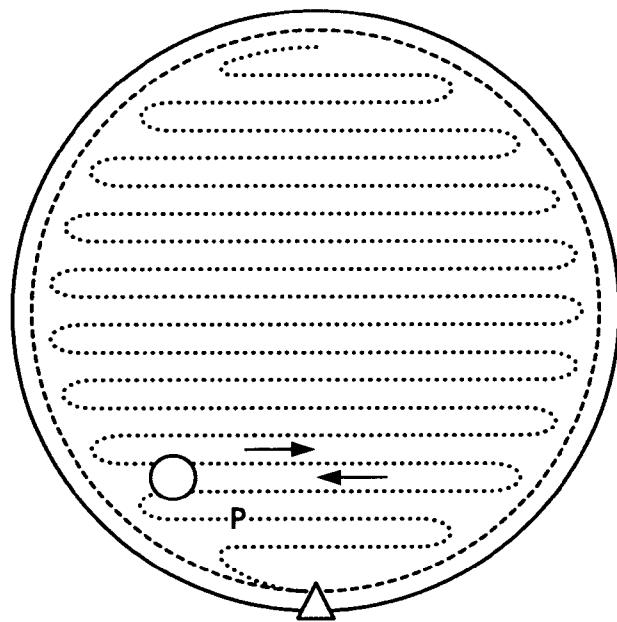

- Figure 6 illustrates a first embodiment of the invention;

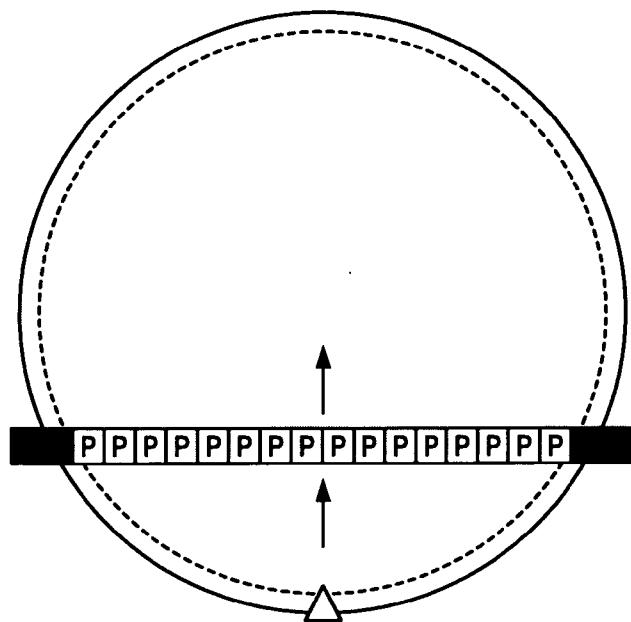

- Figure 7 illustrates a second embodiment of the invention;

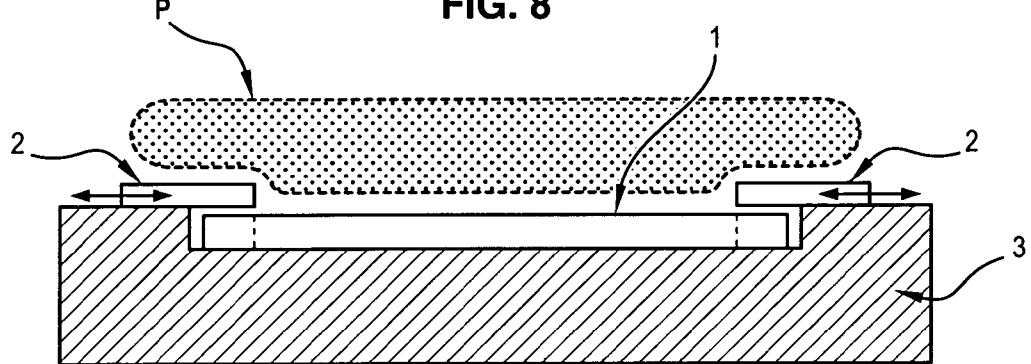

- Figure 8 illustrates a third execution of the invention;

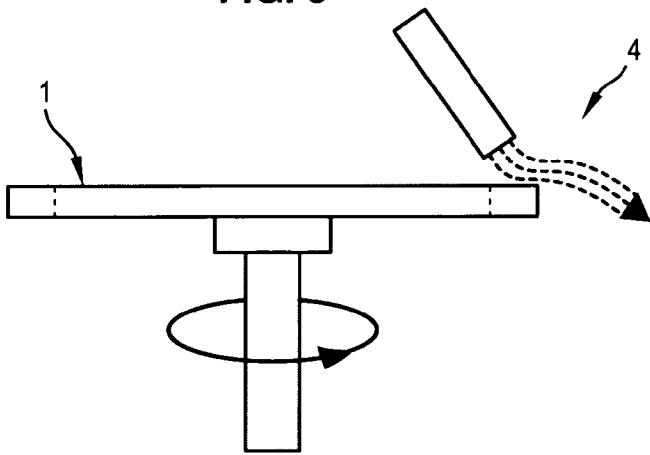

- Figure 9 illustrates a fourth embodiment of the invention.

15

## DETAILED DESCRIPTION OF THE INVENTION

### Notes on SOI wafers:

Figure 4 illustrates the structure obtained after a donor substrate 30 has been bonded to a receiver substrate 10.

20 When the Smart Cut™ technique is used, the donor substrate 30 may, for example, be covered with a layer 20 of oxide. In a manner familiar to the person skilled in the art, the oxide can be deposited or else formed by thermal oxidation of the donor substrate.

25 The donor substrate 30 then undergoes an implantation of atomic species, such as hydrogen and/or helium, for example, the dose and strength of which are adjusted so as to obtain an implantation peak at a depth matching the thickness of the layer of donor substrate to be transferred. Zone 31 into which the atomic species are implanted is called the embrittlement zone.

Once the surface of the donor substrate 30 and/or the receiver substrate 30 10 has undergone plasma activation, where appropriate, the substrates are brought into contact and direct wafer bonded.

The effect of the plasma activation is to increase the bonding strength between the two substrates.

This increase in bonding strength can also be obtained by means of O<sub>3</sub>/RCA cleaning prior to bonding, in which the SC1 is carried out at a temperature below 50 °C. This cleaning is well known to the person skilled in the art and will not therefore be described in detail here. It is simply pointed out 5 that RCA involves a sequence of baths referred to as SC1 and SC2. SC1 is a mixture of H<sub>2</sub>O, H<sub>2</sub>O<sub>2</sub> and NH<sub>4</sub>OH. SC2 is a mixture of H<sub>2</sub>O, H<sub>2</sub>O<sub>2</sub> and HCl. Rinsing stages in H<sub>2</sub>O are inserted between the SC1 and SC2 baths. O<sub>3</sub> cleaning corresponds to a first H<sub>2</sub>O bath in which the ozone gas is dissolved.

As can be seen in Figure 4, the wafers of the two substrates do not have 10 an edge that is perpendicular to the surface, but instead they display an edge roll-off, indicated by the arrows marked C. The substrates 10 and 30 are not therefore bonded right up to the edge, but up to the edge roll-off.

The donor substrate 30 is then detached along the embrittlement zone 31. To achieve this, the detachment can be started by mechanical force or an 15 increase in temperature; the detachment spreads across the entire surface in the form of a detachment wave. The SOI structure thereby obtained is represented in Figure 5. Due to the existence of the edge roll-off at the wafer edges, the part transferred from the donor substrate 30 does not extend over the entire surface of the receiver substrate 10, but only as far as the edge of a 20 peripheral crown CP.

For a 300 mm wafer, the peripheral crown CP is typically 1 mm wide relative to the edge of the wafer.

The jagged edge phenomenon revealed in the introduction is explained by the presence of transferred zones (in other words, oxide 20 and a fine layer 32) 25 within the peripheral crown CP.

In the plasma activation processes commonly used, the plasma activates the substrate's entire useful surface (referred to as the "front") and the wafer edges, but not the back, which is not exposed to the plasma, because it is sitting on an electrode.

30 Detailed description of the invention:

The jagged edge phenomenon would appear to be due to excessively strong bonding at the edge roll-off of the wafers.

In fact, in the event that bonding takes place following plasma activation or adapted cleaning of the donor and/or receiver substrate before bonding, the two

wafers adhere to one another more strongly, which reduces the width of the crown following transfer.

This is explained by the fact that the edge roll-offs are not prominent angles, but rather gradual curves of the wafer edge.

5 If the bonded wafer edges display local irregularities, the transfer following plasma activation reproduces these possible irregularities in the crown, leading to a jagged edge.

If there is no activation, the bonding does not spread to these uneven edges (although one cannot exclude the possibility of surface irregularities 10 existing further within the substrate, which are not revealed due to the local parallel configuration of the bonded surfaces) and the transfer produces crowns that are wider and, above all, more even, in other words, without jagged edges.

In general terms, the invention makes it possible to avoid the jagged edge phenomenon by controlling the activation or cleaning of the surface of the 15 substrate that has been treated, so as to control the bonding strength between the two substrates. It is envisaged, in fact, that if a weak bonding strength can be maintained or achieved around the periphery of the substrates, the risk of transferred zones emerging in the crown will be limited.

To this end, a first solution is to keep the bonding strength low in the 20 peripheral area by not carrying out activation in this area.

An alternative would be to reduce locally the higher bonding strength obtained by activation or by cleaning prior to bonding.

In both cases, the activation or cleaning prior to bonding is controlled, so that at the end the increase in bonding strength between the substrates is 25 weaker in the peripheral area than in the central area of these substrates. Typically, the bonding strength in the peripheral area will be at least 15% lower than the bonding strength in the central area of the substrates.

A first embodiment of the invention consists of the plasma activation of one and/or the other substrate being bonded over its (their) entire surface except for 30 the peripheral area.

A variant of the invention consists of plasma activation or cleaning before bonding of the entire surface of one and/or the other of the substrates to be bonded, followed by localised deactivation (prior to bonding) only in the peripheral area.

The peripheral area in which the deactivation or non-activation takes place will typically be between 0.2 and 10 mm wide, more particularly between 0.5 and 2.5 mm and preferably 2 mm.

5 This width typically corresponds to a width greater than or equal to that of the crown which, at the start of the detachment, generally displays a width of between 0.2 and 2 mm and more particularly between 0.8 and 1.2 mm.

In practical terms, it may be advantageous to produce a reference structure beforehand using the same procedure as for the structure it is hoped to obtain, in other words:

10 i) creation of an embrittlement zone in a donor substrate so as to define a layer,

ii) treatment of the surface of the donor and/or receiver substrate, so as to increase the bonding strength between the two substrates

iii) direct wafer bonding of the donor substrate on the receiver substrate

15 iv) detachment of the donor substrate in the embrittlement zone.

The width of the crown on the receiver substrate is then measured on this reference structure, after which the width of the peripheral area is determined, so that it is greater than or equal to the width of the crown measured on the reference structure.

20 It is likewise possible to proceed through repetition, in other words, by setting an arbitrary width for the peripheral area, 2 mm for example, then initiating the procedure described in the invention and measuring the width of the resulting crown. For the following structures, the width of the peripheral area is adjusted, so that it is greater than or equal to the width of this crown.

25

#### First embodiment: Non-activation of the peripheral area

A first possible embodiment of the invention involves conducting plasma activation before bonding, this being controlled so that the edges of one or both substrates subjected to the plasma are not activated by it.

30 Hence, the bonding strength between the substrates in this peripheral area increases to a lesser extent than in the central area, if it increases at all.

The initiation of this sort of plasma activation depends on the type of equipment used for the plasma treatment.

Where plasma is generated by a source that is smaller than the substrates to be treated, sweeping the whole surface routinely enables the entire substrate, including its periphery, to be uniformly treated.

The invention therefore involves modifying the sweeping action so that the 5 wafer edges are not treated with plasma, such as by sweeping the substrate surface excluding the few last millimetres from the edge, in other words, at least the width of the future crown, with a "punctiform" plasma source. A punctiform source refers here to a source with a surface area measuring a few mm<sup>2</sup>. Figure 6 illustrates this case: the dotted lines depict the trajectory of a 10 punctiform plasma source P sweeping the entire surface of the substrate except for the peripheral area.

In the case of plasma generated by a linear source longer than the greatest substrate dimension (i.e. the diameter in the case of circular wafers), movement in one direction makes it routinely possible to treat the whole surface 15 of the substrates uniformly in one or several sweeps.

The invention therefore involves splitting up this linear source into a succession of small punctiform sources and sweeping the surface to be treated by switching on the small sources only when they are not facing the periphery of the substrates.

20 With reference to Figure 7, the linear plasma source is made up of a succession of small punctiform sources P. The linear source is moved in the direction of the arrows. Only the P sources facing a zone to be activated are switched on (they are represented by the pale coloured squares). The sources opposite the edge (represented by black squares) do not produce any plasma, 25 so that the periphery is left untreated.

In the commonest case in which plasma is generated by a fixed source with a size comparable to the substrates, the invention involves eliminating or confining the plasma, so that it does not activate the periphery of the wafer 4.

To this end, the invention envisages, for example, confining the plasma by 30 preventing it from treating the edge of the wafer.

With regard to Figure 8, this confinement may be achieved, for example, by means of an annular screen 2 attached to the electrode 3 on which the substrate being treated 1 is placed and covering the edge of this substrate without touching it. This screen, the internal diameter of which is equal to the

diameter of the surface being activated, is designed to have the same potential as the electrode supporting the substrate. The space between the wafer and the screen overhanging it – the width of which is equal to the width of the peripheral area – will therefore be free from plasma P.

5 This screen may, for example, be made from the same material as the substrate being treated, a configuration that will make it possible to restrict contamination of the latter.

10 This screen, divided into two diametrically opposed, mobile sections, may be set in place before and removed after the plasma treatment, thereby facilitating manipulation of the substrates following in the equipment.

15 This screen need not necessarily be made from solid material; it may also be a grid in which the greatest mesh size is smaller than the Debye length, so that it is seen by the plasma as a solid material, but permits the circulation of neutral species (the use of a grid makes it possible to achieve fewer disturbances in the gas flow). The conductive material from which the skeleton of the grid is made can then be covered with a coating to prevent any contamination of the substrate – an Si or SiC film for Si substrates, for example.

#### Second embodiment: Deactivation of the peripheral area

20 According to a variant of the invention, the growth in bonding strength is achieved through plasma activation or adapted cleaning of the entire surface and of one and/or the other substrates to be bonded prior to bonding, followed by localised deactivation (prior to bonding) only in the peripheral area, for example with aid of chemical cleaning.

25 In fact, plasma activation involving surface modification to a depth of some tens of angstroms can be partly or completely destroyed by chemical etching of all or part of the plasma-modified thickness at the edges of the substrates, so as to achieve an even crown width.

30 Likewise, in the context of adapted cleaning prior to bonding, deactivation can be achieved by a slight increase in the micro-roughness of the surface in the peripheral area (average roughness typically increased in the order of 0.3 angstrom in the peripheral area).

From a practical point of view, in relation to Figure 9, with the aid of wet cleaning using a jet while the substrate 1 is rotating, the jet of chemical products

can be accurately directed only at the periphery of substrate 1, where the peripheral area is to be deactivated.

The chemical products dispensed are such that they will etch the material(s) present on the surface activated by plasma or cleaning. For 5 example, in the presence of SiO<sub>2</sub> a mixture based on NH<sub>4</sub>OH, H<sub>2</sub>O<sub>2</sub>, H<sub>2</sub>O can be used (e.g. SC1 diluted at 20-80 °C) or even a very dilute HF acid-based solution (e.g. HF 0.5% to etch 4nm followed by the dispensing of ozonised water, in order to restore the hydrophilia of the wafer edge prior to bonding).

The etching solution remains localised in the peripheral area, thanks to the 10 centrifugal force generated by the substrate's rotation.

## CLAIMS

1. Method of producing a semiconductor structure by transferring a layer (32) of a donor substrate (30) to a receiver substrate (10), comprising the following stages:

- 5 (a) creation of an embrittlement zone (31) in the donor substrate (30) so as to define the aforementioned layer (32),

- (b) treatment of the surface of the donor substrate (30) and/or the receiver substrate (10), so as to increase the bonding strength between the two substrates,

- 10 (c) direct wafer bonding of the donor substrate (30) to the receiver substrate (10),

- (d) detachment of the donor substrate (30) in the embrittlement zone (31), so as to form said semiconductor structure, in which the surface of the receiver substrate, except for a peripheral crown, is covered with the transferred layer (32),characterised in that at stage (b) treatment of the substrate is controlled, so that the increase in bonding strength between the donor substrate and the receiver substrate is lower in a peripheral area of these substrates than the increase in bonding strength in the central area of said substrates and in that said peripheral area has a width at least equal to the that of the crown and lower than 10 mm.

2. Method according to claim 1, characterised in that the bonding strength between the substrates is not increased in the peripheral area.

- 25 3. Method according to one of claims 1 or 2, characterised in that the bonding strength in the peripheral area is at least 15% lower than the bonding strength in the central area of the substrates.

- 30 4. Method according to one of the claims 1 to 3, characterised in that said peripheral area has a width of between 0.2 and 10 mm.

5. Method according to claim 4, characterised in that it includes, prior to stage b), the experimental determination of the width of the crown.

6. Method according to claim 5, characterised in that the experimental determination of the width of the crown involves producing a semiconductor reference structure by transferring a layer of donor substrate to a receiver substrate, comprising the following stages:

- a) creation of an embrittlement zone in a donor substrate, so as to define said layer,

- 10 b) treatment of the surface of the donor and/or receiver substrate, so as to increase the bonding strength between the two substrates

- c) direct wafer bonding of the donor substrate on the receiver substrate

- d) detachment of the donor substrate in the embrittlement zone, so as to measure the width of the receiver substrate crown on said reference structure.

15

7. Method according to one of claims 1 to 6, characterised in that the treatment at stage (b) is plasma activation wherein the peripheral area is not exposed to the plasma.

20

8. Method according to one of claims 1 to 6, characterised in that the treatment at stage (b) comprises wet cleaning comprising SC1 at a temperature below 50 °C or plasma activation of the entire surface of the substrate, followed by a deactivation by chemical etching of the peripheral area.

25

9. Method according to claim 8, characterised in that an etching solution is dispensed by a jet onto the peripheral area of the substrate while the substrate is rotated.

30

1/4

FIG. 1

FIG. 2

2/4

FIG. 3

FIG. 4

FIG. 5

**3/4**

**FIG. 6**

**FIG. 7**

4/4

FIG. 8

FIG. 9

# INTERNATIONAL SEARCH REPORT

International application No

PCT/EP2008/062018

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. H01L21/762

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H01L H01J

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                       | Relevant to claim No. |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | WO 2007/060145 A (SOITEC SILICON ON INSULATOR [FR]; KERDILES SEBASTIEN [FR]; DURET CARIN) 31 May 2007 (2007-05-31)<br>page 6, line 25 – page 21, line 29 | 1-9                   |

| A         | US 2006/141746 A1 (DELATTRE CECILE [FR] ET AL) 29 June 2006 (2006-06-29)<br>page 2, paragraph 32 – page 3, paragraph 39                                  | 8                     |

| A         | US 2005/266653 A1 (MORIWAKI RYUJI [JP]) 1 December 2005 (2005-12-01)<br>page 2, paragraph 36 – page 4, paragraph 54; figure 9A                           | 1, 4, 8, 9            |

| A         | EP 0 649 165 A (APPLIED MATERIALS INC [US]) 19 April 1995 (1995-04-19)<br>column 3, line 20 – line 23; figure 1                                          | 7                     |

|           |                                                                                                                                                          | -/-                   |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the international filing date or priority date and no. in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*&\* document member of the same patent family

|                                                           |                                                    |

|-----------------------------------------------------------|----------------------------------------------------|

| Date of the actual completion of the international search | Date of mailing of the international search report |

| 11 December 2008                                          | 19/01/2009                                         |

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL – 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Lyons, Christopher

## INTERNATIONAL SEARCH REPORT

International application No

PCT/EP2008/062018

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                      | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | EP 0 272 142 A (APPLIED MATERIALS INC [US]) 22 June 1988 (1988-06-22)<br>column 14, line 3 - line 10; figure 7<br>----- | 7                     |

| A         | US 2005/268850 A1 (MA BEOM-SUK [KR])<br>8 December 2005 (2005-12-08)<br>page 2, paragraph 33; figures 3,4,7<br>-----    | 7                     |

| A         | US 5 298 465 A (LEVY KARL B [US])<br>29 March 1994 (1994-03-29)<br>figure 2A<br>-----                                   | 7                     |

# INTERNATIONAL SEARCH REPORT

Information on patent family members

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/EP2008/062018 |

|---------------------------------------------------|

| Patent document cited in search report | Publication date | Patent family member(s)                                                                                                                           |  |  | Publication date                                                                                                           |

|----------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|----------------------------------------------------------------------------------------------------------------------------|

| WO 2007060145                          | A 31-05-2007     | NONE                                                                                                                                              |  |  |                                                                                                                            |

| US 2006141746                          | A1 29-06-2006    | EP 1829099 A1<br>WO 2006069945 A1<br>JP 2008526006 T<br>KR 20070088737 A                                                                          |  |  | 05-09-2007<br>06-07-2006<br>17-07-2008<br>29-08-2007                                                                       |

| US 2005266653                          | A1 01-12-2005    | JP 2005347302 A                                                                                                                                   |  |  | 15-12-2005                                                                                                                 |

| EP 0649165                             | A 19-04-1995     | JP 7153740 A<br>US 5423918 A                                                                                                                      |  |  | 16-06-1995<br>13-06-1995                                                                                                   |

| EP 0272142                             | A 22-06-1988     | AT 111261 T<br>AT 151199 T<br>DE 3750502 D1<br>DE 3750502 T2<br>DE 3752042 D1<br>DE 3752042 T2<br>ES 2058132 T3<br>JP 2624975 B2<br>JP 63283024 A |  |  | 15-09-1994<br>15-04-1997<br>13-10-1994<br>12-01-1995<br>07-05-1997<br>17-07-1997<br>01-11-1994<br>25-06-1997<br>18-11-1988 |

| US 2005268850                          | A1 08-12-2005    | KR 20050114920 A                                                                                                                                  |  |  | 07-12-2005                                                                                                                 |

| US 5298465                             | A 29-03-1994     | NONE                                                                                                                                              |  |  |                                                                                                                            |