(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7471812号**

**(P7471812)**

(45)発行日 令和6年4月22日(2024.4.22)

(24)登録日 令和6年4月12日(2024.4.12)

(51)国際特許分類

|                         |     |               |

|-------------------------|-----|---------------|

| H 04 N 25/79 (2023.01)  | F I | H 04 N 25/79  |

| H 04 N 25/70 (2023.01)  |     | H 04 N 25/70  |

| H 01 L 27/146 (2006.01) |     | H 01 L 27/146 |

D

請求項の数 30 (全25頁)

(21)出願番号 特願2019-229328(P2019-229328)

(22)出願日 令和1年12月19日(2019.12.19)

(65)公開番号 特開2020-141397(P2020-141397)

A)

(43)公開日 令和2年9月3日(2020.9.3)

審査請求日 令和4年12月19日(2022.12.19)

(31)優先権主張番号 特願2019-31801(P2019-31801)

(32)優先日 平成31年2月25日(2019.2.25)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100094112

弁理士 岡部 譲

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100106183

弁理士 吉澤 弘司

(74)代理人 100136799

弁理士 本田 亜希

(72)発明者 中村 恒一

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

(72)発明者 山崎 善一

最終頁に続く

(54)【発明の名称】 半導体装置および機器

**(57)【特許請求の範囲】****【請求項1】**

半導体装置であって、

第1の回路部が設けられ、第1の配線層領域を含む第1の半導体部品と、

第2の回路部が設けられ、第2の配線層領域および正面を有し、前記第1の配線層領域と前記第2の配線層領域とが対向するように前記第1の半導体部品に積層された第2の半導体部品と、

金属からなり、前記第1の配線層領域および前記第2の配線層領域に接続された接合コンタクト部と、

前記半導体装置の外部から電源電圧または接地電圧のいずれかが供給されるパッド電極と、

前記パッド電極に接続された容量部とを備え、

前記容量部の少なくとも一部と前記接合コンタクト部とは、前記正面の上方からの平面視において重なることを特徴とする半導体装置。

**【請求項2】**

半導体装置であって、

第1の回路部が設けられ、第1の配線層領域を含む第1の半導体部品と、

第2の回路部が設けられ、第2の配線層領域および正面を有し、前記第1の配線層領域と前記第2の配線層領域とが対向するように前記第1の半導体部品に積層された第2の半導体部品と、

金属からなり、前記第1の配線層領域および前記第2の配線層領域に接続された接合コンタクト部と、

前記半導体装置の外部から電源電圧または接地電圧のいずれかが供給されるパッド電極と、

前記パッド電極に接続された容量部と、

前記第2の半導体部品は、前記容量部と、前記第2の回路部および前記容量部の間に設けられたシールド部とをさらに含み、

前記シールド部の少なくとも一部と前記接合コンタクト部とは、前記正面の上方からの平面視において重ならないことを特徴とする半導体装置。

#### 【請求項3】

10

半導体装置であって、

第1の回路部が設けられ、第1の配線層領域を含む第1の半導体部品と、

第2の回路部を含み、第1の導電型の第1のウェルと、前記第1の導電型の第2のウェルと、前記第1のウェルおよび前記第2のウェルの間に配置された第2の導電型の第3のウェルとを含み、前記第1の半導体部品に積層され、第2の配線層領域および正面を含む第2の半導体部品と、

金属からなり、前記第1の配線層領域および前記第2の配線層領域に接続された接合コンタクト部と、

前記半導体装置の外部から電源電圧または接地電圧のいずれかが供給されるパッド電極と、

20

前記パッド電極に接続され、前記第3のウェルに配置された容量部とを備え、

前記第3のウェルの少なくとも一部と前記接合コンタクト部とは前記正面の上方からの平面視において重なることを特徴とする半導体装置。

#### 【請求項4】

前記第2の半導体部品は、前記第2の回路部および前記容量部の間に設けられたシールド部をさらに含むことを特徴とする請求項1または3に記載の半導体装置。

#### 【請求項5】

前記容量部は、前記第2の半導体部品の半導体基板における前記第2の回路部から分離されたウェルに形成されることを特徴とする請求項1または2に記載の半導体装置。

#### 【請求項6】

30

前記容量部はMOS構造であることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

#### 【請求項7】

前記容量部はさらにゲート電極、ソース領域、ドレイン領域、および基板バイアス部を備え、

前記容量部の第1のノードは前記ゲート電極に接続され、前記容量部の第2のノードは前記ソース領域、前記ドレイン領域、および前記基板バイアス部に接続されることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

#### 【請求項8】

前記容量部は、半導体領域と前記半導体領域の上に絶縁膜を介して形成されたポリシリコン電極とを備え

40

前記容量部の第1のノードは前記半導体領域に接続され、前記容量部の第2のノードは前記ポリシリコン電極に接続されることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

#### 【請求項9】

前記容量部は、前記第2の半導体部品の半導体基板の上の配線層領域に形成された第1の金属配線および第2の金属配線を備え、

前記容量部の第1のノードは前記第1の金属配線に接続され、前記容量部の第2のノードは前記第2の金属配線に接続されることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

50

**【請求項 10】**

前記第1の金属配線および前記第2の金属配線は異なる配線層に形成されていることを特徴とする請求項9に記載の半導体装置。

**【請求項 11】**

前記第1の金属配線および前記第2の金属配線は同じ配線層に形成されていることを特徴とする請求項9に記載の半導体装置。

**【請求項 12】**

平面視において、前記第1の金属配線および前記第2の金属配線のそれぞれは凹部または凸部を備え、前記第1の金属配線の前記凹部内には前記第2の金属配線の前記凸部が位置することを特徴とする請求項9に記載の半導体装置。 10

**【請求項 13】**

前記第1の半導体部品は、平面視において前記第2の回路部と少なくとも一部において重なる第3の回路部を備えることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

**【請求項 14】**

前記第2の回路部は光電変換部を含む画素部であり、

前記第3の回路部は、前記画素部から出力されたアナログ信号をデジタルデータに変換するアナログデジタル変換部と、前記デジタルデータを保持するメモリ部とのうちの少なくとも1つを備えることを特徴とする請求項1~3に記載の半導体装置。 20

**【請求項 15】**

前記容量部の第1のノードは、前記第1の回路部の電源線に接続され、前記容量部の第2のノードは、前記第1の回路部の接地線に接続されることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

**【請求項 16】**

前記第1の回路部は、基準電圧を生成する電圧生成回路を含み、

前記容量部の第1のノードは前記基準電圧の配線に接続され、前記容量部の第2のノードは接地線に接続されることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。 30

**【請求項 17】**

前記第1の半導体部品はトランジスタを含み、前記正面の上方からの平面視において、前記シールド部の少なくとも一部と前記トランジスタとは重なることを特徴とする請求項2に記載の半導体装置。

**【請求項 18】**

前記シールド部は、複数の配線層と、前記複数の配線層を接続する複数の接続部とを含むことを特徴とする請求項2に記載の半導体装置。

**【請求項 19】**

前記シールド部には固定電圧が印加されることを特徴とする請求項2に記載の半導体装置。 40

**【請求項 20】**

前記容量部は、前記第2の半導体部品の半導体基板における前記第2の回路部から分離されたウェルに形成されることを特徴とする請求項2に記載の半導体装置。

**【請求項 21】**

平面視において、前記容量部は前記パッド電極と前記第2の回路部との間に配されることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

**【請求項 22】**

複数の前記容量部を備え、複数の前記容量部は互いに並列に接続されていることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

**【請求項 23】**

平面視において、前記容量部と前記第1の回路部とは少なくとも一部において重なって配置されることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。 50

**【請求項 2 4】**

前記容量部は、平面視において、複数の前記第 2 の回路部の領域の外側に配置されることを特徴とする請求項1乃至3のいずれか 1 項に記載の半導体装置。

**【請求項 2 5】**

前記第 1 の回路部は、演算処理回路であることを特徴とする請求項1乃至3のいずれか 1 項に記載の半導体装置。

**【請求項 2 6】**

前記演算処理回路は、ノイズ低減処理を行うことを特徴とする請求項2 5に記載の半導体装置。

**【請求項 2 7】**

前記第 1 の回路部はアナログデジタル変換回路であることを特徴とする請求項1乃至3のいずれか 1 項に記載の半導体装置。

**【請求項 2 8】**

前記第 1 の回路部は、デジタルデータを処理するデジタル信号処理回路であることを特徴とする請求項1乃至3のいずれか 1 項に記載の半導体装置。

**【請求項 2 9】**

前記デジタル信号処理回路は前記半導体装置の外部に前記デジタルデータを出力することを特徴とする請求項2 8に記載の半導体装置。

**【請求項 3 0】**

請求項1乃至2 9のいずれか 1 項に記載の半導体装置と、

前記半導体装置に接続された装置と、

を有することを特徴とする機器。

10

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は半導体装置および機器に関する。

**【背景技術】****【0 0 0 2】**

近年、複数の半導体部品を積層した固体撮像装置が提案されている。特許文献 1 に記載の固体撮像装置は積層された複数の部品を備え、第 1 の部品には画素部が設けられ、第 2 の部品には画素部の信号を読み出す読み出し部が設けられている。第 1 の部品および第 2 の部品に加えてさらにバイパスコンデンサ専用の部品が積層されている。

30

**【先行技術文献】****【特許文献】****【0 0 0 3】**

【文献】国際公開第 2 0 1 7 / 1 8 7 7 3 8 号

**【発明の概要】****【発明が解決しようとする課題】****【0 0 0 4】**

しかしながら、特許文献 1 に記載の固体撮像装置は、バイパスコンデンサ専用の部品を積層しなければならず、製造コストが増加するという課題が生じていた。

40

**【0 0 0 5】**

本発明は上述の課題に鑑みてなされたものであって、製造コストの増加を抑制しながら容量部を効率的に配置することを目的とする。

**【課題を解決するための手段】****【0 0 0 6】**

本開示の一実施形態によれば、第 1 の回路部が設けられた第 1 の半導体部品と、第 2 の回路部が設けられるとともに、前記第 1 の半導体部品に積層された第 2 の半導体部品とを備え、前記第 2 の半導体部品は、前記第 1 の回路部に接続される第 1 のノードおよび第 2 のノードを有するデカップリング容量としての容量部を備え、前記第 1 の回路部は前記第

50

2の回路部から出力された信号を処理する信号処理回路であることを特徴とする半導体装置が提供される。

**【0007】**

本開示の他の実施形態によれば、第1の回路部が設けられた第1の半導体部品と、第2の回路部が設けられるとともに、前記第1の半導体部品に積層された第2の半導体部品とを備え、前記第2の半導体部品は、前記第1の回路部に接続される第1のノードおよび第2のノードを有する容量部を備え、前記第2の半導体部品は、前記第2の回路部と前記容量部との間に設けられたシールド部をさらに備えることを特徴とする半導体装置が提供される。

**【0008】**

本開示のさらに他の実施形態によれば、第1の回路部が設けられた第1の半導体部品と、第2の回路部が設けられるとともに、前記第1の半導体部品に積層された第2の半導体部品とを備え、前記第2の半導体部品は、前記第1の回路部に接続される第1のノードおよび第2のノードを有するデカップリング容量としての容量部を備え、前記容量部は、半導体領域と前記半導体領域の上に絶縁膜を介して形成されたポリシリコン電極とを備えて構成されることを特徴とする半導体装置が提供される。

**【0009】**

本開示のさらに他の実施形態によれば、第1の回路部が設けられた第1の半導体部品と、第2の回路部が設けられるとともに、前記第1の半導体部品に積層された第2の半導体部品とを備え、前記第2の半導体部品は、前記第1の回路部に接続される第1のノードおよび第2のノードを有する容量部を備え、前記第2の回路部は複数の画素を含む画素部であり、前記容量部は、平面視において前記画素部の外に配されていることを特徴とする半導体装置が提供される。

**【発明の効果】**

**【0010】**

本発明によれば、半導体装置において製造コストの増加を抑制しながら容量部を効率的に配置することができる。

**【図面の簡単な説明】**

**【0011】**

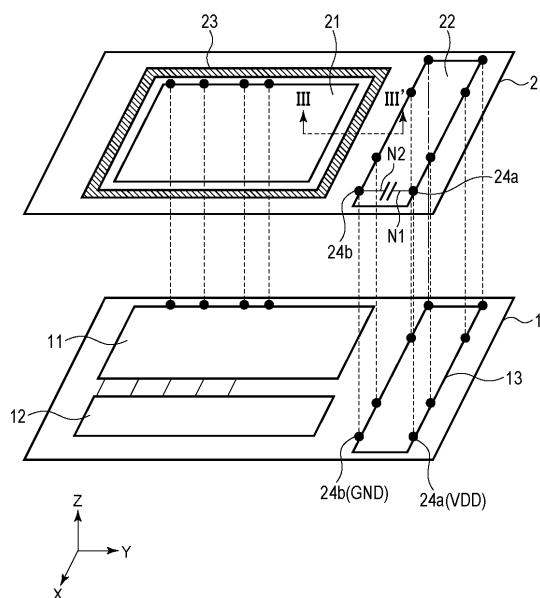

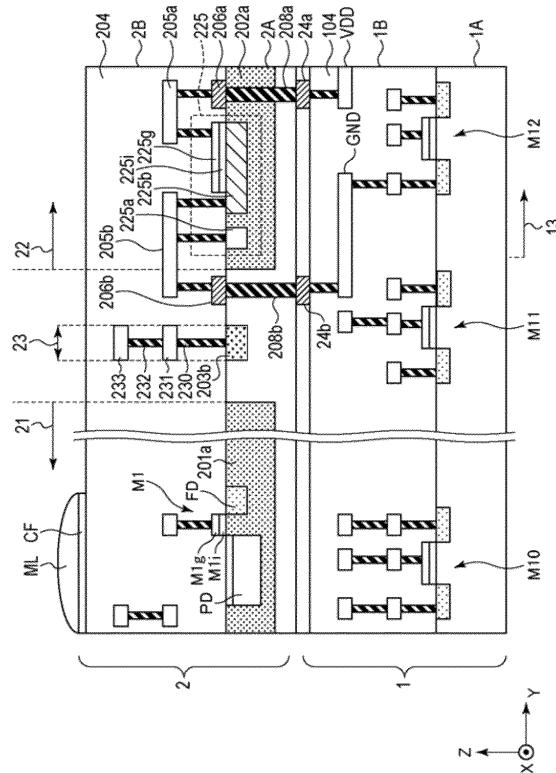

【図1】本発明の第1実施形態における撮像装置の模式図である。

30

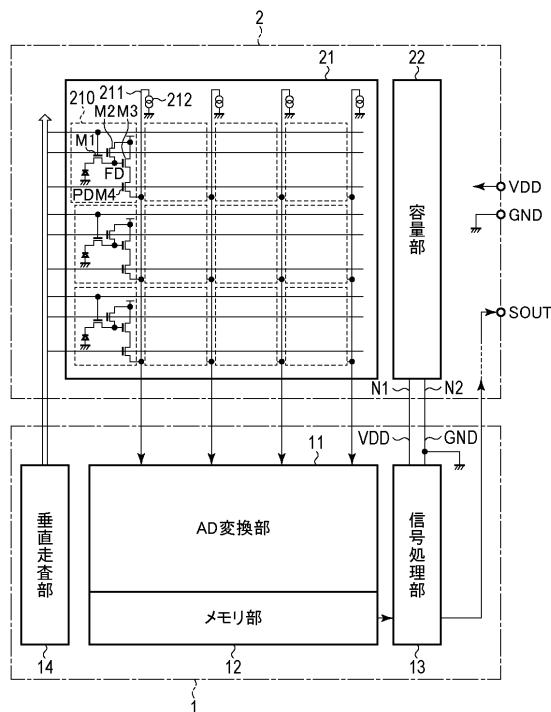

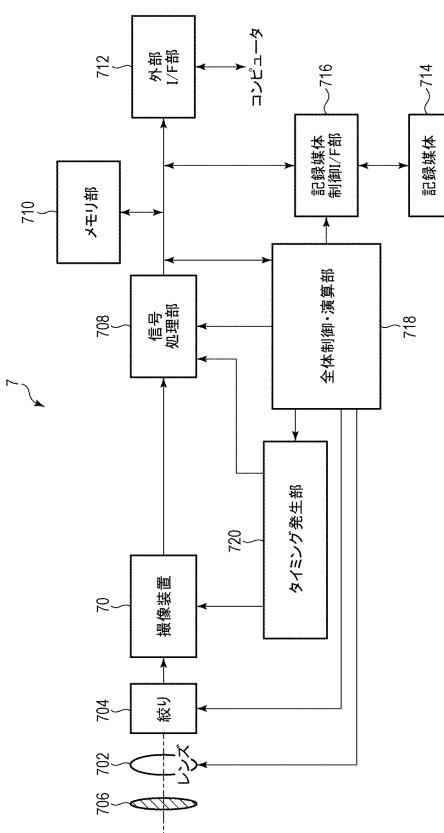

【図2】本発明の第1実施形態における撮像装置のブロック図である。

【図3】本発明の第1実施形態における撮像装置の断面図である。

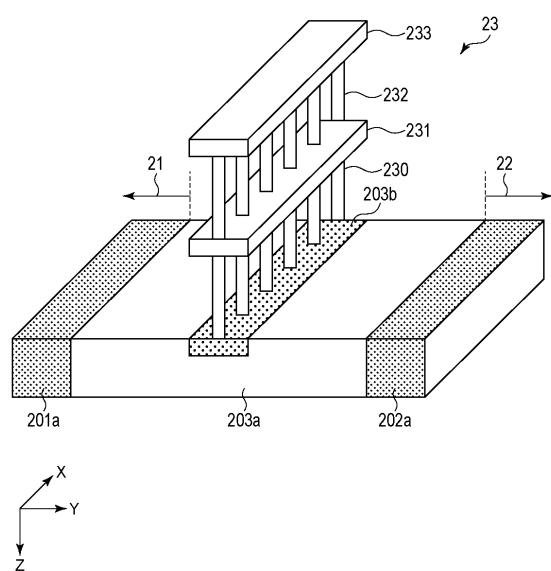

【図4】本発明の第1実施形態におけるシールド部の断面斜視図である。

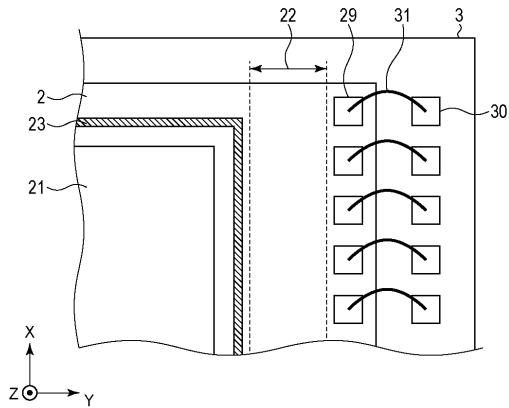

【図5】本発明の第1実施形態における撮像装置の一部の平面図である。

【図6】本発明の第2実施形態における撮像装置の模式図である。

【図7】本発明の第3実施形態における撮像装置の断面図である。

【図8】本発明の第4実施形態における撮像装置の断面図である。

【図9】本発明の第5実施形態における撮像装置を説明するための図である。

【図10】本発明の第6実施形態における撮像装置の断面図である。

【図11】本発明の第7実施形態による撮像システムの概略構成を示すブロック図である。

40

【図12】本発明の第8実施形態による撮像システムおよび移動体の構成例を示す図である。

【図13】本発明の第9実施形態における基準電圧回路の模式図である。

【図14】本発明の第9実施形態における反転增幅回路の模式図である。

【図15】本発明の第9実施形態における反転增幅回路の動作を表すタイミングチャートである。

【図16】本発明の第9実施形態における参照信号生成回路の模式図である。

【図17】本発明の第9実施形態における比較回路の図である。

【図18】本発明の第9実施形態における参照信号生成回路の動作を表すタイミングチャートである。

50

【図19】本発明の第9実施形態におけるアナログデジタル変換部の動作を表すタイミングチャートである。

【図20】本発明の第9実施形態におけるカレントミラー回路の模式図である。

【発明を実施するための形態】

【0012】

[第1実施形態]

本実施形態における半導体装置は例えば光電変換部を備えた撮像装置に適用可能である。以下、撮像装置を例として説明する。

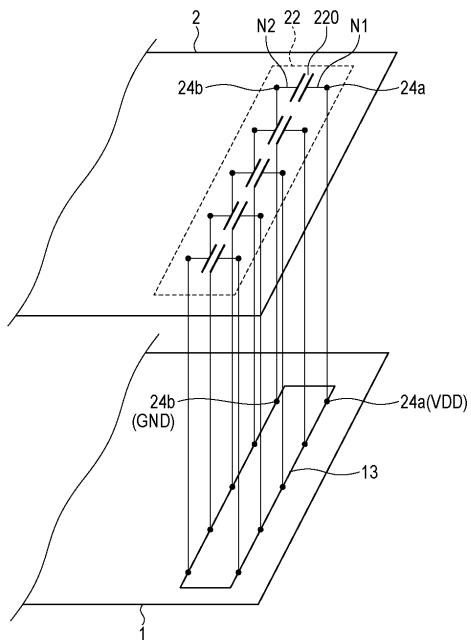

【0013】

図1は本実施形態における撮像装置の模式図である。撮像装置はいわゆる裏面照射型の固体撮像装置であって、第1の半導体部品1、第2の半導体部品2を備える。第1の半導体部品1の第1の主面( Z方向の上面)には第2の半導体部品2が積層される。このような半導体装置は、第1の半導体部品1を含むウエハと、第2の半導体部品2を含むウエハとをウエハレベルで貼り合わせ、貼り合わされたウエハをダイシングすることにより製造される。ダイシングによって得られることから、第1の半導体部品1、第2の半導体部品2をそれぞれ半導体チップと称することができる。ウエハレベルでの貼り合わせを伴わない製造方法として、第1の半導体部品1を含むウエハをダイシングして得られた半導体チップを、第2の半導体部品2を含むウエハをダイシングして得られた半導体チップに積層してもよい。第1の半導体部品1は第1の回路部として例えばアナログデジタル変換部11、メモリ部12、信号処理部13を備える。第2の半導体部品2は、第1の回路部と異なる第2の回路部として例えば画素部21を備える。画素部21は入射光に応じた信号を生成する複数の画素を備え、複数の画素はX方向およびY方向においてマトリクス状に配列されている。画素部21から出力された信号は第1の半導体部品1のアナログデジタル変換部11に出力される。アナログデジタル変換部11は画素部21からの信号をデジタル信号に変換し、メモリ部12はデジタル信号を保持する。信号処理部13はメモリ部12に保持されたデジタル信号を処理する。アナログデジタル変換部11、メモリ部12は第3の回路部を構成し、アナログデジタル変換部11、メモリ部12の少なくとも一部はZ方向の平面視において第2の回路部に重なって配置され得る。

10

20

【0014】

第2の半導体部品2はさらに容量部22を備えている。容量部22は第1の半導体部品1において例えば信号処理部13に接続されている。容量部22と信号処理部13とは、A1、C1、Wなどの金属からなる接合コンタクト24a、24bを介して電気的に接続される。容量部22は第1の入力ノードN1および第2の入力ノードN2を備え、信号処理部13に接続される。容量部22がバイパスコンデンサ(デカップリング容量)として用いられる場合、第1の入力ノードN1は信号処理部13における電源線VDDに接続され、第2の入力ノードは信号処理部13における接地線GNDに接続される。また、容量部22がカップリング容量として用いられる場合、容量部22は信号処理部13の所望の信号線に直列に接続され得る。以下、容量部22がバイパスコンデンサを備える構成を中心について説明する。

30

【0015】

容量部22は、平面視において第2の半導体部品2において信号処理部13に対向する位置に形成され得る。すなわち、撮像装置の平面視において、容量部22と信号処理部13とは少なくとも一部において重なって配置され得る。これにより、容量部22と信号処理部13との間の配線が短くなり、電源線および接地線のインピーダンスを低減することが可能となる。なお、平面視において、容量部22と信号処理部13とが重なって配置されない場合であっても、容量部22と信号処理部13との間の電源線および接地線の長さをできるだけ短くすることが好ましい。

40

【0016】

第2の半導体部品2において、画素部21と容量部22との間にはシールド部23が形成されている。シールド部23は、平面視において画素部21を囲む矩形の環状をなして

50

もよい。シールド部 23 は、後述するように複数の配線を備え、容量部 22 において生じるノイズが画素部 21 に混入するのを防ぐことが可能である。

#### 【 0 0 1 7 】

図 2 は本実施形態における撮像装置のブロック図である。撮像装置は画素部 21、アナログデジタル変換部（A/D 変換部）11、メモリ部 12、信号処理部 13、垂直走査部 14、容量部 22 を備える。

#### 【 0 0 1 8 】

画素部 21 は第 2 の半導体部品 2 に設けられ、マトリクス状に配置された複数の画素 210 を備える。図 2 には画面の簡略化のために 3 行 4 列の画素 210 が示されているが、行方向および列方向に配置される画素 210 の数は特に限定されるものではない。なお、本明細書において、行方向とは画面における水平方向を示し、列方向とは画面において垂直方向を示すものとする。画素 210 上にはマイクロレンズ、カラーフィルタが配置され得る。カラーフィルタは例えば赤、青、緑の原色フィルタであって、ベイヤー配列に従つて各画素 210 に設けられている。一部の画素 210 は O/B 画素（オプティカル・ブラック画素）として遮光されている。複数の画素 210 には、焦点検出用の画素信号を出力する焦点検出画素が配された測距行と、画像を生成するための画素信号を出力する撮像画素が配された複数の撮像行とが設けられ得る。信号線 211 は画素 210 の列毎に設けられ、信号線 211 には定電流源 212 が電気的に接続される。

10

#### 【 0 0 1 9 】

画素 210 は、光電変換部 PD、浮遊拡散領域 FD (Floating Diffusion) 、転送トランジスタ M1、リセットトランジスタ M2、増幅トランジスタ M3、選択トランジスタ M4 を含む。以下の説明は、画素 210 を構成するトランジスタが N 型 MOS トランジスタである例を示している。光電変換部 PD は例えばフォトダイオードから構成されており、入射光による光電変換および電荷の生成および蓄積を行なう。転送トランジスタ M1 はオンになることにより、光電変換部 PD の電荷を浮遊拡散領域 FD に転送する。リセットトランジスタ M2 はオンになることにより、浮遊拡散領域 FD の電位を電源電圧にリセットする。浮遊拡散領域 FD は所定の容量を有し、電荷に応じた電圧を発生させる。増幅トランジスタ M3 は、浮遊拡散領域 FD の電位に応じてソースの電位が変わるソースフォロアとして動作する。選択トランジスタ M4 は増幅トランジスタ M3 のソースを信号線 211 に電気的に接続する。信号線 211 には増幅トランジスタ M3 の負荷として機能する定電流源 212 が接続されている。読み出すべき行の選択トランジスタ M4 がオンとなることで、当該行の光電変換部 PD の電荷に応じた電圧（アナログ信号）が信号線 211 に出力される。

20

#### 【 0 0 2 0 】

トランジスタ M1 ~ M4 は N 型 MOS トランジスタに限定されることなく、P 型 MOS トランジスタであっても良い。画素 210 の構成も図 2 に示された例に限定されることなく様々な画素を用いることができる。例えば、複数の光電変換部 PD が 1 つの増幅トランジスタ M3 を共有しても良く、また、画素 210 は光電変換部 PD から溢れた電荷を排出するオーバーフロードレインを備えても良い。

30

#### 【 0 0 2 1 】

アナログデジタル変換部 11 は、増幅回路、コンパレータ、ランプ信号発生回路、カウント回路などを備える。増幅回路は画素 210 から信号線 211 に出力されたアナログ信号を増幅し、コンパレータの一方の入力端子に入力する。ランプ信号発生回路は時間とともに変化するランプ信号を生成し、コンパレータの他方の入力端子に入力する。コンパレータはアナログ信号とランプ信号とを比較し、比較信号を出力する。カウント回路は、ランプ信号が変化し始めてから比較信号が反転するまでの時間をカウントし、カウント値をデジタルデータとして出力する。

40

#### 【 0 0 2 2 】

メモリ部 12 はアナログデジタル変換部 11 から出力されたデジタルデータを保持する。メモリ部 12 はデジタルデータを行単位またはフレーム単位で保持し得る。さらに、メ

50

モリ部 12 は、保持されたデジタルデータをシリアルデータまたはパラレルデータとして出力する走査回路を備え得る。

#### 【 0 0 2 3 】

信号処理部 13 はデジタル信号処理回路、演算処理回路などを備え、メモリ部 12 から出力されたデジタルデータの信号処理を実行する。信号処理は例えばノイズリダクション処理、ダイナミックレンジ拡張処理、ホワイトバランス処理、シャッタ読み出し処理、デモザイク処理のいずれか若しくは複数であり得る。信号処理部 13 から出力されたデジタルデータは第 2 の半導体部品 2 のパッド電極 S O U T から撮像装置の外部へ出力される。

#### 【 0 0 2 4 】

垂直走査部 14 はシフトレジスタ、ゲート回路などを含み、複数の制御信号を画素 210 に供給する。すなわち、垂直走査部 14 は画素 210 のトランジスタ M1、M2、M4 のゲートに印加される制御信号を駆動し、画素 210 を行単位で読み出す。

#### 【 0 0 2 5 】

容量部 22 は第 2 の半導体部品 2 に設けられ、容量部 22 の第 1 の入力ノード N1 は信号処理部 13 の電源配線 VDD に接続され、容量部 22 の第 2 の入力ノード N2 は信号処理部 13 の接地配線 GND に接続されている。電源配線 VDD、接地配線 GND は第 2 の半導体部品 2 の外部パッド電極 VDD、GND に電気的に接続され、外部パッド電極 VDD、GND を介して半導体装置の外部から電源電圧が供給される。なお、外部パッド電極 VDD、GND と半導体装置内部の各回路部との間に電源制御回路が設けられてもよい。電源制御回路は半導体装置の各部へ供給される電源電圧を制御してもよい。

#### 【 0 0 2 6 】

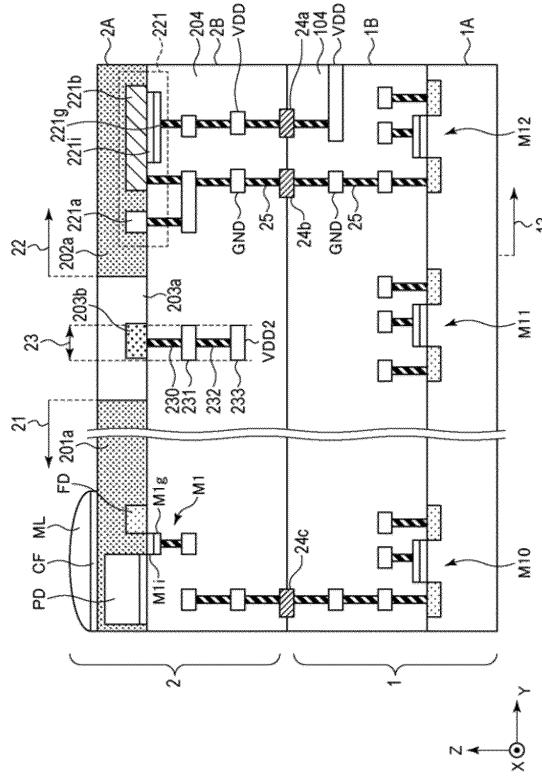

図 3 は本実施形態における撮像装置の詳細を説明するための図であって、図 1 の撮像装置の III - III' に沿った断面図である。第 1 の半導体部品 1 は第 1 の半導体基板 1A、第 1 の配線層領域 1B を含み、第 2 の半導体部品 2 は第 2 の半導体基板 2A、第 2 の配線層領域 2B を含む。第 1 の半導体部品 1 および第 2 の半導体部品 2 のそれぞれの第 1 の主面、すなわち第 1 の配線層領域 1B の表面と第 2 の配線層領域 2B の表面とは対向するよう、第 1 の半導体部品 1 および第 2 の半導体部品 2 が積層されている。第 2 の半導体基板 2A の第 2 の主面（裏面）には入射光が照射される。

#### 【 0 0 2 7 】

第 1 の半導体基板 1A にはトランジスタ M10、M11、M12 が形成される。例えば、トランジスタ M12 は信号処理部 13 に含まれる。第 1 の半導体基板 1A には P 型ウェルが形成され、P 型ウェルにはトランジスタ M10、M11、M12 のそれぞれのソース、ドレインが N 型半導体領域として形成される。ソース、ドレインの間の P 型ウェル上にはゲート絶縁膜を挟んでゲート電極が形成される。

#### 【 0 0 2 8 】

第 1 の配線層領域 1B は第 1 の半導体基板 1A 上に設けられ、有機材料などの層間絶縁膜 104 を介して複数の配線層が形成される。異なる配線層同士は Z 方向に延在する接続部 25 によって接続され、接続部 25 はさらに第 1 の配線層領域 1B の上部の接合コンタクト 24a、24b、24c に接続される。信号処理部 13 において、電源配線 VDD は接合コンタクト 24a に接続され、接地配線 GND は接合コンタクト 24b に接続される。

#### 【 0 0 2 9 】

第 2 の半導体基板 2A は、P 型不純物が注入された P 型ウェル 201a、202a、N 型不純物が注入された N 型ウェル 203a を含む。N 型ウェル 203a は、P 型ウェル 201a、202a の間に形成されている。

#### 【 0 0 3 0 】

画素部 21 は P 型ウェル 201a に形成される。図 3 には、画素部 21 のうち、光電変換部 PD、浮遊拡散領域 FD、転送トランジスタ M1、カラーフィルタ CF、マイクロレンズ ML が示されている。光電変換部 PD は、P 型ウェル 201a に囲まれた N 型領域を含み、N 型領域の上部 (-Z 方向) には P 型領域が設けられる。このような構成により、界面で発生する電荷によるノイズを低減できる。第 2 の半導体基板 2A の第 2 の主面（裏

10

20

30

40

50

面)にはカラーフィルタCF、マイクロレンズMLが設けられている。第2の半導体基板2Aの裏面に入射した光はマイクロレンズML、カラーフィルタCFを介して光電変換部PDに入射する。このように、第2の半導体基板2Aの裏面から受光することで、受光面積を増加し、高感度の撮像装置を実現することができる。

#### 【0031】

浮遊拡散領域FDはN型領域を含み、所定の容量を形成している。転送トランジスタM1のゲート電極M1gは光電変換部PDと浮遊拡散領域FDの間に配され、ゲート絶縁膜M1iを挟んで第2の半導体基板2A上に形成されている。ゲート電極M1gは例えばポリシリコン電極、またはAl、Cuなどのメタル電極から構成され、ゲート絶縁膜M1iは例えばSiO<sub>2</sub>などから構成される。転送トランジスタM1のソース/ドレイン領域は光電変換部PD、浮遊拡散領域FDを共有している。ゲート電極M1gに電圧が印加されることにより、光電変換部PDに蓄積された電荷が浮遊拡散領域FDに転送される。浮遊拡散領域FDの電位は電荷に応じて変化し、增幅トランジスタM3、選択トランジスタM4を介して出力される(図2参照)。画素部21から出力された信号は例えば接合コンタクト24cを介して第1の半導体部品1に出力され得る。

#### 【0032】

容量部22は、画素部21から分離されたP型ウェル202aに形成される。容量部22は単一または複数のバイパスコンデンサ220を備える。本実施形態におけるバイパスコンデンサ220はMOS構造(Metal-Oxide-Semiconductor)を有し、例えばN型のMOSトランジスタによって構成され得る。バイパスコンデンサ220はゲート電極220g、ソース領域220s、ドレイン領域220d、基板バイアス部220a、ゲート絶縁膜220iを含む。ソース領域220s、ドレイン領域220dにはN型不純物が注入される。ゲート電極220gはポリシリコン電極、またはAl、Cuなどのメタル電極から構成され、ソース領域220s、ドレイン領域220dの間に配される。ゲート電極220gはゲート絶縁膜220iを挟んで第2の半導体基板2A上に形成される。ゲート絶縁膜220iはSiO<sub>2</sub>、SiON、SiNなどから構成される。SiON、SiNをゲート絶縁膜220iに用いた場合、高誘電率のバイパスコンデンサ220を実現し得る。

#### 【0033】

また、P型ウェル202aにはN型領域の基板バイアス部220aが形成されている。バイパスコンデンサ220において、ゲート電極220gに電源電圧VDDが印加され、基板バイアス部220a、ソース領域220s、ドレイン領域220dに接地電圧GNDが印加されると、ソース領域220sおよびドレイン領域220dの間にチャネル領域が形成される。ゲート電極220gはバイパスコンデンサ220の一方の電極(第1の入力ノード)を構成し、ソース領域220sおよびドレイン領域220dはバイパスコンデンサ220の他方の電極(第2の入力ノード)を構成している。

#### 【0034】

基板バイアス部220a、ソース領域220s、ドレイン領域220dは第2の配線層領域2Bにおいて接地配線GNDに接続され、接地配線GNDは接続部25を介して接合コンタクト24bに接続される。接合コンタクト24bは第1の配線層領域1Bにおいて信号処理部13の接地配線GNDに接続される。同様に、ゲート電極220gは第2の配線層領域2Bにおいて電源配線VDDに接続され、電源配線VDDは接続部25を介して接合コンタクト24aに接続される。接合コンタクト24aは第1の配線層領域1Bにおいて信号処理部13の電源配線VDDに接続される。すなわち、第2の半導体部品2におけるバイパスコンデンサ220が第1の半導体部品1の信号処理部13に接続される。

#### 【0035】

なお、図3において、接合コンタクト24a、24bの個数はそれぞれ1つのみであるが、接合コンタクト24a、24bの個数は複数であってもよい。これにより、接合コンタクト24a、24b、電源配線VDD、接地配線GNDのインピーダンスが低減され、電源配線VDDの変動を効果的に抑制することができる。

10

20

30

40

50

**【 0 0 3 6 】**

また、図3のバイパスコンデンサ220はN M O Sによって構成されているが、P M O Sによって構成されてもよい。すなわち、容量部22のP型ウェル202aに代えてN型ウェルを用いることで、P M O Sのバイパスコンデンサ220を形成することができる。また、P型ウェル202a内にN型ウェルを形成し、さらにN型ウェル内にP M O Sを形成してもよい。

**【 0 0 3 7 】**

シールド部23は、画素部21と容量部22との間のN型ウェル203aに形成されている。ここで、図3に加えて、図4を参照しながら、シールド部23の詳細な構成を説明する。図4はシールド部の断面斜視図である。シールド部23は基板バイアス部203b、配線層231、233、接続部230、232を備える。基板バイアス部203bは、N型ウェル203a表面に高濃度のN型不純物を注入することによって形成される。基板バイアス部203bはX Yの平面視において画素部21と容量部22との間に配され、所定の幅(Y方向)を有している。基板バイアス部203bに対して鉛直方向(-Z方向)に複数の配線層231、233が形成されている。配線層231、233は基板バイアス部203bと同様に所定の配線幅(Y方向)を有している。なお、配線層231、233のY方向の幅は基板バイアス部203bの幅と同じであってもよい。基板バイアス部203bと配線層231とはZ方向に延在する複数の接続部230によって接続される。複数の接続部230はX方向において一定の間隔で配されている。同様に、配線層231と配線層233とはZ方向に延在する複数の接続部232によって接続される。複数の接続部232は配線層231、233に沿ってX方向に一定の間隔で配されている。なお、接続部232の間隔は接続部230の間隔と同じであってもよい。配線層231、233は固定電圧V D D 2が印加され、シールド部23は低インピーダンスとなっている。固定電圧V D D 2は電源電圧V D Dであってもよく、シールド部23に専用の電源電圧、または接地電圧G N Dであってもよい。

10

20

30

40

**【 0 0 3 8 】**

シールド部23は画素部21と容量部22との間に設けられているため、容量部22において生じ得るノイズが画素部21に混入するのを回避することができる。また、シールド部23は格子状をなし、第2の配線層領域2Bの鉛直方向(-Z方向)に延在している。このため、第2の半導体基板2Aだけでなく第2の配線層領域2Bにおいても十分なシールド効果が得られる。なお、シールド効果をさらに高めるため、シールド部23を構成する配線層、接続部の数を増やしてもよい。さらに、シールド部23を複数の列に配置してもよい。

**【 0 0 3 9 】**

図5は本実施形態における撮像装置の一部の平面図である。第1の半導体部品1および第2の半導体部品2は積層され、パッケージ3上に載置される。第1の半導体部品1および第2の半導体部品2の辺(縁部)に沿って複数のパッド電極29が並んで配され、パッド電極29は第2の半導体部品2の入出力回路、電源線、接地線などに接続されている。パッケージ3には複数の外部パッド電極30が並んで配されている。パッド電極29と外部パッド電極30とはボンディングワイヤ31によって接続され、外部パッド電極30は撮像装置の外部の回路に接続され得る。本例では、パッド電極29が第2の半導体部品2の第2の配線層領域2Bに配置されている。そして、パッド電極29が接合コンタクトを介して第1の半導体部品1に接続されている。しかし、パッド電極29が第1の半導体部品1の第1の配線層領域1Bに配置されてもよい。また、パッド電極29が第2の配線層領域2Bに対して第1の半導体部品1とは反対側に配置されてもよく、パッド電極29が第2の半導体基板2Aを貫通する貫通電極を介して第2の半導体部品2に接続されてもよい。また、パッド電極29が第1の配線層領域1Bに対して第2の半導体部品2とは反対側に配置されてもよく、パッド電極29が第1の半導体基板1Aを貫通する貫通電極を介して第1の半導体部品1に接続されてもよい。

**【 0 0 4 0 】**

50

ポンディングワイヤ31は金、アルミ、銅、パラジウムなど光沢のある素材から構成され、入射光を反射し易い。ポンディングワイヤ31における反射光が画素部21に入り込むと、ゴースト等の画質劣化が生じ得る。ポンディングワイヤ31からの反射光が画素部21に入り込むのを避けるため、画素部21はパッド電極29から離れて配置され、画素部21とパッド電極29との間に余剩スペースが設けられることが多い。本実施形態においては、容量部22を第2の半導体部品2に生じた余剩スペースに設けることにより、バイパスコンデンサ220のための専用の半導体部品等を設ける必要がなくなり、製造コストの増加を抑制することが可能となる。特に、パッド電極29が第2の半導体部品2の4辺に配される場合、余剩スペースは4辺に生じ得る。容量部22を4辺に設けることで、さらにバイパスコンデンサ220の容量を増加し、電源電圧VDDの変動を効果的に抑制することが可能となる。このように、第2の半導体部品2の余剩スペースに応じて、容量部22の大きさ、個数、形状を定め得る。例えば、余剩スペースが小さい箇所には小さな容量部22を配置し、余剩スペースが大きい箇所には大きな容量部22を配置し得る。

#### 【0041】

上述のように構成された撮像装置において、容量部をバイパスコンデンサとして用いることにより、信号処理部に瞬間に大きな電流が流れる場合、電源電圧の変動を効果的に抑制することができる。信号処理部がデジタル回路により構成される場合、スイッチング電流のように瞬間に大きな電流が流れ、電源電圧が低下し得る。電源電圧の変動はノイズとして他の回路に悪影響を及ぼし得る。バイパスコンデンサを電源線と接地線との間に設けることにより、バイパスコンデンサから電流を電源線に供給することができるため、電源電圧の変動を抑制することが可能となる。

#### 【0042】

以上述べたように、本実施形態においては、第1の半導体部品のための容量部は第2の半導体部品に設けられている。このため、容量部の専用の半導体部品を設ける必要がなくなり、製造コストを低減することが可能となる。特に、半導体装置が撮像装置である場合、画素部の周囲または周辺に生じた余剩スペースを利用し、画素部以外の領域に容量部を効率よく配置することができる。

#### 【0043】

なお、本実施形態における容量部はバイパスコンデンサのみならず、カップリング容量など、様々な用途に用いられ得るが、本実施形態は特にバイパスコンデンサに好適である。バイパスコンデンサはできるだけ大きな容量を有することが望ましく、従来はバイパスコンデンサのための専用の半導体部品を設ける必要があった。本実施形態によれば、第2の半導体部品の余剩スペースを利用して、第1の半導体部品の回路のためのバイパスコンデンサを設けることで、バイパスコンデンサの専用の半導体部品を設ける必要がなくなる。

#### 【0044】

また、本実施形態においては、半導体部品の内部にバイパスコンデンサが設けられているため、半導体部品の外部にバイパスコンデンサが設けられている場合と比較して、バイパスコンデンサと信号処理部との配線長を短くすることができる。このため、配線のインピーダンスも低くなり、電源電圧の変動をさらに効果的に抑制することができる。仮に、半導体部品の外部にバイパスコンデンサが設けられた場合、ポンディングワイヤ、外部配線のインダクタンスによって高周波におけるインピーダンスが大きくなり、バイパスコンデンサの効果は減殺されてしまう。バイパスコンデンサを半導体部品の内部に設ける構成は、特に電源電圧の高周波ノイズの抑制に効果的である。

#### 【0045】

さらに、本実施形態において、バイパスコンデンサは接合コンタクトを介して信号処理部に接続されている。接合コンタクトの面積はポンディングパッドの面積よりも小さいため、半導体部品の内部に複数の接合コンタクトを設けることができる。接合コンタクトの数が増えるに従い、バイパスコンデンサと信号処理部との間の電源配線のインピーダンスは低くなる。このため、バイパスコンデンサが半導体部品の外部に設けられている場合に比べて、バイパスコンデンサの配線数および接合コンタクトの数を増やすことができ、よ

り効果的に電源電圧の変動を抑制することができる。

#### 【0046】

なお、上述の実施形態においては、バイパスコンデンサが信号処理部に接続されている例を説明したが、バイパスコンデンサが接続される回路部は信号処理部に限定されない。高周波帯域の電源電圧の変動が生じ得る回路、例えば、アナログデジタル変換回路、高速シリアルデータ伝送のためのパラレルシリアル変換回路、トランスマッタ回路、メモリ回路などにおいてもバイパスコンデンサを接続可能である。また、デジタル回路に限定されず、瞬間的に大きな電流が流れ得るアナログ回路において本実施形態を適用してもよい。

#### 【0047】

##### [第2実施形態]

図6は本実施形態における撮像装置の模式図である。容量部22に含まれるバイパスコンデンサ220は1個に限定されず複数個であってもよい。以下、第1実施形態と異なる構成を中心に本実施形態の撮像装置を説明する。

#### 【0048】

図6において、容量部22は複数のバイパスコンデンサ220を備え、それぞれのバイパスコンデンサ220は接合コンタクト24a、24bを介して第1の半導体部品1の信号処理部13に接続されている。すなわち、バイパスコンデンサ220の第1の入力ノードN1は接合コンタクト24aを介して信号処理部13の電源配線VDDに接続され、バイパスコンデンサ220の第2の入力ノードN2は接合コンタクト24bを介して信号処理部13の接地配線GNDに接続されている。

#### 【0049】

本実施形態においては、並列に接続された複数のバイパスコンデンサを用いることで、容量を大きくすることができます。例えば、単一のバイパスコンデンサの容量を大きくすることが困難な場合等において、複数のバイパスコンデンサを並列に接続することによって、容量の大きなバイパスコンデンサを実現することができる。すなわち、複数のバイパスコンデンサにおいて、複数の第1の入力ノードN1が互いに接続され、複数の第2の入力ノードN2が互いに接続されてもよい。

#### 【0050】

##### [第3実施形態]

図7は本実施形態における撮像装置の断面図であって、図1の撮像装置のIII-III'に沿った断面図である。本実施形態における撮像装置は容量部の構造において第1実施形態と異なっている。以下、第1実施形態と異なる構成を中心に説明する。

#### 【0051】

図7において、バイパスコンデンサ221は第2の半導体基板2AのP型ウェル202aに形成され、基板バイアス部221a、半導体領域221b、ゲート電極221g、ゲート絶縁膜221iを含む。半導体領域221bは、P型ウェル202a内に高濃度のN型不純物が注入されることによって形成される。半導体領域221b上にはゲート絶縁膜221iを介してゲート電極221gが形成される。ゲート電極221gは例えばポリシリコン電極、またはAl、Cuなどのメタル電極から構成され、ゲート絶縁膜221iは例えばSiO<sub>2</sub>、SiON、SiNなどから構成される。P型ウェル202aにはN型領域の基板バイアス部221aが形成されている。

#### 【0052】

基板バイアス部221a、半導体領域221bは第2の配線層領域2Bにおいて接地配線GNDに接続され、接地配線GNDは接続部25を介して接合コンタクト24bに接続される。接合コンタクト24bは第1の配線層領域1Bにおいて信号処理部13の接地配線GNDに接続される。同様に、ゲート電極221gは第2の配線層領域2Bにおいて電源配線VDDに接続され、電源配線VDDは接続部25を介して接合コンタクト24aに接続される。接合コンタクト24aは第1の配線層領域1Bにおいて信号処理部13の電源配線VDDに接続される。すなわち、第2の半導体部品2におけるバイパスコンデンサ221が第1の半導体部品1の信号処理部13に接続される。

10

20

30

40

50

**【0053】**

本実施形態においても、第1の半導体部品のための容量部を第2の半導体部品に設けることにより、容量部の専用の半導体部品を設ける必要がなくなり、製造コストを低減することが可能となる。

**【0054】****[第4実施形態]**

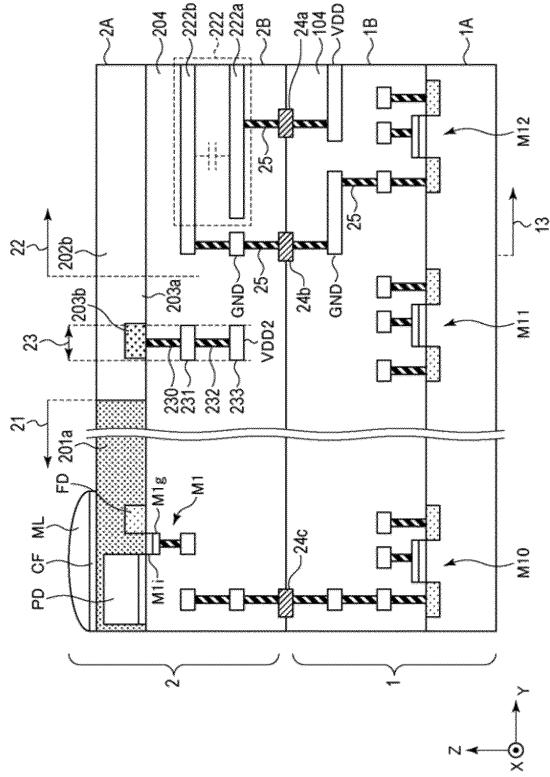

図8は本実施形態における撮像装置の断面図であって、図1の撮像装置のIII-III'に沿った断面図である。本実施形態における撮像装置はMIM(Metal-Insulator-Metal)構造の容量部を備える。以下、第1実施形態と異なる構成を中心に説明する。

10

**【0055】**

図8において、容量部22は単一または複数のバイパスコンデンサ222を含み、それぞれのバイパスコンデンサ222は2層の金属配線222a、222bによって構成されている。金属配線222a、222bはZ方向において互いに対向し、所定の間隔で配されている。金属配線222a、222bの間には層間絶縁膜204が介在し、層間絶縁膜204は誘電体として機能する。金属配線222aは第2の配線層領域2Bにおいて接続部25を介して接合コントクト24aに接続される。接合コントクト24aは第1の配線層領域1Bにおいて信号処理部13の電源配線VDDに接続される。同様に、金属配線222bは第2の配線層領域2Bにおいて接地配線GNDに接続され、接地配線GNDは接続部25を介して接合コントクト24bに接続される。接合コントクト24bは第1の配線層領域1Bにおいて信号処理部13の接地配線GNDに接続される。すなわち、第2の半導体部品2におけるバイパスコンデンサ222が第1の半導体部品1の信号処理部13に接続される。

20

**【0056】**

本実施形態によれば、第2の半導体部品における金属配線を用いてバイパスコンデンサ222を構成することができる。なお、バイパスコンデンサ222を構成する金属配線は2層に限定されず、3層以上であってもよい。金属配線の層数を増やすことにより、大容量のバイパスコンデンサ222を構成することが可能となる。

**【0057】**

なお、本実施形態における容量部22は第2の半導体基板2A上ではなく、第2の配線層領域2Bに配されている。このため、第2の半導体基板2Aにおいて容量部22に対応する領域202bは必ずしもP型ウェルであることを要せず、N型ウェルであってもよい。また、領域202bにP型ウェルを形成し、本実施形態における容量部22に加えて第1～第3実施形態における容量部22をさらに設けてもよい。すなわち、第2の半導体基板2A、第2の配線層領域2Bのそれぞれに容量部22を形成し、バイパスコンデンサの容量を大きくすることも可能である。

30

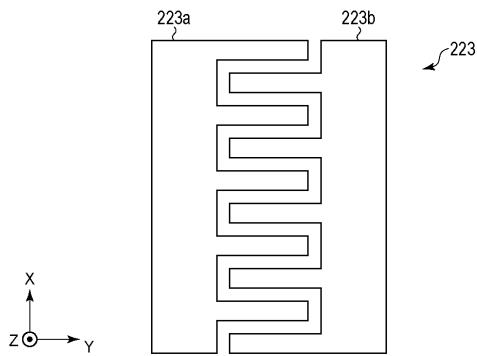

**【0058】****[第5実施形態]**

図9は本実施形態における撮像装置を説明するための図であって、第4実施形態における容量部の変形例を表している。第4実施形態における容量部は異なる2層の金属配線によって構成されていたが、本実施形態における容量部は同一の層の金属配線によって構成されている。以下、第4実施形態と異なる構成を中心に説明する。

40

**【0059】**

図9において、バイパスコンデンサ223は同一の層に形成された金属配線223a、223bを備え、平面視において金属配線223a、223bは所定の間隔で隣接して配されている。金属配線223a、223bにおいて対向するそれぞれの辺には凹部および凸部が形成されている。金属配線223aの凸部は金属配線223bの凹部内に位置し、金属配線223bの凸部は金属配線223aの凹部内に位置している。このような構成により、金属配線223a、223bが対向する辺の全長は長くなり、金属配線223a、223bにおける容量が増加する。金属配線223a、223bは図示されていない接合

50

コンタクト 24a、24b を介して第 1 の半導体部品 1 の信号処理部 13 に接続される。

#### 【0060】

上述したように、第 2 の半導体部品において同一層の金属配線を用いて容量部を構成することができる。本実施形態においても、容量部専用の半導体部品を設ける必要がないため、製造コストを低減することが可能となる。

#### 【0061】

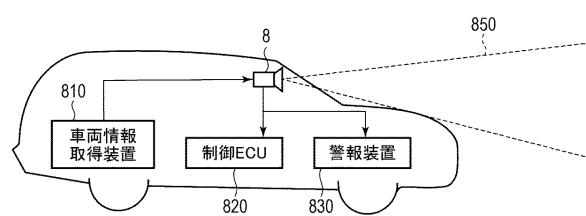

##### [第 6 実施形態]

図 10 は本実施形態における撮像装置の断面図であって、図 1 の撮像装置の III - III' に沿った断面図である。本実施形態においては、第 2 の半導体部品 2 の表裏が第 1 ~ 第 5 実施形態とは逆に配され、表面照射型の撮像装置が構成されている。以下、第 1 ~ 第 5 実施形態と異なる構成を中心に説明する。

10

#### 【0062】

図 10において、第 2 の半導体基板 2A の第 2 の主面(裏面)は第 1 の配線層領域 1B に貼り合わされ、第 2 の配線層領域 2B の第 1 の主面(表面)に入射光が照射される。第 1 の半導体部品 1 には、第 1 ~ 第 5 実施形態と略同様に、アナログデジタル変換部 11、メモリ部 12、信号処理部 13、垂直走査部 14 が設けられる。

#### 【0063】

第 2 の半導体基板 2A は、P 型不純物が注入された P 型ウェル 201a、202a を含む。画素部 21 は P 型ウェル 201a に形成され、図 10 には光電変換部 PD、浮遊拡散領域 FD、転送トランジスタ M1、カラーフィルタ CF、マイクロレンズ ML が示されている。光電変換部 PD の上方の第 2 の配線層領域 2B の表面にはカラーフィルタ CF、マイクロレンズ ML が配されている。

20

#### 【0064】

容量部 22 は P 型ウェル 202a に形成され、バイパスコンデンサ 225 を備える。バイパスコンデンサ 225 は第 3 実施形態におけるバイパスコンデンサ 221 と同様に構成され、基板バイアス部 225a、半導体領域 225b、ゲート電極 225g、ゲート絶縁膜 225i を含む。半導体領域 225b は、P 型ウェル 202a に高濃度の N 型不純物が注入されることによって形成される。半導体領域 225b 上にはゲート絶縁膜 225i を介してゲート電極 225g が形成される。ゲート電極 225g は例えばポリシリコン電極、または Al、Cu などのメタル電極から構成され、ゲート絶縁膜 225i は例えば SiO<sub>2</sub>、SiON、SiN などから構成される。基板バイアス部 225a は P 型ウェル 202a に N 型不純物を注入されることにより形成され得る。

30

#### 【0065】

ゲート電極 225g は第 2 の配線層領域 2B において接続部を介して金属配線 205a に接続される。金属配線 205a はさらに接続部を介して電極 206a に接続され、電極 206a は第 2 の半導体基板 2A の貫通電極 208a を介して接合コンタクト 24a に接続される。接合コンタクト 24a は第 1 の半導体基板 1A における信号処理部 13 の電源配線 VDD に接続される。また、基板バイアス部 225a、半導体領域 225b は第 2 の配線層領域 2B において接続部を介して金属配線 205b に接続される。金属配線 205b はさらに接続部を介して電極 206b に接続され、電極 206b は第 2 の半導体基板 2A の貫通電極 208b を介して接合コンタクト 24b に接続される。接合コンタクト 24b は第 1 の半導体基板 1A における信号処理部 13 の接地配線 GND に接続される。シールド部 23 は第 1 ~ 第 5 実施形態と同様に画素部 21 と容量部 22 との間に設けられる。

40

#### 【0066】

本実施形態においても、第 1 の半導体部品のための容量部は第 2 の半導体部品に設かれているため、容量部の専用の半導体部品を設ける必要がなくなり、製造コストを低減することが可能となる。

#### 【0067】

##### [第 7 実施形態]

本発明の第 7 実施形態による撮像システムについて、図 11 を用いて説明する。図 11

50

は、本実施形態による撮像システムの構成例を示すブロック図である。

#### 【 0 0 6 8 】

上述の実施形態における撮像装置は種々の撮像システムに適用可能である。撮像システムとして、デジタルスチルカメラ、デジタルカムコーダ、カメラヘッド、複写機、ファックス、携帯電話、車載カメラ、観測衛星、監視カメラなどがあげられる。図11に、撮像システムの例としてデジタルスチルカメラのブロック図を示す。

#### 【 0 0 6 9 】

図11に示す撮像システム7は、バリア706、レンズ702、絞り704、撮像装置70、信号処理部708、タイミング発生部720、全体制御・演算部718、メモリ部710、記録媒体制御I/F部716、記録媒体714、外部I/F部712を含む。バリア706はレンズを保護し、レンズ702は被写体の光学像を撮像装置70に結像させる。絞り704はレンズ702を通った光量を可変する。撮像装置70は上述の実施形態のように構成され、レンズ702により結像された光学像を画像データに変換する。ここで、撮像装置70の半導体基板にはAD(アナログデジタル)変換部が形成されているものとする。信号処理部708は撮像装置70より出力された撮像データに各種の補正やデータを圧縮する。

10

#### 【 0 0 7 0 】

タイミング発生部720は撮像装置70および信号処理部708に、各種タイミング信号を出力する。全体制御・演算部718はデジタルスチルカメラ全体を制御し、メモリ部710は画像データを一時的に記憶する。記録媒体制御I/F部716は記録媒体714に画像データの記録または読み出しを行うためのインターフェースであり、記録媒体714は撮像データの記録または読み出しを行うための半導体メモリ等の着脱可能な記録媒体である。外部I/F部712は外部コンピュータ等と通信するためのインターフェースである。タイミング信号などは撮像システムの外部から入力されてもよく、撮像システムは少なくとも撮像装置70と、撮像装置70から出力された撮像信号を処理する信号処理部708とを有すればよい。

20

#### 【 0 0 7 1 】

本実施形態では、撮像装置70とAD変換部とが別の半導体基板に設けられているが、撮像装置70とAD変換部とが同一の半導体基板に形成されていてもよい。また、撮像装置70と信号処理部708とが同一の半導体基板に形成されていてもよい。

30

#### 【 0 0 7 2 】

また、それぞれの画素が第1の光電変換部と、第2の光電変換部を含んでもよい。信号処理部708は、第1の光電変換部で生じた電荷に基づく画素信号と、第2の光電変換部で生じた電荷に基づく画素信号とを処理し、撮像装置70から被写体までの距離情報を取得するように構成されてもよい。

#### 【 0 0 7 3 】

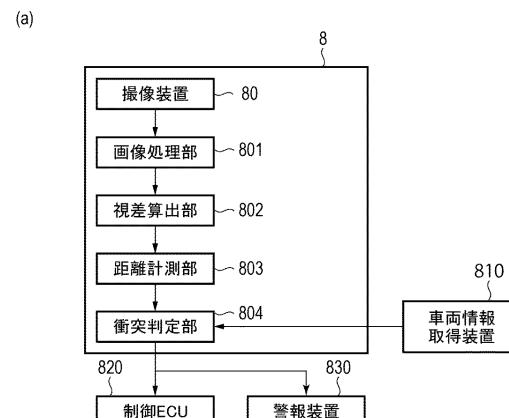

##### 〔 第8実施形態 〕

図12(a)、図12(b)は、本実施形態における車載カメラに関する撮像システムのブロック図である。撮像システム8は、上述した実施形態の撮像装置80を有する。撮像システム8は、撮像装置80により取得された複数の画像データに対し、画像処理を行う画像処理部801と、撮像システム8より取得された複数の画像データから視差(視差画像の位相差)の算出を行う視差算出部802を有する。また、撮像システム8は、算出された視差に基づいて対象物までの距離を算出する距離計測部803と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部804とを有する。ここで、視差算出部802、距離計測部803は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部804はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA(Field Programmable Gate Array)、ASIC(Application Specific Integrated Circuit)によ

40

50

i c a t i o n S p e c i f i c I n t e g r a t e d C i r c u i t ) によって実現されてもよいし、これらの組合せによって実現されてもよい。

#### 【 0 0 7 4 】

撮像システム 8 は車両情報取得装置 810 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、撮像システム 8 には、衝突判定部 804 での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御 E C U 820 が接続されている。また、撮像システム 8 は、衝突判定部 804 での判定結果に基づいて、ドライバーへ警報を発する警報装置 830 とも接続されている。例えば、衝突判定部 804 の判定結果として衝突可能性が高い場合、制御 E C U 820 はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置 830 は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。撮像システム 8 は上述のように車両を制御する動作の制御を行う制御手段として機能する。

#### 【 0 0 7 5 】

本実施形態では車両の周囲、例えば前方または後方を撮像システム 8 で撮像する。図 1 2 ( b ) は、車両前方 ( 撮像範囲 850 ) を撮像する場合の撮像システムを示している。撮像制御手段としての車両情報取得装置 810 が、上述の第 1 ~ 第 7 実施形態に記載した動作を行うように撮像システム 8 ないしは撮像装置 80 に指示を送る。このような構成により、測距の精度をより向上させることができる。

#### 【 0 0 7 6 】

上述では、他の車両と衝突しないように制御する例を説明したが、他の車両に追従して自動運転する制御、車線からはみ出さないように自動運転する制御などにも適用可能である。さらに、撮像システムは、自動車等の車両に限らず、例えば、船舶、航空機、人工衛星、産業用ロボットおよび民生用ロボットなどの移動体 ( 移動装置 ) に適用することができる。加えて、移動体に限らず、高度道路交通システム ( I T S ) 、監視システム等、広く物体認識または生体認識を利用する機器に適用することができる。

#### 【 0 0 7 7 】

##### [ 第 9 実施形態 ]

続いて、本実施形態における半導体装置を説明する。本実施形態における半導体装置は、電源電圧以外の定電圧および時間とともに変化する電圧などの基準電圧を生成する電圧生成回路においても適用され得る。以下、第 1 の半導体部品 1 に配される第 1 の回路部として、図 2 に示されたアナログデジタル変換部 11 を構成する回路を例として説明する。

#### 【 0 0 7 8 】

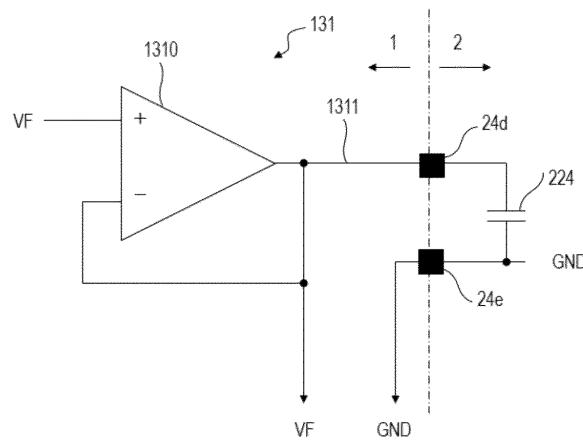

図 13 は本実施形態における基準電圧回路の模式図である。基準電圧回路 131 は、例えばアナログデジタル変換部 11 の前段の列アンプに用いられる。基準電圧回路 131 は、第 1 の半導体部品 1 に設けられた差動増幅器 1310 と第 2 の半導体部品 2 に設けられたバイパスコンデンサ ( 容量部 ) 224 とを備える。差動増幅器 1310 の反転入力端子および出力端子は接続され、ボルテージフォロワ回路として機能する。差動増幅器 1310 は非反転入力端子に印加された電圧に等しい基準電圧 V F を基準電圧線 1311 に出力する。基準電圧線 1311 は接合コンタクト 24d を介してバイパスコンデンサ 224 の一方の電極 ( 第 1 の入力ノード ) に接続されている。バイパスコンデンサ 224 の他方の電極 ( 第 2 の入力ノード ) は第 2 の半導体部品 2 における接地配線 GND に接続されるとともに、接合コンタクト 24e を介して第 1 の半導体部品 1 の接地配線 GND に接続されている。基準電圧線 1311 と接地配線 GNDとの間にはバイパスコンデンサ 224 が設けられているため、基準電圧線 1311 および接地配線 GND のインピーダンスが低減され、基準電圧 V F の変動が抑制される。基準電圧回路 131 は小電流を供給できればよいため、比較的に小さな容量値のバイパスコンデンサ 224 を第 2 の半導体部品 2 に設ければ足りる。チップ外部に大きな容量値のバイパスコンデンサを設けずに済むため、製造コストを低減できるとともに、装置全体を小型に構成することが可能となる。

### 【0079】

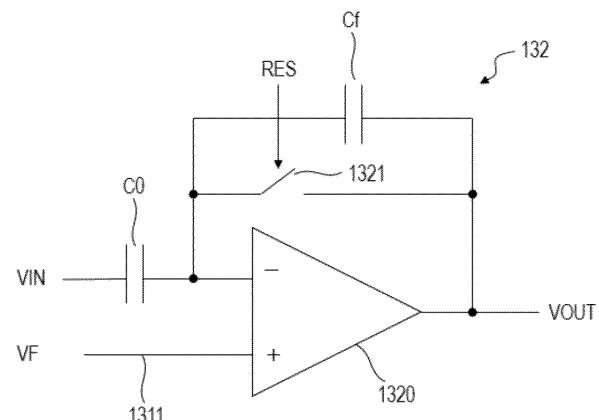

図14は本実施形態における反転増幅回路の模式図である。反転増幅回路132は例えば図2に示された信号線211毎に設けられ、各列の画素210の信号を増幅する。差動増幅器1320、入力容量C0、帰還容量Cf、スイッチ1321を備える。差動増幅器1320の非反転入力端子には図13に示された基準電圧線1311が接続され、基準電圧VFが非反転入力端子に印加される。差動増幅器1320の反転入力端子には入力容量C0を介して信号VINが入力される。差動増幅器1320の反転入力端子と出力端子との間には帰還容量Cf、スイッチ1321が接続される。スイッチ1321はトランジスタから構成され、ゲートに印加された制御信号RESに応じてオンまたはオフとなる。差動増幅器1320は入力容量C0、帰還容量Cf、スイッチ1321に応じた利得で信号VINを増幅し、信号VOUTを出力する。

10

### 【0080】

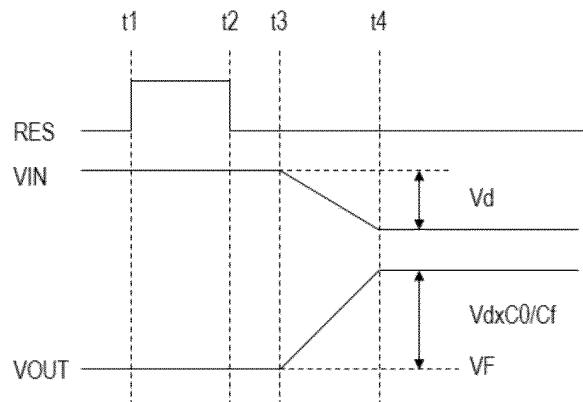

図15は本実施形態における反転増幅回路の動作を表すタイミングチャートである。時刻t1において、制御信号RESがハイレベルとなると、スイッチ1321はオンになり、差動増幅器1320の出力端子と反転入力端子とが短絡し、差動増幅器1320はボルテージフォロワとして動作する。また、非反転入力端子と反転入力端子とはイマジナリーショートとなり、反転入力端子の電圧は非反転入力端子の基準電圧VFに等しくなる。このため、差動増幅器1320の信号VOUTの電圧は基準電圧VFとなる。時刻t2において、制御信号RESがローレベルになり、スイッチ1321はオフになることにより、差動増幅器1320の増幅率はC0/Cfとなる。時刻t3～t4において、入力信号VINの電圧がVdだけ低下すると、出力信号VOUTの電圧はVd×C0/Cfだけ上昇する。反転増幅回路132からの出力信号VOUTは、例えば図2に示されたアナログデジタル変換部11によってデジタルデータに変換される。

20

### 【0081】

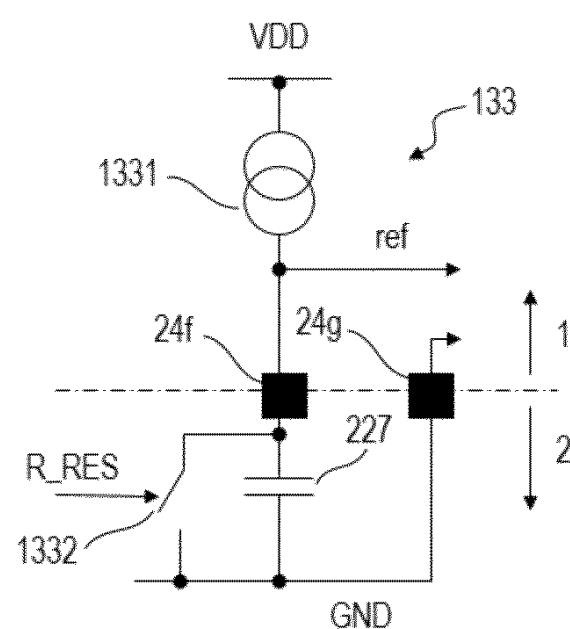

図16は本実施形態における参照信号生成回路の模式図である。参照信号生成回路133はいわゆるスロープ型のアナログデジタル変換部における参照信号を生成する。参照信号生成回路133は電流源1331、リセットスイッチ1332、充電容量(容量部)227を備える。電流源1331は第1の半導体部品1に設けられ、トランジスタなどから構成される。充電容量227は第2の半導体部品2に設けられている。充電容量227を第2の半導体部品2の空いた領域に設けることにより、装置全体を小型に構成することが可能となる。充電容量227の一方の電極(第1の入力ノード)は接合コンタクト24fを介して電流源1331に接続されている。充電容量227には電流源1331から電流が供給され、充電容量227の電荷に応じた参照信号refが出力される。充電容量227の他方の電極(第2の入力ノード)は第2の半導体部品2における接地配線GNDに接続されるとともに、接合コンタクト24gを介して第1の半導体部品1の接地配線GNDに接続されている。リセットスイッチ1332は第2の半導体部品2に設けられ、トランジスタから構成されている。リセットスイッチ1332は、ゲートに印加された制御信号RRESに応じてオンまたはオフとなる。リセットスイッチ1332がオンとなることにより、充電容量227の電荷を接地配線GNDに放電する。なお、リセットスイッチ1332は第1の半導体部品1に設けられてもよい。

30

### 【0082】

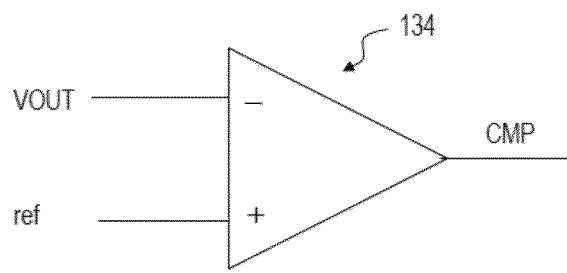

図17は本実施形態における比較回路の図である。比較回路134は差動増幅器から構成され、アナログデジタル変換部において用いられる。比較回路134の非反転入力端子には参照信号refが入力され、反転入力端子にはアナログ信号である信号VOUTが入力される。比較回路134は参照信号refと出力信号VOUTとの比較結果を表す比較信号CMPを出力する。図示されていないカウンタ回路は、比較信号CMPが反転するまでの時間(カウント値)を計測し、カウント値をアナログ信号である出力信号VOUTに対応するデジタル信号DOUTとして出力する。

40

### 【0083】

図18は本実施形態における参照信号生成回路の動作を表すタイミングチャートである

50

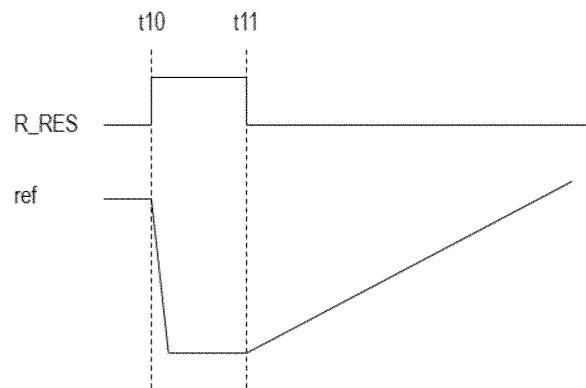

。時刻  $t_{10}$ において、制御信号 R\_ES がハイレベルとなり、リセットスイッチ 1332 がオンになる。リセットスイッチ 1332 がオンになると、充電容量 227 に蓄積されていた電荷が放電され、参照信号生成回路 1333 の参照信号 ref の電圧は GND 電位になる。時刻  $t_{10} \sim t_{11}$ において、制御信号 R\_ES はハイレベルであるため、リセットスイッチ 1332 はオンの状態を維持し、電流源 1331 から供給される電流はリセットスイッチ 1332 を介して接地配線 GND に流れ続ける。時刻  $t_{11}$ において、制御信号 R\_ES がローレベルになり、リセットスイッチ 1332 がオフになる。リセットスイッチ 1332 がオフになると、電流源 1331 から供給される電流が充電容量 227 に充電される。時刻の経過とともに充電容量 227 に蓄積される電荷量が増大し、参照信号 ref の電圧は次第に上昇する。

10

#### 【0084】

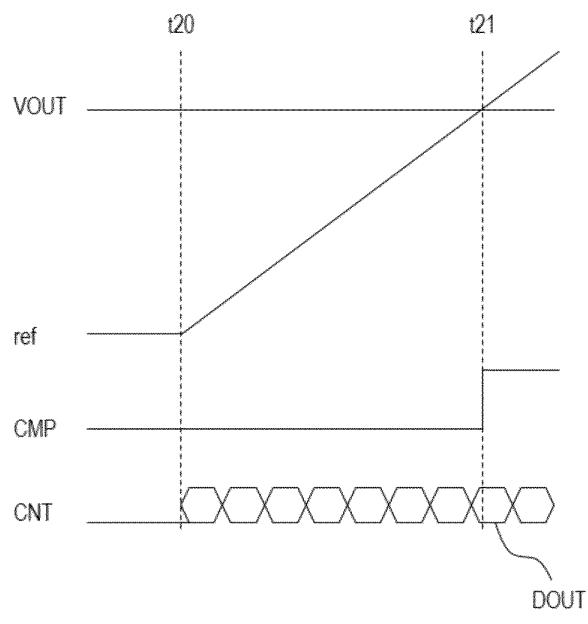

図 19 は、本実施形態におけるアナログデジタル変換部の動作を表すタイミングチャートである。時刻  $t_{20}$ において、参照信号生成回路 1333 は参照信号 ref の電圧の上昇を開始するとともに、カウンタ回路はクロックパルスのカウントを開始する。時刻  $t_{21}$ において、アナログ信号である信号 VOUT と参照信号 ref の電圧の大小関係が反転し、比較信号 CMP はローレベルからハイレベルに反転する。アナログデジタル変換部は、比較信号 CMP が反転した時刻におけるカウント値 CNT をメモリに記憶する。このカウント値 CNT はアナログ信号である信号 VOUT に対応するデジタル信号 DOUT として出力される。

#### 【0085】

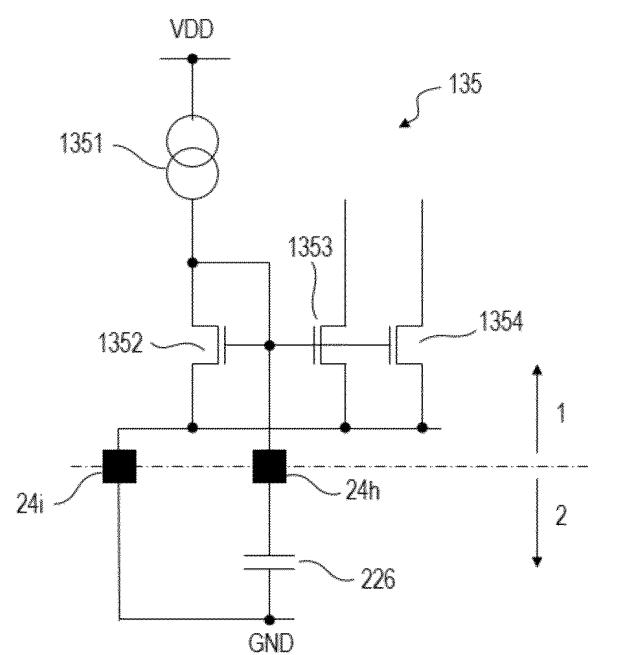

図 20 は本実施形態におけるカレントミラー回路の模式図である。カレントミラー回路 135 は電流源回路として広く用いられる。カレントミラー回路 135 は電流源 1351、トランジスタ 1352、1353、1354、容量 226 を備える。電流源 1351、トランジスタ 1352、1353、1354 は第 1 の半導体部品 1 に設けられ、容量 226 は第 2 の半導体部品 2 に設けられている。容量 226 の一方の電極（第 1 の入力ノード）は接合コンタクト 24h を介してトランジスタ 1352、1353、1354 のゲートに接続されている。容量 226 の他方の電極（第 2 の入力ノード）は第 2 の半導体部品 2 の接地配線 GND に接続されるとともに、接合コンタクト 24i を介して第 1 の半導体部品 1 の接地配線 GND に接続されている。容量 226 がトランジスタ 1352、1353、1354 のゲートと接地配線 GNDとの間に設けられているため、ノイズ等によるゲート電圧の変動を抑制することができる。

20

#### 【0086】

上述のように、本発明は電源電圧以外の基準電圧の生成回路、時間とともに変化する参照信号の生成回路、カレントミラー回路においても適用可能である。本実施形態においても、チップ外部に配置していた容量をチップ内部に配置することにより、チップ外の容量を削減することができる。これにより、コストの削減およびプリント基板の低面積化が可能となる。

30

#### 【0087】

##### [変形実施形態]

本発明は、上述の実施形態に限らず種々の変形が可能である。例えば、いずれかの実施形態の一部の構成を他の実施形態に追加した例や、他の実施形態の一部の構成と置換した例も、本発明の実施形態である。

40

#### 【0088】

本発明は、上述の実施形態の 1 以上の機能を実現するプログラムを、ネットワークまたは記憶媒体を介してシステムまたは装置に供給し、そのシステムまたは装置のコンピュータにおける 1 つ以上のプロセッサがプログラムを読み出し実行する処理でも実現可能である。また、1 以上の機能を実現する回路（例えば、ASIC）によっても実現可能である。

#### 【0089】

なお、上述の実施形態は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないもの

50

である。すなわち、本発明はその技術思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。

#### 【0090】

例えば、本発明における半導体装置は撮像装置に限定されることなく、様々な機器に適用可能である。例えば、カメラ、携帯端末、汎用コンピュータ等の電子機器、自動車や船舶、飛行機等の輸送機器、通信機器、複写機、プリンタ、スキャナ等の事務機器、ディスプレイ等の表示機器、X線診断機器や内視鏡等の医療機器、分析機器、半導体製造装置などの産業機器全般において、本発明における半導体装置を適用することができる。また、本実施形態における半導体装置に接続され得る装置は、演算回路を含む画像処理装置、電源コントローラ、モータコントローラ、ロボットコントローラなどの制御装置、半導体メモリ、磁気記録媒体、光記録媒体を用いた記憶装置、液晶ディスプレイ、OLED (Organic Light Emitting Diode) ディスプレイなどの表示装置などを含み得る。

10

#### 【0091】

また、上述の実施形態において、容量部がバイパスコンデンサ（デカップリング容量）として用いられる例を説明したが、容量部は他の用途に用いられてもよい。例えば、信号線の間に設けられるカップリングコンデンサ（カップリング容量）として容量部を用いてもよい。

#### 【符号の説明】

#### 【0092】

20

- 1 第1の半導体部品

- 1 A 第1の半導体基板

- 1 B 第1の配線層領域

- 1 3 信号処理部

- 2 第2の半導体部品

- 2 A 第2の半導体基板

- 2 B 第2の配線層領域

- 2 1 画素部

- 2 2 容量部

- 2 3 シールド部

- 2 4 接合コンタクト

- 2 5 接続部

- 2 9 パッド電極

- 3 0 外部パッド電極

- 3 1 ボンディングワイヤ

30

40

50

【四面】

【 四 1 】

【 四 2 】

【 図 3 】

【 図 4 】

【 四 5 】

【 四 6 】

10

20

【図7】

【圖 8】

30

40

50

【図9】

【図10】

10

20

30

40

【図11】

【図12】

(b)

50

【図 1 3】

【図 1 4】

10

【図 1 5】

【図 1 6】

20

30

40

50

【図 1 7】

【図 1 8】

【図 1 9】

【図 2 0】

---

フロントページの続き

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 鈴木 明

(56)参考文献 特開2015-139199 (JP, A)

特開2013-016963 (JP, A)

特開2006-147795 (JP, A)

特開2012-124318 (JP, A)

国際公開第2019/031089 (WO, A1)

特開2013-172279 (JP, A)

特開2012-089739 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H04N 25/00 - 25/79

H01L 27/146