(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-107448

(P2014-107448A)

(43) 公開日 平成26年6月9日(2014.6.9)

(51) Int.Cl.

H01L 27/146 (2006.01)

H01L 21/02 (2006.01)

F 1

H01L 27/14

H01L 21/02

テーマコード(参考)

4M118

B

審査請求 未請求 請求項の数 12 O L (全 16 頁)

(21) 出願番号

特願2012-260135 (P2012-260135)

(22) 出願日

平成24年11月28日 (2012.11.28)

(71) 出願人 000004112

株式会社ニコン

東京都千代田区有楽町1丁目12番1号

110000877

龍華国際特許業務法人

綱井 史郎

東京都千代田区有楽町1丁目12番1号

株式会社ニコン内

菅谷 功

東京都千代田区有楽町1丁目12番1号

株式会社ニコン内

岡田 政志

東京都千代田区有楽町1丁目12番1号

株式会社ニコン内

最終頁に続く

(54) 【発明の名称】積層半導体装置の製造方法および積層半導体製造装置

## (57) 【要約】

【課題】簡潔な工程で積層半導体装置を製造する。

【解決手段】積層半導体装置製造方法であって、受光素子を含む受光回路を有する受光基板と、受光回路から受けた信号を処理する処理回路を有する処理基板とを積層して積層半導体装置を製造する方法であって、受光回路側の面と処理回路側の面とを向い合せて受光基板および処理基板を積層する異種基板積層段階と、異種基板積層段階よりも後に受光基板を薄化する受光基板薄化段階とを備える。上記製造方法において、受光基板薄化段階よりも前に、処理基板を薄化する処理基板薄化段階を更に有してもよい。

【選択図】図6

## 【特許請求の範囲】

## 【請求項 1】

受光素子を含む受光回路を有する受光基板と、前記受光回路から受けた信号を処理する処理回路を有する処理基板とを積層して積層半導体装置を製造する製造方法であって、

前記受光回路側の面と前記処理回路側の面とを向い合せて前記受光基板および前記処理基板を積層する異種基板積層段階と、

前記異種基板積層段階よりも後に前記受光基板を薄化する受光基板薄化段階とを備える積層半導体装置製造方法。

## 【請求項 2】

前記受光基板薄化段階よりも前に、前記処理基板を薄化する処理基板薄化段階を更に有する請求項 1 に記載の積層半導体装置製造方法。 10

## 【請求項 3】

前記処理基板薄化段階よりも後であって、前記受光基板薄化段階よりも前に、前記積層された前記受光基板および前記処理基板を一括してアニール処理する段階を更に備える請求項 2 に記載の積層半導体装置製造方法。

## 【請求項 4】

前記異種基板積層段階よりも前に、前記処理回路に接続される他の処理回路を有する他の処理基板を、前記処理回路を有する前記処理基板に積層する処理基板積層段階を更に含む請求項 1 から請求項 3 までのいずれか一項に記載の積層半導体装置製造方法。

## 【請求項 5】

前記処理基板積層段階よりも後であって、前記異種基板積層段階よりも前に、積層された前記処理基板を一括してアニール処理する段階を更に備える請求項 4 に記載の積層半導体装置製造方法。 20

## 【請求項 6】

前記受光基板薄化段階は、前記受光回路に隣接する絶縁層を支持する支持層を化学機械研磨する研磨段階を含む請求項 1 から請求項 5 までのいずれか一項に記載の積層半導体装置製造方法。

## 【請求項 7】

前記受光基板薄化段階は、前記研磨段階の後に、前記絶縁層に到達するまで前記支持層を食刻する食刻段階を含む請求項 6 に記載の積層半導体装置製造方法。 30

## 【請求項 8】

前記積層段階の後であって前記受光基板薄化段階の前に、積層された前記受光基板および前記処理基板を一括してアニール処理する段階を更に備える請求項 1 から請求項 7 までのいずれか一項に記載の積層半導体装置製造方法。

## 【請求項 9】

前記受光基板薄化段階よりも後に、前記積層された前記受光基板および前記処理基板を一括してアニール処理する段階を更に備える請求項 1 から請求項 8 までのいずれか一項に記載の積層半導体装置製造方法。

## 【請求項 10】

前記異種基板積層段階よりも前に、他の受光回路を有する他の受光基板を、前記受光基板に積層する受光基板積層段階を更に含む請求項 1 から請求項 9 までのいずれか一項に記載の積層半導体装置製造方法。 40

## 【請求項 11】

前記受光基板積層段階よりも後であって、前記異種基板積層段階よりも前に、前記他の受光基板を薄化する段階を更に含む請求項 10 に記載の積層半導体装置製造方法。

## 【請求項 12】

受光素子を含む受光回路を有する受光基板と、前記受光回路から受けた信号を処理する処理回路を有する処理基板とを積層して積層半導体装置を製造する装置であって、

受光素子を含む受光回路を有する受光基板における前記受光回路側の面と前記受光回路から受けた信号を処理する処理回路を有する処理基板における前記処理回路側の面と向 50

い合せて前記受光基板および前記処理基板を積層する異種基板積層部と、

異種基板積層部により前記処理基板に積層された前記受光基板において、前記受光基板を薄化する受光基板薄化部と

を備える積層半導体製造装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、積層半導体装置の製造方法および積層半導体製造装置に関する。

【背景技術】

【0002】

受光素子を含む基板と信号処理回路を含む基板とを積層して製造される積層半導体装置がある。

[先行技術文献]

[特許文献]

[特許文献1]特開2006-49361号公報

【発明の概要】

【発明が解決しようとする課題】

【0003】

積層半導体装置は、例えば、基板の薄化段階において支持用のダミー基板を脱着する等の手順により工数が多くなるので生産性が低い。

【課題を解決するための手段】

【0004】

本発明の第一態様においては、受光素子を含む受光回路を有する受光基板と、受光回路から受けた信号を処理する処理回路を有する処理基板とを積層して積層半導体装置を製造する方法であって、受光回路側の面と処理回路側の面とを向い合せて受光基板および処理基板を積層する異種基板積層段階と、異種基板積層段階よりも後に受光基板を薄化する受光基板薄化段階とを備える積層半導体装置製造方法が提供される。

【0005】

本発明の第二態様においては、受光素子を含む受光回路を有する受光基板と、受光回路から受けた信号を処理する処理回路を有する処理基板とを積層して積層半導体装置を製造する装置であって、受光素子を含む受光回路を有する受光基板における受光回路側の面と受光回路から受けた信号を処理する処理回路を有する処理基板における処理回路側の面とを向い合せて受光基板および処理基板を積層する異種基板積層部と、異種基板積層部により処理基板に積層された受光基板において、受光基板を薄化する受光基板薄化部とを備える積層半導体装置が提供される。

【0006】

上記した発明の概要は、本発明の必要な特徴の全てを列挙したものではない。これら特徴群のサブコンビネーションも発明となり得る。

【図面の簡単な説明】

【0007】

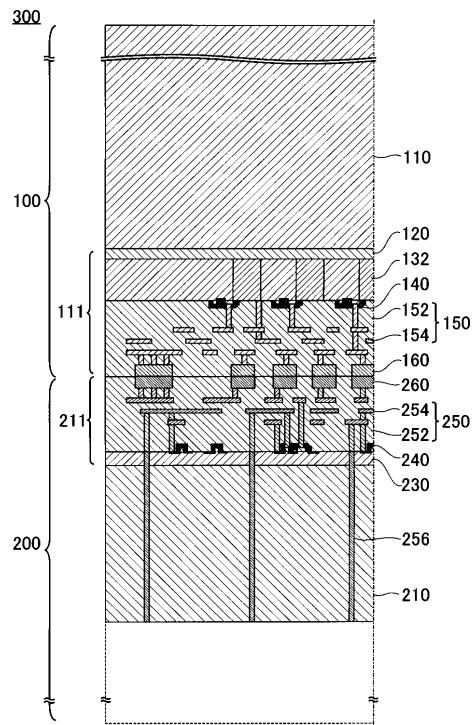

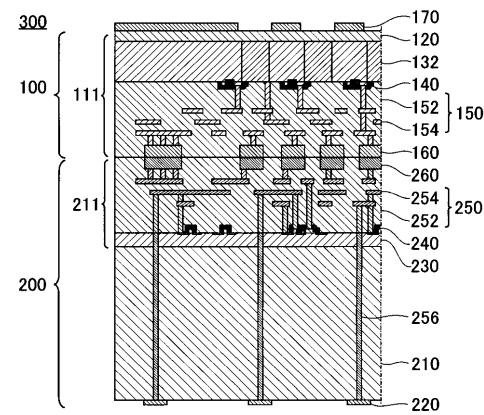

【図1】受光基板100の断面図である。

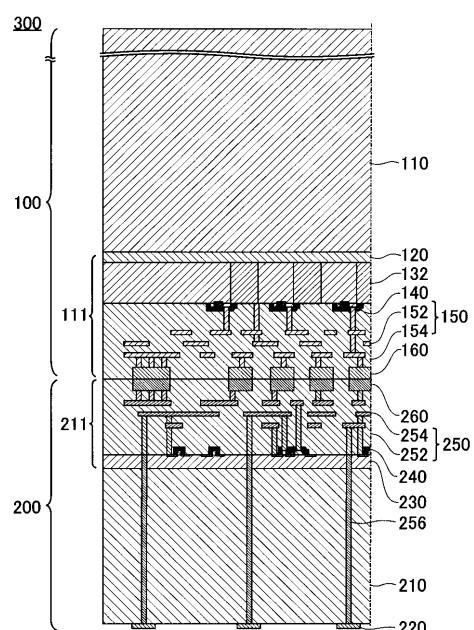

【図2】処理基板200の断面図である。

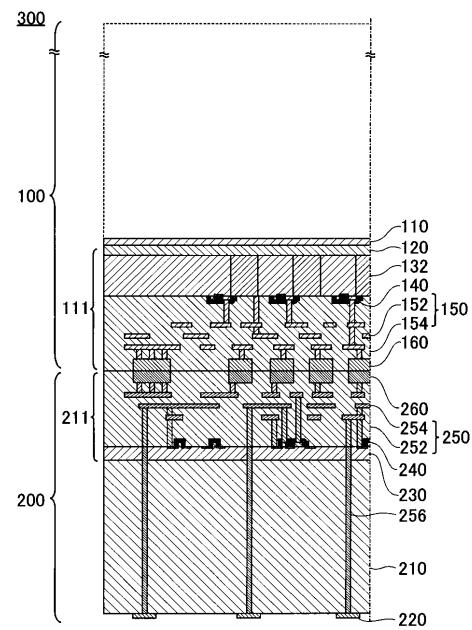

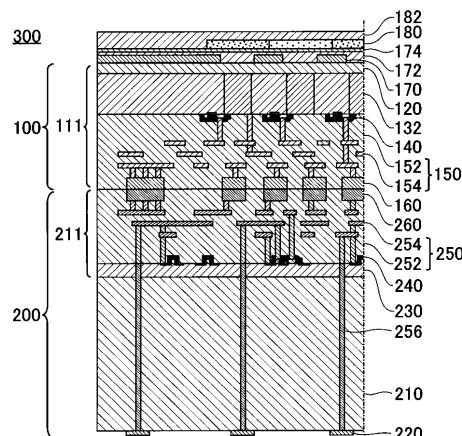

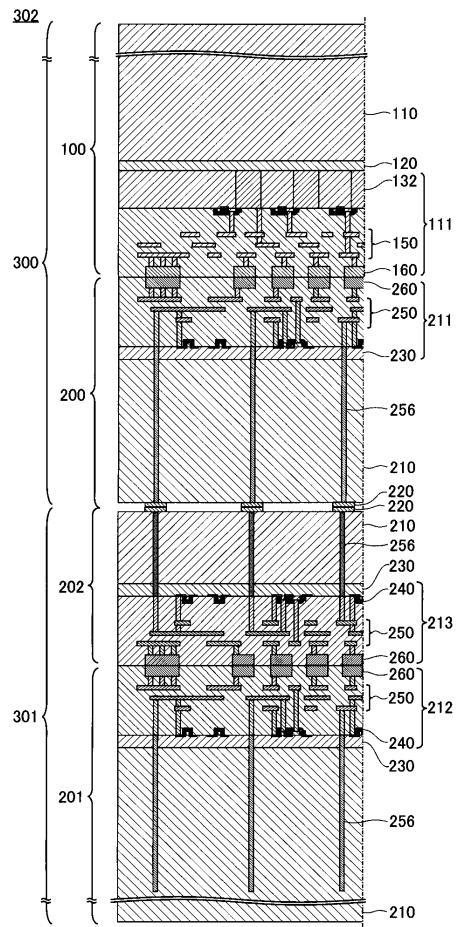

【図3】積層基板300の断面図である。

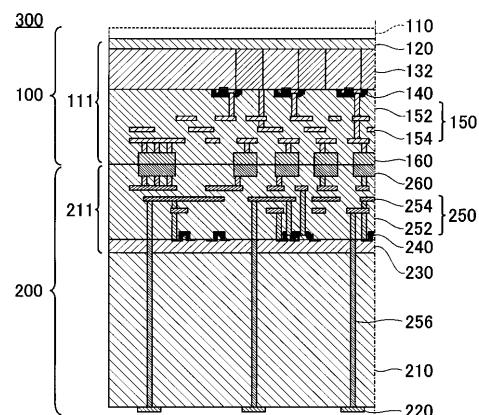

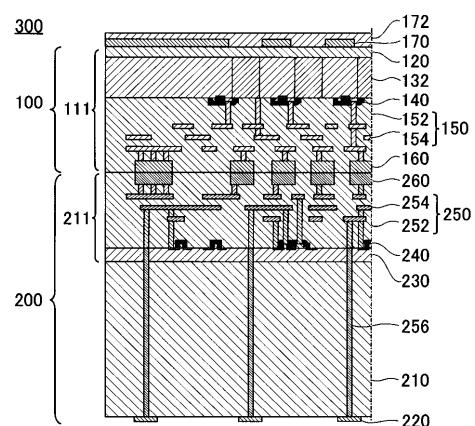

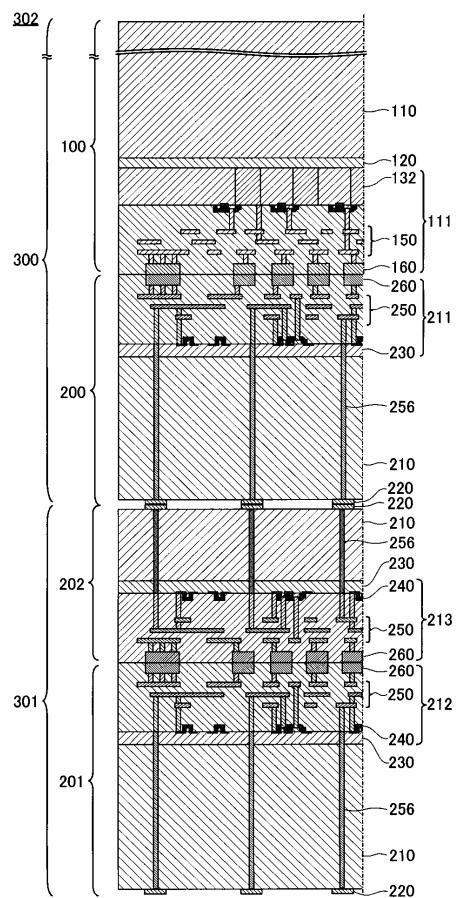

【図4】積層基板300の断面図である。

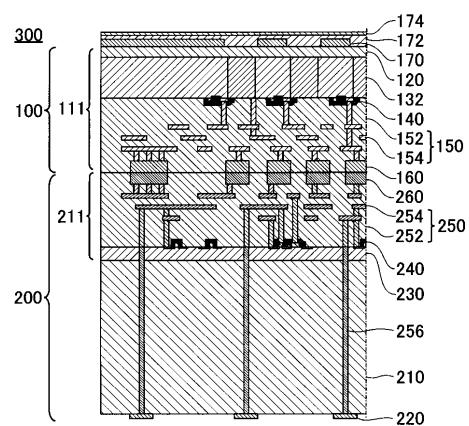

【図5】積層基板300の断面図である。

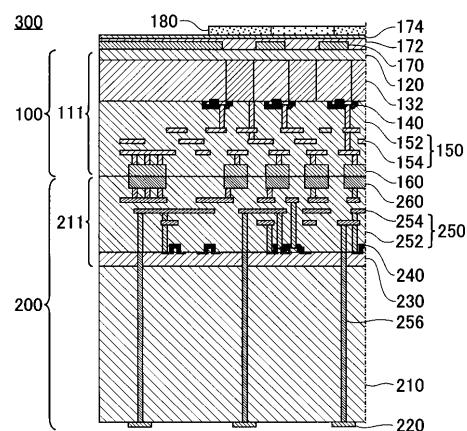

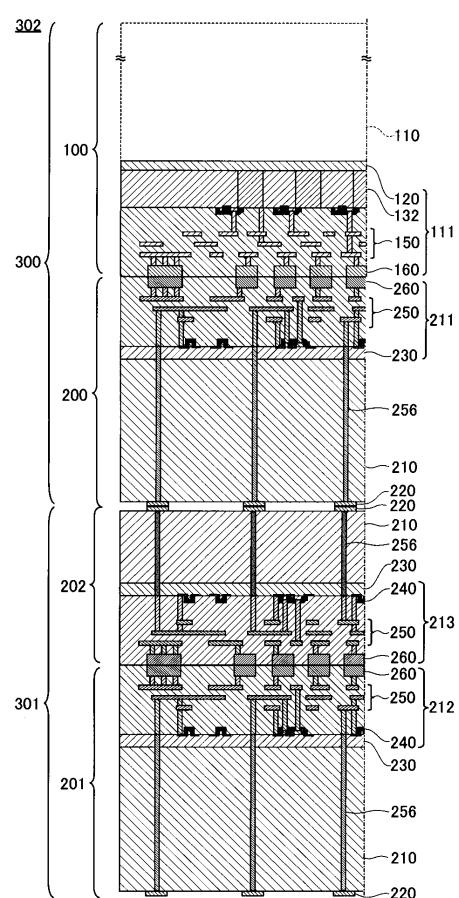

【図6】積層基板300の断面図である。

【図7】積層基板300の断面図である。

【図8】積層基板300の断面図である。

【図9】積層基板300の断面図である。

【図10】積層基板300の断面図である。

10

20

30

40

50

【図11】積層基板300の断面図である。

【図12】積層基板300の断面図である。

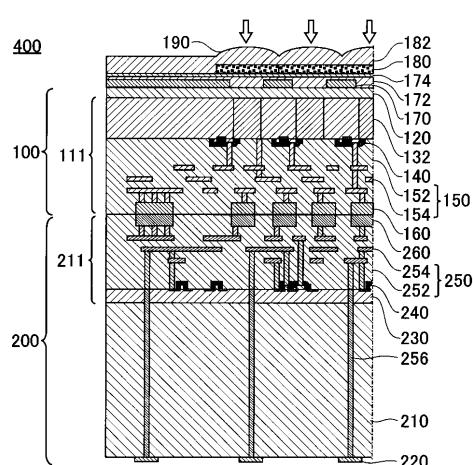

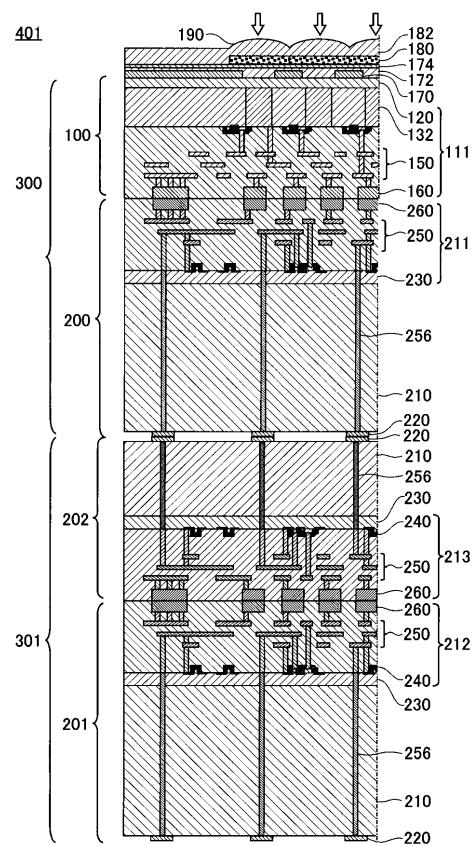

【図13】積層半導体装置400の断面図である。

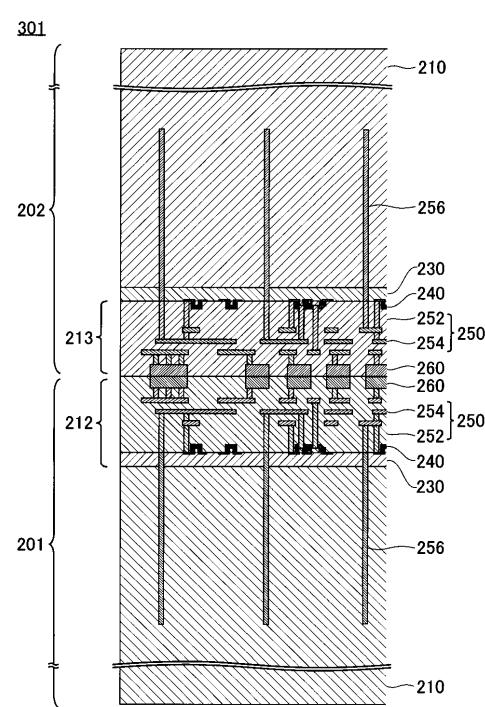

【図14】積層基板301の断面図である。

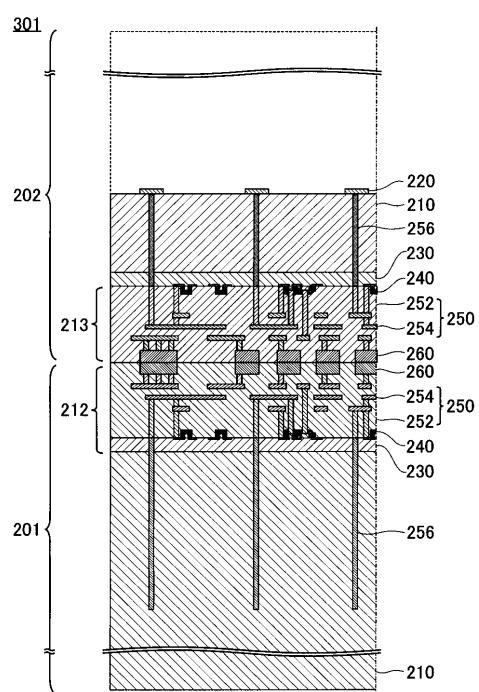

【図15】積層基板301の断面図である。

【図16】積層基板302の断面図である。

【図17】積層基板302の断面図である。

【図18】積層基板302の断面図である。

【図19】積層半導体装置401の断面図である。

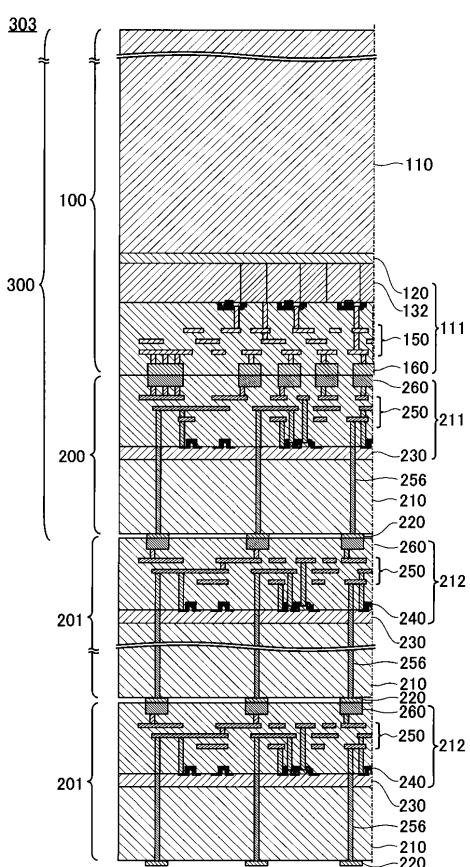

【図20】積層基板303の断面図である。

10

## 【発明を実施するための形態】

## 【0008】

以下、発明の実施の形態を通じて本発明を説明する。下記の実施形態は特許請求の範囲に係る発明を限定するものではない。実施形態の中で説明されている特徴の組み合わせの全てが発明の解決手段に必須であるとは限らない。

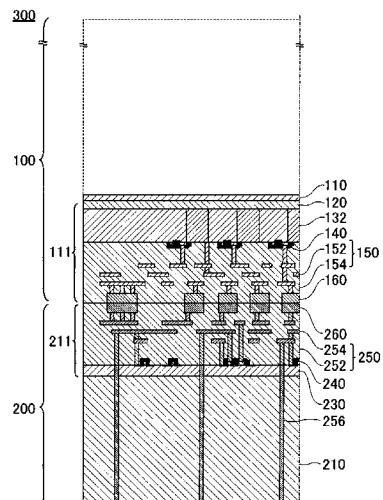

## 【0009】

図1は、積層半導体装置400の材料として用い得る受光基板100の断面図である。受光基板100は、支持基板110、半導体ウェル130および多層配線層150を備える。

20

## 【0010】

支持基板110は、シリコン単結晶ウエハ等により形成され、受光基板100の機械的強度を担う厚さ、例えば、直径12インチのシリコン単結晶ウエハであれば、775 μm程度の厚さを有する。支持基板110の一面には、絶縁層120を介して半導体ウェル130が配される。半導体ウェル130には、支持基板110の面方向に、複数のフォトダイオード132がマトリクス状に作り込まれている。

## 【0011】

半導体ウェル130には、隣接して形成されたゲート電極140等により複数の電界効果トランジスタもが形成される。このような構造により、フォトダイオード132および電界効果トランジスタにより形成された受光回路111に対する支持基板110の浮遊容量が抑制され、受光回路111のスイッチング速度が向上されると共に消費電力が低減される。

30

## 【0012】

多層配線層150は、半導体ウェル130の表面に交互に積層された層間絶縁材152および配線材154により形成される。配線材154としては、チタン、タングステン等の金属材料を使用できる。

## 【0013】

フォトダイオード132および電界効果トランジスタは、多層配線層150により相互に接続されて、概ね厚さ10 μm以下の受光回路111を形成する。多層配線層150における配線材154の一端は、支持基板110と反対側の一面において外部に露出した接続パッド160に電気的に接続される。

40

## 【0014】

受光回路111においては、フォトダイオード132の各々が画素に対応し、電界効果トランジスタが画素毎にリセット、選択および増幅を担う。フォトダイオード132が入射光を受けて蓄積した電荷は、電界効果トランジスタによるソースフォロワを通じて電圧信号として接続パッド160から外部に出力される。

## 【0015】

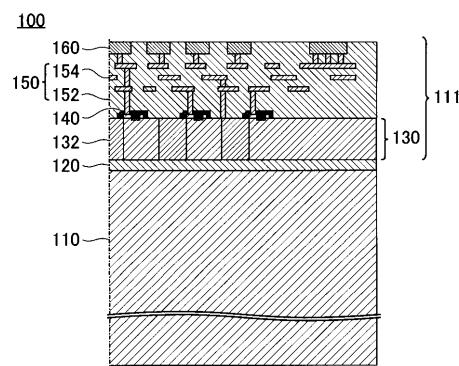

図2は、積層半導体装置400の材料として用い得る処理基板200の断面図である。処理基板200は、支持基板210、半導体ウェル230および多層配線層250を備える。

## 【0016】

50

支持基板 210 は、シリコン単結晶ウエハ等により形成され、受光基板 100 の機械的強度を担う厚さ、例えば、直径 12 インチのシリコン単結晶ウエハであれば、775  $\mu\text{m}$  程度の厚さを有する。支持基板 210 の一面には、半導体ウェル 230 が配される。半導体ウェル 230 には、半導体ウェル 230 に隣接して形成されたゲート電極 240 等により複数の電界効果トランジスタが作り込まれている。

【0017】

多層配線層 150 は、半導体ウェル 230 の表面に交互に積層された層間絶縁材 252 および配線材 254 により形成される。複数の電界効果トランジスタは、多層配線層 250 により相互に接続されて処理回路 211 を形成する。

【0018】

また、多層配線層 250 における配線材 254 の一端は、支持基板 210 と反対側の一面において外部に露出した接続パッド 260 に電気的に接続される。処理基板 200 の接続パッド 260 は、受光基板 100 の接続パッド 160 に接続される。これにより、処理基板 200 の処理回路 211 は、受光基板 100 の受光回路 111 の出力信号を処理する。処理回路 211 における処理としては、アナログ/デジタル変換、ノイズ抑圧、ファイル生成等を例示できる。

【0019】

なお、図示の処理基板 200 は、支持基板 210 に嵌入した貫通電極 256 を有する。貫通電極は、例えば、デュアルダマシン法により銅で形成される。貫通電極 256 の一端は、多層配線層 250 の配線材 254 に電気的に接続される。貫通電極 256 の他端は、図示の段階では、支持基板 210 の内部に埋没している。

【0020】

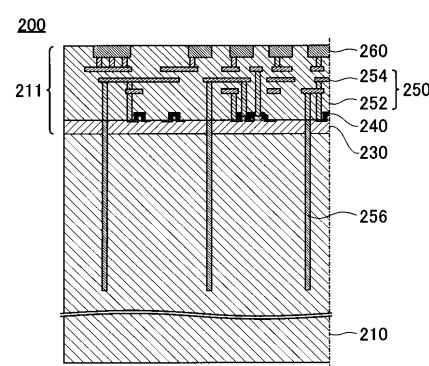

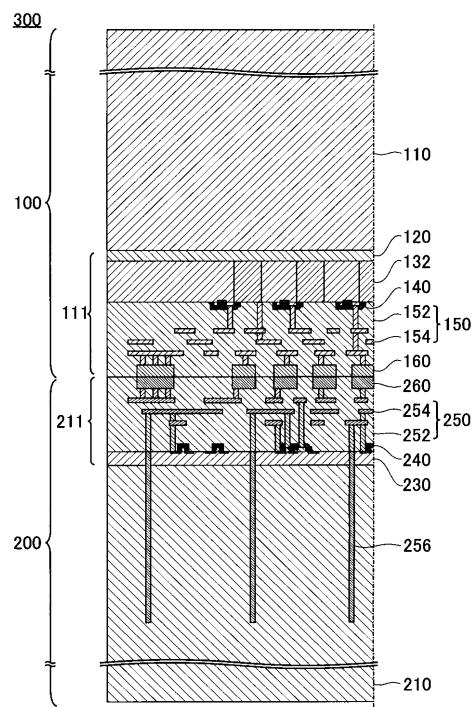

上記のような受光基板 100 および処理基板 200 を貼り合わせることにより、イメージセンサとして用い得る積層半導体装置 400 を製造できる。図 3 から図 13 は、そのような積層半導体装置 400 の製造過程を段階毎に示す断面図である。

【0021】

なお、受光基板 100 および処理基板 200 のそれぞれは、図 1 または図 2 に示した構造をそれぞれの面方向に繰り返し有する。よって、受光基板 100 および処理基板 200 を積層することにより、多数の積層半導体装置 400 を含む積層基板 300 を一括して製造できる。

【0022】

まず、図 3 に示すように、受光基板 100 および処理基板 200 を積層して積層基板 300 を形成する。図示の例では、図 1 に示した状態に対して受光基板 100 の表裏を反転させ、処理基板 200 に積層する。これにより、この段階において 1550  $\mu\text{m}$  以上の厚さを有する積層基板 300 が形成される。積層基板 300 においては、受光基板 100 の接続パッド 160 と、処理基板 200 の接続パッド 260 とが互いに当接して電気的に接続される。

【0023】

受光基板 100 および処理基板 200 は、接続パッド 160、260 の少なくとも一方をはんだバンプ、銅バンプ等にして圧接することにより貼り合わせてもよい。この場合、受光基板 100 および処理基板 200 はそれぞれ支持基板 110、210 を有しているので、十分な圧力を加えることができる。

【0024】

また、接続パッド 160、260 を含む受光基板 100 および処理基板 200 の端面を鏡面研磨して常温接合させてもよい。この場合も、受光基板 100 および処理基板 200 が支持基板 110、210 を有しているので、これら支持基板 110、210 を保持して受光基板 100 および処理基板 200 を研磨することができる。

【0025】

受光基板 100 および処理基板 200 の位置合わせは、予め定めた数箇所の位置合わせ指標の位置ずれに基づいて全体の位置ずれが最小になる位置を算出するグローバルアライ

メント法により、積層基板 300 の歩留りを向上させることができる。更に、位置合わせ指標の位置に基づいて、オフセット補正、回転補正、直交度補正、スケーリング補正等を加えて、位置合わせ精度をより向上させることができる。

【0026】

位置合わせ指標として、接続パッド 160、260 そのものを利用してもよいし、受光基板 100 および処理基板 200 に形成された配線、基板等を利用してもよい。更に、位置合わせに利用する目的で受光基板 100 および処理基板 200 に設けたアライメントマークを利用してもよい。また、位置ずれを測定するために位置合わせ指標を観察する場合、受光基板 100 および処理基板 200 の接合面を直接に観察する方法の他に、基板を透過する赤外帯域で観察してもよい。

10

【0027】

次に、図 4 に示すように、積層基板 300 において、処理基板 200 の支持基板 210 を、例えば 500  $\mu\text{m}$  程度まで薄化する。支持基板 210 は、例えば、化学機械研磨により薄化できる。これにより、支持基板 210 の図中下面には、貫通電極 256 の端部が露出する。

【0028】

なお、処理基板 200 の薄化に先立って、200 から 300 の温度範囲で、30 分から 60 分の処理時間で積層基板 300 をアニール処理してもよい。これにより、受光基板 100 および処理基板 200 の貼り合わせに伴い積層基板 300 に生じた内部応力が緩和されるので、薄化のために研磨等で生じる応力により受光基板 100 および処理基板 200 が剥離することが防止される。

20

【0029】

また、処理基板 200 の薄化処理後にも積層基板 300 を、上記と同様の条件でアニール処理してもよい。薄化処理後の支持基板 210 は平坦性が高いので、積層基板 300 を全体に均一に加熱できる。よって、アニール処理により緩和される内部応力も、積層基板 300 全体で均一になる。

【0030】

次に、図 5 に示すように、支持基板 210 の図中下面に露出した貫通電極 256 の端部にバンプ 220 を形成する。これにより、処理基板 200 の処理回路 211 を、積層基板 300 の図中下面から外部に接続できる状態になる。バンプ 220 は、例えば、溶融はんだにより接合するはんだバンプ、相互拡散により接合する銅バンプ等を適宜選択できる。

30

【0031】

次に、図 6 に示すように、受光基板 100 の支持基板 110 を薄化する。支持基板 110 は、例えば、処理基板 200 側に残る支持基板 210 を保持して化学機械研磨することにより薄化できる。ここで、図示の例では、支持基板 110 を全て除去せずに、絶縁層 120 が露出する直前で化学機械研磨を停止する。

【0032】

ここまで段階においては、受光基板 100 の表面が受光基板 100 の支持基板 210 により覆われている。よって、処理基板 200 側に支持基板 210 の研磨、バンプ 220 の形成等により生じた塵芥は、受光基板 100 側の支持基板 110 に付着していたとしても、支持基板 110 の薄化処理と共に除去される。

40

【0033】

なお、上記のように受光基板 100 側の支持基板 110 を薄化する場合も、薄化処理の前後に、積層基板 300 をアニール処理してもよい。これにより、積層基板 300 の残留応力を緩和できる。また、薄化処理により生じた応力を開放できる。アニール処理は、200 から 300 の温度範囲で、30 分から 60 分の処理時間で有効になる。

【0034】

続いて、図 7 に示すように、絶縁層 120 の表面に残った支持基板 110 を化学エッティングにより除去する。エッチャントとして、支持基板 110 を食刻するが、絶縁層 120 とは反応しない選択性を有するものを用いる。これにより、積層基板 300 には、厚さ 1

50

0 μm程度の受光回路 111 が残る。これにより、支持基板 110 の除去後に形成される受光基板 100 の表面は、絶縁層 120 自体の平坦性を有する。このように、化学機械研磨で支持基板 110 を残し、エッティングにより支持基板 110 を除去することにより、化学機械研磨により生じがちな研磨量の偏りを防止できる。

【0035】

このように、上記の方法では、化学機械研磨をする場合に限って一時的に使用されるダミー基板を用いることなく薄化処理を実行して積層基板 300 を製造できる。よって、ダミー基板の着脱等の作業工数を省くことができ、積層基板の製造工程を簡略化できる。

【0036】

次に、図 8 に示すように、積層基板 300 における受光基板 100 側の表面に遮光層 170 を形成する。遮光層 170 は、受光基板 100 におけるフォトダイオード 132 の周囲に入射する入射光を遮断する。換言すれば、受光基板 100 において、フォトダイオード 132 が形成された領域に限って入射光を入射させる。

【0037】

遮光層 170 は、例えばアルミニウム、タングステン等の金属材料を気相成長方により堆積させることにより形成できる。遮光層 170 の材料は、多層配線層 150 における配線材 154 と同じ材料であってもよい。ただし、遮光層 170 は、透過光を遮断できる厚さを有している。このように、フォトダイオード 132 に隣接して配することにより、遮光層 170 のパターン精度を向上させることができる。

【0038】

このように、積層基板 300 を用いた場合は、受光基板 100 において支持基板 110 があった側からフォトダイオード 132 に光を入射させる裏面照射型イメージセンサが製造される。よって、以降の製造過程には、支持基板 110 が除去された跡に、入射光を透過させる層を形成する段階が含まれる。

【0039】

次に、図 9 に示すように、絶縁層 120 および遮光層 170 の表面に平坦化層 172 を形成する。平坦化層 172 は、プラズマ CVD 等の物理蒸着法により堆積したシリコン酸化膜により形成できる。

【0040】

次に、図 10 に示すように、平坦化層 172 の表面に、有機平坦化層 174 を形成する。有機平坦化層 174 は、例えば、ポリイミド樹脂等を塗布することにより形成できる。これにより、受光基板 100 の入射側端面の平坦性を向上させると共に、次に説明する他の樹脂層の接着性を向上させる。

【0041】

なお、有機平坦化層 174 の耐熱温度は、他の層を形成する Si 化合物等に比較すると低い。よって、有機平坦化層 174 を形成した後の段階では、高温のアニール処理はできない。

【0042】

次に、図 11 に示すように、有機平坦化層 174 の表面に、オンチップカラーフィルタ 180 を形成する。オンチップカラーフィルタ 180 は、フォトダイオード 132 のそれぞれに対応して配される。また、オンチップカラーフィルタ 180 は、顔料を含むフォトレジスト材等により形成され、例えば赤、青および緑（原色系）またはシアン、マゼンタおよびイエロー（補色系）のいずれかに着色される。更に、オンチップカラーフィルタ 180 には、4 色以上のフィルタが組み合わされる場合もある。

【0043】

次に、図 12 に示すように、有機平坦化層 174 およびオンチップカラーフィルタ 180 の各表面を含む受光基板 100 の表面に、更に有機平坦化層 182 が形成される。これにより、オンチップカラーフィルタ 180 は、有機平坦化層 174、182 に埋設された状態になる。また、受光基板 100 の最表面は再び平坦化される。

【0044】

10

20

30

40

50

次に、図13に示すように、有機平坦化層182の表面に、オンチップレンズ190が形成される。オンチップレンズ190は、有機樹脂により形成したレンズ材料層をエッチバック、リフロー等により加工してレンズ形状とすることにより形成される。オンチップレンズ190の各々は、中心が縁よりも厚い凸型レンズをなし、広い面積に入射した入射光をフォトダイオード132に集光する。尚、遮光層170、平坦化層172、有機平坦化層174、182、オンチップカラーフィルタ180、オンチップレンズ190は、これらの全てが必須なわけではなく、用途に応じて全部または一部を作成すればよい。

#### 【0045】

こうして、図13に示した断面構造を有する積層半導体装置400が完成する。積層半導体装置400は、受光基板100において支持基板110があった側から入射光が入射する裏面照射型イメージセンサである。フォトダイオード132への入射光により発生した電荷は、電圧信号として処理回路211に受け渡され、更に、デジタル変換等の処理を経て、バンプ220から外部に出力される。

#### 【0046】

積層半導体装置400が形成された積層基板300は、ダイシングにより切り分けられて多数のダイとなる。こうして得られたダイのそれぞれは、受光基板100および処理基板200を積層して製造したことにより、高い歩留りと高い集積密度とを兼ね備える。

#### 【0047】

なお、図7に示した状態から後に、遮光層170、オンチップカラーフィルタ180およびオンチップレンズ190のように光学的な機能を有する要素を受光基板100の表面に形成する場合には、マスク等を受光基板100に対して位置合わせする。この場合、絶縁層120、平坦化層172、有機平坦化層174、182を通じて見えるフォトダイオード132を、位置合わせ指標として利用してもよい。また、絶縁層120に、予めアライメントマークを形成しておいてもよい。更に、受光基板100を赤外帯域の照明光により観察して、多層配線層150の構造物を位置合わせ指標として利用してもよい。

#### 【0048】

図14は、他の積層基板301の断面図である。積層基板301は、図2に示した処理基板200と同じ構造を有する一対の処理基板201、202を、接続パッド260どうしが接合されるように積層して形成される。処理基板201、202の接合に係る位置合わせ指標、位置合わせ方法および接合方法については、図3を参照して説明した通りである。これにより、処理基板201の処理回路212と処理基板202の処理回路213とが相互に接続され、一体的な回路を形成する。

#### 【0049】

次に、図15に示すように、積層基板301における一方の処理基板202の支持基板210を薄化処理し、支持基板210の表面に露出した貫通電極256の端面にバンプ220を形成する。薄化処理の方法とバンプ220の形成方法は、図4および図5を参照して説明した通りである。

#### 【0050】

次に、図16に示すように、図15に示した状態の積層基板301と、図5に示した状態の積層基板300とを接合して、積層基板302を形成する。積層基板301のバンプ220と積層基板302のバンプ220とは、銅バンプの相互拡散、はんだバンプの溶融等により接合できる。

#### 【0051】

こうして、積層基板300に含まれる受光回路111および処理回路211と、積層基板301における処理回路212、213とが、バンプ220および貫通電極256を通じて相互に結合される。これにより、積層基板302全体では、積層基板300の3倍に及ぶ大規模処理回路が形成される。

#### 【0052】

次に、図17に示すように、積層基板302の図中下端に位置する処理基板201の支持基板210を薄化処理し、支持基板210の表面に露出した貫通電極256の端面にバ

10

20

30

40

50

ンプ 220 を形成する。薄化処理の方法とバンプ 220 の形成方法は、図 4 および図 5 を参照して説明した場合と同様である。こうして、積層基板 302 に形成された大規模処理回路は、図中最下段の処理基板 201 のバンプ 220 を通じて外部に出力できる状態になる。

【0053】

次に、図 18 に示すように、薄化およびエッチングにより、積層基板 302 における受光基板 100 の支持基板 110 を除去する。支持基板 110 の薄化および除去は、図 6 および図 7 を参照して説明した通りである。

【0054】

続いて、図 19 に示すように、受光基板 100 において露出した絶縁層 120 の上に、

10

遮光層 170、平坦化層 172、有機平坦化層 174、182、オンチップカラーフィルタ 180 およびオンチップレンズ 190 を順次形成して、積層半導体装置 401 を完成する。これら光学要素の形成過程は、図 8 から図 13 までを参照して説明した通りである。

【0055】

こうして製造された積層半導体装置 401 は、処理回路 211、212、213 を含む大規模処理回路を備えるので、アナログ / デジタル変換器に加えて、バッファ回路、記憶回路、プロセッサ等を一体的に備えたイメージセンサとすることができます。また、処理基板 200、201、202 を積層する過程では、受光基板 100 の受光面が支持基板 110 に覆われた状態なので、処理基板 200、201、202 の支持基板 210 の薄化処理等により生じた塵芥が受光基板 100 の表面に残留してイメージセンサとしての性能に影響を与えることが防止される。

20

【0056】

なお、積層半導体装置 401 の製造過程においても、処理基板 201、202 の積層段階、積層基板 300, 301 の積層段階のそれぞれの前後にアニール処理をしてもよい。しかしながら、個々の積層基板 300、301 を積層する段階ではアニール処理なしに低温で接合し、全ての基板が積層された後に一括してアニール処理してもよい。これにより、初期に積層された基板が繰り返しアニール処理の熱にさらされることが防止される。

【0057】

図 20 は、更に他の積層基板 303 の断面図である。積層基板 303 は、図 5 に示した状態の積層基板 300 に、複数の処理基板 201 を 1 枚ずつ順次積層して形成される。即ち、支持基板 110 を残した状態の積層基板 300 に対して、支持基板 210 を薄化する前の処理基板 201 を接合し、支持基板 210 を薄化し、バンプ 220 を形成する段階を繰り返すことにより、多層の積層基板 303 を形成できる。

30

【0058】

上記のように、積層基板 303 の製造過程においては、処理基板 201 を 1 枚ずつ順次積層していくので、要求仕様に応じて任意の数の処理基板 201 を積層することができる。なお、図 14 から図 16 までに示したように予め作製した積層基板 301 を更に他の基板に積層する手順と、図 20 に示すように、処理基板 201 を一枚ずつ積層する手順とを混在させて、更に大規模な積層半導体装置を製造してもよい。

【0059】

また、この積層過程においては、受光基板 100 の受光面を支持基板 110 に覆った状態のまま、処理基板 201 の積層と薄化を繰り返すことができる。よって、処理基板 201 における支持基板 210 の薄化処理等により生じた塵芥が受光基板 100 の表面に残留してイメージセンサとしての性能に影響を与えることが防止される。

40

【0060】

これにより、研磨等の薄化処理で一時的に使用されるダミー基板を用いることなく、多層の積層半導体装置を製造できる。よって、積層半導体装置を製造する場合の工数を低減できると共に、破棄されるダミー基板の消費を抑制できる。

【0061】

なお、上記のような積層基板 303 を作製する場合も、個々の積層段階ではアニール処

10

20

30

40

50

理なしに低温で接合し、全ての基板が積層された後に一括してアニール処理してもよい。これにより、初期に積層された基板が繰り返しアニール処理の熱にさらされることが防止される。

#### 【0062】

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。上記実施の形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。その様な変更または改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

#### 【0063】

特許請求の範囲、明細書、および図面中において示した装置、システム、プログラム、および方法における動作、手順、ステップ、および段階等の各処理の実行順序は、特段「より前に」、「先立って」等と明示しておらず、また、前の処理の出力を後の処理で用いるのでない限り、任意の順序で実現しうることに留意すべきである。特許請求の範囲、明細書、および図面中の動作フローに関して、便宜上「まず、」、「次に、」等を用いて説明したとしても、この順で実施することが必須であることを意味するものではない。

#### 【符号の説明】

#### 【0064】

100 受光基板、110 支持基板、111 受光回路、120 絶縁層、130、230 半導体ウェル、132 フォトダイオード、140、240 ゲート電極、150、250 多層配線層、152、252 層間絶縁材、154、254 配線材、160、260 接続パッド、170 遮光層、172 平坦化層、174、182 有機平坦化層、180 オンチップカラーフィルタ、190 オンチップレンズ、200、201、202 処理基板、210 支持基板、211、212、213 処理回路、220 バンプ、256 貫通電極、300、301、302、303 積層基板、400、401 積層半導体装置

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(72)発明者 三ツ石 創

東京都千代田区有楽町一丁目12番1号 株式会社ニコン内

F ターム(参考) 4M118 AA10 AB01 BA14 BA19 CA02 EA01 EA14 EA20 FA06 GA02

GB03 GB07 GB11 GC08 GC09 GD04 GD07 HA22 HA25 HA30

HA31 HA33