### (19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第5655705号 (P5655705)

(45) 発行日 平成27年1月21日(2015.1.21)

(24) 登録日 平成26年12月5日(2014.12.5)

| (51) Int.Cl. | FI                            |                |                         |

|--------------|-------------------------------|----------------|-------------------------|

| HO1L 21/336  | ( <b>2006.01)</b> HO1L        | 29/78 6        | 58L                     |

| HO1L 29/78   | <b>(2006.01)</b> HO1L         | 29/78 6        | 52K                     |

| HO1L 21/66   | <b>(2006.01)</b> HO1L         | 29/78 6        | 52 N                    |

| HO1L 29/06   | <b>(2006.01)</b> HO1L         | 29/78 6        | 52Q                     |

|              | HO1L                          | 21/66          | E                       |

|              |                               |                | 請求項の数 4 (全 13 頁) 最終頁に続く |

| (21) 出願番号    | 特願2011-115652 (P2011-115652)  | (73) 特許権者      | f 000002130             |

| (22) 出願日     | 平成23年5月24日 (2011.5.24)        |                | 住友電気工業株式会社              |

| (65) 公開番号    | 特開2012-244102 (P2012-244102A) |                | 大阪府大阪市中央区北浜四丁目5番33号     |

| (43) 公開日     | 平成24年12月10日 (2012.12.10)      | (74) 代理人       | 100088155               |

| 審査請求日        | 平成25年12月23日 (2013.12.23)      |                | 弁理士 長谷川 芳樹              |

|              |                               | (74) 代理人       | 100113435               |

|              |                               |                | 弁理士 黒木 義樹               |

|              |                               | (74)代理人        | 100108257               |

|              |                               |                | 弁理士 近藤 伊知良              |

|              |                               | (72) 発明者       | 澤田 研一                   |

|              |                               |                | 大阪府大阪市此花区島屋一丁目1番3号      |

|              |                               |                | 住友電気工業株式会社大阪製作所内        |

|              |                               | <br>   審査官<br> | 平野 崇                    |

|              |                               |                | 最終頁に続く                  |

(54) 【発明の名称】半導体装置

# (57)【特許請求の範囲】

# 【請求項1】

FET構造を有する複数の単位セルを含む半導体装置において、

各前記単位セルの前記FET構造が有するゲート電極に電気的に接続されるゲート電極 配線と、

前記ゲート電極配線に電気的に接続されており各前記ゲート電極を外部接続するためのゲート電極パッドと、

前記ゲート電極配線に電気的に接続されており検査用プローブが接触されるプローブ用電極パッドと、

セル部と、

前記セル部を取り囲んでいると共に、前記セル部を電気的に保護する外周部と、を備え、

前記セル部は、複数の前記単位セルが並列に配置されて構成されており、

前記プローブ用電極パッドは、前記セル部の外縁部上に設けられていると共に、前記セル部から前記外周部に向けて張り出している、

半導体装置。

# 【請求項2】

前記ゲート電極配線は、前記セル部の外縁部に沿って配置されている、

# 請求項1に記載の半導体装置。

20

10

【請求項3】

前記セル部の平面視形状は略四角形状であり、

前記プローブ用電極パッドは、前記セル部の4つの角部のうちの少なくとも一つの角部 に設けられている。

請求項1又は2に記載の半導体装置。

### 【請求項4】

複数の前記プローブ用電極パッドを備える、請求項1~<u>3</u>の何れか一項記載の半導体装置。

#### 【発明の詳細な説明】

【技術分野】

[0001]

本発明は半導体装置に関する。

### 【背景技術】

[0002]

半導体装置として、FET構造(例えば、MOSFET構造)を有する複数の単位セルが並列されたセル部を含む半導体装置が知られている(特許文献1及び非特許文献1参照)。このような半導体装置では、各ゲート電極に導通したゲート電極パッドが設けられており、ゲート電極パッドを外部接続することによって、各単位セルのFET構造に含まれるゲート電極を外部接続している。

【先行技術文献】

【特許文献】

[0003]

【特許文献 1 】特開 2 0 0 6 - 1 0 0 3 1 7 号公報

【非特許文献】

[0004]

【非特許文献1】稲葉保著「パワーMOSFET活用の基礎と実際」CQ出版、2012 年2月1日、第22頁

【発明の概要】

【発明が解決しようとする課題】

[0005]

半導体装置が製造された際には半導体装置の検査が行われる。その検査では、検査用の プローブは、通常、ゲート電極パッドに接触させていた。この場合、検査用のプローブを ゲート電極パッドに接触させることによって、本来、外部接続のために使用されるべきゲ ート電極パッドに余分なストレスが付加されていた。

[0006]

そこで、本発明は、検査時におけるゲート電極パッドへのストレスを低減し得る半導体 装置を提供することを目的とする。

【課題を解決するための手段】

[0007]

本発明の一側面に係る半導体装置は、FET構造を有する複数の単位セルを含む。この 半導体装置は、各単位セルのFET構造が有するゲート電極に電気的に接続されるゲート 電極配線と、ゲート電極配線に電気的に接続されており各ゲート電極を外部接続するため のゲート電極パッドと、ゲート電極配線に電気的に接続されており検査用プローブが接触 されるプローブ用電極パッドと、を備える。

[00008]

この形態では、プローブ用電極パッドが、ゲート電極配線を介して各単位セルのゲート電極及びゲート電極パッドに接続されている。よって、ゲート電極パッドの代わりに検査用プローブを接触させることによって、半導体装置を検査し得る。そのため、半導体装置の検査において、ゲート電極パッドへのストレスを低減し得る。

[0009]

10

20

30

50

一実施形態に係る半導体装置は、セル部と、セル部を取り囲んでいると共に、セル部を 電気的に保護する外周部とを備え得る。この形態において、セル部は、複数の単位セルが 並列に配置されて構成され得る。また、プローブ用電極パッドは、セル部の外縁部上に設 けられていると共に、セル部から外周部に向けて張り出し得る。

### [0010]

セル部は、FFET構造を有する複数の単位セルが並列に配置されて構成されているた め、半導体装置において動作領域として機能する。上記形態では、プローブ用電極パッド をゲート電極パッドと別に備えても、動作領域であるセル部の面積(又は大きさ)を確保 することが可能である。

# [0011]

- 実施形形態では、セル部の平面視形状は略四角形状であり得る。この形態では、ゲー ト電極配線がセル部の外縁部に沿って配置され得る。また、プローブ用電極パッドは、セ ル部の外縁部を構成する4つの角部のうちの少なくとも一つの角部の位置に設けられ得る

### [0012]

セル部の平面視形状が略四角形状であり、セル部の外縁部に沿ってゲート電極配線が配 置されている形態では、セル部の角部には電界が集中しやすい。この場合、セル部を取り 囲んでいる外周部の幅はより大きくなる傾向にある。よって、セル部の角部にプローブ用 電極パッドを配置した形態では、外周部の領域を有効に活用できると共に、プローブ用電 極パッドの大きさをより大きくできる。

### [0013]

更に、一実施形態において、プローブ用電極パッドの表面の面積は、検査用プローブの 断面であって検査用プローブの軸に直交する断面の面積より大きい。

#### [0014]

この形態では、検査用プローブをプローブ用電極パッドに接触させる際、検査用プロー ブが、半導体装置におけるプローブ用電極パッド以外の領域に接触しにくい。その結果、 プローブ用電極パッドを利用して半導体装置をより正確に検査し得る。

#### [0015]

一実施形態において、半導体装置は、複数のプローブ用電極パッドを備え得る。この場 合、ゲート電極パッドを利用せずに、複数のプローブ用電極パッドに複数の検査用プロー ブを接触させながら、例えば四端子法を用いて半導体装置を検査し得る。

# 【発明の効果】

#### [0016]

本発明によれば、検査時におけるゲート電極パッドへのストレスを低減し得る半導体装 置を提供し得る。

## 【図面の簡単な説明】

# [0017]

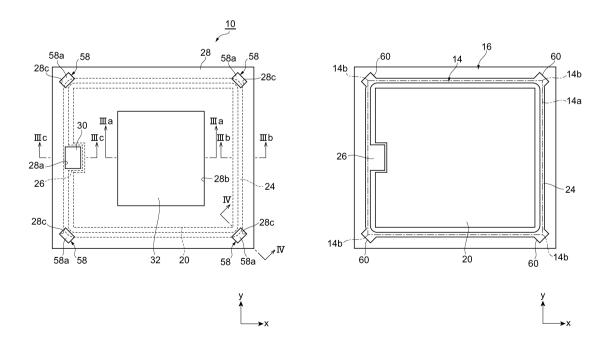

- 【図1】本発明の一実施形態に係る半導体装置の平面図である。

- 【図2】図1に示した半導体装置の表面に設けられるパッシベーション膜を除いた場合の 平面図である。

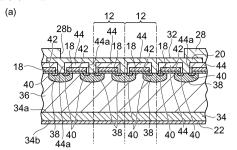

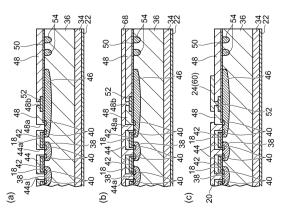

【図3】図1に示したIIIa-IIIa線、IIIb-IIIb線及びIIIc-II Ic線に沿った端面構造を示す図面である。

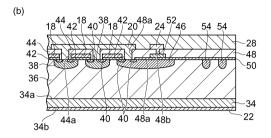

- 【図4】図1に示したVI-VI線に沿った端面構造を示す図面である。

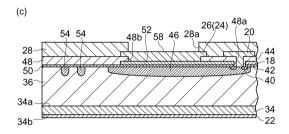

- 【図5】図1に示した半導体装置の製造工程の一例を順次示す図面である。

- 【図6】図5に示した工程の後工程を順次示す図面である。

# 【発明を実施するための形態】

### [0018]

以下、図面を参照して本発明の実施形態について説明する。図面の説明において、同一 要素には同一符号を付し、重複する説明を省略する。図面の寸法比率は、説明のものと必 ずしも一致していない。

10

20

30

40

#### [0019]

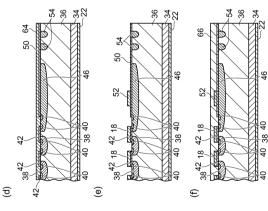

図1は、本発明の一実施形態に係る半導体装置の平面図である。図2は、図1に示した 半導体装置の表面側に設けられるパッシベーション膜を除いた場合の半導体装置の平面図 である。図3(a)、図3(b)及び図3(c)は、それぞれ図1のIIIa IIIIa 線、IIIb IIIb線及びIIIc-IIIc線に沿った端面図である。

### [0020]

図1~図3を利用して半導体装置10の概略構成について説明する。説明のために、図1及び図2に示すように、半導体装置10の厚さ方向(後述する半導体基板34の主面34aの法線方向)に略直交する2つの方向を×軸方向及び×軸方向と称す。

## [0021]

半導体装置10は、化合物半導体を利用したMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)である。半導体装置10に採用される化合物半導体の例は、SiC及びGaNといったワイドバンドギャップ半導体、GaAsを含む。半導体装置10は平面視形状(半導体装置10の厚さ方向から見た形状)の例は、図1に示されているような略四角形状である。略四角形状の例は、正方形及び長方形を含む。半導体装置10の平面視形状が略正方形である場合において、半導体装置10の一辺の長さの例は5mm以下である。

# [0022]

半導体装置 1 0 は、複数の単位セル 1 2 (図 3 (a)参照)が並列に配置されて構成されるセル部 1 4 を備えた半導体チップである。半導体装置 1 0 は、セル部 1 4 を取り囲んでおりセル部 1 4 を電気的に保護する外周部 1 6 (図 2 参照)を備え得る。本実施形態では、外周部 1 6 を備えた半導体装置 1 0 が説明される。

# [0023]

セル部14の平面視形状は、半導体装置10の平面視形状と同様の形状であり得る。本実施形態では、図2に例示したように、セル部14の平面視形状は略正方形として説明される。セル部14の一辺の長さの例は20μm以下である。

### [0024]

各単位セル12は縦型のMOSFET構造を有する。図3(a)に示すように、隣接する単位セル12は物理的に連続して並列配置されている。この形態では、セル部14はチャネル領域に主電流が流れる活性部である。一実施形態において、セル部14は、平面視形状が角状の複数の単位セル12がアレイ状に並列接続されて構成され得る。他の実施形態において、単位セル12は、一方向に延在したストライプ形状を有し得る。この場合には、セル部14は、各単位セル12が単位セル12の延在方向に直交する方向に複数の単位セル12が並列接続された構成とし得る。

# [0025]

単位セル12は、ゲート電極18を基準にして区画されている。半導体装置10では、複数の単位セル12間において、ソース電極20及びドレイン電極22が共有されている。具体的には、半導体装置10の表面側及び裏面側にそれぞれ設けられたソース電極20及びドレイン電極22の一部が各単位セル12におけるソース電極及びドレイン電極として機能する。ただし、単位セル12毎に、ソース電極20及びドレイン電極22がそれぞれ設けられてもよい。

#### [0026]

セル部14の表面には、ゲート電極配線24がセル部14の外縁部14a(図2において一点鎖線で示される縁部)に沿って設けられている。よって、ゲート電極配線24は、環状に配置されている。本実施形態ではセル部14の平面視形状は略正方形であるため、ゲート電極配線24の平面視形状も略正方形である。半導体装置10が有するゲート電極配線24は、各単位セル12のゲート電極18に電気的に接続されている。ゲート電極配線24は、いわゆるゲートランナーである。ゲート電極配線24の一部には、第1のパッド用電極26(図2、図3(c)参照)が物理的に接続されている。ゲート電極配線24及び第1のパッド用電極26はいずれも導電性を有することから、ゲート電極配線24及

10

20

30

40

び第1のパッド用電極26は電気的にも接続されている。

# [0027]

セル部14及び外周部16の表面上には、ソース電極20及ゲート電極配線24を覆う保護膜としてのパッシベーション膜28(図1、図3(a)~図3(c)参照)が形成されている。このパッシベーション膜28によりセル部14及び外周部16の表面が保護される。半導体装置10では、第1のパッド用電極26及びソース電極20上のパッシベーション膜28に開口部28a及び開口部28bがそれぞれ形成されている。開口部28aによって露出した第1のパッド用電極26の領域がゲート電極パッド30として機能する。同様に、ソース電極20のうち開口部28bによって露出された領域がソース電極パッド32として機能する。

[0028]

図3(a)~図3(c)を利用して、半導体装置10の構成について更に詳細に説明する。まず、セル部14及び外周部16に共通の構成について説明する。

### [0029]

[0030]

次に、半導体基板34上のセル部14及び外周部16それぞれの構成について説明する。まず、セル部14について、図3(a)を主に利用してソース電極20の下側の構成を中心にして説明する。セル部14の外縁部14a近傍の構成については後述する。

#### [0031]

[0032]

p 型半導体領域 3 8 には、 2 つの n 型のソース領域 4 0 が離間して形成されている。ソース領域 4 0 内の n 型のドーパントの濃度の例は約  $1 \times 10^{-19}$  c m  $^{-3}$  である。ソース領域 4 0 の厚み (又は深さ)の例は約 0 . 3 μ m である。

[0033]

ドリフト層 36 の表面において隣接する p 型半導体領域 38 , 38 の間の領域上には、ゲート絶縁膜 42 及びゲート電極 18 が積層されている。ゲート絶縁膜 42 及びゲート電極 18 は、p 型半導体領域 38 内のソース領域 40 と共に M 05 構造を形成するように隣接する p 型半導体領域 38 , 38 の間の領域上に配置されている。本実施形態では、ゲート絶縁膜 42 及びゲート電極 18 は、単位セル 12 毎に設けられ得る。ゲート絶縁膜 42 の例はシリコン酸化膜である。ゲート絶縁膜 42 の厚さの例は約 50  $\mu$  mである。ゲート電極 18 の例は 41 膜といった金属膜である。

### [0034]

ゲート絶縁膜42及びゲート電極18からなる隆起部は、層間絶縁膜44によって被覆されている。層間絶縁膜44の例はシリコン酸化膜である。層間絶縁膜44上には、ソー

10

20

30

40

10

20

30

40

50

ス電極 2 0 が設けられている。ソース電極 2 0 の例はN 1 膜といった金属膜である。ソース電極 2 0 の厚さの例は約 0 . 1  $\mu$  mである。ソース領域 4 0 とソース電極 2 0 とが電気的に接触するように層間絶縁膜 4 4 には、層間絶縁膜 4 4 の厚さ方向に貫通するコンタクトホールといったコンタクト領域 4 4 a が形成されている。

## [0035]

上記構成では、単位セル12は、縦型MOSFET構造であって二重拡散型MOSFET構造を有する。具体的には、単位セル12は、ゲート電極18を基準としてみた場合、半導体基板34、裏面34bに設けられたドレイン電極22、主面34a上に設けられたドリフト層36、ドリフト層36の表層部に形成されており互いに離間したp型半導体領域38、各p型半導体領域38内に形成されたソース領域40、ソース領域40とMOS構造を形成するゲート絶縁膜42及びゲート電極18、並びに、ソース領域40と電気的に接続されゲート電極18と絶縁されたソース電極20とを含む。

### [0036]

次に、図3(b)及び図3(c)を主に利用して、ゲート電極配線24が形成されるセル部14の外縁部14aの構成について説明する。

#### [0037]

セル部14の外縁部14aに沿ってpボディ領域としてのp型半導体領域38がドリフト層36の表層部に形成されている。以下、説明の便宜のため、外縁部14aに沿って形成されるp型半導体領域38をp型半導体領域46とも称す。一実施形態において、p型半導体領域46は、半導体装置10の耐圧特性を得るために、セル部14から外周部16側に向けてセル部14から外側に張り出している。p型半導体領域46のセル部14中心側の端部には、単位セル12の一部を構成するソース領域40と、後述する絶縁膜50及びゲート配線部材52と共にMOS構造を構成するソース領域40とが互いに離間して形成されている。

#### [0038]

p型半導体領域 4 6 上には層間絶縁膜 4 8 によって被覆された絶縁膜 5 0 が設けられている。絶縁膜 5 0 及び層間絶縁膜 4 8 の材料及び厚さは、それぞれゲート絶縁膜 4 2 及び層間絶縁膜 4 4 の場合と同じとし得る。層間絶縁膜 4 8 のセル部 1 4 の中心側の端部上には、ソース電極 2 0 の一部が被さっている。層間絶縁膜 4 8 には、 p型半導体領域 4 6 内のソース領域 4 0 とソース電極 2 0 とを電気的に接続するために、層間絶縁膜 4 8 を貫通するコンタクト領域 4 8 a が形成されている。

# [0039]

層間絶縁膜48内には、セル部14の外縁部14aに沿って設けられた導電性のゲート配線部材52が埋設されている。ゲート配線部材52の厚さ及び材料は、ゲート電極18の場合と同様とし得る。ゲート配線部材52は、各ゲート電極18と電気的に接続されている。ゲート配線部材52と各ゲート電極18との電気的な接続の例について説明する。外縁部14aに沿って配置されたゲート配線部材52を主たるゲート配線部材(又は基幹ゲート配線部材)とする。この際、主たるゲート配線部材52から従たるゲート配線部材を導出して、この従たるゲート配線部材を各ゲート電極18と物理的に接続されるようにセル部14内に張り巡らせる。これにより、ゲート配線部材52と各ゲート電極18とが電気的に接続され得る。この場合、従たるゲート配線部材52と各ゲート電極20及びソース領域40とは絶縁されるように絶縁膜などによって被覆又は埋設されていればよい。或いは、単位セル12が一方向に延在している形態では、ゲート電極18の両端を直接ゲート配線部材52に物理的に接続してもよい。

#### [0040]

ゲート配線部材52の延びている方向、すなわち、外縁部14aに沿って層間絶縁膜48上にゲート電極配線24が設けられている。層間絶縁膜48には、ゲート電極配線24上に層間絶縁膜48を貫通するコンタクト領域48bが形成されている。コンタクト領域48bを介してゲート電極配線24は、ゲート配線部材52と電気的に接続される。その結果、ゲート電極配線24は、各単位セル12のゲート電極18と電気的に接続される。

ゲート電極配線24の例はソース電極20の例と同じとし得る。

#### [0041]

ゲート電極配線 2 4 の一部、例えば、図 1 に示すように、略四角形状に配設されたゲート電極配線 2 4 のうち y 軸方向に延在している領域の一部には、図 3 ( c ) に示すように、第 1 のパッド用電極 2 6 が設けられている。ゲート電極配線 2 4 の一部をセル部 1 4 の中心側に向けて幅広に形成することによって第 1 のパッド用電極 2 6 を形成し得る。第 1 のパッド用電極 2 6 の下側においては、 p 型半導体領域 4 6 及びゲート配線部材 5 2 もセル部 1 4 の中心側に張り出している。

### [0042]

図3(b)及び図3(c)を更に利用して、外周部16の構成について説明する。外周部16では、ドリフト層36上に、絶縁膜50及び層間絶縁膜48が順に積層されている。ここでは、外周部16は、絶縁膜50及び層間絶縁膜48を含んでいるとしたが、外周部16は、ドリフト層36を備えていればよい。セル部14と共通のドリフト層36を備えいことで、逆バイアス時の空乏層がより広がりやすく、耐圧特性を得ることができる。この場合、外周部16は、耐圧特性を確保するための外周耐圧部として機能する。

#### [0043]

外周部16のセル部14側の領域には、前述したように、 p型半導体領域46が張り出され得る。このように張り出された p型半導体領域46によって逆バイアス時の空乏層が更に均等に広がり易い。そのため、半導体装置10における耐圧特性をより確保可能である。また、耐圧特性を更に確保するために、外周部16が有するドリフト層36には、トレンチ状の p型半導体領域54が設けられていてもよい。 p型半導体領域54のp型ドーパントの濃度及び厚さは、p型半導体領域38の場合と同様とし得る。

#### [0044]

図3(a)~図3(c)に示すように、セル部14及び外周部16の表面は、パッシベーション膜28で覆われている。第1のパッド用電極26上のパッシベーション膜28に開口部28aが形成されている。開口部28aによって第1のパッド用電極26の露出した領域がゲート電極パッド30である。ソース電極20上のパッシベーション膜28にも開口部28bが形成されている。開口部28bによって、ソース電極20の露出した領域がソース電極パッド32である。パッシベーション膜28の例はSiN膜である。パッシベーション膜28の厚さの例は、10μmである。

### [0045]

上記構成の半導体装置10では、ゲート電極パッド30、ソース電極パッド32及びドレイン電極22を、半導体装置10とは別の素子(又は回路)に外部接続することによって、セル部14を構成する各単位セル12が外部の素子(又は回路)に電気的に接続され得る。

# [0046]

半導体装置10は、図1に示すように、上記ゲート電極パッド30及びソース電極パッド32に加えて、半導体装置10の検査時に、検査用プローブ56(図4参照)を接触させるためのプローブ用電極パッド58を備える。一実施形態において、図1及び図2に示されているように、半導体装置10は、略四角形状のセル部14の角部14bに一ブ用電極パッド58を有し得る。図1では、セル部14の4つの角部14bにプローブ用電極パッド58が配置された構成を例示している。プローブ用電極パッド58は、図1に示すように、セル部14から外周部16に向けて張り出し得る。

# [0047]

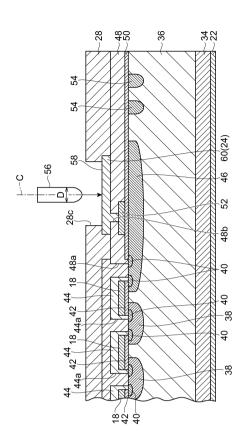

図4を利用してプローブ用電極パッド58の形成位置における半導体装置10の構成について更に説明する。図4は、図1のIV IV線に沿った端面構成を模式的に示す端面図である。

### [0048]

層間絶縁膜48上において、ゲート電極配線24の角部に、ゲート電極配線24に電気的に接続された第2のパッド用電極60が設けられている。第1のパッド用電極26と同

10

20

30

40

10

20

30

40

50

様に、略四角形状に配設されたゲート電極配線24の角部及びその近傍の領域が幅広に形成されることによって、第2のパッド用電極60を形成し得る。パッシベーション膜28は、第2のパッド用電極60上に、開口部28cを更に有する。第2のパッド用電極60のうち開口部28cによって露出した領域がプローブ用電極パッド58である。

### [0049]

プローブ用電極パッド58の平面視形状の例は、略四角形、略扇形状及び円状である。略四角形の例は、略長方形及び略正方形を含む。プローブ用電極パッド58の大きさは、検査用プローブ56がプローブ用電極パッド58に接触される場合に、検査用プローブ56が開口部28cの周壁に接触しない大きさであり得る。検査用プローブ56が開口部28cの周壁に接触しないために、プローブ用電極パッド58の表面58aの面積又は開口部28cの面積は、検査用プローブ56の断面積であってプローブ56の軸Cに直交する断面の面積より大きい。換言すれば、プローブ用電極パッド58の面積は、検査用プローブ56の径Dに基づいて規定される検査用プローブ56の断面積より大きい。

### [0050]

径 D は、プローブ 5 6 の先端部と反対側の端部における径である。しかしながら、プローブ 5 6 の先端部の形状が図 4 に示すように先細りしたテーパ形状或いは湾曲形状である場合、径 D は、パッシベーション膜 2 8 の厚さ分、プローブ 5 6 の先端部からプローブ 5 6 の他端側に寄った位置での径であればよい。

#### [0051]

検査用プローブ 5 6 が開口部 2 8 c の周壁に接触しないために、一実施形態において、プローブ用電極パッド 5 8 を規定する各辺の長さは、プローブ 5 6 の径 D の 1 . 1 倍以上であり得る。プローブ用電極パッド 5 8 を規定する各辺の長さが上記範囲であれば、プローブ 5 6 と開口部 2 8 c の周壁との間に、一定の余白(マージン)が得られるので、プローブ 5 6 が開口部 2 8 c により接触しにくい。具体的には、図 1 に示すように、プローブ 用電極パッド 5 8 の形状が略長方形であり、径 D が 0 . 0 2 7 m m である場合、プローブ 用電極パッド 5 8 の短辺(図 1 の I I I c · I I I c 線に沿った方向の長さ)は 0 . 0 3 m m 以上とし得る。開口部 2 8 c がプローブ用電極パッド 5 8 の形状が円形である場合には、開口部 2 8 c の直径が上記範囲を満たせばよい。プローブ用電極パッド 5 8 の長さの上限は外周部 1 6 の大きさに応じて決めればよいが、例えば径 D の 1 . 5 倍以下である。

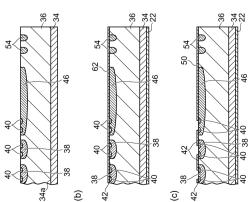

プローブ用電極パッド58を含む半導体装置10の製造方法の一例を、図5(a)~図5(f)及び図6(a)~図6(e)を利用して説明する。以下では、プローブ用電極パッド58の形成工程を具体的に示しながら半導体装置10の製造方法を説明する。図5(a)~図5(f)及び図6(a)~図6(e)は、半導体装置10の製造工程を順次示す図面である。図5(a)~図5(f)及び図6(a)~図6(e)では、プローブ用電極パッド58が形成される領域近傍の半導体装置10の製造工程が主に示されている。

# [0053]

[0052]

図5(a)に示すように、n型のSiC基板からなる半導体基板34の主面34a上にドリフト層36を形成した後、ドリフト層36の表層部にp型半導体領域38,46及びソース領域40をそれぞれ形成する。p型半導体領域54を形成する場合には、p型半導体領域38等と一緒にp型半導体領域54を形成する。以下では、p型半導体領域54を備えた形態が説明される。具体的には、主面34a上に、in-situドープを伴うCVDエピタキシャル成長法を用いてドリフト層36を形成する。このようにエキタキシャル成長法を利用してドリフト層36が形成される場合、ドリフト層36はエキタキシャル成長である。ドリフト層36の所定位置にRIE(Reactive Ion Etching)(反応性イオンエッチング)などにより、p型半導体領域38,46,54となる凹部を形成した後、各凹部の底面及び側面の上に、in-situドープを伴うCVDエピタキシャル成長法によってp型半導体領域38,46,54をエピタキシャル成長させる。この場合、p型半導体領域は埋込選択成長領域である。p型半導体領域38,46に、注入マスクを用いたイオン注入を実施することによって、複数のソース領域40を形成する。

#### [0054]

次いで、図5(b)に示すように、ドリフト層36上に、例えばCVD法を用いて絶縁膜としてのシリコン酸化膜62を成膜する。その後、蒸着法又はスパッタ法などによって、裏面34b上にNi膜からなるドレイン電極22を形成する。

## [0055]

次に、図5(c)に示すように、シリコン酸化膜62をパターニングすることによって、ゲート絶縁膜42及び絶縁膜50をそれぞれ形成する。続いて、図5(d)に示すように、半導体基板34上に、例えばCVD法などによってA1膜64を形成する。そのA1膜64をパターニングすることによって、図5(e)に示すように、ゲート電極18及びゲート配線部材52を形成する。第1のパッド用電極26の直下に位置する領域においては、図3(c)に示したように、ゲート配線部材52を、セル部14の内側に向けて幅広に形成する。その後、図5(f)に示すように、半導体基板34上に更に、例えばCVD法を用いてシリコン酸化膜66を成膜することによって、ゲート電極18及びゲート配線部材52を埋設する。

### [0056]

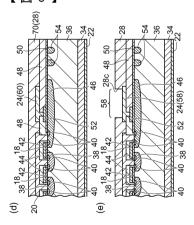

続いて、図6(a)に示すように、ソース領域40とソース電極20との電気的接触及びゲート配線部材52とゲート電極配線24との電気的接触を確保するために、シリコン酸化膜66にコンタクト領域44a,48a,48bを形成する。コンタクト領域44a,48a,48bは、エッチングなどを利用して形成され得る。

# [0057]

図6(b)に示すように、コンタクト領域44a,48a,48bが形成された絶縁膜66を有する半導体基板34上に、例えばCVD法によってNi膜68を成膜する。そのNi膜68をパターニングすることによって、図6(c)に示すように、ソース電極20及びゲート電極配線24を形成する。この際、セル部14の角部14b上において、ゲート電極配線24を外周部16側に拡大して形成することによって、第2のパッド用電極60を得る。ここで、半導体基板34を、熱処理することによって、ソース電極41及びドレイン電極22を構成するNiと、ソース領域40及び半導体基板34を構成するSiCとの接触をショットキー接触からオーミック接触に変化させる。

## [0058]

図6(d)に示すように、ソース電極20が形成された半導体基板34上にSiN膜70を例えばCVD法などにより形成する。このSiN膜70がパッシベーション膜28である。このパッシベーション膜28に、エッチング等を利用して開口部28cを形成することによって、図6(e)に示すように、プローブ用電極パッド58を形成する。この際、パッシベーション膜28に開口部28a,28bを形成することによって、ゲート電極パッド30及びソース電極パッド32を形成する。

### [0059]

ここでは、半導体基板 3 4、ゲート電極 1 8、ソース電極 2 0 及びドレイン電極 2 2 などの材料及び各膜の形成方法などを一部例示しながら説明したが、半導体装置 1 0 を構成する各構成要素の材料及び各膜の形成方法などは例示したものに限定されない。

# [0060]

以上説明した半導体装置10は、ゲート電極パッド30とは別に、半導体装置10の検査のためのプローブ用電極パッド58を有する。プローブ用電極パッド58はゲート電極配線24を介してゲート電極18及びゲート電極パッド30に電気的に接続されている。そのため、ゲート電極パッド30ではなく、プローブ用電極パッド58に検査用プローブ56を接触させることによって、半導体装置10を検査することができる。

# [0061]

このように、プローブ用電極パッド58を利用して半導体装置10を検査することにより、ゲート電極パッド30を検査用プローブによる検査のためではなく、ワイヤボンディングなどを利用した外部接続のために使用することができる。その結果、検査時においてゲート電極パッド30に余分なストレスが付加されることがなく、外部接続時にゲート電

10

20

30

40

10

20

30

40

50

極パッド30を最適な状態で使用し得る。また、半導体装置10の検査時にゲート電極パッド30にストレスがかからないので、ゲート電極パッド30をより小さく形成し得る。そのため、半導体装置10の電流定格を上げることができる。

#### [0062]

また、検査時におけるゲート電極パッド30へのストレスを考慮する必要がないので、ストレスの影響を低下するために、ゲート電極パッド30やゲート電極18の厚さをより厚く形成する必要がない。その結果、ゲート電極パッド30をより厚くしてストレスの影響の低下を図る場合よりも、半導体装置10の製造時間を短縮することも可能である。

### [0063]

図1に例示したように、耐圧特性を確保するため、半導体装置10がセル部14を囲繞する外周部16を備えている形態では、プローブ用電極パッド58は、セル部14の外縁部14a上に配置されると共に、外周部16側に張り出すように設けられ得る。この場合、ゲート電極パッド30とは別にプローブ用電極パッド58を備えたとしても、半導体装置10の主動作領域である活性部としてのセル部14の面積を維持できる。結果として、半導体装置10としての動作性能を確保し得る。また、耐圧特性の確保のために備える外周部16の領域を利用しているため、プローブ用電極パッド58をセル部14側から外側に張り出して形成するための領域を別途確保する必要がない。近年、半導体チップといった半導体装置10はチップサイズの小型化が望まれていると共に、化合物半導体を採用した場合には、結晶欠陥などの関係から大型化が困難である。そのため、図1に示したように、外周部16を備え、外周部16側にプローブ用電極パッド58を張り出した形態は、半導体装置10の小型化(例えば、チップの一辺が5mm以下といったチップサイズ)に資する構成であると共に、化合物半導体を採用した場合により有効な構成である。

#### [0064]

# [0065]

また、図1に示したように、半導体装置10が2つ以上(図1では4個)のプローブ用電極パッド58を備えている形態では、半導体装置10の検査方法として四端子法を採用した場合であっても、ゲート電極パッド30を使用せずに、2つのプローブ用電極パッド58を利用して半導体装置10を検査可能である。よって、検査時に、ゲート電極パッド30にストレスをかけずに、半導体装置10をより精度よく検査し得る。

#### [0066]

以上、本発明の実施形態について説明したが、本発明は上記実施形態に限定されずに、本発明の趣旨を逸脱しない範囲で種々変形が可能である。例えば、半導体装置10の単位セル12は、FET構造を有してればよい。よって、単位セルは、MOSFET構造は縦型のMOSFET構造に限らず、横型のMOSFET構造であってもよい。更に、単位セル12は、JFET(接合型電界効果トランジスタ)であもよい。単位セル12が有するFET構造は、nチャネル型のものに限らず、pチャネル型であり得る。更に、プローブ用電極パッド58は、半導体装置10においてゲート電極パッド18とは別に設けられており、ゲート電極配線24に電気的に接続されていればよい。例えば、プローブ用電極パ

ッド 5 8 は、セル部 1 4 の角部 1 4 b とは異なる位置に設けられていてもよい。更に、プローブ用電極パッド 5 8 の個数は 1 個 ~ 3 個でもよく、 5 個以上でもよい。

# 【符号の説明】

# [0067]

10…半導体装置、12…単位セル、14…セル部、14a…外縁部、14b…角部、16…外周部、18…ゲート電極、24…ゲート電極配線、30…ゲート電極パッド、56…検査用プローブ、58…プローブ用電極パッド。

# 【図1】 【図2】

【図3】

【図4】

【図5】

<u>a</u>

【図6】

# フロントページの続き

(51) Int.CI. F I

H 0 1 L 29/78 6 5 2 P

(56)参考文献 特開平08-162537(JP,A)

特開平11-177087(JP,A)

特開2006-184136(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/336

H01L 21/66

H01L 29/06

H01L 29/78