【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】令和2年11月5日(2020.11.5)

【公開番号】特開2020-31088(P2020-31088A)

【公開日】令和2年2月27日(2020.2.27)

【年通号数】公開・登録公報2020-008

【出願番号】特願2018-154251(P2018-154251)

【国際特許分類】

H 01 L 29/78 (2006.01)

H 01 L 29/06 (2006.01)

H 01 L 21/336 (2006.01)

【F I】

H 01 L 29/78 6 5 2 H

H 01 L 29/06 3 0 1 D

H 01 L 29/06 3 0 1 V

H 01 L 29/78 6 5 2 B

H 01 L 29/78 6 5 2 F

H 01 L 29/78 6 5 3 C

H 01 L 29/78 6 5 2 J

H 01 L 29/78 6 5 2 C

H 01 L 29/78 6 5 8 A

【手続補正書】

【提出日】令和2年9月16日(2020.9.16)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

第1導電形の第1半導体層と、第2導電形の第2半導体層と、を含む半導体部と、前記半導体部の表面上に設けられた第1電極と、前記半導体部の裏表面上に設けられた第2電極と、前記半導体部と前記第1電極との間に設けられ、前記半導体部の表面に第1絶縁膜を介して向き合い、前記第1電極から第2絶縁膜により電気的に絶縁された制御電極と、を備え、

前記第2半導体層は、前記半導体部の表面に沿った第1方向において前記第1半導体層の一部と前記第1半導体層の別の一部との間に位置し、

前記半導体部は、前記第1半導体層および前記第2半導体層に接する第2導電形の第3半導体層と、前記第3半導体層中に選択的に設けられた第1導電形の第4半導体層と、をさらに含み、前記半導体部の表面は、前記第3半導体層の表面および前記第4半導体層の表面を含み、

前記第3半導体層は、前記第1半導体層の前記一部中に位置する第1端部と、前記第2半導体層中に位置する第2端部と、を有し、

前記第4半導体層は、前記第3半導体層の前記第2端部に設けられ、

前記第1電極は、前記第3半導体層および前記第4半導体層に電気的に接続され、

前記制御電極は、前記第4半導体層と第1半導体層の前記別の一部との間に位置する前記第3半導体層の一部および前記第2半導体層の一部、および、前記第1半導体層の前記

別の一部に向き合う半導体装置。

【請求項 2】

前記第1電極と前記第3半導体層の前記第1端部との間には、前記第4半導体層は設けられない請求項1記載の半導体装置。

【請求項 3】

前記第1半導体層および前記第2半導体層は、前記第1方向と交差し、前記半導体部の前記表面に沿った第2方向、および、前記半導体部の前記表面と交差する第3方向に延びる請求項1または2に記載の半導体装置。

【請求項 4】

前記第3半導体層、前記第4半導体層および前記制御電極は、前記第2方向に延びる請求項3記載の半導体装置。

【請求項 5】

前記半導体部は、第2導電形の第5半導体層と、第1導電形の第6半導体層と、をさらに含み、前記第5半導体層は、前記第1半導体層の前記別の一部および前記第2半導体層に接し、前記第6半導体層は、前記第5半導体層中に選択的に設けられ、

前記第1電極は、前記第5半導体層および前記第6半導体層に電気的に接続され、前記半導体部は、前記第2方向に交互に配置された第1領域と第2領域とを含み、

前記第1領域は、前記第3半導体層と前記第4半導体層とを含み、

前記第2領域は、前記第5半導体層と、前記第6半導体層と、を含み、

前記半導体部の前記表面は、前記第5半導体層の表面および前記第6半導体層の表面を含み、

前記第5半導体層は、前記第1半導体層の前記別の一部中に位置する第3端部と、前記第2半導体層中に位置する第4端部と、を有し、

前記第6半導体層は、前記第5半導体層の第4端部に設けられた請求項3記載の半導体装置。

【請求項 6】

第1導電形の第1半導体層を含む半導体部と、

前記半導体部の表面上に設けられた第1電極と、

前記半導体部の裏面上に設けられた第2電極と、

前記半導体部と前記第1電極との間に位置し、前記半導体部中に絶縁膜を介して設けられた制御電極と、

を備え、

前記半導体部は、前記第1半導体層と前記第1電極との間に設けられた第2導電形の第2半導体層と、前記第2半導体層と前記第1電極との間に選択的に設けられた第1導電形の第3半導体層と、前記第1半導体層と前記制御電極との間に選択的に設けられ、前記第2半導体層につながった第2導電形の第4半導体層と、をさらに含み、

前記制御電極は、前記半導体層の表面に沿った第1方向と交差する第1面と、前記第1方向において前記第1面と対向する第2面と、を有し、

前記第4半導体層は、前記第2面側において前記絶縁膜に沿って延在し、前記第2面側において前記絶縁膜に接し、前記絶縁膜上において前記第2半導体層に接続され、

前記制御電極の前記第1面は、前記絶縁膜を介して前記第1半導体層、前記第2半導体層および前記第3半導体層に向き合い、

前記制御電極の前記第2面は、前記絶縁膜を介して前記第2半導体層および前記第4半導体層に向き合う半導体装置。

【請求項 7】

前記半導体部は、複数の前記第1半導体層と、前記第1方向において前記複数の第1半導体層と交互に配置された第2導電形の複数の第5半導体層と、をさらに含み、

前記第2半導体層は、前記第5半導体層と前記第1電極との間に位置する請求項6記載の半導体装置。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0005

【補正方法】変更

【補正の内容】

【0005】

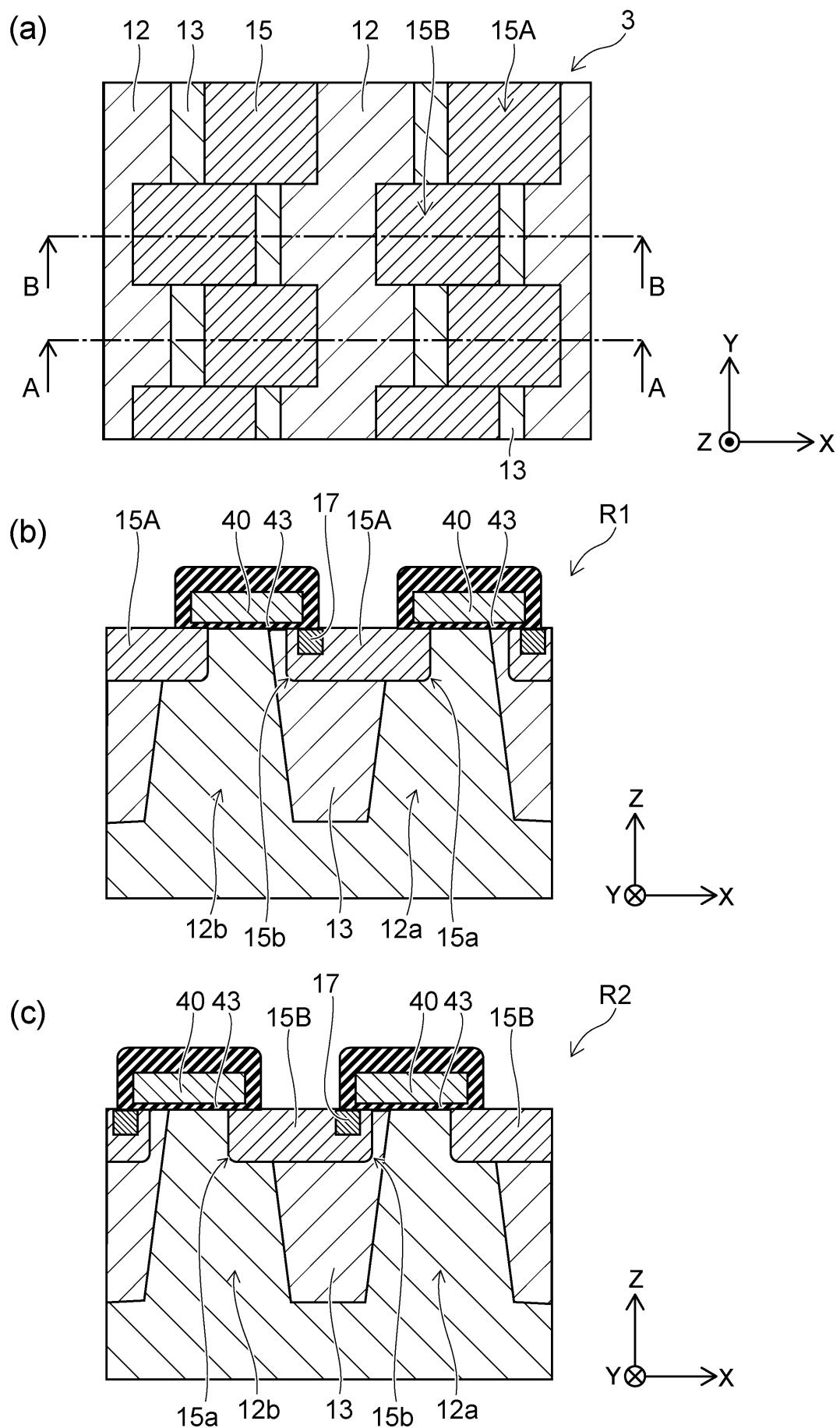

実施形態に係る半導体装置は、第1導電形の第1半導体層と、第2導電形の第2半導体層と、を含む半導体部と、前記半導体部の表面上に設けられた第1電極と、前記半導体部の裏面上に設けられた第2電極と、前記半導体部と前記第1電極との間に設けられ、前記半導体部の表面に第1絶縁膜を介して向き合い、前記第1電極から第2絶縁膜により電気的に絶縁された制御電極と、を備える。前記第2半導体層は、前記半導体部の表面に沿った第1方向において前記第1半導体層の一部と前記第1半導体層の別の一部との間に位置する。前記半導体部は、前記第1半導体層および前記第2半導体層に接する第2導電形の第3半導体層と、前記第3半導体層中に選択的に設けられた第1導電形の第4半導体層と、をさらに含む。前記半導体部の表面は、前記第3半導体層の表面および前記第4半導体層の表面を含む。前記第3半導体層は、前記第1半導体層の前記一部中に位置する第1端部と、前記第2半導体層中に位置する第2端部と、を有する。前記第4半導体層は、前記第3半導体層の前記第2端部に設けられ、前記第1電極は、前記第3半導体層および前記第4半導体層に電気的に接続され、前記制御電極は、前記第4半導体層と第1半導体層の前記別の一部との間に位置する前記第3半導体層の一部および前記第2半導体層の一部、および、前記第1半導体層の前記別の一部に向き合う。

【手続補正3】

【補正対象書類名】図面

【補正対象項目名】図6

【補正方法】変更

【補正の内容】

【図6】