(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6871934号

(P6871934)

(45) 発行日 令和3年5月19日(2021.5.19)

(24) 登録日 令和3年4月20日(2021.4.20)

(51) Int.Cl.

**H03G** 3/20 (2006.01)

**H03G** 3/30 (2006.01)

F 1

H03G 3/20 E

H03G 3/30 D

H03G 3/20 A

請求項の数 13 (全 25 頁)

(21) 出願番号 特願2018-544247 (P2018-544247)

(86) (22) 出願日 平成28年12月6日 (2016.12.6)

(65) 公表番号 特表2019-507552 (P2019-507552A)

(43) 公表日 平成31年3月14日 (2019.3.14)

(86) 國際出願番号 PCT/US2016/065189

(87) 國際公開番号 WO2017/146798

(87) 國際公開日 平成29年8月31日 (2017.8.31)

審査請求日 令和1年11月19日 (2019.11.19)

(31) 優先権主張番号 15/049,963

(32) 優先日 平成28年2月22日 (2016.2.22)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 591025439

ザイリンクス インコーポレイテッド

X I L I N X I N C O R P O R A T E D

アメリカ合衆国 カリフォルニア州 95

124-3400 サン・ホセ ロジック

ドライブ 2100

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 ターカー・メレク、ディデム・ジイ

アメリカ合衆国、95124 カリフォル

ニア州、サン・ホセ、ロジック・ドライブ

、2100

最終頁に続く

(54) 【発明の名称】線形ゲイン符号をインターリープされたオートゲインコントロール回路

## (57) 【特許請求の範囲】

## 【請求項1】

オートゲインコントロール(A G C)回路であって、

A G C符号語の第1のビットに応答するプログラム可能ソースデジネレーション抵抗

を有するベース電流ゲイン回路と、

前記ベース電流ゲイン回路の入力と出力との間に結合され、前記A G C符号語の第2の

ビットに応答するプログラム可能電流源を有するプログラム可能電流ゲイン回路と、

前記ベース電流ゲイン回路の前記出力に結合され、前記A G C符号語の前記第2のビット

の論理的補完物に応答するプログラム可能電流源と、前記ベース電流ゲイン回路に入力

される電圧とは別のバイアス電圧を受信するように結合された入力とを有するブリーダ回

路と、

前記ベース電流ゲイン回路の前記出力に結合された負荷回路とを備え、

前記A G C符号語の一部は、第1の複数の前記第2のビットをインターリープされた第

1の複数の前記第1のビットで構成される、A G C回路。

## 【請求項2】

前記ベース電流ゲイン回路は、固定電流源を備える、請求項1に記載のA G C回路。

## 【請求項3】

前記プログラム可能電流ゲイン回路は、前記A G C符号語の前記第2のビットに応答す

るプログラム可能ソースデジネレーション抵抗を備える、請求項1に記載のA G C回路

。

**【請求項 4】**

前記プログラム可能電流ゲイン回路は、各々が前記プログラム可能電流源の少なくとも1つの分岐を提供する複数の電流ゲインセルを備える、請求項1に記載のAGC回路。

**【請求項 5】**

前記AGC符号語の最下位部分は、第2の複数の前記第1のビットで構成される、請求項1に記載のAGC回路。

**【請求項 6】**

前記AGC符号語の最上位部分は、第2の複数の前記第2のビットで構成される、請求項1に記載のAGC回路。

**【請求項 7】**

前記ベース電流ゲイン回路の前記プログラム可能ソースデジエネレーション抵抗は、固定抵抗と、

前記固定抵抗と並列の複数の切替可能抵抗とを備える、請求項1に記載のAGC回路。

**【請求項 8】**

前記ベース電流ゲイン回路は、前記AGC符号語の前記第1のビットに応答するプログラム可能電流源を備える、請求項1に記載のAGC回路。

**【請求項 9】**

バイナリ符号語から温度計符号として前記AGC符号語を生成するように構成されたデコーダをさらに備える、請求項1に記載のAGC回路。

**【請求項 10】**

受信機であって、

アナログ信号を受信するように結合された第1の入力を有するオートゲインコントロール(AGC)回路と、

前記AGC回路の出力に結合されたフロントエンド回路と、

前記AGC回路の第2の入力と前記フロントエンド回路の出力との間に結合されたAGC制御回路とを備え、

前記AGC回路は、

前記AGC回路の前記第1の入力と前記出力との間に結合されたベース電流ゲイン回路を含み、前記ベース電流ゲイン回路は、AGC符号語の第1のビットに応答するプログラム可能ソースデジエネレーション抵抗を有し、前記AGC回路はさらに、

前記AGC回路の前記第1の入力と前記出力との間に結合され、前記AGC符号語の第2のビットに応答するプログラム可能電流源を有するプログラム可能電流ゲイン回路と、

前記AGC回路の前記出力に結合され、前記AGC符号語の前記第2のビットの論理的補完物に応答するプログラム可能電流源と、前記ベース電流ゲイン回路に入力される電圧とは別のバイアス電圧を受信するように結合された入力とを有するブリーダ回路と、

前記AGC回路の前記出力に結合された負荷回路とを含み、

前記AGC符号語の一部は、第1の複数の前記第2のビットをインターリープされた第1の複数の前記第1のビットで構成される、受信機。

**【請求項 11】**

前記プログラム可能電流ゲイン回路は、各々が前記プログラム可能電流源の少なくとも1つの分岐を提供する複数の電流ゲインセルを備える、請求項10に記載の受信機。

**【請求項 12】**

前記AGC符号語の最下位部分は、第2の複数の前記第1のビットで構成され、前記AGC符号語の最上位部分は、第2の複数の前記第2のビットで構成される、請求項10に記載の受信機。

**【請求項 13】**

前記AGC回路は、前記AGC制御回路によって出力されたバイナリ符号語から温度計符号として前記AGC符号語を生成するように構成されたデコーダをさらに含む、請求項10に記載の受信機。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】****技術分野**

本開示の実施例は、一般に電子回路に関し、特に線形ゲイン符号をインターリープされたオートゲインコントロール回路に関する。

**【背景技術】****【0002】****背景**

送受信機では、オートゲインコントロール (automatic gain control : AGC) プロックを用いて、入来するアナログ信号を減衰させたり増幅したりすることにより、当該アナログ信号が、その出力において、アナログデータを検出してデジタルビットストリームに変換するサンプリング回路のダイナミックレンジの範囲内であるようにする。AGC プロックは、一般に、可変ゲイン増幅器と、増幅器のゲインを自動的に調節する制御ループとを含む。

10

**【0003】**

有線送受信機では、高損失チャネルは、受信機フロントエンドに小信号をもたらす一方、低損失チャネルは、受信機フロントエンドを飽和させる大信号をもたらす。ゲインが自動適応ループを介して決定される AGC 回路は、大入力信号を減衰させ、小入力信号を増幅することにより、信号は、その出力において、サンプラ回路の感度よりも小さくなることはなく、サンプリング回路を飽和させることもなく、信号がサンプラ回路の感度よりも小さくなることおよびサンプリング回路を飽和させることは両方とも、誤検出およびビットエラーを生じさせることになる。したがって、ゲイン範囲が広く、帯域幅が高く、線形性に優れており、AGC ゲイン設定にわたって寄生帯域内ピーキングを持たない AGC 回路を提供することが望ましい。

20

**【発明の概要】****【課題を解決するための手段】****【0004】****概要**

線形ゲイン符号をインターリープされたオートゲインコントロール (AGC) 回路を提供するための技術について説明する。実施例において、AGC 回路は、AGC 符号語の第 1 のビットに応答するプログラム可能ソースデジジェネレーション抵抗を有するベース電流ゲイン回路を含む。上記 AGC 回路は、上記ベース電流ゲイン回路の入力と出力との間に結合され、上記 AGC 符号語の第 2 のビットに応答するプログラム可能電流源を有するプログラム可能電流ゲイン回路をさらに含む。上記 AGC 回路は、上記ベース電流ゲイン回路の上記出力に結合され、上記 AGC 符号語の上記第 2 のビットの論理的補完物に応答するプログラム可能電流源を有するブリーダ回路をさらに含む。上記 AGC 回路は、上記ベース電流ゲイン回路の上記出力に結合された負荷回路をさらに含む。

30

**【0005】**

任意に、上記ベース電流ゲイン回路は、固定電流源を含み得る。

40

任意に、上記プログラム可能電流ゲイン回路は、上記 AGC 符号語の上記第 2 のビットに応答するプログラム可能ソースデジジェネレーション抵抗を含み得る。

**【0006】**

任意に、上記プログラム可能電流ゲイン回路は、各々が上記プログラム可能電流源の少なくとも 1 つの分岐を提供する複数の電流ゲインセルを含み得る。

**【0007】**

任意に、上記 AGC 符号語の一部は、第 1 の複数の上記第 2 のビットをインターリープされた第 1 の複数の上記第 1 のビットで構成され得る。

**【0008】**

任意に、上記 AGC 符号語の最下位部分は、第 2 の複数の上記第 1 のビットで構成され

50

得る。

**【 0 0 0 9 】**

任意に、上記 A G C 符号語の最上位部分は、第 2 の複数の上記第 2 のビットで構成され得る。

**【 0 0 1 0 】**

任意に、上記ベース電流ゲイン回路の上記プログラム可能ソースデジエネレーション抵抗は、固定抵抗と、上記固定抵抗と並列の複数の切替可能抵抗とを含み得る。

**【 0 0 1 1 】**

任意に、上記ベース電流ゲイン回路は、上記 A G C 符号語の上記第 1 のビットに応答するプログラム可能電流源を含み得る。 10

**【 0 0 1 2 】**

任意に、上記 A G C 回路は、バイナリ符号語から温度計符号として上記 A G C 符号語を生成するように構成されたデコーダをさらに含み得る。

**【 0 0 1 3 】**

別の実施例において、受信機は、アナログ信号を受信するように結合された第 1 の入力を有する A G C 回路を含む。上記受信機は、上記 A G C 回路の出力に結合されたフロントエンド回路をさらに含む。上記受信機は、上記 A G C 回路の第 2 の入力と上記フロントエンド回路の出力との間に結合された A G C 制御回路をさらに含む。上記 A G C 回路は、上記 A G C 回路の上記第 1 の入力と上記出力との間に結合されたベース電流ゲイン回路を含み、上記ベース電流ゲイン回路は、A G C 符号語の第 1 のビットに応答するプログラム可能ソースデジエネレーション抵抗を有する。上記 A G C 回路は、上記 A G C 回路の上記第 1 の入力と上記出力との間に結合され、上記 A G C 符号語の第 2 のビットに応答するプログラム可能電流源を有するプログラム可能電流ゲイン回路をさらに含む。上記 A G C 回路は、上記 A G C 回路の上記出力に結合され、上記 A G C 符号語の上記第 2 のビットの論理的補完物に応答するプログラム可能電流源を有するブリーダ回路をさらに含む。上記 A G C 回路は、上記 A G C 回路の上記出力に結合された負荷回路をさらに含む。 20

**【 0 0 1 4 】**

任意に、上記プログラム可能電流ゲイン回路は、各々が上記プログラム可能電流源の少なくとも 1 つの分岐を提供する複数の電流ゲインセルを含み得る。

**【 0 0 1 5 】**

任意に、上記 A G C 符号語の一部は、第 1 の複数の上記第 2 のビットをインターリープされた第 1 の複数の上記第 1 のビットで構成され得る。 30

**【 0 0 1 6 】**

任意に、上記 A G C 符号語の最下位部分は、第 2 の複数の上記第 1 のビットで構成され得る。

**【 0 0 1 7 】**

任意に、上記 A G C 符号語の最上位部分は、第 2 の複数の上記第 2 のビットで構成され得る。

**【 0 0 1 8 】**

任意に、上記 A G C 回路は、上記 A G C 制御回路によって出力されたバイナリ符号語から温度計符号として上記 A G C 符号語を生成するように構成されたデコーダをさらに含み得る。 40

**【 0 0 1 9 】**

別の実施例において、オートゲインコントロール方法は、ベース電流ゲイン回路とプログラム可能電流ゲイン回路とブリーダ回路と負荷回路とを有する A G C 回路を制御するための A G C 符号語を生成するステップを含む。上記方法は、上記 A G C 符号語の第 1 のビットを制御して、上記ベース電流ゲイン回路のプログラム可能ソースデジエネレーション抵抗を制御するステップをさらに含む。上記方法は、上記 A G C 符号語の第 2 のビットを制御して、上記プログラム可能電流ゲイン回路のプログラム可能電流源を制御するステップをさらに含む。上記方法は、上記 A G C 符号語の上記第 2 のビットを論理的に補完して 50

、上記ブリーダ回路のプログラム可能電流源を制御するステップをさらに含む。

**【0020】**

任意に、上記A G C符号語の一部は、第1の複数の上記第2のビットをインターリープされた第1の複数の上記第1のビットで構成され得る。

**【0021】**

任意に、上記A G C符号語の最下位部分は、第2の複数の上記第1のビットで構成され得る。

**【0022】**

任意に、上記A G C符号語の最上位部分は、第2の複数の上記第2のビットで構成され得る。

10

**【0023】**

これらのおよび他の局面は、以下の詳細な説明を参照することにより理解することができる。

**【0024】**

上記の特徴を詳細に理解することができるよう、上に簡単に要約した説明が例示的な実現例を参照することによりさらに詳細になされ得て、例示的な実現例のうちのいくつかは添付の図面に示されている。しかし、添付の図面は、代表的な例示的な実現例を示しているに過ぎず、そのためその範囲を限定するものと考えるべきではない、ということに注意しなければならない。

**【図面の簡単な説明】**

20

**【0025】**

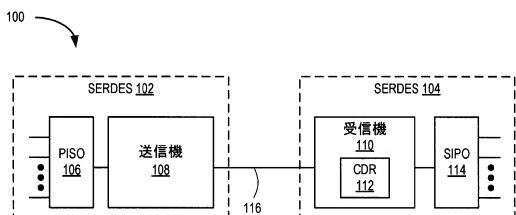

【図1】本明細書に記載されているオートゲインコントロール(A G C)回路の例を利用することができる例示的な通信システムを示すブロック図である。

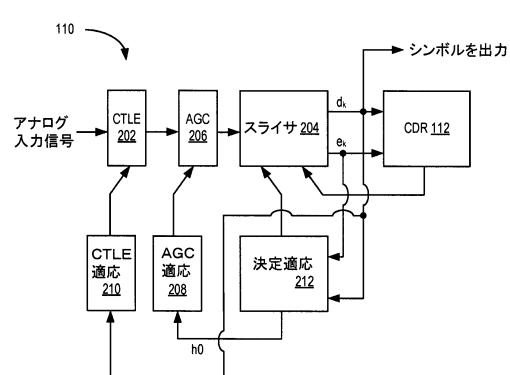

**【図2】**図1の通信システムにおける受信機の一例を示すブロック図である。

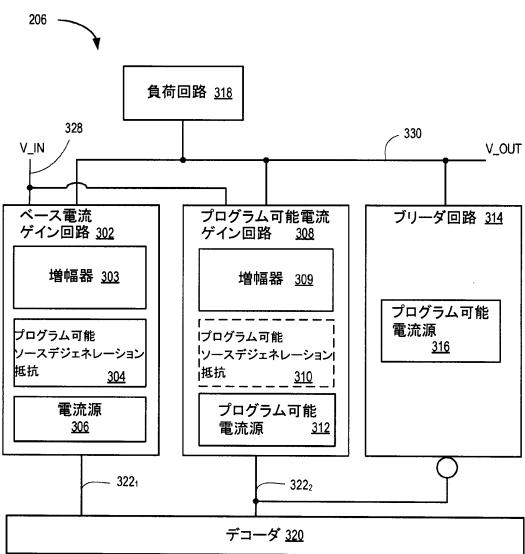

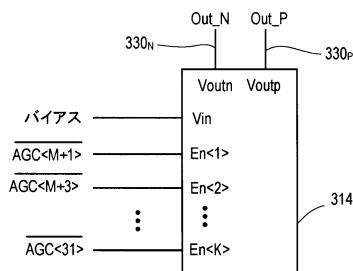

**【図3】**実施例に係るA G C回路を示すブロック図である。

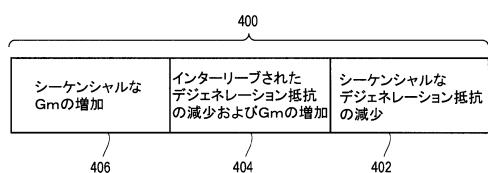

**【図4 A】**実施例に係るA G C符号の一般的なフォーマットを示すブロック図である。

**【図4 B】**実施例に係るA G C符号の具体例を示すブロック図である。

**【図5 A】**ベース電流ゲイン回路の一例を示す概略図である。

**【図5 B】**ベース電流ゲイン回路の一例を示す概略図である。

**【図6】**実施例に係るプログラム可能電流ゲイン回路を示すブロック図である。

30

**【図7】**実施例に係るブリーダ回路を示すブロック図である。

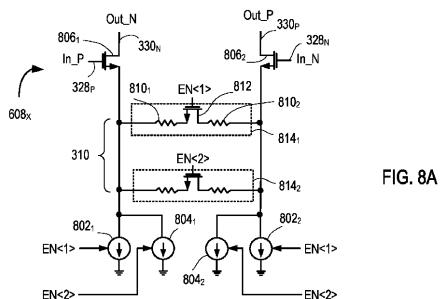

**【図8 A】**電流ゲインセルの一例を示す概略図である。

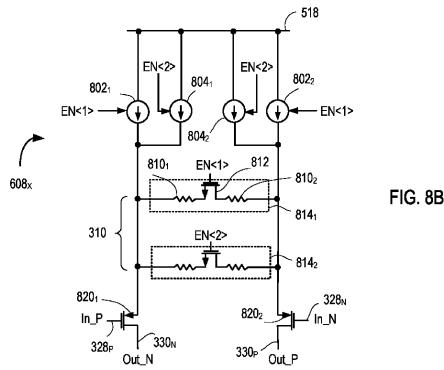

**【図8 B】**電流ゲインセルの一例を示す概略図である。

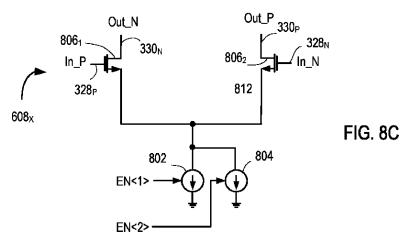

**【図8 C】**電流ゲインセルの一例を示す概略図である。

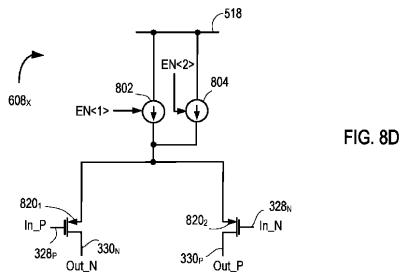

**【図8 D】**電流ゲインセルの一例を示す概略図である。

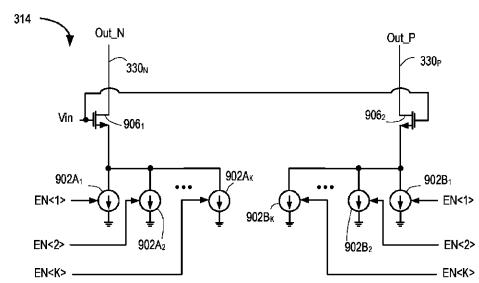

**【図9 A】**実施例に係るブリーダ回路を示す概略図である。

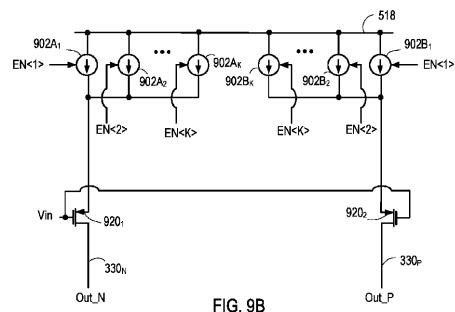

**【図9 B】**実施例に係るブリーダ回路を示す概略図である。

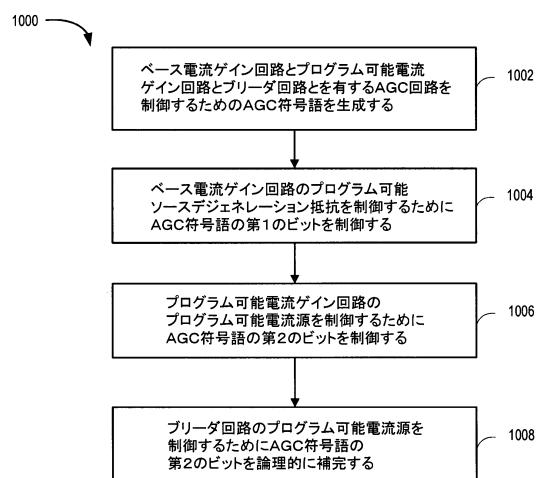

**【図10】**実施例に係るオートゲインコントロール方法を示すフロー図である。

【図11】本明細書に記載されているA G C回路を含み得るフィールドプログラマブルゲートアレイ(field programmable gate array : F P G A)のアーキテクチャを示す図である。

40

**【発明を実施するための形態】**

**【0026】**

理解を容易にするために、図面に共通している同一の要素については、可能な限り同一の参照番号を用いて示している。ある実施例の要素を他の実施例に有益に組み込むことができると考えられる。

**【0027】**

**詳細な説明**

以下、図面を参照して、さまざまな特徴について説明する。なお、図面は一定の縮尺で描かれている場合もあればそうでない場合もあり、同様の構造または機能の要素は図面全

50

体にわたって同様の参照番号によって示されている。なお、図面は特徴の説明を容易にすることのみを意図している。図面は、請求項に係る発明を網羅的に説明するものとして意図されているわけではなく、請求項に係る発明の範囲を限定するものとして意図されているわけでもない。また、示されている実施例は、示されている全ての局面または利点を有している必要はない。特定の実施例に関連して記載されている局面または利点は、必ずしも当該実施例に限定されるものではなく、たとえそのように示されていなくても、またはたとえそのように明確に説明されていなくても、その他の実施例で実施することができる。

### 【0028】

線形ゲイン符号をインターリープされたオートゲインコントロール（A G C）増幅器を提供するための技術について説明する。A G C回路の一例は、ギルバートセルベースのバイアス電流ステアリング回路によるアナログゲインコントロールを利用する。別の例では、A G C回路は、ソースデジエネレーションを有する線形抵抗器負荷増幅器を利用する。高速有線送受信機では、このような増幅器は、微調整および小さなゲインステップにより、広いダイナミックレンジを実現しながら線形動作を維持する。このような増幅器では、ゲインは、ソースデジエネレーション抵抗を調整することによって制御され、あるゲインコントロール符号から別のゲインコントロール符号までのゲインステップを小さくすることができます。また、ソースデジエネレーションにより、線形性に影響を及ぼす出力振幅および入力トランジスタ電流密度が、ゲイン符号を変化させた際に損なわれることがない。

### 【0029】

ソースデジエネレーション抵抗器ベースのゲイン調整の1つの問題は、A G C回路が広いゲイン範囲および高い帯域幅を有する広ダイナミックレンジ・高データレートの送受信機で起こる。広いダイナミックレンジを実現するために、増幅器は、小ゲイン（または、減衰）設定では実効デジエネレーション抵抗が大きくなり、高ゲイン設定では実効抵抗が小さくなるように、幅広いソースデジエネレーション抵抗を有するべきである。ソースデジエネレーションを有する線形抵抗器負荷増幅器は、入力トランジスタのソースノードにおいて寄生キャパシタンスを有する。この寄生キャパシタンスは、トランジスタの固有のキャパシタンスおよびテール電流源への配線およびソースデジエネレーション抵抗器の配線に由来する。ソースデジエネレーション抵抗器が多くなると、寄生キャパシタンスが大きくなる。実効デジエネレーション抵抗（ $R_{s e f f}$ ）および合計寄生キャパシタンス（ $C_p$ ）は、以下のように寄生ゼロを形成する。

### 【0030】

#### 【数1】

$$f_z = \frac{1}{2\pi R_{s e f f} C_p}$$

### 【0031】

高帯域幅増幅器では、寄生ゼロ  $f_z$  は、帯域内であり、望ましくないピーキングを周波数応答に生じさせる。A G C周波数応答における寄生ピーキングは、以下の理由で望ましくない。ピーキングは、寄生ベースであるため、十分に制御されず、ゲイン設定に依存する周波数を有する。さらに、このタイプのピーキングは、望ましくない等化を生じさせる可能性があり、ピーキング周波数における入力信号成分が残りの周波数成分よりも多くなって、シンボル間干渉（inter-symbol interference : I S I）を生じさせる。また、このような増加は、非常に大きな信号を生じさせてサンプルを飽和させ、適応ループを駆動して誤ったビット決定を生じさせる可能性がある。有線送受信機では、多くの場合、A G Cブロックの後に、所望の周波数でピーキングを介して等化を実行する連続時間線形等化器（continuous time linear equalizer : C T L E）が続くか、またはA G Cブロックの前にC T L Eがくる。C T L Eの役割は、ピーキングがしばしば調整される周波数範囲をターゲットにするようにこのような増加を提供するというものである。一方、A G Cの役割は、ゲインまたは減衰を提供するのみである平坦応答増幅器を実現するというものであ

10

20

30

40

50

る。C T L E および A G C を用いることによって、周波数増加および信号増幅の作業が分離され、独立して制御できるようになる。したがって、A G C において各ゲイン設定について平坦な周波数応答を実現することが不可欠であろう。

#### 【 0 0 3 2 】

望ましくない寄生ゼロピーキングを減少させるための 1 つの技術は、A G C 出力にデピーキング (de-peaking) キャパシタを追加して、ピーキングを減少させてフィルタリングするというものであり、当該ピーキングは、ゲインを調整して寄生ピーキングを導入するソースデジエネレーション抵抗器によって引き起こされる。これらのキャパシタは、大きなデジエネレーション抵抗が帯域内ピーキングを生じさせ、A G C 帯域幅、したがって帯域内ピーキングの量を減少させる低ゲイン設定でイネーブルにされる。高ゲイン設定では、A G C 帯域幅が望み通りに高くなるようにキャパシタがディスエーブルにされる。この技術の欠点は、キャパシタアレイが必要であることであり、各ゲイン設定当たりどのぐらいのキャパシタンスをイネーブル / ディスエーブルにすべきかを判断するための複雑なスキームが必要であることである。また、キャパシタは、プロセス変動およびモデリング不正確を有し、これらは両方とも設計の中で考慮に入れられるべきである。なぜなら、ナノメートルスケールのシリコン技術における無線周波数 (radio frequency : R F ) キャパシタ装置は、しばしば、トランジスタおよび抵抗器ほどには正確に制御されない別々の特別なモデルを必要とするからである。最後に、A G C 出力に大きなキャパシタアレイを追加することにより、面積が大きくなり、配線および単位キャパシタのオフキャパシタンスにより多くの寄生キャパシタンスが出力に追加され、A G C の高帯域幅が損なわれることになる。10

#### 【 0 0 3 3 】

本明細書に記載されている実施例では、帯域内寄生ピーキングゼロを導入することなく、ダイナミックレンジが広く、ゲインステップが微調整され、線形性に優れ、帯域幅が高い平坦な周波数応答を実現するゲインコントロールを有する A G C 回路が提供される。A G C 回路におけるゲインコントロールは、ソースデジエネレーション抵抗器調整とバイアス電流およびトランスコンダクタンス (ゲイン) 調整とのインターリープされた組み合わせによって得られる。A G C 回路は、ゲインを変化させるようにイネーブル / ディスエーブルにされるモジュール式のプログラム可能電流ソースデジエネレートゲイン回路を含む。A G C 回路は、ブリーダ回路と固定電流ベース回路とをさらに含み、ゲインは、プログラム可能ソースデジエネレーション抵抗器のアレイによって制御される。ゲインコントロールは、デジタルゲインコントロールビットを介して固定電流ベース回路とプログラム可能ゲイン回路との間でインターリープされた態様でなされる（すなわち、ゲイン符号インターリービング）。このようなインターリープされた制御により、出力における望ましくない寄生ピーキングなしに、線形性、高帯域幅および平坦な周波数応答を維持しながら、正確で広範囲のゲインコントロールが実現される。また、インターリープされた A G C 回路は、ゲインコントロールビットを介して自動的に制御されるブリーダ回路を用いることにより、全てのゲイン設定について一定の出力共通モードを実現する。30

#### 【 0 0 3 4 】

減少した電流および小さなゲインをベースとして用いて最低ゲイン設定を実現することによって、本明細書に記載されている A G C 回路は、ベースにおいて大きなデジエネレーション抵抗または大きな入力装置を必要とせず、したがって上記の帯域内ゼロ問題を有することはない。インターリープされたゲインコントロールアプローチを用いてゲインを増加させてデジエネレーション抵抗を減少させることによって、A G C 回路は、振幅の増加およびゲインの増加、したがって優れた線形性を実現し、全てのゲイン符号について広いゲイン範囲および優れたデシベル (d B) 線形導出を実現する。これらのおよび他の局面について、図面を参照して以下でさらに説明する。40

#### 【 0 0 3 5 】

図 1 は、本明細書に記載されている A G C 回路の例を利用することができる例示的な通信システム 1 0 0 を示すブロック図である。通信システム 1 0 0 は、チャネル 1 1 6 を介50

して受信機 110 に結合された送信機 108 を備える。実施例では、送信機 108 は、シリアルライザ / デシリアルライザ (SerDes) 102 の一部であり、受信機 110 は、SerDes 104 の一部である。明確にするために、デシリアルライゼーション回路は SerDes 102 から省略されており、シリアルライゼーション回路は SerDes 104 から省略されている。SerDes 102 は、並列入力データを直列出力データに変換して、送信機 108 によってチャネル 116 を介して送信する並列入力直列出力 (parallel-in-serial-out : PISO) 回路 106 を含む。SerDes 104 は、受信機 110 によって出力された直列データを並列出力データに変換する直列入力並列出力 (serial-in-parallel-out : SIPO) 回路を含む。SerDes 102 および SerDes 104 は、デコーダ、エンコーダなどの他の回路 (図示せず) を含んでもよい。

10

#### 【0036】

SerDes 102 および SerDes 104 が示されているが、他の実施例では、送信機 108 および / または受信機 110 の各々は、より大きな送受信機回路の一部ではないスタンダードアロンの回路であってもよい。いくつかの実施例では、送信機および受信機 110 は、特定用途向け集積回路 (application specific integrated circuit : ASIC) 、またはフィールドプログラマブルゲートアレイ (FPGA) などのプログラマブル IC 、などの 1つ以上の集積回路 (integrated circuit : IC) の一部であってもよい。

#### 【0037】

チャネル 116 は、電気的伝送媒体を含み得る。電気的伝送媒体は、送信機 108 と受信機 110 との間のいかなるタイプの電気経路であってもよく、金属トレース、ビア、ケーブル、コネクタ、デカップリングキャパシタ、終端抵抗器などを含み得る。電気的伝送媒体は、低電圧差動信号 (low-voltage differential signal : LVDS) 経路などの差動信号経路であってもよい。

20

#### 【0038】

実施例では、送信機 108 は、データを有する基準クロックを送信しない。受信機 110 は、入来するシンボルストリームからクロックを抽出するためのクロックデータ復元 (clock data recovery : CDR) 回路 112 を含む。抽出されたクロックは、入来するシンボルストリームをサンプリングして、送信されたビットを復元するために用いられる。

#### 【0039】

図 2 は、受信機 110 の一例を示すブロック図である。受信機 110 は、連続時間線形等化器 (CTLE) 202 と、AGC 回路 206 と、スライサ 204 と、CDR 112 と、オートゲインコントロール (AGC) 適応回路 208 と、CTLE 適応回路 210 と、決定適応回路 212 とを含む。CTLE 回路 202 は、チャネル 116 からアナログ信号を受信するように結合される。CTLE 202 は、ハイパスフィルタとして動作して、チャネル 116 のローパス特性を補償する。CTLE 202 の周波数応答のピークは、CTLE 適応回路 210 によって調節することができる。CTLE 202 は、等化されたアナログ信号を出力し、AGC 回路 206 の入力に結合される。AGC 回路 206 は、ゲイン調節された信号をスライサ 204 に出力する。AGC 206 のゲインは、AGC 適応回路 208 によって制御することができる。別の実施例では、AGC 回路 206 は、CTLE 回路 202 の前にきてもよい。一般に、AGC 回路 206 の出力は、スライサ 204 、 CTLE 202 などの受信機のさまざまな回路を含み得るフロントエンド回路に結合され得る。

30

#### 【0040】

スライサ 204 は、AGC 回路 206 に結合され、等化されゲイン調節されたアナログ信号を受信する。スライサ 204 は、等化されゲイン調節されたアナログ信号をサンプリングして、シンボル ( $k$ ) 当たりデータサンプル ( $d_k$ ) およびエラーサンプル ( $e_k$ ) を生成するように動作可能である。スライサ 204 は、ボーレートで動作するサンプリングクロックに基づいて、等化されたアナログ信号からシンボルの決定を行う。決定適応回路 212 は、スライサ 204 の決定閾値を制御する。CDR 112 は、スライサ 204 のサンプリング位相を制御する。決定適応回路 212 および CDR 112 は、エラーサンプ

40

50

ルの値を最小化するように動作する。

#### 【0041】

C D R 1 1 2 は、スライサ 2 0 4 に結合され、データサンプルおよびエラーサンプルを受信する。C D R 1 1 2 は、データサンプルおよびエラーサンプルに基づいて、シンボル当たりタイミングエラー値および波形推定値を両方とも生成する。C D R 1 1 2 は、生成されたタイミングエラー値に基づいて、スライサ 2 0 4 のサンプリング位相を適応させるための制御信号を生成する。

#### 【0042】

決定適応回路 2 1 2 は、スライサ 2 0 4 に結合され、データサンプルおよびエラーサンプルを受信する。決定適応回路 2 1 2 は、データサンプルおよびエラーサンプルに基づいて、スライサ 2 0 4 の決定閾値を制御するための制御信号を生成する。決定適応回路 2 1 2 は、各々の処理されたシンボルについてメインカーソルのカーソル重み ( $h_0$ ) も生成し、A G C 適応回路 2 0 8 に結合される。C T L E 適応回路 2 1 0 は、スライサ 2 0 4 に結合され、データサンプルを受信する。C T L E 適応回路 2 1 0 は、C T L E 2 0 2 のピーク周波数応答を調節するための制御信号を生成する。A G C 適応回路 2 0 8 は、決定適応回路 2 1 2 に結合され、メインカーソル大きさ信号を受信する。A G C 適応回路 2 0 8 は、A G C 回路 2 0 6 のゲインを調節するための制御信号を生成する。当該制御信号は、以下でさらに説明する A G C 制御語を提供する。

#### 【0043】

図 3 は、実施例に係る A G C 回路 2 0 6 を示すブロック図である。図 3 に示される A G C 回路 2 0 6 は、図 2 に示される受信機 1 1 0 などの受信機で用いられてもよく、またはその他のタイプの受信機およびオートゲインコントロールを必要とする他のタイプの回路で用いられてもよい。A G C 回路 2 0 6 は、ベース電流ゲイン回路 3 0 2 と、プログラム可能電流ゲイン回路 3 0 8 と、ブリーダ回路 3 1 4 と、負荷回路 3 1 8 とを含む。いくつかの実施例では、A G C 回路 2 0 6 は、デコーダ 3 2 0 をさらに含む。他の実施例では、デコーダ 3 2 0 は、外部回路（たとえば、A G C 適応回路 2 0 8 ）の一部であってもよい。

#### 【0044】

ベース電流ゲイン回路 3 0 2 は、アナログ電圧 (V\_IN と記載) を受信するように構成された入力 3 2 8 を含む。入力 3 2 8 は、正および負の成分を有する差動入力である。ベース電流ゲイン回路 3 0 2 は、出力アナログ電圧 (V\_OUT と記載) を提供するように構成された出力 3 3 0 を含む。出力 3 3 0 は、正および負の成分を有する差動出力である。出力アナログ電圧 V\_OUT は、入力アナログ電圧 V\_IN に対して増幅されたり減衰されたりし得る。ベース電流ゲイン回路 3 0 2 は、プログラム可能ソースデジエネレーション抵抗 3 0 4 を有し、電流源 3 0 6 によってバイアスされる増幅器 3 0 3 を備える。実施例では、電流源 3 0 6 は、固定電流源（すなわち、プログラム可能でない）である。代替的に、いくつかの実施例では、電流源 3 0 6 は、プログラム可能であってもよい。ベース電流ゲイン回路 3 0 2 の一例については、以下で説明する。

#### 【0045】

プログラム可能電流ゲイン回路 3 0 8 は、ベース電流ゲイン回路 3 0 2 の入力 3 2 8 に結合された入力と、ベース電流ゲイン回路 3 0 2 の出力 3 3 0 に結合された出力とを有する。プログラム可能電流ゲイン回路 3 0 8 は、プログラム可能電流源 3 1 2 を用いてバイアスされる 1 つ以上の増幅器 3 0 9 を備える。プログラム可能電流ゲイン回路 3 0 8 における各増幅器 3 0 9 は、プログラム可能電流源 3 1 2 の 1 つ以上の分岐を含む。実施例では、プログラム可能電流ゲイン回路 3 0 8 は、プログラム可能ソースデジエネレーション抵抗 3 1 0 も含む。プログラム可能電流ゲイン回路 3 0 8 における各増幅器 3 0 9 は、プログラム可能ソースデジエネレーション抵抗 3 1 0 の 1 つ以上の分岐を含み得る。他の実施例では、プログラム可能ソースデジエネレーション抵抗 3 1 0 は省略される。プログラム可能電流ゲイン回路 3 0 8 の一例については、以下で説明する。

#### 【0046】

10

20

30

40

50

ブリーダ回路 314 は、ベース電流ゲイン回路 302 の出力 330 に結合された出力を有する。ブリーダ回路 314 は、プログラム可能電流源 316 を含む。ブリーダ回路 314 は、以下でさらに説明するようにプログラム可能な量の電流を電源（図示せず）から引き込むように構成される。ブリーダ回路 314 の一例については、以下で説明する。

#### 【0047】

負荷回路 318 は、ベース電流ゲイン回路 302 の出力 330 に結合される。負荷回路 318 は、ベース電流ゲイン回路 302 およびプログラム可能電流ゲイン回路 308 によって引き込まれた電流を出力アナログ電圧 V\_OUT に変換するように構成される。固定抵抗を有する負荷、プログラム可能抵抗を有する負荷、いかなるタイプのピーキング技術（たとえば、シャント、直列、tコイルなど）も利用するためにインダクタンスと組み合わせられた抵抗（固定またはプログラム可能）を有する負荷などのさまざまなタイプの負荷回路を利用してもよい。負荷回路 318 の一例については、以下で説明する。

10

#### 【0048】

デコーダ 320 は、バイナリ符号語（バイナリ AGC 符号とも称される）を受信するように構成された入力と、出力 322 とを含む。デコーダ 320 は、バイナリ AGC 符号を温度計符号語（温度計符号語、温度計符号語、AGC 符号および AGC 符号語とさまざまに称される）に変換するように構成されたデジタル回路を含む。すなわち、デコーダ 320 は、バイナリ - 温度計デコーダを実現する。出力 322 は、AGC 符号を提供する。出力 322 の第 1 の部分 322<sub>1</sub>（「第 1 のビット」または「デジエネレーション抵抗制御ビット」とも称される）は、ベース電流ゲイン回路 302 に結合されて、プログラム可能ソースデジエネレーション抵抗 304 を制御する。出力 322 の第 2 の部分 322<sub>2</sub>（「第 2 のビット」または「電流源制御ビット」とも称される）は、プログラム可能電流ゲイン回路 308 に結合されて、プログラム可能電流源 312 を制御する。したがって、AGC 符号は、デジエネレーション抵抗制御ビットおよびプログラム可能電流源制御ビットで構成される。出力 322 の第 2 の部分 322<sub>2</sub> の論理的補完物は、ブリーダ回路 314 に結合される。実施例では、ブリーダ回路 314 は、出力 322 の第 2 の部分 322<sub>2</sub> を反転させるための論理インバータ回路を含み得る。代替的に、デコーダ 320 が論理インバータ回路を含んでもよい。

20

#### 【0049】

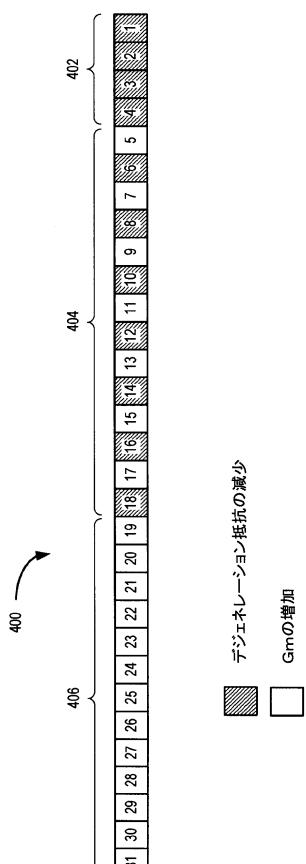

図 4A は、実施例に係るデコーダ 320 によって出力される AGC 符号 400 の一般的なフォーマットを示すブロック図である。当該実施例では、AGC 符号 400 は、第 1 の部分 402 と、第 2 の部分 404 と、第 3 の部分 406 とを含む。第 1 の部分 402 は、AGC 符号 400 の最下位ビット（least-significant bit : LSB）（最下位部分）を備える。第 3 の部分 406 は、AGC 符号 400 の最上位ビット（most-significant bit : MSB）（最上位部分）を備える。第 2 の部分 404 は、最下位ビットと最上位ビットとの間のビット（中間ビットまたは中間部分）を含む。

30

#### 【0050】

AGC 符号 400 の第 1 の部分 402 は、ベース電流ゲイン回路 302 におけるプログラム可能ソースデジエネレーション抵抗 304 を制御する。第 1 の部分 402 は、出力 322 の第 1 の部分 322<sub>1</sub> のビットのみ（デジエネレーション抵抗制御ビットのみ）を含む。したがって、AGC 符号 400 の最下位ビットは、プログラム可能ソースデジエネレーション抵抗 304 のシーケンシャルな制御を提供する。すなわち、第 1 の部分 402 におけるビットを連続的に設定することにより、プログラム可能ソースデジエネレーション抵抗 304 が減少し、第 1 の部分 402 におけるビットを連続的に設定しないことにより、プログラム可能ソースデジエネレーション抵抗 304 が増加する。

40

#### 【0051】

AGC 符号 400 の第 3 の部分 406 は、プログラム可能電流ゲイン回路 308 におけるプログラム可能電流源 312 を制御する。第 3 の部分 406 は、出力 322 の第 2 の部分 322<sub>2</sub> のビットのみ（電流源制御ビットのみ）を含む。したがって、AGC 符号 400 の最上位ビットは、プログラム可能電流源 312 のシーケンシャルな制御を提供する。

50

すなわち、第3の部分406におけるビットを連続的に設定することにより、プログラム可能電流源312の分岐が活性化され、第3の部分406におけるビットを連続的に設定しないことにより、プログラム可能電流源312の分岐が不活性化される。

#### 【0052】

AGC符号400の第2の部分404は、プログラム可能ソースデジエネレーション抵抗304もプログラム可能電流源312も制御する。第2の部分404は、出力の第2の部分322<sub>2</sub>のビットをインターリープされた出力322の第1の部分322<sub>1</sub>のビット（すなわち、電流源制御ビットをインターリープされたデジエネレーション制御ビット）を含む。すなわち、第2の部分404は、1つ以上のデジエネレーション制御ビットの組と1つ以上の電流源制御ビットの組との間を行ったり来たりする。実施例では、インターリービング比率は、1：1である。すなわち、第2の部分404は、1つの電流源制御ビットと1つのデジエネレーション抵抗制御ビットとの間を行ったり来たりする。他のインターリービング比率が利用されてもよい。たとえば、第2の部分404は、2：1というインターリービング比率（すなわち、2つの電流源制御ビット対1つのデジエネレーション抵抗制御ビット）、1：2というインターリービング比率（すなわち、1つの電流源制御ビット対2つのデジエネレーション抵抗制御ビット）、またはその他の比率を含み得る。

#### 【0053】

一般に、バイナリAGC符号は、N個のビットを含み、Nは正の整数である。このような場合、AGC符号400の幅は、 $2^N - 1$ であり得る。図4Bは、N = 5の実施例に係るAGC符号400の具体的なフォーマットを示すブロック図である。すなわち、バイナリAGC符号は5個のビットを含み、AGC符号400（温度計符号）は31個のビットを含む。このような場合、AGC回路206には32個の異なるゲイン設定が存在する。バイナリ語11111が31ビット温度計符号111...1に変換されるまで、バイナリ語00000は31ビット温度計符号000...0に変換され、バイナリ語00001は31ビット温度計符号000...1に変換され、バイナリ語00010は31ビット温度計符号000...11に変換される、などである。AGC回路206の要求されるダイナミックレンジおよび各ゲインステップの要求される導出によって、Nの値は、5よりも大きくてよく、5よりも小さくてもよい。

#### 【0054】

図4Bの実施例では、AGC符号400の第1の部分402は、本明細書ではAGC<1>、AGC<2>、AGC<3>およびAGC<4>（まとめてAGC<4：1>）と記載される4個のビットを含む。AGC符号400のビットAGC<4：1>は、それらがベース電流ゲイン回路302におけるプログラム可能ソースデジエネレーション抵抗304を制御することを示すために網掛けで示されている。網掛けなしのAGC符号400におけるビットは、プログラム可能電流ゲイン回路308におけるプログラム可能電流源312を制御する。

#### 【0055】

AGC符号400の第2の部分404は、本明細書ではAGC<5>、AGC<6>...AGC<18>（まとめてAGC<18：5>）と記載される14個のビットを含む。図4Bの実施例では、第2の部分404におけるビットは、プログラム可能電流源312におけるイネーブルにされた電流分岐を増加させることと、プログラム可能ソースデジエネレーション抵抗304におけるソースデジエネレーション抵抗を減少させることを交互に行う。したがって、ビットAGC<5>、AGC<7>、AGC<9>、AGC<11>、AGC<13>、AGC<15>およびAGC<17>は、プログラム可能電流源312を制御する。ビットAGC<6>、AGC<8>、AGC<10>、AGC<12>、AGC<14>、AGC<16>およびAGC<18>は、プログラム可能ソースデジエネレーション抵抗304を制御する。

#### 【0056】

AGC符号400の第3の部分406は、本明細書ではAGC<19>、AGC<20>

10

20

30

40

50

> . . . A G C < 3 1 > (まとめて A G C < 3 1 : 1 9 >) と記載される 13 個のビットを含む。A G C 符号 4 0 0 のビット A G C < 3 1 : 1 9 > は、それらがプログラム可能電流源 3 1 2 を制御することを示すために網掛けなしで示されている。

#### 【 0 0 5 7 】

図 4 A に戻って、A G C 符号 4 0 0 の第 1 の部分 4 0 2 の幅は、一般に、M 個のビットを含み、M はゼロ以上である。したがって、実施例では、M = 0 であり、第 2 の部分 4 0 4 は、A G C 符号 4 0 0 の最下位ビットになる（すなわち、シーケンシャルなソースデジエネレーション抵抗の制御を提供する第 1 の部分 4 0 2 は省略される）。他の実施例では、M は正の整数である。図 4 B の実施例では、M = 4 である。

#### 【 0 0 5 8 】

第 2 の部分 4 0 4 の幅は、プログラム可能ソースデジエネレーション抵抗 3 0 4 の分岐の数および特定のインターリービング比率によって決まる。図 4 B の実施例では、第 2 の部分 4 0 4 は、プログラム可能ソースデジエネレーション抵抗 3 0 4 を制御する 7 個のビットを含み、そのため、プログラム可能ソースデジエネレーション抵抗 3 0 4 は、合計 11 個の分岐を含む。また、図 4 B の実施例では、第 2 の部分 4 0 4 は、1 : 1 というインターリービング比率を含み、そのため、第 2 の部分の合計幅は、14 ビットである（7 個の電流源制御ビット + 7 個のデジエネレーション抵抗制御ビット）。

10

#### 【 0 0 5 9 】

第 3 の部分 4 0 6 の幅は、プログラム可能電流源 3 1 2 の分岐の数および第 2 の部分 4 0 4 で用いられる特定のインターリービング比率によって決まる。図 4 B の実施例では、第 3 の部分 4 0 6 は、プログラム可能電流源 3 1 2 のそれぞれ 13 個の分岐を制御する 13 個のビットを含む。したがって、図 4 B の実施例では、プログラム可能電流源 3 1 2 は、合計 20 個の分岐（7 個は第 2 の部分 4 0 4 によって制御され、13 個は第 3 の部分 4 0 6 によって制御される）を含む。一般に、第 3 の部分の幅は、ゼロ以上であり得る。したがって、実施例では、第 3 の部分 4 0 6 は省略されてもよく、第 2 の部分 4 0 4 が A G C 符号 4 0 0 の最上位ビットになる。

20

#### 【 0 0 6 0 】

図 3、図 4 A および図 4 B を参照して、A G C 回路 2 0 6 のゲインは、A G C 符号 4 0 0 のビットをオン / オフにすることによって制御される。実施例では、ゲインコントロールは、A G C 符号 4 0 0 の各ビットが設定されるときにゲインが増加するように単調である。実施例では、電流源 3 0 6 は、固定電流源である。ベース電流ゲイン回路 3 0 2 内では、ゲインは、プログラム可能ソースデジエネレーション抵抗 3 0 4 の分岐をオン / オフにすることによって制御される。すなわち、ゲインは、プログラム可能ソースデジエネレーション抵抗 3 0 4 の分岐をオンにすることによって増加させることができ、プログラム可能ソースデジエネレーション抵抗 3 0 4 の分岐をオフにすることによって減少させることができる。

30

#### 【 0 0 6 1 】

プログラム可能電流ゲイン回路 3 0 8 内では、ゲインは、プログラム可能電流源 3 1 2 の分岐をオン / オフにすることによって制御される。プログラム可能電流源 3 1 2 の分岐は、增幅器 3 0 9 の中に分散されている。以下で説明する実施例では、各增幅器 3 0 9 は、プログラム可能電流源 3 1 2 の 2 個の分岐を含む。他の実施例では、各增幅器 3 0 9 は、プログラム可能電流源 3 1 2 の 2 個の分岐よりも多くの分岐を含んでもよく、それよりも少ない分岐を含んでもよい。プログラム可能電流源 3 1 2 の第 1 の分岐がイネーブルにされると、第 1 の增幅器 3 0 9 もイネーブルにされる。したがって、ゲインは、バイアス電流およびトランスクンダクタンス (Gm) を増加させることによって増加される。プログラム可能電流源 3 1 2 の他の分岐がイネーブルにされると、他の增幅器 3 0 9 がイネーブルにされ、バイアス電流および Gm をさらに増加させてゲインを増加させ得る。プログラム可能電流ゲイン回路 3 0 8 がプログラム可能ソースデジエネレーション抵抗 3 1 0 を含む場合には、プログラム可能ソースデジエネレーション抵抗 3 1 0 の分岐は、プログラム可能電流源 3 1 2 の分岐と同様に、増幅器 3 0 9 の中に分散され得る。プログラム可能

40

50

電流源 312 の分岐がイネーブルにされると、プログラム可能ソースデジエネレーション抵抗 310 の分岐がイネーブルにされ得て、ソースデジエネレーション抵抗およびイネーブルにされた電流分岐当たりのゲイン増加を制御する。

#### 【0062】

AGC 回路では、ゲインが小さい場合、AGC 符号当たりのゲインステップも、細かい調整および導出を維持するために小さくあるべきである。したがって、AGC 回路ではデシベル (dB) 線形ゲインコントロールが望ましいことが多い。第 1 の M 個の AGC 符号（たとえば、 $AGC < 4 : 1 >$ ）では、ベース電流ゲイン回路 302 におけるプログラム可能ソースデジエネレーション抵抗 304 の分岐をオンにすることによってのみゲインを増加させる。M 番目の AGC 符号の後で、さらなる AGC 符号がプログラム可能電流ゲイン回路 308 におけるプログラム可能電流源 312 の分岐をイネーブルにすることを開始して、ゲインおよびバイアス電流を増加させる。ゲインコントロールは、M 番目の AGC 符号（たとえば、 $M = 4$  の場合、 $AGC < 18 : 5 >$ ）の後で、インターリープされた態様でベース電流ゲイン回路 302 とプログラム可能電流ゲイン回路 308 との間に分散される。このようにベース電流ゲイン回路 302 とプログラム可能電流ゲイン回路 308 との間をインターリープされた態様で行ったり来たりすることは、（たとえば、1:1 インターリーピングでは）他の全ての AGC 符号においてバイアス電流の増加を生じさせ、プログラム可能ソースデジエネレーション抵抗 304 の全ての分岐がイネーブルにされるまで継続する。このように、ゲインが増加するにつれてバイアス電流が増加し、線形性は損なわれない。また、ベース電流ゲイン回路 302 の制御とプログラム可能電流ゲイン回路 308 の制御との間を行ったり来たりすることにより、dB 線形制御された優れた AGC ゲインステップが提供される。10 20

#### 【0063】

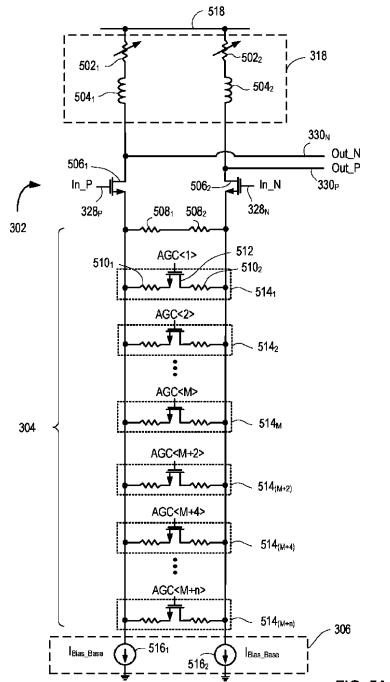

図 5A は、実施例に係るベース電流ゲイン回路 302 を示す概略図である。ベース電流ゲイン回路 302 は、トランジスタ対 506 と、固定抵抗 508 と、切替可能抵抗分岐 514 と、電流源 306 とを含む。トランジスタ対 506 は、増幅器 303 を実現し、固定抵抗 508 および切替可能抵抗分岐 514 は、プログラム可能ソースデジエネレーション抵抗 304 を実現する。

#### 【0064】

トランジスタ対 506 は、トランジスタ 506<sub>1</sub> とトランジスタ 506<sub>2</sub> とを含む。トランジスタ 506<sub>1</sub> および 506<sub>2</sub> は、N チャネル電界効果トランジスタ (field effect transistor : FET) である。たとえば、トランジスタ 506<sub>1</sub> および 506<sub>2</sub> は、N 型金属酸化膜半導体 FET (metal oxide semiconductor FET : MOSFET) であってもよい。トランジスタ 506<sub>1</sub> のゲートは、差動入力電圧 V\_IN の正の成分 (In\_P と記載) を受信するように結合される。トランジスタ 506<sub>2</sub> のゲートは、差動入力電圧 V\_IN の負の成分 (In\_N と記載) を受信するように結合される。トランジスタ 506<sub>1</sub> のドレインは、差動出力電圧 V\_OUT の負の成分 (Out\_N と記載) を提供するように結合される。トランジスタ 506<sub>2</sub> のドレインは、差動出力電圧 V\_OUT の正の成分 (Out\_P と記載) を提供するように結合される。実施例では、固定抵抗 508 は、抵抗器 508<sub>2</sub> と直列に結合された抵抗器 508<sub>1</sub> を含む。トランジスタ 506<sub>1</sub> のソースは、固定抵抗 508 の一方の側に結合され、トランジスタ 506<sub>2</sub> のソースは、固定抵抗 508 の他方の側に結合される。30 40

#### 【0065】

切替可能抵抗分岐 514 は、複数の分岐 514<sub>1</sub> ~ 514<sub>M</sub> および 514<sub>(M+2)</sub> 、

514<sub>(M+4)</sub> . . . 514<sub>(M+n)</sub> を含む。切替可能抵抗分岐 514 は、互いに並列に結合され、固定抵抗 508 と並列に結合される。実施例では、各々の切替可能抵抗分岐 514 は、直列に結合された抵抗器 510<sub>1</sub> 、トランジスタ 514 および抵抗器 510<sub>2</sub> を含む。トランジスタ 512 のソースおよびドレインは、抵抗器 510<sub>1</sub> および抵抗器 510<sub>2</sub> にそれぞれ結合される。トランジスタ 512 のゲートは、AGC 符号 400 のビットを受信するように結合される。分岐 514<sub>(M+n)</sub> がビット AGC < M+n > を受50

信するまで、分岐 514<sub>1</sub> はビット A G C < 1 > を受信し、分岐 514<sub>M</sub> はビット A G C < M > を受信する、などである。切替可能抵抗分岐 514 は、他の構成を含んでもよい。たとえば、各々の切替可能抵抗分岐は、一対のトランジスタの間に結合された抵抗器を含んでもよい。

#### 【 0 0 6 6 】

電流源 306 は、第 1 の電流源 516<sub>1</sub> と第 2 の電流源 516<sub>2</sub> とを含む。第 1 の電流源 516<sub>1</sub> は、トランジスタ 506<sub>1</sub> のソースと基準電圧（たとえば、電気接地）との間に結合される。第 2 の電流源 516<sub>2</sub> は、トランジスタ 506<sub>2</sub> のソースと基準電圧との間に結合される。各電流源 516<sub>1</sub> および 516<sub>2</sub> は、I<sub>Bias\_Base</sub> と記載される電流を下げる。

10

#### 【 0 0 6 7 】

図 5 A は、負荷回路 318 の一例も示している。実施例では、負荷回路 318 は、インダクタ 504<sub>1</sub> および 504<sub>2</sub> と、プログラム可能抵抗器 502<sub>1</sub> および 502<sub>2</sub> とを含む。インダクタ 504<sub>1</sub> は、プログラム可能抵抗器 502<sub>1</sub> と直列に結合され、インダクタ 504<sub>2</sub> は、プログラム可能抵抗器 502<sub>2</sub> と直列に結合される。インダクタ 504<sub>1</sub> とプログラム可能抵抗器 502<sub>1</sub> との直列の組み合わせは、供給電圧 518 とトランジスタ 506<sub>1</sub> のドレインとの間に結合される。インダクタ 504<sub>2</sub> とプログラム可能抵抗器 502<sub>2</sub> との直列の組み合わせは、供給電圧 518 とトランジスタ 506<sub>2</sub> のドレインとの間に結合される。プログラム可能抵抗器 502 は、プロセスおよび温度変動 (process and temperature variations : P V T) を考慮に入れるようにプログラムすることができる。インダクタ 504 は、誘導性ピーキングを提供する。上記のように、負荷回路 318 は、他の構成を有してもよい。

20

#### 【 0 0 6 8 】

動作時、A G C 符号 400 がゼロである場合（すなわち、A G C < 31 : 1 > のうちいずれも設定されない場合）、プログラム可能ソースデジエネレーション抵抗 304 は、固定抵抗 508 のみを含む。したがって、ソースデジエネレーション抵抗は、その最高値にある。バイアス電流は I<sub>Bias\_Base</sub> に等しく、これは A G C 回路 206 の最低バイアス電流である。このゲイン設定が低いので、線形性に必要な振幅も低い。したがって、小さなバイアス電流を用いることによって線形性が損なわれることはない。A G C 符号 400 が増加すると（たとえば、A G C 符号 400 のより多くのビットが設定されると）、より多くの切替可能抵抗分岐 514 がイネーブルにされ、ソースデジエネレーション抵抗を減少させ、A G C 回路 206 のゲインを増加させる。

30

#### 【 0 0 6 9 】

A G C 符号が (M + n) に達すると、プログラム可能ソースデジエネレーション抵抗 304 の全ての分岐がイネーブルにされる。A G C 符号が (M + n) よりも大きくなると、最大 A G C 符号（たとえば、図 4 B の実施例では A G C < 31 >）に達するまで、各 A G C 符号は、プログラム可能電流源 312 の分岐をオンにして、より多くのバイアス電流を提供する。切替可能抵抗分岐 514 の数は、設計仕様によって決まる。ゲイン符号が高ければ、ゲイン比率に対して一定のゲインステップ (d B の点で一定のゲインステップ) を維持するために、大きなゲインステップが好まれる。したがって、大きなゲイン符号では、プログラム可能ソースデジエネレーション抵抗 304 は調節されない。それどころか、プログラム可能電流ゲイン回路 308 のみが調節され、大きなゲインステップを実現する。これは、また、プログラム可能ソースデジエネレーション抵抗 304 のサイズを小さくし、寄生キャパシタンスを減少させる。図 4 B の実施例では、M = 4 であり、これは、インターリービングが A G C 符号 M + 1 = 5 で開始することを意味する。設計仕様によつては、インターリービングが最低 A G C 符号ですぐに開始するように、M は、4 よりも大きくてよく、1 程度であつてもよい。

40

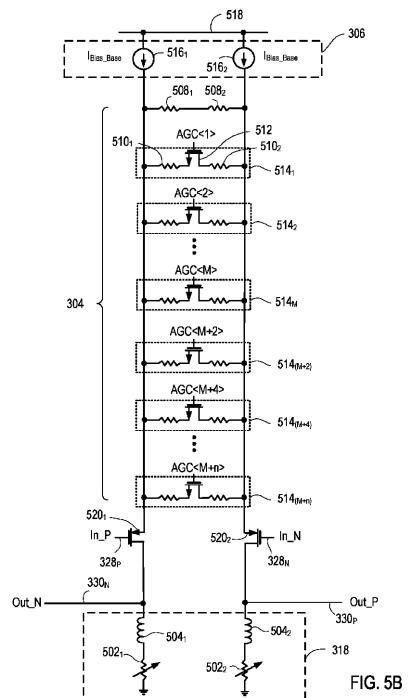

#### 【 0 0 7 0 】

図 5 B は、別の実施例に係るベース電流ゲイン回路 302 を示す概略図である。図 5 A の要素と同一または同様の図 5 B における要素は、同一の参照番号で示されている。図 5

50

B の実施例では、増幅器 303 のトランジスタは、P 型 MOSFET などの P チャネル FET を備える。すなわち、ベース電流ゲイン回路 302 は、トランジスタ 520<sub>1</sub> とトランジスタ 520<sub>2</sub> とを備えるトランジスタ対 520 を含む。トランジスタ 520<sub>1</sub> および 520<sub>2</sub> のソースは、固定抵抗 508 および切替可能抵抗分岐 514 のそれぞれの端子に結合される。トランジスタ 520<sub>1</sub> および 520<sub>2</sub> のドレインは、負荷回路 318 に結合される。トランジスタ 520<sub>1</sub> および 520<sub>2</sub> のゲートは、電圧 In\_P および In\_N をそれぞれ受信する。図 5B に示されるベース電流ゲイン回路 302 は、上記の図 5A に示される実施例と同様に動作する。

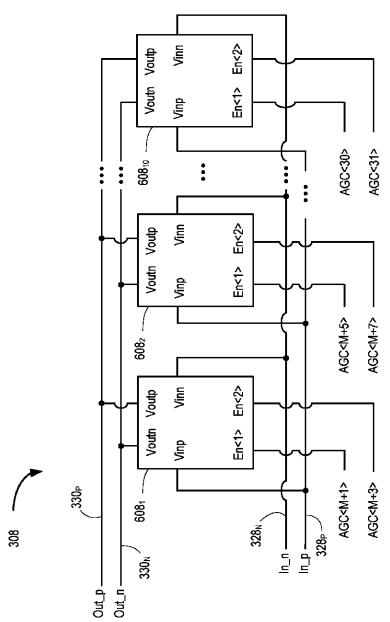

#### 【0071】

図 6 は、実施例に係るプログラム可能電流ゲイン回路 308 を示すブロック図である。

10

プログラム可能電流ゲイン回路 308 は、複数の電流ゲインセル 608 を含む。この実施例では、プログラム可能電流ゲイン回路 308 は、10 個の電流ゲインセル 608<sub>1</sub> ~ 608<sub>10</sub> を含む。他の実施例では、プログラム可能電流ゲイン回路 308 は、より多くの電流ゲインセル 608 を含んでもよく、より少ない電流ゲインセル 608 を含んでもよい。各電流ゲインセル 608 は、差動入力 (Vin\_p および Vin\_n) と差動出力 (Vout\_n および Vout\_p) とを含む。各電流ゲインセル 608 の差動入力は、差動入力 328\_p および 328\_N に結合される。各電流ゲインセル 608 の差動出力は、差動出力 330\_p および 330\_N に結合される。

#### 【0072】

各電流ゲインセル 608 は、プログラム可能電流源 312 のそれぞれの 1 つ以上の分岐をイネーブルにするための 1 つ以上のイネーブル入力を含む。この実施例では、各電流ゲインセル 608 は、En<1> および En<2> と記載される 2 つのイネーブル入力を含む。電流ゲインセル 608<sub>1</sub> がそれぞれのビット AGC<30> および AGC<31> を受信するように結合されるまで、電流ゲインセル 608<sub>1</sub> のイネーブル入力 En<1> および En<2> は、AGC 符号 400 のそれぞれのビット AGC<M+1> および AGC<M+3> を受信するように結合され、電流ゲインセル 608<sub>2</sub> のイネーブル入力 En<1> および En<2> は、それぞれのビット AGC<M+5> および AGC<M+7> を受信するように結合される、などである。

#### 【0073】

図 6 に示されるプログラム可能電流ゲイン回路 308 の例は、図 4B に示される例的な AGC 符号 400 に対応する。図 4B に示されるように、AGC 符号 400 は、プログラム可能電流源 312 の分岐を制御するように構成された 20 個のビットを含む。図 6 の実施例では、プログラム可能電流ゲイン回路 308 は、10 個の電流ゲインセルを含み、当該 10 個の電流ゲインセルの各々は、プログラム可能電流源 312 の 20 個の分岐をそれぞれ制御するための合計 20 個のイネーブル入力のために 2 個のイネーブル入力を有する。イネーブルにされるプログラム可能電流源 312 の 2 個の分岐ごとに 1 個の電流ゲインセル 608 がイネーブルにされる。他の実施例では、10 個よりも多くの電流ゲインセルがあってもよく、10 個よりも少ない電流ゲインセルがあってもよい。さらに、他の実施例では、各電流ゲインセル 608 は、より多くのイネーブル入力を有してもよく、より少ないイネーブル入力を有してもよい。

#### 【0074】

図 7 は、実施例に係るブリーダ回路 314 を示すブロック図である。ブリーダ回路 314 は、バイアス電圧を受信するように結合された入力 (Vin) を含む。ブリーダ回路 314 は、差動出力 330\_N および 330\_P に結合された差動出力 (Vout\_n, Vout\_p) を含む。ブリーダ回路 314 は、複数のイネーブル入力 En<1> ~ En<K> を含み、K は、プログラム可能電流源 312 を制御する AGC 符号 400 におけるビットの数に等しい。図 4B の実施例では、AGC 符号 400 は、プログラム可能電流源 312 を制御するように構成された 20 個のビットを含むため、当該実施例では、K = 20 である。イネーブル入力の各々は、AGC 符号 400 のビットの論理的補完物を受信するように構成される。具体的には、イネーブル入力 En<K> (K = 20) が AGC<31> の論理

10

20

30

40

50

的補完物を受信するまで、イネーブル入力  $E_{n < 1 >}$  は A G C  $< M + 1 >$  の論理的補完物を受信し、イネーブル入力  $E_{n < 2 >}$  は A G C  $< M + 3 >$  の論理的補完物を受信する、などである。各々のイネーブル入力は、プログラム可能電流源 3 1 6 の分岐をイネーブルにするように構成される。

#### 【 0 0 7 5 】

動作時、プログラム可能電流源 3 1 6 は、プログラム可能電流源 3 1 2 と同数の分岐を含む。プログラム可能電流源 3 1 6 の分岐は、イネーブルにされるプログラム可能電流源 3 1 2 の各分岐についてディスエーブルにされる。図 4 A の実施例では、A G C 符号 0 ~ M までは、全ての電流ゲインセル 6 0 8 がオフであり（イネーブルにされるプログラム可能電流源 3 1 2 の分岐はない）、プログラム可能電流源 3 1 6 の分岐は全てオンである。A G C 符号 M + 1 ~ 3 1 までは、プログラム可能電流源 3 1 6 の分岐が各符号についてディスエーブルにされる。このように、A G C 回路 2 0 6 によって引き込まれる合計 D C 電流は一定のままであり、固定された共通モードをもたらす。A G C 回路 2 0 6 によって引き込まれる合計 D C 電流が一定である場合、A G C 回路 2 0 6 のゲインに影響を及ぼすバイアス電流は、電流ゲインセル 6 0 8 をイネーブルにしたりディスエーブルにしたりすることにより A G C 符号とともに変化する。これは、ブリーダ回路 3 1 4 が、入力信号 V\_I N に結合されるのではなく、別々の入力バイアス信号を受信するように結合されるからである。したがって、ブリーダ回路 3 1 4 によって引き込まれる電流は、共通モードにのみ影響を及ぼし、信号ゲインには影響を及ぼさない。

#### 【 0 0 7 6 】

図 8 A ~ 図 8 D は、電流ゲインセル 6 0 8 の一例を示す概略図である。図 8 A に示されるように、電流ゲインセル 6 0 8 は、トランジスタ 8 0 6<sub>1</sub> とトランジスタ 8 0 6<sub>2</sub> とを備えるトランジスタ対 8 0 6 を含む。トランジスタ 8 0 6<sub>1</sub> および 8 0 6<sub>2</sub> は、N チャネル F E T (たとえば、N 型 M O S F E T ) を備える。トランジスタ 8 0 6<sub>1</sub> および 8 0 6<sub>2</sub> のドレインは、出力 3 3 0<sub>N</sub> および 3 3 0<sub>P</sub> にそれぞれ結合される。トランジスタ 8 0 6<sub>1</sub> および 8 0 6<sub>2</sub> のゲートは、入力 3 2 8<sub>P</sub> および 3 2 8<sub>N</sub> にそれぞれ結合される。

#### 【 0 0 7 7 】

図 8 A の実施例では、電流ゲインセル 6 0 8 は、プログラム可能ソースデジエネレーション抵抗 3 1 0 の分岐 8 1 4<sub>1</sub> および 8 1 4<sub>2</sub> を含む。各分岐 8 1 4<sub>1</sub> は、直列に結合された抵抗器 8 1 0<sub>1</sub>、トランジスタ 8 1 2 および抵抗器 8 1 0<sub>2</sub> を含む。分岐 8 1 4<sub>2</sub> は、トランジスタ 8 0 6<sub>1</sub> のソースとトランジスタ 8 0 6<sub>2</sub> のソースとの間に並列に結合される。分岐 8 1 4<sub>1</sub> におけるトランジスタ 8 1 2 のゲートは、イネーブル信号  $E_{n < 1 >}$  を受信し、分岐 8 1 4<sub>2</sub> におけるトランジスタ 8 1 2 のゲートは、イネーブル信号  $E_{n < 2 >}$  を受信する。

#### 【 0 0 7 8 】

図 8 A の実施例では、電流ゲインセル 6 0 8 は、分岐 8 0 2 および分岐 8 0 4 と記載されるプログラム可能電流源 3 1 2 の 2 つの分岐を含む。分岐 8 0 2 は、イネーブル信号  $E_{n < 1 >}$  によってイネーブルにされ、分岐 8 0 4 は、イネーブル信号  $E_{n < 2 >}$  によってイネーブルにされる。分岐 8 0 2 は、トランジスタ 8 0 6<sub>1</sub> のソースと基準電圧との間に結合された電流源 8 0 2<sub>1</sub> と、トランジスタ 8 0 6<sub>2</sub> のソースと基準電圧との間に結合された電流源 8 0 2<sub>2</sub> とを含む。分岐 8 0 4 は、電流源 8 0 2<sub>1</sub> と並列の電流源 8 0 4<sub>1</sub> と、電流源 8 0 2<sub>2</sub> と並列の電流源 8 0 4<sub>2</sub> とを含む。

#### 【 0 0 7 9 】

動作時、イネーブル信号が両方とも未設定であれば、電流ゲインセル 6 0 8 はディスエーブルにされる。イネーブル信号  $E_{n < 1 >}$  が設定されると、プログラム可能電流源 3 1 2 の分岐 8 0 2 およびプログラム可能ソースデジエネレーション抵抗 3 1 0 の分岐 8 1 4<sub>1</sub> がイネーブルにされる。イネーブル信号  $E_{n < 1 >}$  および  $E_{n < 2 >}$  が両方とも設定されると、プログラム可能電流源 3 1 2 の両方の分岐 8 0 2 および 8 0 4、ならびに、プログラム可能ソースデジエネレーション抵抗 3 1 0 の両方の分岐 8 1 4<sub>1</sub> および 8 1 4<sub>2</sub> がイネーブルにされる。イネーブルにされると、電流ゲインセル 6 0 8 は、バイアス電流を

10

20

30

40

50

増加させて入力トランジスタサイズを事実上増加させる（すなわち、G<sub>m</sub>を増加させる）ことによってゲインを増加させる。電流ゲインセル608のゲインは、ベース電流ゲイン回路302のゲインに線形に追加される。電流ゲインセル608をオンにすることは、バイアス電流および増幅器回路の入力トランジスタの有効幅を増加させることと同様である。

#### 【0080】

図8Aの要素と同一または同様の図8Bにおける要素は、同一の参照番号で示されている。図8Bの実施例では、Nチャネルトランジスタは、Pチャネルトランジスタ（たとえば、P型MOSFET）と置き換えられている。すなわち、電流ゲインセル608は、上記のトランジスタ806<sub>1</sub>および806<sub>2</sub>と同様に構成されたトランジスタ820<sub>1</sub>および820<sub>2</sub>を含む。プログラム可能電流源312の分岐802および804は、トランジスタ820<sub>1</sub>および820<sub>2</sub>のソースと電圧供給518との間に結合される。図8Bに示される電流ゲインセル608は、上記と同様に動作する。

10

#### 【0081】

図8Aの要素と同一または同様の図8Cにおける要素は、同一の参照番号で示されている。図8Cの実施例では、プログラム可能ソースデジエネレーション抵抗310は省略されている。トランジスタ806<sub>1</sub>のソースおよびトランジスタ806<sub>2</sub>のソースは、結合されている。プログラム可能電流源312の分岐802および804は、トランジスタ806<sub>1</sub>および806<sub>2</sub>のソースと基準電圧との間に並列に結合される。図8Cに示される電流ゲインセル608は、上記と同様に動作するが、ソースデジエネレーション抵抗を持たない。

20

#### 【0082】

図8Bの要素と同一または同様の図8Dにおける要素は、同一の参照番号で示されている。図8Dの実施例では、プログラム可能ソースデジエネレーション抵抗310は省略されている。トランジスタ820<sub>1</sub>のソースおよびトランジスタ820<sub>2</sub>のソースは、結合されている。プログラム可能電流源312の分岐802および804は、トランジスタ820<sub>1</sub>および820<sub>2</sub>のソースと供給電圧518との間に並列に結合される。図8Dに示される電流ゲインセル608は、上記と同様に動作するが、ソースデジエネレーション抵抗を持たない。

#### 【0083】

30

図9Aは、実施例に係るブリーダ回路314を示す概略図である。ブリーダ回路314は、トランジスタ906<sub>1</sub>とトランジスタ906<sub>2</sub>とを備えるトランジスタ対906を含む。トランジスタ906<sub>1</sub>および906<sub>2</sub>のドレインは、出力330<sub>N</sub>および330<sub>P</sub>にそれぞれ結合される。トランジスタ906<sub>1</sub>および906<sub>2</sub>のゲートは、バイアス電圧V<sub>in</sub>を受信するように結合される。プログラム可能電流源316は、K個のイネーブル信号E<sub>n<1></sub>～E<sub>n<K></sub>にそれぞれ対応するK個の分岐902<sub>1</sub>～902<sub>K</sub>を含む。各分岐は、一対の電流源（AおよびBと表記）を含む。したがって、分岐902<sub>K</sub>が電流源902A<sub>K</sub>と902B<sub>K</sub>とを含むまで、分岐902<sub>1</sub>は電流源902A<sub>1</sub>と902B<sub>1</sub>とを含み、分岐902<sub>2</sub>は電流源902A<sub>2</sub>と902B<sub>2</sub>とを含む、などである。電流源902Aは、トランジスタ906<sub>1</sub>のソースと基準電圧との間に結合される。電流源902Bは、トランジスタ906<sub>2</sub>のソースと基準電圧との間に結合される。電流源902Aは並列に結合され、電流源902Bは並列に結合される。ブリーダ回路314の動作については、すでに説明している。図9は、ブリーダ回路314の一例を示しているに過ぎない。ブリーダ回路314は、さまざまな構成を有してもよい。一般に、ブリーダ回路314は、各々がプログラム可能電流源316の1つ以上の分岐を有する1つ以上のセルを含む。各セルは、図9に示されるNチャネルトランジスタを用いて構成されてもよく、図8Bおよび図8Dに示される電流ゲインセル608と同様の構成のPチャネルトランジスタを用いて構成されてもよい。

40

#### 【0084】

図9Bは、別の実施例に係るブリーダ回路314を示す概略図である。図9Aの要素と

50

同一または同様の要素は、同一の参照番号で示されており、すでに説明している。この実施例では、Nチャネルトランジスタ906は、Pチャネルトランジスタ920（たとえば、P型MOSFET）と置き換えられている。すなわち、ブリーダ回路314は、Nチャネルトランジスタ906<sub>1</sub>およびNチャネルトランジスタ906<sub>2</sub>の代わりに、Pチャネルトランジスタ920<sub>1</sub>とPチャネルトランジスタ920<sub>2</sub>とを含む。電流源902は、供給電圧518とPチャネルトランジスタ920のソースとの間に結合される。

#### 【0085】

図10は、実施例に係るオートゲインコントロール方法1000を示すフロー図である。方法1000は、上記のAGC回路206によって実行可能であり、上記の動作を要約している。方法1000は、ステップ1002から開始し、ステップ1002において、ベース電流ゲイン回路302とプログラム可能電流ゲイン回路308とブリーダ回路314とを有するAGC回路206を制御するためのAGC符号語を生成するようにデコーダ320が制御される。例示的なAGC符号語は、上記の図4Aおよび図4Bに示されている。

10

#### 【0086】

ステップ1004において、AGC符号語の第1のビットにベース電流ゲイン回路のプログラム可能ソースデジエネレーション抵抗304を制御せしめるようにデコーダ320が制御される。図4Aの実施例では、ステップ1004において言及される第1のビットは、第1の部分402内の全てのビットおよび第2の部分404内のいくつかのビットを備える。図4Bの実施例では、ステップ1004において言及される第1のビットは、AGC<4:1>およびAGC<6>、AGC<8>...AGC<18>を備える。

20

#### 【0087】

ステップ1006において、AGC符号語の第2のビットにプログラム可能電流ゲイン回路308のプログラム可能電流源312を制御せしめるようにデコーダ320が制御される。図4Aの実施例では、ステップ1006において言及される第2のビットは、第3の部分406内の全てのビットおよび第2の部分404内のいくつかのビットを備える。図4Bの実施例では、ステップ1006において言及される第2のビットは、AGC<31:19>およびAGC<5>、AGC<7>...AGC<17>を備える。

#### 【0088】

ステップ1008において、ブリーダ回路314のデコーダ320は、AGC符号語の第2のビットを論理的に補完して、プログラム可能電流源316を制御する。

30

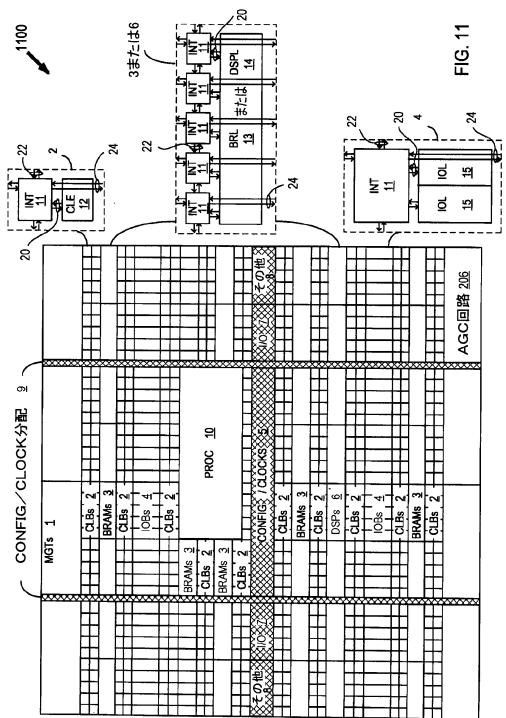

#### 【0089】

本明細書に記載されているAGC回路206は、フィールドプログラマブルゲートアレイ(FPGA)などのICまたは他のタイプのプログラマブルICに配置された直列受信機または送受信機で用いられる。図11は、FPGA1100のアーキテクチャを示し、FPGA1100は、多数の異なるプログラム可能タイルを含み、当該プログラム可能タイルは、マルチギガビット送受信機(「MGT」)1と、コンフィギュラブル論理ブロック(「CLB」)2と、ランダムアクセスメモリブロック(「RAM」)3と、入力/出力ブロック(「IOB」)4と、コンフィギュレーションおよびクロッキング論理(「CONFIG/CLKS」)5と、デジタル信号処理ブロック(「DSP」)6と、専門入力/出力ブロック(「I/O」)7(たとえば、コンフィギュレーションポートおよびクロックポート)と、デジタルクロックマネージャ、アナログデジタル変換器、システムモニタリング論理などの他のプログラム可能論理8とを含む。いくつかのFPGAは、専用プロセッサブロック(「PROC」)10も含む。

40

#### 【0090】

いくつかのFPGAでは、各々のプログラム可能タイルは、図11の上部に含まれる例によって示されるように、同一のタイル内でプログラム可能論理要素の入力および出力端子20に対する接続を有する少なくとも1つのプログラム可能相互接続要素(「INT」)11を含み得る。各々のプログラム可能相互接続要素11は、同一のタイルまたは他のタイルにおける隣接するプログラム可能相互接続要素の相互接続セグメント22に対する

50

接続も含み得る。各々のプログラム可能相互接続要素 11 は、論路ブロック（図示せず）間の一般的なルーティングリソースの相互接続セグメント 24 に対する接続も含み得る。一般的なルーティングリソースは、相互接続セグメント（たとえば、相互接続セグメント 24）のトラックを備える論理ブロック（図示せず）と相互接続セグメントを接続するためのスイッチブロック（図示せず）との間にルーティングチャネルを含み得る。一般的なルーティングリソースの相互接続セグメント（たとえば、相互接続セグメント 24）は、1 つ以上の論理ブロックにまたがっていてもよい。プログラム可能相互接続要素 11 は、一般的なルーティングリソースとともに、示されている F P G A のためのプログラム可能相互接続構造（「プログラム可能相互接続」）を実現する。

## 【0091】

10

例示的な実現例では、C L B 2 は、ユーザ論理 + 単一のプログラム可能相互接続要素（「I N T」）11 を実現するようにプログラム可能なコンフィギュラブル論理要素（「C L E」）12 を含み得る。B R A M 3 は、1 つ以上のプログラム可能相互接続要素に加えて、B R A M 論理要素（「B R L」）13 を含み得る。一般に、タイルに含まれる相互接続要素の数は、タイルの高さによって決まる。示されている実施例では、B R A M タイルは、5 個の C L B と同一の高さを有しているが、他の数（たとえば、4 個）も用いられてもよい。D S P タイル 6 は、適切な数のプログラム可能相互接続要素に加えて、D S P 論理要素（「D S P L」）14 を含み得る。I O B 4 は、たとえば、プログラム可能相互接続要素 11 の 1 つのインスタンスに加えて、入力 / 出力論理要素（「I O L」）15 の 2 つのインスタンスを含み得る。当業者に明らかであるように、たとえば I / O 論理要素 15 に接続される実際の I / O パッドは、一般に、入力 / 出力論理要素 15 の領域に限定されない。

20

## 【0092】

示されている実施例では、（図 11 に示される）ダイの中心付近の水平な領域がコンフィギュレーション、クロックおよび他の制御論理に用いられる。この水平な領域または列から延在する垂直な列 9 は、F P G A の幅にわたってクロックおよびコンフィギュレーション信号を分散させることに用いられる。

## 【0093】

30

図 11 に示されるアーキテクチャを利用するいくつかの F P G A は、F P G A の大部分を構成する規則的な列構造を乱すさらなる論理ブロックを含む。当該さらなる論理ブロックは、プログラム可能ブロックおよび / または専用論理であってもよい。たとえば、プロセッサブロック 10 は、C L B および B R A M のいくつかの列にまたがっている。プロセッサブロック 10 は、単一のマイクロプロセッサから、マイクロプロセッサ、メモリコントローラ、周辺装置などの完全なプログラム可能処理システムまでのさまざまなコンポーネントを含み得る。

## 【0094】

なお、図 11 は、例示的な F P G A アーキテクチャを示すように意図されているに過ぎない。たとえば、一行の中の論理ブロックの数、行の相対幅、行の数および順序、行に含まれる論理ブロックのタイプ、論理ブロックの相対的サイズ、ならびに、図 11 の上部に含まれる相互接続 / 論理実現例は、単なる例示に過ぎない。たとえば、実際の F P G A では、一般に、2 つ以上の隣接する C L B 行が、C L B が現れるたびに含まれ、ユーザ論理の効率的な実現を容易にするが、隣接する C L B 行の数は、F P G A の全体サイズによって変わる。

40

## 【0095】

線形インターリーブ A G C 回路を提供するための技術について説明してきた。当該設計は、平坦な周波数応答を有する広いダイナミックレンジを実現する。広いダイナミックレンジは、ベース電流ゲイン回路 302 の電流源およびトランジスタ対に対して、ならびに最低 A G C ゲイン符号に対して、小さなバイアス電流および小さなトランジスタサイズを用いることによって、実現される。A G C ゲイン符号が大きくなると、より多くのバイアス電流がイネーブルにされ、より多くのトランジスタが入力に結合されて、入力トランジ

50

スタの有効幅を増大させる。したがって、最小のゲインを実現するために必要な実効デジエネレーション抵抗は大きくなくともよく、抵抗器アレイ配線からの入力トランジスタによる寄生キャパシタンスは大きくない。これは、目標帯域幅の範囲外であり、かつ、パラメータM、nおよびプログラム可能電流ゲイン回路308における電流ゲインセル608の数を調節することによって常に帯域幅の範囲外に保つことができる高周波数ゼロにつながる。さらに、A G C回路設計は、ベースとプログラム可能回路との間のインターリービングにより、全てのゲイン符号にわたって線形性を実現する。ゲイン符号が増加するにつれて、より多くのバイアス電流が追加され、制限された振幅によって信号がクリップされることのないようにゲインとともに振幅を増加させる。当該設計は、A G Cゲイン符号によって制御されて、D C電流源を自動的にオン／オフにして、全てのA G C符号について出力共通モードが確実に一定になるようにするブリーダ回路314を用いることによって、一定の出力共通モードを実現する。

10

#### 【0096】

上記のA G C回路206は、いくつかの変形例を含み得る。上記の実施例では、単調な挙動を確実にするために、ゲインは、A G C符号を増加させるように常に追加され、差し引かれる事はない。各々のA G C符号の増加は、ベース内の抵抗器分岐をオンにするか、または電流ゲインセルをイネーブルにし、これらは両方ともゲインを常に増加させる。しかし、符号当たりのゲインステップサイズを小さくするために、プログラム可能電流ゲイン回路308における電流ゲインセルをイネーブルにすることによってゲインをベースから差し引いて追加してもよく、その結果、2つの間の差が事実上のゲイン増加である。

20たとえば、プログラム可能電流ゲイン回路308における所与の電流ゲインセル608がイネーブルにされると、プログラム可能ソースデジエネレーション抵抗304における抵抗器分岐はディスエーブルにされてもよい。差し引かれるゲインが追加されるゲインよりも常に小さい場合、ゲインは、依然としてA G C符号で単調であろう。

#### 【0097】

別の実施例では、ベース電流ゲイン回路302における電流源306は、さらに小さなゲイン符号でのさらに一層の線形性のために大きくされてもよい。合計バイアス電流が高くなり過ぎないように、プログラム可能電流ゲイン回路308における電流ゲインセルがイネーブルにされると、電流源306によって提供されるベース電流のうちの一部がオフにされ得る。これは、合計ゲインがA G C符号の増加とともに増加するようにいくらかのゲインがプログラム可能電流ゲイン回路308によってベース電流ゲイン回路302から差し引かれて追加される上記のアプローチと同様である。このような変形例では、電流源306は、固定式ではなくプログラム可能であり得る。

30

#### 【0098】

別の実施例では、ベース電流ゲイン回路302における電流源306は、プログラム可能であってもよく、プログラム可能ソースデジエネレーション抵抗304の分岐とともに調整されてもよい。すなわち、プログラム可能ソースデジエネレーション抵抗304の分岐がイネーブル／ディスエーブルにされると、電流源306の分岐はイネーブル／ディスエーブルにされてもよい。

#### 【0099】

さらに、上記のように、プログラム可能ソースデジエネレーション抵抗304における分岐の数、A G C符号ステップの数、電流ゲインセル608の数、プログラム可能電流源312の分岐の数、および電流ゲインセル608当たりのプログラム可能電流源312の分岐の数は、上記の実施例とは異なっていてもよく、具体的な設計要件によって決まってよい。

40

#### 【0100】

上記は具体的な実施例に向けられているが、その基本的範囲から逸脱することなく他のおよびさらなる実施例が考案されてもよく、その範囲は以下の特許請求の範囲によって決定される。

【 図 1 】

FIG. 1

【 図 2 】

FIG. 2

【 四 3 】

FIG. 3

【図4A】

FIG. 4A

【 図 4 B 】

FIG. 4B

【図 5 A】

FIG. 5A

【図 5 B】

FIG. 5B

【図 6】

FIG. 6

【図 7】

FIG. 7

【図 8 A】

FIG. 8A

【図 8 B】

【図 8 D】

【図 8 C】

【図 9 A】

【図 9 B】

【図 10】

FIG. 10

【図 1 1】

---

フロントページの続き

(72)発明者 ウパディアヤ , パラグ

アメリカ合衆国、95124 カリフォルニア州、サン・ノゼ、ロジック・ドライブ、2100

(72)発明者 チャン , クン - ユン

アメリカ合衆国、95124 カリフォルニア州、サン・ノゼ、ロジック・ドライブ、2100

審査官 及川 尚人

(56)参考文献 米国特許出願公開第2011/0298542(US, A1)

国際公開第2014/136170(WO, A1)

米国特許出願公開第2006/0244530(US, A1)

米国特許出願公開第2010/0315164(US, A1)

特開2004-159221(JP, A)

米国特許出願公開第2005/0225390(US, A1)

米国特許第07583144(US, B1)

米国特許出願公開第2014/0225669(US, A1)

特開2013-247421(JP, A)

米国特許第07321259(US, B1)

(58)調査した分野(Int.Cl., DB名)

H03G 3/20

H03G 3/30