(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5339928号

(P5339928)

(45) 発行日 平成25年11月13日(2013.11.13)

(24) 登録日 平成25年8月16日(2013.8.16)

(51) Int.Cl.

F 1

H05K 1/02 (2006.01)

H05K 3/46 (2006.01)H05K 1/02

H05K 3/46

H05K 3/46E

Z

B

請求項の数 9 (全 15 頁)

(21) 出願番号

特願2009-6894 (P2009-6894)

(22) 出願日

平成21年1月15日 (2009.1.15)

(65) 公開番号

特開2010-165855 (P2010-165855A)

(43) 公開日

平成22年7月29日 (2010.7.29)

審査請求日

平成23年12月20日 (2011.12.20)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者 堀内 章夫

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 宮坂 俊次

長野県長野市小島田町80番地 新光電氣

工業株式会社内

審査官 中田 誠二郎

最終頁に続く

(54) 【発明の名称】配線基板及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の配線層が樹脂からなる絶縁層を介在させて積層され、各絶縁層に形成されたピアを介して層間接続された構造を有する配線基板であって、

前記配線基板の一方の面となる絶縁層と、

前記配線基板の配線形成領域の前記一方の面となる絶縁層に側面が埋め込まれたパッドであって、前記パッドの表面が前記絶縁層の表面と同一面に露出する前記パッドと、

前記配線形成領域の周辺領域の前記一方の面となる絶縁層に埋め込まれ、前記パッドと同一の導体層から形成された補強パターンであって、前記補強パターンの表面が前記絶縁層の表面と同一面に露出し、かつ平面視したときに断続したリング状に設けられた前記補強パターンと、

前記パッドの裏面に接続されたピアと、

前記ピアを介して前記パッドに接続された配線層とを有し、

前記パッド及び前記補強パターンは表面に金層を含み、前記金層が前記絶縁層から露出していることを特徴とする配線基板。

## 【請求項 2】

前記配線層は所要の層数で積層されており、

前記配線層の周辺領域に、前記配線層と同一層から形成された補強パターンが配置されていることを特徴とする請求項 1 に記載の配線基板。

## 【請求項 3】

前記配線基板の他方の面となる絶縁層に形成された前記配線層のパッド部分を露出させてソルダレジスト層が設けられ、

該ソルダレジスト層で覆われた前記配線層を除いた他の各配線層にそれぞれ対応させて前記補強パターンが設けられていることを特徴とする請求項2に記載の配線基板。

**【請求項4】**

前記ソルダレジスト層は、その端部が前記配線基板の周縁部から後退した位置となるよう設けられていることを特徴とする請求項3に記載の配線基板。

**【請求項5】**

支持基材上の配線形成領域に最下に金層を含むパッドを形成すると共に、前記配線形成領域の周辺領域に、前記パッドと同一の導体層からなる補強パターンを、平面視して断続したリング状に配置されるように形成する工程と、

10

前記支持基材の上に、前記パッド及び補強パターンを被覆する絶縁層を形成する工程と、

前記絶縁層に、前記パッドに到達するビアホールを形成する工程と、

前記ビアホールを介して前記パッドに接続される配線層を前記絶縁層の上に形成する工程と、

前記支持基材を除去する工程とを有することを特徴とする配線基板の製造方法。

**【請求項6】**

前記支持基板上に前記パッド及び補強パターンを形成する工程は、

前記支持基材上に、前記配線形成領域及び前記周辺領域に対応する部分にそれぞれ開口部を有するレジスト層を形成する工程と、

20

前記レジスト層の各開口部から露出している前記支持基材上に、電解めっきにより、前記パッド及び補強パターンを形成することを含むことを特徴とする請求項5に記載の配線基板の製造方法。

**【請求項7】**

前記配線層を形成する工程は、

前記ビアホールの内部を含めて前記絶縁層上にシード層を形成する工程と、

前記ビアホールを含む領域に開口部が設けられたレジスト膜を形成する工程と、

前記シード層を給電層とする電解めっきにより、前記ビアホール及び前記開口部に導体パターンを形成する工程と、

30

前記レジスト膜を除去する工程と、

前記導体パターンをマスクにして前記シード層をエッチングする工程と

を含むことを特徴とする請求項5又は6に記載の配線基板の製造方法。

**【請求項8】**

前記配線層は所要の層数で積層され、

前記支持基材を除去する前に、最外層の前記配線層のパッド部分を露出させてソルダレジスト層を形成する工程を有し、

前記ソルダレジスト層で覆われた配線層を除いた他の各配線層にそれぞれ対応させて補強パターンを形成することを特徴とする請求項5に記載の配線基板の製造方法。

**【請求項9】**

前記ソルダレジスト層は、その端部が前記配線基板の周縁部から後退した位置となるよう形成されることを特徴とする請求項8に記載の配線基板の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体素子等の電子部品を搭載するのに用いられる配線基板に関し、より詳細には、複数の配線層が絶縁層を介在させて積層され、各絶縁層に形成されたビアを介して層間接続された構造を有する配線基板及びその製造方法に関する。

**【0002】**

かかる配線基板は、半導体素子等を搭載するパッケージとしての機能を果たすという点

40

で、以下の記述では便宜上、「半導体パッケージ」ともいう。

【背景技術】

【0003】

多層構造の配線基板を製造する技術として、ビルトアップ法が広く用いられている。このビルトアップ法を用いた多層配線基板は、層間絶縁層の材料（代表的には、樹脂）とビアホール形成プロセスの組合せにより多種類のものが作製可能であり、その典型的な製造プロセスは、支持基材としてのコア基板を中心としてその両面もしくは一方の面に、絶縁層の形成、絶縁層におけるビアホールの形成、ビアホールの内部への導体充填（ビア）を含めた配線層の形成を順次繰り返して積み上げていくものである。かかる構造では、配線層と絶縁層の部分はビルトアップ法で積層しているので薄く形成することができるが、コア基板の部分は配線基板に剛性をもたらすために相応の厚さを必要とし、半導体パッケージ全体としての薄型化に限界があった。10

【0004】

そのため、最近では、配線基板（半導体パッケージ）の更なる薄型化を図るべく、コア基板（支持基材）を除去した構造が採用されている。かかる構造の配線基板は、「コア」の部分が無いという意味で、「コアレス基板」とも呼ばれている。かかるコアレス基板の製造方法については後で説明するが、その基本的なプロセスは、支持体としての仮基板を用意し、この仮基板上に所要数のビルトアップ層（ビアホールを含む絶縁層、ビアホールの内部（ビア）を含めた配線層）を順次形成した後、仮基板（支持体）を除去するものである。20

【0005】

このように薄型基板（コアレス基板）のプロセスは、従来の厚型基板（コア有り基板）のプロセスと比べて、支持基材を最終的に除去するか、コアとしてそのまま残しておくかの違いはあるにせよ、配線層の形成方法については基本的に同じである。つまり、配線パターンの幅やその配設間隔（ピッチ）、配線基板に占める配線部（配線形成領域）の大きさなどが同じデザインルールの下に決定され、それに基づいて配線設計がなされていた。このため、基板端部（配線基板の周縁部）から配線部（配線形成領域）までの距離についても同じ設計がされている。現状の技術では、その距離（配線が形成されていない部分）は、例えば 500 μm 程度に設計されている。30

【0006】

かかる従来技術に関連する技術としては、例えば、特許文献 1 に記載されるように、半導体装置用多層基板において、半導体素子が搭載される搭載面を可及的に平坦に形成し、且つ厚さを可及的に薄く形成し得るようにしたものがある。この文献に開示されている多層基板は、導体配線が絶縁層を介して多層に形成されており、その多層基板の一面側が、搭載される半導体素子の電極端子と接続される半導体素子用パッドが形成された半導体素子搭載面であり、且つ当該多層基板の他面側が、外部接続端子用パッドが形成された外部接続端子装着面であり、上記絶縁層の両面に形成された導体配線及び／又はパッドを電気的に接続するビアが、絶縁層を貫通して形成され、且つ当該絶縁層の外部接続端子装着面側に開口されていると共に、半導体素子搭載面側に形成された導体配線又はパッドの外部接続端子装着面側の内面に底面が形成された、開口面積が底面面積よりも大の円錐台状の凹部に形成されている。40

【0007】

また、これに関連する他の技術として、特許文献 2 に記載されたコアレス基板の製造方法がある。ここに開示されている方法では、プリプレグ上の配線形成領域に下地層が配置され、この下地層より大きな金属箔が配線形成領域の外周部に接するように、下地層を介して金属箔をプリプレグ上に配置し、加熱・加圧によってプリプレグを硬化させることにより、仮基板を得るとともに、仮基板に金属箔を接着している。さらに、その金属箔上にビルトアップ配線層を形成し、その構造体の下地層の周縁部分を切断することにより、仮基板から金属箔を分離して、当該金属箔上にビルトアップ配線層が形成された配線部材を得るようにしている。また、特許文献 3 には、絶縁層に配線基板本体の反りを低減する部50

材を内設した配線基板が開示されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2000-323613号公報

【特許文献2】特開2007-158174号公報

【特許文献3】特開2009-123874号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

上述したように従来のコアレス基板（半導体パッケージ）では、コア基板を不要とするので薄型化という点では有利であるが、その反面、コア基板がないためにパッケージ全体の剛性が小さく、外部からの機械的な応力（衝撃）に対して脆弱な構造となっている。このため、特に基板の端部が欠け易いといった問題があった。

【0010】

つまり、従来のコアレス基板（半導体パッケージ）の構造では、パッケージ全体の剛性が小さいことに起因して、外部から機械的な応力もしくは衝撃が加わったときに基板の端部に「欠け」が発生するリスクが高く、また、その「欠け」の程度によっては配線部が露出したりすることも想定される。さらに、パッケージの最外層の絶縁層（ソルダレジスト層）は、その内層側の絶縁層（エポキシ系樹脂等のビルドアップ層）と比べて比較的軟らかいため、外部から機械的な応力等が加わると基板本体から剥離してしまうこと（デラミネーション）もあり得る。

【0011】

このように基板に欠け等が発生すると、製品（パッケージ）としては不良品となる。特に、製造プロセスの途中で外部から何らかの機械的な応力が加わったときに基板端部が欠けた場合、その段階で不良品となるのはもちろん、それまでに費やされた材料や工数等が無駄になってしまい、製造歩留りの低下をきたすといった課題があった。

【0012】

本発明は、かかる従来技術における課題に鑑み創作されたもので、外部からの機械的な応力等に対して基板の欠け等が発生し難い構造を容易に実現することができる配線基板及びその製造方法を提供することを目的とする。

【0013】

さらに本発明は、基板の欠け等が発生し難い構造を、追加的な製造工程を伴うことなく容易に実現可能とし、ひいては製造歩留りの向上に寄与することができる配線基板の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0014】

上記の従来技術の課題を解決するため、本発明の一形態によれば、複数の配線層が樹脂からなる絶縁層を介在させて積層され、各絶縁層に形成されたビアを介して層間接続された構造を有する配線基板であって、前記配線基板の一方の面となる絶縁層と、前記配線基板の配線形成領域の前記一方の面となる絶縁層に側面が埋め込まれたパッドであって、前記パッドの表面が前記絶縁層の表面と同一面に露出する前記パッドと、前記配線形成領域の周辺領域の前記一方の面となる絶縁層に埋め込まれ、前記パッドと同一の導体層から形成された補強パターンであって、前記補強パターンの表面が前記絶縁層の表面と同一面上に露出し、かつ平面視したときに断続したリング状に設けられた前記補強パターンと、前記パッドの裏面に接続されたビアと、前記ビアを介して前記パッドに接続された配線層とを有し、前記パッド及び前記補強パターンは表面に金層を含み、前記金層が前記絶縁層から露出していることを特徴とする配線基板が提供される。

【0015】

また、本発明の他の形態によれば、支持基材上の配線形成領域に最下に金層を含むパッ

10

20

30

40

50

ドを形成すると共に、前記配線形成領域の周辺領域に、前記パッドと同一の導体層からなる補強パターンを、平面視して断続したリング状に配置されるように形成する工程と、前記支持基材の上に、前記パッド及び補強パターンを被覆する絶縁層を形成する工程と、前記絶縁層に、前記パッドに到達するビアホールを形成する工程と、前記ビアホールを介して前記パッドに接続される配線層を前記絶縁層の上に形成する工程と、前記支持基材を除去する工程とを有することを特徴とする配線基板の製造方法が提供される。

#### 【発明の効果】

##### 【0016】

本発明の一形態に係る配線基板の構成によれば、配線形成領域の周辺領域（基板端部の近傍）において当該配線層と同じ面内に補強パターンが設けられているので、配線基板の周辺部分が補強され、基板全体として剛性が高められている。つまり、外部からの機械的な応力もしくは衝撃に対して強い構造となっているので、そのような応力等が加わった場合でも、従来技術に見られたような基板端部の「欠け」の発生を抑制することができる。また、基板端部が欠け難い構造となっているので、配線部が露出したりする可能性も低い。

10

##### 【0017】

本発明の他の形態に係る配線基板の製造方法によれば、上記の形態に係る配線基板で得られた効果（基板の欠け等が発生し難い構造の実現）を、追加的な製造工程を伴うことなく（つまり、従来の製造工程をそのまま利用できるため、基板へのコスト負荷が無い）、容易に実現することができる。

20

##### 【0018】

これにより、製造工程の途中で外部から何らかの機械的な応力等が加わった場合でも、配線基板の周辺近傍に形成された導体層（補強パターン）の存在により、基板端部等の欠けを防止し得るので、不良品とはならず、製造歩留りを向上させることができる。

#### 【図面の簡単な説明】

##### 【0019】

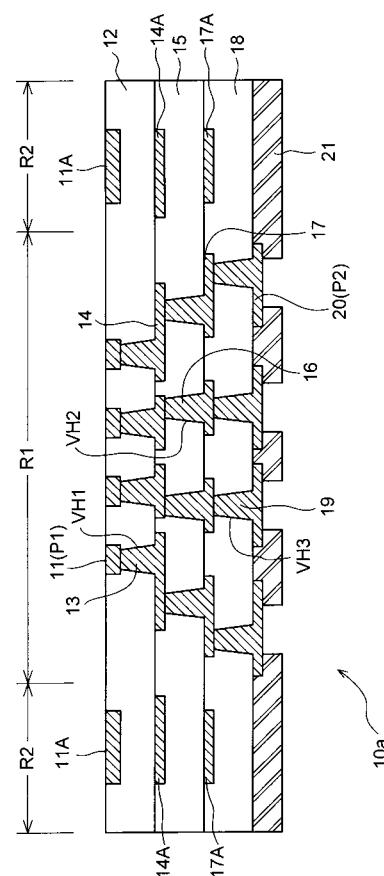

【図1】本発明の一実施形態に係る配線基板（半導体パッケージ）の構成を示す断面図である。

【図2】図1の配線基板をチップ搭載面側から見たときの概略平面図である。

30

【図3】図1の配線基板の製造方法の工程（その1）を示す断面図である。

【図4】図3の製造工程に続く工程（その2）を示す断面図である。

【図5】図1の実施形態の一変形例に係る配線基板の構成を示す断面図である。

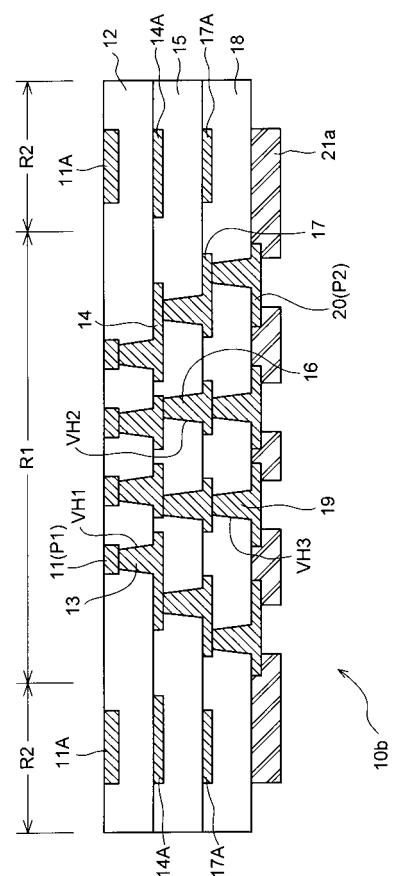

【図6】図1の実施形態の他の変形例に係る配線基板の構成を示す断面図である。

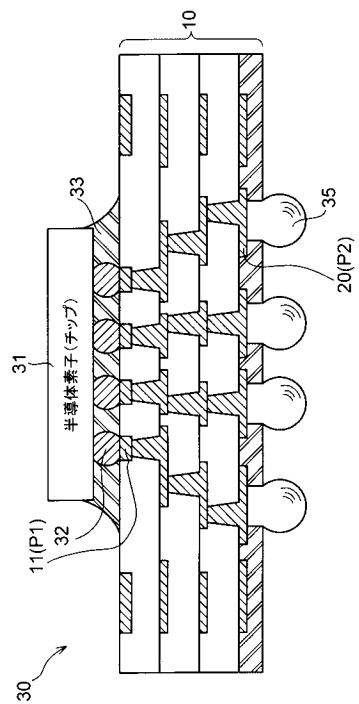

【図7】図1の配線基板にチップを搭載した状態（半導体装置の構成）を示す断面図である。

##### 【0020】

本発明に係る配線基板及びその製造方法の他の構成上の特徴及びそれに基づく有利な利点等については、添付図面を参照しながら以下に記述する発明の実施の形態を用いて説明する。

40

#### 【発明を実施するための形態】

##### 【0021】

以下、本発明の好適な実施の形態について、添付の図面を参照しながら説明する。

##### 【0022】

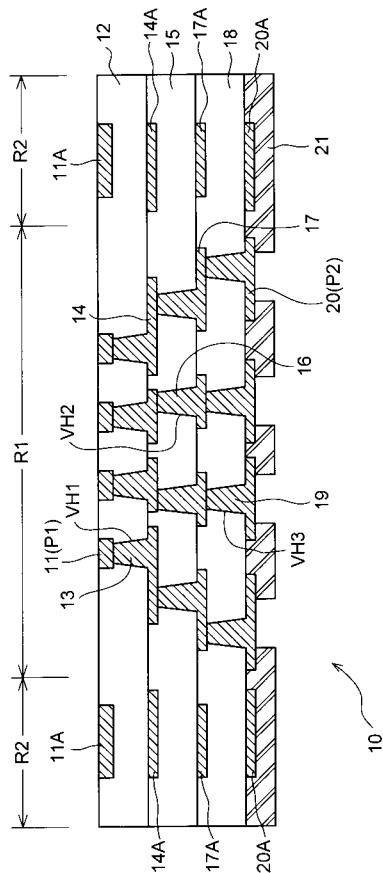

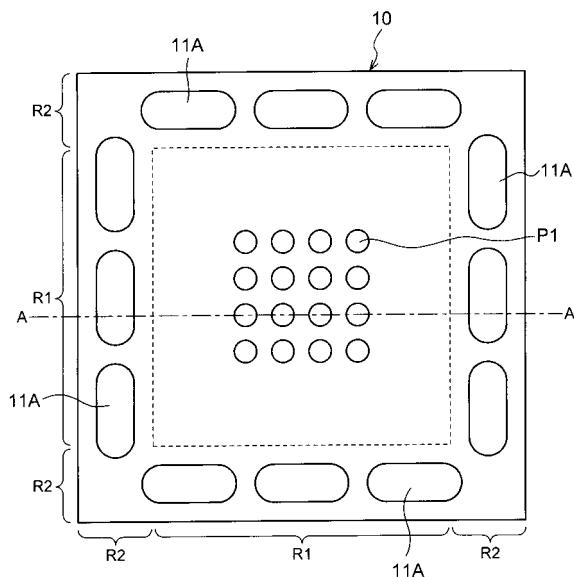

図1は本発明の一実施形態に係る配線基板（半導体パッケージ）の構成を縦断面図の形態で示したものであり、図2はその配線基板10を上側（半導体素子等の電子部品（チップ）を搭載する側）から平面的に見たときの構成を概略的に示したものである。図2の平面図においてA-A線に沿って断面的に見たときの構成が図1の縦断面図である。

##### 【0023】

本実施形態に係る配線基板（半導体パッケージ）10は、図1に示すように、複数の配線層11, 14, 17, 20が絶縁層（具体的には、樹脂層）12, 15, 18を介在さ

50

せて積層され、各絶縁層 1 2 , 1 5 , 1 8 に形成されたビアホール V H 1 , V H 2 , V H 3 にそれぞれ充填された導体（ビア 1 3 , 1 6 , 1 9 ）を介して層間接続された構造を有している。つまり、本パッケージ 1 0 は、一般的なビルトアップ法を用いて作製される配線基板（支持基材としてのコア基板の両面もしくは片面に所要数のビルトアップ層を順次形成して積み上げていくもの）とは違い、支持基材を含まない「コアレス基板」の形態を有している。

#### 【 0 0 2 4 】

このコアレス基板は、図 2 に示すように、チップが搭載される領域に対応する部分に画定された配線形成領域 R 1 （破線で囲んだ部分）とその周囲の周辺領域 R 2 とを有している。本実施形態では、コアレス基板（配線基板 1 0 ）において配線形成領域 R 1 は 1 辺の長さが 2 0 ~ 4 0 mm 程度の矩形（例えば、3 0 mm × 3 0 mm ）、周辺領域 R 2 の幅は 5 0 0 ~ 1 0 0 0 μ m 程度、基板の厚さは 0 . 1 ~ 0 . 5 mm 程度に選定されている。10

#### 【 0 0 2 5 】

このコアレス基板の一方の面側（図 1 の例では上側）の最外層の樹脂層 1 2 には、チップ搭載エリア（配線形成領域 R 1 ）にパッド P 1 （配線層 1 1 の所要の箇所に画定された部分）が配置されている。図 2 の例では、1 6 個のパッド P 1 が配列されている。パッド P 1 は、図 1 に示すように本パッケージ 1 0 の表面と同一面に露出するように設けられており、このパッド P 1 には、本パッケージ 1 0 に搭載される半導体素子等の電子部品（チップ）の電極パッドがはんだバンプ等の導電性部材を介してフリップチップ接続されるようになっている。20

#### 【 0 0 2 6 】

一方、パッド P 1 が形成されている側と反対側の面（図 1 の例では下側）には、保護膜として機能するソルダレジスト層（絶縁層）2 1 が、最外層の配線層（図示の例では配線層 2 0 ）の所要の箇所に画定されたパッド P 2 の部分を露出させてその表面を覆うように形成されている。このパッド P 2 は、ビア 1 9 、配線層 1 7 、ビア 1 6 、配線層 1 4 及びビア 1 3 を介してチップ搭載エリア内のパッド P 1 に接続されている。ソルダレジスト層 2 1 から露出するパッド P 2 には、本パッケージ 1 0 をマザーボード等の実装用基板に実装する際に使用されるはんだボールやピン等の外部接続端子が接合されるようになっている。あるいは、はんだボール等を接合する代わりに、当該パッド P 2 自体を外部接続端子として用いてもよい。30

#### 【 0 0 2 7 】

つまり、本実施形態では、ソルダレジスト層 2 1 が形成されている側の面を「外部接続端子接合面」とし、これと反対側の面（パッケージ 1 0 の表面と同一面に露出するパッド P 1 が形成されている側の面）を「チップ搭載面」として利用している。ただし、本パッケージ 1 0 が使用される条件や配置様態等の使用環境によっては、チップ搭載面と外部接続端子接合面を上下反対の使用形態としてもよい。

#### 【 0 0 2 8 】

また、本パッケージ 1 0 の配線が形成されていない部分（周辺領域 R 2 ）には、本発明を特徴付ける補強パターン 1 1 A , 1 4 A , 1 7 A , 2 0 A が設けられている。各補強パターンは、後述するように本パッケージ 1 0 を作製するプロセスにおいて各配線層 1 1 , 1 4 , 1 7 , 2 0 を形成する際に同時に形成される導体層（配線層と同じ材料からなる）により構成されている。このうち、最上層の配線層 1 1 （パッド P 1 ）に対応する補強パターン 1 1 A は、図 2 に例示するように、平面視したときに断続したリング状の形態で設けられている。図示の例では、パッケージ 1 0 の各辺毎に 3 個ずつ、計 1 2 個の部分に分離された補強パターン 1 1 A が形成されている。他の配線層 1 4 , 1 7 , 2 0 に対応する補強パターン 1 4 A , 1 7 A , 2 0 A についても、最上層の補強パターン 1 1 A と同様のレイアウトで設けられている。40

#### 【 0 0 2 9 】

このように各補強パターン 1 1 A , 1 4 A , 1 7 A , 2 0 A を断続的に設けているのは以下の理由による。すなわち、補強パターンを連続したリング状のパターンにすると、こ50

の補強パターン（導体層）とその周囲の樹脂部との熱膨張係数の違いに起因して応力が特定の方向（そのパターン部分と樹脂部との境界面に直交する方向）に発生するため、その方向に沿って基板に歪みが生じる可能性が高い。特に、その歪みの大きさが一定限度を超えた状態で一定期間にわたり継続されると、その歪んだ状態（部分的な反り）がそのまま残ったままとなることもあり得る。そこで、この補強パターンを図示のように断続的に設けることで、熱膨張係数の違いに起因して発生する応力を複数方向に分散させて、基板の歪みが発生する可能性を低減している。

#### 【0030】

なお、補強パターン11A, 14A, 17A, 20Aは、各配線層11, 14, 17, 20に対応させて設けているが、必ずしも各配線層に対応させて設ける必要はなく、いくつつかの配線層について間引いてもよい。例えば、パッケージ10の最外層の配線層11, 20についてのみ当該配線層とともに補強パターン11A, 20Aを形成し、他の配線層14, 17については当該配線層のみを形成し、補強パターン14A, 17Aは省略してもよい。10

#### 【0031】

また、補強パターン11A, 14A, 17A, 20Aは、本発明の所期の目的を達成するのに必須の構成要素であり、その機能を考慮すると、基板端部（パッケージ10の周縁部）まで延在しているのが望ましい。しかし、この場合、補強パターン（導体層）の側面を露出させると、その側面部が酸化され、場合によっては腐食し、何らかの悪影響が及ぼされる可能性がある。従って、補強パターンを延在させるにしても、その側面は露出させないよう形成する必要がある。なお、最上層の補強パターン11Aについては、その表面はパッケージ10の表面から露出しているが、後述するように補強パターン11Aの表面には金（Au）めっき層が被着されているので、酸化、腐食等の不都合は生じない。20

#### 【0032】

一方、本パッケージ10は、最初から1個単位で作製されるのではなく、生産性の向上のため、複数個の配線基板を作り込んだ多数個取りの基板を最終的にパッケージ単位に切断分割して得られるものである。そのため、最終的に切断分割されるパッケージの周囲には切断の際のマージン（ $\pm 50 \mu m$ 程度の切断精度）を加味したスペース部分を必要とする。

#### 【0033】

例えば、基板端部から配線部（配線形成領域R1）までの距離が $500 \mu m$ 程度に設計されている場合、この $500 \mu m$ 程度のエリア内に各補強パターン11A, 14A, 17A, 20Aが形成されることになるが、切断の精度（ $\pm 50 \mu m$ 程度）を考慮して補強パターンの側面を露出させないことを確実にするためには、基板端部から補強パターンの側面までの距離を $250 \mu m$ 程度に選定すれば十分である。30

#### 【0034】

本パッケージ10を構成する各部材の具体的な材料や大きさ、厚さ等については、以下に記述するプロセスに関連させて説明する。

#### 【0035】

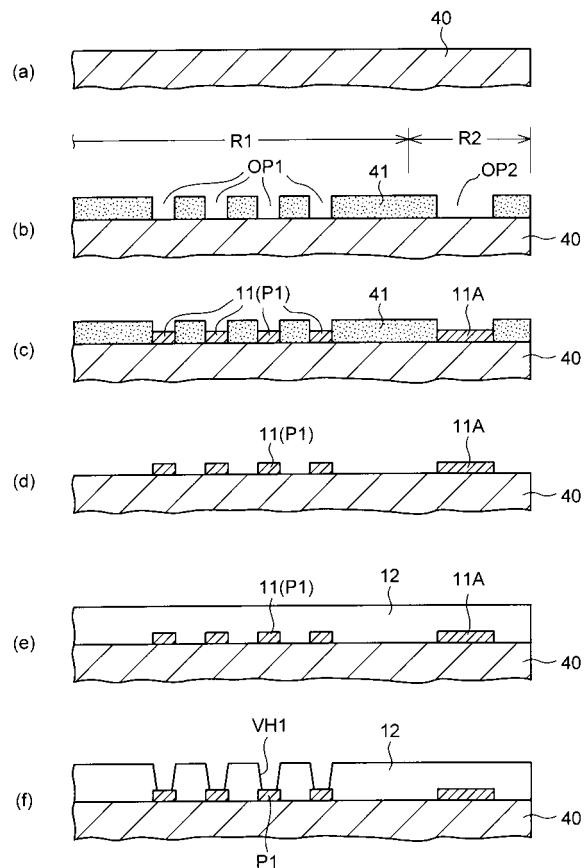

以下、本実施形態に係る配線基板（半導体パッケージ）10を製造する方法について、その製造工程の一例を示す図3及び図4を参照しながら説明する。40

#### 【0036】

先ず最初の工程では（図3（a）参照）、仮基板としての支持基材40を用意する。この支持基材40の材料としては、後述するように最終的にはエッチングされることを考慮して、エッチング液で溶解可能な金属（例えば、銅（Cu））が用いられる。また、支持基材40の形態としては、基本的には金属板もしくは金属箔で十分であるが、具体的な例としては、本願出願人が前に提案した「配線基板の製造方法及び電子部品実装構造体の製造方法」（特開2007-158174号公報）において開示されているような形態のものが使用され得る。すなわち、プリプレグ（補強材のガラス布にエポキシ系樹脂、ポリイミド系樹脂等の熱硬化性樹脂を含浸させ、半硬化のBステージ状態にした接着シート）上50

に下地層及び銅箔を配置して加熱・加圧することにより得られた構造体を、支持基材 40 として好適に使用することができる。

#### 【 0 0 3 7 】

次の工程では(図3(b)参照)、支持基材40上に、パターニング材料を使用してめっきレジストを形成し、所要の形状にパターニングしてレジスト層41を形成する。このレジスト層41は、配線形成領域R1に対応する部分において形成すべきパッドP1の形状に応じた開口部OP1と、その周辺領域R2に対応する部分において形成すべき補強パターン11Aの形状(図2参照)に応じた開口部OP2とを有するようにパターニング形成される。

#### 【 0 0 3 8 】

パターニング材料としては、感光性のドライフィルム(レジスト材料をポリエステルのカバーシートとポリエチレンのセパレータシートの間に挟んだ構造のもの)、又は液状のフォトレジスト(ノボラック系樹脂、エポキシ系樹脂等の液状レジスト)を用いることができる。例えば、ドライフィルムを使用する場合には、支持基材40の表面を洗浄後、ドライフィルムを熱圧着によりラミネートし、このドライフィルムを、所要の形状にパターニングされたマスク(図示せず)を用いて紫外線(UV)照射による露光を施して硬化させ、更に所定の現像液を用いて当該部分をエッティング除去し(開口部OP1, OP2)、所要のパターニング形状に応じたレジスト層41を形成する。液状のフォトレジストを用いた場合にも、同様の工程を経て、めっきレジスト(レジスト層41)を形成することができる。

10

#### 【 0 0 3 9 】

次の工程では(図3(c)参照)、そのめっきレジスト41の各開口部OP1, OP2から露出している支持基材(Cu)40上に、この支持基材40を給電層として利用した電解めっきにより、各開口部OP1, OP2に対応させてそれぞれ配線層11及び導体層11Aを形成する。配線層11は、半導体素子等の電子部品(チップ)を搭載するためのパッドP1として機能する。また、導体層11Aは、本発明を特徴付ける補強パターンを構成し、いずれの配線層にも接続されていない。

20

#### 【 0 0 4 0 】

配線層11及び導体層11Aを構成する材料としては、これに接触する支持基材40が最終的にエッティングされることを考慮して、そのエッティング液で溶解されない金属種を選定する。本実施形態では、支持基材40の材料として銅(Cu)を用いているので、これとは異なる金属として、良好な導電性を確保できるという点を考慮し、金(Au)めっきを施している。さらに、このAuめっき層上にニッケル(Ni)めっきを施している。あるいは、このNiめっき層上に、さらに銅(Cu)めっきを施してもよい。このようなめっき層構成とするのは、後の工程でパッドP1に銅(Cu)のビアを介して配線層を接続したときの密着性を高めるためと、CuがAuめっき層中へ拡散するのを防止するためである。つまり、この工程では、Auめっき層とNiめっき層の2層構造(もしくはAuめっき層とNiめっき層とCuめっき層の3層構造)からなるパッドP1及び補強パターン11Aを形成している。

30

#### 【 0 0 4 1 】

次の工程では(図3(d)参照)、めっきレジストとして用いたレジスト層41を除去する。例えば、めっきレジストとしてドライフィルムを使用した場合には、水酸化ナトリウムやモノエタノールアミンなどのアルカリ性の薬液を用いて除去することができ、ノボラック系樹脂、エポキシ系樹脂等の液状レジストを使用した場合には、アセトンやアルコール等を用いて除去することができる。これにより、図示のように支持基材40上に配線層11(パッドP1)及び導体層(補強パターン)11Aが形成された構造体が作製されたことになる。

40

#### 【 0 0 4 2 】

次の工程では(図3(e)参照)、支持基材40上の配線層11及び導体層11Aが形成されている側の面に絶縁層12を形成する。この絶縁層12の材料としては、エポキシ

50

系樹脂やポリイミド系樹脂等が使用され得る。形成方法としては、例えば、エポキシ系樹脂フィルムを支持基材40、配線層11及び導体層11A上にラミネートし、この樹脂フィルムをプレスしながら130～150℃の温度で熱処理して硬化させることにより、樹脂層（絶縁層12）を形成することができる。

#### 【0043】

次の工程では（図3（f）参照）、この絶縁層12の所要箇所（支持基材40上に形成されたパッドP1に対応する部分）に、炭酸ガスレーザ、エキシマレーザ等による穴明け加工により、当該パッドP1に達するビアホールVH1を形成する。なお、本工程ではレーザ等によりビアホールVH1を形成しているが、絶縁層12が感光性樹脂を用いて形成されている場合には、フォトリソグラフィにより所要のビアホールを形成することも可能である。10

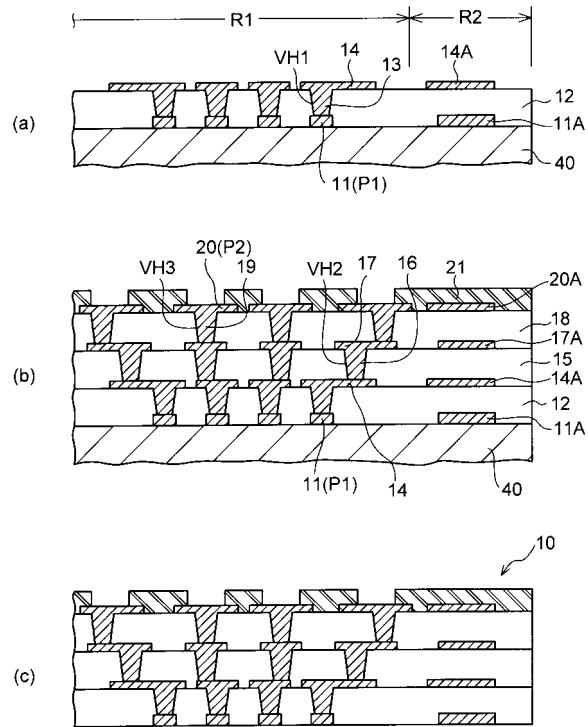

#### 【0044】

次の工程では（図4（a）参照）、ビアホールVH1が形成された絶縁層12上に、ビアホールVH1を充填して（ビア13の形成）当該パッドP1に接続される所要パターンの配線層14を形成するとともに、補強パターンを構成する導体層14Aを形成する。配線層14及び導体層14Aは、それぞれ配線形成領域R1に対応する部分及びその周囲の周辺領域R2に対応する部分に形成され、例えば、セミアディティブ法により形成され得る。

#### 【0045】

具体的には、先ず、無電解めっきやスパッタリング等により、ビアホールVH1の内部を含めて絶縁層12上に銅（Cu）のシード層（図示せず）を形成した後、形成すべき配線層14及び導体層14Aの各形状に応じた各開口部を備えたレジスト膜（図示せず）を形成する。次に、このレジスト膜の各開口部から露出しているシード層（Cu）上に、このシード層を給電層として利用した電解Cuめっきにより、導体（Cu）パターン（図示せず）を形成する。さらに、レジスト膜を除去後、導体（Cu）パターンをマスクにしてシード層をエッチングすることで、所要の配線層14及び導体層14Aが得られる。20

#### 【0046】

なお、セミアディティブ法以外に、サブトラクティブ法など各種の配線形成方法を用いて形成することも可能である。

#### 【0047】

次の工程では（図4（b）参照）、図3（e）～図4（a）の工程で行った処理と同様にして、絶縁層と配線層／導体層を交互に積層する。図示の例では、簡単化のため、2層の絶縁層と2層の配線層／導体層が積層されている。すなわち、絶縁層12及び配線層14／導体層14A上に樹脂層（絶縁層15）を形成し、この絶縁層15に、配線層14のパッド（図示せず）に達するビアホールVH2を形成した後、このビアホールVH2を充填して（ビア16の形成）当該パッドに接続される所要パターンの配線層17を形成するとともに、補強パターンを構成する導体層17Aを形成する。さらに、絶縁層15及び配線層17／導体層17A上に樹脂層（絶縁層18）を形成し、この絶縁層18に、配線層17のパッド（図示せず）に達するビアホールVH3を形成した後、このビアホールVH3を充填して（ビア19の形成）当該パッドに接続される所要パターンの配線層20を形成するとともに、補強パターンを構成する導体層20Aを形成する。本実施形態では、配線層20は最外層の配線層を構成する。3040

#### 【0048】

さらに、この配線層20の所要箇所に画定されるパッドP2の部分を露出させてその表面（絶縁層18及び配線層20／導体層20A上）を覆うようにソルダレジスト層21を形成する。このソルダレジスト層21は、例えば、感光性のソルダレジストフィルムをラミネートし、又は液状のソルダレジストを塗布し、当該レジストを所要の形状にパターンングすることにより、形成することができる。これによって、ソルダレジスト層21の開口部からパッドP2が露出する。

#### 【0049】

このパッドP2には、本パッケージ10をマザーボード等に実装する際に使用されるはんたボールやピン等の外部接続端子が接合されるので、コンタクト性を良くするために金(Au)めっきを施しておくのが望ましい。その際、パッド(Cu)P2上にNiめっきを施してからAuめっきを施す。つまり、Niめっき層とAuめっき層の2層構造からなる導体層(図示せず)をパッドP2上に形成する。

#### 【0050】

最後の工程では(図4(c)参照)、仮基板として用いた支持基材40(図4(b))を除去する。例えば、塩化第二鉄水溶液、塩化第二銅水溶液、過硫酸アンモニウム水溶液などを用いたウェットエッチングにより、露出しているパッドP1,P2(それぞれ表層部にAuめっき層が形成されている)、樹脂層12及びソルダレジスト層21に対して、支持基材(Cu)40を選択的にエッチングして除去することができる。10

#### 【0051】

以上の工程により、本実施形態の配線基板10(図1)が製造されたことになる。

#### 【0052】

以上説明したように、本実施形態に係る配線基板(半導体パッケージ)10及びその製造方法(図1～図4)によれば、パッケージ10の周辺領域R2(配線が形成されていない部分)において基板端部の近傍部分に補強パターン11A,14A,17A,20Aが形成されているので、パッケージ10の周辺部分が補強された構造、すなわち、外部からの機械的な応力や衝撃等に対して強い構造となっている。つまり、パッケージ全体として剛性が高められているので、外部からの機械的な応力等が加わった場合でも、従来技術に見られたような基板端部の「欠け」の発生を効果的に抑制することができる。また、パッケージ10の端部が欠け難い構造となっているので、配線層14,17,20の部分が露出したりする可能性も低い。20

#### 【0053】

このような欠け防止用の補強パターン11A,14A,17A,20Aは、例えば、電源層もしくはグランド層として割り当てられる配線層(多くの場合、「べた状」に形成されたプレーン層)の部分を拡張して設計できるため、補強パターンの設計は容易に行うことができる。これにより、外部からの機械的な応力等に対して基板の欠け等が発生し難い構造を容易に実現することができる。

#### 【0054】

また、本実施形態のプロセスでは、補強パターン11A,14A,17A,20Aの形成にあたり、従来のコアレス基板の製造工程(図3、図4)をそのまま利用できるため、基板へのコスト負荷が無い。つまり、追加的な製造工程を伴うことなく、基板の欠け等が発生し難いパッケージ構造を容易に実現することができる。30

#### 【0055】

これにより、プロセスの途中で外部から何らかの機械的な応力等が加わった場合でも、パッケージ10の周辺近傍に設けられた補強パターン11A,14A,17A,20Aの存在により、基板端部等の欠けを防止することができるので、不良品とはならず、製造歩留りを向上させることができる。

#### 【0056】

上述した実施形態に係る配線基板(半導体パッケージ)10の構成では、ソルダレジスト層(絶縁層)21を含めた全ての絶縁層12,15,18にそれぞれ補強パターン(導体層11A,14A,17A,20A)を内蔵させた場合を例にとって説明したが、本発明の要旨(配線基板の端部の近傍部分に補強パターンを設けること)からも明らかのように、必ずしも各絶縁層内に補強パターンを設ける必要はない。図5はその一例(図1の実施形態の一変形例)を示したものである。40

#### 【0057】

図5に示す実施形態に係る配線基板(半導体パッケージ)10aは、図1の配線基板10の構成と比べて、最外層のソルダレジスト層21において補強パターン20A(図1参照)を省略した点で相違している。他の構成については、図1の配線基板10の構成と基50

本的に同じであるのでその説明は省略する。

#### 【0058】

また、本実施形態の配線基板10aは、基本的には、上述した実施形態に係る製造方法の各工程(図3～図4)で行った処理と同様にして製造することができる。ただし、本実施形態に係るプロセスでは、図4(b)の工程において最外層の配線層20を形成する際に、導体層(補強パターン)20Aを形成しない点で相違する。本実施形態によれば、上述した実施形態(図1～図4)で得られた効果に加えて、以下の利点が得られる。

#### 【0059】

すなわち、上述したように層間絶縁層12, 15, 18はエポキシ系樹脂等から形成されているが、例えば、エポキシ系樹脂にはその剛性を増すためにシリカフィラーが含有されている。これに対し、最外層の絶縁層(ソルダレジスト層21)にはシリカフィラーは含有されていないため、内層側の絶縁層12, 15, 18と比べて比較的軟らかい。このため、パッケージ10の外部から何らかの機械的な応力が加わると、ソルダレジスト層21の部分で「欠け」が発生し、場合によってはソルダレジスト層21の端部が基板本体から剥離してしまうこと(デラミネーション)も起こり得る。その場合、ソルダレジスト層21によって覆われていた補強パターン20Aの側面が露出することになる。側面が露出すると、上述したように酸化、腐食等の不都合が生じる。

#### 【0060】

そこで、図5に示すようにソルダレジスト層21内の導体部分を基板端部から引下げた構造(つまり、補強パターン20Aを省略した構造)とすることで、かかる不都合に対処することができる。

#### 【0061】

かかる不都合に対処するための別の実施形態も考えられる。図6はその一例(図1の実施形態の他の変形例)を示したものである。

#### 【0062】

図6に示す実施形態に係る配線基板(半導体パッケージ)10bは、図1の配線基板10の構成と比べて、最外層のソルダレジスト層21aにおいて補強パターン20A(図1参照)を省略するとともに、このソルダレジスト層21aを、その端部が基板端部(パッケージ10bの周縁部)から所定の距離だけ後退した位置となるよう形成した点で相違している。この後退させる「所定の距離」は、例えば、250μm程度に選定される。他の構成については、図1の配線基板10の構成と基本的に同じであるのでその説明は省略する。

#### 【0063】

また、本実施形態の配線基板10bについても、上述した実施形態に係る製造方法の各工程(図3～図4)で行った処理と同様にして製造することができる。ただし、本実施形態に係るプロセスでは、図4(b)の工程において最外層の配線層20を形成する際に、導体層(補強パターン)20Aを形成しない点、さらにソルダレジスト層21aを形成する際に、その端部が基板端部から所定の距離だけ後退した位置となるようレジストのパターンニングを行う点で相違する。本実施形態においても、図5の実施形態の場合と同様の作用効果を奏すことができる。

#### 【0064】

上述した各実施形態の配線基板(半導体パッケージ)10, 10a, 10bには、一方の面(チップ搭載面)から露出するパッドP1にチップの電極パッドがはんだバンプ等を介して接続され、他方の面(外部接続端子接合面)から露出するパッドP2にはんだボール等の外部接続端子が接合される。図7はその一構成例を示したものである。

#### 【0065】

図7の例では、図1のパッケージ10に電子部品としての半導体素子(例えば、CPU等の能動素子のチップ)31を搭載した状態、すなわち、半導体装置30を構成した場合の断面構造を示している。搭載されるチップ31は、その電極パッド(図示せず)がはんだバンプ32を介してチップ搭載エリア(配線形成領域R1)内のパッドP1にフリップ

10

20

30

40

50

チップ接続されている。さらに、その搭載されたチップ31とパッケージ10との間隙にアンダーフィル樹脂33（熱硬化性のエポキシ系樹脂など）を充填し、熱硬化させて、チップ31とパッケージ10との接続信頼性を高めている。

### 【0066】

一方、チップ搭載面と反対側の外部接続端子接合面のパッドP2には、はんだボール35がリフローにより接合されている。図示の例では、パッドP2にはんだボール35を接合したBGA（ボール・グリッド・アレイ）の形態としているが、これに代えて、当該パッドにピンを接合したPGA（ピン・グリッド・アレイ）の形態や、当該パッド自体を外部接続端子としたLGA（ランド・グリッド・アレイ）の形態としてもよい。

### 【符号の説明】

10

### 【0067】

- 10, 10a, 10b...配線基板（半導体パッケージ）、

- 11, 14, 17, 20...配線層、

- 11A, 14A, 17A, 20A...補強パターン（導体層）、

- 12, 15, 18...樹脂層（絶縁層）、

- 13, 16, 19...ビア、

- 21, 21a...ソルダレジスト層（絶縁層）、

- 30...半導体装置、

- 31...半導体素子（チップ／電子部品）、

- P1, P2...パッド、

- R1...配線形成領域、

- R2...周辺領域、

- VH1, VH2, VH3...ビアホール。

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 実開昭62-010463(JP, U)

特開平11-135677(JP, A)

特開2003-124637(JP, A)

特開2000-013019(JP, A)

特開2003-304072(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 05 K 1 / 02

H 05 K 3 / 46