## (12) 发明专利

(10) 授权公告号 CN 108427647 B

(45) 授权公告日 2023.08.08

(21) 申请号 201711136385.4

(51) Int.CI.

(22) 申请日 2017.11.16

G06F 12/06 (2006.01)

(65) 同一申请的已公布的文献号

G06F 12/0875 (2016.01)

申请公布号 CN 108427647 A

(56) 对比文件

(43) 申请公布日 2018.08.21

US 2013227220 A1, 2013.08.29

(30) 优先权数据

US 2015019823 A1, 2015.01.15

62/459,414 2017.02.15 US

CN 104809179 A, 2015.07.29

15/587,286 2017.05.04 US

CN 104035887 A, 2014.09.10

(73) 专利权人 三星电子株式会社

CN 104090852 A, 2014.10.08

地址 韩国京畿道水原市

US 2013290607 A1, 2013.10.31

(72) 发明人 张牧天 牛迪民 郑宏忠

US 2014289467 A1, 2014.09.25

(74) 专利代理机构 北京铭硕知识产权代理有限公司 11286

姜国松.一种高效、可扩展细粒度缓存管理

混合存储研究.计算机科学.2013, (第08期), 全文.

专利代理人 张川绪 王兆庚

审查员 宋巧君

权利要求书3页 说明书13页 附图5页

## (54) 发明名称

读取数据的方法以及混合存储器模块

## (57) 摘要

公开一种读取数据的方法以及混合存储器模块。根据一个实施例，所述方法包括：提供一种混合存储器模块，包括：DRAM缓存；闪存；以及用于存储元数据缓存的SRAM；通过对从主机计算机接收的数据访问请求进行解码获取主机地址，其中，主机地址包括DRAM缓存标签和DRAM缓存索引；从DRAM缓存索引获取元数据地址，其中，元数据地址包括元数据缓存标签和元数据缓存索引；基于在SRAM的元数据缓存中的匹配的元数据缓存条目的存在，确定元数据缓存命中；在元数据缓存命中的情况下，从DRAM缓存获取数据并跳过对DRAM缓存的元数据的访问；将从DRAM缓存获取的数据返回到主机计算机。

B

CN 108427647

1. 一种读取数据的方法,包括:

提供混合存储器模块,混合存储器模块包括:动态随机存取存储器DRAM缓存;闪存;以及用于存储布隆过滤器和元数据缓存的静态随机存取存储器SRAM,其中,DRAM缓存包括存储在闪存中的多条数据的缓存副本和与所述多条数据的缓存副本对应的元数据,其中,元数据缓存包括包括在DRAM缓存中的元数据的部分的缓存副本;

从主机计算机接收对存储在混合存储器模块中的数据的数据访问请求,

通过对数据访问请求进行解码获取主机地址,其中,主机地址包括DRAM缓存标签和DRAM缓存索引;

从DRAM缓存索引获取元数据地址,其中,元数据地址包括元数据缓存标签和元数据缓存索引;

基于存储在SRAM中的元数据缓存中的匹配的元数据缓存条目的存在,确定元数据缓存命中,其中,匹配的元数据缓存条目具有元数据缓存标签和DRAM缓存标签的对;

基于元数据缓存命中,使用匹配的元数据缓存条目的DRAM缓存标签从包括在DRAM缓存中的数据的缓存副本获取数据并跳过对包括在DRAM缓存中的元数据的访问;

将从DRAM缓存获取的数据的缓存副本返回到主机计算机;

基于存储在SRAM中的元数据缓存中的匹配的元数据缓存条目的缺失,确定元数据缓存未命中;

基于元数据缓存未命中使用布隆过滤器执行布隆过滤器测试,并且基于布隆过滤器测试的结果确定DRAM缓存未命中或者潜在的DRAM缓存命中。

2. 如权利要求1所述的方法,其中,确定元数据缓存命中的步骤还包括:

将元数据地址的元数据缓存标签与一个或多个元数据缓存条目的元数据缓存标签进行比较,以确定元数据缓存中的匹配的元数据缓存条目的存在。

3. 如权利要求2所述的方法,还包括:

基于DRAM缓存未命中,从存储在闪存中的所述多条数据获取数据,并且跳过对包括在DRAM缓存中的元数据的访问;

将从闪存获取的数据返回到主机计算机。

4. 如权利要求1所述的方法,其中,元数据缓存标签的比较和布隆过滤器测试同时被执行。

5. 如权利要求1所述的方法,还包括:

基于元数据缓存未命中并且潜在的DRAM缓存命中,访问包括在DRAM缓存中的元数据;

基于主机地址的DRAM缓存标签与包括在DRAM缓存中的元数据的比较,确定数据是否存储在DRAM缓存中;

在包括在DRAM缓存中的元数据中存在主机地址的DRAM缓存标签的匹配条目的情况下,获取包括在DRAM缓存中缓存的数据并将从DRAM缓存获取的数据的缓存副本返回到主机计算机;

在包括在DRAM缓存中的元数据中不存在主机地址的DRAM缓存标签的匹配条目的情况下,从闪存获取数据并将从闪存获取的数据返回到主机计算机。

6. 如权利要求1所述的方法,其中,布隆过滤器包括具有多个条目的布隆过滤器阵列,布隆过滤器测试通过将哈希函数应用到布隆过滤器阵列来提供肯定结果或否定结果。

7. 如权利要求6所述的方法,还包括:删除布隆过滤器阵列,或者重置布隆过滤器阵列。

8. 如权利要求1所述的方法,还包括:当元数据缓存命中率比阈值高时,对混合存储器模块的缓存控制器进行编程以禁用布隆过滤器。

9. 如权利要求1所述的方法,其中,混合存储器模块包括缓存控制器,并且所述方法还包括:当元数据缓存命中率比阈值低时,对缓存控制器进行编程以禁用元数据缓存。

10. 如权利要求1所述的方法,还包括:在低功率条件下,串行访问布隆过滤器和元数据缓存。

11. 一种混合存储器模块,包括:

闪存;

动态随机存取存储器DRAM缓存,其中,DRAM缓存包括存储在闪存中的多条数据的缓存副本和与所述多条数据的缓存副本对应的元数据;

静态随机存取存储器SRAM,用于存储布隆过滤器和元数据缓存,元数据缓存包括包括在DRAM缓存中的元数据的部分的缓存副本;

存储器接口,用于向主机计算机提供接口;

存储器访问控制器,用于访问包括在DRAM缓存中的缓存副本和存储在闪存中的所述多条数据;

DRAM控制器,用于控制对DRAM缓存的访问;

闪存控制器,用于控制对闪存的访问;

缓存控制器,用于确定DRAM缓存中的与从主机计算机接收的数据访问请求中请求的数据对应的缓存的数据的存在,

其中,缓存控制器被配置为:

通过对经由存储器接口从主机计算机接收的数据访问请求进行解码来获取主机地址,其中,主机地址包括DRAM缓存标签和DRAM缓存索引;

从DRAM缓存索引获取元数据地址,其中,元数据地址包括元数据缓存标签和元数据缓存索引;

基于存储在SRAM中的元数据缓存中的匹配的元数据缓存条目的存在,确定元数据缓存命中,其中,匹配的元数据缓存条目具有元数据缓存标签和DRAM缓存标签的对;

基于元数据缓存命中,指示DRAM控制器使用匹配的元数据缓存条目的DRAM缓存标签从包括在DRAM缓存中的缓存副本获取数据,跳过对包括在DRAM缓存中的元数据的访问,

其中,存储器访问控制器被配置为:将从DRAM缓存获取的数据的缓存副本返回到主机计算机,

其中,缓存控制器还被配置为:

基于存储在SRAM中的元数据缓存中的匹配的元数据缓存条目的缺失,确定元数据缓存未命中;

使用布隆过滤器执行布隆过滤器测试;

基于布隆过滤器测试的结果确定DRAM缓存未命中或潜在的DRAM缓存命中。

12. 如权利要求11所述的混合存储器模块,其中,缓存控制器还被配置为:将元数据地址的元数据缓存标签与一个或多个元数据缓存条目的元数据缓存标签进行比较,以确定元数据缓存中的匹配的元数据缓存条目的存在。

13. 如权利要求12所述的混合存储器模块，

其中，缓存控制器还被配置为：

跳过对包括在DRAM缓存中的元数据的访问而指示闪存控制器从存储在闪存中的所述多条数据获取数据，

其中，存储器访问控制器被配置为将从闪存获取的数据返回到主机计算机。

14. 如权利要求11所述的混合存储器模块，其中，缓存控制器同时执行元数据缓存标签的比较和布隆过滤器测试。

15. 如权利要求11所述的混合存储器模块，

其中，基于元数据缓存未命中并且潜在的DRAM缓存命中，DRAM控制器被配置为：

访问包括在DRAM缓存中的元数据；

基于主机地址的DRAM缓存标签与包括在DRAM缓存中的元数据的比较，确定数据是否存储在DRAM缓存中，

其中，在包括在DRAM缓存中的元数据中存在主机地址的DRAM缓存标签的匹配条目的情况下，DRAM控制器被配置为获取包括在DRAM缓存中的缓存的数据，存储器访问控制器被配置为将从DRAM缓存获取的数据的缓存副本返回到主机计算机；

其中，在包括在DRAM缓存中的元数据中不存在主机地址的DRAM缓存标签的匹配条目的情况下，闪存控制器被配置为从闪存获取数据，存储器访问控制器被配置为将从闪存获取的数据返回到主机计算机。

16. 如权利要求11所述的混合存储器模块，其中，布隆过滤器包括具有多个条目的布隆过滤器阵列，布隆过滤器测试通过将哈希函数应用到布隆过滤器阵列来提供肯定结果或否定结果。

17. 如权利要求16所述的混合存储器模块，其中，缓存控制器还被配置为：删除布隆过滤器阵列，或者重置布隆过滤器阵列。

18. 如权利要求11所述的混合存储器模块，其中，当元数据缓存命中率比阈值高时，缓存控制器被编程以禁用布隆过滤器。

19. 如权利要求11所述的混合存储器模块，其中，当元数据缓存命中率比阈值低时，缓存控制器被编程以禁用元数据缓存。

20. 如权利要求11所述的混合存储器模块，其中，缓存控制器被配置为：在低功率条件下，串行访问布隆过滤器和元数据缓存。

## 读取数据的方法以及混合存储器模块

[0001] 本申请要求于2017年2月15日提交的第62/459,414号美国临时专利申请以及2017年5月4日提交的第15/587,286号美国专利申请的权益,所述申请的公开通过引用完整地包含于此。

### 技术领域

[0002] 本公开总体涉及混合存储器模块,更具体地,涉及一种用于使用SRAM元数据缓存(metadata cache)和布隆过滤器(Bloom filter)缓解访问混合存储器模块中的DRAM缓存(cache)的元数据的开销的系统和方法。

### 背景技术

[0003] 混合存储器模块指包含易失性存储器(例如,动态随机存取存储器(DRAM))和非易失性存储器(例如,闪存)二者作为主要的数据存储装置的存储器模块。混合存储器模块的一个示例为集成DRAM和闪存的混合双列直插式存储器模块(DIMM)。在典型配置中,DRAM可用作针对存储在闪存中的数据的缓存存储器。为了实现对DRAM缓存的快速访问,DRAM缓存的元数据可被存储在混合存储器模块的静态随机存取存储器(SRAM)中。

[0004] 然而,DRAM缓存的元数据所需的存储大小可大于SRAM的可用大小。集成在混合DIMM中的SRAM的存储容量由于其成本而可能保持相对小。由于SRAM的有限存储大小,DRAM缓存的全部元数据可能无法容纳在SRAM中,结果,元数据的无法容纳在SRAM中的剩余部分必须存储在DRAM中。在这种情况下,当访问数据时,对存储在DRAM中的元数据的慢访问可导致性能下降。

[0005] 为了解决这个问题,已经提出若干方法。第一种方法是减小存储在SRAM中的元数据的大小。例如,可通过减少存储在SRAM中的缓存行的数量来减小元数据的大小。在这种情况下,每个缓存行的大小被减小。缓存行的减小后的大小可负面影响命中率,并且在缓存未命中的情况下需要从闪存读取多个页。在另一示例中,可通过减少标签位(tag bit)和替换位(replacement bit)来减小缓存关联,但这种方法也可负面影响命中率。在另一示例中,替换策略可被更换为不需要替换位。

[0006] 然而,测试结果显示,用于减小元数据大小的这些效果的组合仅能够实现少量所需的元数据大小的减少。因此,用于存储元数据的SRAM的有限大小的问题可仍然保持为:闪存的数据存储容量和DRAM缓存的大小增长。

### 发明内容

[0007] 根据一个实施例,一种方法包括:提供一种混合存储器模块,包括:动态随机存取存储器(DRAM)缓存;闪存;以及用于存储元数据缓存的静态随机存取存储器(SRAM),其中,DRAM缓存包括存储在闪存中的数据的缓存副本和与数据的缓存副本对应的元数据,其中,元数据缓存包括DRAM缓存的元数据的部分的缓存副本;从主机计算机接收对存储在混合存储器模块中的数据的数据访问请求;通过对数据访问请求进行解码获取主机地址,其中,主

机地址包括DRAM缓存标签和DRAM缓存索引；从DRAM缓存索引获取元数据地址，其中，元数据地址包括元数据缓存标签和元数据缓存索引；基于在SRAM的元数据缓存中的匹配的元数据缓存条目的存在，确定元数据缓存命中，其中，匹配的元数据缓存条目具有元数据缓存标签和DRAM缓存标签的对；在元数据缓存命中的情况下，从DRAM缓存获取数据并跳过对DRAM缓存的元数据的访问；将从DRAM缓存获取的数据返回到主机计算机。

[0008] 根据另一实施例，一种混合存储器模块包括：闪存；动态随机存取存储器(DRAM)缓存，其中，DRAM缓存包括存储在闪存中的数据的缓存副本和与数据的缓存副本对应的元数据；静态随机存取存储器(SRAM)，用于存储元数据缓存，元数据缓存包括DRAM缓存的元数据的部分的缓存副本；存储器接口，用于向主机计算机提供接口；存储器访问控制器，用于访问存储在DRAM缓存和闪存中的数据；DRAM控制器，用于控制对DRAM缓存的访问；闪存控制器，用于控制对闪存的访问；缓存控制器，用于确定从主机计算机请求的数据的缓存副本的存在。

[0009] 缓存控制器被配置为：通过对数据访问请求进行解码来获取主机地址，其中，主机地址包括DRAM缓存标签和DRAM缓存索引；从DRAM缓存索引获取元数据地址，其中，元数据地址包括元数据缓存标签和元数据缓存索引；基于在SRAM的元数据缓存中的匹配的元数据缓存条目的存在，确定元数据缓存命中，其中，匹配的元数据缓存条目具有元数据缓存标签和DRAM缓存标签的对；在元数据缓存命中的情况下，指示DRAM控制器跳过对DRAM缓存的元数据的访问而从DRAM缓存获取数据。存储器访问控制器被配置为：将从DRAM缓存获取的数据返回到主机计算机。

[0010] 现在将参照附图更具体地描述并在权利要求中指出包括事件的实现和组合的各种新颖性细节的以上和其他优选特征。将理解，仅通过说明的方式而不作为限制来示出这里描述的具体系统和方法。如本领域技术人员将理解的，在不脱离本公开的范围的情况下，可在各种以及许多实施例中采用这里描述的原理和特征。

## 附图说明

[0011] 作为本说明书的部分包括的附图示出目前优选实施例，并且与以上给出的总体描述以及以下给出的优选实施例的详细描述一起用来解释和教导这里描述的原理。

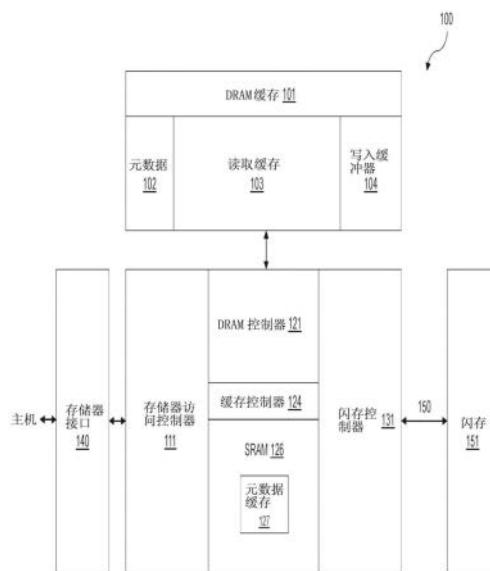

[0012] 图1示出传统的混合存储器模块的架构；

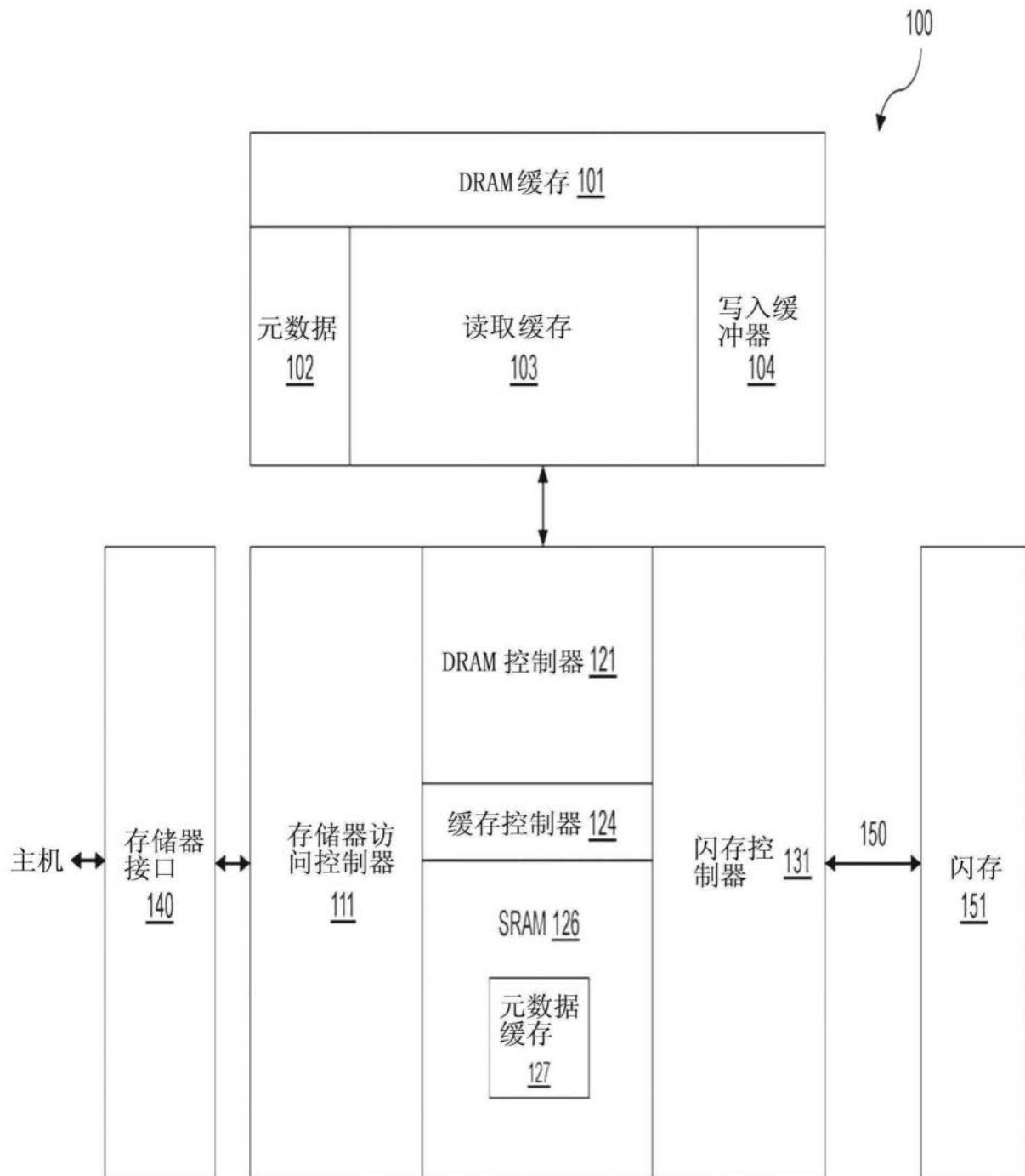

[0013] 图2示出根据一个实施例的示例的混合存储器模块的架构；

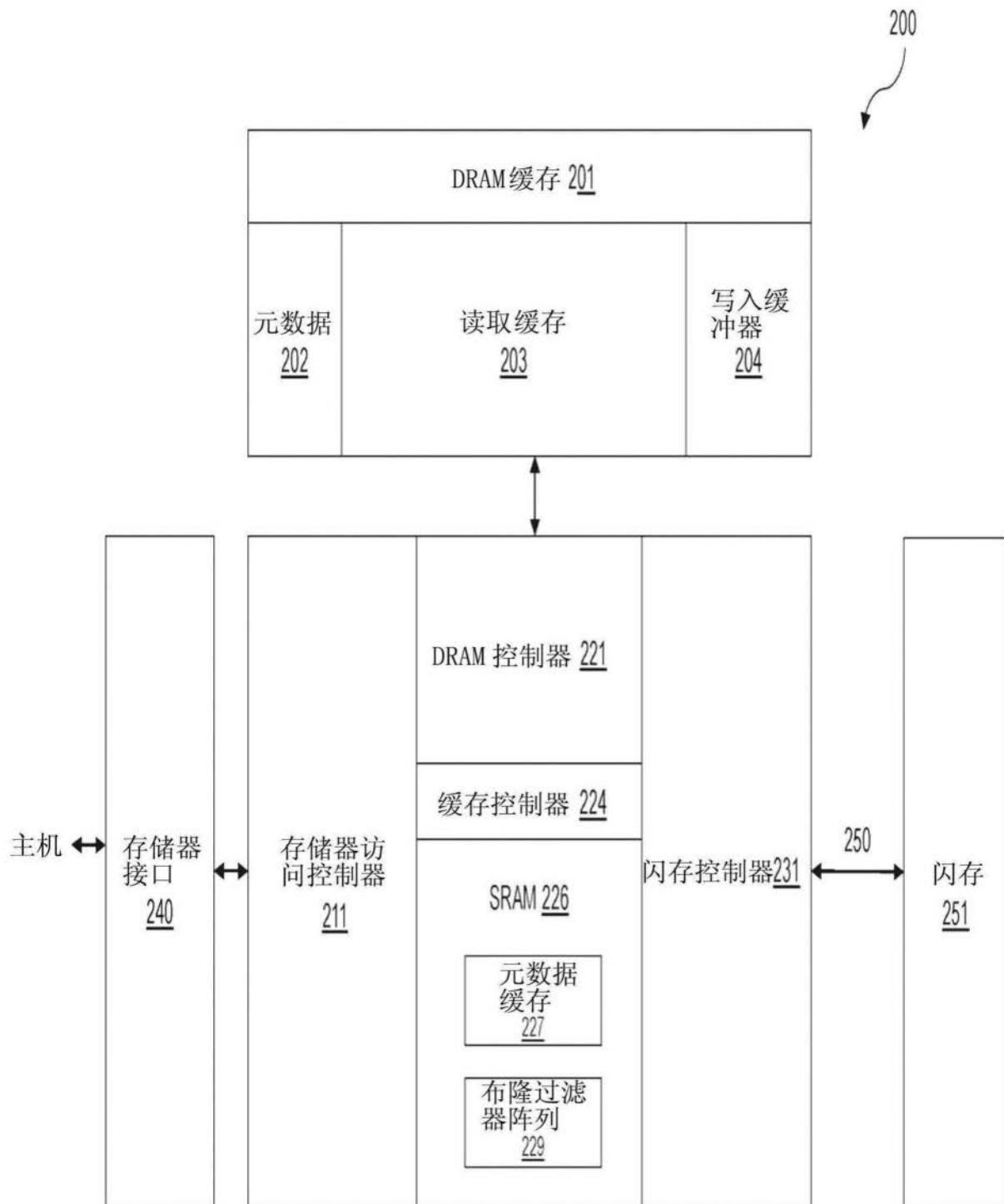

[0014] 图3示出根据一个实施例的示例的缓存控制器操作的框图；

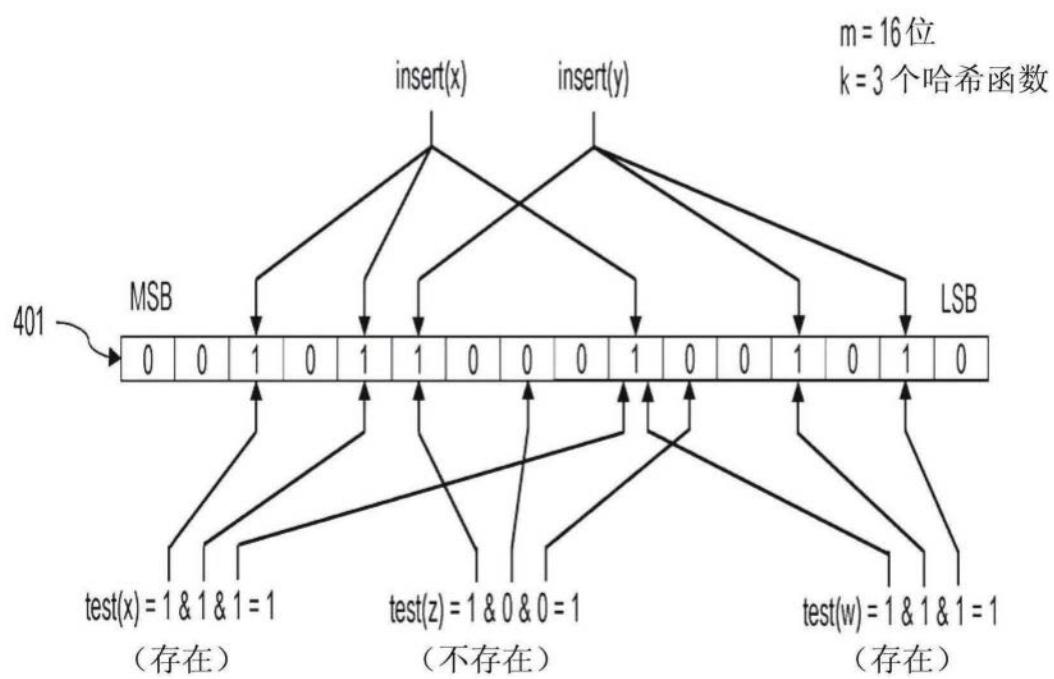

[0015] 图4示出根据一个实施例的在混合存储器模块中实现的示例的布隆过滤器；

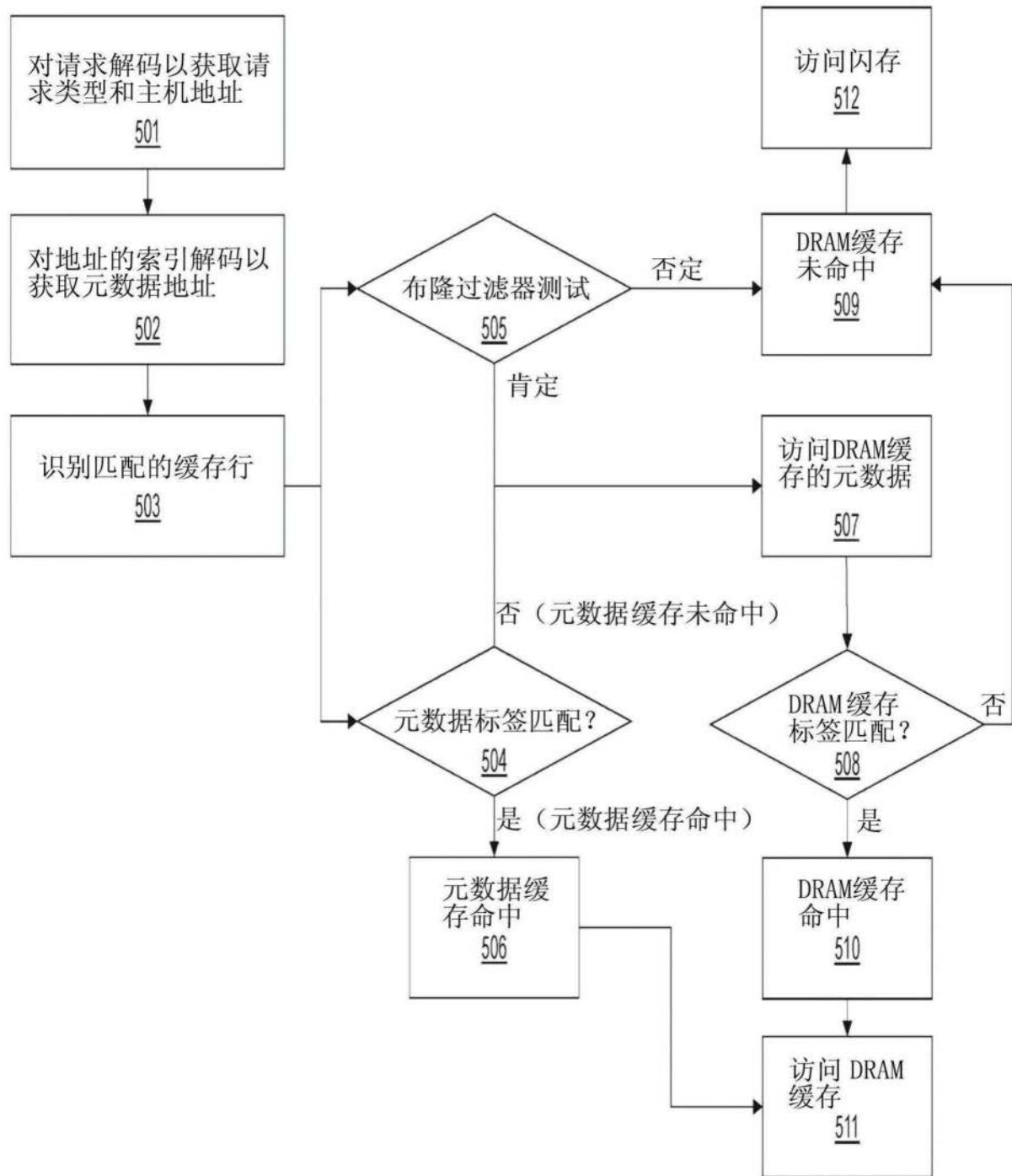

[0016] 图5是根据一个实施例的用于通过缓存控制器执行数据请求的流程图。

[0017] 贯穿附图，为了说明的目的，附图不必按照比例绘制，并且相似的结构或功能的元素通常由相同的参考标号来表示。附图仅意在帮助描述这里描述的各种实施例。附图不描述这里公开的教导的各个方面，并且不限制权利要求的范围。

## 具体实施方式

[0018] 这里公开的特征和教导中的每个可被单独地利用或与其他特征和教导结合地利用，以提供用于使用SRAM元数据缓存和布隆过滤器缓解访问混合存储器模块中的DRAM缓存

的元数据的开销的系统和方法。参照附图进一步详细描述单独地和组合地利用这些额外特征和教导中的许多的代表性示例。该具体实施方式仅意在教导本领域人员实践本教导方面的进一步细节,而不意在限制权利要求的范围。因此,以下在具体实施方式中公开的特征的组合可不是在最广义上实践本教导所必要的,相反仅被教导为具体描述本教导的代表性示例。

[0019] 在以下描述中,仅出于解释的目的,阐述特定命名以提供对本公开的彻底理解。然而,本领域技术人员将清楚,实践本公开的教导不需要这些特定细节。

[0020] 根据对计算机存储器内数据位的操作的算法和符号表示来呈现这里的具体实施方式的一些部分。这些算法描述和表示被数据处理领域的技术人员使用,以有效地将它们的工作的实质传达给本领域其他技术人员。算法在此通常被构思为导致期望的结果的自相一致的一系列步骤。这些步骤是需要物理量的物理操作的步骤。通常(但不必),这些量采用能够被存储、传递、组合、比较和另外操作的电信号或磁信号的形式。主要出于普通使用的原因,已证明将这些信号称为位、值、元素、符号、字符、项、数字等有时是方便的。

[0021] 然而,应牢记,所有这些术语和相似术语将与适当的物理量关联,并且仅是应用于这些量的方便的标记。除非另有如从下面的讨论清楚可知的特别声明,否则应理解,贯穿本说明书,利用诸如“处理”、“运算”、“计算”、“确定”、“显示”等的术语的讨论表示计算机系统或类似的电子计算装置的行为和处理,其中,计算机系统或类似的电子计算装置操纵被表示为计算机系统的寄存器或存储器内的物理(电子)量的数据,并将被表示为计算机系统的寄存器或存储器内的物理(电子)量的数据转换为被类似地表示为计算机系统存储器或寄存器或其他这样的信息存储、传输或显示装置内的物理量的其他数据。

[0022] 本公开描述用于减少对DRAM元数据的访问的各种技术。例如,可通过使用随机替换策略来减少DRAM元数据访问。在这种情况下,可不需要替换位,但性能可受负面影响。在另一示例中,可通过将部分DRAM缓存元数据存储在SRAM中来减少DRAM元数据访问。在这种情况下,仅SRAM匹配会触发DRAM搜索。然而,当元数据匹配能够频繁发生时,部分元数据方法可具有劣化的性能。一种替代方法是使用SRAM来缓存元数据自身,并使用布隆过滤器来有效地过滤出DRAM缓存未命中,并仅在标签匹配时执行DRAM搜索,但布隆过滤器可触发误报(false positive)。然而,因为DRAM缓存的劣化性能,所以在SRAM中使用布隆过滤器通常可能不是有效的。

[0023] 此外,为了提供本教导的额外的有用实施例,可以以非具体枚举或非明确枚举的方式组合代表性示例和从属权利要求的各种特征。还要特别注意,出于原始公开的目的以及出于限制所要求保护的主题的目的,所有的值的范围或实体的组的指示公开每个可能的中间值或中间实体。还要特别注意,附图中所示的组件的维度和形状被设计为帮助理解如何实践本教导,而不意在限制示例中所示的维度和形状。

[0024] 本公开提供一种用于使用SRAM元数据缓存和布隆过滤器缓解访问混合存储器模块中的DRAM缓存元数据的开销的系统和方法。根据一个实施例,布隆过滤器和SRAM缓存被组合,以存储DRAM缓存的元数据。布隆过滤器和SRAM缓存的组合使用会补偿各自的缺点,并提供改进的性能以访问存储在混合存储器模块中的数据。总体上,布隆过滤器有利于缓存未命中,元数据缓存有利于缓存命中。如果并行访问元数据缓存和布隆过滤器二者,布隆过滤器FALSE表明缓存未命中,因而不需要DRAM访问。SRAM元数据缓存命中被视为快速缓存命

中,因而不需要DRAM元数据访问。

[0025] 图1示出传统的混合存储器模块的架构。混合存储器模块100包括DRAM缓存101、闪存151、存储器访问控制器111、DRAM控制器121、缓存控制器124、用于存储元数据缓存127的元数据的SRAM 126、以及闪存控制器131。元数据缓存127包括DRAM缓存101的元数据102的缓存版本。DRAM缓存101存储闪存151的缓存数据,并包括元数据102、读取缓存103以及写入缓冲器104。元数据102可包括标签、有效位、脏位(dirty bit)等。DRAM缓存还可包括存储在闪存中的数据的缓存副本,元数据102与数据的缓存副本对应。注意,除非另外明确声明,否则术语元数据和标签可在这里互换使用。读取缓存103存储来自闪存151的缓存的数据。读取缓存103用于对数据进行缓存。读取缓存103可减少对闪存151的存储器访问的次数。待写入闪存151的数据可缓冲在写入缓冲器104中。写入缓冲器104可减少至闪存151的写入流量(write traffic)。

[0026] 主机计算机(未示出)根据在主机计算机与混合存储器模块100之间建立的存储器主/从接口协议(例如,NVDIMM-P),经由存储器接口140发送存储器访问请求以访问存储在混合存储器模块100中的数据。存储器访问请求被转发到存储器访问控制器111。存储器访问控制器111充当中间转换器(translator),并将(经由NVDIMM-P协议)来自主机的请求转换为可由混合存储器模块100读取的格式。在转换来自主机的请求之后,存储器访问控制器111将转换信息转发到缓存控制器124。

[0027] 缓存控制器124检查存储在SRAM 126中的元数据缓存127并确定元数据缓存命中或元数据缓存未命中。如果是元数据缓存命中,则缓存控制器124确认请求的数据被存储在DRAM缓存101中,并在不访问DRAM缓存101中的元数据102的情况下,使用存储在元数据缓存127中的元数据来请求DRAM控制器121访问DRAM缓存101中的请求的数据。如果是元数据缓存未命中,则缓存控制器124请求DRAM控制器121访问存储在DRAM缓存101中的元数据102,并确定DRAM缓存命中或DRAM缓存未命中。在检查DRAM缓存命中或DRAM缓存未命中之后,缓存控制器124可确定请求的数据的准确目的地址。如果是DRAM缓存命中,则缓存控制器124请求DRAM控制器121访问存储在DRAM缓存101中的请求的数据。如果是DRAM缓存未命中,则缓存控制器124请求闪存控制器131访问存储在闪存151中的请求的数据。

[0028] 当缓存控制器124确定请求的数据被存储在DRAM缓存101中时,缓存控制器124通过在元数据缓存命中的情况下参考存储在SRAM 126中的元数据缓存127或通过在DRAM缓存命中的情况下参考元数据102,来指示DRAM控制器121访问DRAM缓存101。当缓存控制器124确定请求的数据被存储在闪存151中时,闪存控制器131经由闪存流(flash stream)150访问并检索存储在闪存151中的数据。

[0029] 图2示出根据一个实施例的示例的混合存储器模块的架构。混合存储器模块200包括DRAM缓存201、闪存251、存储器访问控制器211、DRAM控制器221、缓存控制器224、SRAM 226以及闪存控制器231。

[0030] SRAM 226将DRAM缓存201的元数据202的缓存副本存储在元数据缓存227中。根据元数据缓存227的可用大小,存储在元数据缓存227中的元数据202的缓存副本可以是元数据202的子集。SRAM 226还以布隆过滤器中的布隆过滤器阵列229的形式存储另一“集合”的缓存元数据(元数据202的完整集合或元数据202的子集)。

[0031] 元数据缓存227包括DRAM缓存201的元数据202的缓存版本。DRAM缓存201存储闪存

251的缓存数据,并包括元数据202、读取缓存203以及写入缓冲器204。元数据202可包括标签、有效位、脏位等。注意,除非另外明确声明,否则术语元数据和标签可在这里互换使用。读取缓存203存储来自闪存251的缓存数据。读取缓存203用于对数据进行缓存。读取缓存203可减少对闪存251的存储器访问的次数。待写入闪存251的数据可缓冲在写入缓冲器204中。写入缓冲器204可减少至闪存251的写入流量。

[0032] 主机计算机(未示出)根据在主机计算机与混合存储器模块200之间建立的存储器主/从接口协议(例如,NVDIMM-P),经由存储器接口240发送存储器访问请求以访问存储在混合存储器模块200中的数据。存储器访问请求被转发到存储器访问控制器211。存储器访问控制器211充当中间转换器,并将(经由NVDIMM-P协议)来自主机的请求转换为可由混合存储器模块200读取的格式。在转换来自主机的请求之后,存储器访问控制器211将转换信息转发到缓存控制器224。

[0033] 缓存控制器224检查存储在SRAM 226中的关于缓存227的元数据,并确定元数据缓存命中或元数据缓存未命中。如果是元数据缓存命中,则缓存控制器224确认请求的数据被存储在DRAM缓存201中,并在不访问DRAM缓存201中的元数据202的情况下,使用存储在元数据缓存227中的元数据来请求DRAM控制器221访问DRAM缓存201中的请求的数据。

[0034] 根据一个实施例,缓存控制器224提供各种功能以对存储在SRAM 226中的元数据进行操作。这样的功能的示例包括管理存储在SRAM 226中的元数据的插入功能和测试功能,但不限于此。布隆过滤器可使用这些功能对存储在SRAM 226中的布隆过滤器阵列229进行操作,以确定是存在DRAM缓存命中还是存在DRAM缓存未命中。例如,缓存控制器224对布隆过滤器阵列229执行布隆过滤器测试功能。如果布隆过滤器测试结果是否定的,则意味着DRAM缓存未命中,指示数据未被存储在DRAM缓存201中,并且缓存控制器224在不访问DRAM缓存201的元数据202的情况下向闪存控制器231发送请求以获取数据。根据一个实施例,对元数据缓存227的元数据缓存检查以及对布隆过滤器阵列的布隆过滤器测试可独立地、同时地或以特定顺序被执行。

[0035] 如果是元数据缓存未命中并且布隆过滤器的测试结果为肯定的(即,指示DRAM缓存命中,但它可能是误报),则缓存控制器224请求DRAM控制器221访问DRAM缓存201的元数据202,以确定实际上是DRAM缓存命中还是DRAM缓存未命中。基于在DRAM缓存201的元数据202中的匹配元数据的存在,缓存控制器224可确定请求的数据的准确的目的地址。如果是DRAM缓存命中,则缓存控制器224请求DRAM控制器221访问存储在DRAM缓存201中的请求的数据。如果是DRAM缓存未命中,则缓存控制器224请求闪存控制器231访问存储在闪存251中的请求的数据。

[0036] 参照图2,元数据缓存227和布隆过滤器阵列229可具有独立的数据结构并可存储相同的或不同的元数据。元数据缓存227和布隆过滤器阵列229彼此独立,在SRAM 226中具有它们自己的专用区域,专用区域用于存储它们自己的元数据和操作元数据的逻辑。根据一个实施例,SRAM 226仅包括元数据缓存227和布隆过滤器阵列229中的一个,或者缓存控制器224仅操作元数据缓存227和布隆过滤器阵列229中的一个。不管布隆过滤器阵列229的存在或操作,元数据缓存227可以以相同的方式操作。类似地,不管元数据缓存227的存在或操作,布隆过滤器阵列229可以以相同的方式操作。根据元数据缓存227的操作的模式和存在(或缺失),元数据缓存227和布隆过滤器阵列229在SRAM 226中的分配区域可动态地改

变。该混合存储器模块200向元数据缓存227和布隆过滤器阵列229提供一个或多个“封装(wrapper)”功能,以帮助在不必依赖彼此的情况下确定缓存命中或缓存未命中。

[0037] 在元数据缓存命中的情况下,即,如果SRAM 226中的元数据缓存227存储了元数据的缓存副本,则缓存控制器224确定请求的数据被存储在DRAM缓存201中,缓存控制器224通过参考存储在SRAM 226中的元数据缓存227来指示DRAM控制器221访问DRAM缓存201。在DRAM缓存命中的情况下,缓存控制器224通过参考元数据202来指示DRAM控制器221访问DRAM缓存201。当缓存控制器224确定请求的数据被存储在闪存251中时,闪存控制器231经由闪存流250访问并检索存储在闪存251中的数据。

[0038] 根据一个实施例,因为DRAM元数据202是包容性的(inclusive)并且是干净的(clean),所以元数据缓存227可被有效地保持。例如,元数据缓存227中的行也被存储在DRAM缓存201的元数据202中。任何对元数据缓存227的访问类型总被视为读取访问。表1示出由混合存储器模块200的缓存控制器224根据访问类型和请求的数据的位置执行的动作的列表。

| 访问类型   | 在元数据缓存中? | 在 DRAM 缓存中? | 动作                                                       |

|--------|----------|-------------|----------------------------------------------------------|

| [0039] | 读取       | 否           | [元数据缓存未命中, DRAM 缓存未命中]<br>向 DRAM 缓存插入标签和数据<br>向元数据缓存插入标签 |

|        | 读取       | 是           | 由于包容性, 因此不适用 (N/A)                                       |

|        | 读取       | 否           | [元数据缓存未命中, DRAM 缓存命中]<br>向元数据缓存插入标签                      |

|        | 读取       | 是           | [元数据缓存命中, DRAM 缓存命中]<br>不操作                              |

|        | 写入       | 否           | [元数据缓存未命中, DRAM 缓存未命中]<br>向 DRAM 缓存插入标签和数据<br>向元数据缓存插入标签 |

|        | 写入       | 是           | 由于包容性, 因此 N/A                                            |

|        | 写入       | 否           | [元数据缓存未命中, DRAM 缓存命中]<br>向元数据缓存插入标签                      |

|        | 写入       | 是           | [元数据缓存命中, DRAM 缓存命中]<br>不操作                              |

[0040] 表1:数据访问和动作

[0041] 在读取访问请求的情况下,缓存控制器224可按照以下方式确定是否能够在DRAM缓存201中找到所请求的数据的缓存副本。首先,缓存控制器224检查元数据缓存227中是否存在匹配元数据。如果找到匹配,则由于元数据标签和DRAM缓存标签的包容性,缓存控制器224可推断出读取访问请求在元数据缓存227中命中。然后,缓存控制器224可使用元数据缓存227中命中的元数据而在不访问DRAM元数据202的情况下,从DRAM缓存201请求目标数据。

除了元数据缓存检查之外,缓存控制器224可使用布隆过滤器阵列229执行DRAM缓存命中或未命中检查。在通过布隆过滤器测试的DRAM缓存未命中的情况下,缓存控制器224可推断出目标数据不在DRAM缓存201中,并向闪存控制器231发送请求以在不访问DRAM缓存201的元数据202的情况下获取数据。如果布隆过滤器测试结果指示DRAM缓存命中,则由于通过布隆过滤器的DRAM缓存命中可能是误报,因此缓存控制器224不能在这个阶段确定是真的DRAM缓存命中还是未命中。因此,在这种情况下,缓存控制器224还请求DRAM控制器221访问DRAM元数据202以确定是真的DRAM缓存命中还是未命中。通过将包括在数据访问请求中的DRAM缓存标签与DRAM元数据202进行比较,缓存控制器224可准确地确定数据请求在DRAM缓存201中命中还是未命中。如果DRAM缓存命中,则缓存控制器224可从DRAM缓存201请求目标数据。如果DRAM缓存未命中,则缓存控制器224可从闪存251请求目标数据,将从闪存251获取的数据插入到DRAM缓存201,并更新DRAM元数据202。不管DRAM缓存命中还是未命中,由于元数据缓存未命中,因此缓存控制器224可使用从DRAM元数据202获取的元数据来更新元数据缓存227。

[0042] 在写入访问请求的情况下,缓存控制器224可基于元数据缓存227与DRAM缓存201的匹配结果如在读取访问请求的情况下那样执行等同的动作。将在以下详细强调读取访问操作与写入访问操作之间的不同。

[0043] 图3示出根据一个实施例的示例的缓存控制器操作的框图。参考图3解释的缓存控制器可以是如图2所示的集成在混合存储器模块200中的缓存控制器224。在这种情况下,将省略混合存储器模块200以及集成在混合存储器模块中的内部元件、模块和装置的重复解释。

[0044] 响应于从主机计算机接收的数据访问请求,缓存控制器对数据访问请求解码以获取请求的数据的主机地址301并识别访问类型(例如,读取、写入)。主机地址301包括标签302(这里也称为DRAM缓存标签)、索引303(这里也称为DRAM缓存索引)、偏移304。

[0045] 根据一个实施例,DRAM缓存中的缓存行可大于主机请求的数据的大小。在这种情况下,偏移304用于确定缓存行的与请求的数据对应的部分。例如,如果缓存行为2KB,并且请求的数据大小为1B,则缓存行中存在2048(2KB/1B)片数据,需要总共2048个偏移号以唯一地确定主机地址所涉及的数据片。例如,偏移304为0是指缓存行中的第一数据片,偏移304为2047是指缓存行中的最后数据片。

[0046] 根据一个实施例,索引303可包括与DRAM缓存关联的元数据信息。缓存控制器可进一步对索引303解码以获取元数据地址311并将元数据地址311与存储在SRAM中的元数据缓存327进行比较,以确定元数据缓存命中或未命中。根据一个实施例,元数据地址311包括元数据(MDC)标签312和元数据(MDC)索引313。

[0047] 首先,缓存控制器使用元数据地址311的MDC索引313在存储在SRAM元数据缓存327中的多个DRAM缓存元数据之中选择匹配元数据条目(entry)。存储在SRAM元数据缓存327中的每个匹配元数据条目可具有包括MDC标签(例如,333a至333d)和DRAM缓存标签(例如,332a至332d)的标签对以及有效位V。有效位V指示关联的缓存行是否有效。例如,如果V=0,则具有匹配元数据条目的缓存行指示缓存未命中。如果SRAM元数据缓存327被组织为如在示例中所示的多个路(way)(例如,路0、路1、路2以及路3),则MCD索引313可对应于路ID。

[0048] 为了确定元数据缓存命中或未命中,缓存控制器在元数据缓存327中搜索匹配条

目,并将元数据地址311的MCD标签312与识别的匹配条目的MDC标签进行比较。如果元数据标签312与MDC标签匹配,则从匹配条目读取包括原始主机标签的数据。存储在元数据缓存327中的原始主机标签与主机地址301的主机标签302进行比较。如果它们匹配,则缓存控制器确定元数据缓存命中,并在不访问DRAM缓存的元数据的情况下使用存储在元数据缓存327中的匹配的主机标签访问DRAM缓存中的请求的数据。

[0049] 除了元数据缓存检查之外,缓存控制器可执行布隆过滤器测试以使用布隆过滤器确定DRAM缓存中的缓存数据的存在(或不存在)(即,DRAM缓存命中或未命中)。可以以各种形式(例如,通过比较器)实现布隆过滤器。缓存控制器将主机地址301的标签302与通过元数据缓存检查所识别的匹配元数据对的DRAM缓存标签进行比较。如果布隆过滤器测试指示DRAM缓存未命中(即,在元数据缓存327中不存在与主机地址301的标签302匹配的DRAM缓存标签),则缓存控制器可推断出在DRAM缓存中不存在目标数据,并请求闪存控制器来访问存储在闪存中的数据。

[0050] 在一些情况下,缓存控制器在元数据缓存327中找不到匹配元数据条目(即,元数据缓存未命中),并且布隆过滤器可指示DRAM缓存命中。然而,由布隆过滤器指示的DRAM缓存命中可能是误报,因此,缓存控制器进而访问DRAM缓存的元数据以确定目标数据是否确实存储在DRAM缓存中(真的DRAM缓存命中或未命中)。基于主机地址301的标签302与DRAM缓存的元数据之间的比较结果,缓存控制器可准确地确定目标数据的位置。如果在DRAM缓存中没有匹配的元数据(即,真的DRAM缓存未命中),则缓存控制器可确保在DRAM中没有请求的数据的缓存副本。在这种情况下,缓存控制器可跳过访问DRAM缓存,而直接访问闪存控制器以访问存储在闪存中的数据。如果在DRAM缓存中存在匹配的元数据(即,真的DRAM缓存命中),则缓存控制器可访问DRAM控制器以访问存储在DRAM缓存中的数据。

[0051] 图4示出根据一个实施例的在混合存储器模块中实现的示例的布隆过滤器。缓存控制器针对布隆过滤器提供插入函数和测试函数。根据一个实施例,插入函数是哈希函数。缓存控制器可根据布隆过滤器的设置而采用不止一个哈希函数。例如,被表示为x、y、z和w的插入函数和测试函数的输入可以是元数据缓存标签。

[0052] 存储在本混合存储器模块的SRAM的专用区域中的布隆过滤器的元数据可被实现为包括多个条目的阵列(这里也称为布隆过滤器阵列)。在本示例中,布隆过滤器阵列的每个条目为16位,并且存在三个哈希函数。测试函数针对全部三个哈希函数提供匹配结果。注意,这些仅是示例,在不脱离本公开的范围的情况下,可使用不同长度的布隆过滤器和不同数量的哈希函数。

[0053] 对于给定的缓存标签(例如,图3中的标签302),插入函数根据哈希算法将位插入(或更新)到布隆过滤器阵列401的指向的条目。在本示例中,对于缓存标签x,哈希函数插入如缓存标签x所指向的布隆过滤器阵列401的条目的集合(位7、12和14)。稍后,当接收到数据访问请求时,测试函数test(x)被调用,以读取来自布隆过滤器阵列401的由缓存标签x所指向的条目,并测试布隆过滤器阵列401是否包含缓存标签x。使用哈希函数插入,第二个缓存标签y可被输入到如缓存标签y所指向的布隆过滤器阵列401的条目(位2、4和11),缓存标签y的存在可使用函数test(y)来测试。

[0054] 在本示例中,缓存标签x和y被示出为布隆过滤器阵列401的输入。布隆过滤器阵列401的每个条目可为0或1。插入函数可基于一个或多个哈希函数,每个哈希函数可采用缓存

标签作为输入。插入函数的输出是与布隆过滤器阵列401中的指向的条目对应的位号。注意,本公开不限于具体的哈希函数以及使用的哈希函数的数量。例如,当接收到缓存标签作为输入时,插入函数可更新布隆过滤器阵列的四个条目。

[0055] 注意,标签z和w未被具体输入到布隆过滤器401。当接收到具有缓存标签z的数据请求时,针对标签z的测试函数test(z)被调用,并返回为否定,准确地指示z不包含在布隆过滤器中(因而在DRAM缓存中)。然而,当接收到具有缓存标签w的数据访问请求时,测试函数test(w)被调用,以读取如由缓存标签w指向的布隆过滤器阵列401的条目并测试缓存标签w在布隆过滤器阵列401中的存在或不存在。在本示例中,测试函数test(w)指示缓存标签w存在于布隆过滤器阵列401中。因此,在本示例中,测试函数test(w)是误报的示例。因此,布隆过滤器可用于确切识别不在缓存中的标签,但不能用于准确地预测什么缓存标签在缓存中。

[0056] 根据一个实施例,本布隆过滤器可删除布隆过滤器阵列的选择的部分或整个部分。例如,删除函数可随缓存控制器的意愿被应用,以除去布隆过滤器阵列的部分或整个布隆过滤器阵列。当于缓存行替换而缓存行不再存在于DRAM缓存中或由被驱逐时,删除函数可以是有用的。在这种情况下,删除函数可除去本布隆过滤器阵列中的对应条目。在布隆过滤器阵列不足够大的情况下,缓存控制器可删除布隆过滤器阵列的部分,以为新的条目腾出空间。在替换实施例中,本布隆过滤器可使用大的布隆过滤器阵列以能够覆盖整个标签范围,或缓存控制器可在布隆过滤器满了从而在布隆过滤器变得低效时不能再添加阵列时,重置布隆过滤器。

[0057] 图5是根据一个实施例的用于通过缓存控制器执行数据请求的流程图。响应于来自主机计算机的数据访问的请求,混合存储器模块的缓存控制器对请求进行解码以获取请求类型(例如,读取、写入)以及请求的数据的主机地址(501)。主机地址可包括标签(DRAM标签)、索引和偏移。然后,缓存控制器对主机地址的索引进行解码以获取包括MDC标签和MDC索引的元数据地址(502)。缓存控制器使用元数据地址的MDC索引来从存储在混合存储器模块的SRAM中的元数据缓存识别匹配的缓存行(503)。匹配的缓存行存储MDC标签和DRAM缓存标签的对。如果在元数据缓存中不存在匹配的缓存行,则缓存控制器请求DRAM控制器访问DRAM缓存的元数据并确定DRAM缓存中是否存在请求的数据的缓存副本(即,真的DRAM缓存命中或未命中)。

[0058] 另一方面,如果在SRAM元数据缓存中识别到匹配的缓存行,则缓存控制器确定匹配的缓存行的MDC标签是否与元数据地址的MDC标签匹配,并进一步确定匹配的MDC标签所引用的主机标签是否与原始主机标签匹配(504)。如果主机标签匹配(即,元数据缓存命中),则缓存控制器确定请求的数据被缓存在DRAM缓存中(506),并且请求DRAM控制器访问DRAM缓存,并跳过访问DRAM缓存的元数据,使用匹配的主机标签来从DRAM缓存获取请求的数据(511)。

[0059] 此外,缓存控制器使用匹配的缓存行的DRAM标签(或主机地址的DRAM标签)来执行布隆过滤器测试,以确定DRAM缓存命中或未命中(505)。如果布隆过滤器的测试结果为否定,则缓存控制器推断出请求的数据未被缓存在DRAM缓存中(即,DRAM缓存未命中)(509),并且请求闪存控制器访问闪存并获取请求的数据(512)。在这种情况下,可跳过对DRAM缓存的元数据的访问,改善对闪存的数据访问的延迟。

[0060] 如果不存在针对元数据缓存的匹配(即,元数据缓存未命中)并且布隆过滤器测试结果为肯定(可能是DRAM缓存命中的误报),则缓存控制器请求DRAM控制器访问DRAM缓存的元数据(507),以确定主机地址的标签(DRAM标签)是否与DRAM缓存的元数据的条目匹配(508)。如果DRAM缓存标签匹配,则缓存控制器确定请求的数据被缓存在DRAM缓存中(即,DRAM缓存命中)(510),并请求DRAM控制器访问DRAM缓存中的请求的数据(511)。如果DRAM缓存标签匹配失败,则缓存控制器确定请求的数据未被缓存在DRAM缓存中(即,DRAM缓存未命中)(509),并请求闪存控制器访问闪存中的请求的数据(512)。

[0061] 本缓存控制器可被编程以支持元数据缓存和布隆过滤器中的任一个、二者或都不支持。例如,缓存控制器监视缓存命中率以确定禁用/启用元数据缓存和/或布隆过滤器。如果元数据缓存命中率比第一预定阈值高,则由于布隆过滤器在缓解访问DRAM缓存元数据的开销方面提供很少益处,因此缓存控制器可禁用布隆过滤器。在另一示例中,元数据缓存命中率比第二预定阈值低,缓存控制器可禁用元数据缓存,仅留下布隆过滤器。如果DRAM不用作闪存的缓存,则缓存控制器可禁用元数据缓存和布隆过滤器二者。

[0062] 根据一个实施例,缓存控制器可并行访问布隆过滤器和元数据缓存,以获取快速的比较结果。根据另一实施例,缓存控制器可在低功率条件下,串行地访问布隆过滤器和元数据缓存。缓存控制器可首先检查布隆过滤器,如果布隆过滤器结果是元数据缓存未命中,则缓存控制器不激活元数据缓存。如果布隆过滤器结果是元数据缓存命中,则缓存控制器可激活元数据缓存以检查DRAM缓存命中或未命中。如果布隆过滤器结果是元数据缓存命中但元数据缓存返回假,则缓存控制器访问DRAM缓存标签。串行访问的次序可被颠倒,也就是说,以元数据缓存、布隆过滤器和DRAM缓存标签的次序进行访问。

[0063] 根据一个实施例,一种方法包括:提供一种混合存储器模块,包括:动态随机存取存储器(DRAM)缓存;闪存;以及用于存储元数据缓存的静态随机存取存储器(SRAM),其中,DRAM缓存包括存储在闪存中的数据的缓存副本和与数据的缓存副本对应的元数据,其中,元数据缓存包括DRAM缓存的元数据的部分的缓存副本;从主机计算机接收对存储在混合存储器模块中的数据的数据访问请求;通过对数据访问请求进行解码获取主机地址,其中,主机地址包括DRAM缓存标签和DRAM缓存索引;从DRAM缓存索引获取元数据地址,其中,元数据地址包括元数据缓存标签和元数据缓存索引;基于在SRAM的元数据缓存中的匹配的元数据缓存条目的存在,确定元数据缓存命中,其中,匹配的元数据缓存条目具有元数据缓存标签和DRAM缓存标签的对;在元数据缓存命中的情况下,从DRAM缓存获取数据并跳过对DRAM缓存的元数据的访问;将从DRAM缓存获取的数据返回到主机计算机。

[0064] 确定元数据缓存命中的步骤还可包括:将元数据地址的元数据缓存标签与一个或多个元数据缓存条目的元数据缓存标签进行比较,以确定元数据缓存中的匹配的元数据缓存条目的存在。

[0065] SRAM还可存储布隆过滤器,所述方法还可包括:基于SRAM的元数据缓存中的匹配的元数据缓存条目的不存在,确定元数据缓存未命中;使用布隆过滤器执行布隆过滤器测试;基于布隆过滤器测试的结果确定DRAM缓存未命中或潜在的DRAM缓存命中;在DRAM缓存未命中的情况下,从闪存获取数据;将从闪存获取的数据返回到主机计算机。

[0066] 元数据缓存标签的比较和布隆过滤器测试可同时被执行。

[0067] 所述方法还可包括:在元数据缓存未命中并且潜在的DRAM缓存命中的情况下,访

问DRAM缓存的元数据；基于主机地址的DRAM标签与DRAM缓存的元数据的比较，确定数据是否存储在DRAM缓存中；在DRAM缓存的元数据中存在主机地址的DRAM标签的匹配条目的情况下，从DRAM缓存获取数据并将从DRAM缓存获取的数据返回到主机计算机；在DRAM缓存的元数据中不存在主机地址的DRAM标签的匹配条目的情况下，从闪存获取数据并将从闪存获取的数据返回到主机计算机。

[0068] 布隆过滤器可包括具有多个条目的布隆过滤器阵列，布隆过滤器测试可通过将哈希函数应用到布隆过滤器阵列来提供肯定结果或否定结果。

[0069] 所述方法还可包括删除布隆过滤器阵列或重置布隆过滤器阵列。

[0070] 所述方法还可包括：当元数据缓存命中率比阈值高时，对缓存控制器编程以禁用布隆过滤器。

[0071] 所述方法还可包括：当元数据缓存命中率比阈值低时，对缓存控制器编程以禁用元数据缓存。

[0072] 所述方法还可包括：在低功率条件下，串行访问布隆过滤器和元数据缓存。

[0073] 根据另一实施例，一种混合存储器模块包括：闪存；动态随机存取存储器(DRAM)缓存，其中，DRAM缓存包括存储在闪存中的数据的缓存副本和与数据的缓存副本对应的元数据；静态随机存取存储器(SRAM)，用于存储元数据缓存，元数据缓存包括DRAM缓存的元数据的部分的缓存副本；存储器接口，用于向主机计算机提供接口；存储器访问控制器，用于访问存储在DRAM缓存和闪存中的数据；DRAM控制器，用于控制对DRAM缓存的访问；闪存控制器，用于控制对闪存的访问；缓存控制器，用于确定从主机计算机请求的数据的缓存副本的存在。

[0074] 缓存控制器被配置为：通过对数据访问请求进行解码获取主机地址，其中，主机地址包括DRAM缓存标签和DRAM缓存索引；从DRAM缓存索引获取元数据地址，其中，元数据地址包括元数据缓存标签和元数据缓存索引；基于在SRAM的元数据缓存中的匹配的元数据缓存条目的存在确定元数据缓存命中，其中，匹配的元数据缓存条目具有元数据缓存标签和DRAM缓存标签的对；在元数据缓存命中的情况下，指示DRAM控制器跳过对DRAM缓存的元数据的访问而从DRAM缓存获取数据。存储器访问控制器被配置为：将从DRAM缓存获取的数据返回到主机计算机。

[0075] 缓存控制器还可被配置为：将元数据地址的元数据缓存标签与一个或多个元数据缓存条目的元数据缓存标签进行比较，以确定元数据缓存中的匹配的元数据缓存条目的存在。

[0076] SRAM还可存储布隆过滤器，缓存控制器还可被配置为：基于SRAM的元数据缓存中的匹配的元数据缓存条目的不存在，确定元数据缓存未命中；使用布隆过滤器执行布隆过滤器测试；基于布隆过滤器测试的结果确定DRAM缓存未命中或潜在的DRAM缓存命中；在DRAM缓存未命中的情况下，跳过对DRAM缓存的元数据的访问而指示闪存控制器从闪存获取数据；从闪存获取数据，存储器访问控制器可被配置为将从闪存获取的数据返回到主机计算机。

[0077] 缓存控制器可同时执行元数据缓存标签的比较和布隆过滤器测试。

[0078] 在元数据缓存未命中并且潜在的DRAM缓存命中的情况下，DRAM控制器可被配置为：访问DRAM缓存的元数据；基于主机地址的DRAM标签与DRAM缓存的元数据的比较，确定数

据是否存储在DRAM缓存中。在DRAM缓存的元数据中存在主机地址的DRAM标签的匹配条目的情况下,DRAM控制器被配置为从DRAM缓存获取数据,存储器访问控制器被配置为将从DRAM缓存获取的数据返回到主机计算机。在DRAM缓存的元数据中不存在主机地址的DRAM标签的匹配条目的情况下,闪存控制器被配置为从闪存获取数据,存储器访问控制器被配置为将从闪存获取的数据返回到主机计算机。

[0079] 布隆过滤器可包括具有多个条目的布隆过滤器阵列,布隆过滤器测试可通过将哈希函数应用到布隆过滤器阵列来提供肯定结果或否定结果。

[0080] 缓存控制器还可被配置为删除布隆过滤器阵列或重置布隆过滤器阵列。

[0081] 当元数据缓存命中率比阈值高时,缓存控制器可被编程以禁用布隆过滤器。

[0082] 当元数据缓存命中率比阈值低时,缓存控制器可被编程以禁用元数据缓存。

[0083] 缓存控制器可被配置为:在低功率条件下,串行访问布隆过滤器和元数据缓存。

[0084] 已在上文描述了上面的示例实施例,以示出实现用于使用SRAM元数据缓存和布隆过滤器缓解访问混合存储器模块中的DRAM缓存的元数据的开销的系统和方法的各种实施例。本领域普通技术人员将想到来自公开的示例实施例的各种修改和偏差。在权利要求中阐述意在处于本发明的范围内的主题。

图1

图2

图3

图4

图5