(12)发明专利

(10)授权公告号 CN 103824886 B

(45)授权公告日 2019.03.01

(21)申请号 201310572119.1

(51)Int.CI.

(22)申请日 2013.11.15

H01L 29/786(2006.01)

(65)同一申请的已公布的文献号

H01L 29/06(2006.01)

申请公布号 CN 103824886 A

(56)对比文件

(43)申请公布日 2014.05.28

US 2011/0140100 A1, 2011.06.16,

(30)优先权数据

US 2011/0240991 A1, 2011.10.06,

2012-251794 2012.11.16 JP

US 2011/0140100 A1, 2011.06.16,

(73)专利权人 株式会社半导体能源研究所

US 2012/0193625 A1, 2012.08.02,

地址 日本神奈川

审查员 郑钰

(72)发明人 佐藤贵洋 中泽安孝 长隆之

越冈俊介 德永肇 神长正美

(74)专利代理机构 中国国际贸易促进委员会专

权利要求书3页 说明书39页 附图36页

利商标事务所 11038

代理人 陈华成

(54)发明名称

半导体装置

(57)摘要

本发明涉及一种半导体装置及其制造方法，赋予使用氧化物半导体膜的晶体管稳定的电气特性。另外，赋予使用氧化物半导体膜的晶体管具有优良的电气特性。另外，本发明提供一种具有该晶体管的高可靠性的半导体装置。关于具有层叠有氧化物半导体膜及氧化物膜的多层膜、栅电极以及栅极绝缘膜的晶体管，多层膜经由栅极绝缘膜而重叠于所述栅电极地设置，多层膜是具有由氧化物半导体膜的下表面与氧化物半导体膜的侧面所呈的第一角度、以及由氧化物膜的下表面与氧化物膜的侧面所呈的第二角度的形状，并且，第一角度小于第二角度且被设为锐角。另外，通过使用该晶体管来制造半导体装置。

B

CN 103824886 B

1. 一种半导体装置，包括：

多层膜，其中层叠有氧化物半导体膜及氧化物膜；

栅电极；以及

栅极绝缘膜，

其中，所述多层膜隔着所述栅极绝缘膜与所述栅电极重叠，

所述多层膜具有如下形状，所述形状具有所述氧化物半导体膜的底面与所述氧化物半导体膜的侧面所呈的第一角度、以及所述氧化物膜的底面与所述氧化物膜的侧面所呈的第二角度，

所述第一角度为锐角且小于所述第二角度，

并且，所述第一角度及所述第二角度分别为 $10^\circ$ 以上且小于 $90^\circ$ 。

2. 根据权利要求1所述的半导体装置，其中，所述氧化物膜的下端与所述氧化物半导体膜的上端之间的距离为30nm以下。

3. 根据权利要求1所述的半导体装置，其中，在所述多层膜中，所述氧化物膜层叠在所述氧化物半导体膜上。

4. 根据权利要求1所述的半导体装置，

其中，所述氧化物半导体膜层叠在所述氧化物膜上，

并且，第二氧化物膜层叠在所述氧化物半导体膜上。

5. 根据权利要求1所述的半导体装置，

其中，所述氧化物半导体膜及所述氧化物膜各自都包含In-M-Zn氧化物，其中M为选自由Al、Ga、Ge、Y、Zr、La、Ce和Nd构成的组中的一个，

并且，所述氧化物膜的In对M的原子个数比小于所述氧化物半导体膜。

6. 根据权利要求1所述的半导体装置，

其中，所述氧化物膜为非晶的，

所述氧化物半导体膜为结晶的，

并且，包括在所述氧化物半导体膜中的结晶部的c轴平行于所述氧化物半导体膜的表面的法向量。

7. 根据权利要求1所述的半导体装置，还包括接触于所述多层膜的源电极及漏电极。

8. 根据权利要求7所述的半导体装置，其中，低电阻区设置在如下区域，该区域处于所述多层膜中并且处于所述多层膜与所述源电极和所述漏电极中的一个之间的界面附近。

9. 根据权利要求7所述的半导体装置，还包括具有与所述氧化物膜相同或不同的组成的第二氧化物膜，其中所述第二氧化物膜设置在所述源电极的上表面、所述漏电极的上表面及所述多层膜的上表面上且与它们接触。

10. 一种半导体装置，包括：

栅电极；

所述栅电极上的氧化物半导体膜；以及

所述氧化物半导体膜上的氧化物膜，

其中，所述氧化物膜包含In-Ga-Zn氧化物，

所述氧化物半导体膜的底面与所述氧化物半导体膜的侧面所呈的第一角度小于所述氧化物膜的底面与所述氧化物膜的侧面所呈的第二角度，

并且,所述第一角度为锐角。

11.根据权利要求10所述的半导体装置,其中,所述氧化物半导体膜包含In-Ga-Zn氧化物。

12.根据权利要求10所述的半导体装置,

其中,所述氧化物半导体膜包含结晶,该结晶的c轴在垂直于所述氧化物半导体膜的上表面的方向上取向,

所述结晶中的一个的a轴的方向不同于所述结晶中的另一个的a轴的方向,

并且,所述结晶中的一个的b轴的方向不同于所述结晶中的另一个的b轴的方向。

13.一种半导体装置,包括:

多层膜,其中层叠有氧化物半导体膜及氧化物膜;

栅电极;以及

栅极绝缘膜,

其中,所述氧化物半导体膜包含In-Ga-Zn氧化物,

所述氧化物膜包含In-Ga-Zn氧化物,

所述多层膜隔着所述栅极绝缘膜与所述栅电极重叠,

所述多层膜具有如下形状,所述形状具有所述氧化物半导体膜的底面与所述氧化物半导体膜的侧面所呈的第一角度、以及所述氧化物膜的底面与所述氧化物膜的侧面所呈的第二角度,

所述第一角度为锐角且小于所述第二角度,

所述氧化物膜包含化学元素,

所述氧化物半导体膜包含所述化学元素,

并且,所述氧化物膜的导带底的能量比所述氧化物半导体膜的导带底的能量更接近于真空能级。

14.根据权利要求13所述的半导体装置,其中,所述氧化物膜的下端与所述氧化物半导体膜的上端之间的距离为30nm以下。

15.根据权利要求13所述的半导体装置,其中,在所述多层膜中,所述氧化物膜层叠在所述氧化物半导体膜上。

16.根据权利要求13所述的半导体装置,

其中,所述氧化物半导体膜层叠在所述氧化物膜上,

并且,第二氧化物膜层叠在所述氧化物半导体膜上。

17.根据权利要求13所述的半导体装置,其中,所述氧化物膜的所述导带底的所述能量比所述氧化物半导体膜的所述导带底的所述能量更接近于所述真空能级0.05eV以上且2eV以下。

18.根据权利要求13所述的半导体装置,

其中,所述氧化物半导体膜及所述氧化物膜各自都包含In-M-Zn氧化物,其中M为选自由Al、Ga、Ge、Y、Zr、La、Ce和Nd构成的组中的一个,

并且,所述氧化物膜的In对M的原子个数比小于所述氧化物半导体膜。

19.根据权利要求13所述的半导体装置,

其中,所述氧化物膜为非晶的,

- 所述氧化物半导体膜为结晶的，

并且，包括在所述氧化物半导体膜中的结晶部的c轴平行于所述氧化物半导体膜的表面的法向量。

20. 根据权利要求13所述的半导体装置，还包括接触于所述多层膜的源电极及漏电极。

21. 根据权利要求20所述的半导体装置，其中，低电阻区设置在如下区域，该区域处于所述多层膜中并且处于所述多层膜与所述源电极和所述漏电极中的一个之间的界面附近。

22. 根据权利要求20所述的半导体装置，还包括具有与所述氧化物膜相同或不同的组成的第二氧化物膜，其中所述第二氧化物膜设置在所述源电极的上表面、所述漏电极的上表面及所述多层膜的上表面上且与它们接触。

## 半导体装置

### 技术领域

[0001] 本发明涉及一种半导体装置及其制造方法。

[0002] 此外,在本说明书中半导体装置是指能够通过利用半导体特性而发挥功能的所有装置,电光装置、半导体电路以及电子设备等都是半导体装置。

### 背景技术

[0003] 使用形成在具有绝缘表面的基板上的半导体膜构成晶体管的技术受到关注。该晶体管被广泛地应用于如集成电路或显示装置等的半导体装置。作为可应用于晶体管的半导体膜,已知硅膜。

[0004] 关于用于晶体管的半导体膜的硅膜,根据用途分别使用非晶体硅膜或多晶硅膜。例如,当应用于构成大型的显示装置的晶体管时,优选使用已确立了向大面积基板上进行成膜的技术的非晶体硅膜。另一方面,当应用于构成一体地形成有驱动电路的高功能的显示装置的晶体管时,优选使用可以制造具有高场效应迁移率的晶体管的多晶硅膜。关于多晶硅膜,已知通过对非晶体硅膜进行高温下的加热处理或激光处理来形成的方法。

[0005] 进一步地,近年来氧化物半导体膜受到关注。例如,公开了一种使用载流子密度低于 $10^{18}/\text{cm}^3$ 的包含铟、镓及锌的氧化物半导体膜的晶体管(参照专利文献1)。

[0006] 氧化物半导体膜可以利用溅射法形成,所以可以应用于构成大型的显示装置的晶体管。另外,使用氧化物半导体膜的晶体管具有高场效应迁移率,因而可以实现一体形成有驱动电路的高功能的显示装置。另外,因为可以改良使用非晶体硅膜的晶体管的生产装置的一部分而利用,所以在可以抑制设备投资的方面上优势。

[0007] 并且,已知使用氧化物半导体膜的晶体管在截止状态下,其泄漏电流(也称为截止电流)极小。例如,公开了一种应用了使用氧化物半导体膜的晶体管的低泄漏特性的低耗电的CPU等(参照专利文献2)。

[0008] [专利文献1]日本专利申请公开2006-165528号公报

[0009] [专利文献2]美国专利申请公开第2012/0032730号说明书

[0010] 使用氧化物半导体膜的晶体管由于在氧化物半导体膜中产生的缺陷、以及氧化物半导体膜与所接触的绝缘膜之间的界面处产生的缺陷,晶体管的电气特性变得不良。另外,随着使用氧化物半导体膜的晶体管的应用范围扩大,对于可靠性的要求也多样化了。

### 发明内容

[0011] 于是,本发明的一个方式要解决的问题之一是赋予使用氧化物半导体膜的晶体管稳定的电气特性。另外,本发明的一个方式要解决的问题之一是赋予使用氧化物半导体膜的晶体管优良的电气特性。另外,本发明的一个方式要解决的问题之一是提供具有该晶体管的高可靠性的半导体装置。

[0012] 本发明的一个方式是一种半导体装置,其特征在于,具有:层叠有氧化物半导体膜及氧化物膜的多层膜;栅电极;以及栅极绝缘膜,多层膜经由栅极绝缘膜而与所述栅电极重

叠地设置，多层膜具有如下形状，该形状具有氧化物半导体膜的下表面与氧化物半导体膜的侧面所呈的第一角度以及氧化物膜的下表面与氧化物膜的侧面所呈的第二角度，并且，第一角度小于第二角度且第一角度为锐角。

[0013] 在上述半导体装置中，在多层膜中氧化物半导体膜的上端与所述氧化物膜的下端大致一致。另外，在多层膜中，既可以在氧化物半导体膜之上层叠有氧化物膜，又可以在氧化物半导体膜的上下都层叠有氧化物膜。

[0014] 在上述半导体装置中，第一角度及第二角度优选为10°以上且小于90°。

[0015] 在上述半导体装置中，优选的是氧化物膜包含与氧化物半导体膜共同的元素，且氧化物膜的导带底的能量比氧化物半导体膜更接近于真空能级。例如，优选的是，氧化物半导体膜及氧化物膜是In-M-Zn氧化物(M为Al、Ga、Ge、Y、Zr、Sn、La、Ce或Nd)，并且，氧化物膜的In对M的原子个数比小于氧化物半导体膜。

[0016] 在上述半导体装置中，优选的是，氧化物膜为非晶质的，氧化物半导体膜为结晶质的，并且，氧化物半导体膜所包括的结晶部的c轴平行于氧化物半导体膜的表面的法向量。

[0017] 在上述半导体装置中，源电极及漏电极以接触于多层膜的方式设置，并且，在多层膜与源电极和漏电极相接触的界面附近的区域中设置低电阻区。

[0018] 此外，在上述半导体装置中，具有与氧化物膜相同或不同的组成的氧化物膜也可以接触于源电极和漏电极以及多层膜的上表面的方式设置。

[0019] 根据本发明的一个方式，通过使用包含氧化物膜和氧化物半导体膜的多层膜，可以赋予晶体管稳定的电气特性。

[0020] 另外，通过将该多层膜的形状设为至少具有第一角度和大于该第一角度的第二角度的锥形状，可以增大作为沟道区的氧化物半导体膜与源电极及漏电极之间的接触面积，并可以使晶体管的导通电流增大。

[0021] 另外，根据本发明的一个方式，可以提供具有上述晶体管的高可靠性的半导体装置。

## 附图说明

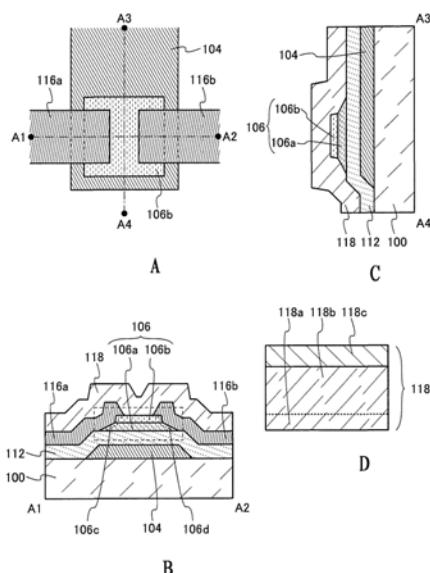

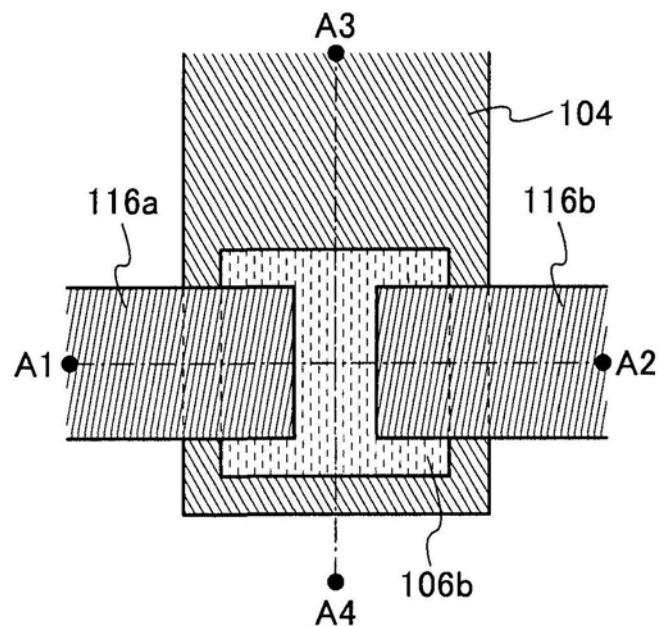

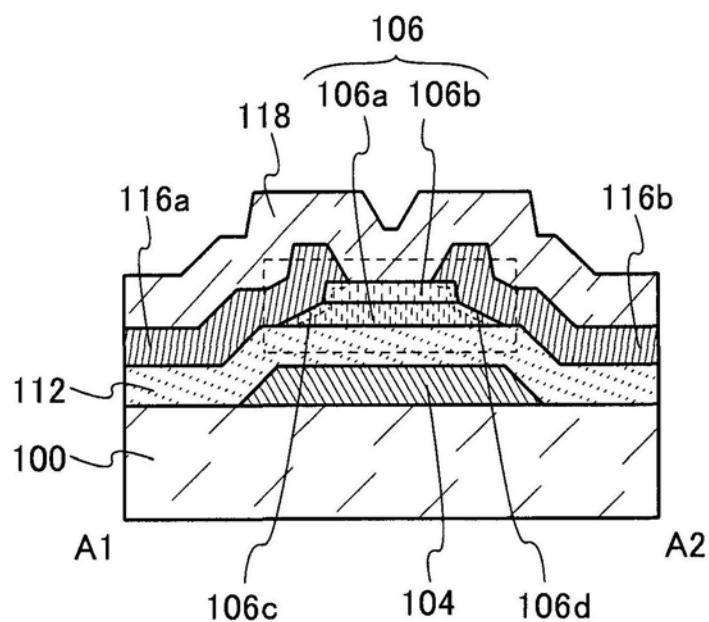

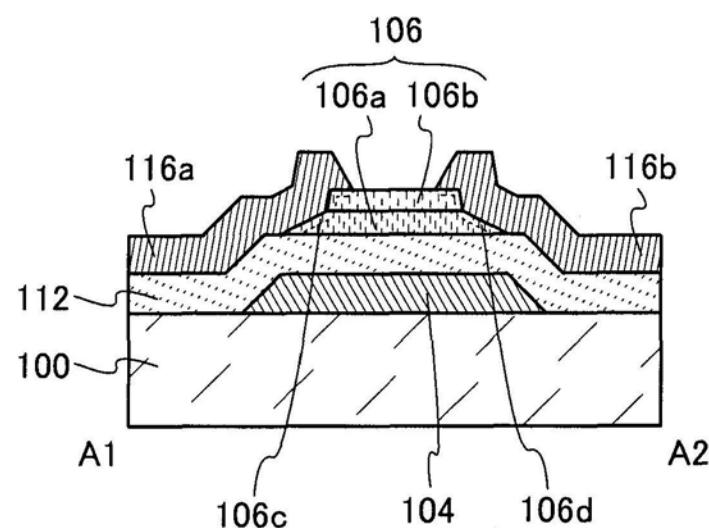

[0022] 图1A至图1D是说明晶体管的俯视图及截面图；

[0023] 图2是说明晶体管的截面图；

[0024] 图3是说明多层膜的能带结构的图；

[0025] 图4是说明多层膜的能带结构的图；

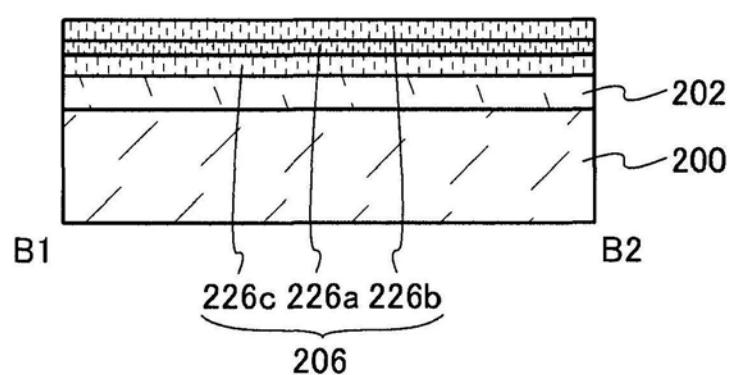

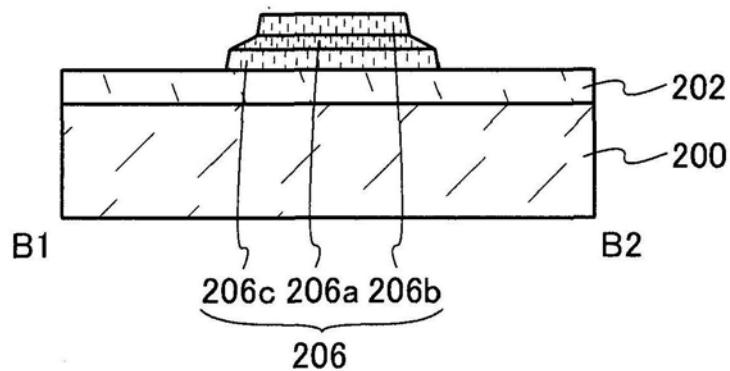

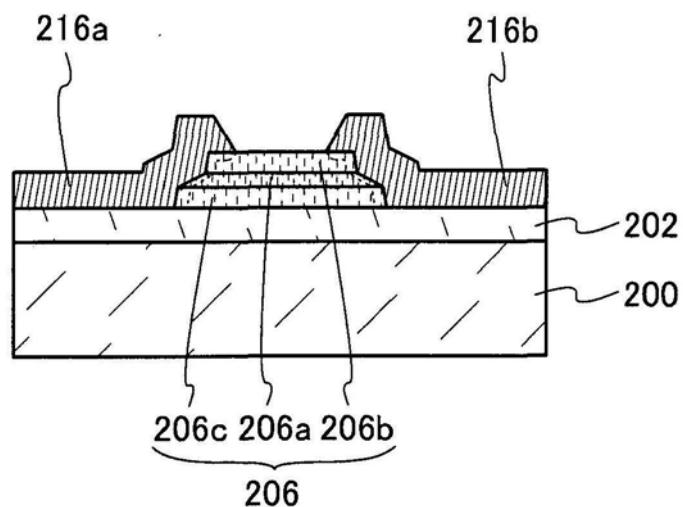

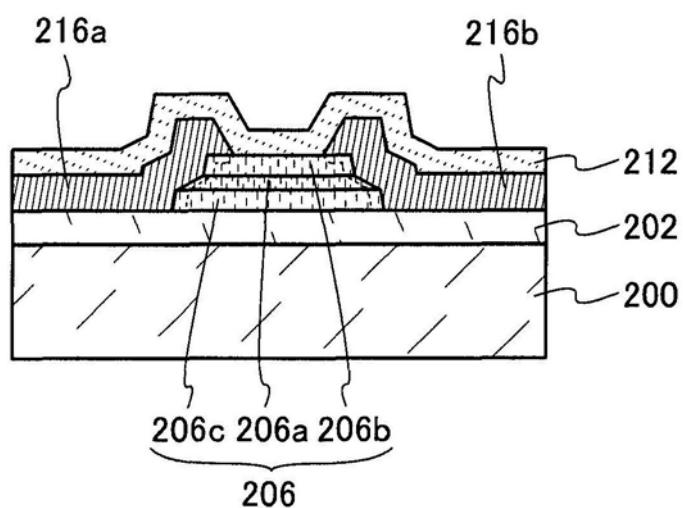

[0026] 图5A至图5C是说明晶体管的制造方法的截面图；

[0027] 图6A和图6B是说明晶体管的制造方法的截面图；

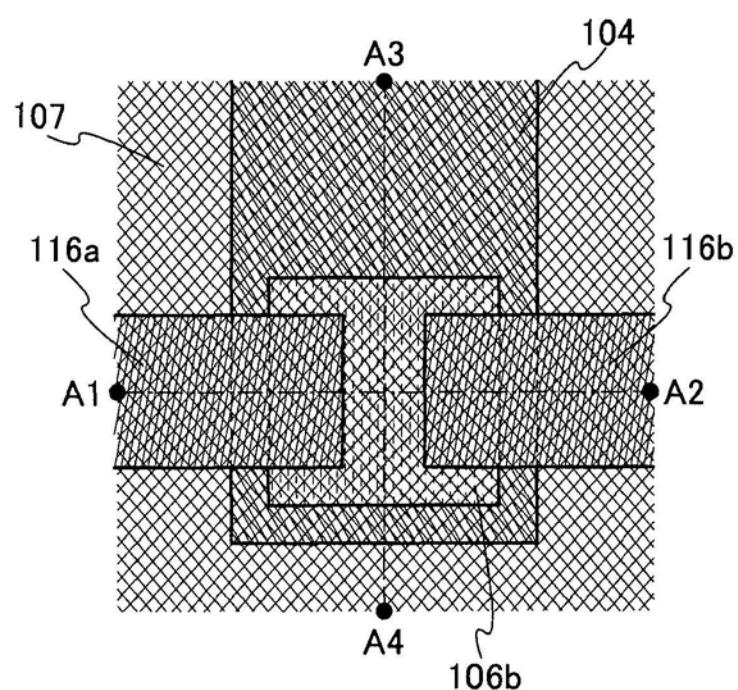

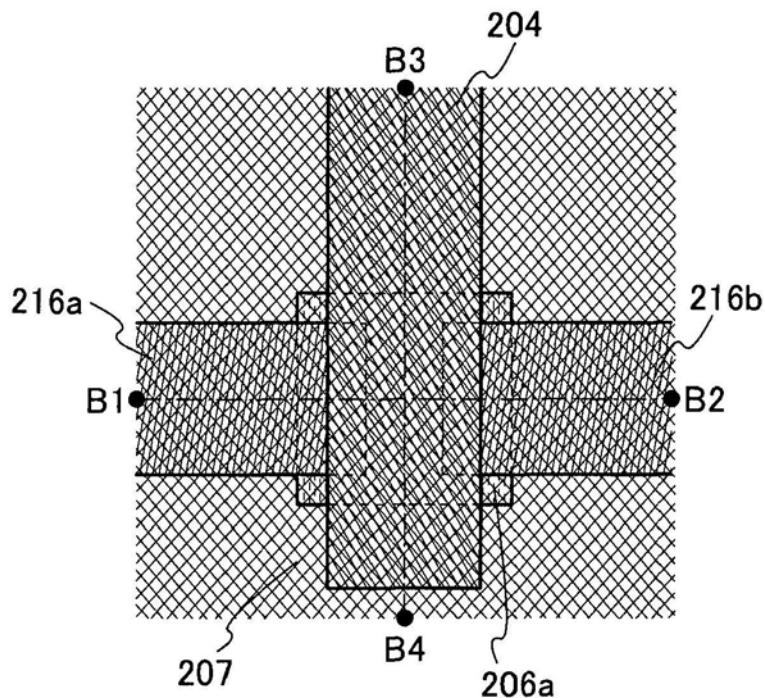

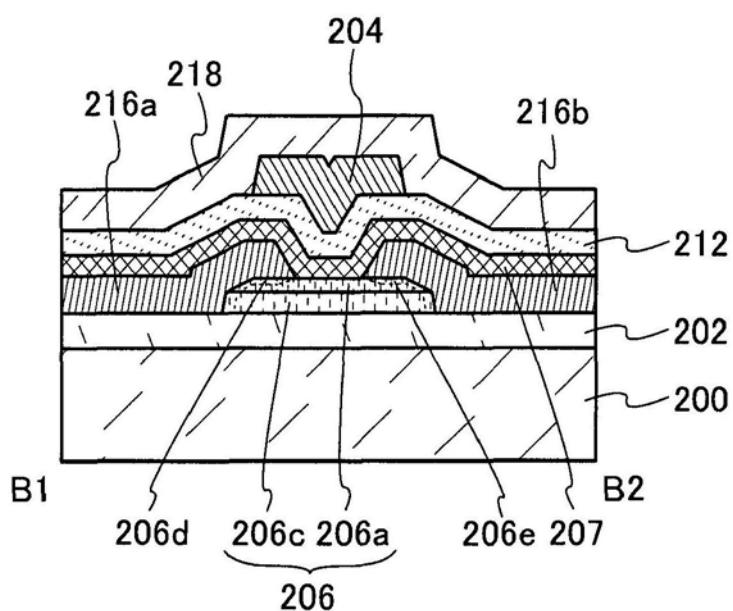

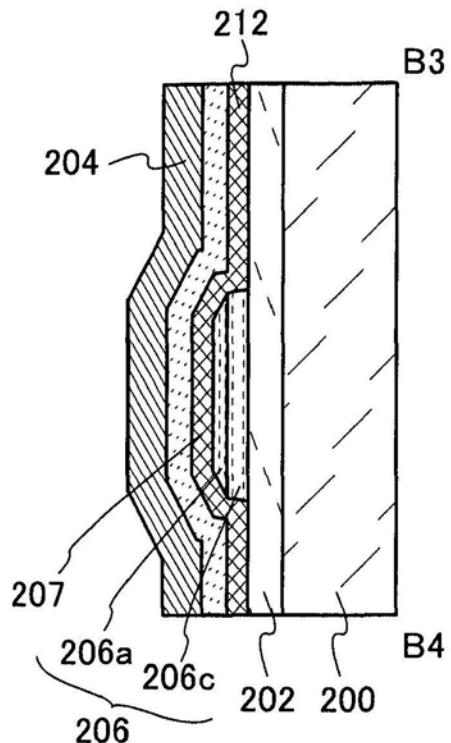

[0028] 图7A至图7D是说明晶体管的俯视图及截面图；

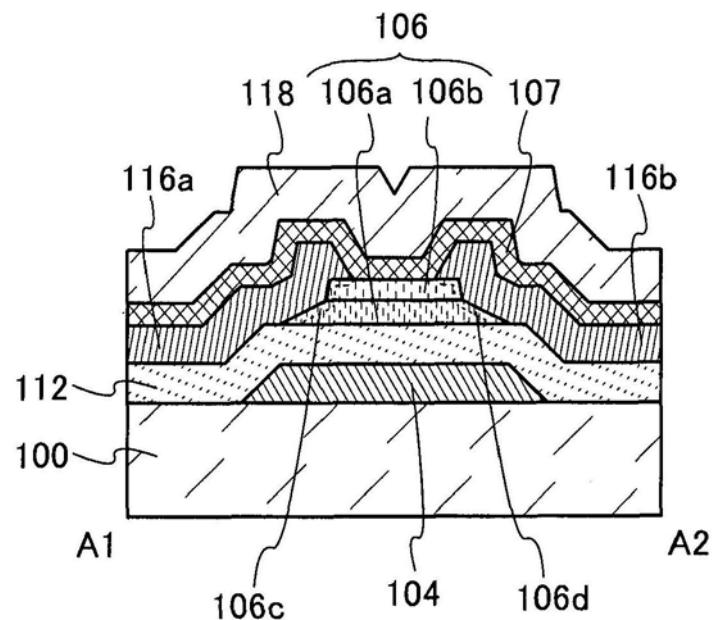

[0029] 图8A至图8C是说明晶体管的俯视图及截面图；

[0030] 图9是说明晶体管的截面图；

[0031] 图10A至图10C是说明多层膜的能带结构的图；

[0032] 图11A至图11C是说明晶体管的制造方法的截面图；

[0033] 图12A和图12B是说明晶体管的制造方法的截面图；

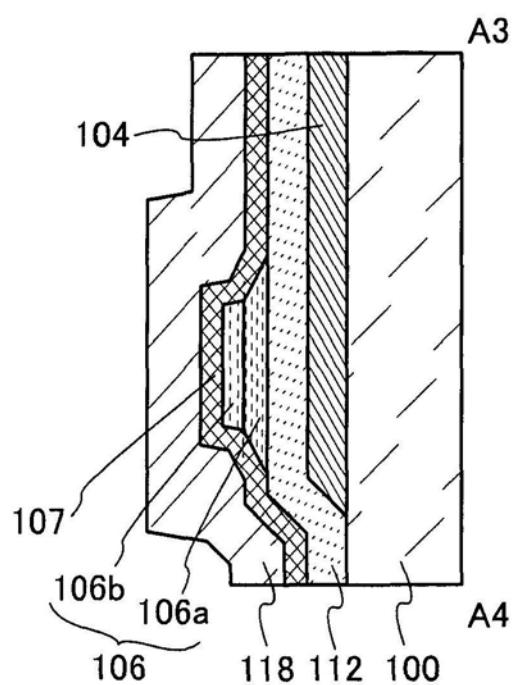

[0034] 图13A至图13C是说明晶体管的俯视图及截面图；

- [0035] 图14A至图14C是说明晶体管的俯视图及截面图；

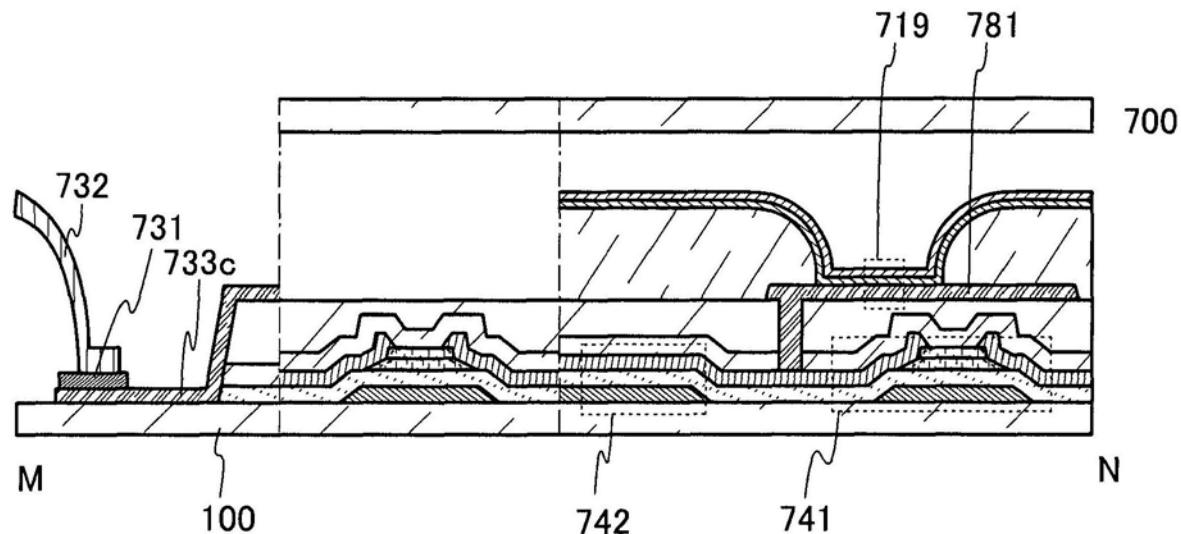

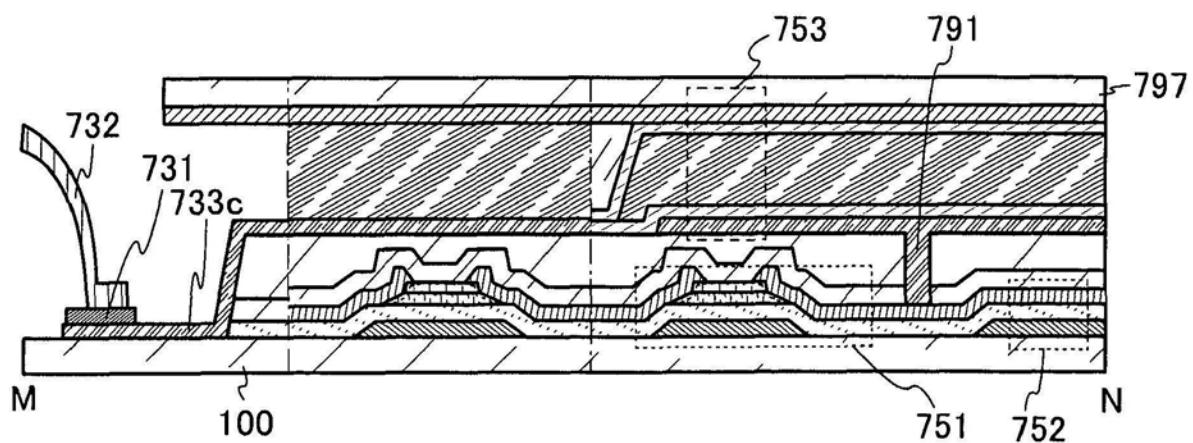

- [0036] 图15是示出EL显示装置的一个例子的电路图；

- [0037] 图16A至图16C是示出EL显示装置的一个例子的俯视图及截面图；

- [0038] 图17A和图17B是示出EL显示装置的一个例子的截面图；

- [0039] 图18是示出液晶显示装置的一个例子的电路图；

- [0040] 图19A至图19C是示出液晶显示装置的一个例子的截面图；

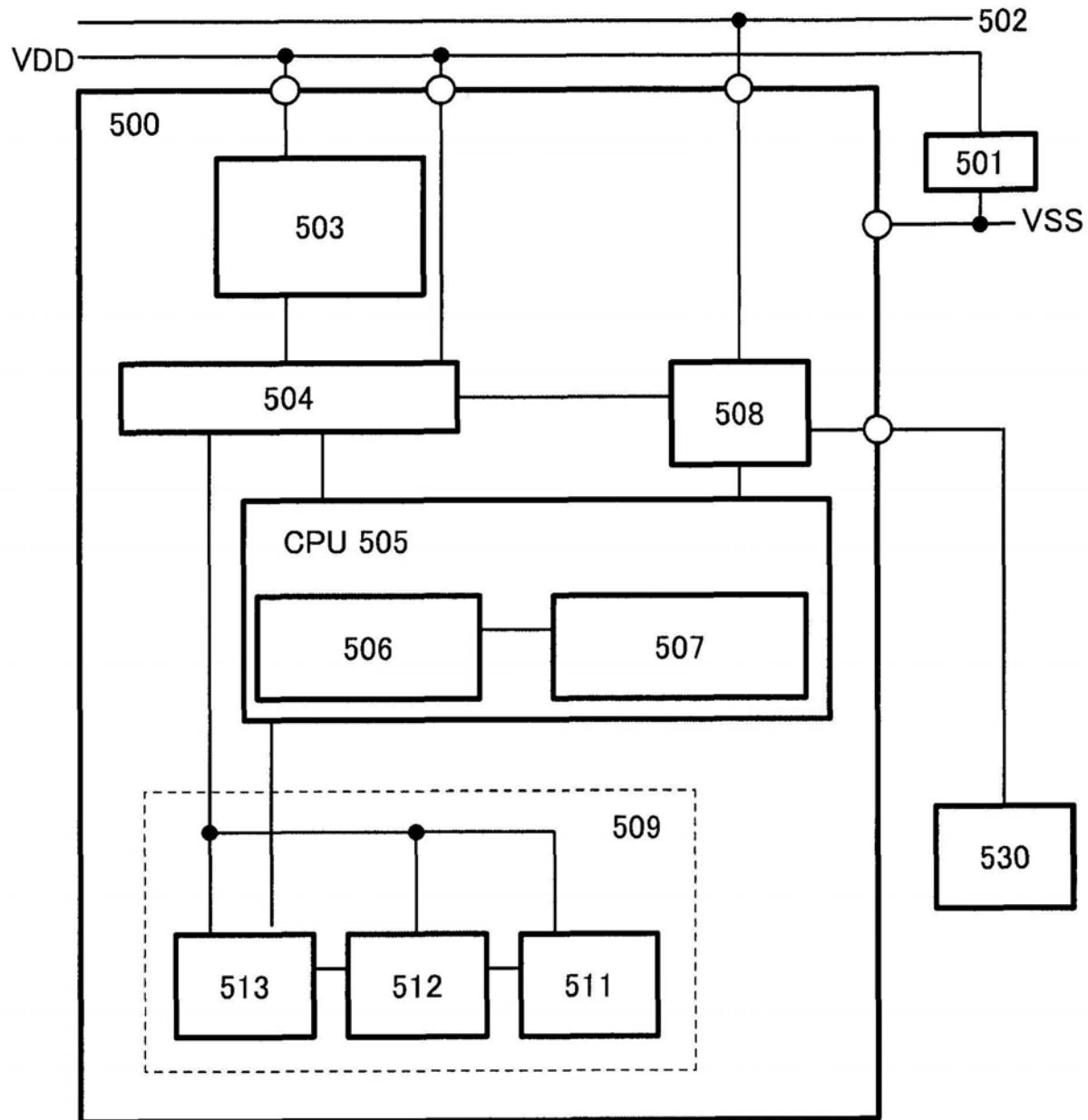

- [0041] 图20是示出半导体装置的一个例子的方框图；

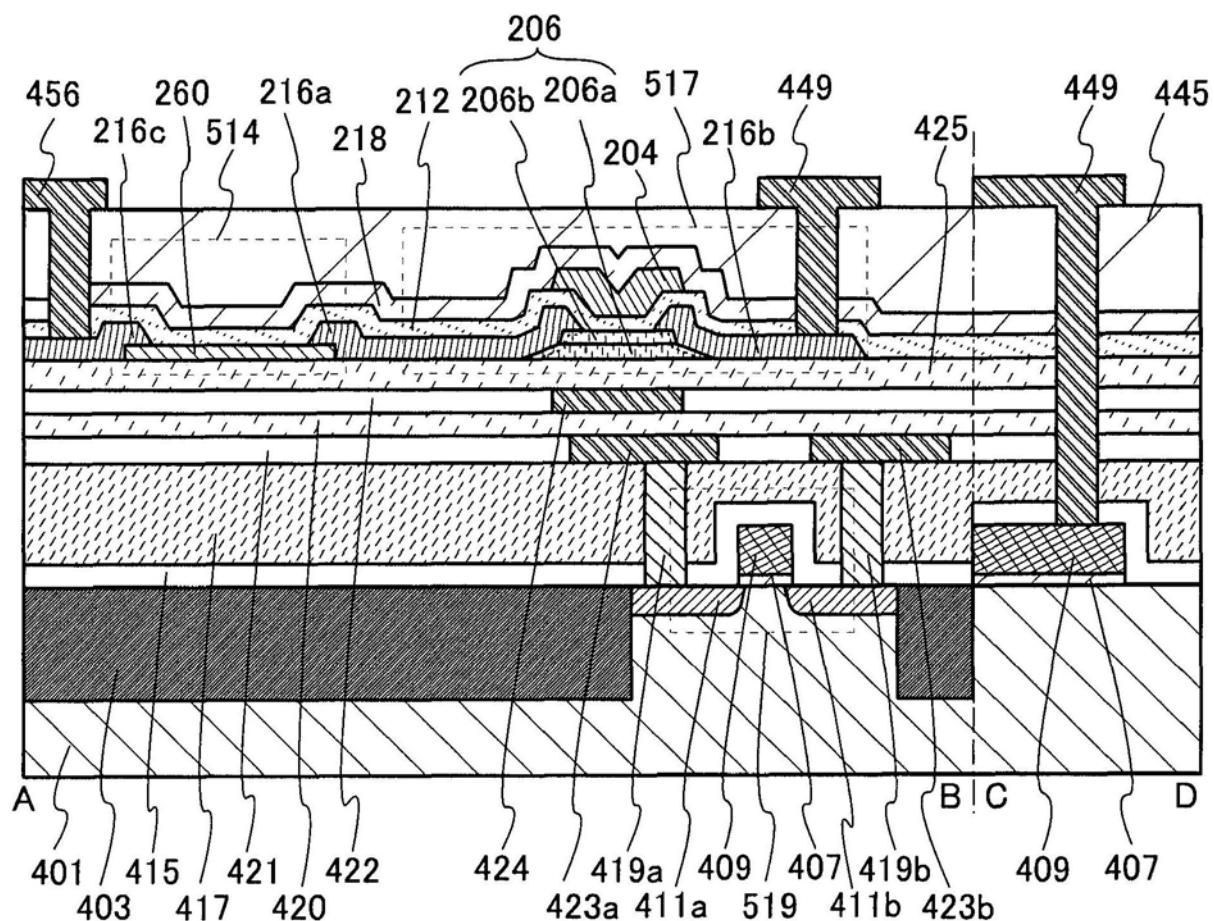

- [0042] 图21是示出半导体装置的一个例子的截面图；

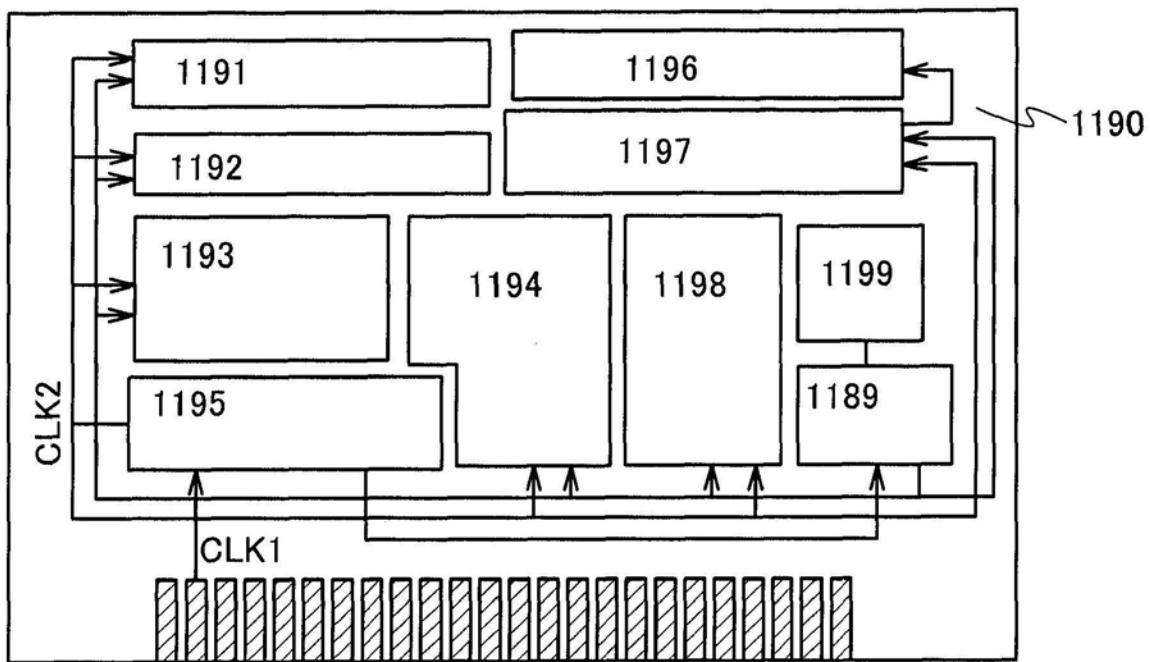

- [0043] 图22A至图22C是示出CPU的一个例子的方框图；

- [0044] 图23A至图23C是示出电子设备的一个例子的图；

- [0045] 图24是说明蚀刻液与蚀刻速度的关系的图；

- [0046] 图25A和图25B是说明STEM图像的图；

- [0047] 图26是说明STEM图像的图；

- [0048] 图27A和图27B是说明STEM图像的图；

- [0049] 图28A和图28B是说明STEM图像的图；

- [0050] 图29A和图29B是说明STEM图像的图；

- [0051] 图30A和图30B是说明STEM图像的图；

- [0052] 图31A和图31B是说明多层膜的结构的图；

- [0053] 图32A和图32B是说明多层膜的结构的图。

- [0054] 符号说明

- [0055] 100 基板

- [0056] 104 栅电极

- [0057] 106 多层膜

- [0058] 106a 氧化物半导体膜

- [0059] 106b 氧化物膜

- [0060] 106c 低电阻区

- [0061] 106d 低电阻区

- [0062] 107 氧化物膜

- [0063] 112 栅极绝缘膜

- [0064] 113 台阶

- [0065] 116a 源电极

- [0066] 116b 漏电极

- [0067] 117 氧化物膜

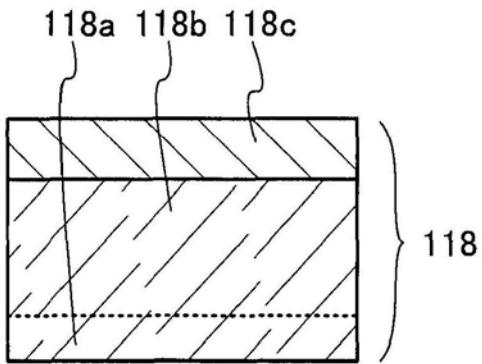

- [0068] 118 保护绝缘膜

- [0069] 118a 氧化硅膜

- [0070] 118b 氧化硅膜

- [0071] 118c 氮化硅膜

- [0072] 126a 氧化物半导体膜

- [0073] 126b 氧化物膜

- [0074] 200 基板

- [0075] 202 基底绝缘膜

- [0076] 204 栅电极

- [0077] 206 多层膜

- [0078] 206a 氧化物半导体膜

- [0079] 206b 氧化物膜

- [0080] 206c 氧化物膜

- [0081] 206d 低电阻区

- [0082] 206e 低电阻区

- [0083] 207 氧化物膜

- [0084] 212 栅极绝缘膜

- [0085] 212a 源电极

- [0086] 212b 漏电极

- [0087] 213 台阶

- [0088] 214 台阶

- [0089] 216a 源电极

- [0090] 216b 漏电极

- [0091] 216c 电极

- [0092] 218 保护绝缘膜

- [0093] 226a 氧化物半导体膜

- [0094] 226b 氧化物膜

- [0095] 226c 氧化物膜

- [0096] 260 半导体膜

- [0097] 401 半导体基板

- [0098] 403 元件分离区

- [0099] 407 栅极绝缘膜

- [0100] 409 栅电极

- [0101] 411a 杂质区

- [0102] 411b 杂质区

- [0103] 415 绝缘膜

- [0104] 417 绝缘膜

- [0105] 419 晶体管

- [0106] 419a 接触插头

- [0107] 419b 接触插头

- [0108] 420 绝缘膜

- [0109] 421 绝缘膜

- [0110] 422 绝缘膜

- [0111] 423a 布线

- [0112] 423b 布线

- [0113] 424 电极

- [0114] 425 绝缘膜

- [0115] 445 绝缘膜

- [0116] 449 布线

- [0117] 456 布线

- [0118] 500 微型计算机

- [0119] 501 直流电源

- [0120] 502 总线

- [0121] 503 电源门控制器

- [0122] 504 电源门

- [0123] 505 CPU

- [0124] 506 易失性存储部

- [0125] 507 非易失性存储部

- [0126] 508 接口

- [0127] 509 检测部

- [0128] 511 光传感器

- [0129] 512 放大器

- [0130] 513 AD转换器

- [0131] 514 光电转换元件

- [0132] 517 晶体管

- [0133] 519 晶体管

- [0134] 530 发光元件

- [0135] 700 基板

- [0136] 719 发光元件

- [0137] 720 绝缘膜

- [0138] 721 绝缘膜

- [0139] 731 端子

- [0140] 732 FPC

- [0141] 733a 布线

- [0142] 733b 布线

- [0143] 733c 布线

- [0144] 734 密封材料

- [0145] 735 驱动电路

- [0146] 736 驱动电路

- [0147] 737 像素

- [0148] 741 晶体管

- [0149] 742 电容器

- [0150] 743 开关元件

- [0151] 744 信号线

- [0152] 750 像素

- [0153] 751 晶体管

- [0154] 752 电容器

- [0155] 753 液晶元件

- [0156] 754 扫描线

- [0157] 755 信号线

- [0158] 781 电极

- [0159] 782 发光层

- [0160] 783 电极

- [0161] 784 分隔壁

- [0162] 785a 中间层

- [0163] 785b 中间层

- [0164] 785c 中间层

- [0165] 785d 中间层

- [0166] 786a 发光层

- [0167] 786b 发光层

- [0168] 786c 发光层

- [0169] 791 电极

- [0170] 792 绝缘膜

- [0171] 793 液晶层

- [0172] 794 绝缘膜

- [0173] 795 隔离物

- [0174] 796 电极

- [0175] 797 基板

- [0176] 801 玻璃基板

- [0177] 803 In-Ga-Zn氧化物膜

- [0178] 805 In-Ga-Zn氧化物膜

- [0179] 807 抗蚀剂

- [0180] 811 玻璃基板

- [0181] 813 In-Ga-Zn氧化物膜

- [0182] 815 In-Ga-Zn氧化物膜

- [0183] 817 抗蚀剂

- [0184] 821 氮化硅膜

- [0185] 823 氧氮化硅膜

- [0186] 825 氧化物半导体膜

- [0187] 826 膜

- [0188] 827 氧氮化硅膜

- [0189] 829 低密度区

- [0190] 831 玻璃基板

- [0191] 833 氧氮化硅膜

- [0192] 835 氧化物半导体膜

- [0193] 837 氧氮化硅膜

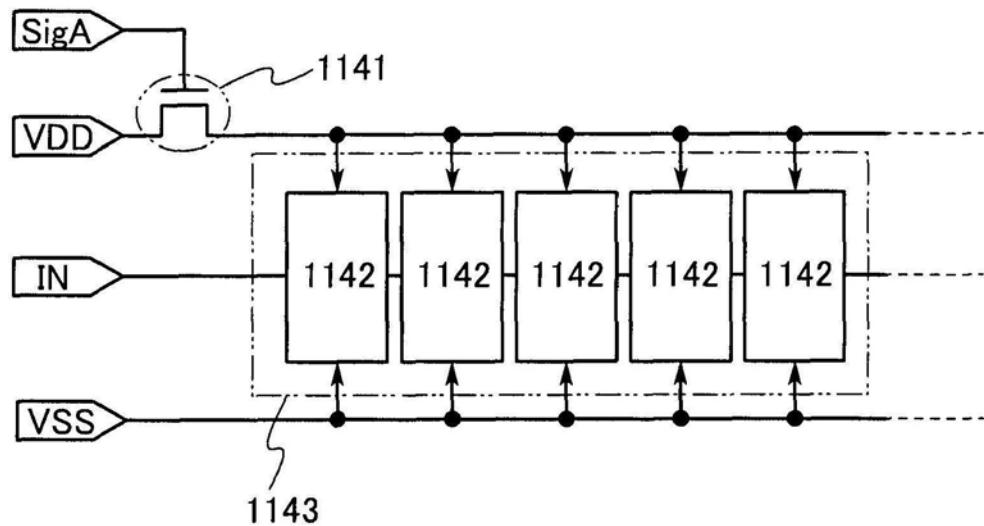

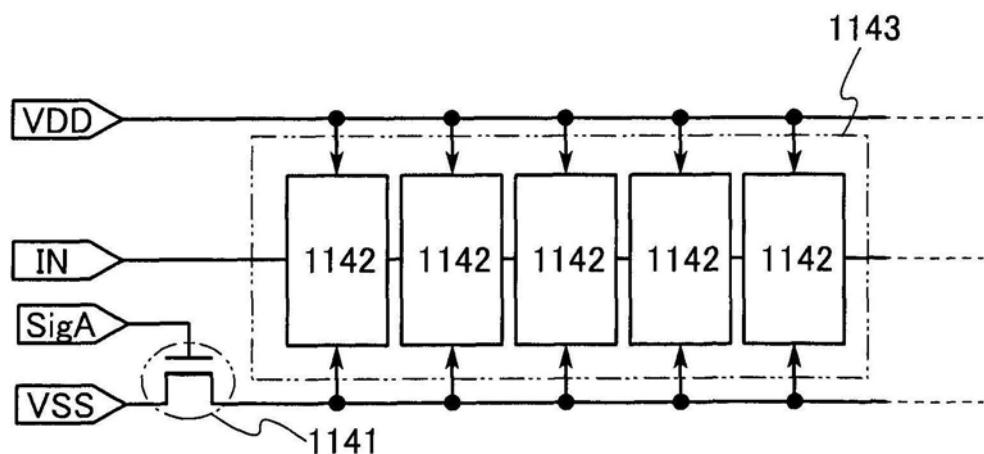

- [0194] 1141 开关元件

- [0195] 1142 存储单元

- [0196] 1143 存储单元组

- [0197] 1189 ROM接口

- [0198] 1190 基板

- [0199] 1191 ALU

- [0200] 1192 ALU控制器

- [0201] 1193 指令解码器

- [0202] 1194 中断控制器

- [0203] 1195 时序控制器

- [0204] 1196 寄存器

- [0205] 1197 寄存器控制器

- [0206] 1198 总线接口

- [0207] 1199 ROM

- [0208] 8100 警报装置

- [0209] 8101 微型计算机

- [0210] 8200 室内机

- [0211] 8201 框体

- [0212] 8202 送风口

- [0213] 8203 CPU

- [0214] 8204 室外机

- [0215] 8300 电冷藏冷冻箱

- [0216] 8301 框体

- [0217] 8302 冷藏室用门

- [0218] 8303 冷冻室用门

- [0219] 8304 CPU

- [0220] 9700 电动汽车

- [0221] 9701 二次电池

- [0222] 9702 控制电路

- [0223] 9703 驱动装置

- [0224] 9704 处理装置

### 具体实施方式

[0225] 下面,参照附图对本发明的实施方式进行详细说明。但是,本发明不局限于以下说明,只要是本领域技术人员就可以很容易地理解其实施方式和详细内容可以进行各种变换。另外,本发明不应该被解释为仅限定在以下所示的实施方式所记载的内容中。此外,当

利用附图说明发明的结构时,表示相同对象的附图标记在不同的附图中共同使用。另外,在表示相同的对象时,有时使用相同的阴影图案,而不特别附加标记。

[0226] 作为第一、第二等而附上的序数词是为了方便而使用的,并不表示工序顺序或层叠顺序。此外,在本说明书中,不表示作为用于特定发明的事项的固有名称。

[0227] 另外,电压大多指某个电位与标准电位(例如,接地电位(GND)或源极电位)之间的电位差。由此,可以将电压改称为电位。

[0228] 另外,即使在记载为“电连接”的情况下,也有时在现实的电路中没有物理连接的部分而只是布线延伸。

[0229] 另外,在电路动作中电流方向发生变化等的情况下,源极及漏极的功能有时互相调换。因此,在本说明书中,源极及漏极这样的术语可以互相调换而使用。

[0230] 在本说明书中,“平行”是指两条直线以所呈的角度为-10°以上且10°以下的方式配置的状态,因此也包括角度为-5°以上且5°以下的情况。另外,“垂直”是指两条直线以所呈的角度为80°以上且100°以下的方式配置的状态,因此也包括角度为85°以上且95°以下的情况。

[0231] 另外,在本说明书中,在结晶为三方晶或菱方晶的情况下,以六方晶系来表示。

[0232] 此外,在本说明书等中,各实施方式及各实施例所记载的结构及内容可以适当地组合。

[0233] 实施方式1

[0234] 在本实施方式中,说明本发明的一个方式的晶体管。

[0235] 1-1. 晶体管结构(1)

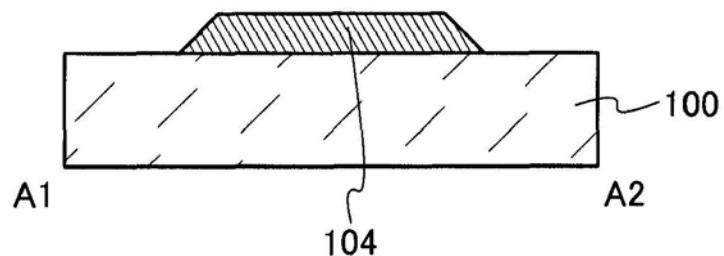

[0236] 图1A至图1D示出BGTC结构的晶体管的俯视图及截面图。图1A示出晶体管的俯视图。图1B示出对应于图1A所示的点划线A1-A2的截面图。图1C示出对应于图1A所示的点划线A3-A4的截面图。另外,在图1A中,为了使附图清楚,省略了该晶体管的构成要素的一部分(栅极绝缘膜及保护绝缘膜等)。

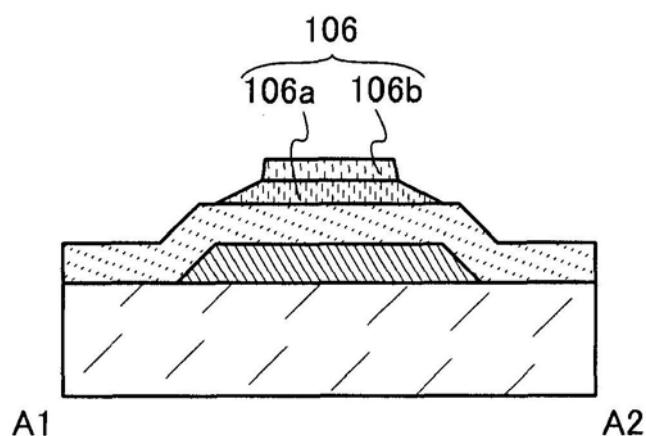

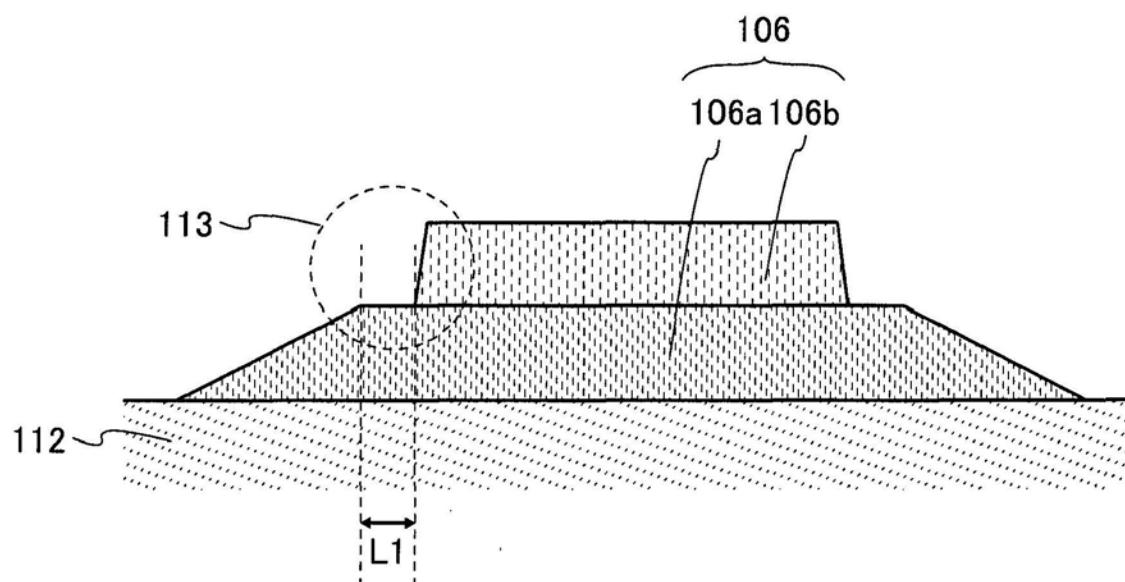

[0237] 在本项中说明底栅型晶体管。在此,使用图1A至图1D说明作为一种底栅型晶体管的底栅顶接触结构(BGTC结构)的晶体管。图1B所示的晶体管包括:设置在基板100上的栅电极104;设置在栅电极104上的栅极绝缘膜112;设置在栅极绝缘膜112上的包含氧化物半导体膜106a以及设置在氧化物半导体膜106a上的氧化物膜106b的多层膜106;设置在栅极绝缘膜112和多层膜106上的源电极116a及漏电极116b;设置在多层膜106、源电极116a以及漏电极116b上的保护绝缘膜118。

[0238] 另外,根据用于源电极116a及漏电极116b的导电膜的种类,有时通过从多层膜106的一部分夺取氧或者形成混合层,而在多层膜106中形成低电阻区106c及低电阻区106d。在图1B中,低电阻区106c及低电阻区106d是多层膜106中的与源电极116a及漏电极116b接触的界面附近的区域(多层膜106的虚线与源电极116a及漏电极116b之间的区域)。低电阻区106c及低电阻区106d的一部或全部作为源极区及漏极区发挥功能。

[0239] 在图1A中的重叠于栅电极104的区域中,将源电极116a和漏电极116b之间的间隔称为沟道长度。但是,在晶体管包括源极区和漏极区的情况下,在重叠于栅电极104的区域中,也可以将低电阻区106c与低电阻区106d之间的间隔称为沟道长度。

[0240] 此外,沟道形成区是指在多层膜106中重叠于栅电极104并且夹在源电极116a和漏

电极116b的区域(参照图1B)。另外,沟道区是指在沟道形成区中的电流主要流过的区域。在此,沟道区是沟道形成区中的氧化物半导体膜106a的一部分。

[0241] 此外,如图1A所示那样,在上表面形状中以多层膜106包含于栅电极104的内侧的方式设置栅电极104。通过这样设置,当光从基板100一侧入射时,可以抑制在多层膜106中因光而产生载流子。就是说,栅电极104具有作为遮光膜的功能。但是,也可以形成多层膜106直到栅电极104的外侧为止。

[0242] 氧化物半导体膜106a的下表面是指,相当于氧化物半导体膜106a的基板100一侧的表面或氧化物半导体膜106a的与栅极绝缘膜112接触的表面。氧化物膜106b的下表面是指,相当于氧化物膜106b的基板100一侧的表面或氧化物膜106b与氧化物半导体膜106a之间的边界面。此外,多层膜106的层叠结构通过使用STEM(Scanning Transmission Electron Microscopy:扫描透射电子显微术)观察,可以确认出边界。但是,根据用于氧化物半导体膜106a及氧化物膜106b的材料,有时不能明确地确认出该边界。

[0243] 1-1-1. 多层膜

[0244] 以下,参照图1A至图2说明多层膜106和构成多层膜106的氧化物半导体膜106a及氧化物膜106b。

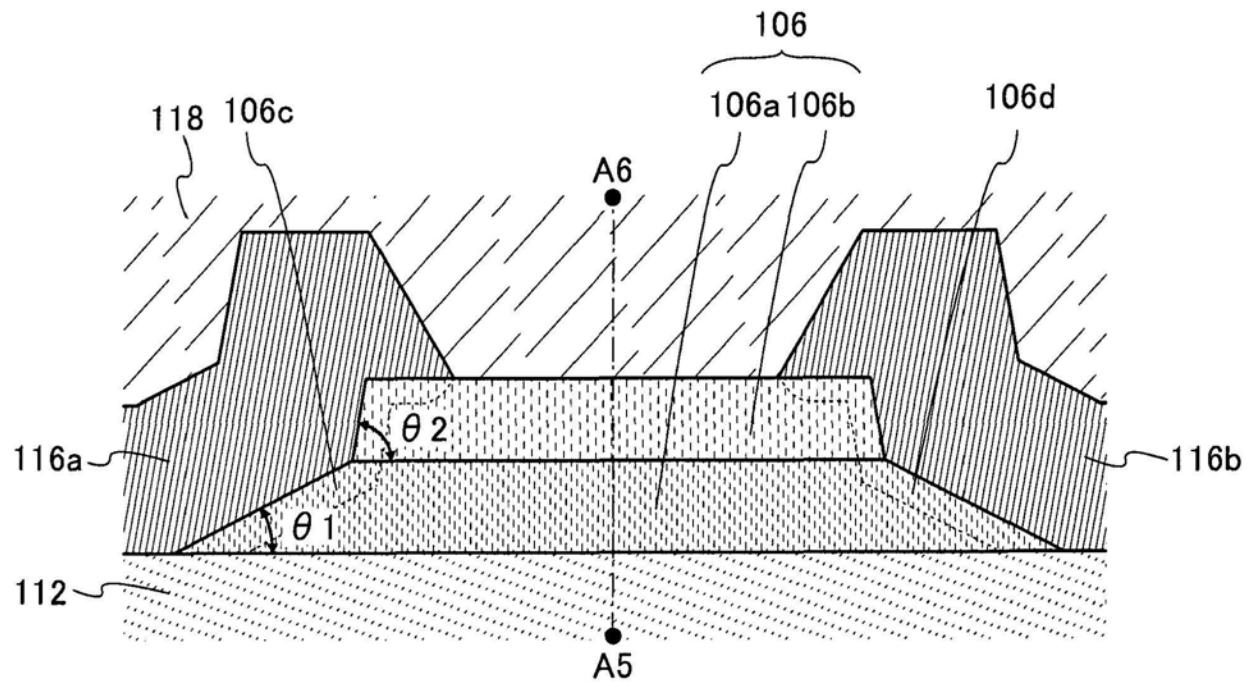

[0245] 图2是图1B的由虚线围绕的区域的放大图。

[0246] 在多层膜106中,至少氧化物半导体膜106a具有锥形状。优选的是,氧化物膜106b也具有锥形状。另外,氧化物半导体膜106a的锥形状与氧化物膜106b的锥形状不同。

[0247] 具体而言,在氧化物半导体膜106a中,将氧化物半导体膜106a的下表面与氧化物半导体膜106a的侧面所呈的角度称为第一角度θ1,并且在氧化物膜106b中,将氧化物膜106b的下表面与氧化物膜106b的侧面所呈的角度称为第二角度θ2。在这种情况下,第一角度θ1可以为锐角,第二角度θ2可以为锐角或垂直。

[0248] 优选的是,第一角度θ1及第二角度θ2都是锐角,并且第一角度θ1小于第二角度θ2。

[0249] 另外,第一角度θ1为10°以上且小于90°,优选为30°以上且70°以下。第二角度θ2为10°以上且小于90°,优选为30°以上且70°以下。

[0250] 如上所述,通过将多层膜106的形状设为具有不同的锥角的锥形状,可以得到下述效果。关于多层膜106,通过将其设为具有不同的锥角的锥形状,与具有恒定的锥角的锥形状相比,可以扩大它与源电极116a及漏电极116b之间的接触面积。由此,可以降低多层膜106与源电极116a以及漏电极116b之间的接触电阻并使晶体管的导通电流增大。

[0251] 另外,通过使第二角度θ2大于第一角度θ1,可以减小氧化物膜106b与源电极116a及漏电极116b之间的接触面积,从而可以减小形成在氧化物膜106b中的低电阻区。由此,可以抑制氧化物膜106b的低电阻化,并抑制在源电极116a与漏电极116b之间产生的泄漏路径,同时能够在作为沟道区发挥功能的氧化物半导体膜106a中有效地形成低电阻区,从而可以同时实现晶体管的导通电流的增大和晶体管的截止电流的降低。

[0252] 另外,氧化物半导体膜106a的上端与氧化物膜106b的下端大致一致(参照图2)。就是说,多层膜106没有由氧化物半导体膜106a和氧化物膜106b形成的大的台阶113(参照图31A和图31B)。因此,可以抑制设置在多层膜106上的膜(例如,被加工成源电极116a及漏电极116b的导电膜)的断开,而可以制造电气特性良好的晶体管。此外,“氧化物半导体膜106a的上端与氧化物膜106b的下端大致一致”是指氧化物膜106b的下端与氧化物半导体膜106a

的上端之间的距离L1为30nm以下,优选为10nm以下(参照图31A和图31B)。

[0253] 在通过蚀刻来形成多层膜106时,利用氧化物半导体膜106a与氧化物膜106b之间的蚀刻速度的差异,可以形成上述锥形状。尤其是,通过使氧化物半导体膜106a的蚀刻速度低于氧化物膜106b的蚀刻速度,可以形成上述锥形状。

[0254] 例如,通过作为蚀刻剂使用包含磷酸的溶液的湿蚀刻,可以形成上述锥形状。

[0255] 通过湿蚀刻形成多层膜106的优点是如下。例如,在被加工成多层膜106的氧化物半导体膜及氧化物膜具有针孔等缺陷的情况下,如果通过干蚀刻对该氧化物半导体膜及该氧化物膜进行加工的话,有时通过该针孔对设置在该氧化物半导体膜及该氧化物膜下的绝缘膜(栅极绝缘膜等)也进行蚀刻。由此,在该绝缘膜中,有时形成了直到设置在该绝缘膜之下的电极(栅电极等)的开口。如果在这种状况下制造晶体管的话,有时会制造出在该电极与形成在多层膜106上的电极(源电极及漏电极等)之间产生短路等特性不良的晶体管。就是说,如果通过干蚀刻形成多层膜106的话,有时关系到晶体管的成品率的下降。因此,通过利用湿蚀刻形成多层膜106,可以高生产率地制造电气特性良好的晶体管。

[0256] 另外,由于湿蚀刻的蚀刻速度根据蚀刻剂的浓度及蚀刻剂的温度等而变化,所以优选将氧化物半导体膜106a的蚀刻速度适当地调整为低于氧化物膜106b的蚀刻速度的速度。另外,通过使第二角度θ2大于第一角度θ1,可以尽可能地减小在该湿蚀刻中暴露于蚀刻剂的面积。另外,通过使第二角度θ2大于第一角度θ1,可以减小因为由蚀刻剂所引起的污染或缺陷的产生而形成在氧化物膜106b中的低电阻区。

[0257] 例如,作为上述蚀刻剂,可以举出调整为85%左右的磷酸水溶液或混合了磷酸(72%)、硝酸(2%)及醋酸(9.8%)的混合溶液(也称为混合酸铝溶液)。另外,蚀刻剂的温度优选为20℃至35℃左右的室温或常温。此外,还可以使用上述以外的蚀刻剂。

[0258] 氧化物半导体膜106a是至少包含铟的氧化物半导体膜。例如,除了铟之外还可以包含锌。另外,氧化物半导体膜106a除铟之外,优选还包含元素M(M是Al、Ga、Ge、Y、Zr、Sn、La、Ce或Nd)。

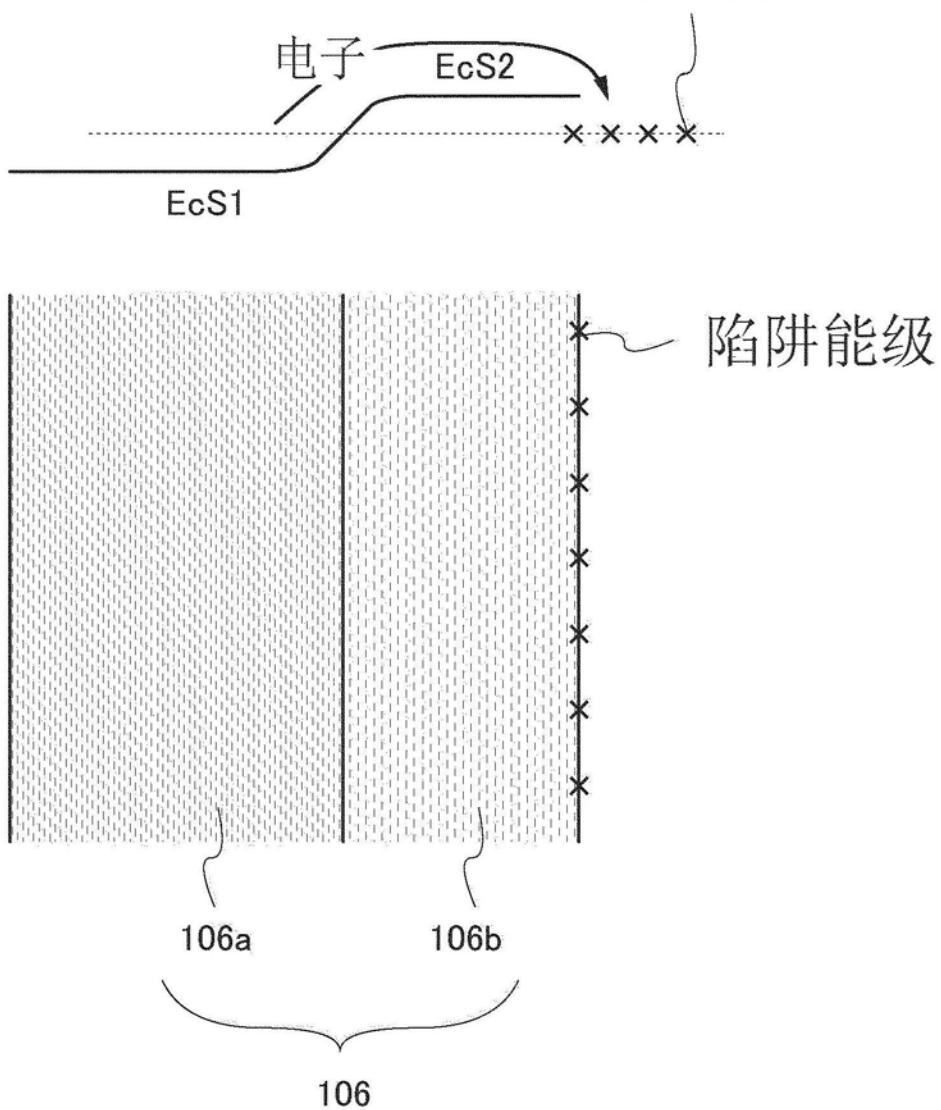

[0259] 氧化物膜106b是这样的氧化物膜:由构成氧化物半导体膜106a的元素中的一种以上构成,并且,其导带底的能量相比氧化物半导体膜106a更接近于真空能级0.05eV以上、0.07eV以上、0.1eV以上或0.15eV以上且2eV以下、1eV以下、0.5eV以下或0.4eV以下。此时,当对栅电极104施加电场,沟道形成于多层膜106中导带底的能量较低的氧化物半导体膜106a。就是说,通过在氧化物半导体膜106a与保护绝缘膜118之间具有氧化物膜106b,可以将晶体管的沟道形成在不与保护绝缘膜118接触的氧化物半导体膜106a。另外,由构成氧化物半导体膜106a的元素中的一种以上构成氧化物膜106b,所以在氧化物半导体膜106a与氧化物膜106b之间不容易产生界面散射。因此,在氧化物半导体膜106a与氧化物膜106b之间不阻碍载流子的移动,从而提高晶体管的场效应迁移率。另外,在氧化物半导体膜106a与氧化物膜106b之间不容易形成界面能级。当在氧化物半导体膜106a与氧化物膜106b之间存在界面能级,有时会形成将该界面作为沟道的阈值电压不同的第二晶体管,使得晶体管的外观上的阈值电压发生变动。因此,通过设置氧化物膜106b,可以降低晶体管的阈值电压等电气特性的不均匀。

[0260] 例如,氧化物膜106b以比氧化物半导体膜106a高的原子个数比来包含Al、Ga、Ge、Y、Zr、Sn、La、Ce、Nd或Hf(尤其是Al或Ga)即可。具体地,作为氧化物膜106b,使用以比氧化物

半导体膜106a高1.5倍以上、优选为2倍以上、更优选为3倍以上的原子个数比来包含上述元素的氧化物膜。上述元素与氧坚固地键合，所以具有抑制在氧化物膜中产生氧空位的功能。就是说，与氧化物半导体膜106a相比，氧化物膜106b不容易产生氧空位。

[0261] 例如，在氧化物半导体膜106a是In-M-Zn氧化物并且将氧化物膜106b也设为In-M-Zn氧化物的时候，当将氧化物膜106b设定为 $In:M:Zn=x_2:y_2:z_2$  [原子个数比] 并且将氧化物半导体膜106a设定为 $In:M:Zn=x_1:y_1:z_1$  [原子个数比]，选择 $y_1/x_1$ 比 $y_2/x_2$ 大的氧化物膜106b及氧化物半导体膜106a。此外，元素M是与氧的键合力比In与氧的键合力大的金属元素，例如可以举出Al、Ga、Ge、Y、Zr、Sn、La、Ce或Nd（尤其是Al或Ga）等。优选的是，选择 $y_1/x_1$ 比 $y_2/x_2$ 大1.5倍以上的氧化物膜106b及氧化物半导体膜106a。更优选的是，选择 $y_1/x_1$ 比 $y_2/x_2$ 大2倍以上的氧化物膜106b及氧化物半导体膜106a。进一步优选的是，选择 $y_1/x_1$ 比 $y_2/x_2$ 大3倍以上的氧化物膜106b及氧化物半导体膜106a。此时，在氧化物膜106b中，如果 $y_2$ 为 $x_2$ 以上就可以赋予晶体管稳定的电气特性，所以是优选的。但是，如果 $y_2$ 为 $x_2$ 的3倍以上，则晶体管的场效应迁移率变低，所以优选 $y_2$ 不到 $x_2$ 的3倍。

[0262] 另外，在氧化物膜106b致密时，不容易因用于晶体管的制造工序的等离子体等而产生损伤，由此可以赋予晶体管稳定的电气特性，所以是优选的。

[0263] 将氧化物膜106b的厚度设定为3nm以上且100nm以下，优选为3nm以上且50nm以下。另外，将氧化物半导体膜106a的厚度设定为3nm以上且200nm以下，优选为3nm以上且100nm以下，更优选为3nm以上且50nm以下。

[0264] 以下说明氧化物半导体膜106a及氧化物膜106b的硅浓度。此外，为了使晶体管的电气特性稳定，降低氧化物半导体膜106a中的杂质浓度而实现本征或实际上本征是有效的。具体地，将氧化物半导体膜的载流子密度设为低于 $1 \times 10^{17}/\text{cm}^3$ 、低于 $1 \times 10^{15}/\text{cm}^3$ 或低于 $1 \times 10^{13}/\text{cm}^3$ 即可。另外，在氧化物半导体膜中，除了主成分以外（低于1原子%）的轻元素、半金属元素及金属元素等都是杂质。例如，在氧化物半导体膜中，氢、氮、碳、硅、锗、钛及铪成为杂质。为了降低氧化物半导体膜中的杂质浓度，优选还降低相接近的栅极绝缘膜112及氧化物膜106b中的杂质浓度。

[0265] 例如，在氧化物半导体膜106a包含硅的情况下，形成杂质能级。尤其是，当在氧化物半导体膜106a与氧化物膜106b之间存在硅，该杂质能级就成为陷阱。因此，将氧化物半导体膜106a和氧化物膜106b之间的硅浓度设定为低于 $1 \times 10^{19}\text{atoms}/\text{cm}^3$ 、优选低于 $5 \times 10^{18}\text{atoms}/\text{cm}^3$ ，更优选低于 $2 \times 10^{18}\text{atoms}/\text{cm}^3$ 。

[0266] 另外，在氧化物半导体膜106a中，氢及氮形成施主能级，使得载流子密度增大。氧化物半导体膜106a的氢浓度在二次离子质谱分析法（SIMS：Secondary Ion Mass Spectrometry）中为 $2 \times 10^{20}\text{atoms}/\text{cm}^3$ 以下，优选为 $5 \times 10^{19}\text{atoms}/\text{cm}^3$ 以下，更优选为 $1 \times 10^{19}\text{atoms}/\text{cm}^3$ 以下，进一步优选为 $5 \times 10^{18}\text{atoms}/\text{cm}^3$ 以下。另外，氮浓度在SIMS中低于 $5 \times 10^{19}\text{atoms}/\text{cm}^3$ ，优选为 $5 \times 10^{18}\text{atoms}/\text{cm}^3$ 以下，更优选为 $1 \times 10^{18}\text{atoms}/\text{cm}^3$ 以下，进一步优选为 $5 \times 10^{17}\text{atoms}/\text{cm}^3$ 以下。

[0267] 另外，为了降低氧化物半导体膜106a的氢浓度及氮浓度，优选降低氧化物膜106b的氢浓度及氮浓度。氧化物膜106b的氢浓度在SIMS中为 $2 \times 10^{20}\text{atoms}/\text{cm}^3$ 以下，优选为 $5 \times 10^{19}\text{atoms}/\text{cm}^3$ 以下，更优选为 $1 \times 10^{19}\text{atoms}/\text{cm}^3$ 以下，进一步优选为 $5 \times 10^{18}\text{atoms}/\text{cm}^3$ 以下。另外，氮浓度在SIMS中低于 $5 \times 10^{19}\text{atoms}/\text{cm}^3$ ，优选为 $5 \times 10^{18}\text{atoms}/\text{cm}^3$ 以下，更优选为 $1 \times$

$10^{18}$ atoms/cm<sup>3</sup>以下,进一步优选为 $5\times10^{17}$ atoms/cm<sup>3</sup>以下。

[0268] 氧化物半导体膜106a及氧化物膜106b为非晶质或结晶质。作为该结晶质,可以举出多晶结构、单晶结构及微晶结构等。另外,氧化物半导体膜106a及氧化物膜106b也可以是晶粒分散在非晶区中的混合结构。此外,微晶结构的各晶粒的面方位随机,并且微晶结构或混合结构所包含的晶粒的粒径为0.1nm以上且10nm以下,优选为1nm以上且10nm以下,更优选为2nm以上且4nm以下。

[0269] 关于氧化物半导体膜106a及氧化物膜106b,优选的是,氧化物半导体膜106a为结晶质,氧化物膜106b为非晶质或结晶质。由于形成沟道的氧化物半导体膜106a为结晶质,所以可以赋予晶体管稳定的电气特性。另外,结晶质的氧化物半导体膜106a优选为CAAC-OS(CAxis Aligned Crystalline Oxide Semiconductor:c轴取向晶体氧化物半导体)。

[0270] 此外,氧化物半导体膜106a优选在非晶膜上形成。例如,可以举出在非晶绝缘膜的表面上或非晶半导体膜的表面上等。通过使用后述成膜方法可以在非晶膜上形成CAAC-OS的氧化物半导体膜106a。

[0271] CAAC-OS膜是具有多个结晶部的氧化物半导体膜之一,大部分的结晶部的尺寸为能够容纳于一边短于100nm的立方体内的尺寸。因此,也包含这样的情况:包括在CAAC-OS膜中的结晶部的尺寸为能够容纳于一边短于10nm、短于5nm或短于3nm的立方体内的尺寸。CAAC-OS膜的缺陷能级密度低。下面,对CAAC-OS膜进行详细的说明。

[0272] 当用TEM观察CAAC-OS膜,无法确认出结晶部与结晶部之间的明确的边界,即晶界(也称为grain boundary)。因此,可以说,CAAC-OS膜不容易发生起因于晶界的电子迁移率的降低。

[0273] 当从大致平行于样品面的方向通过TEM观察CAAC-OS膜(截面TEM图像),则在结晶部中可以确认出金属原子排列为层状。金属原子的各层为反映了形成CAAC-OS膜的有面(也称为被形成面)或CAAC-OS膜的上表面的凸凹的形状,并以平行于CAAC-OS膜的被形成面或上表面的方式排列。

[0274] 另一方面,当从大致垂直于样品面的方向通过TEM观察CAAC-OS膜(平面TEM图像),则在结晶部中可以确认出金属原子排列为三角形状或六角形状。但是,在不同的结晶部之间金属原子的排列没有发现规律性。

[0275] 由截面TEM图像及平面TEM图像可知,CAAC-OS膜的结晶部具有取向性。

[0276] 当使用X射线衍射(XRD:X-Ray Diffraction)装置对CAAC-OS膜进行结构分析,则在例如具有InGaZnO<sub>4</sub>的结晶的CAAC-OS膜的out-of-plane法的分析中,有时在衍射角( $2\theta$ )为31°附近出现峰值。由于该峰值归属于InGaZnO<sub>4</sub>结晶的(009)面,由此可以确认出CAAC-OS膜中的结晶具有c轴取向性,并且c轴朝向大致垂直于CAAC-OS膜的被形成面或上表面的方向。

[0277] 另一方面,在通过使X线从大致垂直于c轴的方向入射到样品的in-plane法对CAAC-OS膜的分析中,有时在 $2\theta$ 为56°附近出现峰值。该峰值归属于InGaZnO<sub>4</sub>结晶的(110)面。只要是InGaZnO<sub>4</sub>的单晶氧化物半导体膜,当将 $2\theta$ 固定为56°附近并在以样品面的法向量为轴( $\Phi$ 轴)旋转样品并且进行分析( $\Phi$ 扫描),则会观察到六个归属于与(110)面等价的结晶面的峰值。与此相对地,在CAAC-OS膜的情况下,即使在将 $2\theta$ 固定为56°附近地进行 $\Phi$ 扫描的情况下,也不会出现明显的峰值。

[0278] 由以上叙述可知,在CAAC-OS膜中,虽然在结晶部之间a轴及b轴的取向的不规则的,但是具有c轴取向,并且c轴朝向平行于被形成面或上表面的法向量的方向。因此,在上述截面TEM观察中确认出的排列为层状的金属原子的各层是与结晶的ab面平行的面。

[0279] 此外,结晶部在形成CAAC-OS膜或进行加热处理等晶体化处理时形成。如上所述,结晶的c轴在平行于CAAC-OS膜的被形成面或上表面的法向量的方向上取向。由此,例如,在CAAC-OS膜的形状因蚀刻等而发生改变的情况下,结晶的c轴有时不平行于CAAC-OS膜的被形成面或上表面的法向量。

[0280] 另外,CAAC-OS膜中的晶体化度也可以不均匀。例如,在CAAC-OS膜的结晶部通过来自CAAC-OS膜的上表面附近的晶体生长而形成的情况下,有时上表面附近的区域相比被形成面附近的区域而晶体化度变高。另外,在对CAAC-OS膜添加杂质的情况下,被添加了杂质的区域的晶体化度改变,有时也部分地形成晶体化度不同的区域。

[0281] 此外,在具有InGaZnO<sub>4</sub>结晶的CAAC-OS膜的out-of-pLane法的分析中,除了在2θ为31°附近的峰值之外,有时还在2θ为36°附近出现峰值。2θ为36°附近的峰值表示在CAAC-OS膜中的一部分中含有不具有c轴取向性的结晶。优选的是,在CAAC-OS膜中在2θ为31°附近示出峰值而在2θ为36°附近时不示出峰值。

[0282] 在使用CAAC-OS的晶体管中,因照射可见光或紫外光而产生的电气特性变动小。因此,该晶体管具有稳定的电气特性。

[0283] 另外,由于氧化物半导体膜106a包含高浓度的硅及碳,有时使得氧化物半导体膜106a的结晶性降低。为了不使氧化物半导体膜106a的结晶性降低,将氧化物半导体膜106a的硅浓度设为低于 $1 \times 10^{19}$ atoms/cm<sup>3</sup>、优选低于 $5 \times 10^{18}$ atoms/cm<sup>3</sup>,更优选低于 $2 \times 10^{18}$ atoms/cm<sup>3</sup>即可。另外,为了不使氧化物半导体膜106a的结晶性降低,将氧化物半导体膜106a的碳浓度设为低于 $1 \times 10^{19}$ atoms/cm<sup>3</sup>、优选低于 $5 \times 10^{18}$ atoms/cm<sup>3</sup>,更优选低于 $2 \times 10^{18}$ atoms/cm<sup>3</sup>。

[0284] 这样地,在形成有沟道的氧化物半导体膜106a具有高结晶性并且起因于杂质或缺陷等的能级少的情况下,使用多层膜106的晶体管具有稳定的电气特性。

[0285] 以下说明多层膜106中的局部能级。通过降低多层膜106中的局部能级密度,可以赋予使用多层膜106的晶体管稳定的电气特性。可以利用恒定光电流测定法(CPM:Constant Photocurrent Method)对多层膜106的局部能级进行评价。

[0286] 为了赋予晶体管稳定的电气特性,将由CPM测定获得的多层膜106中的局部能级的吸收系数设定为小于 $1 \times 10^{-3}$ cm<sup>-1</sup>,优选为小于 $3 \times 10^{-4}$ cm<sup>-1</sup>即可。另外,通过将由CPM测定获得的多层膜106中的局部能级的吸收系数设定为小于 $1 \times 10^{-3}$ cm<sup>-1</sup>,优选为小于 $3 \times 10^{-4}$ cm<sup>-1</sup>,可以提高晶体管的场效应迁移率。此外,为了将由CPM测定获得的多层膜106中的局部能级的吸收系数设定为小于 $1 \times 10^{-3}$ cm<sup>-1</sup>,优选为小于 $3 \times 10^{-4}$ cm<sup>-1</sup>,将作为在氧化物半导体膜106a中形成局部能级的元素的硅、锗、碳、铪或钛等的浓度设定为低于 $2 \times 10^{18}$ atoms/cm<sup>3</sup>,优选为低于 $2 \times 10^{17}$ atoms/cm<sup>3</sup>即可。

[0287] 此外,在CPM测定中,在各波长上进行:调整照射到端子之间的样品表面的光量以使得在对与作为样品的多层膜106接触地设置的电极和电极之间施加电压的状态下光电流值恒定,并且根据照射光量导出吸收系数。在CPM测定中,当样品有缺陷时,对应于存在缺陷的能级的能量(根据波长换算)的吸收系数增加。通过用常数乘以该吸收系数的增加相当

量,可以导出样品的缺陷密度。

[0288] 可以认为,由CPM测定得到的局部能级是起因于杂质或缺陷的能级。就是说,可知,使用由CPM测定得到的局部能级的吸收系数小的多层膜106的晶体管具有稳定的电气特性。

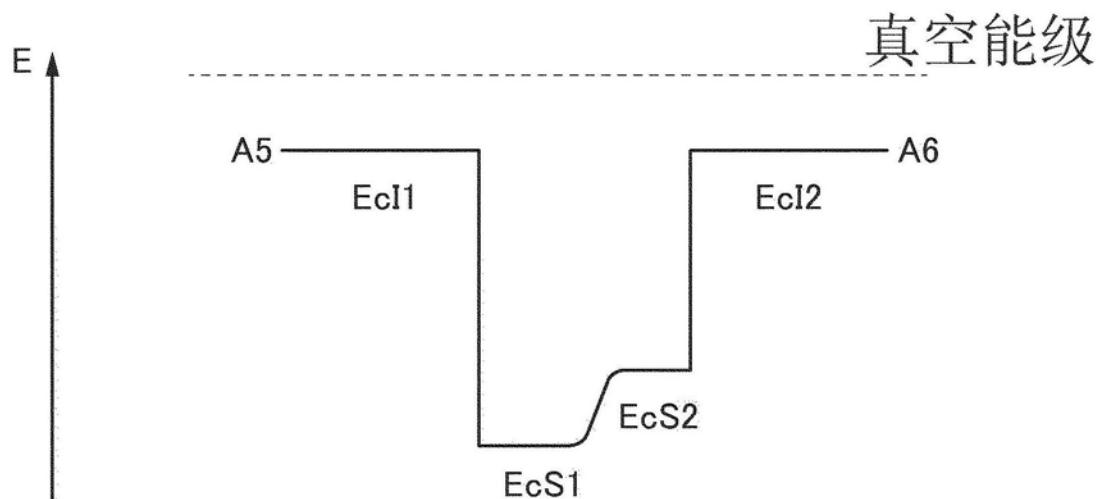

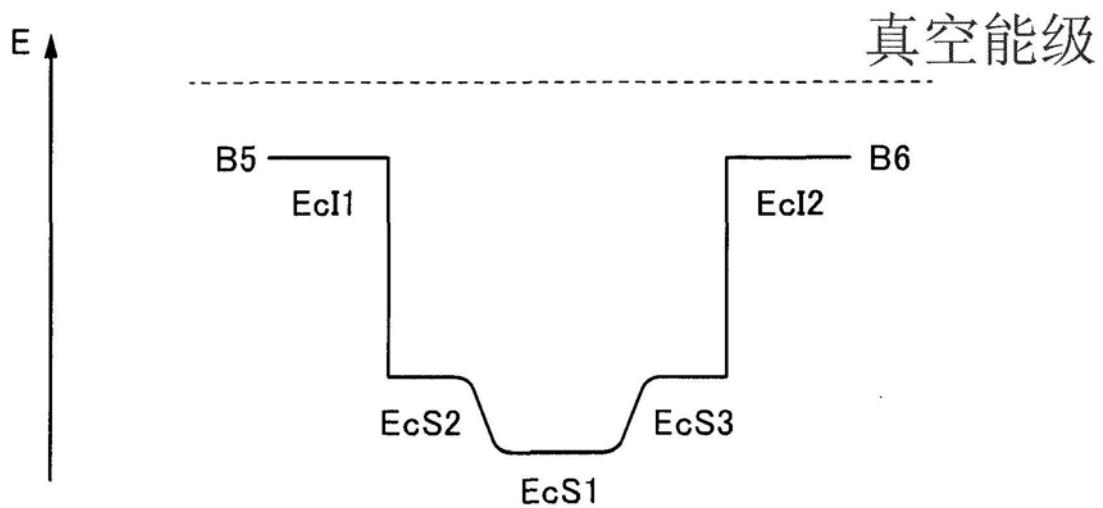

[0289] 以下,参照图3说明多层膜106的能带结构。

[0290] 作为例子,使用能隙为3.15eV的In-Ga-Zn氧化物作为氧化物半导体膜106a,使用能隙为3.5eV的In-Ga-Zn氧化物作为氧化物膜106b。利用光谱椭偏仪(HORIBA JOBIN YVON公司的UT-300)测定能隙。

[0291] 氧化物半导体膜106a及氧化物膜106b的真空能级与价带上端之间的能量差(也称为电离电位)分别为8eV及8.2eV。此外,关于真空能级和价带顶端之间的能量差,利用紫外线光电子能谱(UPS:Ultraviolet Photoelectron Spectroscopy)装置(PHI公司的VersaProbe)进行测定。

[0292] 因此,氧化物半导体膜106a及氧化物膜106b的真空能级和导带底的能量之间的能量差(也称为电子亲和能)分别为4.85eV及4.7eV。

[0293] 图3示意性地示出多层膜106的能带结构的一部分。图3是对应于图2的点划线A5-A6的能带结构。具体而言,说明了与氧化物半导体膜106a以及氧化物膜106b的每一个接触地设置氧化硅膜(栅极绝缘膜112及保护绝缘膜118)的情况。在此,E<sub>cI1</sub>表示氧化硅膜的导带底的能量,E<sub>cS1</sub>表示氧化物半导体膜106a的导带底的能量,E<sub>cS2</sub>表示氧化物膜106b的导带底的能量,E<sub>cI2</sub>表示氧化硅膜的导带底的能量。

[0294] 如图3所示,在氧化物半导体膜106a及氧化物膜106b中,导带底的能量没有位垒而平缓地变化。换而言之,也可以说是连续地变化。这可以说是因为氧化物膜106b包含与氧化物半导体膜106a共同的元素,并且通过在氧化物半导体膜106a和氧化物膜106b之间氧相互移动而形成有混合层。

[0295] 从图3可知,多层膜106的氧化物半导体膜106a成为阱(well),在使用多层膜106的晶体管中沟道区形成于氧化物半导体膜106a。此外,由于多层膜106的导带底的能量连续地变化,所以也可以说氧化物半导体膜106a与氧化物膜106b连续地接合。

[0296] 此外,如图4所示那样,虽然在氧化物膜106b与保护绝缘膜118之间的界面附近有可能形成起因于杂质或缺陷的陷阱能级,但是通过设置氧化物膜106b,可以使氧化物半导体膜106a与该陷阱能级远离。但是,当E<sub>cS1</sub>和E<sub>cS2</sub>之间的能量差小时,有时氧化物半导体膜106a的电子会越过该能量差而到达陷阱能级。电子被陷阱能级捕获,使得在绝缘膜的界面产生负的固定电荷,这导致晶体管的阈值电压向正的方向移动。

[0297] 因此,当将E<sub>cS1</sub>与E<sub>cS2</sub>之间的能量差设为0.1eV以上,优选为0.15eV以上,则可减少晶体管的阈值电压的变动而得到稳定的电气特性,所以是优选的。

[0298] 1-1-2.源电极及漏电极

[0299] 作为源电极116a及漏电极116b,可以以单层或层叠的方式使用包含铝、钛、铬、钴、镍、铜、钇、锆、钼、钌、银、钽以及钨中的一种以上的导电膜。优选的是,源电极116a及漏电极116b为具有包含铜的层的多层膜。通过将具有包含铜的层的多层膜用作源电极116a及漏电极116b,当在与源电极116a及漏电极116b相同的层中形成布线的情况下,可以降低布线电阻。另外,源电极116a及漏电极116b可以为相同的组成,也可以为不同的组成。

[0300] 并且,在将具有包含铜的层的多层膜用作源电极116a及漏电极116b的情况下,由

于铜的影响,有时在氧化物膜106b与保护绝缘膜118之间的界面形成如图4所示那样的陷阱能级。在这种情况下,由于具有氧化物膜106b,所以可以抑制电子被该陷阱能级捕获。因此,可以赋予晶体管稳定的电气特性并降低布线电阻。

[0301] 1-1-3. 保护绝缘膜

[0302] 作为保护绝缘膜118,以单层或层叠的方式使用包含氧化铝、氧化镁、氧化硅、氧氮化硅、氮氧化硅、氮化硅、氧化镓、氧化锗、氧化钇、氧化锆、氧化镧、氧化钕、氧化铪以及氧化钽中的一种以上的绝缘膜即可。

[0303] 例如,保护绝缘膜118采用将氧化硅膜设为第一层并将氮化硅膜设为第二层的多层膜即可。在这种情况下,氧化硅膜也可以为氧氮化硅膜。另外,氮化硅膜也可以为氮氧化硅膜。氧化硅膜优选使用缺陷密度小的氧化硅膜。具体而言,使用如下氧化硅膜:在电子自旋共振(ESR:Electron Spin Resonance)测定中,来源于g值为2.001的信号的自旋的密度为 $3 \times 10^{17}$ spins/cm<sup>3</sup>以下,优选为 $5 \times 10^{16}$ spins/cm<sup>3</sup>以下。氮化硅膜使用氢气及氨气的释放量少的氮化硅膜。氢气及氨气的释放量通过热脱附谱(TDS:Thermal Desorption Spectroscopy)分析进行测定即可。另外,氮化硅膜使用使氢、水及氧不透过或几乎不透过的氮化硅膜。

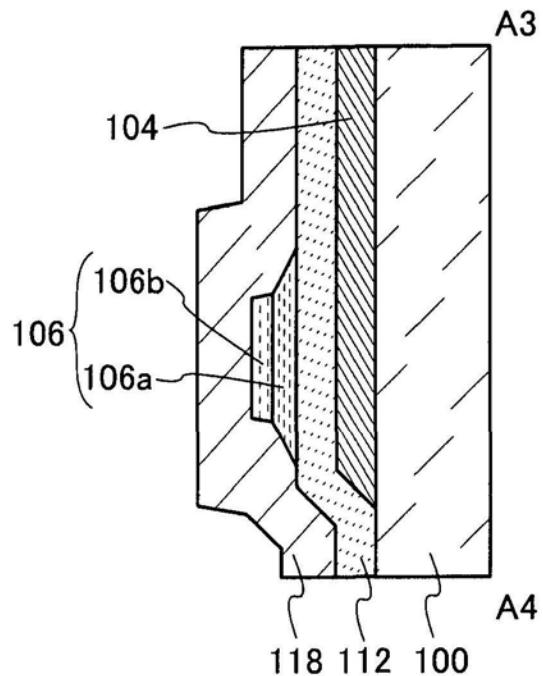

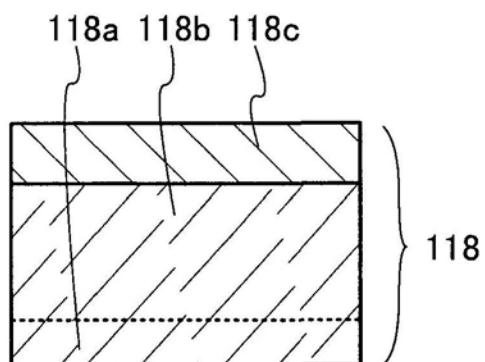

[0304] 另外,例如,保护绝缘膜118采用将第一氧化硅膜118a设为第一层,将第二氧化硅膜118b设为第二层并将氮化硅膜118c设为第三层的多层膜即可(参照图1D)。在这种情况下,第一氧化硅膜118a和第二氧化硅膜118b中的一个或两个也可以为氧氮化硅膜。另外,氮化硅膜也可以为氮氧化硅膜。第一氧化硅膜118a优选使用缺陷密度小的氧化硅膜。具体而言,使用如下氧化硅膜:在ESR测定中,来源于g值为2.001的信号的自旋的密度为 $3 \times 10^{17}$ spins/cm<sup>3</sup>以下,优选为 $5 \times 10^{16}$ spins/cm<sup>3</sup>以下。第二氧化硅膜118b使用包含过量氧的氧化硅膜。氮化硅膜118c使用氢气及氨气的释放量少的氮化硅膜。另外,氮化硅膜使用使氢、水及氧不透过或几乎不透过的氮化硅膜。

[0305] 包含过量氧的氧化硅膜是指通过加热处理等可以释放氧的氧化硅膜。另外,包含过量氧的绝缘膜是具有通过加热处理可以释放氧的功能的绝缘膜。

[0306] 包含过量氧的绝缘膜可以降低氧化物半导体膜106a中的氧空位。氧化物半导体膜106a中的氧空位形成缺陷能级,并且其一部分成为施主能级。因此,通过降低氧化物半导体膜106a中的氧空位(尤其是沟道区的氧空位),可以降低氧化物半导体膜106a(尤其是沟道区)的载流子密度,从而可以赋予晶体管稳定的电气特性。

[0307] 在此,通过加热处理释放氧的膜有时也释放出通过TDS分析的量为 $1 \times 10^{18}$ atoms/cm<sup>3</sup>以上、 $1 \times 10^{19}$ atoms/cm<sup>3</sup>以上或 $1 \times 10^{20}$ atoms/cm<sup>3</sup>以上的氧(换算为氧原子)。

[0308] 另外,通过加热处理释放氧的膜有时包含过氧化自由基。具体而言,上述情况是指起因于过氧化自由基的自旋密度为 $5 \times 10^{17}$ spins/cm<sup>3</sup>以上。另外,在ESR中,包含过氧化自由基的膜有时也在g值为2.01附近具有非对称性的信号。

[0309] 另外,包含过量氧的绝缘膜也可以是氧过量的氧化硅(SiO<sub>x</sub>(X>2))。在氧过量的氧化硅(SiO<sub>x</sub>(X>2))中,每单位体积中含有的氧原子数多于硅原子数的2倍。每单位体积的硅原子数及氧原子数为通过卢瑟福背散射光谱学法(RBS:Rutherford Backscattering Spectrometry)测定的值。

[0310] 1-1-4. 栅极绝缘膜

[0311] 棚极绝缘膜112以单层或层叠的方式使用包含氧化铝、氧化镁、氧化硅、氮化硅、氮氧化硅、氧化镓、氧化锗、氧化钇、氧化锆、氧化镧、氧化钕、氧化铪以及氧化钽中的一种以上的绝缘膜即可。

[0312] 例如,棚极绝缘膜采用将氮化硅膜设为第一层并且将氧化硅膜设为第二层的多层膜即可。在这种情况下,氧化硅膜也可以为氮化硅膜。另外,氮化硅膜也可以为氮氧化硅膜。氧化硅膜优选使用缺陷密度小的氧化硅膜。具体而言,使用如下氧化硅膜:在ESR中,来源于g值为2.001的信号的自旋的密度为 $3 \times 10^{17}$ spins/cm<sup>3</sup>以下,优选为 $5 \times 10^{16}$ spins/cm<sup>3</sup>以下。氧化硅膜优选使用包含过量氧的氧化硅膜。氮化硅膜使用氢气及氨气的释放量少的氮化硅膜。氢气及氨气的释放量通过TDS分析进行测定即可。

[0313] 当棚极绝缘膜112及保护绝缘膜118中的至少一个包括包含过量氧的绝缘膜的情况下,可以减少氧化物半导体膜106a的氧空位而赋予晶体管稳定的电气特性。

#### [0314] 1-1-5. 棚电极

[0315] 棚电极104以单层或层叠的方式使用包含铝、钛、铬、钴、镍、铜、钇、锆、钼、钌、银、钽以及钨中的一种以上的导电膜即可。

#### [0316] 1-1-6. 基板

[0317] 对于基板100没有大的限制。例如,作为基板100,也可以使用玻璃基板、陶瓷基板、石英基板、蓝宝石基板等。另外,作为基板100,也可以应用硅或碳化硅等的单晶半导体基板、多晶半导体基板、硅锗等的化合物半导体基板、SOI (Silicon On Insulator: 绝缘体上硅片) 基板等,并且也可以使用在这些基板上设置有半导体元件的基板。

[0318] 另外,作为基板100而使用第五代(1000mm×1200mm或1300mm×1500mm)、第六代(1500mm×1800mm)、第七代(1870mm×2200mm)、第八代(2200mm×2500mm)、第九代(2400mm×2800mm)、第十代(2880mm×3130mm)等大型玻璃基板的情况下,由于半导体装置的制造工序中的加热处理等所导致的基板100的收缩,有时难以进行精细加工。因此,在作为基板100使用上述大型玻璃基板的情况下,优选使用由加热处理导致的收缩少的基板。例如,作为基板100使用在400°C、优选为450°C、更优选为500°C的温度下进行1小时的加热处理之后的收缩量为10ppm以下、优选为5ppm以下、更优选为3ppm以下的大型玻璃基板。

[0319] 此外,基板100也可以使用柔性基板。另外,作为在柔性基板上设置晶体管的方法,也存在如下方法:在非柔性的基板上制作晶体管之后,剥离晶体管并将该晶体管转置到作为柔性基板的基板100上。在这种情况下,优选在非柔性的基板和晶体管之间设置剥离层。

[0320] 按上述步骤构成的晶体管通过将沟道形成在氧化物半导体膜106a中,由此具有稳定的电气特性并具有高场效应迁移率。另外,即使将具有包含铜的层的多层膜用于源电极116a及漏电极116b,也可以得到稳定的电气特性。

#### [0321] 1-2. 晶体管结构(1)的制造方法

[0322] 在此,参照图5A至图6B说明晶体管的制造方法。

[0323] 首先,准备基板100。

[0324] 接着,形成作为棚电极104的导电膜。关于作为棚电极104的导电膜,通过使用溅射法、化学气相沉积(CVD:Chemical Vapor Deposition)法、分子束外延(MBE:Molecular Beam Epitaxy)法、原子层沉积(ALD:Atomic Layer Deposition)法或脉冲激光沉积(PLD:Pulsed Laser Deposition)法来形成作为棚电极104所示的导电膜即可。

[0325] 接着,对作为栅电极104的导电膜的一部分进行蚀刻,形成栅电极104(参照图5A)。

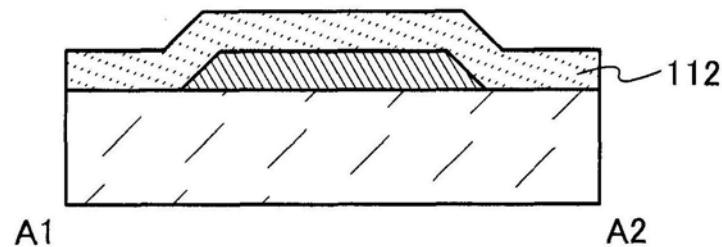

[0326] 接着,形成栅极绝缘膜112(参照图5B)。关于栅极绝缘膜112,通过使用溅射法、CVD法、MBE法、ALD法或PLD法来形成上述作为栅极绝缘膜112举出的绝缘膜即可。

[0327] 接着,形成被加工成氧化物半导体膜106a的氧化物半导体膜126a(参照图5C)。关于氧化物半导体膜126a,通过使用溅射法、CVD法、MBE法、ALD法或PLD法来形成上述作为氧化物半导体膜106a举出的氧化物半导体膜即可。

[0328] 接着,形成被加工成氧化物膜106b的氧化物膜126b。关于氧化物膜126b,通过使用溅射法、CVD法、MBE法、ALD法或PLD法来形成上述作为氧化物膜106b举出的氧化物膜即可。

[0329] 在通过溅射法形成氧化物半导体膜126a及氧化物膜126b的情况下,用于产生等离子体的电源装置可以适当地使用RF电源装置、AC电源装置、DC电源装置等。

[0330] 溅射气体可以适当地使用稀有气体(典型地为氩)气氛、氧气气、稀有气体及氧的混合气体。此外,在采用稀有气体和氧的混合气体的情况下,优选相对稀有气体增高氧气的比例。

[0331] 另外,结合氧化物半导体膜126a及氧化物膜126b的组成而适当地选择靶材即可。

[0332] 在利用溅射法的情况下,至少氧化物半导体膜126a通过如下工序形成,由此可以形成CAAC-OS。具体而言,将基板温度设定为150℃以上且500℃以下,优选设定为150℃以上且450℃以下,更优选设定为200℃以上且350℃以下,进行加热而形成氧化物半导体膜126a。此外,对氧化物膜126b也可以这样地进行加热而形成。

[0333] 另外,为了使氧化物半导体膜106a与氧化物膜106b连续接合,优选以不暴露于大气的方式连续地形成氧化物半导体膜126a及氧化物膜126b。另外,氧化物半导体膜126a及氧化物膜126b可以抑制杂质进入到各层之间。

[0334] 具体而言,为了形成连续接合,优选使用具备有装载闭锁室的多室方式的成膜装置(溅射装置)以不使各膜接触于大气的方式连续地层叠。在溅射装置中的各室中,优选使用应能够尽可能地去除对氧化物半导体膜而言为杂质的水等的、如低温泵这样的吸附式真空排气泵来进行高真空排气(排气到 $1 \times 10^{-4}$ Pa至 $5 \times 10^{-7}$ Pa左右)。或者,优选组合涡轮分子泵和冷阱而防止气体从排气系统倒流到室内。

[0335] 为了获得杂质及载流子密度被降低的氧化物半导体膜,不但需要对室内进行高真空排气,也需要进行溅射气体的高纯度化。关于作为用作溅射气体的氧气或氩气体,通过使用高纯度化到露点为-40℃以下、优选为-80℃以下、更优选为-100℃以下的气体,可以尽可能防止水分等进入到氧化物半导体膜。

[0336] 此外,在利用溅射法形成氧化物膜126b的情况下,从降低在成膜时产生的粒子数的观点来看,优选使用包含铟的靶材。另外,优选使用镓的原子个数比较少的氧化物靶材。这是因为通过使用包含铟的靶材,可以提高靶材的导电率并容易进行DC放电及AC放电,从而容易对应于大面积的基板。由此,可以提高半导体装置的生产率。

[0337] 另外,也可以在形成氧化物半导体膜126a及氧化物膜126b之后以氧气气、或者氮及氧气气进行等离子体处理。由此,能够至少减少氧化物半导体膜126a中的氧空位。

[0338] 接着,在氧化物半导体膜126a及氧化物膜126b上形成抗蚀剂掩模,利用该抗蚀剂掩模对氧化物半导体膜126a及氧化物膜126b的一部分进行蚀刻,形成包括氧化物半导体膜106a及氧化物膜106b的多层膜106(参照图6A)。该蚀刻采用如上所述的湿蚀刻。通过进行该

湿蚀刻,可以将多层膜106设为具有不同的两个锥角的锥形状。

[0339] 接着,优选进行第一加热处理。第一加热处理在250℃以上且650℃以下,优选为在以300℃以上且500℃以下进行即可。第一加热处理在惰性气体气氛下,包含10ppm以上、1%以上或10%以上的氧化气体气氛下或者在减压状态下进行。或者,第一加热处理在采用惰性气体气氛进行加热处理之后,为了在填补脱离了的氧,也可以在包含10ppm以上、1%以上或10%以上的氧化气体气氛下进行。通过进行第一加热处理,可以提高氧化物半导体膜106a的结晶性,还可以从栅极绝缘膜112及多层膜106去除水、氢、氮及碳等杂质。

[0340] 此外,第一加热处理可以在形成多层膜106的蚀刻工序之前或之后进行。

[0341] 接着,形成用作源电极116a及漏电极116b的导电膜。关于作为源电极116a及漏电极116b的导电膜,通过使用溅射法、CVD法、MBE法、ALD法或PLD法来形成作为源电极116a及漏电极116b所示的导电膜即可。

[0342] 例如,作为成为源电极116a及漏电极116b的导电膜,形成包括钨层和设置在钨层上的铜层的多层膜即可。

[0343] 接着,对作为源电极116a及漏电极116b的导电膜的一部分进行蚀刻,形成源电极116a及漏电极116b(参照图6B)。在作为成为源电极116a及漏电极116b的导电膜而使用包括钨层和设置在钨层上的铜层的多层膜的情况下,可以使用相同掩模对该多层膜进行蚀刻。即使一次地对钨层以及铜层进行蚀刻,通过在氧化物半导体膜106a上设置氧化物膜106b,也可以将氧化物半导体膜106a与氧化物膜106b之间的铜浓度设定为低于 $1 \times 10^{19}$ atoms/cm<sup>3</sup>、低于 $2 \times 10^{18}$ atoms/cm<sup>3</sup>或低于 $2 \times 10^{17}$ atoms/cm<sup>3</sup>,因而,不发生由铜导致的晶体管的电气特性的劣化。因此,可以提高工序的自由度,并提高晶体管的生产率。

[0344] 接着,优选进行第二加热处理。第二加热处理参照第一加热处理的说明进行即可。通过第二加热处理,可以从多层膜106去除氢及水等杂质。由于氢特别容易在多层膜106中移动,所以当通过进行第二加热处理减少氢,则可以赋予晶体管稳定的电气特性。此外,水也是包含氢的化合物,所以有可能成为氧化物半导体膜106a中的杂质。

[0345] 另外,通过第二加热处理可以在接触于源电极116a及漏电极116b的多层膜106中形成低电阻区106c及低电阻区106d。

[0346] 如上所述,通过形成多层膜106,可以提高氧化物半导体膜106a的结晶性,并可以降低氧化物半导体膜106a的杂质浓度、氧化物膜106b的杂质浓度以及氧化物半导体膜106a与氧化物膜106b之间的界面的杂质浓度。

[0347] 接着,形成保护绝缘膜118(参照图1B)。关于保护绝缘膜118,通过使用溅射法、CVD法、MBE法、ALD法或PLD法来形成上述作为保护绝缘膜118举出的绝缘膜即可。

[0348] 在此,说明将保护绝缘膜118设为图1D所示的三层结构的情况。首先,形成第一氧化硅膜118a。接着,形成第二氧化硅膜118b。然后,也可以进行对第二氧化硅膜118b添加氧离子的处理。添加氧离子的处理利用离子掺杂装置或等离子体处理装置即可。作为离子掺杂装置,也可以利用具有质量分离功能的离子掺杂装置。作为氧离子的原料,使用<sup>16</sup>O<sub>2</sub>或<sup>18</sup>O<sub>2</sub>等氧气、一氧化二氮气体或臭氧气体等即可。接着,通过形成氮化硅膜118c来形成保护绝缘膜118即可。

[0349] 第一氧化硅膜118a优选通过CVD法之一的等离子体CVD法形成。具体而言,可以如下条件下形成:将基板温度设定为180℃以上且400℃以下,优选为200℃以上且370℃以

下,使用含有硅的沉积性气体及氧化性气体并将压力设定为20Pa以上且250Pa以下,优选设定为40Pa以上且200Pa以下,并对电极供应高频功率。另外,作为包含硅的沉积性气体的典型例子,可以举出硅烷、乙硅烷、丙硅烷、氟化硅烷等。作为氧化性气体,可以举出氧、臭氧、一氧化二氮、二氧化氮等。

[0350] 另外,通过将氧化性气体的流量设定为含有硅的沉积性气体的100倍以上,可以减少第一氧化硅膜118a中的氢含量,并可以减少悬空键。

[0351] 通过上述方式,形成缺陷密度小的第一氧化硅膜118a。就是说,第一氧化硅膜118a可以将在ESR中来源于g值为2.001的信号的自旋的密度设为 $3 \times 10^{17} \text{ spins/cm}^3$ 以下或 $5 \times 10^{16} \text{ spins/cm}^3$ 以下。

[0352] 第二二氧化硅膜118b优选通过等离子体CVD法形成。具体而言,可以如下条件下形成:将基板温度设定为160°C以上且350°C以下,优选为180°C以上且260°C以下,使用含有硅的沉积性气体及氧化性气体并将压力设定为100Pa以上且250Pa以下,优选设定为100Pa以上且200Pa以下,并对电极供应 $0.17 \text{ W/cm}^2$ 以上且 $0.5 \text{ W/cm}^2$ 以下,优选为 $0.25 \text{ W/cm}^2$ 以上且 $0.35 \text{ W/cm}^2$ 以下的高频功率。

[0353] 由于通过上述方法等离子体中的气体的分解效率得到提高,氧自由基增加,气体的氧化增进,因此可以形成包含过量氧的第二二氧化硅膜118b。

[0354] 氮化硅膜118c优选通过等离子体CVD法形成。具体而言,可以如下条件下形成:将基板温度设定为180°C以上且400°C以下,优选为200°C以上且370°C以下,使用含有硅的沉积性气体、氮气及氨气并将压力设定为20Pa以上且250Pa以下,优选设定为40Pa以上且200Pa以下,并供应高频功率。

[0355] 此外,氮气的流量为氨气的流量的5倍以上且50倍以下,优选为10倍以上且50倍以下。此外,通过使用氨气可以促进含有硅的沉积性气体及氮气的分解。这是因为:氨气因等离子体能及热能而离解,通过离解时产生的能量有助于含有硅的沉积性气体的键合及氮气的键合的分解。

[0356] 因此,通过上述方法可以形成氢气及氨气的释放量少的氮化硅膜118c。另外,由于氢含量少,所以可以形成致密的、使氢、水及氧不透过或几乎不透过的氮化硅膜118c。

[0357] 接着,优选进行第三加热处理。第三加热处理参照第一加热处理的记载进行即可。通过第三加热处理,可以从栅极绝缘膜112或/及保护绝缘膜118释放过量氧,并且降低多层膜106的氧空位。另外,在多层膜106中,由于氧空位捕获所相邻的氧原子而在外观上进行移动。

[0358] 通过上述步骤,可以制造图1A至图1D所示的BGTC结构的晶体管。

[0359] 1-3. 晶体管结构(2)

[0360] 在此,使用图7A至图7D说明图1A至图1D所示的晶体管的变形例。

[0361] 图7A至图7D示出作为该变形例的晶体管的俯视图及截面图。图7A示出晶体管的俯视图。图7B示出对应于图7A所示的点划线A1-A2的截面图。另外,图7C示出对应于图7A所示的点划线A3-A4的截面图。此外,在图7A中,为了使附图清楚,省略该晶体管的构成要素的一部分(栅极绝缘膜及保护绝缘膜等)。

[0362] 图7A至图7D所示的晶体管与图1A至图1D所示的晶体管不同之处在于:以接触于源电极116a和漏电极116b的上表面、以及多层膜106的上表面的方式设置有氧化物膜107。

[0363] 氧化物膜117可以使用能够应用于多层膜106的氧化物膜106b的氧化物膜，并可以利用能够应用于氧化物膜106b的方法而形成。此外，图7A至图7D所示的晶体管的其他构成要素与图1A至图1D所示的晶体管相同，可以适当地参照上述记载。

[0364] 由于图7A至图7D所示的晶体管为在氧化物半导体膜106a与保护绝缘膜118之间设置有氧化物膜106b及氧化物膜107的结构，所以可以进一步使起因于形成在与保护绝缘膜118之间的界面附近的杂质或缺陷的陷阱能级与氧化物半导体膜106a远离。就是说，即使在EcS1和EcS2之间的能量差小的情况下，也可以抑制氧化物半导体膜106a的电子越过该能量差到达陷阱能级。因此，图7A至图7D所示的晶体管是阈值电压的变动进一步被降低的具有稳定的电气特性的晶体管。

[0365] 另外，图7A至图7D所示的晶体管的制造方法可以适当地参照关于图1A至图1D所示的晶体管的记载。

[0366] 如上所述，由于在多层膜106的氧化物半导体膜106a（尤其是沟道区）中杂质及载流子密度被降低，所以图1A至图1D及图7A至图7D所示的晶体管具有稳定的电气特性。

[0367] 实施方式2

[0368] 在本实施方式中说明本发明的一个方式的其结构与实施方式1部分不同的晶体管。

[0369] 2-1. 晶体管结构(3)

[0370] 在本项中说明顶栅型晶体管。在此，使用图8A至图8C说明一种顶栅型晶体管的顶栅顶接触结构(TGTC结构)的晶体管。

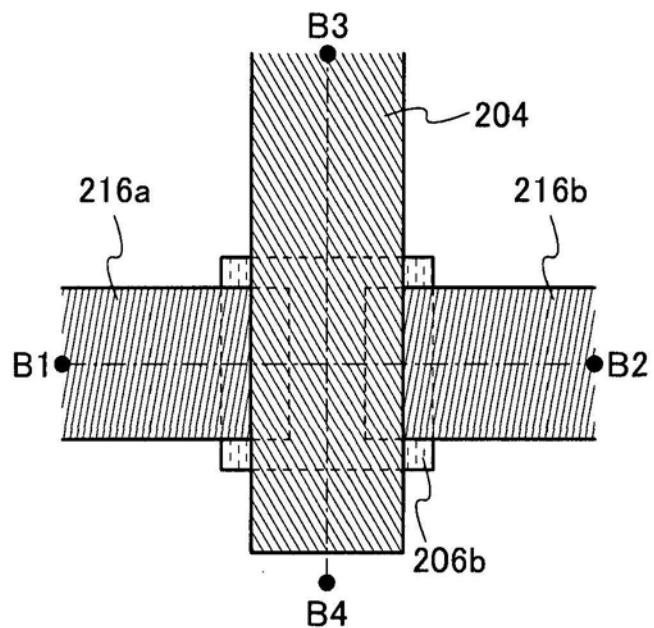

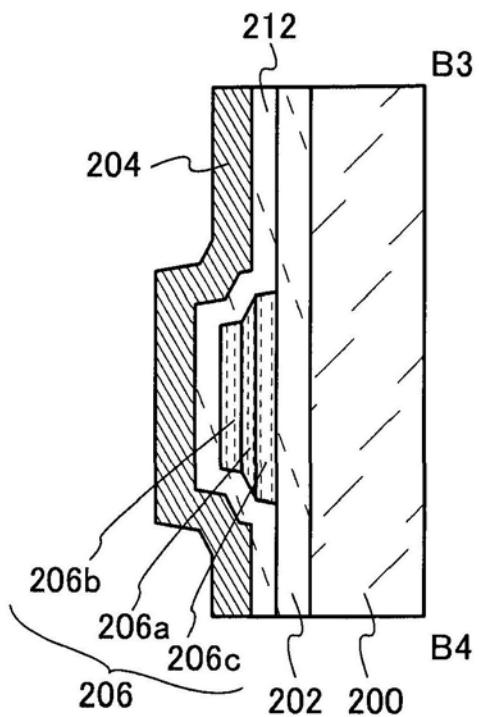

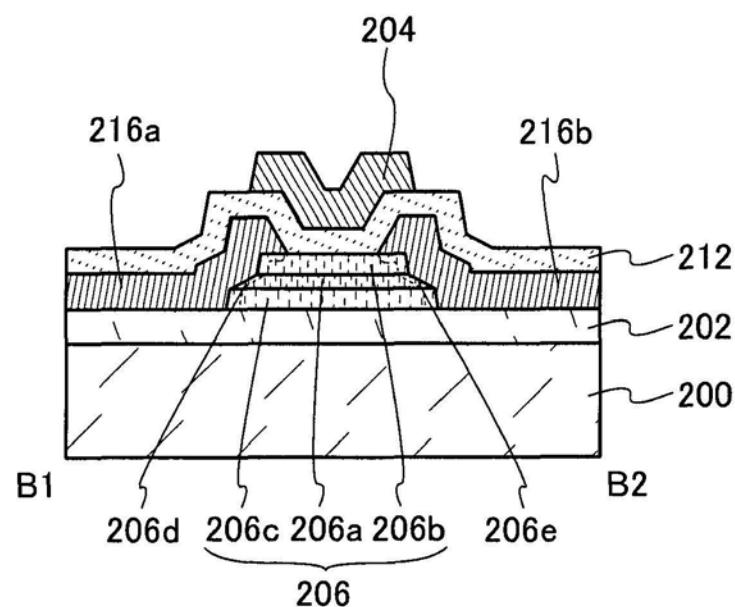

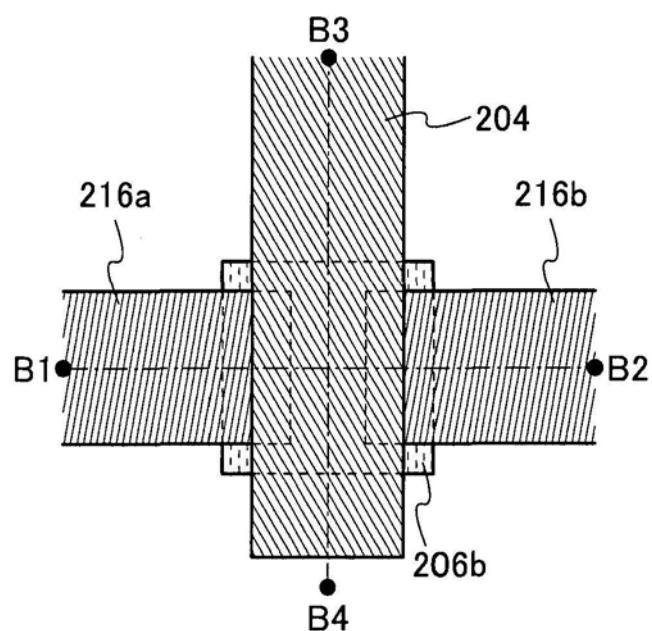

[0371] 图8A至图8C示出TGTC结构的晶体管的俯视图及截面图。图8A示出晶体管的俯视图。图8B示出对应于图8A所示的点划线B1-B2的截面图。图8C示出对应于图8A所示的点划线B3-B4的截面图。

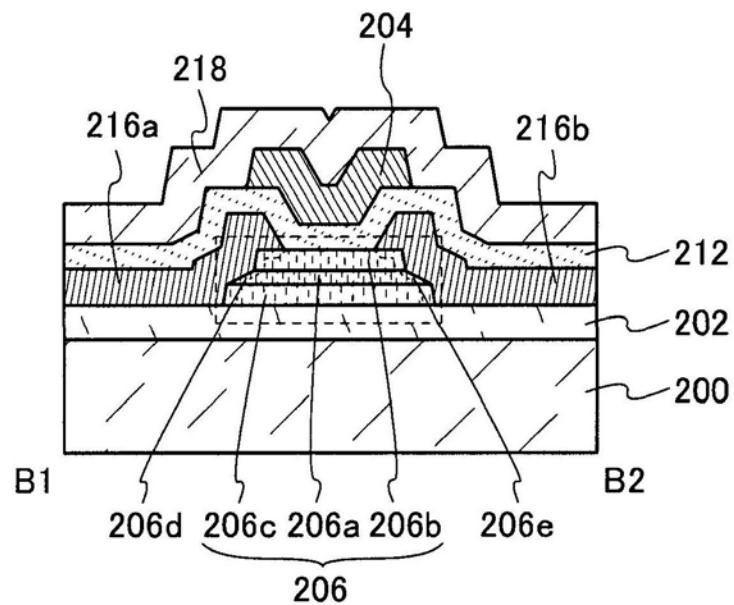

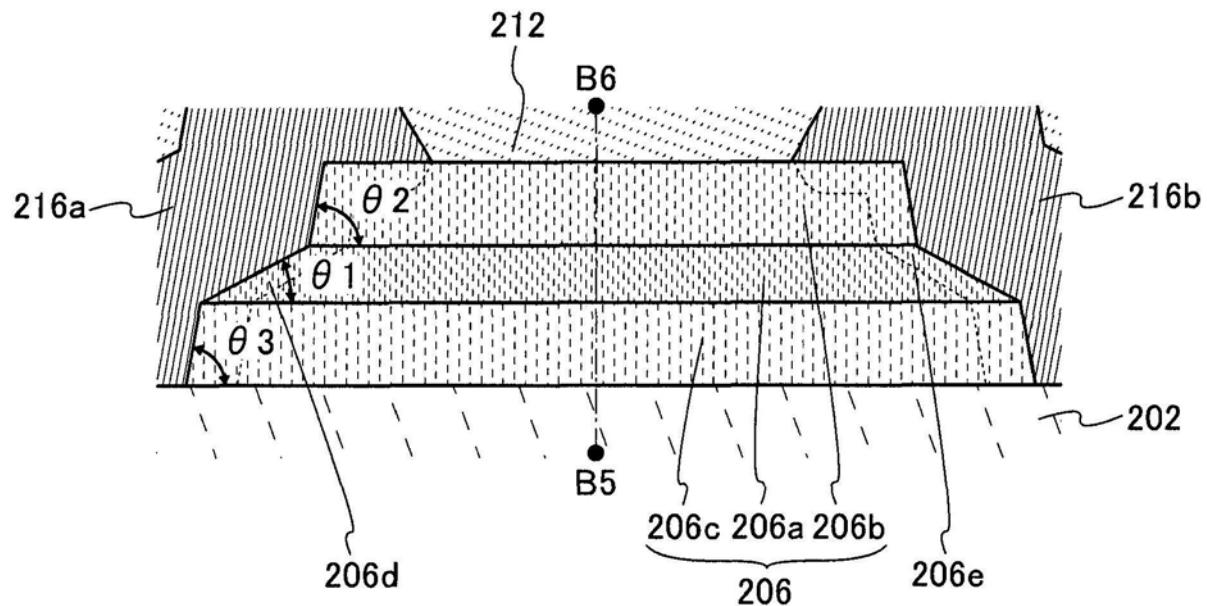

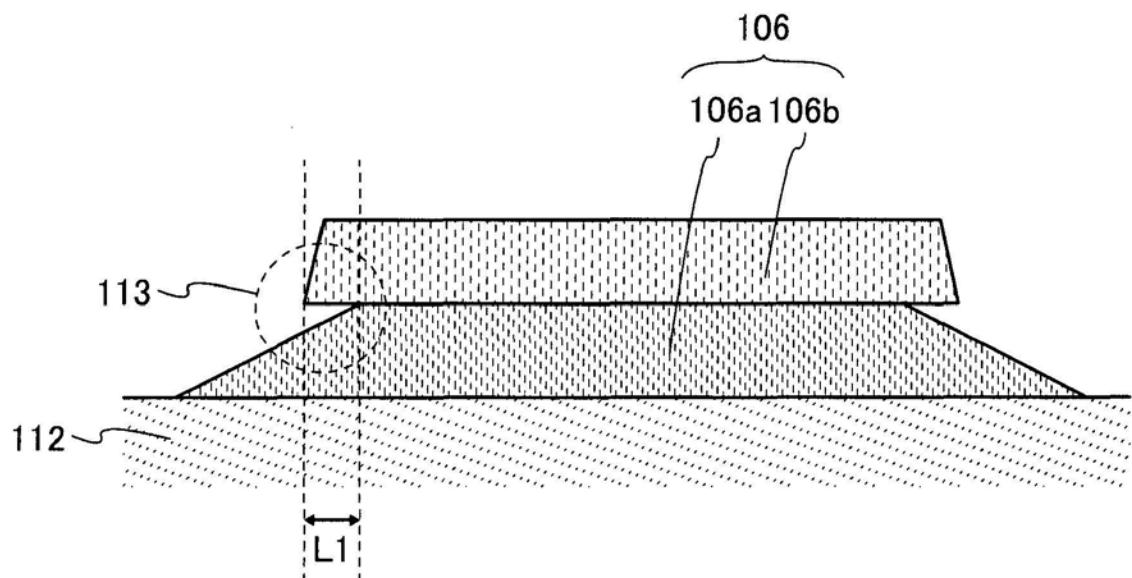

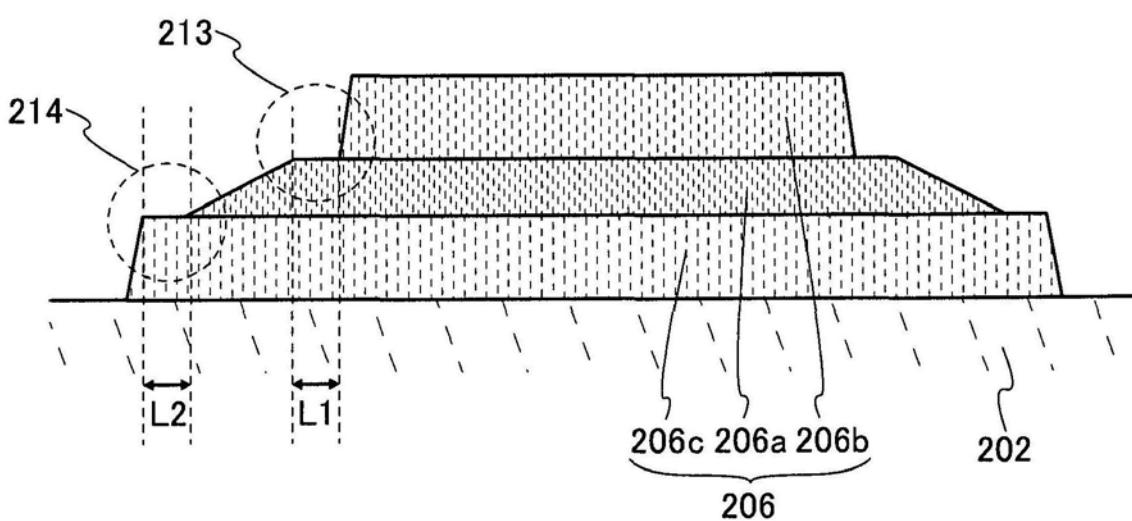

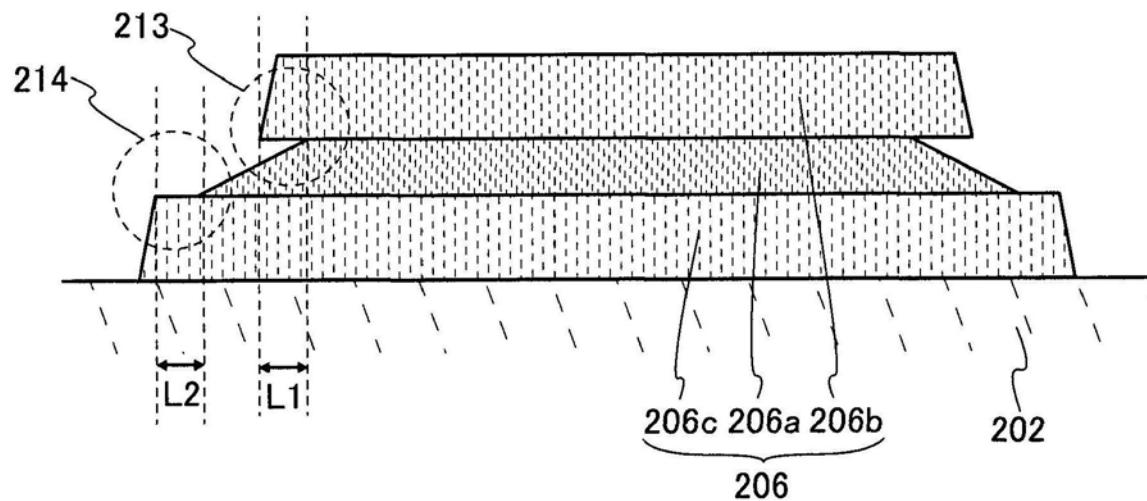

[0372] 图8B所示的晶体管包括：设置在基板200上的基底绝缘膜202；多层膜206，该多层膜206包括设置在基底绝缘膜202上的氧化物膜206c、设置在氧化物膜206c上的氧化物半导体膜206a以及设置在氧化物半导体膜206a上的氧化物膜206b；设置在基底绝缘膜202及多层膜206上的源电极216a及漏电极216b；设置在多层膜206、源电极216a及漏电极216b上的栅极绝缘膜212；设置在栅极绝缘膜212上的栅电极204；以及设置在栅极绝缘膜212及栅电极204上的保护绝缘膜218。此外，晶体管也可以不包括基底绝缘膜202和保护绝缘膜218中的一个或两个。

[0373] 另外，根据用于源电极216a及漏电极216b的导电膜的种类，有可能从多层膜206的一部分夺取氧或者形成混合层，而在多层膜206中形成低电阻区206d及低电阻区206e。在图8B中，低电阻区206d及低电阻区206e成为多层膜206中的与源电极216a及漏电极216b接触的界面附近的区域（多层膜206的虚线与源电极216a及漏电极216b之间的区域）。低电阻区206d及低电阻区206e的一部或全部作为源极区及漏极区发挥功能。

[0374] 在图8A所示的重叠于栅电极204的区域中，将源电极216a和漏电极216b之间的间隔称为沟道长度。此外，在晶体管包括源极区和漏极区的情况下，在重叠于栅电极204的区域中，也可以将源极区与漏极区之间的间隔称为沟道长度。

[0375] 此外，沟道形成区是指多层膜206中的重叠于栅电极204并且夹在源电极216a和漏电极216b的区域。另外，沟道区是指沟道形成区中的电流主要流过的区域。在此，沟道区是

沟道形成区中的氧化物半导体膜206a的一部分。

[0376] 2-1-1. 关于多层膜

[0377] 多层膜206为在氧化物半导体膜206a的上下层叠了氧化物膜206b及氧化物膜206c的结构。氧化物半导体膜206a的下表面相当于氧化物半导体膜206a的基板200一侧的表面或与氧化物膜206c之间的边界面。氧化物膜206b的下表面相当于氧化物膜206b的基板200一侧的表面或与氧化物半导体膜206a之间的边界面。氧化物膜206c的下表面相当于氧化物膜206c的基板200一侧的表面或氧化物膜206c的接触于栅极绝缘膜112的表面。另外，多层膜206的层叠结构通过使用STEM(Scanning Transmission Electron Microscopy: 扫描透射电子显微术)观察，可以确认出其边界。但是，根据用于氧化物半导体膜206a、氧化物膜206b及氧化物膜206c的材料，有时不能明确地确认出该边界。

[0378] 氧化物半导体膜206a可以使用能够应用于实施方式1的氧化物半导体膜106a的氧化物半导体膜。氧化物膜206b可以使用能够应用于实施方式1的氧化物膜106b的氧化物膜。氧化物膜206c可以使用能够应用于实施方式1的氧化物膜106b的氧化物膜。

[0379] 在多层膜206中，至少氧化物半导体膜206a具有锥形状。优选的是，氧化物膜206b及氧化物膜206c也具有锥形状。此外，优选的是，至少氧化物半导体膜206a的锥形状与氧化物膜206b的锥形状及氧化物膜206c的锥形状不同。氧化物膜206b和氧化物膜206c的锥形状既可以是相同，又可以是不同。

[0380] 具体而言，在氧化物半导体膜206a中，将氧化物半导体膜206a的下表面与氧化物半导体膜206a的侧面所呈的角度称为第一角度θ1，在氧化物膜206b中，将氧化物膜206b的下表面与氧化物膜206b的侧面所呈的角度称为第二角度θ2，并且在氧化物膜206c中，将氧化物膜206c的下表面与氧化物膜206c的侧面所呈的角度称为第三角度θ3。在这种情况下，第一角度θ1可以设为锐角，第二角度θ2及第三角度θ3可以设为锐角或垂直。

[0381] 优选的是，第一角度θ1、第二角度θ2及第三角度θ3都是锐角，并且至少第一角度θ1小于第二角度θ2及第三角度θ3(参照图9)。

[0382] 此外，第二角度θ2和第三角度θ3既可以是相同角度，又可以是不同角度。例如，通过将氧化物膜206b和氧化物膜206c设为相同种类的氧化物膜，可以将第二角度θ2和第三角度θ3设为相同角度。

[0383] 另外，第一角度θ1为10°以上且小于90°，优选为30°以上且70°以下。第二角度θ2及第三角度θ3为10°以上且小于90°，优选为30°以上且70°以下。

[0384] 如上所述，通过将多层膜206的形状设为具有不同的锥角的锥形状，可以得到下述效果。对于多层膜206，通过将其设为具有不同的锥角的锥形状，与具有相同的锥角的锥形状相比，可以扩大多层膜206与源电极216a及漏电极216b之间的接触面积。由此，可以降低多层膜206与源电极216a及漏电极216b之间的接触电阻而使晶体管的导通电流增大。

[0385] 另外，通过使第二角度θ2及第三角度θ3大于第一角度θ1，可以减小氧化物膜206b及氧化物膜206c与源电极216a及漏电极216b之间的接触面积，从而可以减小形成在氧化物膜206b及氧化物膜206c中的低电阻区。因此，可以抑制氧化物膜206b及氧化物膜206c中的一个或两个的低电阻化，抑制在源电极216a与漏电极216b之间产生的泄漏路径，同时在作为沟道区发挥功能的氧化物半导体膜206a中高效地形成低电阻区，从而可以同时实现晶体管的导通电流的增大和晶体管的截止电流的降低。

[0386] 另外,氧化物半导体膜206a的上端与氧化物膜206b的下端大致一致,氧化物膜206c的上端与氧化物半导体膜206a的下端大致一致(参照图9)。就是说,多层膜206没有由氧化物半导体膜206a、氧化物膜206b和氧化物膜206c中的两个以上的膜形成的大的台阶213及大的台阶214(参照图32A和图32B)。因此,可以抑制设置在多层膜206上的膜(例如,被加工成源电极216a及漏电极216b的导电膜)的断开,从而可以制造电气特性良好的晶体管。此外,“氧化物半导体膜206a的上端与氧化物膜206b的下端大致一致,氧化物膜206c的上端与氧化物半导体膜206a的下端大致一致”是指氧化物膜206b的下端与氧化物半导体膜206a的上端之间的距离L1以及氧化物膜206c的上端与氧化物半导体膜206a的下端之间的距离L2为30nm以下,优选为10nm以下(参照图32A和图32B)。

[0387] 通过利用在由蚀刻来形成多层膜206时的每个膜的蚀刻速度的差异,可以形成上述锥形状。尤其是,上述锥形状通过使氧化物半导体膜206a的蚀刻速度低于氧化物膜206b的蚀刻速度及氧化物膜206c的蚀刻速度来可以形成。

[0388] 在使第二角度θ2小于第三角度θ3的情况下,使氧化物膜206b的蚀刻速度低于氧化物膜206c的蚀刻速度即可。另外,在使第二角度θ2大于第三角度θ3时,使氧化物膜206b的蚀刻速度高于氧化物膜206c的蚀刻速度即可。

[0389] 与实施方式1相同,上述锥形状可以通过作为蚀刻剂而使用包含磷酸的溶液的湿蚀刻来形成。另外,关于该湿蚀刻的详细内容可以参照实施方式1。另外,通过使第二角度θ2及第三角度θ3大于第一角度θ1,可以尽可能减小在该湿蚀刻中暴露于蚀刻剂的面积。另外,通过使第二角度θ2及第三角度θ3大于第一角度θ1,可以减小由于蚀刻剂所引起的污染或缺陷的生成而被形成在氧化物膜206b及氧化物膜206c中的低电阻区。

[0390] 通过湿蚀刻形成多层膜206,如实施方式1所示,可以抑制晶体管的成品率的下降并且以高生产率制造电气特性良好的晶体管。

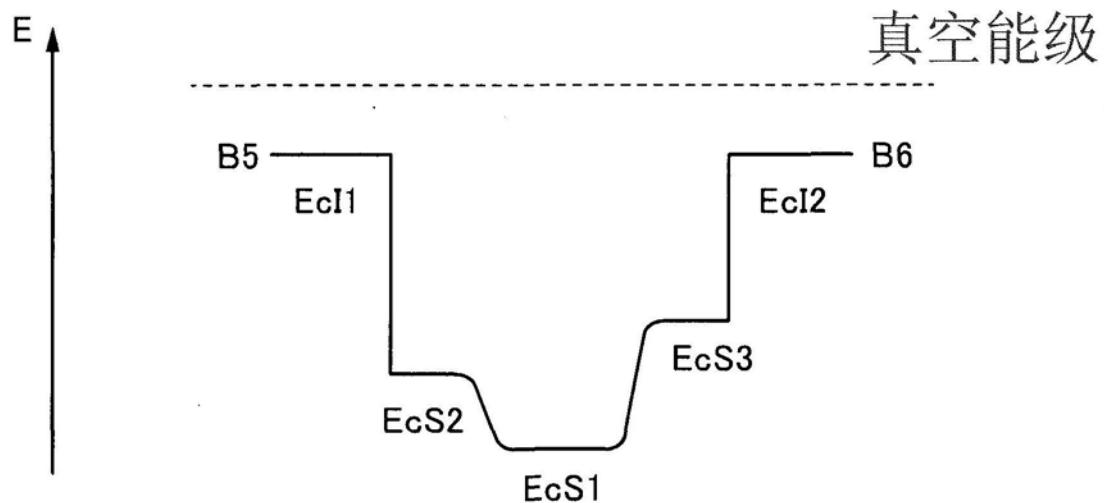

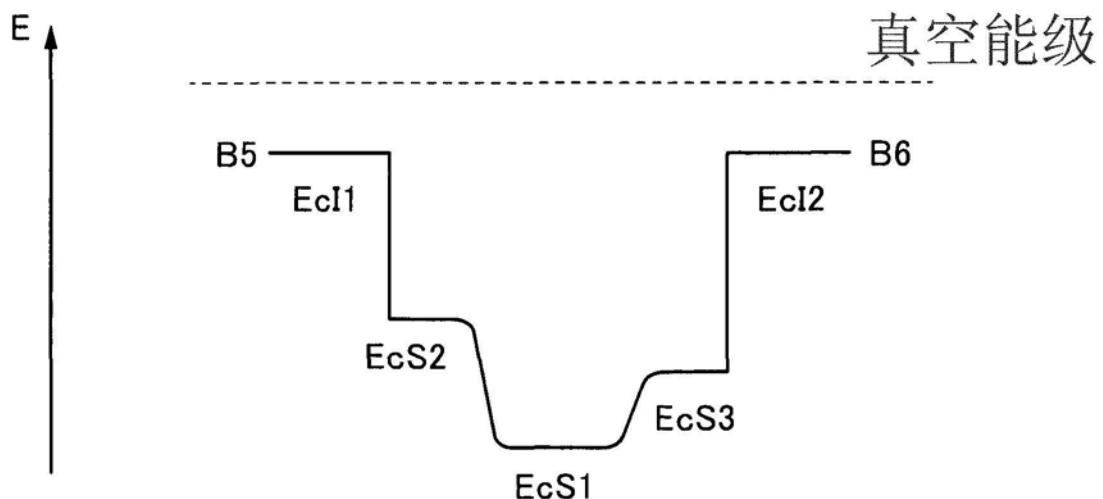

[0391] 以下,参照图10A至图10C说明多层膜206的能带结构。

[0392] 例如,使用能隙为3.15eV的In-Ga-Zn氧化物作为氧化物半导体膜206a,使用能隙为3.5eV的In-Ga-Zn氧化物作为氧化物膜206b及氧化物膜206c。利用光谱椭偏仪(HORIBA JOBIN YVON公司的UT-300)测定能隙。

[0393] 氧化物半导体膜206a的真空能级与价带上端之间的能量差(也称为电离电位)为8eV。另外,氧化物膜206b及氧化物膜206c的电离电位为8.2eV。此外,关于真空能级和价带顶端之间的能量差,利用紫外线光电子能谱(UPS:Ultraviolet Photoelectron Spectroscopy)装置(PHI公司的VersaProbe)进行测定。

[0394] 因此,氧化物半导体膜206a的真空能级和导带底的能量之间的能量差(也称为电子亲和能)为4.85eV。氧化物膜206b及氧化物膜206c的电子亲和能为4.7eV。

[0395] 图10A示意性地示出多层膜206的能带结构的一部分。在图10A中,说明了与氧化物膜206b以及氧化物膜206c的每一个接触地设置氧化硅膜(基底绝缘膜202及栅极绝缘膜212)的情况。在此,E<sub>C11</sub>表示氧化硅膜的导带底的能量,E<sub>C11</sub>表示氧化物半导体膜206a的导带底的能量,E<sub>C2</sub>表示氧化物膜206b的导带底的能量,E<sub>C3</sub>表示氧化物膜206c的导带底的能量,E<sub>C12</sub>表示氧化硅膜的导带底的能量。

[0396] 如图10A所示那样,在氧化物半导体膜206a、氧化物膜206b及氧化物膜206c中,导带底的能量没有位垒而平缓地变化。换言之,也可以说是连续地变化。这可以说是因为氧化

物膜206b以及氧化物膜206c包含与氧化物半导体膜206a相同的元素，并且通过在氧化物半导体膜206a和氧化物膜206b之间以及在氧化物半导体膜206a和氧化物膜206c之间氧相互移动而形成有混合层。

[0397] 从图10A可知，多层膜206的氧化物半导体膜206a成为阱(well)，在使用多层膜206的晶体管中，沟道区形成在氧化物半导体膜206a。另外，由于多层膜206的导带底的能量连续地变化，所以也可以说氧化物半导体膜206a与氧化物膜206b连续地接合，氧化物半导体膜206a与氧化物膜206c连续地接合。

[0398] 另外，通过将氧化物膜206b与氧化物膜206c分别设为导带底的能量不同的氧化物膜，可以根据该导带底的能量的大小关系而改变多层膜206的能带结构。

[0399] 通过作为氧化物膜206c而使用其导带底的能量比氧化物膜206b大的氧化物，可以形成具有图10B所示的能带结构的多层膜206。

[0400] 通过作为氧化物膜206c而使用其导带底的能量比氧化物膜206b小的氧化物，可以形成图10C所示的具有能带结构的多层膜206。

[0401] 此外，在具有图10B及图10C所示的能带结构的多层膜206中，沟道区也形成在氧化物半导体膜206a中。

[0402] 另外，虽然在氧化物膜206b与栅极绝缘膜212之间的界面附近有可能形成起因于杂质或缺陷的陷阱能级，但是通过设置氧化物膜206b，可以使氧化物半导体膜206a与该陷阱能级远离。然而，在EcS1和EcS2之间的能量差小的情况下，有时氧化物半导体膜206a的电子会越过该能量差到达陷阱能级。由于电子被陷阱能级捕获，使得在绝缘膜的界面产生负的固定电荷，这导致晶体管的阈值电压向正的方向移动。

[0403] 另外，虽然在氧化物膜206c与基底绝缘膜202之间的界面附近有可能形成起因于杂质或缺陷的陷阱能级，但是可以使氧化物半导体膜206a与该陷阱能级远离。此外，当EcS1和EcS3之间的能量差小时，有时氧化物半导体膜206a的电子越过该能量差到达陷阱能级。电子被陷阱能级捕获，使得在绝缘膜的界面产生负的固定电荷，这导致晶体管的阈值电压向正的方向移动。

[0404] 因此，当将EcS1与EcS2之间的能量差以及EcS1与EcS3之间的能量差分别设定为0.1eV以上，优选为0.15eV以上，则减少晶体管的阈值电压的变动而得到稳定的电气特性，所以是优选的。

[0405] 2-1-2. 关于其他结构

[0406] 基板200可以参照关于基板100的记载。此外，源电极216a及漏电极216b可以参照关于源电极116a及漏电极116b的记载。另外，栅极绝缘膜212可以参照关于栅极绝缘膜112的记载。另外，栅电极204可以参照关于栅电极104的记载。此外，保护绝缘膜218可以参照关于保护绝缘膜118的记载。

[0407] 此外，在图8A中，虽然多层膜206在上表面形状中形成到栅电极204的外侧，但是也可以形成为栅电极204的宽度大于多层膜206的宽度，以抑制因来自上方的光而在多层膜206中生成载流子。

[0408] 基底绝缘膜202可以以单层或层叠的方式使用包含氧化铝、氧化镁、氧化硅、氮化硅、氮氧化硅、氮化硅、氧化镓、氧化锗、氧化钇、氧化锆、氧化镧、氧化钕、氧化铪以及氧化钽中的一种以上的绝缘膜。

[0409] 例如,作为基底绝缘膜202,可以是将第一层设为氮化硅膜,将第二层设为氧化硅膜的层叠结构。此时,氧化硅膜也可以为氧氮化硅膜。另外,氮化硅膜也可以为氮氧化硅膜。氧化硅膜优选使用缺陷密度小的氧化硅膜。具体而言,使用如下氧化硅膜:在ESR中,来源于g值为2.001的信号的自旋的密度为 $3 \times 10^{17}$ spins/cm<sup>3</sup>以下,优选为 $5 \times 10^{16}$ spins/cm<sup>3</sup>以下。氮化硅膜使用氢及氨的释放量少的氮化硅膜。氢及氨的释放量通过TDS分析进行测定即可。另外,氮化硅膜使用使氢、水及氧不透过或几乎不透过的氮化硅膜。

[0410] 另外,例如,作为基底绝缘膜202,可以是将第一层设为第一氮化硅膜,将第二层设为第一氧化硅膜并将第三层设为第二氧化硅膜的层叠结构。在这种情况下,第一氧化硅膜或/和第二氧化硅膜也可以为氧氮化硅膜。另外,氮化硅膜也可以为氮氧化硅膜。第一氧化硅膜优选使用缺陷密度小的氧化硅膜。具体而言,使用如下氧化硅膜:在ESR中,来源于g值为2.001的信号的自旋的密度为 $3 \times 10^{17}$ spins/cm<sup>3</sup>以下,优选为 $5 \times 10^{16}$ spins/cm<sup>3</sup>以下。第二氧化硅膜使用包含过量氧的氧化硅膜。氮化硅膜使用氢及氨的释放量少的氮化硅膜。另外,氮化硅膜使用使氢、水及氧不透过或几乎不透过的氮化硅膜。

[0411] 在栅极绝缘膜212和基底绝缘膜202中的一个或两个具有包含过量氧的绝缘膜的情况下,可以降低氧化物半导体膜206a中的氧空位。

[0412] 如上所述,本实施方式所示的晶体管由于降低多层膜206的氧化物半导体膜206a(尤其是沟道区)的杂质及载流子密度,从而具有稳定的电气特性和高场效应迁移率。

[0413] 2-2. 晶体管结构(3)的制造方法

[0414] 在此,使用图11A至图12B说明晶体管的制造方法。

[0415] 首先,准备基板200。

[0416] 在基板200上形成基底绝缘膜202。关于基底绝缘膜202,通过使用溅射法、CVD法、MBE法、ALD法或PLD法来形成上述绝缘膜即可。

[0417] 接着,形成被加工成氧化物膜206c的氧化物膜226c。氧化物膜206c的成膜方法可以参照关于实施方式1的氧化物膜106b的记载。此外,氧化物膜206c形成为CAAC-OS或非晶质。当氧化物膜206c为CAAC-OS或非晶质,则作为氧化物半导体膜206a的氧化物半导体膜226a容易成为CAAC-OS。

[0418] 接着,形成被加工成氧化物半导体膜206a的氧化物半导体膜226a。氧化物半导体膜226a的成膜方法可以参照关于实施方式1的氧化物半导体膜106a的记载。

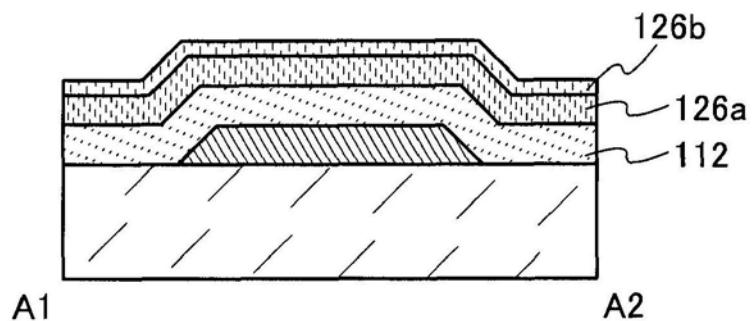

[0419] 接着,形成被加工成氧化物膜206b的氧化物膜226b。氧化物膜226b的成膜方法可以参照关于实施方式1的氧化物膜106b的记载(参照图11A)。

[0420] 如实施方式1所示,为了使氧化物膜206c、氧化物半导体膜206a与氧化物膜206b连续接合,优选以不使各膜暴露于大气的方式连续地层叠氧化物膜226c、氧化物半导体膜226a及氧化物膜226b。

[0421] 接着,对氧化物膜226c、氧化物半导体膜226a及氧化物膜226b的一部分进行蚀刻,形成包括氧化物膜206c、氧化物半导体膜206a及氧化物膜206b的多层膜206(参照图11B)。此外,该蚀刻可以参照上述蚀刻。

[0422] 接着,优选进行第一加热处理。第一加热处理也可以在250℃以上且650℃以下,优选为在300℃以上且500℃以下进行即可。第一加热处理在惰性气体气氛,包含10ppm以上、1%以上或10%以上的氧化气体气氛下或者在减压状态下进行。或者,第一加热处理在采用

惰性气体气氛进行加热处理之后,为了填补脱离了的氧,也可以在包含10ppm以上、1%以上或10%以上的氧化气体气氛下进行。通过进行第一加热处理,可以提高氧化物半导体膜226a的结晶性,进而可以从基底绝缘膜202及多层膜206去除水、氢、氮及碳等杂质。

[0423] 此外,第一加热处理可以在形成多层膜206的蚀刻工序之前或之后进行。

[0424] 接着,形成用作源电极216a及漏电极216b的导电膜。用作源电极216a及漏电极216b的导电膜的成膜方法可以参照关于实施方式1的源电极116a及漏电极116b的记载。

[0425] 接着,对作为源电极216a及漏电极216b的导电膜的一部分进行蚀刻,形成源电极216a及漏电极216b(参照图11C)。

[0426] 接着,优选进行第二加热处理。关于第二加热处理,参照第一加热处理的说明进行即可。通过进行第二加热处理,可以从多层膜206去除水、氢、氮及碳等杂质。

[0427] 另外,通过第二加热处理可以在接触于源电极216a及漏电极216b的多层膜206中形成低电阻区206d及低电阻区206e。

[0428] 接着,形成栅极绝缘膜212(参照图12A)。栅极绝缘膜212的成膜方法可以参照关于实施方式1的栅极绝缘膜112的记载。

[0429] 接着,形成作为栅电极204的导电膜。接着,对作为栅电极204的导电膜的一部分进行蚀刻,形成栅电极204(参照图12B)。栅电极204的成膜方法及蚀刻工序可以参照关于实施方式1的栅电极104的记载。

[0430] 接着,形成保护绝缘膜218(参照图8B)。保护绝缘膜218的成膜方法可以参照关于保护绝缘膜118的记载。

[0431] 通过上述步骤,可以制造图8A至图8C所示的晶体管。

[0432] 2-3. 晶体管结构(4)

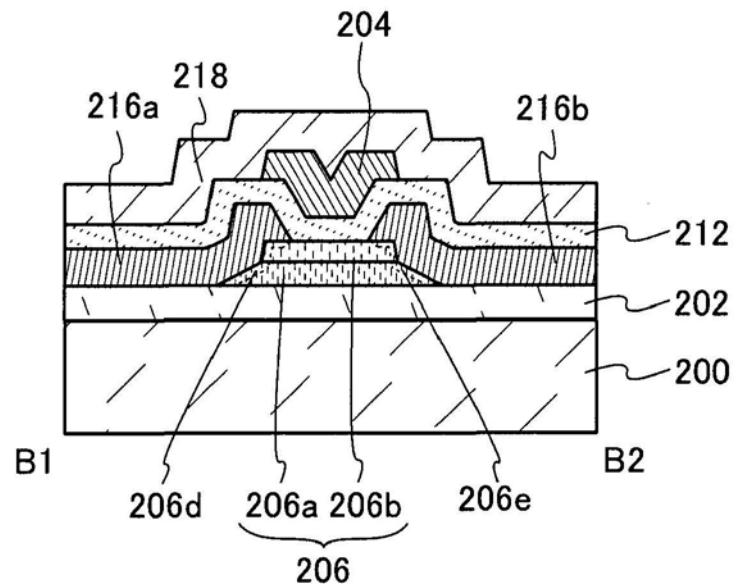

[0433] 在此,使用图13A至图13C说明图8A至图8C所示的晶体管的变形例。

[0434] 图13A至图13C示出作为该变形例的晶体管的俯视图及截面图。图13A示出晶体管的俯视图。图13B示出对应于图13A所示的点划线B1-B2的截面图。另外,图13C示出对应于图13A所示的点划线B3-B4的截面图。另外,在图13A中,为了使附图清楚,省略该晶体管的构成要素的一部分(栅极绝缘膜及保护绝缘膜等)。

[0435] 图13A至图13C所示的晶体管与图8A至图8C所示的晶体管不同之处在于:在多层膜206中不包括氧化物膜206c。就是说,图13A至图13C所示的晶体管中的多层膜206是氧化物半导体膜206a及氧化物膜206b。此外,图13A至图13C所示的晶体管的其他构成要素与图8A至图8C所示的晶体管相同,而可以适当地参照上述记载。

[0436] 在图13A至图13C所示的晶体管中,虽然在氧化物膜206b与栅极绝缘膜212之间的界面附近有可能形成起因于杂质或缺陷的陷阱能级,但是通过设置氧化物膜206b,可以使氧化物半导体膜206a与该陷阱能级远离。因此,图13A至图13C所示的晶体管是阈值电压的变动被降低的具有稳定的电气特性的晶体管。

[0437] 此外,图13A至图13C所示的晶体管的制造方法可以适当地参照关于实施方式1及图8A至图8C所示的晶体管的记载。

[0438] 2-4. 晶体管结构(5)

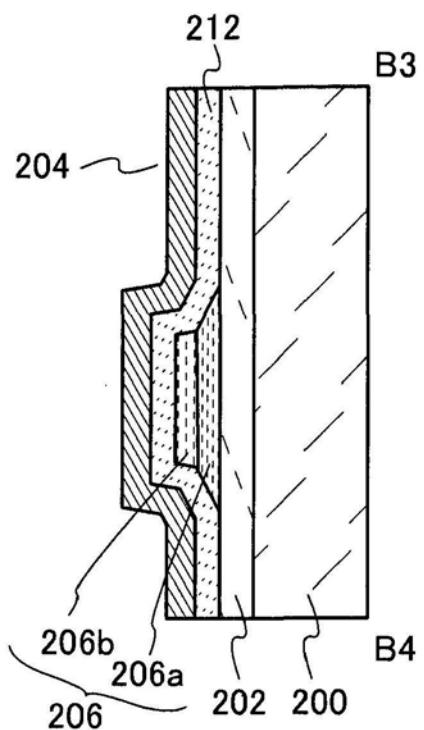

[0439] 在此,使用图14A至图14C说明作为图8A至图8C所示的晶体管的变形例的晶体管。

[0440] 图14A至图14C示出作为该变形例的晶体管的俯视图及截面图。图14A示出晶体管

的俯视图。图14B示出对应于图14A所示的点划线B1-B2的截面图。另外,图14C示出对应于图14A所示的点划线B3-B4的截面图。另外,在图14A中,为了使附图清楚,省略该晶体管的构成要素的一部分(栅极绝缘膜及保护绝缘膜等)。

[0441] 图14A至图14C所示的晶体管与图8A至图8C所示的晶体管不同之处在于:在多层膜206中不包括氧化物膜206b。就是说,图14A至图14C所示的晶体管中的多层膜206是氧化物膜206c及氧化物半导体膜206a。另外,在以接触于源电极216a的上表面、漏电极216b的上表面及多层膜206的上表面的方式设置有氧化物膜207这一点上也不同。

[0442] 氧化物膜207可以使用能够应用于实施例1的多层膜106的氧化物膜106b的氧化物膜,并可以利用能够应用于氧化物膜106b的方法而形成。此外,图14A至图14C所示的晶体管的其他构成要素与图8A至图8C所示的晶体管相同,而可以适当地参照上述记载。

[0443] 由于图14A至图14C所示的晶体管为在氧化物半导体膜206a与栅极绝缘膜212之间设置有氧化物膜207的结构,所以可以进一步使起因于形成在氧化物膜207与栅极绝缘膜212之间的界面附近的杂质或缺陷的陷阱能级与氧化物半导体膜106a远离。因此,图14A至图14C所示的晶体管是晶体管的阈值电压的变动被降低的具有稳定的电气特性的晶体管。

[0444] 另外,图14A至图14C所示的晶体管的制造方法可以适当地参照关于实施方式1及图8A至图8C所示的晶体管的记载。

#### [0445] 2-5. 其他晶体管结构

[0446] 例如,在图8A至图8C所示的晶体管中,如下结构的晶体管也包括在本发明的一个方式中:在源电极212a和漏电极212b的上表面、以及多层膜206的上表面与栅极绝缘膜212之间设置有图14A至图14C所示的晶体管的氧化物膜207。

[0447] 通过采用具有上述结构的晶体管,可以得到在氧化物半导体膜206a与栅极绝缘膜212之间设置有氧化物膜206b及氧化物膜207的结构,所以可以进一步使起因于形成在氧化物膜207与栅极绝缘膜212之间的界面附近的杂质或缺陷的陷阱能级与氧化物半导体膜206a远离。就是说,即使在EcS1和EcS2之间的能量差小的情况下,也可以抑制氧化物半导体膜206a的电子越过该能量差到达陷阱能级。因此,可以得到阈值电压的变动进一步被降低的具有稳定的电气特性的晶体管。

[0448] 此外,如下晶体管也包括在本发明的一个方式中:使用具有氧化物半导体膜206a、氧化物膜206b及氧化物膜206c的多层膜206来代替在实施方式1中说明的底栅结构的晶体管的多层膜106。

[0449] 如上所述,由于在多层膜106、206的氧化物半导体膜106a、206a(尤其是沟道区)中杂质及载流子密度被降低,所以图8A至图8C、图13A至图13C以及图14A至图14C所示的晶体管具有稳定的电气特性。

#### [0450] 实施方式3

[0451] 在本实施方式中,说明使用在上述实施方式中记载的晶体管的半导体装置。

#### [0452] 3-1. 显示装置

[0453] 在此,说明使用在上述实施方式中记载的晶体管的半导体装置之一的显示装置。

[0454] 作为设置在显示装置中的显示元件,可以使用液晶元件(也称为液晶显示元件)、发光元件(也称为发光显示元件)等。发光元件在其范围内包括其亮度由电流或电压控制的元件,具体而言,包括无机EL(Electro Luminescence:电致发光)元件、有机EL元件等。此

外,也可以采用电子墨水等由于电作用而改变对比度的显示媒体作为显示元件。下面,作为显示装置的一个例子对使用EL元件的显示装置及使用液晶元件的显示装置进行说明。

[0455] 另外,下面示出的显示装置包括处于密封有显示元件的状态的面板及处于在该面板中安装有包括控制器的IC等的状态的模块。

[0456] 另外,下面示出的显示装置是指图像显示器件或光源(包括照明装置)。此外,显示装置还包括:安装有连接器(诸如FPC或TCP)的模块;在TCP的端部设置有印刷线路板的模块;或者通过COG方式将IC(集成电路)直接安装到显示元件的模块。

[0457] 此外,在下面示出的显示装置中可以设置由根据接触或非接触的传感来进行的输入单元(未图示)。例如,作为由根据接触的传感进行的输入单元,可以采用各种方式诸如电阻式、电容式、红外线式、电磁感应方式、表面声波式等各种方式的触控传感器。此外,作为由根据非接触的传感来进行的输入单元,可以采用红外线相机等来实施。

[0458] 该输入单元既可以通过另行设置在下面示出的显示装置上的所谓“单元上(On-cell)”方式来设置,又可以通过和下面示出的显示装置一体地设置的所谓“单元内(In-cell)”方式来设置。

[0459] 3-1-1. EL显示装置

[0460] 在此,说明使用EL元件的显示装置(也称为EL显示装置)。

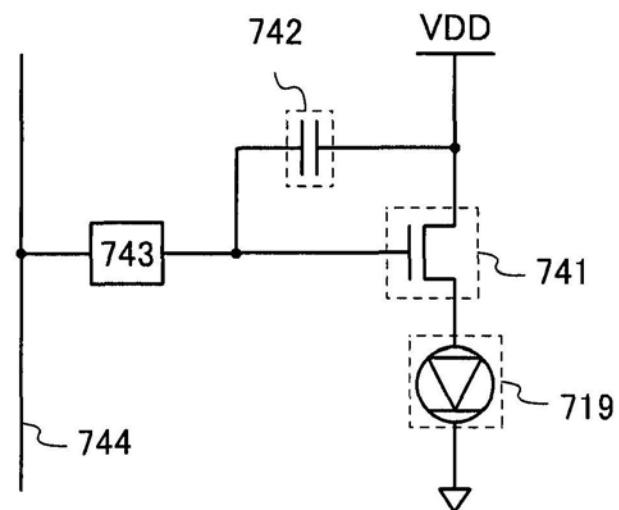

[0461] 图15是EL显示装置的像素的电路图的一个例子。

[0462] 图15所示的EL显示装置具有开关元件743、晶体管741、电容器742、发光元件719。

[0463] 晶体管741的栅极与开关元件743的一端及电容器742的一端电连接。晶体管741的源极与发光元件719的一端电连接。晶体管741的漏极与电容器742的另一端电连接,并被提供电源电位VDD。开关元件743的另一端与信号线744电连接。发光元件719的另一端被提供恒电位。另外,恒电位为等于或低于接地电位GND的电位。

[0464] 另外,晶体管741采用在上述实施方式中记载的晶体管。该晶体管具有稳定的电气特性。因此,可以成为显示品质高的EL显示装置。

[0465] 作为开关元件743优选使用晶体管。通过使用晶体管,可以减小像素的面积,由此可以成为分辨率高的EL显示装置。另外,开关元件743也可以采用在上述实施方式中记载的晶体管。通过作为开关元件743而使用该晶体管,可以通过与晶体管741相同工序来制作开关元件743,由此可以提高EL显示装置的生产率。

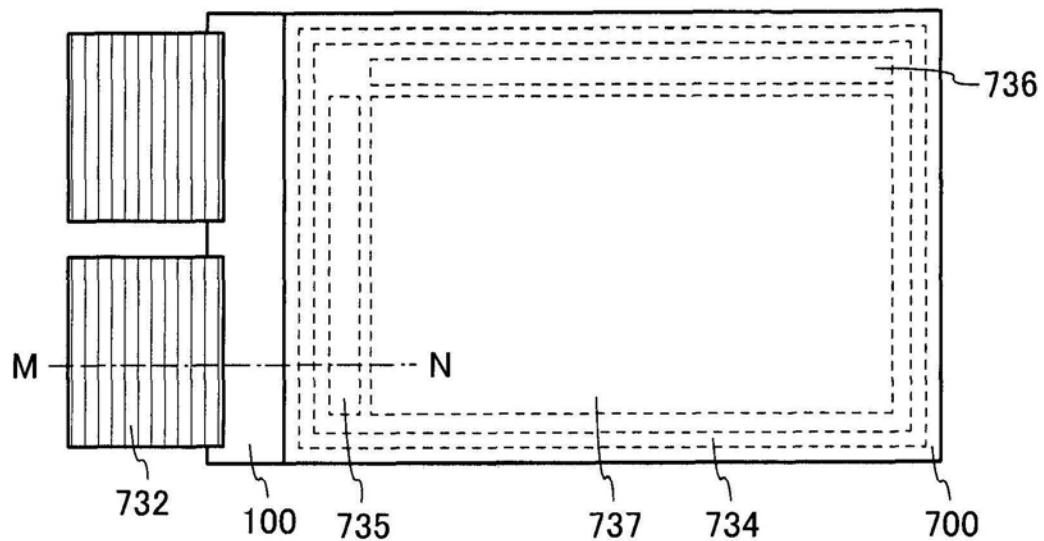

[0466] 图16A是EL显示装置的俯视图。EL显示装置包含基板100、基板700、密封材料734、驱动电路735、驱动电路736、像素737以及FPC732。密封材料734以包围像素737、驱动电路735以及驱动电路736的方式设置在基板100与基板700之间。另外,驱动电路735和驱动电路736中的一个或两个也可以设置在密封材料734的外侧。

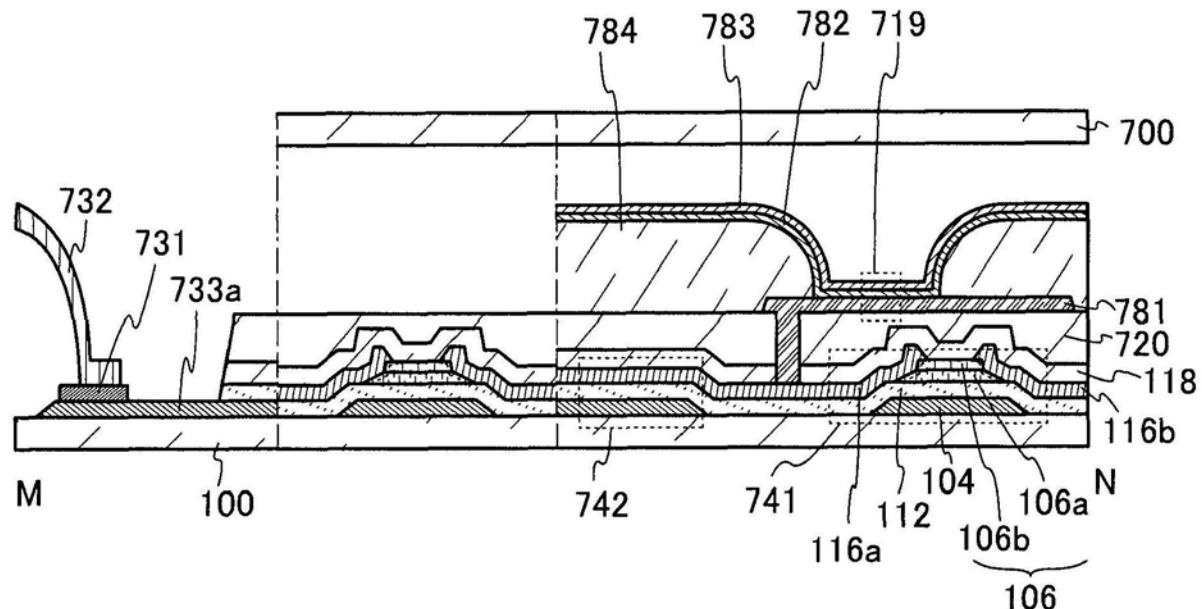

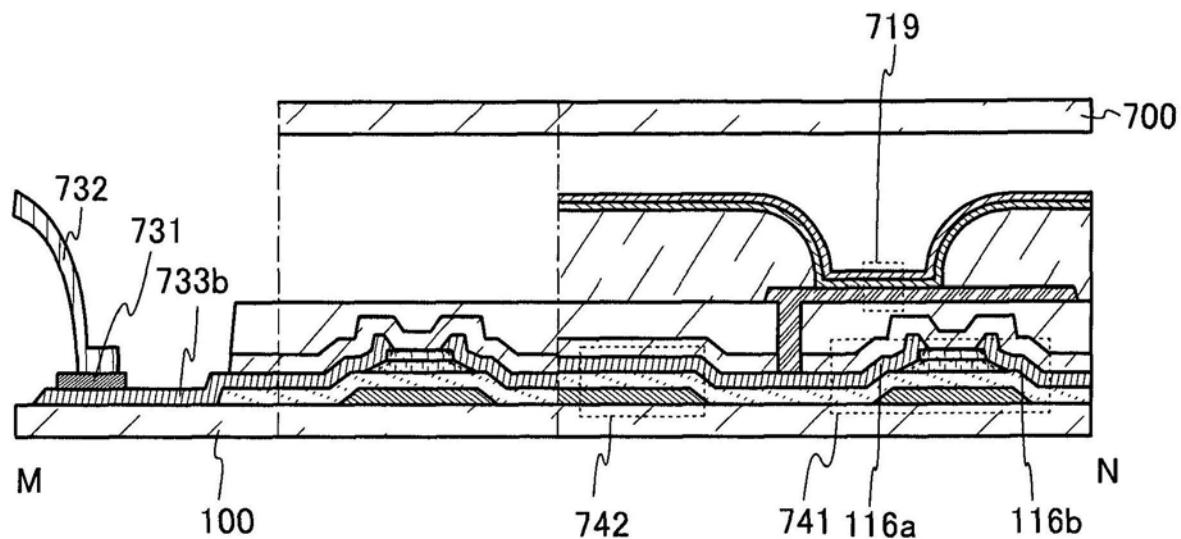

[0467] 图16B是对应于图16A的点划线M-N的EL显示装置的截面图。FPC732经由端子731与布线733a连接。另外,布线733a在与栅电极104相同的层。

[0468] 另外,图16B示出晶体管741及电容器742设置在相同平面上的例子。通过采用这种结构,可以将电容器742形成在与晶体管741的栅电极、栅极绝缘膜及源电极(漏电极)相同平面上。如此,通过将晶体管741及电容器742设置在相同平面上,可以缩短EL显示装置的制造工序,由此可以提高生产率。

[0469] 图16B示出作为晶体管741而应用图1A至图1D所示的晶体管的例子。因此,关于在

晶体管741的各构成中以下不特别进行说明的构成，参照关于图1A至图1D所记载的说明。

[0470] 在晶体管741及电容器742上设置有绝缘膜720。

[0471] 在此，在绝缘膜720及保护绝缘膜118中设置有直到晶体管741的源电极116a的开口部。

[0472] 在绝缘膜720上设置有电极781。电极781经由设置在绝缘膜720及保护绝缘膜118中的开口部与晶体管741的源电极116a连接。

[0473] 在电极781上设置有包含直到电极781的开口部的隔壁784。

[0474] 在隔壁784上设置有通过设置在隔壁784中的开口部而与电极781接触的发光层782。

[0475] 在发光层782上设置有电极783。

[0476] 电极781、发光层782和电极783相重叠的区域成为发光元件719。

[0477] 另外，关于绝缘膜720，参照保护绝缘膜118的记载。或者，也可以使用聚酰亚胺树脂、丙烯酸树脂、环氧树脂、硅酮树脂等的树脂膜。

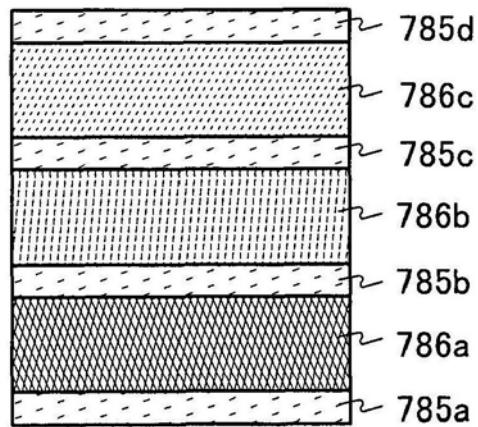

[0478] 发光层782不局限于单层，也可以通过层叠多种发光层等来设置发光层782。例如，可以采用图16C所示的结构。图16C是依次层叠了中间层785a、发光层786a、中间层785b、发光层786b、中间层785c、发光层786c以及中间层785d的结构。此时，当发光层786a、发光层786b以及发光层786c采用适当的发光颜色的发光层，则可以形成彩色再现性高或者发光效率高的发光元件719。

[0479] 也可以通过层叠多种发光层地设置而得到白色光。虽然在图16B中未图示，但是也可以采用经由着色层提取白色光的结构。

[0480] 虽然在此示出了设置有三个发光层及四个中间层的结构，但是不局限于该结构，也可以适当地改变发光层及中间层的层数。例如，可以仅由中间层785a、发光层786a、中间层785b、发光层786b以及中间层785c构成。此外，也可以采用由中间层785a、发光层786a、中间层785b、发光层786b、发光层786c以及中间层785d构成而省略中间层785c的结构。

[0481] 另外，中间层可以以层叠结构而采用空穴注入层、空穴传输层、电子传输层及电子注入层等。另外，中间层不一定包含上述所有层。可以适当地选择并设置这些层。另外，也可以重复设置具有同样功能的层。另外，作为中间层，除了载流子产生层以外，还可以适当地追加电子中继层等。

[0482] 电极781使用具有可见光透过性的导电膜即可。具有可见光透过性是指在可见光区(例如波长范围在400nm至800nm之间)的平均透过率为70%以上，尤其为80%以上。

[0483] 作为电极781例如可以使用In-Zn-W氧化物膜、In-Sn氧化物膜、In-Zn氧化物膜、氧化铟膜、氧化锌膜以及氧化锡膜等氧化物膜。另外，上述氧化物膜也可以添加有微量的Al、Ga、Sb、F等。另外，也可以使用具有能够透光的程度的金属薄膜(优选为5nm至30nm左右)。例如可以使用5nm厚的Ag膜、Mg膜或者Ag-Mg合金膜。

[0484] 或者，电极781优选使用高效率地反射可见光的膜。例如，电极781使用包含锂、铝、钛、镁、镧、银、硅或镍的膜即可。

[0485] 电极783可以使用选自作为电极781而示出的膜。此外，在电极781具有可见光透过性的情况下，优选的是，电极783高效率地反射可见光。另外，在电极781高效率地反射可见光的情况下，优选的是，电极783具有可见光透过性。

[0486] 此外,虽然以图16B所示的结构来设置电极781及电极783,但是也可以互相调换电极781和电极783。作为阳极发挥功能的电极优选使用功函数大的导电膜,作为阴极发挥功能的电极优选使用功函数小的导电膜。但是,在与阳极接触并设置载流子产生层的情况下,可以将各种导电膜用于阳极,而不用考虑功函数。

[0487] 关于隔壁784,参照保护绝缘膜118的记载。或者也可以使用聚酰亚胺树脂、丙烯酸树脂、环氧树脂、硅酮树脂等的树脂膜。

[0488] 此外,在显示装置中,适当地设置黑矩阵(遮光膜)、偏振构件、相位差构件、防反射构件等的光学构件(光学基板)等。例如,也可以使用利用偏振基板以及相位差基板的圆偏振。

[0489] 与发光元件719连接的晶体管741具有稳定的电气特性。因此,可以提供显示品质高的EL显示装置。

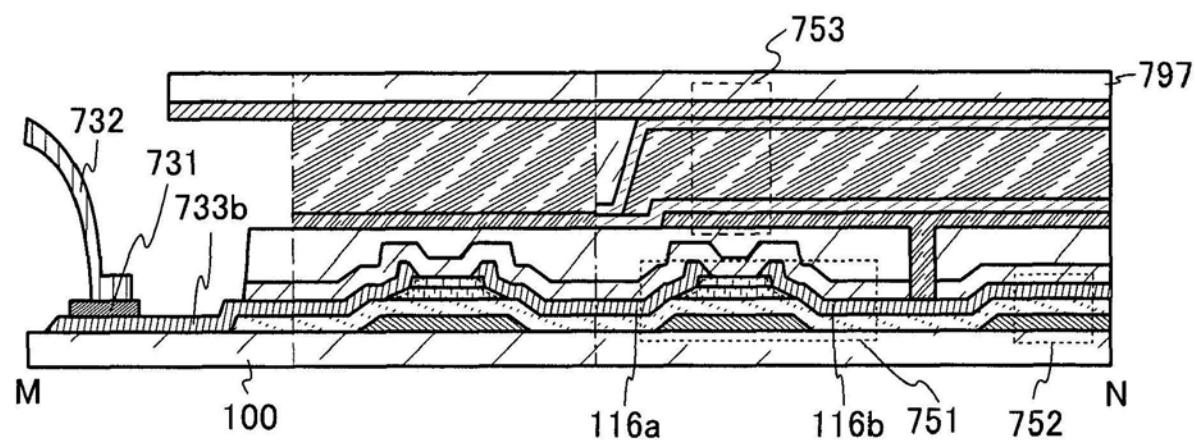

[0490] 图17A和图17B是与图16B一部分不同的EL显示装置的截面图的一个例子。具体地,不同点为与FPC732连接的布线。在图17A中,FPC732经由端子731与布线733b连接。布线733b在与源电极116a及漏电极116b相同的层。在图17B中,FPC732经由端子731与布线733c连接。布线733c在与电极781相同的层。

[0491] 3-1-2. 液晶显示装置

[0492] 接着,对使用液晶元件的显示装置(也称为液晶显示装置)进行说明。

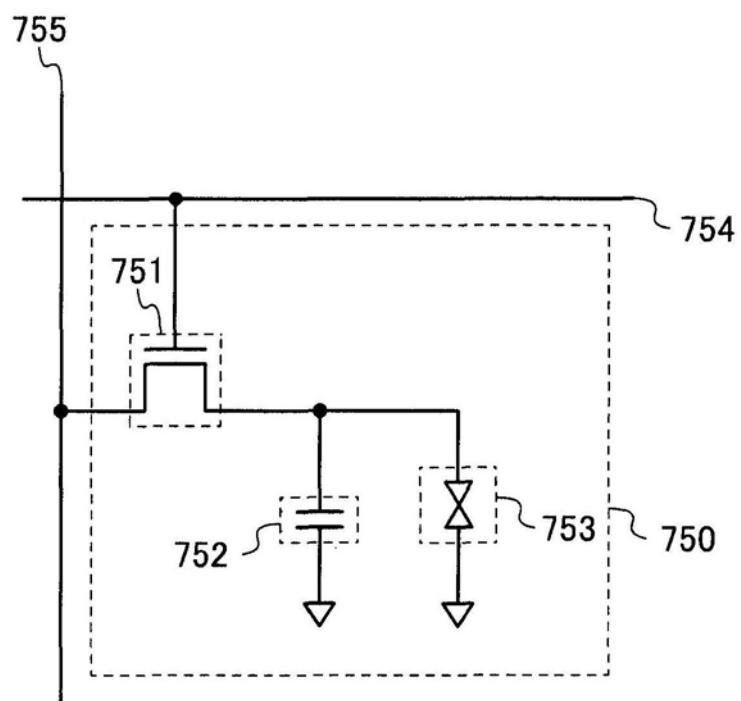

[0493] 图18是示出液晶显示装置的像素的结构例的电路图。图18所示的像素750包含晶体管751、电容器752、一对在电极之间的填充有液晶的元件(以下称为液晶元件)753。

[0494] 在晶体管751中,源极和漏极中的一个与信号线755电连接,栅极与扫描线754电连接。

[0495] 在电容器752中,一个电极与晶体管751的源极和漏极中的另一个电连接,另一个电极与供应公共电位的布电线连接。

[0496] 在液晶元件753中,一个电极与晶体管751的源极和漏极中的另一个电连接,另一个电极与供应公共电位的布电线连接。此外,上述供应到与上述电容器752的另一个电极电连接的布线的公共电位与供应到液晶元件753的另一个电极的公共电位可以不同。

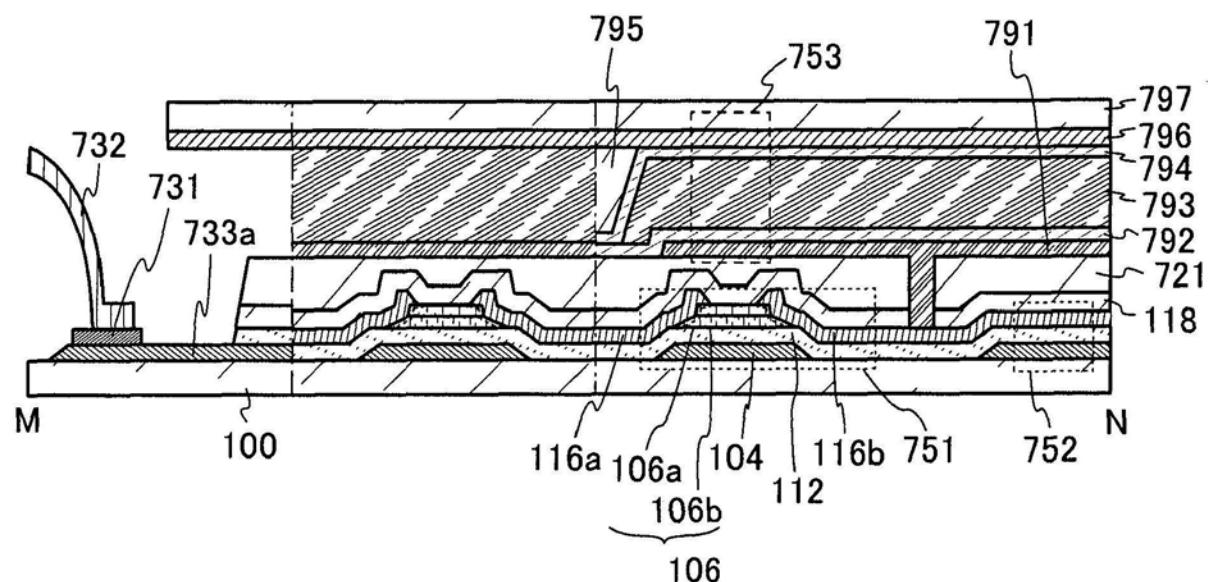

[0497] 另外,液晶显示装置的俯视图与EL显示装置的俯视图大致相同。图19A示出对应于图16A的点划线M-N的液晶显示装置的截面图。在图19A中,FPC732经由端子731与布线733a连接。另外,布线733a在与栅电极104相同的层。

[0498] 图19A示出晶体管751及电容器752设置在相同平面上的例子。通过采用这种结构,可以将电容器752制作在与晶体管751的栅电极、栅极绝缘膜及源电极(漏电极)相同平面上。这样地,通过将晶体管751及电容器752设置在相同平面上,可以缩短液晶显示装置的制造工序,由此提高生产率。

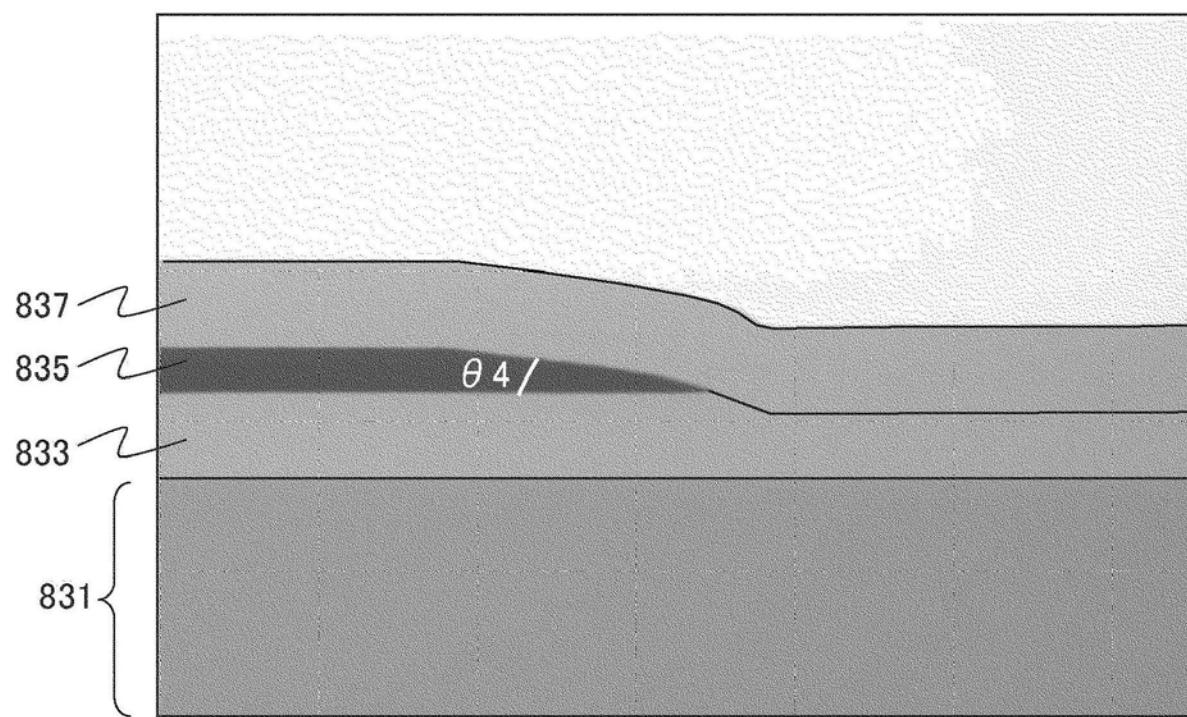

[0499] 作为晶体管751可以使用上述晶体管。图19A示出应用图1A至1D所示的晶体管的例子。因此,关于在晶体管751的各构成中以下不进行说明的构成,参照图1A至1D所示的说明。

[0500] 另外,晶体管751可以使用截止电流极小的晶体管。因此,保持在电容器752中的电荷不容易泄漏,可以在长期间保持施加到液晶元件753的电压。因此,当显示动作少的动态图像、静态图像时,通过使晶体管751成为截止状态,不需要用于晶体管751的动作的功率,由此可以成为耗电量低的液晶显示装置。

[0501] 考虑到配置在像素部中的晶体管751的泄漏电流等,将设置在液晶显示装置中的电容器752的大小设定成能够在规定期间内保存电荷。通过使用晶体管751,因设置具有各像素中的液晶电容的1/3以下,优选为1/5以下的电容大小的电容器就已足够,所以可以提高像素的开口率。

[0502] 在晶体管751及电容器752上设置有绝缘膜721。

[0503] 在此,在绝缘膜721及保护绝缘膜118中设置有直到晶体管751的漏电极116b的开口部。

[0504] 在绝缘膜721上设置有电极791。电极791通过设置在绝缘膜721及保护绝缘膜118中的开口部与晶体管751的漏电极116b连接。

[0505] 在电极791上设置有作为取向膜发挥功能的绝缘膜792。

[0506] 在绝缘膜792上设置有液晶层793。

[0507] 在液晶层793上设置有作为取向膜发挥功能的绝缘膜794。

[0508] 在绝缘膜794上设置有隔离物795。

[0509] 在隔离物795及绝缘膜794上设置有电极796。

[0510] 在电极796上设置有基板797。

[0511] 此外,关于绝缘膜721,参照保护绝缘膜118的记载。或者,也可以使用聚酰亚胺树脂、丙烯酸树脂、环氧树脂、硅酮树脂等的树脂膜。

[0512] 液晶层793使用热致液晶、低分子液晶、高分子液晶、高分子分散型液晶、强介电性液晶、反强介电性液晶等即可。这些液晶根据条件而呈现胆甾相、近晶相、立方相、手性向列相、各向同性相等。

[0513] 此外,作为液晶层793也可以使用呈现蓝相的液晶。在这种情况下,采用不设置作为取向膜发挥功能的绝缘膜792及绝缘膜794的结构即可。

[0514] 电极791使用具有可见光透过性的导电膜即可。

[0515] 在液晶显示装置为透过型的情况下,作为电极791例如可以使用In-Zn-W氧化物膜、In-Sn氧化物膜、In-Zn氧化物膜、氧化铟膜、氧化锌膜以及氧化锡膜等氧化物膜。另外,上述氧化物膜也可以添加有微量的Al、Ga、Sb、F等。另外,也可以使用具有能够透光的程度的金属薄膜(优选为5nm至30nm左右)。

[0516] 在液晶显示装置为反射型的情况下,电极791优选使用高效率地反射可见光的膜。例如,电极791使用包含铝、钛、铬、铜、钼、银、钽或钨的膜即可。

[0517] 在液晶显示装置为透过型的情况下,电极796可以使用选自作为电极791而示出的具有可见光透过性的导电膜。另一方面,在液晶显示装置为反射型的情况下,在电极791具有可见光透过性的情况下,优选的是电极796高效率地反射可见光。另外,在电极791高效率地反射可见光的情况下,电极796优选具有可见光透过性。

[0518] 此外,虽然以图19A所示的结构设置电极791及电极796,但是也可以互相调换电极791和电极796。

[0519] 绝缘膜792及绝缘膜794使用有机化合物或者无机化合物形成即可。

[0520] 隔离物795从有机化合物或者无机化合物选择而使用即可。另外,隔离物795可以具有柱状或者球状等各种形状。

[0521] 电极791、绝缘膜792、液晶层793、绝缘膜794以及电极796相互重叠的区域成为液

晶元件753。

[0522] 基板797使用玻璃、树脂或者金属等即可。基板797可以具有柔性。

[0523] 图19B和图19C是其一部分与图19A不同的液晶显示装置的截面图的一个例子。具体地,不同点为与FPC732连接的布线。在图19B中,FPC732通过端子731与布线733b连接。布线733b在与源电极116a及漏电极116b相同的层。在图19C中,FPC732经由端子731与布线733c连接。布线733c在与电极791相同的层。

[0524] 与液晶元件753连接的晶体管751具有稳定的电气特性。因此,可以提供显示品质高的液晶显示装置。另外,由于可以使晶体管751的截止电流极小,所以可以提供耗电量低的液晶显示装置。

[0525] 在液晶显示装置中,可以适当地选择动作模式。例如,有与基板垂直地施加电压的垂直电场方式以及与基板平行地施加电压的水平电场方式。具体而言,可以举出TN模式、VA模式、MVA模式、PVA模式、ASM模式、TBA模式、OCB模式、FLC模式、AFLC模式或FFS模式等。

[0526] 在液晶显示装置中,适当地设置黑矩阵(遮光层)、偏振构件、相位差构件、防反射构件等的光学构件(光学基板)等。例如,也可以使用利用偏振基板以及相位差基板的圆偏振。另外,作为光源,也可以使用背光灯、侧光灯等。

[0527] 另外,也可以作为背光灯而使用多个发光二极管(LED)来进行时间分割显示方式(场序制驱动方式)。通过应用场序制驱动方式,可以不使用着色层地进行彩色显示。

[0528] 如上所述,作为像素部中的显示方式,可以采用前进方式或交错方式等。此外,当进行彩色显示时作为在像素中受到控制的色彩要素不局限于RGB(R表示红色,G表示绿色,B表示蓝色)这三种颜色。例如,也可以采用RGBW(W表示白色)或者对RGB追加黄色(yellow)、青色(cyan)、品红色(magenta)等中的一种以上的颜色。此外,每个色彩要素的点中的显示区的大小也可以不同。但是,本发明不局限于彩色显示的显示装置,而也可以应用于单色显示的液晶显示装置。

[0529] 3-2.微型计算机

[0530] 上述晶体管可以用于装载在各种电子设备中的微型计算机。

[0531] 下面,作为装载了微型计算机的电子设备的一个例子,使用图20、图21、图22A至图22C以及图23A说明火灾警报器的结构及动作。

[0532] 另外,在本说明书中,火灾警报器表示紧急通报火灾发生的所有装置,其包括诸如住宅用火灾警报器、自动火灾警报设备、用于该自动火灾警报设备的火灾检测器等。

[0533] 图20所示的警报装置至少具有微型计算机500。在此,微型计算机500设置在警报装置的内部。微型计算机500包括与高电位电源线VDD电连接的电源门控制器503、与高电位电源线VDD及电源门控制器503电连接的电源门504、与电源门504电连接的CPU(Central Processing Unit:中央处理器)505、以及与电源门504及CPU505电连接的检测部509。另外,CPU505包含易失性存储部506及非易失性存储部507。

[0534] 另外,CPU505经接口508与总线502电连接。与CPU505同样,接口508也与电源门504电连接。作为接口508的总线标准,例如可以使用I<sup>2</sup>C总线等。在警报装置中设置经由接口508与电源门504电连接的发光元件530。

[0535] 作为发光元件530优选发出指向性强的光,例如可以使用有机EL元件、无机EL元件、LED等。

[0536] 电源门控制器503具有定时器,依照该定时器控制电源门504。电源门504依照电源门控制器503的控制,对CPU505、检测部509及接口508供应或切断从高电位电源线VDD供应的电源。在此,作为电源门504可以使用如晶体管等的开关元件。

[0537] 通过使用这种电源门控制器503及电源门504,可以在测定光量的期间内,进行对检测部509、CPU505及接口508的电源供应,并且在测定期间的空闲期间可以切断对检测部509、CPU505及接口508的电源供应。通过使警报装置这样动作,与对上述各个结构常时供应电源的情况相比,能够谋求耗电量的降低。

[0538] 另外,在作为电源门504使用晶体管的情况下,优选使用用于非易失性存储部507并且截止电流极低的晶体管,例如在上述实施方式中记载的晶体管。通过采用这种晶体管,当由电源门504切断电源时可以减少泄漏电流,谋求耗电量的降低。

[0539] 也可以在警报装置中设置直流电源501,从直流电源501对高电位电源线VDD供应电源。直流电源501的高电位一侧的电极与高电位电源线VDD电连接,直流电源501的低电位一侧的电极与低电位电源线VSS电连接。低电位电源线VSS与微型计算机500电连接。在此,对高电位电源线VDD供应高电位H。另外,对低电位电源线VSS提供诸如接地电位(GND)等的低电位L。

[0540] 在作为直流电源501而使用电池的情况下,例如采用在框体中设置包括如下部件的电池箱的结构即可,即与高电位电源线VDD电连接的电极、与低电位电源线VSS电连接的电极、以及可以保持该电池的框体。另外,警报装置也可以不一定设置直流电源501,例如也可以采用从设置在该警报装置的外部的交流电源经由布线供应电源的结构。

[0541] 此外,作为上述电池,也可以使用二次电池,如锂离子二次电池(也称为锂离子蓄电池、锂离子电池或lithium ion battery)。另外,优选设置太阳能电池以能够对该二次电池进行充电。

[0542] 检测部509测量有关异常的物理量而对CPU505发送测量值。有关异常的物理量根据警报装置的用途而不同,在作为火灾警报器发挥功能的警报装置中,测量有关火灾的物理量。因此,在检测部509中,测量作为有关火灾的物理量的光量而检测出烟雾的存在。

[0543] 检测部509具有与电源门504电连接的光传感器511、与电源门504电连接的放大器512、以及与电源门504及CPU505电连接的AD转换器513。发光元件530、光传感器511、放大器512及AD转换器513在电源门504对检测部509供应电源时进行动作。

[0544] 图21示出警报装置的截面的一部分。在p型半导体基板401上具有元件分离区403,形成有n型晶体管519,该n型晶体管519包括:栅极绝缘膜407、栅电极409、n型杂质区411a、以及n型杂质区411b。n型晶体管519使用单晶硅等的半导体来形成,所以可以进行高速动作。因此,可以形成能够进行高速访问的CPU的易失性存储部。另外,在n型晶体管519上设置有绝缘膜415及绝缘膜417。

[0545] 另外,在对绝缘膜415及绝缘膜417的一部分选择性地进行了蚀刻的开口部处形成接触插头419a及接触插头419b,在绝缘膜417、接触插头419a以及接触插头419b上设置有具有沟槽部的绝缘膜421。另外,在绝缘膜421的沟槽部形成布线423a及布线423b。另外,在绝缘膜421、布线423a以及布线423b上通过溅射法、CVD法等形成绝缘膜420,在该绝缘膜420上形成具有沟槽部的绝缘膜422。在绝缘膜422的沟槽部形成电极424。电极424是作为第二晶体管517的背栅电极发挥功能的电极。通过设置这样的电极424,可以进行第二晶体管517的

阈值电压的控制。

[0546] 另外,在绝缘膜422及电极424上通过溅射法、CVD法等设置绝缘膜425。

[0547] 在绝缘膜425上设置第二晶体管517及光电转换元件514。第二晶体管517包括:包含氧化物半导体膜206a及氧化物膜206b的多层膜206;接触于多层膜206上的源电极216a及漏电极216b;栅极绝缘膜212;栅电极204;以及保护绝缘膜218。另外,设置覆盖光电转换元件514及第二晶体管517的绝缘膜445,在绝缘膜445上具有接触于漏电极216b的布线449。布线449作为使第二晶体管517的漏电极与n型晶体管519的栅电极409电连接的节点发挥功能。

[0548] 光传感器511包括光电转换元件514、电容元件、第一晶体管、第二晶体管517、第三晶体管以及n型晶体管519。在此,作为光电转换元件514,例如可以采用光电二极管等。

[0549] 光电转换元件514的端子的一个与低电位电源线VSS电连接,端子的另一个与第二晶体管517的源电极和漏电极中的一个电连接。对第二晶体管517的栅电极提供电荷累积控制信号Tx,源电极和漏电极中的另一个与电容元件的一对电极中的一个、第一晶体管的源电极和漏电极中的一个、以及n型晶体管519的栅电极电连接(下面,有时将该节点称为节点FD)。电容元件的一对电极中的另一个与低电位电源线VSS电连接。对第一晶体管的栅电极提供复位信号Res,源电极和漏电极中的另一个与高电位电源线VDD电连接。n型晶体管519的源电极和漏电极中的一个与第三晶体管的源电极和漏电极中的一个、以及放大器512电连接。另外,n型晶体管519的源电极和漏电极中的另一个与高电位电源线VDD电连接。对第三晶体管的栅电极提供偏置信号Bias,源电极和漏电极中的另一个与低电位电源线VSS电连接。

[0550] 此外,也可以不一定要设置电容元件,例如在n型晶体管519等的寄生电容充分大的情况下也可以采用不设置电容元件的结构。

[0551] 另外,第一晶体管及第二晶体管517优选使用截止电流极低的晶体管。此外,作为截止电流极低的晶体管,优选采用使用了上述的包含氧化物半导体膜的多层膜的晶体管。通过采用这种结构,能够长时间保持节点FD的电位。

[0552] 另外,在图21所示的结构中,与第二晶体管517电连接地在绝缘膜425上设置有光电转换元件514。

[0553] 光电转换元件514具有设置在绝缘膜425上的半导体膜260、以及接触于半导体膜260上地设置的第二晶体管517的源电极216a、电极216c。源电极216a是作为第二晶体管517的源电极或漏电极发挥功能的电极,并使光电转换元件514与第二晶体管517电连接。

[0554] 在半导体膜260、第二晶体管517的源电极216a及电极216c上设置有栅极绝缘膜212、保护绝缘膜218以及绝缘膜445。另外,在绝缘膜445上设置有布线456,经由设置于栅极绝缘膜212、保护绝缘膜218以及绝缘膜445的开口与电极216c接触。

[0555] 电极216c可以通过与第二晶体管517的源电极216a及漏电极216b相同的工序形成,布线456可以通过与布线449相同的工序形成。

[0556] 作为半导体膜260,设置能够进行光电转换的半导体膜即可,例如可以使用硅及锗等。在将硅用于半导体膜260的情况下,作为检测可见光的光传感器发挥功能。另外,因为硅和锗能够吸收的电磁波的波长不同,所以如果采用将锗用于半导体膜260的结构,则能够用作检测红外线的传感器。

[0557] 如上所述那样,可以在微型计算机500中内置地设置包含光传感器511的检测部509,所以可以缩减部件数,并缩小警报装置的框体。

[0558] 在上述的包含IC芯片的火灾警报器中,采用了组合多个使用上述晶体管的电路并将它们装载于一个IC芯片的CPU505。

[0559] 3-3.CPU

[0560] 图22A至图22C是示出将上述晶体管至少用于其一部分的CPU的具体结构的方框图。

[0561] 图22A所示的CPU在基板1190上包括:ALU1191(Arithmetic logic unit:算术逻辑单元);ALU控制器1192;指令解码器1193;中断控制器1194;时序控制器1195;寄存器1196;寄存器控制器1197;总线接口1198(Bus I/F);可改写的ROM1199;以及ROM接口1189(ROM I/F)。基板1190使用半导体基板、SOI基板及玻璃基板等。ROM1199和ROM接口1189可以设置在不同的芯片上。当然,图22A所示的CPU只是将其结构简化而示出的一个例子,并且实际上的CPU根据其用途具有多种结构。

[0562] 经由总线接口1198输入到CPU的命令被输入到指令解码器1193并且被解码之后,被输入到ALU控制器1192、中断控制器1194、寄存器控制器1197和时序控制器1195。

[0563] 根据被解码的指令,ALU控制器1192、中断控制器1194、寄存器控制器1197、时序控制器1195进行各种控制。具体而言,ALU控制器1192生成用于控制ALU1191的动作的信号。另外,中断控制器1194在CPU的程序执行中,根据其优先度或掩模状态来判断来自外部的输入/输出装置、外围电路的中断请求,并处理该请求。寄存器控制器1197生成寄存器1196的地址,并根据CPU的状态进行从寄存器1196的读出或对寄存器1196的写入。

[0564] 另外,时序控制器1195生成控制ALU1191、ALU控制器1192、指令解码器1193、中断控制器1194以及寄存器控制器1197的动作定时的信号。例如,时序控制器1195具备有根据基准时钟信号CLK1来生成内部时钟信号CLK2的内部时钟生成部,将内部时钟信号CLK2供应到上述各种电路。

[0565] 在图22A所示的CPU中,在寄存器1196中设置有存储单元。作为寄存器1196的存储单元,可以使用上述晶体管。

[0566] 在图22A所示的CPU中,寄存器控制器1197依照来自ALU1191的指示,进行寄存器1196中的保持动作的选择。换言之,在寄存器1196所具有的存储单元中,选择进行基于触发器的数据的保持还是进行基于电容元件的数据的保持。在选择基于触发器的数据的保持的情况下,进行对寄存器1196内的存储单元的电源电压的供应。在选择基于电容元件的数据的保持的情况下,进行对电容元件的数据改写,可以停止对寄存器1196内的存储单元的电源电压的供应。

[0567] 如图22B或图22C所示那样,关于停止电源电压供应,可以通过在存储单元组与被供应有电源电位VDD或电源电位VSS的节点之间设置开关元件来进行。以下说明图22B及图22C的电路。

[0568] 图22B及图22C是将上述晶体管用于控制对存储单元的电源电位的供应的开关元件的存储装置。

[0569] 图22B所示的存储装置具有开关元件1141以及具有多个存储单元1142的存储单元组1143。具体而言,各存储单元1142可以使用上述晶体管。经由开关元件1141,高电平的电

源电位VDD被供应到存储单元组1143所具有的各存储单元1142。进一步地,信号IN的电位和低电平的电源电位VSS的电位供应到存储单元组1143所具有的各存储单元1142。

[0570] 在图22B中,作为开关元件1141使用了上述晶体管,关于该晶体管,由提供到其栅电极层的信号SigA来控制其开关。

[0571] 此外,在图22B中示出开关元件1141只具有一个晶体管的结构,但是对此没有特别的限制,也可以具有多个晶体管。在开关元件1141具有多个作为开关元件发挥功能的晶体管时,既可以将上述多个晶体管并联地连接,又可以串联地连接,还可以并联和串联组合地连接。

[0572] 另外,在图22B中,由开关元件1141控制对存储单元组1143所具有的各存储单元1142的高电平的电源电位VDD的供应,但是也可以由开关元件1141控制低电平的电源电位VSS的供应。

[0573] 另外,图22C示出存储装置的一个例子,其中经由开关元件1141将低电平的电源电位VSS供应到存储单元组1143所具有的各存储单元1142。通过开关元件1141可以控制对存储单元组1143所具有的各存储单元1142的低电平的电源电位VSS的供应。

[0574] 在设置开关元件于存储单元组与被施加电源电位VDD或电源电位VSS的节点之间,并暂时停止CPU的动作,停止电源电压的供应的情况下,也可以保持数据,由此可以降低耗电量。具体而言,例如,在个人计算机的用户停止对键盘等输入装置输入信息的期间,也可以停止CPU的动作,由此可以降低耗电量。

[0575] 在此,以CPU为例子进行了说明,但是也可以应用于DSP (Digital Signal Processor:数字信号处理器)、定制LSI、FPGA (Field Programmable Gate Array:现场可编程门阵列) 等的LSI。

#### [0576] 3-4. 设置例

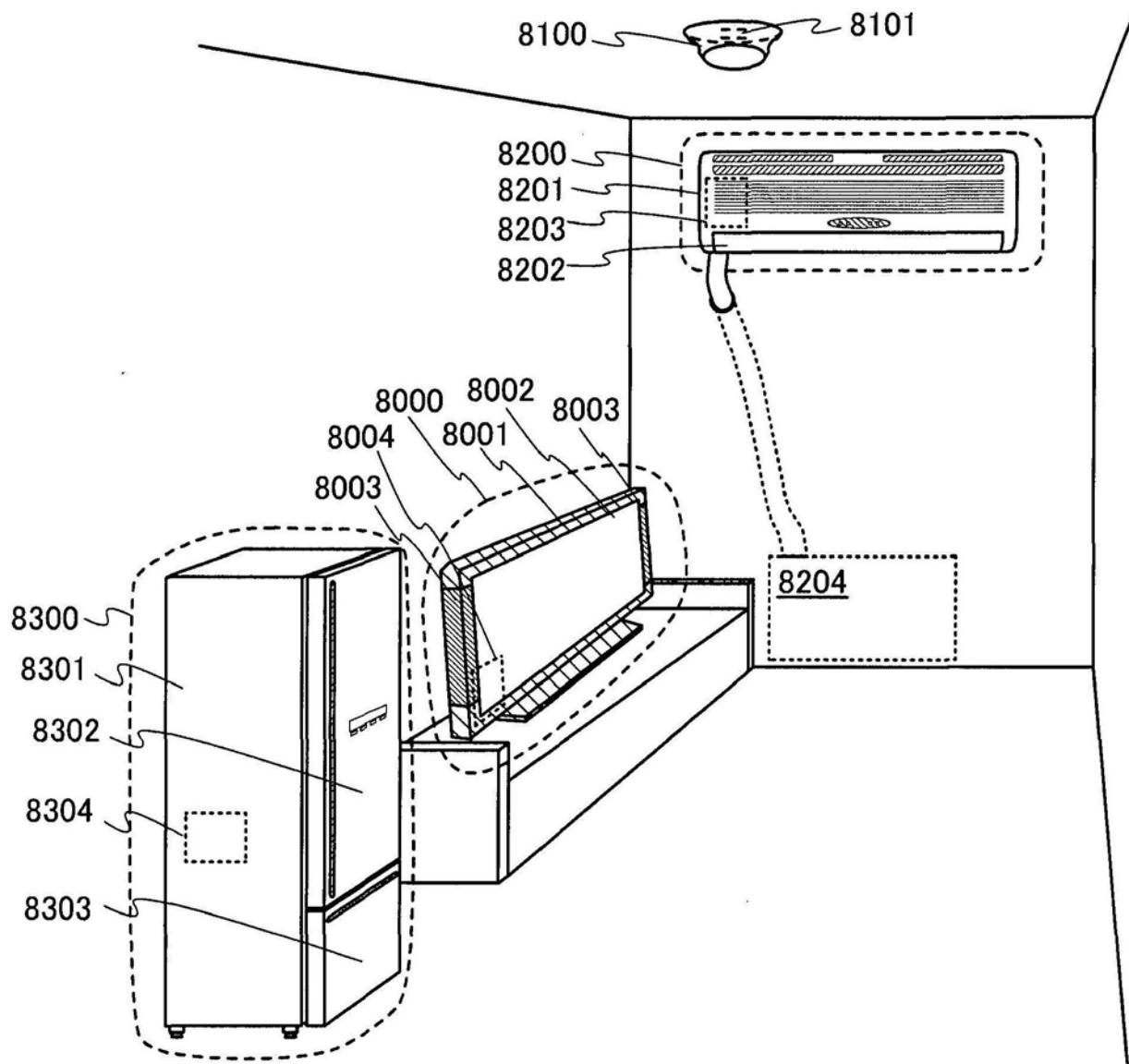

[0577] 在图23A中,警报装置8100是住宅用火灾警报器,具有检测部以及微型计算机8101。微型计算机8101包括使用上述晶体管的CPU。

[0578] 在图23A中,具有室内机8200及室外机8204的空调器包括使用上述晶体管的CPU。具体地说,室内机8200具有框体8201、送风口8202、CPU8203等。在图23A中,示例了CPU8203设置在室内机8200中的情况,但是CPU8203也可以设置在室外机8204中。或者,也可以在室内机8200和室外机8204两个中都设置有CPU8203。通过包括使用上述晶体管的CPU,可以使空调器实现省电化。

[0579] 在图23A中,电冷藏冷冻箱8300包括使用上述晶体管的CPU。具体地说,电冷藏冷冻箱8300包括框体8301、冷藏室用门8302、冷冻室用门8303及CPU8304等。在图23A中,CPU8304设置在框体8301的内部。通过包括使用上述晶体管的CPU,可以使电冷藏冷冻箱8300实现省电化。

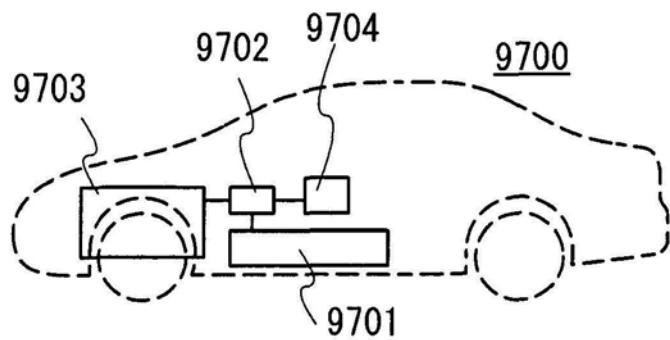

[0580] 图23B及图23C示出电动汽车的例子。电动汽车9700装载有二次电池9701。二次电池9701的电力由控制电路9702调整其输出,并供给到驱动装置9703。控制电路9702由具有未图示的ROM、RAM、CPU等的处理装置9704控制。通过包括使用上述晶体管的CPU,可以使电动汽车9700实现省电化。

[0581] 驱动装置9703是由直流电动机或交流电动机单独或者与电动机和内燃机组合而构成的。处理装置9704根据电动汽车9700的驾驶员的操作信息(加速、减速、停止等)、行车

时的信息(爬坡、下坡等信息、驱动轮受到的负荷信息等)等的输入信息,向控制电路9702输出控制信号。控制电路9702根据处理装置9704的控制信号来调整从二次电池9701供应的电能并控制驱动装置9703的输出。在装载交流电动机的情况下,虽然未图示,但是还内置有将直流转换为交流的逆变器。

[0582] 实施例1

[0583] 在本实施例中,利用图24至图30B来说明对氧化物半导体膜进行湿蚀刻时的蚀刻速度和氧化物半导体膜的侧面的形状。

[0584] 首先,说明氧化物半导体膜及蚀刻液各自的种类及蚀刻速度。

[0585] 以下说明样品1及样品2的制造方法。

[0586] 在玻璃基板上形成氧化物半导体膜。样品1在玻璃基板上具有使用 $In:Ga:Zn=1:1:1$ (原子个数比)的金属氧化物的溅射靶材形成的厚度为100nm的In-Ga-Zn氧化物膜。样品2在玻璃基板上具有使用 $In:Ga:Zn=1:3:2$ (原子个数比)的金属氧化物的溅射靶材形成的厚度为100nm的In-Ga-Zn氧化物膜。

[0587] 作为样品1中的In-Ga-Zn氧化物膜的成膜条件,使用如下条件:将溅射靶材设为 $In:Ga:Zn=1:1:1$ (原子个数比)的靶材,向溅射装置的反应室内供应作为溅射气体的流量为50sccm的氩和流量为50sccm的氧,将反应室内的压力控制为0.6Pa,并供应5kW的直流功率。此外,将形成In-Ga-Zn氧化物膜时的基板温度设为170°C。

[0588] 作为样品2的In-Ga-Zn氧化物膜的成膜条件,使用如下条件:将溅射靶材设为 $In:Ga:Zn=1:3:2$ (原子个数比)的靶材,向溅射装置的反应室内供应作为溅射气体的流量为90sccm的Ar和流量为10sccm的氧,将反应室内的压力控制为0.3Pa,并供应5kW的直流功率。此外,形成In-Ga-Zn氧化物膜时的基板温度为100°C。

[0589] 接着,对形成在样品1及样品2中的In-Ga-Zn氧化物膜进行湿蚀刻。在该湿蚀刻工序中,使用第一蚀刻液至第三蚀刻液中的任一个。作为第一蚀刻液使用25°C的85重量%的磷酸。作为第二蚀刻液使用60°C的草酸类水溶液(例如,日本关东化学株式会社制造的ITO-07N(含有5重量%以下草酸的水溶液))。作为第三蚀刻液,使用30°C的磷酸类水溶液(例如,日本和光纯药工业株式会社制造的混合酸铝液(含有72重量%的磷酸、2重量%的硝酸及9.8重量%的醋酸的水溶液))。

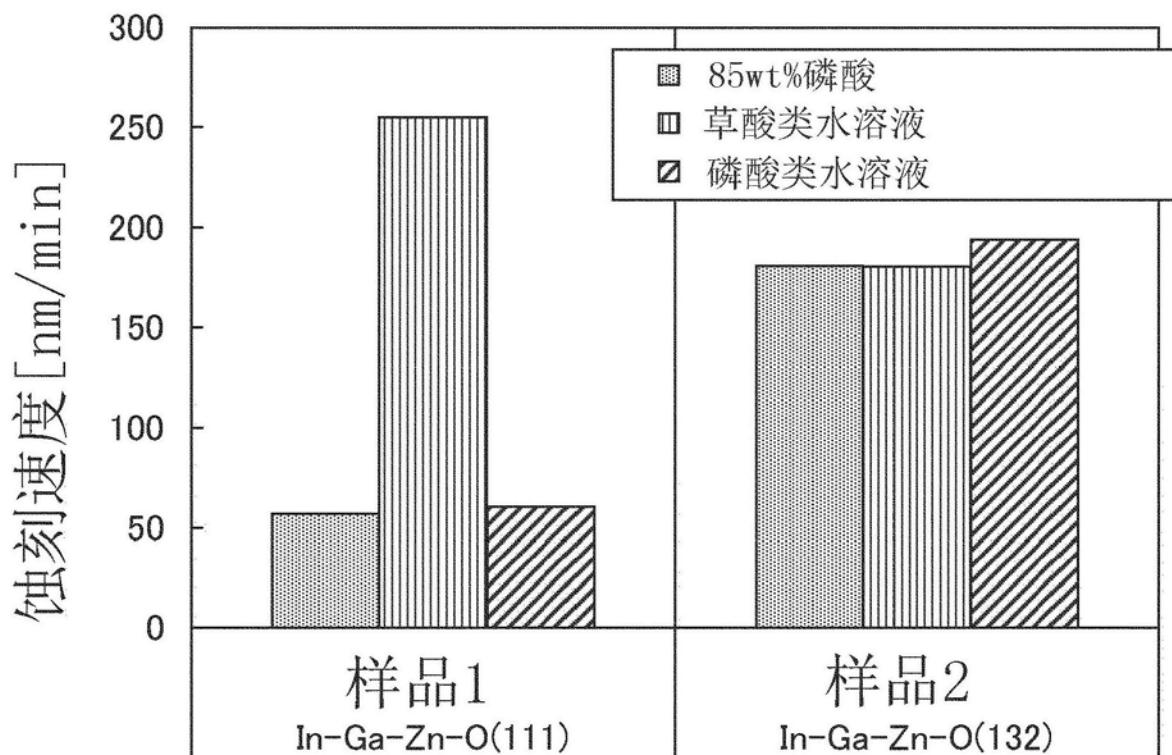

[0590] 接着,图24示出样品1及样品2中的各蚀刻液与蚀刻速度的关系。

[0591] 由图24可知,具有使用 $In:Ga:Zn=1:1:1$ (原子个数比)作为溅射靶材而形成的In-Ga-Zn氧化物膜(表示为In-Ga-Zn-O(111))的样品1在使用作为第二蚀刻液的草酸类水溶液的蚀刻中,蚀刻速度快。

[0592] 另一方面,可知,具有使用 $In:Ga:Zn=1:3:2$ (原子个数比)作为溅射靶材而形成的In-Ga-Zn氧化物膜(表示为In-Ga-Zn-O(132))的样品2在所有蚀刻液中,蚀刻速度大致相同。

[0593] 接着,说明当使用第一蚀刻液至第三蚀刻液中的任一个对层叠结构的氧化物半导体膜进行蚀刻时的氧化物半导体膜的侧面的形状。

[0594] 以下说明样品3及样品4的制造方法。此外,样品3及样品4是层叠有第一In-Ga-Zn氧化物膜和第二In-Ga-Zn氧化物膜的两层结构。

[0595] 在玻璃基板上对层叠结构的氧化物半导体膜进行成膜。首先,在玻璃基板上使用

In:Ga:Zn=1:1:1(原子个数比)的金属氧化物的溅射靶材来对厚度为35nm的第一In-Ga-Zn氧化物膜进行成膜。接着,使用In:Ga:Zn=1:3:2(原子个数比)的金属氧化物的溅射靶材来对厚度为20nm的第二In-Ga-Zn氧化物膜进行成膜。

[0596] 此外,第一In-Ga-Zn氧化物膜是利用与样品1的In-Ga-Zn氧化物膜相同的成膜条件而被进行成膜的膜。另外,第二In-Ga-Zn氧化物膜是利用与样品2的In-Ga-Zn氧化物膜相同的成膜条件而被进行成膜的膜。

[0597] 接着,对层叠结构的氧化物半导体膜进行蚀刻。在样品3中,作为蚀刻液,使用作为第一蚀刻液的25℃的85重量%的磷酸。在样品4中,作为蚀刻液,使用作为第三蚀刻液的30℃的磷酸类水溶液。

[0598] 接着,对样品5的制造方法进行说明。此外,样品5是层叠有第一In-Ga-Zn氧化物膜至第三In-Ga-Zn氧化物膜的三层结构。

[0599] 在玻璃基板上通过CVD法形成氮化硅膜及氧氮化硅膜。接着,在氧氮化硅膜上形成层叠结构的氧化物半导体膜。接着,在氧氮化硅膜上使用In:Ga:Zn=1:3:2(原子个数比)的金属氧化物的溅射靶材来形成厚度为5nm的第一In-Ga-Zn氧化物膜。接着,使用In:Ga:Zn=3:1:2(原子个数比)的金属氧化物的溅射靶材来形成厚度为20nm的第二In-Ga-Zn氧化物膜。接着,使用In:Ga:Zn=1:1:1(原子个数比)的金属氧化物的溅射靶材来形成厚度为20nm的第三In-Ga-Zn氧化物膜。接着,在第三In-Ga-Zn氧化物膜上通过CVD法形成氧氮化硅膜。

[0600] 此外,样品5中的第一In-Ga-Zn氧化物膜使用如下条件来形成:将溅射靶材设为In:Ga:Zn=1:3:2(原子个数比)的靶材,向溅射装置的反应室内供应作为溅射气体的90sccm的氩和10sccm的氧,将反应室内的压力控制为0.6Pa,并供应5kW的直流功率。第二In-Ga-Zn氧化物膜使用如下条件来形成:将溅射靶材设为In:Ga:Zn=3:1:2(原子个数比)的靶材,向溅射装置的反应室内供应作为溅射气体的50sccm的氩和50sccm的氧,将反应室内的压力控制为0.6Pa,并供应5kW的直流功率。第三In-Ga-Zn氧化物膜使用如下条件来形成:将溅射靶材设为In:Ga:Zn=1:1:1(原子个数比)的靶材,向溅射装置的反应室内供应作为溅射气体的100sccm的氧,将反应室内的压力控制为0.6Pa,并供应5kW的直流功率。此外,形成第一In-Ga-Zn氧化物膜至第三In-Ga-Zn氧化物膜时的基板温度为170℃。

[0601] 接着,对层叠结构的氧化物半导体膜进行蚀刻。在样品5中,作为蚀刻液使用作为第二蚀刻液的60℃的草酸类水溶液。

[0602] 接着,说明样品6的制造方法。此外,样品6是层叠有第一In-Ga-Zn氧化物膜及第二In-Ga-Zn氧化物膜的两层结构。

[0603] 在玻璃基板上通过CVD法形成氧氮化硅膜。接着,在氧氮化硅膜上使用与样品3及样品4相同的成膜条件,并使用In:Ga:Zn=1:1:1(原子个数比)的金属氧化物的溅射靶材而形成厚度为35nm的第一In-Ga-Zn氧化物膜之后,使用In:Ga:Zn=1:3:2(原子个数比)的金属氧化物的溅射靶材来形成厚度为20nm的第二In-Ga-Zn氧化物膜。接着,在第二In-Ga-Zn氧化物膜上形成氧氮化硅膜。

[0604] 接着,对层叠结构的氧化物半导体膜进行蚀刻。在样品6中,通过干蚀刻法对层叠结构的氧化物半导体膜进行蚀刻。此外,作为蚀刻气体使用BCl<sub>3</sub>。

[0605] 接着,使用STEM(Scanning Transmission Electron Microscopy:扫描透射电子显微术)来观察样品3至样品6的截面形状。

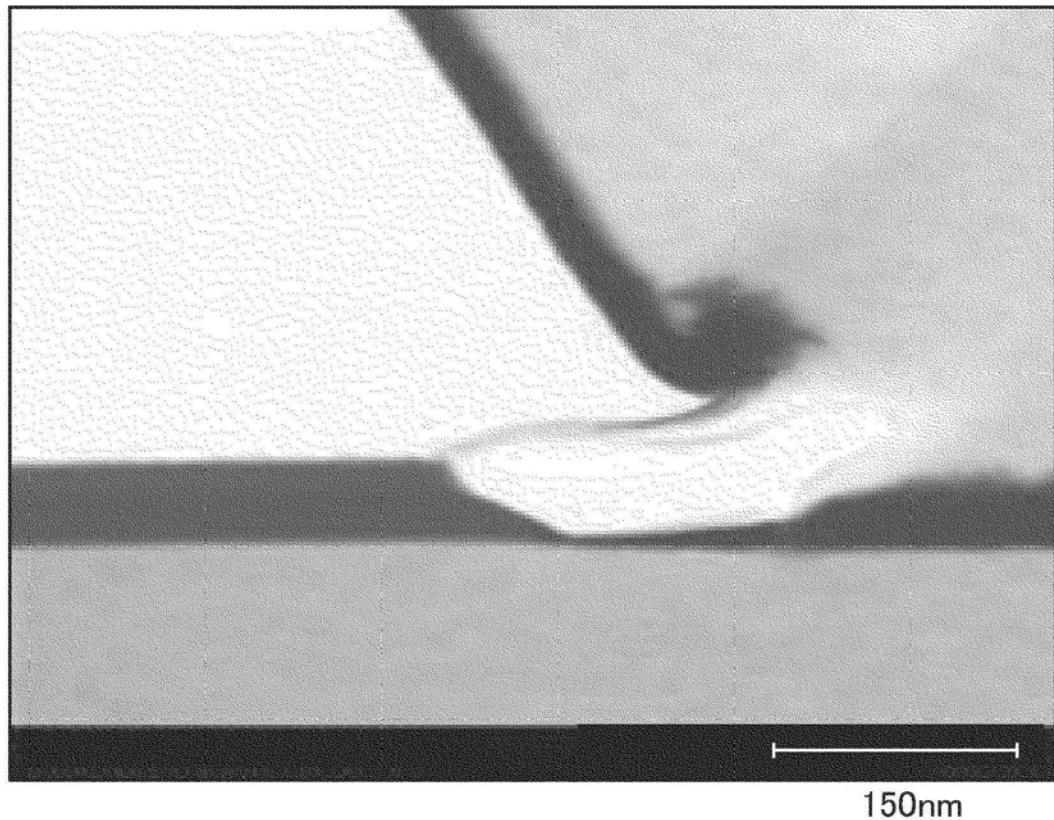

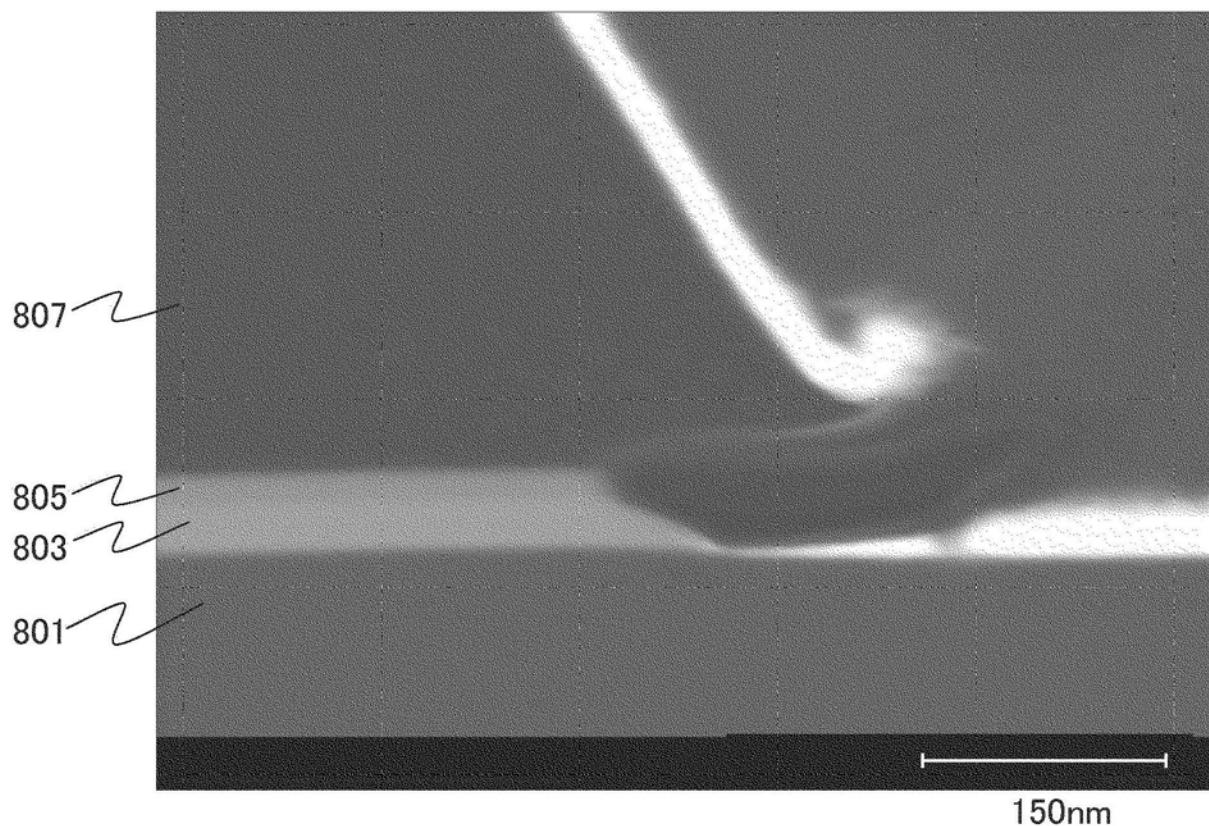

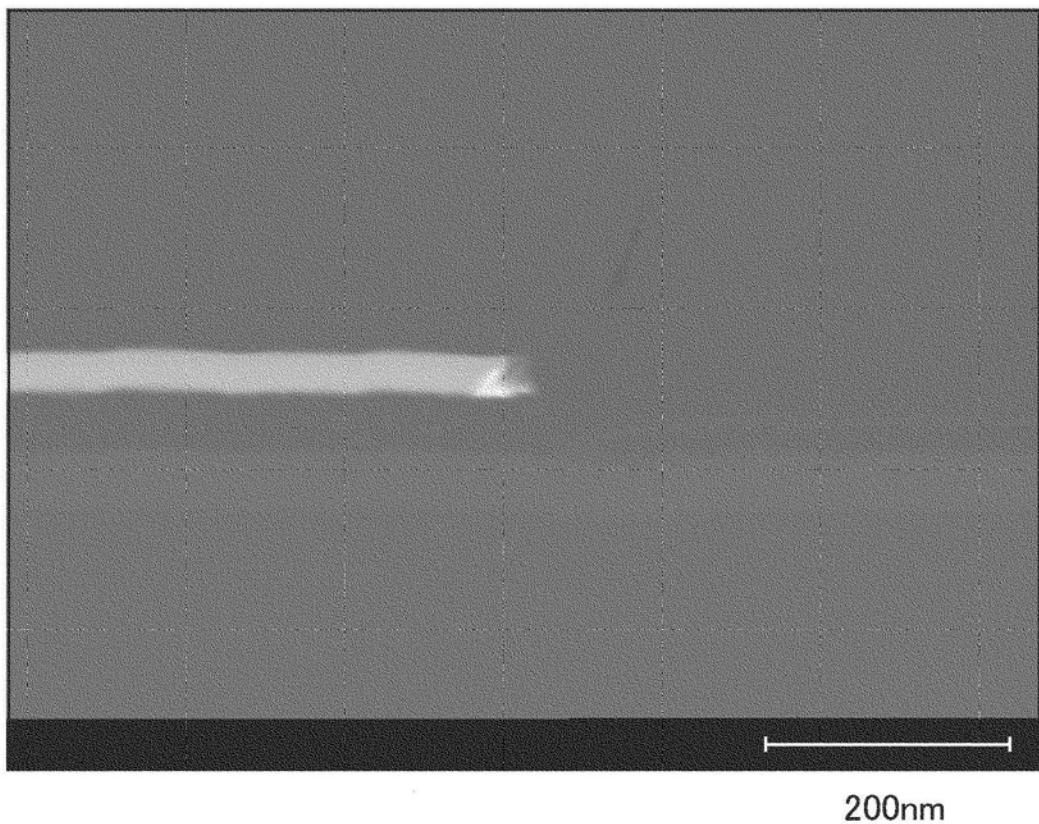

[0606] 图25A示出样品3的20万倍放大倍率的相衬图像(TE图像),图25B示出图25A的示意图。另外,图26示出样品3的15万倍放大倍率的Z对比图像(ZC图像)。

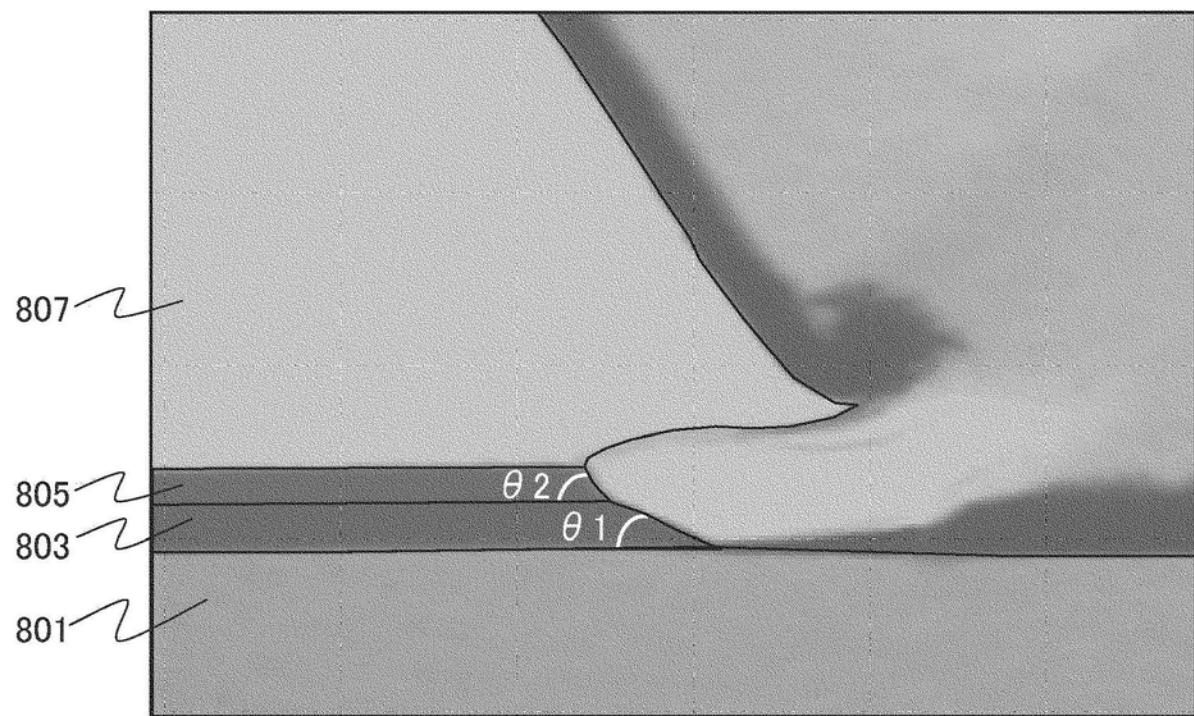

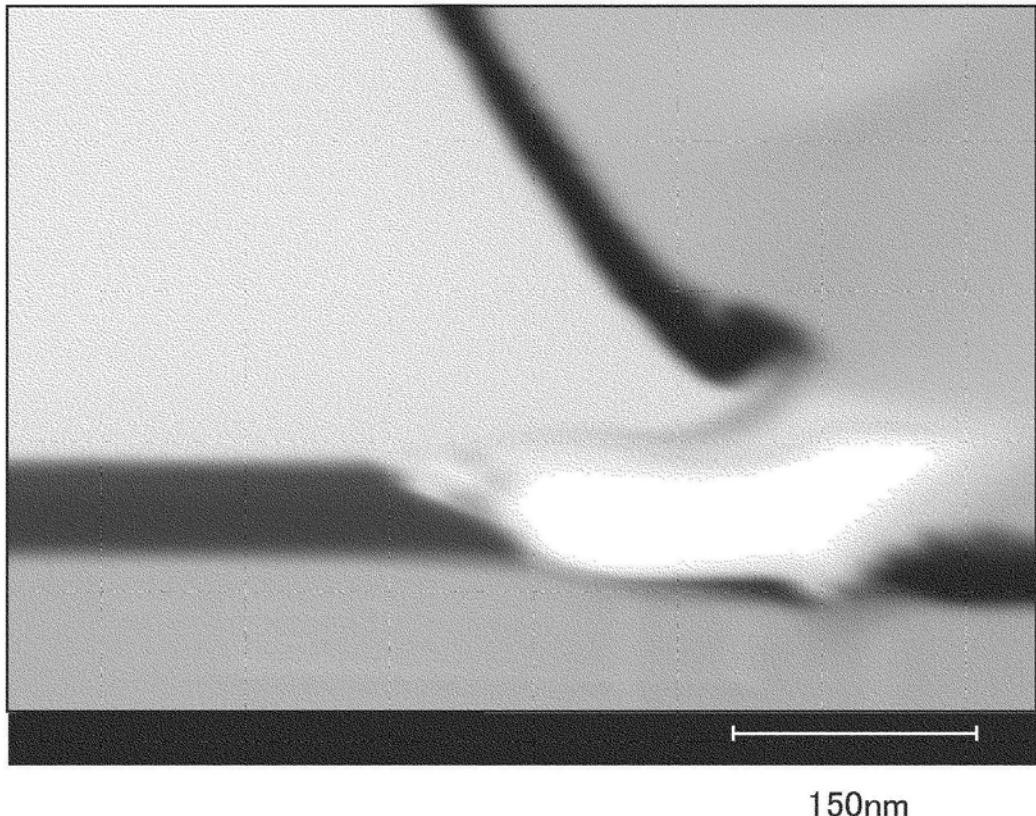

[0607] 图27A示出样品4的20万倍放大倍率的相衬图像(TE图像),图27B示出图27A的示意图。

[0608] 图28A示出样品5的15万倍放大倍率的相衬图像(TE图像),图28B示出图28A的示意图。为了说明样品5中的层叠结构的氧化物半导体膜的侧面附近的详细情况,图29A示出样品5的15万倍放大倍率的Z对比图像(ZC图像),图29B示出图29A的示意图。

[0609] 图30A示出样品6的15万倍放大倍率的相衬图像(TE图像),图30B示出图30A的示意图。

[0610] 如图25B所示,在样品3中,在玻璃基板801上形成有第一In-Ga-Zn氧化物膜803。在第一In-Ga-Zn氧化物膜803上形成有第二In-Ga-Zn氧化物膜805。在第二In-Ga-Zn氧化物膜805上设置有抗蚀剂807。

[0611] 另外,如图26所示,在样品3中,第一In-Ga-Zn氧化物膜803及第二In-Ga-Zn氧化物膜805根据其浓淡的差异而可以确认出两者的边界。就是说,在本发明的一个方式的晶体管中,即使在氧化物半导体膜和氧化物膜包含相同元素的情况下,也可以根据其组成的差异而确认出两者的边界。

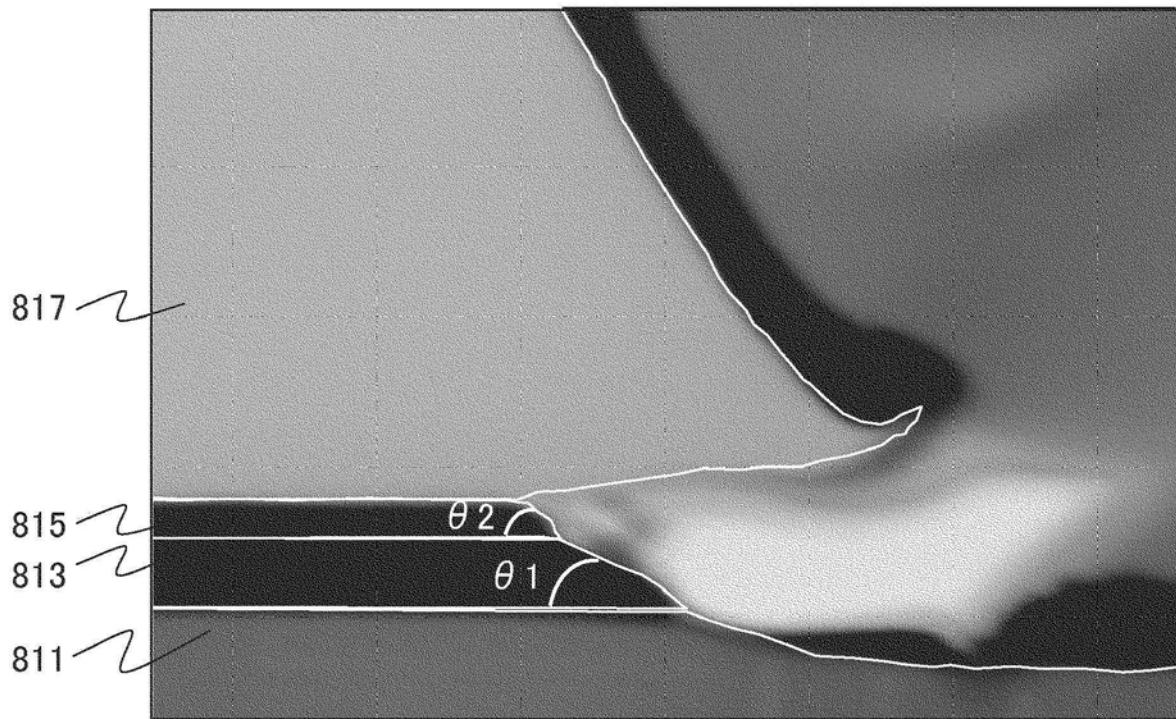

[0612] 如图27B所示,在样品4中,在玻璃基板811上形成有第一In-Ga-Zn氧化物膜813。在第一In-Ga-Zn氧化物膜813上形成有第二In-Ga-Zn氧化物膜815。在第二In-Ga-Zn氧化物膜815上设置有抗蚀剂817。

[0613] 在样品3及样品4中,将玻璃基板801、811与第一In-Ga-Zn氧化物膜803、813的侧面所呈的角度设为角度θ1。将第一In-Ga-Zn氧化物膜803、813及第二In-Ga-Zn氧化物膜805、815的界面与第二In-Ga-Zn氧化物膜805、815的侧面所呈的角度设为角度θ2。如图25A和图25B及图27A和图27B所示,可知在样品3及样品4中角度θ2大于角度θ1。

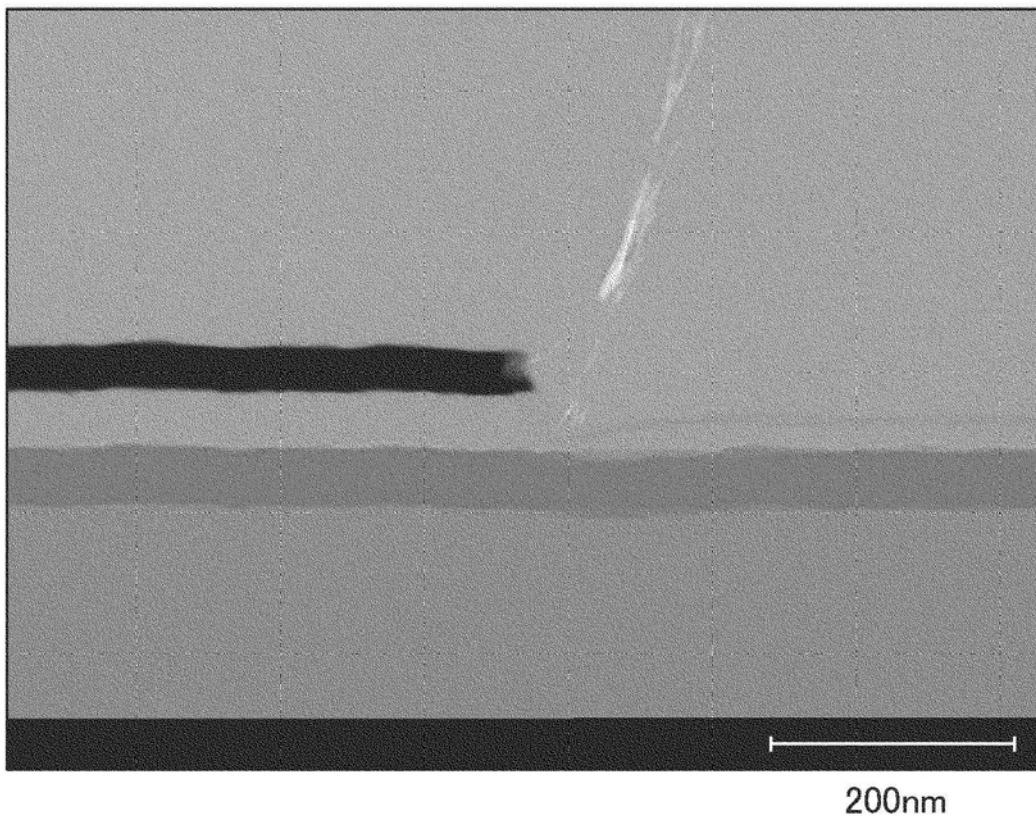

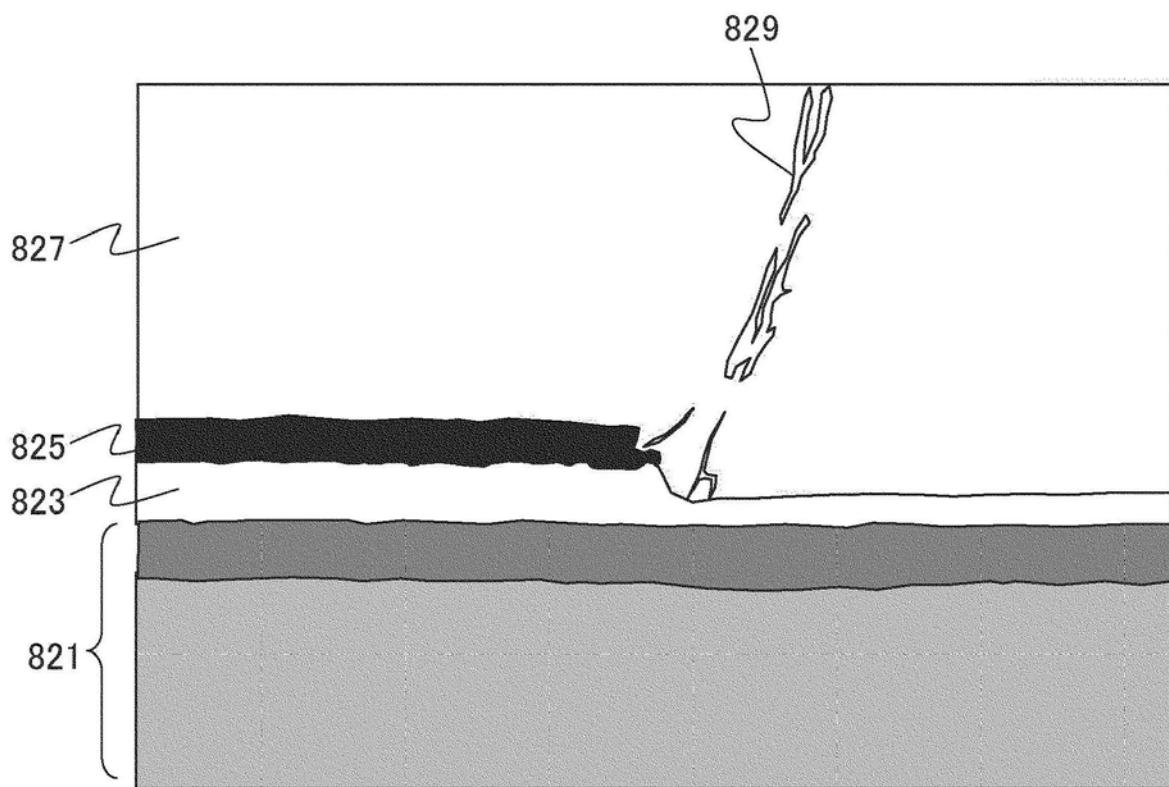

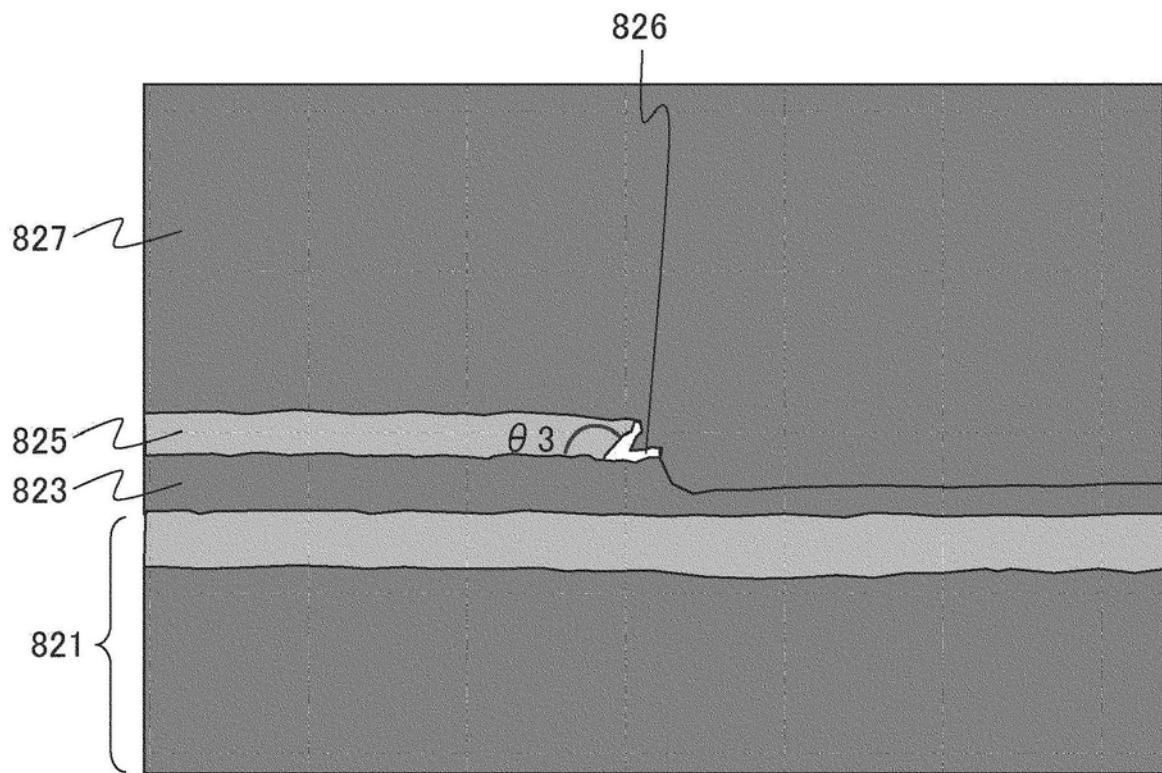

[0614] 如图28B所示,在样品5中,在氮化硅膜821上形成有氧氮化硅膜823。在氧氮化硅膜823上形成有层叠结构的氧化物半导体膜825。在氧氮化硅膜823及层叠结构的氧化物半导体膜825上形成有氧氮化硅膜827。此外,在氧氮化硅膜827中形成有低密度区829。

[0615] 在样品5中,将氧氮化硅膜823及层叠结构的氧化物半导体膜825的界面与层叠结构的氧化物半导体膜825的侧面所呈的角度称为角度θ3。如图29B所示,在样品5中,角度θ3为钝角。此外,ZC图像根据原子番号的差异而其对比度不同,由此可知在层叠结构的氧化物半导体膜825的侧面形成有具有与氧化物半导体膜不同的组成的膜826。当通过能量分散型X射线分析(Energy dispersive X-ray spectrometry:EDX)对该膜826进行分析可知,膜826包含钨。

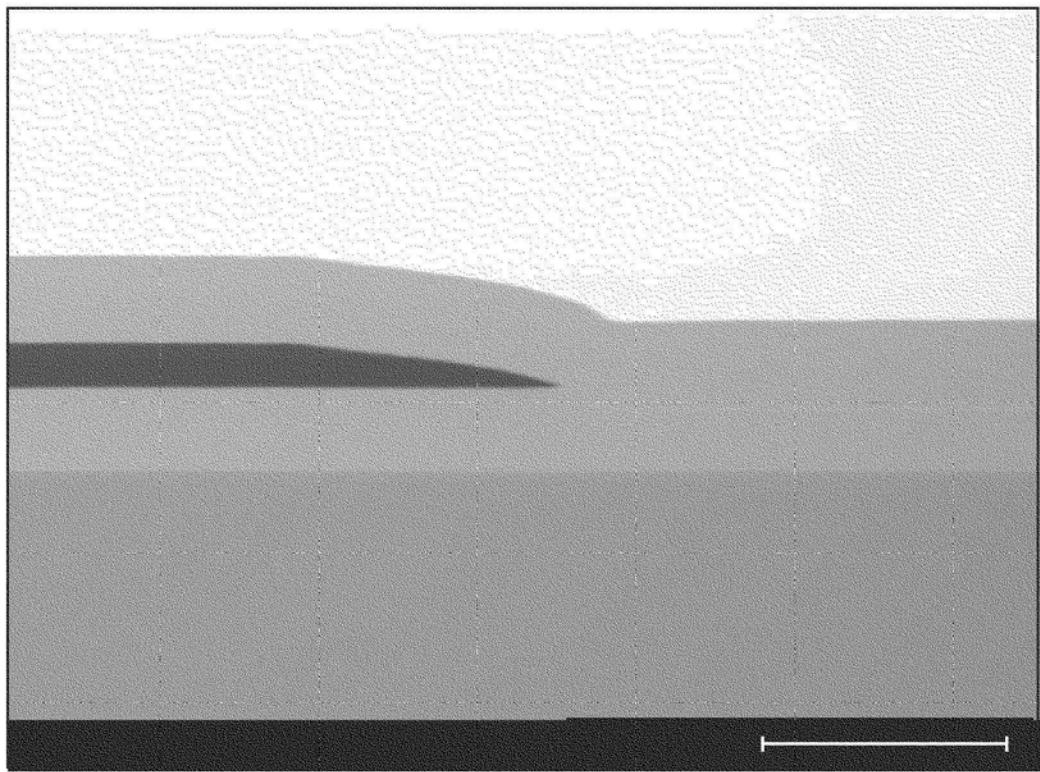

[0616] 如图30B所示,在样品6中,在玻璃基板831上形成有氧氮化硅膜833。在氧氮化硅膜833上形成有层叠结构的氧化物半导体膜835。在氧氮化硅膜833及层叠结构的氧化物半导体膜835上形成有氧氮化硅膜837。

[0617] 在样品6中,将氧氮化硅膜833及层叠结构的氧化物半导体膜835的界面与层叠结构的氧化物半导体膜835的侧面所呈的角度称为角度θ4。如图30B所示,在样品6中,角度θ4大致相同,不因氧化物半导体膜的侧面的位置而改变。

[0618] 由以上所述可知,在层叠结构的氧化物半导体膜中,通过利用将磷酸或磷酸类水

溶液用于蚀刻液的湿蚀刻法,可以使使用 $In:Ga:Zn=1:1:1$ (原子个数比)的溅射靶材形成的In-Ga-Zn氧化物膜的侧面与In-Ga-Zn氧化物膜的基底膜的界面所呈的角度 $\theta_1$ 小于使用 $In:Ga:Zn=1:3:2$ (原子个数比)的溅射靶材形成的In-Ga-Zn氧化物膜的侧面与In-Ga-Zn氧化物膜的基底膜的界面所呈的角度 $\theta_2$ 。

图1A

图1B

图1C

图1D

图2

图3

## 陷阱能级

图4

图5A

图5B

图5C

图6A

图6B

图7A

图7B

图7C

图7D

图8A

图8B

图8C

图9

图10A

图10B

图10C

图11A

图11B

图11C

图12A

图12B

图13A

图13B

图13C

图14A

图14B

图14C

图15

图16A

图16B

782

图16C

图17A

图17B

图18

图19A

图19B

图19C

图20

图21

图22A

图22B

图22C

图23A

图23B

图23C

图24

图25A

图25B

图26

150nm

图27A

图27B

图28A

图28B

图29A

图29B

图30A

图30B

图31A

图31B

图32A

图32B