(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5113609号

(P5113609)

(45) 発行日 平成25年1月9日(2013.1.9)

(24) 登録日 平成24年10月19日(2012.10.19)

(51) Int.Cl.

F 1

G09F 9/30 (2006.01)

G09F 9/30 338

G09F 9/00 (2006.01)

G09F 9/00 338

G02F 1/1368 (2006.01)

G09F 9/00 352

GO2F 1/1368

請求項の数 12 (全 16 頁)

(21) 出願番号

特願2008-114683 (P2008-114683)

(22) 出願日

平成20年4月24日 (2008.4.24)

(65) 公開番号

特開2009-265348 (P2009-265348A)

(43) 公開日

平成21年11月12日 (2009.11.12)

審査請求日

平成22年7月6日 (2010.7.6)

(73) 特許権者 506087819

パナソニック液晶ディスプレイ株式会社

兵庫県姫路市飾磨区妻鹿日田町1-6

(74) 代理人 110000154

特許業務法人はるか国際特許事務所

(72) 発明者 上原 淳一

千葉県茂原市早野3732番地 株式会社

IPSアルファテクノロジ内

審査官 井口 猶二

最終頁に続く

(54) 【発明の名称】表示装置及びその製造方法

(57) 【特許請求の範囲】

## 【請求項 1】

基板上に順次積層された走査信号線、絶縁膜、半導体層及び導電体層を備える表示装置であって、

前記導電体層は、前記走査信号線と前記絶縁膜を介して交差する映像信号線と、薄膜トランジスタのドレイン電極及びソース電極と、前記映像信号線と前記ドレイン電極又は前記ソース電極のいずれか一方とを接続する接続線と、を含んで形成され、

前記半導体層は、少なくとも、前記絶縁膜の、前記映像信号線及び前記接続線が形成される領域より広がった領域を覆うように形成され、

前記走査信号線には、開口部が、前記映像信号線の一部と重なるように形成され、

10

前記接続線は、前記開口部上において前記映像信号線と接続され、かつ、前記開口部外に延伸して前記ドレイン電極又は前記ソース電極のいずれか一方と接続され、

前記映像信号線又はノード及び前記接続線には、前記開口部に対応する領域又はその近傍において、切欠部、突起部又は拡幅部が形成されている、

ことを特徴とする表示装置。

## 【請求項 2】

前記映像信号線と前記接続線との接続箇所に前記切欠部が形成されていることを特徴とする請求項1に記載の表示装置。

## 【請求項 3】

前記映像信号線の、前記接続線が接続される側とは反対側に前記突起部が形成されてい

20

ることを特徴とする請求項 1 に記載の表示装置。

【請求項 4】

前記接続線の、前記開口部に対応する領域外であって、かつ、前記開口部の近傍に前記突起部が形成されていることを特徴とする請求項 1 に記載の表示装置。

【請求項 5】

前記映像信号線と前記接続線との接続箇所に前記突起部が形成されていることを特徴とする請求項 1 に記載の表示装置。

【請求項 6】

前記接続線には、前記映像信号線との接続端から所定距離以内の領域において、前記映像信号線に近づくにつれて幅が徐々に広くなる前記拡幅部が形成されていることを特徴とする請求項 1 に記載の表示装置。 10

【請求項 7】

基板上に、走査信号線と、絶縁膜と、半導体層を構成する半導体材料と、導電体層を構成する導電体材料と、が順次積層されてなる積層構造上にパターン形成されたレジスト材をマスクとして前記導電体材料をエッチングすることによって、前記走査信号線と前記絶縁膜を介して交差する映像信号線と、薄膜トランジスタのドレイン電極及びソース電極と、前記映像信号線と前記ドレイン電極又は前記ソース電極のいずれか一方とを接続する接続線と、を含んだ前記導電体層を形成する工程と、

前記導電体層が形成された後、前記導電体層上に残っている前記レジスト材を融解し、該融解された前記レジスト材をマスクとして前記半導体材料をエッチングすることによって、前記半導体層を形成する工程と、 20

を含み、

前記走査信号線には、開口部が、前記映像信号線の一部と重なるように形成され、

前記接続線は、前記開口部上において前記映像信号線と接続され、かつ、前記開口部外に延伸して前記ドレイン電極又は前記ソース電極のいずれか一方と接続され、

前記レジスト材は、前記レジスト材を融解した場合の、前記開口部における前記レジスト材の広がりを制御するための切欠部、突起部又は拡幅部を前記映像信号線又はノード及び前記接続線が備えるようにパターン形成される、

ことを特徴とする表示装置の製造方法。

【請求項 8】

前記映像信号線と前記接続線との接続箇所に前記切欠部が形成されるように、前記レジスト材がパターン形成されることを特徴とする請求項 7 に記載の表示装置の製造方法。 30

【請求項 9】

前記映像信号線の、前記接続線が接続される側とは反対側に前記突起部が形成されるように、前記レジスト材がパターン形成されることを特徴とする請求項 7 に記載の表示装置の製造方法。

【請求項 10】

前記接続線の、前記開口部に対応する領域外であって、かつ、前記開口部の近傍に前記突起部が形成されるように、前記レジスト材がパターン形成されることを特徴とする請求項 7 に記載の表示装置の製造方法。 40

【請求項 11】

前記映像信号線と前記接続線との接続箇所に前記突起部が形成されるように、前記レジスト材がパターン形成されることを特徴とする請求項 7 に記載の表示装置の製造方法。

【請求項 12】

前記接続線の、前記映像信号線との接続端から所定距離以内の領域において、前記映像信号線に近づくにつれて幅が徐々に広くなる前記拡幅部が形成されるように、前記レジスト材がパターン形成されることを特徴とする請求項 7 に記載の表示装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜トランジスタ（TFT：Thin Film Transistor）を用いて画素の表示制御を行う表示装置及びその製造方法に関する。

【背景技術】

【0002】

例えば液晶表示装置などの表示装置の中には、薄膜トランジスタを用いたアクティブマトリクス方式により、各画素の表示制御を行うものがある。このような表示装置では、基板（以下、TFT基板という）上に互いに立体的に交差するように複数の走査信号線と複数の映像信号線とが配置されており、走査信号線と映像信号線の交点のそれぞれが表示装置の画素に対応している。そして、走査信号線の一部は薄膜トランジスタのゲート電極として機能し、映像信号線には薄膜トランジスタのドレイン電極又はソース電極のいずれか一方（以下ではドレイン電極とする）が接続されている。また、映像信号線と接続されない側の電極（以下ではソース電極とする）には、画素電極が接続されている。これにより、表示制御したい画素に対応する走査信号線及び映像信号線の双方に電圧が印加されると、スイッチ素子として機能する薄膜トランジスタを介して、対応する画素電極に電圧が印加され、画素の表示制御を行うことができる。10

【0003】

このような薄膜トランジスタを構成するためには、TFT基板上に、走査信号線、絶縁体層、半導体層、及び導電体層をこの順に形成する必要がある。なお、この場合の導電体層は、映像信号線、ドレイン電極、及びソース電極を含んだ層である。このような所望のパターンの走査信号線や半導体層、導電体層をTFT基板上に形成するためには、いわゆるフォトリソグラフィの手法を用いることができる。この手法によれば、形成対象となる材料膜の表面にレジスト材を塗布し、露光・現像によって形成対象のパターンにレジスト材を加工し、当該加工されたレジスト材をマスクとして形成対象の膜のエッチングを行うことで、走査信号線や半導体層、導電体層を所望のパターンに形成することができる。20

【0004】

さらに、半導体層や導電体層を一度の露光によって形成するために、レジストリフロー方式を採用することができる（例えば特許文献1参照）。この方式では、走査信号線及び絶縁膜が形成されたTFT基板上に半導体材料の膜、導電体材料の膜を順次積層し、前述した手法により導電体材料の膜を所望のパターンの導電体層に形成した後、当該導電体層の上に残っているレジスト材を融解する。これにより、レジスト材は導電体層が形成された領域よりも広がった領域を覆うことになる。そして、この広がったレジスト材をマスクとしてさらに半導体材料の膜をエッチングすることで、半導体層についてはレジスト材の露光を行うことなく、導電体層が形成された領域を含んだ形状に形成することができる。30

【0005】

また、上述したような薄膜トランジスタを備えた表示装置において、走査信号線内の映像信号線と交差する箇所に、開口部が設けられることがある（例えば特許文献2参照）。開口部が設けられることによって、走査信号線はこの開口部が設けられた箇所で二股に分岐し、平面的に見た場合、分岐した二股の走査信号線のそれぞれが映像信号線と交差することになる。こうすれば、万一製造プロセスにおいて走査信号線と映像信号線とが交差箇所で短絡してしまった場合にも、二股に分岐した走査信号線のうち、映像信号線と短絡している方の走査信号線の、映像信号線の両側の箇所を例えばレーザーによって切断することで、走査信号線全体から映像信号線と短絡した箇所だけを切り離すことができる。さらに、映像信号線と薄膜トランジスタのドレイン電極とを接続する接続線が、この開口部上で映像信号線から分岐するように、導電体層を形成することもある。こうすれば、ある画素の黒点化修正を行いたい場合に、当該画素に対応する薄膜トランジスタのドレイン電極と映像信号線とを接続する接続線を、例えばレーザーによって、開口部上で切断することにより、映像信号線と薄膜トランジスタとを切り離すことができる。40

【0006】

【特許文献1】特開2002-90779号公報

【特許文献2】特開平9-258244号公報50

**【発明の開示】****【発明が解決しようとする課題】****【0007】**

上述したように、走査信号線内の映像信号線と交差する箇所に開口部を設け、かつ半導体層及び導電体層をレジストリフロー方式により形成する場合、半導体層が導電体層よりも広がった領域を覆うように形成されることになる。さらに、例えば映像信号線から接続線が分岐される箇所のように、導電体層が鋭角に近いパターンとなるような箇所には、レジスト材が融解される際に生じる表面張力の作用などによって、他の箇所よりもレジスト材が集まりやすく、そのために広い範囲に半導体層が形成されやすい。これにより、半導体層が開口部を塞ぐように形成されてしまうと、上述したような、接続線を開口部で切断する黒点化修正や、開口部によって二股に分岐した走査信号線のうち、映像信号線と短絡している方の走査信号線を切り離す修正が困難になってしまう場合がある。

10

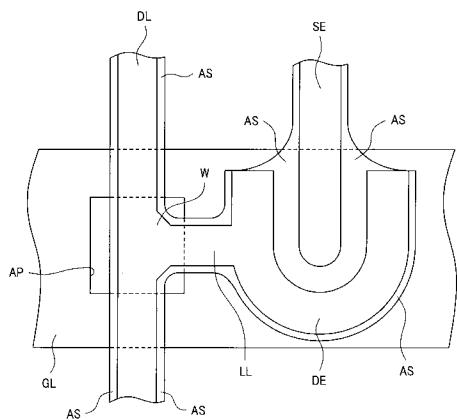

**【0008】**

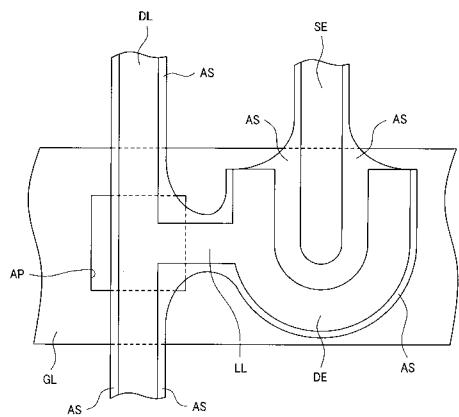

図13は、このように開口部が塞がれてしまった状態の薄膜トランジスタ周辺部分の様子を示す、TFT基板の部分平面図である。図13においては、TFT基板上に形成された、開口部APが設けられた走査信号線GL、半導体層AS、映像信号線DL、薄膜トランジスタTのドレイン電極DE及びソース電極SE、並びにドレイン電極DEと映像信号線DLとを接続する接続線LLの間の位置関係が示されている。例えば、黒点化修正を行う場合（映像信号線DLとドレイン電極DEとを切り離そうとする場合）には、半導体層ASも含めて接続線LLを切断する必要があるため、開口部AP内の半導体層ASが形成されていない箇所を起点及び終点としてレーザーなどによる切断を行う必要がある。この点、図13に示すように、半導体層ASが、接続線LLが配置される側の開口部APの大部分の領域を占めるように広がって形成されてしまうと、半導体層ASも含めて接続線LLを切断するための場所的余裕が開口部AP内に十分に確保できなくなってしまう。同様に、開口部APによって二股に分岐した走査信号線GLのうち、映像信号線DLと短絡している方の走査信号線GLを切り離そうとする場合の場所的余裕も開口部AP内に十分に確保できなくなってしまう。

20

**【0009】**

このような問題を解消するための方法の一つとして、融解されて広がるレジスト材が到達しないような位置まで、走査信号線GLが延伸する方向に沿って開口部APの大きさを広げることが考えられる。しかしながら、このように開口部APを走査信号線GLが延伸する方向に広げると、その分走査信号線GLの電気抵抗が増大してしまう。また、映像信号線DLと薄膜トランジスタTとの間の距離が広くなってしまうため、一画素あたりの面積を小さくする際の制約となり、表示装置全体の高解像度化を阻む要因となってしまう。

30

**【0010】**

本発明は上記課題に鑑みてなされたものであって、その目的は、走査信号線の映像信号線と交差する箇所に開口部を設け、かつ半導体層及び導電体層をレジストリフロー方式によって形成する場合において、例えば、薄膜トランジスタのドレイン電極又はソース電極と映像信号線とを接続する接続線を開口部内で切断する補修、又は、開口部によって二股に分岐した走査信号線のうちの一方を切断する補修を行えるように担保することが可能になる表示装置及びその製造方法を提供することにある。

40

**【課題を解決するための手段】****【0011】**

上記課題を解決するために、本発明に係る表示装置は、基板上に順次積層された走査信号線、絶縁膜、半導体層及び導電体層を備える表示装置であって、前記導電体層は、前記走査信号線と前記絶縁膜を介して交差する映像信号線と、薄膜トランジスタのドレイン電極及びソース電極と、前記映像信号線と前記ドレイン電極又は前記ソース電極のいずれか一方とを接続する接続線と、を含んで形成され、前記半導体層は、少なくとも、前記絶縁膜の、前記映像信号線及び前記接続線が形成される領域より広がった領域を覆うように形成され、前記走査信号線には、開口部が、前記映像信号線の一部と重なるように形成され

50

、前記接続線は、前記開口部上において前記映像信号線と接続され、かつ、前記開口部外に延伸して前記ドレイン電極又は前記ソース電極のいずれか一方と接続され、前記映像信号線又はノン及び前記接続線には、前記開口部に対応する領域又はその近傍において、切欠部、突起部又は拡幅部が形成されていることを特徴とする。

【0012】

また本発明の一態様では、前記映像信号線と前記接続線との接続箇所に前記切欠部が形成されるようにしてもよい。

【0013】

また本発明の一態様では、前記映像信号線の、前記接続線が接続される側とは反対側に前記突起部が形成されるようにしてもよい。 10

【0014】

また本発明の一態様では、前記接続線の、前記開口部に対応する領域外であって、かつ、前記開口部の近傍に前記突起部が形成されるようにしてもよい。

【0015】

また本発明の一態様では、前記映像信号線と前記接続線との接続箇所に前記突起部が形成されるようにしてもよい。

【0016】

また本発明の一態様では、前記接続線には、前記映像信号線との接続端から所定距離以内の領域において、前記映像信号線に近づくにつれて幅が徐々に広くなる前記拡幅部が形成されるようにしてもよい。 20

【0017】

また、本発明に係る表示装置の製造方法は、基板上に、走査信号線と、絶縁膜と、半導体層を構成する半導体材料と、導電体層を構成する導電体材料と、が順次積層されてなる積層構造上にパターン形成されたレジスト材をマスクとして前記導電体材料をエッチングすることによって、前記走査信号線と前記絶縁膜を介して交差する映像信号線と、薄膜トランジスタのドレイン電極及びソース電極と、前記映像信号線と前記ドレイン電極又は前記ソース電極のいずれか一方とを接続する接続線と、を含んだ前記導電体層を形成する工程と、前記導電体層が形成された後、前記導電体層上に残っている前記レジスト材を融解し、該融解された前記レジスト材をマスクとして前記半導体材料をエッチングすることによって、前記半導体層を形成する工程と、を含み、前記走査信号線には、開口部が、前記映像信号線の一部と重なるように形成され、前記接続線は、前記開口部上において前記映像信号線と接続され、かつ、前記開口部外に延伸して前記ドレイン電極又は前記ソース電極のいずれか一方と接続され、前記レジスト材は、前記レジスト材を融解した場合の、前記開口部における前記レジスト材の広がりを制御するための切欠部、突起部又は拡幅部を前記映像信号線又はノン及び前記接続線が備えるようにパターン形成されることとする。 30

【0018】

また本発明の一態様では、前記映像信号線と前記接続線との接続箇所に前記切欠部が形成されるように、前記レジスト材がパターン形成されることとしてもよい。

【0019】

また本発明の一態様では、前記映像信号線の、前記接続線が接続される側とは反対側に前記突起部が形成されるように、前記レジスト材がパターン形成されることとしてもよい。

【0020】

また本発明の一態様では、前記接続線の、前記開口部に対応する領域外であって、かつ、前記開口部の近傍に前記突起部が形成されるように、前記レジスト材がパターン形成されることとしてもよい。

【0021】

また本発明の一態様では、前記映像信号線と前記接続線との接続箇所に前記突起部が形成されるように、前記レジスト材がパターン形成されることとしてもよい。 50

## 【0022】

また本発明の一態様では、前記接続線の、前記映像信号線との接続端から所定距離以内の領域において、前記映像信号線に近づくにつれて幅が徐々に広くなる前記拡幅部が形成されるように、前記レジスト材がパターン形成されるようにしてもよい。

## 【発明の効果】

## 【0023】

本発明によれば、走査信号線の映像信号線と交差する箇所に開口部を設け、かつ半導体層及び導電体層をレジストリフロー方式によって形成する場合において、例えば、薄膜トランジスタのドレイン電極又はソース電極と映像信号線とを接続する接続線を開口部内で切断する補修、又は、開口部によって二股に分岐した走査信号線のうちの一方を切断する補修を行えるように担保することが可能になる。

10

## 【発明を実施するための最良の形態】

## 【0024】

以下、本発明の実施形態の例について図面に基づき詳細に説明する。なお、以下では、いわゆるIPS(In Plane Switching)方式の液晶表示装置に本発明を適用した場合の例について説明する。

## 【0025】

## [第1実施形態]

本発明の実施形態に係る表示装置は液晶表示装置であって、走査信号線、映像信号線、薄膜トランジスタ、画素電極、及びコモン電極が形成されたTFT基板と、当該TFT基板と対向し、カラーフィルタが設けられたフィルタ基板と、両基板に挟まれた領域に封入された液晶材料と、を含んで構成される。TFT基板及びフィルタ基板は、いずれもガラス基板などである。

20

## 【0026】

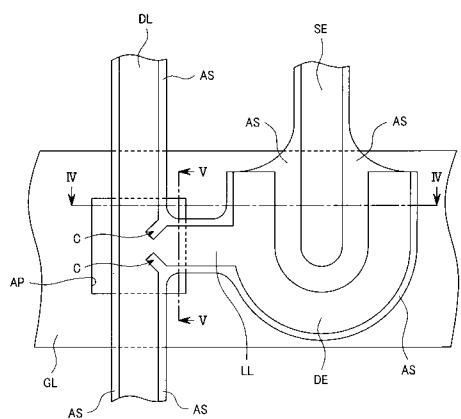

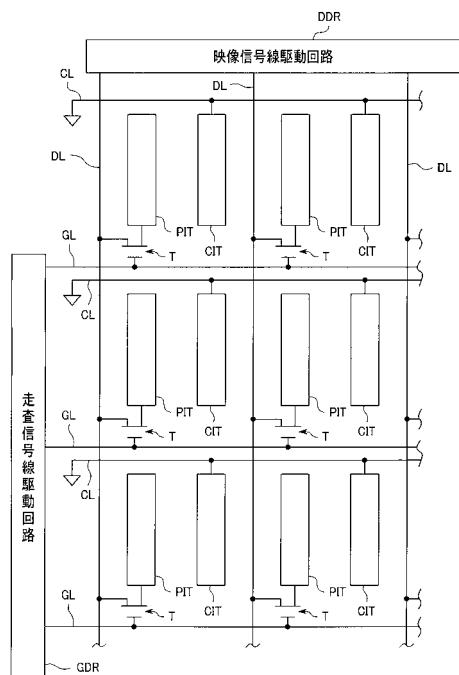

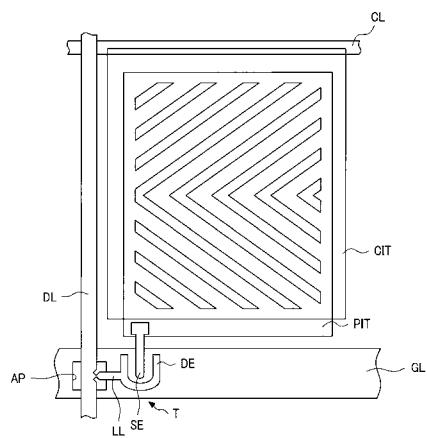

図1は、TFT基板上に実装される走査信号線GL、映像信号線DL、接続線LL、及び薄膜トランジスタTの位置関係を示すTFT基板上の部分平面図である。また、図2は、TFT基板上に実装される走査信号線GL、映像信号線DL、薄膜トランジスタT、画素電極PIT、コモン信号線CL、及びコモン電極CITの概略の回路構成を示す回路図である。さらに、図3は、TFT基板の1つの画素領域の平面図である。

## 【0027】

30

これらの図に示されるように、TFT基板上には、互いに平行な複数本の走査信号線GLが配置されている。また、複数本の映像信号線DLが、互いに平行に、かつ平面的に見た場合に複数本の走査信号線GLのそれぞれと略直交するように交差して配置されている。これらの走査信号線GLと映像信号線DLとによって、碁盤状に並ぶ画素のそれぞれが区画されており、走査信号線GLと映像信号線DLとが交差する箇所のそれぞれが、本実施形態に係る表示装置の画素に対応する。

## 【0028】

また、走査信号線GL及び映像信号線DLによって区画される複数の画素領域のそれには、当該画素の表示制御を行うための薄膜トランジスタTが形成されている。薄膜トランジスタTのゲート電極は走査信号線GLの一部によって構成されており、ドレイン電極DEは接続線LLを介して映像信号線DLと接続され、ソース電極SEは画素電極PITと接続されている。一方、各画素電極PITと対応するコモン電極CITは、それぞれ走査信号線GLと平行に配置された複数本のコモン信号線CLのいずれかと接続される。なお、本実施形態ではドレイン電極DEがU字型形状を有しているが、ドレイン電極DEの形状は他の形状であってもよい。

40

## 【0029】

本実施形態に係る表示装置では、走査信号線駆動回路GDRによって、所定タイミングごとに走査信号線GLに選択的に電圧が印加され、映像信号線駆動回路DDRによって、所定タイミングごとに映像信号線DLに選択的に電圧が印加される。こうして、表示制御の対象となる画素電極に対応する薄膜トランジスタTのオン／オフが制御され、当該薄膜

50

トランジスタTを介して表示対象の画素の画素電極PITに電圧が印加される。これにより、本実施形態に係る表示装置は、画素電極PITとコモン電極CITとの間に生じる電界によって液晶分子を制御して、画素ごとの表示制御を行う。ここで、画素電極PIT及びコモン電極CITは、いずれも透明電極膜であって、平面的に見た場合に互いにその少なくとも一部が重なるように配置されている。

#### 【0030】

また、図1に示すように、走査信号線GL内の、走査信号線GLと映像信号線DLとが交差する箇所には、その一部が映像信号線DLと重なるように、開口部APが設けられている。そして、前述した接続線LLは、この開口部AP上で映像信号線DLから分岐して、開口部APの外まで（すなわち走査信号線GL上まで）伸びてからドレイン電極DEと接続されている。10

#### 【0031】

さらに、本実施形態に係る表示装置では、映像信号線DLから接続線LLが分岐する箇所に切欠部Cが形成されている。具体的には、映像信号線DL及び接続線LLによって形成される角から、映像信号線DL及び接続線LLの中心線の交点への方向と略等しい方向に向かって切り欠かれてなる切欠部Cが形成されている。この切欠部Cの役割については後述する。

#### 【0032】

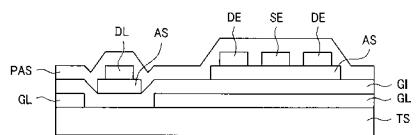

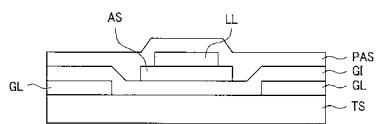

図4は、図1のIV-IV線におけるTFT基板の断面の様子を示す部分断面図であり、図5は、図1のV-V線におけるTFT基板の断面の様子を示す部分断面図である。図4及び図5に示すように、TFT基板TS上には、走査信号線GL、絶縁膜GI、半導体層AS、導電体層、及び保護膜PASが順次積層されている。ここで、導電体層は、映像信号線DL、接続線LL、ドレイン電極DE、及びソース電極SEを含んだ層である。なお、図4及び図5には示されていないが、コモン電極CIT及びコモン信号線CLが存在する領域では、TFT基板TS上にコモン電極CIT及びコモン信号線CLも形成される。また、画素電極PITが存在する領域では、保護膜PASの上の層にさらに画素電極PITがソース電極SEと接続するように形成される。20

#### 【0033】

絶縁膜GIは、例えば窒化シリコンなどの材料を含んだ層であって、TFT基板TS上に形成された走査信号線GLを覆うように形成されている。半導体層ASは、例えばアモルファスシリコンなどの材料を含んだ層であって、図1に示されるように、平面的に観た場合に、絶縁膜GIの、導電体層が形成される領域より広がった領域を覆うように形成されている。すなわち、図4に示されるように、絶縁膜GIの、映像信号線DL、ドレイン電極DE、及びソース電極SEが形成される領域より広がった領域を覆うように半導体層ASは形成されている。また、図5に示されるように、絶縁膜GIの、接続線LLが形成される領域より広がった領域を覆うように半導体層ASは形成されている。30

#### 【0034】

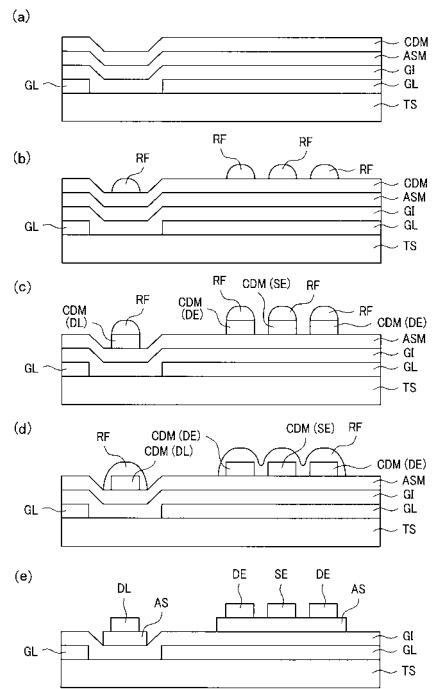

ここで、以上説明したような走査信号線GL、絶縁膜GI、半導体層AS、導電体層、及び保護膜PASを含んだ層が順次積層されたTFT基板TSを製造する方法について説明する。図6(a)～(e)はこの製造方法について説明するための図であり、図4と同じ場所のTFT基板TSの断面の様子を示す部分断面図である。40

#### 【0035】

まず、フォトリソグラフィによって、走査信号線GLをTFT基板TSの基板面上に形成する。具体的には、TFT基板TS上に走査信号線GLを構成する材料の膜を形成し、その上にレジスト材の膜（レジスト膜）を積層して形成する。そして、露光及び現像によってレジスト膜を走査信号線GLの形状に対応するパターンに加工して、この加工されたレジスト膜をマスクとしてエッチングを行うことによって、走査信号線GLを形成する。その後、残っているレジスト膜を除去する。

#### 【0036】

次に、その状態のTFT基板TSの基板面上に、絶縁膜GI、半導体層ASを構成する50

半導体材料ASMの膜、及び導電体層を構成する導電体材料CDMの膜を、この順に順次積層して形成する。図6(a)は、この段階におけるTFT基板TSの断面の様子を示している。

#### 【0037】

さらに、図6(a)に示す状態のTFT基板TSにおいて、導電体材料CDMの膜の上にレジスト膜を形成する。そして、フォトリソグラフィによって、導電体層の形成を行う。具体的には、形成しようとする導電体層の形状に対応するマスクパターンを用いてレジスト膜の露光を行い、さらに現像処理を行うことによって、レジスト膜を導電体層の形状に対応するパターンに加工する。図6(b)は、この段階におけるTFT基板TSの断面の様子を示している。なお、本実施形態では、レジスト膜RFを露光する際のマスクパターンは、映像信号線DLから接続線LLが分岐する箇所に前述の切欠部Cが形成されるように設定される。10

#### 【0038】

次に、図6(b)に示す状態のTFT基板TSにおいて、上記の加工されたレジスト膜RFをマスクとして導電体材料CDMの膜をエッチングすることによって、映像信号線DL、接続線LL、ドレイン電極DE、及びソース電極SEを含んだ導電体層を形成する。図6(c)は、この段階におけるTFT基板TSの断面の様子を示している。

#### 【0039】

続いて、導電体層が形成されて図6(c)に示す状態になった後に、導電体層上に残っているレジスト膜RFを加熱融解する。これにより、TFT基板TSを平面的に見た場合に、レジスト膜RFは、導電体層が形成された領域よりも広がった領域を覆うように広がった状態になる。図6(d)は、このレジスト膜RFが融解された状態のTFT基板TSの断面の様子を示している。20

#### 【0040】

この状態において、融解されたレジスト膜RFをマスクとして、半導体材料ASMの膜に対するエッチングを行う。その後、残っているレジスト膜RFを除去する。このようにすることによって、絶縁膜GIの、導電体層が形成される領域より広がった領域を覆うように、半導体層ASが形成される。図6(e)は、この段階におけるTFT基板TSの断面の様子を示している。なお、この状態において保護膜PASがさらに形成され、TFT基板TSは図4に示す状態になる。30

#### 【0041】

ここで、レジスト膜RFの広がりは融解によって生じるため、レジスト膜RFに生じる表面張力の影響などにより、半導体層ASの導電体層からはみ出す領域の幅は均一にはならない。特に、融解されたレジスト膜RFは、映像信号線DLや接続線LLなどによって形成される角に集まりやすく、例えば、映像信号線DLから接続線LLが分岐する箇所などに集まりやすい。このため、図13に示されるように、映像信号線DLから接続線LLが分岐する箇所などでは、半導体層ASの広がりが大きくなりやすい。

#### 【0042】

この点、本実施形態では、映像信号線DLから接続線LLが分岐する箇所に切欠部Cが形成されている。下記に説明するように、この切欠部Cは、半導体層ASを形成する工程において導電体層上に残っているレジスト膜RFを融解した場合の、開口部AP内におけるレジスト膜RFの広がりを制御する役割を果たす。40

#### 【0043】

すなわち、本実施形態では、導電体層上に残っているレジスト膜RFを融解した場合、融解されたレジスト膜RFの一部が切欠部Cに流れ込むようになる。このため、映像信号線DLから接続線LLが分岐する箇所付近に本来は溜るはずであったレジスト膜RFの一部が切欠部C内に流れ込むようになり、映像信号線DLから接続線LLが分岐する箇所付近におけるレジスト膜RFの広がりが軽減される。その結果、半導体層ASが、接続線LLが配置される側の開口部APの大部分の領域を占めるように広がって形成されないようになる。本実施形態によれば、黒点化修正を行おうとする場合(接続線LLを切断し50

とする場合)の場所的余裕が開口部 A P 内に確保されるようになる。また、開口部 A P によって二股に分岐した走査信号線 G L のうち、映像信号線 D L と短絡している方の走査信号線 G L を切り離そうとする場合の場所的余裕も開口部 A P 内に確保されるようになる。

#### 【 0 0 4 4 】

ところで、図 1 に示す例では、切欠部 C が映像信号線 D L 及び接続線 L L の両方にまたがるようにして形成されている。しかしながら、切欠部 C は映像信号線 D L 又は接続線 L L の一方に形成されるようにしてもよい。この場合、映像信号線 D L から接続線 L L が分岐する箇所付近に本来は溜るはずであったレジスト膜 R F の一部が流れ込むような位置に、切欠部 C を形成するようにすればよい。例えば、開口部 A P に対応する領域内であって、かつ、映像信号線 D L から接続線 L L が分岐する箇所の近傍に切欠部 C を形成するよう 10 にすればよい。

#### 【 0 0 4 5 】

##### [ 第 2 実施形態 ]

第 2 実施形態に係る表示装置も第 1 実施形態と同様の構成(図 2 ~ 図 5 参照)を有し、第 2 実施形態における TFT 基板 TS の製造方法も第 1 実施形態と同様の製造方法(図 6 参照)であるため、ここでは説明を省略する。

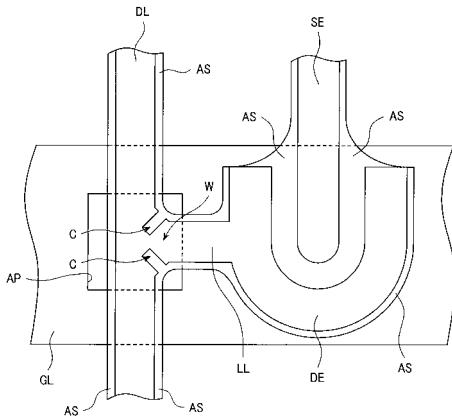

#### 【 0 0 4 6 】

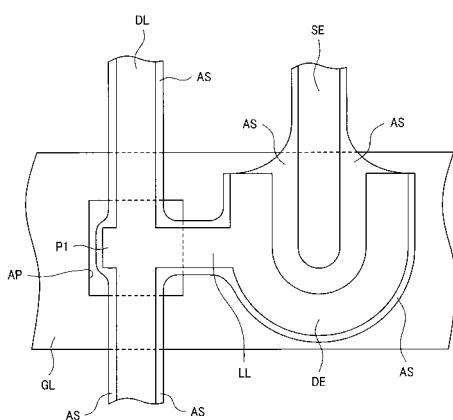

本実施形態に係る表示装置は、半導体層 A S を形成する工程において導電体層上に残っているレジスト膜 R F を融解した場合の、開口部 A P 内におけるレジスト膜 R F の広がりを制御するための拡幅部が、映像信号線 D L 又は / 及び接続線 L L に設けられる点で、第 1 実施形態とは相違する。図 7 は、本実施形態に係る表示装置の TFT 基板 TS の部分平面図であり、第 1 実施形態における図 1 に対応する図である。 20

#### 【 0 0 4 7 】

図 7 に示すように、本実施形態に係る表示装置では、接続線 L L の、映像信号線 D L との接続端から所定距離以内の領域において、映像信号線 D L に近づくにつれて幅が徐々に広くなるような拡幅部 W が形成されている。この拡幅部 W が形成されることによって、映像信号線 D L と接続線 L L とが形成する角が比較的緩やかになっている。なお、この拡幅部 W は、接続線 L L が配置される側の開口部 A P の全域が覆われてしまうことがないように、すなわち、接続線 L L が配置される側の開口部 A P の一部のみが覆われるよう 30 形成される。

#### 【 0 0 4 8 】

なお、本実施形態では、導電体層を形成する工程(図 6 ( b ) 参照)において、導電体材料 C DM 上に積層されたレジスト膜 R F を露光する際のマスクパターンは、前述の拡幅部 W が接続線 L L に形成されるように設定される。

#### 【 0 0 4 9 】

半導体層 A S を形成する工程において導電体層上に残っているレジスト膜 R F を融解した場合、映像信号線 D L と接続線 L L とが形成する角が鋭い程、映像信号線 D L から接続線 L L が分岐する箇所に、融解されたレジスト膜 R F が集まりやすくなる。この点、本実施形態では、拡幅部 W が形成されることによって、映像信号線 D L と接続線 L L と形成する角が比較的緩やかになるため、映像信号線 D L から接続線 L L が分岐する箇所に、融解されたレジスト膜 R F が集まり難くなる。このため、映像信号線 D L から接続線 L L が分岐する箇所におけるレジスト膜 R F の広がりが軽減され、半導体層 A S が、接続線 L L が配置される側の開口部 A P の大部分の領域を占めるように広がって形成されてしまわないようになる。本実施形態によっても、黒点化修正を行おうとする場合の場所的余裕が開口部 A P 内に確保されるようになる。また、開口部 A P によって二股に分岐した走査信号線 G L のうち、映像信号線 D L と短絡している方の走査信号線 G L を切り離そうとする場合の場所的余裕も開口部 A P 内に確保されるようになる。 40

#### 【 0 0 5 0 】

なお、図 7 に示す例では、映像信号線 D L に拡幅部 W が形成されているともいうことができる。すなわち、接続線 L L の分岐箇所に近づくにつれて幅が接続線 L L の延伸方向に 50

向かって徐々に広くなるような拡幅部Wが映像信号線DLに形成されているともいうことができる。また、拡幅部Wは映像信号線DLと接続線LLとにまたがって形成されているともいいうことができる。

#### 【0051】

##### [第3実施形態]

第3実施形態に係る表示装置も第1実施形態と同様の構成(図2～図5参照)を有し、第3実施形態におけるTFT基板TSの製造方法も第1実施形態と同様の製造方法(図6参照)であるため、ここでは説明を省略する。

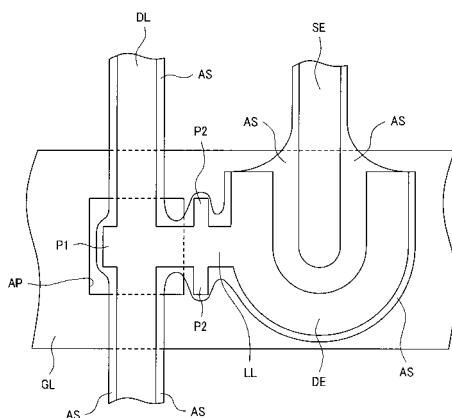

#### 【0052】

本実施形態に係る表示装置は、半導体層ASを形成する工程において導電体層上に残っているレジスト膜RFを融解した場合の、開口部AP内におけるレジスト膜RFの広がりを制御するための突起部が映像信号線DLに設けられる点で、第1実施形態とは相違する。図8は、本実施形態に係る表示装置のTFT基板TSの部分平面図であり、第1実施形態における図1に対応する図である。

10

#### 【0053】

図8に示すように、本実施形態に係る表示装置では、映像信号線DLの、接続線LLが接続される側とは反対側に突起部P1が形成されている。なお、本実施形態では、導電体層を形成する工程(図6(b)参照)において、導電体材料CDM上に積層されたレジスト膜RFを露光する際のマスクパターンは、前述の突起部P1が映像信号線DLに形成されるように設定される。

20

#### 【0054】

本実施形態では、半導体層ASを形成する工程において導電体層上に残っているレジスト膜RFを融解した場合、融解されたレジスト膜RFが、突起部P1付近にも集まりやすくなる。このため、開口部APの接続線LLが配置される側の領域に本来流れ込むはずであったレジスト膜RFの一部が、開口部APの接続線LLが配置されない側の領域にも流れ込むようになる。その結果、開口部APの接続線LLが配置される側の領域へのレジスト膜RFの広がりが軽減されるようになり、半導体層ASが、接続線LLが配置される側の開口部APの大部分の領域を占めるように広がって形成されてしまわないようになる。本実施形態によても、黒点化修正を行おうとする場合の場所的余裕が開口部AP内に確保されるようになる。また、開口部APによって二股に分岐した走査信号線GLのうち、映像信号線DLと短絡している方の走査信号線GLを切り離そうとする場合の場所的余裕も開口部AP内に確保されるようになる。

30

#### 【0055】

なお、図8に示す例では、突起部P1が、接続線LLと映像信号線DLに対して線対称となるような位置に設けられているが、突起部P1の位置は、接続線LLと映像信号線DLに対して線対称となるような位置に限られない。突起部P1は、開口部APの接続線LLが配置される側の領域に本来流れ込むはずであったレジスト膜RFの一部が集まってくるような位置に形成するようにすればよい。例えば、映像信号線DLの、接続線LLが接続される側とは反対側であって、かつ、開口部APに対応する領域内又はその近傍の位置に、突起部P1を形成するようにすればよい。また、図8に示す例では、突起部P1の突起方向が、接続線LLの延伸方向と略正反対の方向になっているが、必ずしも、突起部P1の突起方向は、接続線LLの延伸方向と略正反対の方向に限られない。さらに、図8に示す例では、平面的に見た場合の突起部P1の幅が接続線LLの幅と略等しくなっているが、突起部P1の幅は接続線LLの幅と略等しくなくてもよい。

40

#### 【0056】

##### [第4実施形態]

第4実施形態に係る表示装置も第1実施形態と同様の構成(図2～図5参照)を有し、第4実施形態におけるTFT基板TSの製造方法も第1実施形態と同様の製造方法(図6参照)であるため、ここでは説明を省略する。

#### 【0057】

50

本実施形態に係る表示装置は、半導体層 A S を形成する工程において導電体層上に残っているレジスト膜 R F を融解した場合の、開口部 A P 内におけるレジスト膜 R F の広がりを制御するための突起部が接続線 L L に設けられる点で、第 1 実施形態とは相違する。図 9 は、本実施形態に係る表示装置の TFT 基板 T S の部分平面図であり、第 1 実施形態における図 1 に対応する図である。

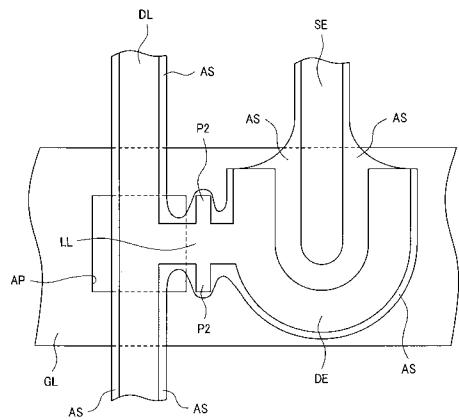

#### 【 0 0 5 8 】

図 9 に示すように、本実施形態に係る表示装置では、接続線 L L の、開口部 A P に対する領域より外側であって、かつ、開口部 A P の近傍の位置に突起部 P 2 が形成されている。なお、本実施形態では、導電体層を形成する工程（図 6 ( b ) 参照）において、導電体材料 C DM 上に積層されたレジスト膜 R F を露光する際のマスクパターンは、前述の突起部 P 2 が接続線 L L に形成されるように設定される。10

#### 【 0 0 5 9 】

半導体層 A S を形成する工程において導電体層上に残っているレジスト膜 R F を融解した場合、融解されたレジスト膜 R F は、映像信号線 D L や接続線 L L などによって形成される角に集まりやすい。この点、本実施形態では、前述の突起部 P 2 が接続線 L L に形成されているため、融解されたレジスト膜 R F は突起部 P 2 の付近にも集まりやすくなる。その結果、開口部 A P の接続線 L L が配置される側の領域内に本来溜るはずであったレジスト膜 R F の一部が、開口部 A P 外に溜るようになる。このため、開口部 A P の接続線 L L が配置される側の領域におけるレジスト膜 R F の広がりが軽減されるようになり、半導体層 A S が、接続線 L L が配置される側の開口部 A P の大部分の領域を占めるように広がって形成されてしまわないようになる。本実施形態によっても、黒点化修正を行おうとする場合の場所的余裕が開口部 A P 内に確保されるようになる。また、開口部 A P によって二股に分岐した走査信号線 G L のうち、映像信号線 D L と短絡している方の走査信号線 G L を切り離そうとする場合の場所的余裕が開口部 A P 内に確保されるようになる。20

#### 【 0 0 6 0 】

なお、図 9 に示す例では、突起部 P 2 の突起方向が、接続線 L L の延伸方向と略直交する方向になっているが、必ずしも、突起部 P 2 の突起方向は、接続線 L L の延伸方向と略直交する方向に限られない。

#### 【 0 0 6 1 】

##### [ 第 5 実施形態 ]

第 5 実施形態に係る表示装置も第 1 実施形態と同様の構成（図 2 ~ 図 5 参照）を有し、第 5 実施形態における TFT 基板 T S の製造方法も第 1 実施形態と同様の製造方法（図 6 参照）であるため、ここでは説明を省略する。30

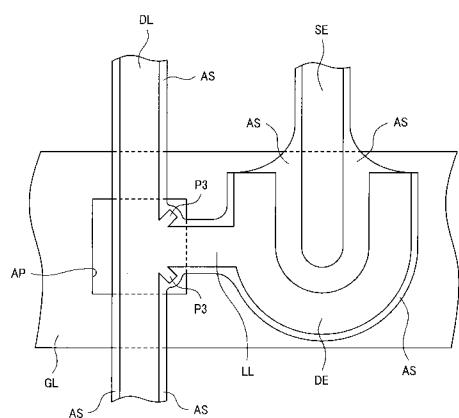

#### 【 0 0 6 2 】

本実施形態に係る表示装置は、半導体層 A S を形成する工程において導電体層上に残っているレジスト膜 R F を融解した場合の、開口部 A P 内におけるレジスト膜 R F の広がりを制御するための突起部が、映像信号線 D L から接続線 L L が分岐する箇所に形成される点で、第 1 実施形態とは相違する。図 10 は、本実施形態に係る表示装置の TFT 基板 T S の部分平面図であり、第 1 実施形態における図 1 に対応している。40

#### 【 0 0 6 3 】

図 10 に示すように、本実施形態に係る表示装置では、映像信号線 D L から接続線 L L が分岐する箇所に突起部 P 3 が形成されている。なお、本実施形態では、導電体層を形成する工程（図 6 ( b ) 参照）において、導電体材料 C DM 上に積層されたレジスト膜 R F を露光する際のマスクパターンは、映像信号線 D L から接続線 L L が分岐する箇所に前述の突起部 P 3 が形成されるように設定される。50

#### 【 0 0 6 4 】

半導体層 A S を形成する工程において導電体層上に残っているレジスト膜 R F を融解した場合、融解されたレジスト膜 R F は、映像信号線 D L や接続線 L L などによって形成される角に集まりやすい。この点、本実施形態では、映像信号線 D L から接続線 L L が分岐する箇所に突起部 P 3 が設けられているため、融解されたレジスト膜 R F は、映像信号線

D L から接続線 L L が分岐する箇所に、より集まりやすくなる。すなわち、開口部 A P の接続線 L L が配置される側の領域に広がるはずであったレジスト膜 R F が、映像信号線 D L から接続線 L L が分岐する箇所に、より集中するようになる。その結果、開口部 A P の接続線 L L が配置される側の領域におけるレジスト膜 R F の広がりが軽減され、半導体層 A S が、接続線 L L が配置される側の開口部 A P の大部分の領域を占めるように広がって形成されてしまわないようになる。本実施形態によっても、黒点化修正を行おうとする場合の場所的余裕が開口部 A P 内に確保されるようになる。また、開口部 A P によって二股に分岐した走査信号線 G L のうち、映像信号線 D L と短絡している方の走査信号線 G L を切り離そうとする場合の場所的余裕も開口部 A P 内に確保されるようになる。

## 【0065】

10

なお、本発明は以上に説明した実施の形態に限定されるものではない。

## 【0066】

例えば、第1～5実施形態のうちの複数を組み合わせるようにしてもよい。図11は、第1実施形態と第2実施形態とを組み合わせた例を示しており、図12は、第3実施形態と第4実施形態とを組み合わせた例を示している。このようにすれば、導電体層上に残っているレジスト膜 R F を融解した場合の、開口部 A P の接続線 L L が配置される側の領域におけるレジスト膜 R F の広がりをさらに軽減できるようになる。

## 【0067】

また例えば、以上では、いわゆるIPS方式の液晶表示装置に本発明を適用した場合の例について説明した。すなわち、TFT基板 TS 上に形成された画素電極 P I T 及びコモン電極 C I T の間に生じる横方向の電界によって、液晶分子の制御を行う方式を採用した表示装置に本発明を適用した場合の例について説明した。しかしながら、本発明は、他の方式を採用する表示装置にも適用することが可能である。例えば、本発明は、いわゆるVA (Vertical Alignment) 方式の液晶表示装置にも適用することが可能である。すなわち、TFT基板 TS の画素電極 P I T と、フィルタ基板の対抗電極と、の間に生じる縦方向の電界によって、液晶分子の制御を行う方式を採用した液晶表示装置にも本発明は適用することができる。また例えば、本発明は、いわゆるTN (Twisted Nematic) 方式の液晶表示装置にも適用することが可能である。さらに、例えば、本発明は液晶表示装置以外の表示装置にも適用することができる。例えば有機EL表示装置等の他の表示装置においても、画素ごとに薄膜トランジスタが形成される場合には、前述した課題と同様の課題が生じ得るからである。

20

## 【図面の簡単な説明】

## 【0068】

30

【図1】本発明の第1実施形態に係る表示装置のTFT基板の部分平面図である。

【図2】本発明の第1実施形態に係る表示装置のTFT基板に実装される回路構成を示す回路図である。

【図3】TFT基板の画素領域を示す平面図である。

【図4】TFT基板の部分断面図である。

【図5】TFT基板の部分断面図である。

【図6】TFT基板の製造方法について説明するための図である。

40

【図7】本発明の第2実施形態に係る表示装置のTFT基板の部分平面図である。

【図8】本発明の第3実施形態に係る表示装置のTFT基板の部分平面図である。

【図9】本発明の第4実施形態に係る表示装置のTFT基板の部分平面図である。

【図10】本発明の第5実施形態に係る表示装置のTFT基板の部分平面図である。

【図11】本発明の他の実施形態に係る表示装置のTFT基板の部分平面図である。

【図12】本発明の他の実施形態に係る表示装置のTFT基板の部分平面図である。

【図13】従来の表示装置のTFT基板の部分平面図である。

## 【符号の説明】

## 【0069】

A P 開口部、A S 半導体層、A S M 半導体材料、C 切欠部、C D M 導電体材

50

料、C I T コモン電極、C L コモン信号線、D D R 映像信号線駆動回路、D E ドレイン電極、D L 映像信号線、G D R 走査信号線駆動回路、G I 絶縁膜、G L 走査信号線、L L 接続線、P 1 , P 2 , P 3 突起部、P A S 保護膜、P I T 画素電極、R F レジスト膜、S E ソース電極、T 薄膜トランジスタ、T S T F T 基板、W 拡幅部。

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

---

フロントページの続き

(56)参考文献 特開平08-146462(JP,A)

特開2002-261078(JP,A)

国際公開第2006/117909(WO,A1)

特開平05-232503(JP,A)

特開平11-119253(JP,A)

特開2002-190605(JP,A)

特開平10-221704(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 09 F 9 / 00 - 9 / 46

G 02 F 1 / 1368