(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6462410号

(P6462410)

(45) 発行日 平成31年1月30日(2019.1.30)

(24) 登録日 平成31年1月11日(2019.1.11)

(51) Int.Cl.

F 1

G 11 C 29/50 (2006.01)

G 11 C 29/06 (2006.01)G 11 C 29/50 150

G 11 C 29/06

請求項の数 13 (全 22 頁)

(21) 出願番号 特願2015-36297 (P2015-36297)

(22) 出願日 平成27年2月26日 (2015.2.26)

(65) 公開番号 特開2016-157504 (P2016-157504A)

(43) 公開日 平成28年9月1日 (2016.9.1)

審査請求日 平成29年11月27日 (2017.11.27)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

東京都江東区豊洲三丁目2番24号

(74) 代理人 100103894

弁理士 家入 健

(74) 代理人 100089071

弁理士 玉村 静世

(72) 発明者 宮西 篤史

神奈川県川崎市中原区下沼部1753番地

ルネサスエレクトロニクス株式会社内

(72) 発明者 石井 雄一郎

神奈川県川崎市中原区下沼部1753番地

ルネサスエレクトロニクス株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置、テストプログラムおよびテスト方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ワード線と、ビット線対と、前記ワード線と前記ビット線対とが交差する箇所に配置されたメモリセルと、前記メモリセルにデータを書込むために前記ビット線対を所定の電圧で駆動する駆動回路とを備え、

前記メモリセルには、第1電位と前記第1電位よりも高い第2電位とが電源として供給され、

第1動作モードと第2動作モードとを有し、

前記第1動作モードにおいて、前記駆動回路は、前記ビット線対の一方のビット線を前記第1電位側に駆動し、他方のビット線を前記第2電位側に駆動し、

10

前記第2動作モードにおいて、前記駆動回路は、前記ビット線対の一方のビット線を前記第1電位よりも高く前記第2電位よりも低い第3電位に駆動し、他方のビット線を前記第2電位側に駆動し、

前記駆動回路は、

前記第2動作モードにおいて、第2電源線から前記ビット線対のそれぞれのビット線への電流経路を形成する、第1及び第2NチャネルMOSFETと、

前記第1及び第2動作モードにおいて、第1電源線から前記ビット線対の一方のビット線への電流経路を形成する、第3及び第4NチャネルMOSFETと、

を備え、

第1NチャネルMOSFETと第3NチャネルMOSFET、及び、第2NチャネルM

20

MOSFETと第4NチャネルMOSFETのチャネル幅及び／又はチャネル長は異なる、半導体装置。

**【請求項2】**

請求項1において、

前記第1及び第2NチャネルMOSFETはテストモード信号で制御され、

前記第2動作モードにおいて、前記テストモード信号は、前記データの書き込みを指示するライトイネーブル信号に応じてハイレベルとなるか、又は、ハイレベルに固定される、

半導体装置。

**【請求項3】**

10

請求項1において、前記メモリセルは、前記第1及び第2電源線に接続され、第1及び第2記憶ノードを有し、第1及び第2PチャネルMOSFETと第5乃至第8NチャネルMOSFETとを備え、

前記第1PチャネルMOSFETのドレイン電極と、前記第5NチャネルMOSFETのドレイン電極と、前記第7NチャネルMOSFETのソース電極と、前記第2PチャネルMOSFETのゲート電極と、前記第6NチャネルMOSFETのゲート電極とは、前記第1記憶ノードに接続され、

前記第2PチャネルMOSFETのドレイン電極と、前記第6NチャネルMOSFETのドレイン電極と、前記第8NチャネルMOSFETのソース電極と、前記第1PチャネルMOSFETのゲート電極と、前記第5NチャネルMOSFETのゲート電極とは、前記第2記憶ノードに接続され、

前記第1PチャネルMOSFETのソース電極と、前記第2PチャネルMOSFETのソース電極とは前記第2電源線に接続され、

前記第5NチャネルMOSFETのソース電極と、前記第6NチャネルMOSFETのソース電極とは前記第1電源線に接続され、

前記第7NチャネルMOSFETのゲート電極と、前記第8NチャネルMOSFETのゲート電極とは前記ワード線に接続され、

前記第7NチャネルMOSFETのドレイン電極は、前記ビット線対の一方のビット線に接続され、

前記第8NチャネルMOSFETのドレイン電極は、前記ビット線対の他方のビット線に接続され、

前記第1電源線には前記第1電位が、前記第2電源線には前記第2電位がそれぞれ供給される、

半導体装置。

**【請求項4】**

30

請求項3において、前記ワード線を第1ワード線とし、前記ビット線対を第1ビット線対とし、第2ワード線と第2ビット線対をさらに備え、

前記メモリセルは、第9及び第10NチャネルMOSFETをさらに備え、

前記第7NチャネルMOSFETのゲート電極と、前記第8NチャネルMOSFETのゲート電極とは前記第1ワード線に接続され、

40

前記第7NチャネルMOSFETのドレイン電極は、前記第1ビット線対の一方のビット線に接続され、

前記第8NチャネルMOSFETのドレイン電極は、前記第1ビット線対の他方のビット線に接続され、

前記第9NチャネルMOSFETのゲート電極と、前記第10NチャネルMOSFETのゲート電極とは前記第2ワード線に接続され、

前記第9NチャネルMOSFETのドレイン電極は、前記第2ビット線対の一方のビット線に接続され、

前記第10NチャネルMOSFETのドレイン電極は、前記第2ビット線対の他方のビット線に接続され、

前記第10NチャネルMOSFETのドレイン電極は、前記第2ビット線対の他方のビット線に接続され、

50

前記第1動作モードにおいて、前記駆動回路は、前記第1ビット線対と前記第2ビット線対のうちの少なくとも1組のビット線対について、一方のビット線を前記第1電位側に駆動し、他方のビット線を前記第2電位側に駆動し、

前記第2動作モードにおいて、前記駆動回路は、前記第1ビット線対と前記第2ビット線対のうちの少なくとも1組のビット線対について、一方のビット線を前記第1電位よりも高く前記第2電位よりも低い第3電位に駆動し、他方のビット線を前記第2電位側に駆動する、

半導体装置。

**【請求項5】**

請求項1において、前記ワード線と前記ビット線対と前記メモリセルと前記駆動回路とを含むメモリ回路と、前記第1動作モードにおいて前記駆動回路によって前記メモリセルに書込むデータを供給するバスと、前記第2動作モードにおいて前記駆動回路によって前記メモリセルに書込むデータを供給するテスト回路とを、单一の半導体基板上に備える、

半導体装置。

**【請求項6】**

ワード線と、ビット線対と、前記ワード線と前記ビット線対とに接続されるメモリセルと、前記ビット線対を駆動する駆動回路とを備えるS R A Mのテストを含む、テストプログラムであって、

前記駆動回路は、

第2電源線から前記ビット線対のそれぞれのビット線への電流経路を形成する、第1及び第2NチャネルM O S F E Tと、

20

第1電源線から前記ビット線対の一方のビット線への電流経路を形成する、第3及び第4NチャネルM O S F E Tと、

を備え、

第1NチャネルM O S F E Tと第3NチャネルM O S F E T、及び、第2NチャネルM O S F E Tと第4NチャネルM O S F E Tのチャネル幅及び／又はチャネル長は異なり、

前記S R A Mのテストは、

前記ワード線に選択信号をアサートすることによって選択されたメモリセルについて、前記ビット線対の一方のビット線をハイレベル電位、前記第3及び第4NチャネルM O S F E Tの何れか一方をオンとすることによって、他方のビット線をロウレベル電位にそれぞれ駆動して、当該メモリセルにデータを書込む第1ステップと、

30

前記ワード線に選択信号をアサートすることによって選択されたメモリセルについて、前記ビット線対の一方のビット線を前記ハイレベル電位、前記第1及び第2NチャネルM O S F E Tをオンとし、前記第3及び第4NチャネルM O S F E Tのいずれか一方をオンとすることによって、他方のビット線を前記ロウレベル電位よりも高く前記ハイレベル電位よりも低い電位にそれぞれ駆動して、当該メモリセルにデータを書込む第2ステップとを含む、

テストプログラム。

**【請求項7】**

請求項6において、

前記S R A Mのテストは、前記第2ステップの直後に、前記第2ステップでデータが書込まれたメモリセルから、書込まれたデータを読み出す第3ステップをさらに含む、

40

テストプログラム。

**【請求項8】**

請求項6において、

前記第2ステップは、前記ワード線に選択信号をアサートして当該メモリセルへデータを書込んだ後、当該ワード線のアサート状態を維持したまま、前記ビット線対をプリチャージする期間をさらに含む、

テストプログラム。

**【請求項9】**

10

20

30

40

50

請求項 6において、前記ロウレベル電位よりも高く前記ハイレベル電位よりも低い前記電位は、前記S R A Mの動作範囲における最低動作温度に基づいて規定され、前記第2ステップは、前記S R A Mを前記最低動作温度以上の温度で実行される、

テストプログラム。

【請求項 1 0】

ワード線と、ビット線対と、前記ワード線と前記ビット線対とに接続されるメモリセルと、前記ビット線対を駆動する駆動回路とを備えるS R A Mのテストを含む、テスト方法であって、

前記駆動回路は、

第2電源線から前記ビット線対のそれぞれのビット線への電流経路を形成する、第1及び第2NチャネルM O S F E Tと、

第1電源線から前記ビット線対の一方のビット線への電流経路を形成する、第3及び第4NチャネルM O S F E Tと、

を備え、

第1NチャネルM O S F E Tと第3NチャネルM O S F E T、及び、第2NチャネルM O S F E Tと第4NチャネルM O S F E Tのチャネル幅及び／又はチャネル長は異なり、

前記S R A Mのテストは、

前記ワード線に選択信号をアサートすることによって選択されたメモリセルについて、前記ビット線対の一方のビット線をハイレベル電位、前記第3及び第4NチャネルM O S F E Tの何れか一方をオンとすることによって、他方のビット線をロウレベル電位でそれぞれ駆動して、当該メモリセルにデータを書込む第1ステップと、

前記ワード線に選択信号をアサートすることによって選択されたメモリセルについて、前記ビット線対の一方のビット線を前記ハイレベル電位、前記第1及び第2NチャネルM O S F E Tをオンとし、前記第3及び第4NチャネルM O S F E Tのいずれか一方をオンとすることによって、他方のビット線を前記ロウレベル電位よりも高く前記ハイレベル電位よりも低い電位でそれぞれ駆動して、当該メモリセルにデータを書込む第2ステップとを含む、

テスト方法。

【請求項 1 1】

請求項 1 0において、

前記S R A Mのテストは、前記第2ステップの直後に、前記第2ステップでデータが書き込まれたメモリセルから、書き込まれたデータを読み出す第3ステップをさらに含む、

テスト方法。

【請求項 1 2】

請求項 1 0において、

前記第2ステップは、前記ワード線に選択信号をアサートして当該メモリセルへデータを書き込んだ後、当該ワード線のアサート状態を維持したまま、前記ビット線対をプリチャージする期間をさらに含む、

テスト方法。

【請求項 1 3】

請求項 1 0において、前記ロウレベル電位よりも高く前記ハイレベル電位よりも低い前記電位は、前記S R A Mの動作範囲における最低動作温度に基づいて規定され、前記第2ステップは、前記S R A Mを前記最低動作温度以上の温度で実行される、

テスト方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、半導体装置、テストプログラムおよびテスト方法に関し、特に、前記半導体装置に搭載されるS R A M (Static Random Access Memory) の低温における不良を常温でのテストで代替して選別するテスト技術に好適に利用できるものである。

10

20

30

40

50

**【背景技術】****【0002】**

従来、安価な半導体製品においては、製品出荷のための選別試験において、低温（例えば0℃以下）でのテストを省略することで、テストコストを下げる場合がある。これは、これまでの半導体製造プロセスでは、SRAMメモリセルにおいて、静的ノイズマージン(SNM: Static Noise Margin)不足等の製造起因の回路動作不具合が高温で多数発生する傾向があり、上記、低温でのテストを省略しても問題が生じなかつたからである。低温での動作が最も厳しいようなテスト項目については、常温で同等の動作条件となるような電源電圧等を予め求めておき、常温テストで代替する技術が提供されている。

**【0003】**

10

特許文献1には、予め準備されて提供される、温度とワード線電位の対応関係を記述した温度 - ワード線電位変換表に基づいて、ワード線電位を測定すべき温度に対応した電圧に変化させるテスト技術が開示されている。

**【先行技術文献】****【特許文献】****【0004】****【特許文献1】特開2010-244659号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

20

特許文献1について本発明者が検討した結果、以下のような新たな課題があることがわかった。

**【0006】**

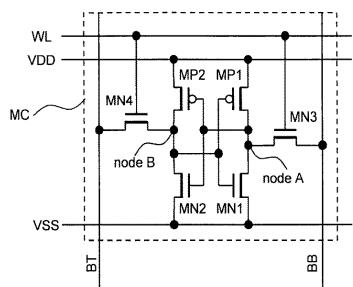

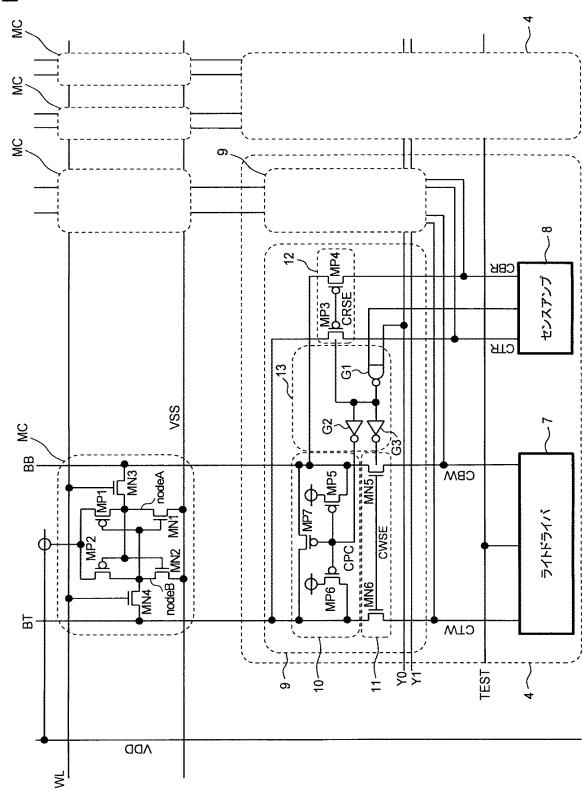

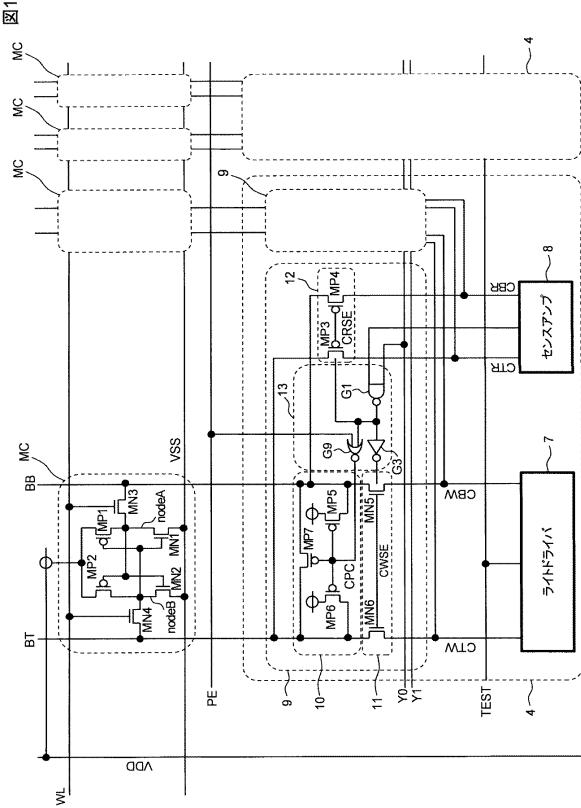

図1に、一般的な6トランジスタ構成のSRAMメモリセルの回路を示す。メモリセルMCは、ワード線WLとビット線対(BTとBB)と、電源を供給する電源線VDDと接地線VSSとに接続されている。メモリセルMCは、2個の記憶ノード(node Aとnode B)で互いの入力が他方の出力にそれぞれ接続される2個のインバータと、2個の転送ゲート(MN3とMN4)とを含んで構成される。2個のインバータは、それぞれがPチャネルMOSFET(Metal Oxide Semiconductor Field Effect Transistor)(MP1とMP2)とNチャネルMOSFET(MN1とMN2)とで構成される。PチャネルMOSFET(MP1とMP2)は負荷MOS、NチャネルMOSFET(MN1とMN2)は駆動MOSと呼ばれる。2個の転送ゲートは、ゲート電極がワード線WLに接続され、ソース電極が2個の記憶ノード(node Aとnode B)にそれぞれ接続され、ドレインがビット線対を構成する2本のビット線(BTとBB)にそれぞれ接続される、2個のNチャネルMOSFET(MN3とMN4)で構成される。なお、本明細書で参照するMOSFETでは、ソース電極とドレイン電極は電気的に対称であり、逆の称呼で呼んでもよい。ソース電極またはドレイン電極の一方をソース電極と呼ぶときに他方をドレイン電極と呼んでいるに過ぎない。

30

**【0007】**

40

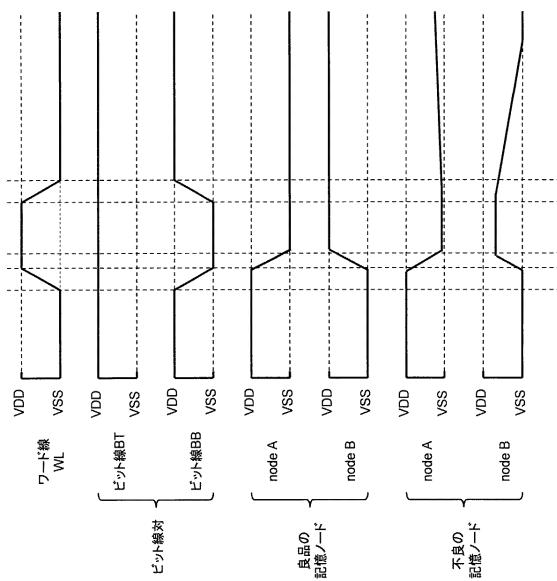

図2は、図1のSRAMメモリセルMCにデータが書き込まれるときの動作を示す波形図である。ワード線WLに選択信号がアサートされビット線対(BTとBB)に書き込みデータに対応する電圧が相補的に印加される。ワード線WLによって選択されたメモリセルMCにおいて、ビット線対(BTとBB)から記憶ノード(node Aとnode B)にそれぞれ印加された電圧が書き込まれる。図2には、ビット線BTにハイレベルがビット線BBにロウレベルがそれぞれ印加され、記憶ノード(node Aとnode B)に保持されるレベルが反転する例が示される。良品では、ノードAはハイレベルである電源(VDD)電位から、ロウレベルである接地(VSS)電位に遷移し、ノードBは逆にVSS電位からVDD電位に遷移する。

**【0008】**

この回路において、ノードB(node B)と電源線VDDの経路に障害が発生した場合、

50

メモリセルMCへのデータの書き込み動作において、ノードBにハイレベルが保持されるデータが書込まれたときに、ノードBの電位が電源VDDと同電位まで上昇せず、中間電位に留まる不良がある（図2の「不良の記憶ノード」参照）。障害として、負荷MOSであるPチャネルMOSFET（MP2）の閾値電圧が異常に高くオン電流が小さい場合や、経路上に半断線等による高抵抗箇所が存在する場合などが想定される。この不良は特に、低温で顕著になる。この不良を選別するためには、低温で試験を行うか、常温で不良化する電圧まで電源電圧を下げて試験を行っていた。

#### 【0009】

低温選別試験を実施する場合には、試験対象の半導体素子を低温（例えば-20~-40）にするための施設等が必要となり、かつ、高温、常温、低温の3温度で選別試験を行う必要があるためにテスト時間が長くなり、その結果、テストコストが高くなる問題が生じる。10

#### 【0010】

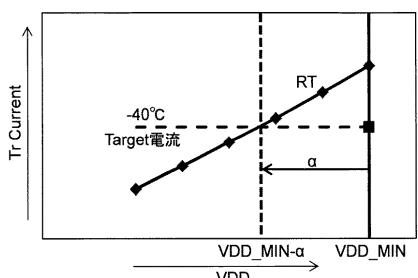

低温選別試験に代えて常温での選別試験を実施することによって、上記テストコストの上昇の問題は解決される。低温選別試験の代替えを常温で実施する場合には、電圧でガードバンドを設ける必要がある。図3は、一般的なトランジスタ（MOSFET）におけるトランジスタ電流の温度依存性を示す特性図である。横軸は電源電圧VDDであり、縦軸はトランジスタ電流（Tr Current；MOSFETの場合のドレイン電流）である。このトランジスタに関して、仕様の上での動作の下限電圧をVDD\_MINとするとき、この下限電圧VDD\_MINにおける低温時のトランジスタ電流（例えば-40のターゲット電流）と常温（例えば25）時のトランジスタ電流では、常温時のトランジスタ電流の方が大きい。常温時のトランジスタ電流を低温時のトランジスタ電流に合わせるためにには、VDD\_MINよりも電源電圧をさらにV下げるガードバンドをとる必要がある。ここで、Vは一般には数十mVである。20

#### 【0011】

低温選別試験の代替となる、このような常温での選別試験について、本発明者が検討した結果、以下のような新たな課題があることがわかった。

#### 【0012】

電源電圧を下げるガードバンドを設けることによって、電流駆動能力を下げる必要のあるトランジスタだけでなく、すべてのトランジスタの電流駆動能力が下がってしまう。このため、本来のテスト項目以外の原因で動作エラーになる半導体チップが発生し、排除したい不良の半導体チップ以外の、本来は良品である半導体チップまでも不良品と判定してしまう、所謂オーバーキルを発生させる問題が生じることがわかった。例えば、図1に示したSRAMメモリセルMCにおいて、負荷MOSであるPチャネルMOSFET（MP2）の電流駆動能力の低下に起因する、図2の「不良の記憶ノード」に示したような不良を検出するために、電源電圧を下げるガードバンドを設けたテストを行うと、その影響でメモリ読み出し時のセル電流が低下してセンスアンプ感度が下がり、不良と判定されてしまう恐れがある。30

#### 【0013】

さらに、半導体素子の微細化が進んだ場合には、オーバーキルの発生がより顕著であることがわかった。即ち、最近の微細化プロセスでは、ローカルばらつきが大きくなる影響で、SRAMメモリセルの製造起因の回路動作不具合は、低温でも多数発生することがわかった。40

#### 【0014】

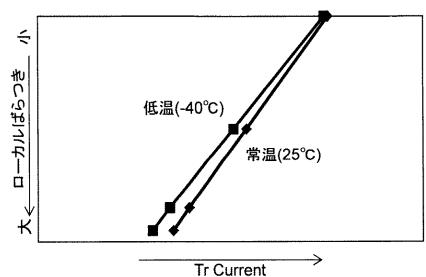

図4は、トランジスタ電流とローカルばらつきの関係および温度依存性を模式的に示す説明図である。横軸はトランジスタ電流、縦軸はローカルばらつきであり、常温（25）と低温（-40）の場合の特性が示される。ローカルばらつきが支配的なプロセスにおいては、中央値（Median；0）付近のトランジスタ特性とばらつきの大きい領域（6）のトランジスタ特性の温度依存性が異なる。低温（-40）の方が常温（25）よりもトランジスタ電流のローカルばらつきが大きいことがわかった。このため、中央値50

(0) 付近の特性を基準としてガードバンドを設定する選別試験では、不良流出の危険が増加することがわかった。

**【0015】**

このような課題を解決するための手段を以下に説明するが、その他の課題と新規な特徴は、本明細書の記述及び添付図面から明らかになるであろう。

**【課題を解決するための手段】**

**【0016】**

一実施の形態によれば、下記の通りである。

**【0017】**

すなわち、ワード線と、ビット線対と、メモリセルと、前記ビット線対を駆動する駆動回路とを備えるS R A Mにおいて、前記メモリセルへデータを書き込むときに、前記ビット線対の一方のビット線をハイレベル電位で駆動し、他方のビット線を通常書き込みの場合のロウレベル電位よりも高く前記ハイレベル電位よりも低い中間電位で駆動することができる機能を持たせる。10

**【発明の効果】**

**【0018】**

前記一実施の形態によって得られる効果を簡単に説明すれば下記のとおりである。

**【0019】**

すなわち、S R A Mについての低温選別試験に代えて常温での選別試験を実施する場合に、オーバーキルを減らし、かつ、ローカルばらつきに起因する不良流出の危険を抑えることができる。20

**【図面の簡単な説明】**

**【0020】**

**【図1】**図1は、一般的な6トランジスタ構成のS R A Mメモリセルの回路図である。

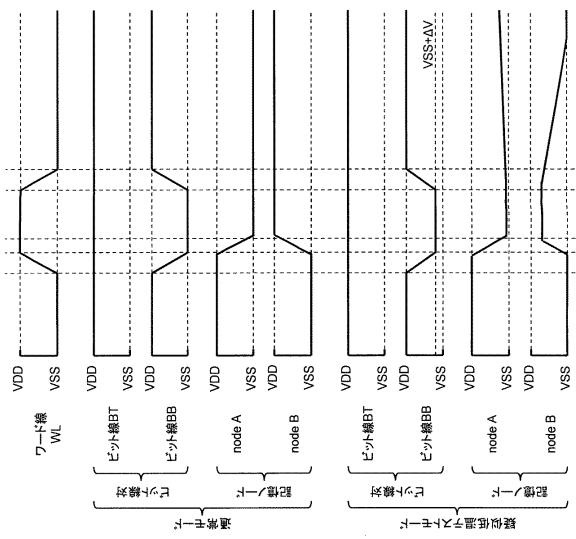

**【図2】**図2は、図1のS R A Mメモリセルにデータが書き込まれるときの動作を示す波形図である。

**【図3】**図3は、一般的なトランジスタにおけるトランジスタ電流の温度依存性を示す特性図である。

**【図4】**図4は、トランジスタ電流とローカルばらつきの関係および温度依存性を模式的に示す説明図である。30

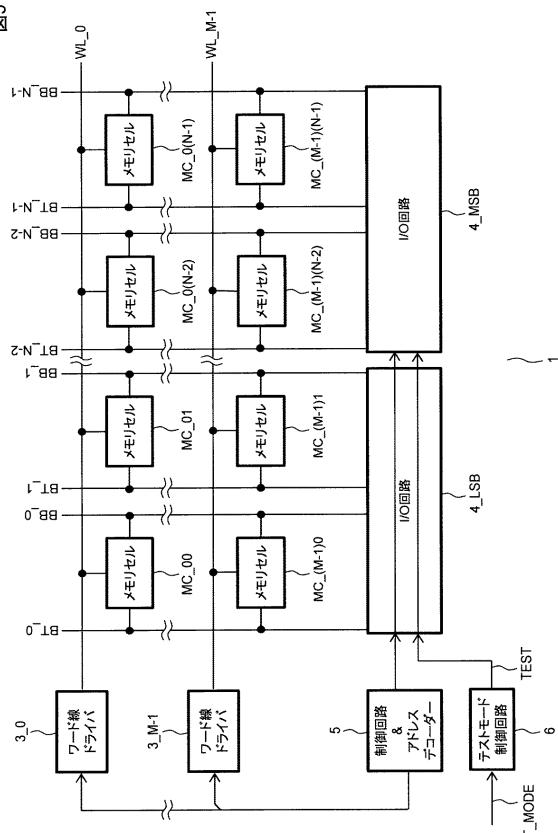

**【図5】**図5は、テスト対象であるS R A Mモジュールの構成例を示すブロック図である。

**【図6】**図6は、1個のメモリセルに着目して描いたI / O回路とメモリセルの回路構成例を示す構成図である。

**【図7】**図7は、図6のS R A Mメモリセルにデータが書き込まれるときの動作を示す波形図である。

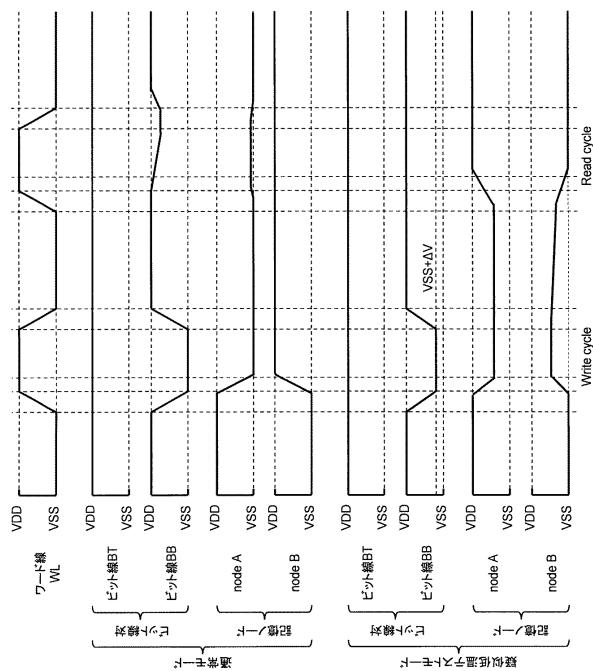

**【図8】**図8は、図6のS R A Mメモリセルにデータが書き込まれるときの動作の変形例（ライトサイクルの直後にリードサイクルを追加）を示す波形図である。

**【図9】**図9は、ライトドライバの構成例を示す回路図である。

**【図10】**図10は、図9に示されるライトドライバの動作例を示す波形図である。

**【図11】**図11は、図9に示されるライトドライバの通常動作モードにおける動作例を示す波形図である。

**【図12】**図12は、図9に示されるライトドライバの疑似低温選別テストモードにおける動作例を示す波形図である。

**【図13】**図13は、図9に示されるライトドライバの疑似低温選別テストモードにおける別の動作例を示す波形図である。

**【図14】**図14は、1個のメモリセルに着目して描いたI / O回路とメモリセルの回路構成についての別の例を示す構成図である。

**【図15】**図15は、図14の回路構成による書き込み直後のストレス動作を示す波形図である。50

【図16】図16は、図6の回路構成による書き込み直後のストレス動作を示す波形図である。

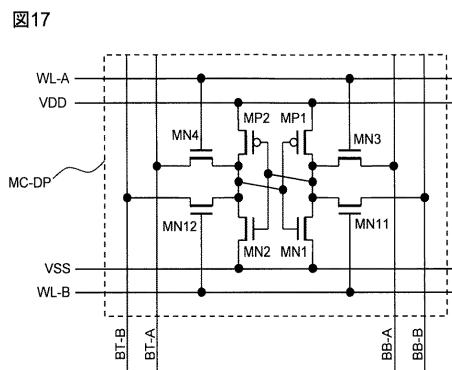

【図17】図17は、8トランジスタ構成のデュアルポートSRAMメモリセルの回路図である。

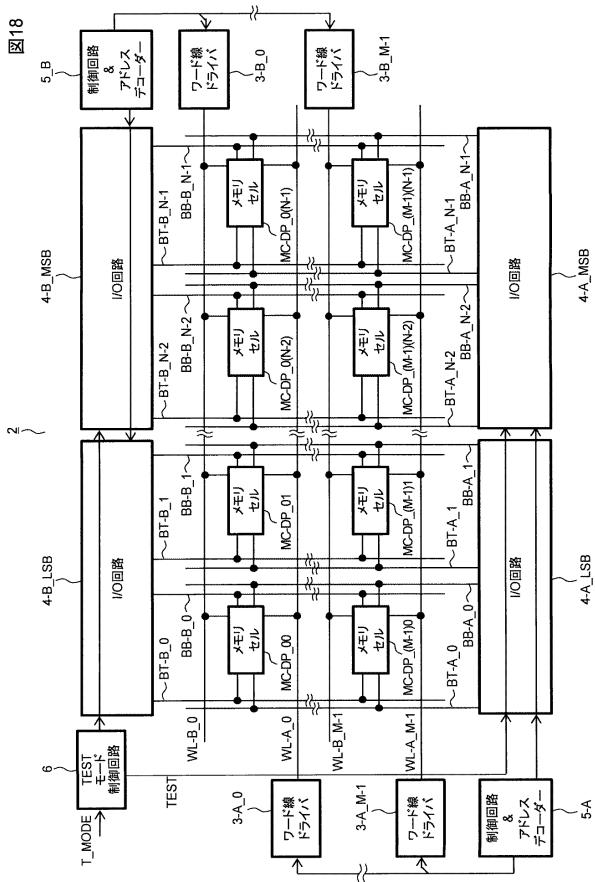

【図18】図18は、テスト対象であるデュアルポートSRAMモジュールの構成例を示すブロック図である。

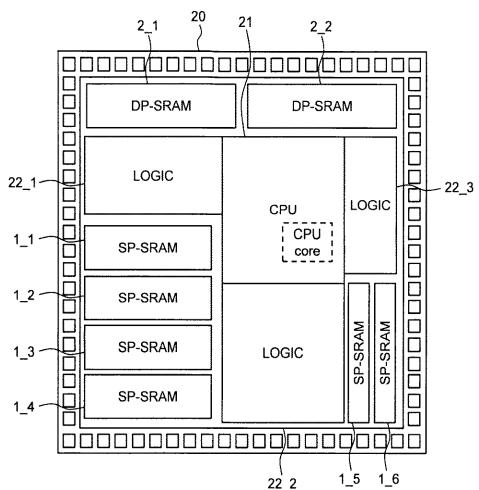

【図19】図19は、実施形態5における半導体チップのレイアウト構成を示す図である。

#### 【発明を実施するための形態】

##### 【0021】

実施の形態について詳述する。

##### 【0022】

###### 〔実施形態1〕

図5は、テスト対象であるSRAMモジュール1の構成例を示すブロック図である。本実施形態1ではMワード×Nビット(M,Nは整数)のシングルポートのSRAMモジュール1について説明する。SRAMモジュール1は、メモリセルMC<sub>00</sub>～MC<sub>(M-1)(N-1)</sub>、I/O回路4\_LSB(LSB:Least Significant Bit)と4\_MSB(MSB:Most Significant Bit)、ワード線ドライバ3\_0～3\_M-1、制御回路とアドレスデコーダー5、及び、テストモード制御回路6から成る。SRAMモジュール1は、ワード線WL\_0～WL\_M-1と、ビット線対BT\_0～BT\_N-1とBB\_0～BB\_N-1とを備え、ワード線とビット線対とが交差する箇所にメモリセルMC<sub>00</sub>～MC<sub>(M-1)(N-1)</sub>が接続されている。ワード線ドライバ3\_0～3\_M-1は、それぞれに接続されるワード線WL\_0～WL\_M-1のうち、アドレスデコーダー5のデコード結果に基づいて選択される1本のワード線に対して、ワード選択信号をアサートする。メモリセルMCが例えば図1に図示されるようにNチャネルMOSFETの転送ゲートを備える場合に「ワード選択信号をアサートする」とは、当該ワード線をハイレベル(通常はVDD電位)で駆動することを言う。I/O回路4\_LSBは下位ビット(LSB)側のメモリセルMC<sub>00</sub>～MC<sub>(M-1)0</sub>、MC<sub>01</sub>～MC<sub>(M-1)1</sub>…に接続され、I/O回路4\_MSBは上位ビット(MSB)側のメモリセルMC…、MC<sub>0(N-2)</sub>～MC<sub>(M-1)(N-2)</sub>、MC<sub>0(N-1)</sub>～MC<sub>(M-1)(N-1)</sub>に接続される。I/O回路4\_LSBと4\_MSBは、リード/ライト制御のために制御回路とアドレスデコーダー5に接続され、さらに、通常動作モードかテストモードかを制御するために、テストモード切替信号T\_MODEによって制御されるテストモード制御回路6からテストモード信号TESTが供給される。

##### 【0023】

メモリセルMCとI/O回路4について、より詳細に説明する。

##### 【0024】

図6は、1個のメモリセルに着目して描いたI/O回路4とメモリセルMCの回路構成例を示す構成図である。着目した1個のメモリセルMCと、それに接続されるI/O回路4のうち、メモリセルMCに接続されるライトドライバ7、センスアンプ8、及び、カラムI/O回路9が示される。カラムI/O回路9は、さらに、プリチャージ回路10、ライトカラムスイッチ11、リードカラムスイッチ12、及び、カラムI/O制御回路13よりなる。CTWとCBWはコモンライトビット線対、CTRとCBRはコモンリードビット線対、Y0とY1はYアドレス選択信号、CPCはプリチャージ制御信号、CWEはライトスイッチ制御信号、CRSEはリードスイッチ制御信号である。

##### 【0025】

図6では図示が省略されているが、SRAMモジュール1は、図2に例示されるように、制御回路とアドレスデコーダー5及びワード線ドライバ3\_0～3\_M-1を含んで構成され、図6に示されるワード線WLはワード線ドライバ3によって駆動される1本のみが図示され、他のワード線及びそれに接続されるメモリセルMCは図示が省略されている

10

20

30

40

50

。カラム方向も同様である。図6ではI/O回路4は2ビット分のみが図示されているが、カラム方向にさらに並べてもよい。また、図6では1個のI/O回路4あたり2個のカラムI/O回路9から成る例が図示されている。すなわち、MUX2の回路が例示されているが、より多くの選択回路、例えばMUX4,MUX8の構成に変更することもできる。ライトドライバ7には、テストモード信号TESTが入力されており、テストモードでは、ビット線対BTとBBのうちのロウ側のレベルを、VSSよりも高めの電位（中間電位）に浮かせて駆動することができるような回路が設けられている。

#### 【0026】

その中間電位とは、通常動作モードでは常温では良品、低温では不良となるようなメモリセルMCについて、常温でも不良として検出されるような電位である。回路シミュレーションや実験に基づいて設定され、VSSよりも数十mV～百数十mV（例えば20mV～120mV）だけ高く、VDDよりも低い電位となる。図6に示されるような、2個の記憶ノード（node Aとnode B）で互いの入力が他方の出力にそれぞれ接続される2個のインバータと、2個の転送ゲート（MN3とMN4）とを含んで構成されるメモリセルMCでは、ビット線対BTとBBから転送ゲート（MN3とMN4）を介して入力される電位によって、本来反転すべき記憶ノードの電位が反転しない場合に不良と判定される。このようなメモリセルMCにおいては、上述の通り、障害として、負荷MOSであるPチャネルMOSFET（MP1とMP2）の閾値電圧が異常に高くオン電流が小さい場合や、経路上に半断線等の高抵抗箇所が存在する場合などが想定される。この不良は特に低温で顕著になるため、通常動作モードでは、常温では正常動作するものの、低温では不良となる。テストモードで、ビット線対BTとBBのうちのロウレベル側を、VSSよりも高めの電位（中間電位）に浮かせて駆動することにより、記憶ノードをロウレベルからハイレベルに遷移させる駆動能力が弱められ、書き込みが阻害される。したがって、このテストモードは擬似低温テストモードであり、そのテストを擬似低温選別テストと呼ぶ。このとき、記憶ノードをロウレベルからハイレベルに遷移させる書き込みに対して、選択的にストレスを加えることができ、センスアンプなど他の回路にはストレスは加えられない。このように、メモリモジュール全体の電源電圧を下げるこによってストレスを加え、常温テストで低温状態を模擬する従来のテストと比較すると、テスト項目の対象となる素子に選択的にストレスを印加することができるので、当該素子以外の周辺の回路がストレスによって正常動作を阻害され不良として検出される、オーバーキルの発生を抑えることができる。

#### 【0027】

SRAMモジュール1の動作について、さらに詳しく説明する。

#### 【0028】

図7は、図6のSRAMメモリセルMCにデータが書き込まれるときの動作を示す波形図である。

#### 【0029】

通常動作モードの書き込み動作では、ライトドライバ7がコモンライトビット線対CTWとCBW（図7では図示を省略）を介してビット線対BTとBBに対して書き込みのための信号を出力し、ビット線対の一方をハイレベル（VDD電位）で、他方をロウレベル（VSS電位）で駆動する。ほぼ同時に、ワード線ドライバ3を駆動してワード線WLを立ち上げる。これは、ワード線選択信号のアサートであり、これにより選択されたメモリセルMCの記憶ノードであるノードAとノードB（node Aとnode B）のレベルがそれぞれ反転することで、データが書き込まれる。書き込み終了後、ワード線WLを立ち下げ、ビット線対BTとBBをプリチャージすることで1サイクルが終了する。この書き込みにおいて、ビット線対BTとBBのうちロウ側に設定されるビット線の電位は、通常の動作の場合は、VSS（GND）レベルに設定される。

#### 【0030】

これに対して、疑似低温テストモードでは、ロウ側のビット線電位をVSS（GND）レベルに対して数十mV～百数十mV浮かす（VSS+V）。その結果、図7に示すように書き込み後ロウ側になる内部ノードAがVSS（GND）レベルまで下がらず、上記の浮か

10

20

30

40

50

した電位 ( $V_{SS} + V$ ) になる。図6のメモリセルMCにおける負荷MOSであるPチャネルMOSFET (MP2) のゲート (ノードA) にも浮いた電位 ( $V_{SS} + V$ ) が印加されるため、 $V_{SS}$  (GND) が印加された場合に対して、PチャネルMOSFET (MP2) のソース・ドレイン間オン抵抗は大きくなり、ノードBのハイレベルへの引き上げが阻害される。

#### 【0031】

このように、書き込みを阻害することで、十分に書き込み能力が無い場合 (電源VDDからノードBに電流を供給する経路に障害 (故障) がある場合) に書き込みストレスがかかり、正常な書き込みができなくなる。したがって、常温では正常に動作するが低温では不良となるような不良品を、常温でのテストで選別することで排除することができる。

10

#### 【0032】

さらに、不良をより顕在化させるためには、上記のストレスを掛けた書き込みを行った直後 (次のサイクル) に同一アドレスにリード動作を行うとよい。

#### 【0033】

図8は、図6のSRAMメモリセルにデータが書き込まれるときの動作の変形例 (ライトサイクルの直後にリードサイクルを追加) を示す波形図である。

#### 【0034】

通常動作モードで、ライトサイクルの直後に追加されたリードサイクルでは、書き込みが行われたメモリセルMCと同一のメモリセルMCに対してワード線WLが再び立ち上げられ (ワード選択信号のアサート) 、これに伴って記憶ノードであるノードAのレベルがビット線BBに、ノードBのレベルがビット線BTにそれぞれ読み出される。上記の例では、書き込まれたレベルはノードAがロウレベル、ノードBがハイレベルであるので、ビット線BBにノードAからロウレベルが読み出されて、ビット線BBの電位が低下する。このとき、ノードAの電位は、プリチャージされたビット線BBから電流が流れ込むために、若干上昇する。

20

#### 【0035】

疑似低温テストモードでも、ライトサイクルの直後に追加されたリードサイクルでは、書き込みが行われたメモリセルMCと同一のメモリセルMCに対してワード線WLが再び立ち上げられ (ワード選択信号のアサート) 、これに伴って記憶ノードであるノードAのレベルがビット線BBに、ノードBのレベルがビット線BTにそれぞれ読み出される。このとき、メモリセルMCに低温での障害があり、内部の書き込みが十分完了していない状態では、ノードAのレベルは $V_{SS}$  (GND) レベルまで下がりきらず、ノードBのレベルはVDDまで上がりきらない。この時点で同一のメモリセルMCに対してリードサイクルが実行され、ワード線WLが立上ることにより、ノードAとノードBは、プリチャージされたビット線対BBとBTに、それぞれ転送ゲート (MN3とMN4) を介して接続される。通常動作モードでは、ノードAの電位は、プリチャージされたビット線BBから電流が流れ込むために、若干上昇するに留まったが、内部の書き込みが十分完了していない状態では、ノードAのレベルはビット線BBから流れ込む電流によって反転し、これに伴ってノードBのレベルも反転する。このように、低温での障害があり静的ノイズマージン (SNM) が小さいメモリセルMCでは、ライト動作で記憶されたデータが直後のリード動作によって揮発することとなり、不良品として選別し、排除することができる。このようにSNMが小さいメモリセルMCでは、ライト動作の後、ある程度時間が経過すると、ノードAのレベルが $V_{SS}$  (GND) レベルまで下がり、ノードBのレベルがVDDまで上がりきって安定し、その後のリード動作では不良として選別し排除することができない場合がある。疑似低温テストモードでライトサイクルの直後にリードサイクルを追加することにより、上記のような不安定な不良までも適切に排除することができる。

30

#### 【0036】

以上のテスト方法は、テストプログラムに所定の制御言語を使いまたテストパターンとして記述される。このテストプログラムを、上記SRAMが実装される半導体チップをテスト対象として、半導体テスターが実行することによって、そのテスト方法が実行される

40

50

。半導体テスターによる実行に代えて、同等のテストシーケンスを実行するテスト回路を、半導体チップに内蔵しても良い。このことは、以下の実施形態についても同様である。

#### 【0037】

以上説明したように、S R A M メモリセルへの書き込み時において、ビット線対のうち口ウ側の電位を通常動作時より数十mV~百数十mV浮かして書き込みを阻害することで、書き込み能力が不足している不良メモリセルに対する低温選別試験を常温で疑似的に行うことが可能となり、通常の常温テストと同じ電源電圧で行うことで、オーバーキルを防止することができる。さらに、上記ストレスモードで書込んだ後、次のサイクルで同一アドレスをリードすることで、書き込みに対するストレスをより顕著に印加できることにより、不安定な不良までも適切に排除することができる。

10

#### 【0038】

##### 〔実施形態2〕

S R A M メモリセルへの書き込み時において、ビット線対のうち口ウ側の電位を通常動作時より数十mV~百数十mV浮かす機能を備える、ライトドライバ7の構成例について説明する。

#### 【0039】

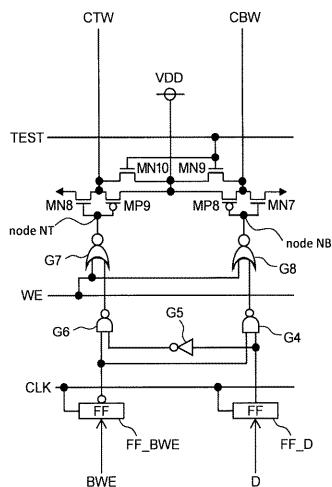

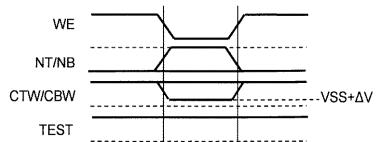

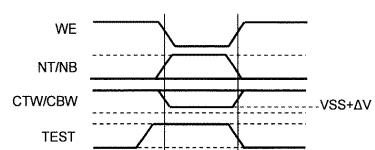

図9は、ライトドライバ7の構成例を示す回路図である。ライトドライバ7のうち、1ビット分だけが示される。入力されるDは書き込みデータ、BWEはビット書き込みマスク制御信号、TESTはテストモード信号、WEはライトイネーブル信号、CLKはクロック、出力されるCTWとCBWはコモンライトビット線対である。書き込みデータDとビット書き込みマスク制御信号BWEは、クロックCLKに同期してそれぞれ対応するフリップフロップFF\_DとFF\_BWEに取り込まれる。フリップフロップFF\_Dに取り込まれた書き込みデータDは、論理ゲートG4~G8により、相補的な論理レベルでコモンライトビット線対CTWとCBWに出力される。ただし、ビット書き込みマスク制御信号BWEがアサートされている状態では、書き込みデータDはマスクされ、コモンライトビット線対CTWとCBWにはともにハイレベルが出力される。このビット書き込みマスク機能は、省略することもできる。図9は1ビットに対して1個のビット書き込みマスク制御信号BWEが入力される例であるが、例えば8ビット又は9ビットなど複数のビット毎にまとめて1個のビット書き込みマスク制御信号BWEが入力されるように構成してもよい。バイト毎にまとめるにより、バイト書き込みマスク機能が提供される。

20

#### 【0040】

ライトドライバ7は、通常のライトドライバと同様に、入力されるノードNTとNBのレベルをそれぞれ反転して、コモンライトビット線対CTWとCBWに出力する2個のインバータを備える。2個のインバータは、PチャネルMOSFET(MP9)とNチャネルMOSFET(MN10)、PチャネルMOSFET(MP8)とNチャネルMOSFET(MN9)によって構成される。本実施形態のライトドライバ7は、疑似低温テストモードでテストモード信号TESTがハイになったときに、コモンライトビット線対CTWとCBWとを電源VDDに接続する、2個のNチャネルMOSFET(MN9とMN10)をさらに備える。

30

#### 【0041】

テストモード信号TESTで制御される2個のNチャネルMOSFET(MN9とMN10)の駆動能力をそのチャネル幅W2BとW2でそれぞれ表し、2個のインバータを構成する2個のNチャネルMOSFET(MN7とMN8)の駆動能力をそのチャネル幅W1BとW1でそれぞれ表す。テストモード信号TESTがアサートされる疑似低温テストモードでは、コモンライトビット線対CTWとCBWをロウレベルに駆動するインバータと、NチャネルMOSFET(MN7またはMN8)が競合して、コモンライトビット線対に接続されるビット線対のうちロウレベル側を、VSS(GND)電位よりも数十mV~百数十mV浮かす(中間電位にする)ことができる。CTWにロウレベル、CBWにハイレベルがそれぞれ出力されるとき、ロウレベルが出力されるCTWに接続されるNチャネルMOSFET(MN10)もオンになるので、CTWの実際の電位(中間電位)は、Nチ

40

50

チャネルMOSFET (MN10) のチャネル幅W2とインバータを構成するNチャネルMOSFET (MN8) のチャネル幅W1の違いによって規定される。逆に、CTWにハイレベル、CBWにロウレベルがそれぞれ出力されるとき、ロウレベルが出力されるCBWに接続されるNチャネルMOSFET (MN9) もオンになるので、CBWの実際の電位(中間電位)は、NチャネルMOSFET (MN9) のチャネル幅W2Bとインバータを構成するNチャネルMOSFET (MN7) のチャネル幅W1Bの違いによって規定される。

#### 【0042】

以上は、疑似低温テストモードにおけるビット線対のうちロウ側を所望の中間電位に設定するために、チャネル幅W1, W2, W1B, W2Bを調整する方法について説明したが、チャネル長Lも合わせて調整してもよい。チャネル長の調整は、現実に2倍のチャネル長2LのMOSFETを備える代わりに、通常のチャネル長(L)のMOSFETを2個、直列接続して実現しても良い。

10

#### 【0043】

このように、通常のライトバッファに、テストモード信号TESTで制御される2個のNチャネルMOSFET (MN9とMN10) を追加するだけで、SRAMメモリセルへの書き込み時において、ストレスを与える(ビット線対のうちロウ側の電位を通常動作時より数十mV~百数十mV浮かす機能を備える)ライトドライバ7を実現することができる。

#### 【0044】

ライトドライバ7の動作についてさらに詳しく説明する。

20

#### 【0045】

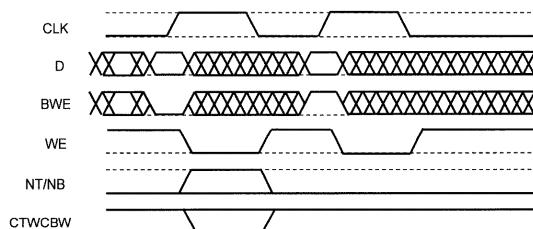

図10及び図11~図13は、図9に示されるライトドライバ7の動作例を示す波形図である。

#### 【0046】

図10及び図11に示される、通常動作モードにおける書き込み動作は、クロックCLKが立上ることで、フリップフロップFF\_Dに入力信号Dを、フリップフロップFF\_BWEにビット書き込みマスク制御信号BWEをそれぞれ取り込む。BWEがイネーブル(ロウレベル)の場合に、フリップフロップFF\_Dに取り込まれたデータDがメモリセルMCに書き込まれ(図10前半)、BWEがディセーブル(ハイレベル)の場合には書き込みは行われない(図10後半)。

30

#### 【0047】

ライトイネーブル信号WEが初期段階はハイレベルであり、このときの内部ノードNT及びNBは共にロウレベルとなり、コモンライトビット線対CTWとCBWは共にハイレベルである。

#### 【0048】

次に、ライトイネーブル信号WEがロウレベルとなると、内部ノードNT及びNBは入力信号Dに応じて一方がハイ、他方がロウとなり、コモンライトビット線対CTWとCBWもそれに応じて、一方がロウレベル、他方がハイレベルとなる。

#### 【0049】

その後、ライトイネーブル信号WEがハイレベルとなると、内部ノードNT及びNBは共にロウレベルとなり、コモンライトビット線対CTWとCBWは共にハイレベルにプリチャージされる。

40

#### 【0050】

BWEがイネーブル(ロウレベル)でメモリセルMCにデータDが書き込まれるときには、図11に示されるように、ライトイネーブル信号WEが立下り、フリップフロップFF\_Dに取り込まれたデータDに基づいて内部ノードNT/NBが変化し、コモンライトビット線対CTW/CBWもそれに応じて駆動される。通常動作モードであるので、テストモード信号TESTはロウレベルであり、図9の2個のNチャネルMOSFET (MN9とMN10) は共にオフされているため、コモンライトビット線対CTW/CBWのハイ側はVDD電位まで、ロウ側はVSS(GND)電位まで、それぞれ駆動される。

50

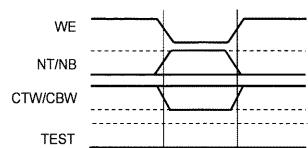

**【0051】**

これに対して、疑似低温選別テストモードでは、図12に示されるように、テストモード信号TESTが、ライトイネーブル信号WEが立上る以前にアサートされており、図9の2個のNチャネルMOSFET(MN9とMN10)は共にオンされているため、コモンライトビット線対CTW/CBWは共にVDD電位に引き上げられている。ライトイネーブル信号WEが立下り、フリップフロップFF\_Dに取り込まれたデータDに基づいて内部ノードNT/NBが変化し、コモンライトビット線対CTW/CBWもそれに応じて駆動される。このとき、コモンライトビット線対CTW/CBWのうちの口ウ側は、MN9またはMN10と、ロウレベルを出力するインバータのNチャネルMOSFETであるMN7またはMN8との間で信号が競合し、上述のようにそれらの駆動能力で決まる中間的な電位になる。これにより、書き込み時にロウ側のビット線を数十mV~百数十mV浮かすことでストレスを加えることができる。10

**【0052】**

図12に示すように、テストモード信号TESTはライトイネーブル信号WEの逆相で制御される。遷移させるタイミングは、テストモード信号TESTの立ち上がりを、ライトイネーブル信号WEの立上りと同時かそれよりも早くし、立下りはライトイネーブル信号WEと同時とする。

**【0053】**

これに対して、図13に示すように、テストモード信号TESTをハイレベルに固定したままでもよい。図12に示す例では、テストモード中に疑似低温選別テストモードと通常の常温選別試験モードと間をテストモード信号TESTによって切り替える制御を可能とすることができます。一方、図13に示す例では、テストモード信号TESTを通常動作モードとテストモードの切替え制御信号と兼用することができ、動作モードの切替え制御回路が簡略化される。20

**【0054】**

以上説明したように、SRAMメモリセルへの書き込み時において、ビット線対のうちロウ側の電位を通常動作時より数十mV~百数十mV浮かして書き込みを阻害することにより、疑似低温選別テストモードを実現するための、ライトドライバ7に好適な回路構成が提供される。即ち、ビット線を浮かすために、ソース側がVDDにドレイン側がビット線対にそれぞれ接続され、ゲートにテストモード信号TESTが接続される、2個のNチャネルMOSFET(MN9とMN10)が、ライドドライバ7に追加される。2個のNチャネルMOSFET(MN9とMN10)の駆動能力は、ビット線対をロウに駆動するNチャネルMOSFET(MN7とMN8)よりも弱く、その駆動能力のバランスでロウ側のビット線を浮かす電位(中間電位)を決定することができる。このように、2個のNチャネルMOSFET(MN9とMN10)を追加するのみでストレス回路を実現することができる。30

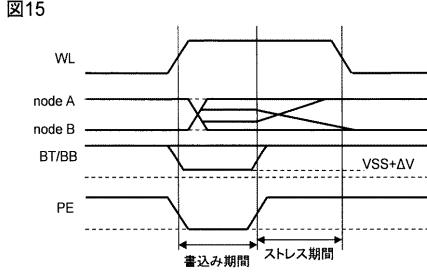

**【0055】****[実施形態3]**

図14は、1個のメモリセルに着目して描いたI/O回路4とメモリセルMCの回路構成についての別の例を示す構成図である。実施形態1において図6に示される構成例との違いは、プリチャージイネーブル信号PEが追加されている点である。プリチャージイネーブル信号PEが入力される論理ゲートがインバータG2からNORゲートG9に変更されている。他の構成は図6に示される構成例と同様であるので、説明を省略する。40

**【0056】**

図15は、図14の回路構成による書き込み直後のストレス動作を示す波形図である。

**【0057】**

実施形態1において図8を引用して説明した動作例では、ライトサイクルの直後にリードサイクルが追加され、合せて2サイクルを要する。これに対して、図15に示す本実施形態3の動作例では、メモリセルMCへの1回のアクセス期間内に、書き込み期間と疑似読み出しによるストレス期間とが含まれる。50

**【0058】**

書き込み期間は、実施形態1の図8の書き込みサイクルと同様に、ストレスをかけた書き込みである。即ち、ビット線対BT/BBのうちのロウ側の電位を通常動作時より数十mV~百数十mV浮かして書き込みを行う。この期間は、プリチャージイネーブル信号PEをネガートして、プリチャージをオフにする。

**【0059】**

ストレス期間では、書き込み期間が完了した後もワード線WLは立ち下げず、プリチャージイネーブル信号PEをアサートして、引き続き同一メモリセルMCに対する対象ビット線対のプリチャージをオンにし、ビット線対BT/BBをVDDレベルにする。ワード線WLを立ち上げたまま対象ビット線対BT/BBがプリチャージされた結果、低温での障害があり内部の書き込みが十分完了していないメモリセルMCでは、内部ノードA/Bにおける記憶レベルが揮発する。このように、メモリセルMCのデータ保持特性に対してストレスを加えることができ、不良を顕在化させ、不良サンプルを選別することをより容易にすることができます。10

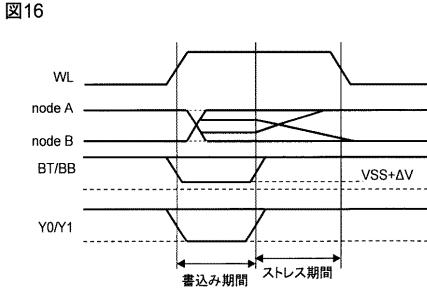

**【0060】**

図14に示した回路構成例では、プリチャージイネーブル信号PEを追加したが、これに代えて、図6に示される構成例のまま、Yアドレス選択信号Y0とY1をプリチャージの制御信号と兼用することも可能である。

**【0061】**

図16は、図6の回路構成による書き込み直後のストレス動作を示す波形図である。20

**【0062】**

書き込み期間は、図15の書き込み期間と同様に、ストレスをかけた書き込みである。即ち、ビット線対BT/BBのうちのロウ側の電位を通常動作時より数十mV~百数十mV浮かして書き込みを行う。書き込み期間に先立つプリチャージ期間では、プリチャージイネーブル信号PEをアサートする代わりにYアドレス選択信号Y0とY1をともに非選択とすることにより、全ビットをプリチャージする。書き込み期間には選択されたカラムのYアドレス選択信号Y0またはY1を選択状態にすることで、プリチャージをオフにする。

**【0063】**

ストレス期間では、図15のストレス期間と同様に、書き込み期間が完了した後もワード線WLは立ち下げないが、プリチャージイネーブル信号PEをアサートする代わりにYアドレス選択信号Y0とY1をともに非選択とすることにより、ビット線対BT/BBをVDDレベルにプリチャージする。30

**【0064】**

これにより、制御回路を変更するだけで、図15に示す動作と同様の効果を奏すことができる。

**【0065】**

以上説明したように、SRAMメモリセルへの書き込み時に、ビット線対のうちロウ側の電位を通常動作時より数十mV~百数十mV浮かして書き込みを阻害する、疑似低温選別テストモードにおいて、ストレスを加えた書き込みとその後のダミーリード動作を連続的に1つのコマンドで行うことができる。通常の書き込みコマンドで2つのストレス試験を行うことができる為、特別なテストパターンを不要とし、選別試験時のテストパターンを簡略化することができる。また、テストタイムが短縮されるので、テストコストを低減することができる。40

**【0066】****〔実施形態4〕**

以上は、専らシングルポートSRAMを例に採って説明してきたが、マルチポートSRAMにおいても同様に実施することができる。その一例として、デュアルポートSRAMに適用する実施形態について説明する。

**【0067】**

図17は、8トランジスタ構成のデュアルポートSRAMメモリセルMC-DPの回路50

図である。図1に示される一般的な6トランジスタ構成のSRAMメモリセルと比較して、ワード線はWL-AとWL-B、ビット線対はBT-A/BB-AとBT-B/BT-Bのそれぞれ2ポートに増設され、これに伴って転送ゲートとして機能する2個のNチャネルMOSFET(MN11とMN12)が追加されている。他の構成と動作についてはシングルポートSRAMのメモリセルと同様であるので、説明を省略する。

#### 【0068】

図18は、テスト対象であるデュアルポートSRAMモジュールの構成例を示すプロック図である。図5と同様にMワード×Nビット(M,Nは整数)の構成であり、メモリセルはデュアルポートSRAMメモリセルMC-DP00~MC-DP\_(M-1)(N-1)に置き換えられている。Aポート側のI/O回路4-A\_LSBと4-A\_MSB、ワード線ドライバ3-A\_0~3-A\_M-1、制御回路とアドレスデコーダー5-A、Bポート側のI/O回路4-B\_LSBと4-B\_MSB、ワード線ドライバ3-B\_0~3-B\_M-1、制御回路とアドレスデコーダー5-B、及び、テストモード制御回路6から成る。I/O回路4、ワード線ドライバ3、制御回路とアドレスデコーダー5は、Aポート側とBポート側で同じ回路が実装され、それぞれが、実施形態1で説明したシングルポートのSRAMと同様に動作する。テストモード制御回路6は、全体で1個備えればよく、テストモード信号TESTは、一方のI/O回路、例えば図18に示されるようにポートA側のI/O回路4-A\_LSBと4-A\_MSBにのみ供給される。ポートA側のI/O回路4-A\_LSBと4-A\_MSBは、図7に例示されるような、疑似低温テストモードで、ロウ側のビット線電位をVSS(GND)レベルに対して数十mV~百数十mV浮かす回路が搭載される。一方、ポートB側のI/O回路4-B\_LSBと4-B\_MSBは、疑似低温テストモードのための上記回路は省略される。低温で顕著となる不良が、メモリセルの障害に原因があるので、どちらか一方のポートから、疑似低温テストモードでの選別試験を実施することができれば十分だからである。

#### 【0069】

一方、ポートB側のI/O回路4-B\_LSBと4-B\_MSBにも同様の回路を搭載し、両方のポートから、疑似低温テストモードでの選別試験を実施することができるよう構成しても良い。例えばビット線対やワード線に起因する障害が、低温で顕著となる不良を惹き起こしている場合には、両方のポートから疑似低温テストモードでの選別試験を実施することにより、不良品の流出を防止することができる。

#### 【0070】

##### 〔実施形態5〕

以上の実施形態1~4で説明したシングルポート及びマルチポートのSRAMモジュールは、SoC(System-on-a-Chip)やマイクロコンピュータを含むシステムが形成された半導体チップ20に組み込むことができる。図19は、本実施形態5における半導体チップ20のレイアウト構成を示す図である。図19において、半導体チップ20は、CPU(Central Processing Unit)21、シングルポートSRAM(SP-SRAM)1\_1~1\_6、デュアルポートSRAM(DP-SRAM)2\_1~2\_2および論理回路(LOGIC)22\_1~22\_3を有している。ここで、シングルポートSRAM(SP-SRAM)1\_1~1\_6は、実施形態1~4で説明したシングルポートSRAMであり、デュアルポートSRAM(DP-SRAM)2\_1~2\_2は、実施形態4で説明したデュアルポートSRAMである。なお、SRAMの他、EEPROM(Electrically Erasable Programmable Read Only Memory)などの他の記憶素子を有する構成としてもよろしく、また、アナログ回路などを内蔵してもよい。

#### 【0071】

CPU21は、中央演算処理装置とも呼ばれ、コンピュータなどの心臓部にあたる。このCPU21は、記憶装置から命令を読み出して解読し、それに基づいて多種多様な演算や制御を行なうものである。このCPU21の内部には、CPUコア(CPU core)が内蔵されており、かかるCPUコアの内部にはSRAMが組み込まれている。このCPUコアの内部のSRAMとしては、高性能なSRAMが用いられており、上記実施形態1~4に

10

20

30

40

50

説明した S R A M を用いて好適である。もちろん、上記シングルポートの S R A M ( S P - S R A M ) 1\_1 ~ 1\_6 やデュアルポートの S R A M ( D P - S R A M ) 2\_1 ~ 2\_2 にも、上記実施形態 1 ~ 4 で詳細に説明した S R A M を用いてもよい。

#### 【 0 0 7 2 】

このように、上記実施形態 1 ~ 4 で説明した S R A M を、S o C やマイクロコンピュータを含むシステムが形成された半導体チップ 20 に組み込むことにより、その特性を向上させることができる。また、低温で顕著となる不良を惹き起こすのが、搭載される S R A M でのみ顕著で、C P U 2 1 や論理回路 ( L O G I C ) 2 2\_1 ~ 2 2\_3 などの他の回路では低温選別試験が不要である場合には、半導体チップ 20 に搭載される全ての S R A M に本実施形態 1 ~ 4 を適用することにより、チップ全体の低温選別試験を省略しながらも、オーバーキルや不良流出の問題を防止することができる。

10

#### 【 0 0 7 3 】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

#### 【 符号の説明 】

#### 【 0 0 7 4 】

M C メモリセル

M C - D P デュアルポートメモリセル

M P 1 ~ 7 P チャネルM O S F E T

20

M N 1 ~ 1 2 N チャネルM O S F E T

F F フリップフロップ

G 1 ~ G 8 論理ゲート

V D D 電源線

V S S 接地線

W L ワード線

B T , B B ビット線対

T \_ M O D E テストモード切替信号

T E S T テストモード信号

C T W , C B W コモンライトビット線対

30

C T R , C B R コモンリードビット線対

Y 0 , Y 1 Y アドレス選択信号

C P C プリチャージ制御信号

P E プリチャージイネーブル信号

C W S E ライトスイッチ制御信号

C R S E リードスイッチ制御信号

D 書込みデータ

B W E ビット書込みマスク制御信号

W E ライトイネーブル信号

C L K クロック

40

1 シングルポート S R A M モジュール

2 デュアルポート S R A M モジュール

3 ワード線ドライバ

4 I / O 回路

5 制御回路 & アドレスデコーダー

6 テストモード制御回路

7 ライトドライバ

8 センスアンプ

9 カラム I / O 回路

1 0 プリチャージ回路

50

- 1 1 ライトカラムスイッチ

2 0 半導体チップ

2 1 C P U (Central Processing Unit)

2 2 論理回路 (LOGIC)

【図1】

図1

【図2】

図2

【図3】

図3

【 四 4 】

図4

【 义 6 】

6

【図5】

5

【 四 7 】

7

【図8】

図8

【図9】

図9

【図10】

図10

【図13】

図13

【図11】

図11

【図12】

図12

【図14】

【図15】

【図16】

【図17】

【図18】

## 【図19】

図19

---

フロントページの続き

(72)発明者 横山 佳巧

神奈川県川崎市中原区下沼部1753番地 ルネサスエレクトロニクス株式会社内

審査官 篠塚 隆

(56)参考文献 特開2011-227969(JP,A)

特開2013-012275(JP,A)

特開平10-144096(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 29 / 50

G 11 C 29 / 06