#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

23 December 2015 (23.12.2015)

(10) International Publication Number WO 2015/195372 A1

- (21) International Application Number:

PCT/US2015/034465

(22) International Filing Date:

5 June 2015 (05.06.2015)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

14/311,165

20 June 2014 (20.06.2014)

US

- (71) Applicant: VISHAY-SILICONIX [US/US]; 2201 Laurel-wood Road, Santa Clara, CA 95054 (US).

- (72) Inventors: TIPIRNENI, Naveen; 700 Agnew Road, Apt 236, Santa Clara, CA 95054 (US). PATTANAYAK, Deva; 19123 Brookhaven Drive, Saratoga, CA 95070 (US).

- (74) Agent: ZARBIS, William; Murabito Hao & Barnes, LLP, 2n. Market St., 3rd Floor, San Jose, CA 95113 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK,

[Continued on next page]

$(54)\ Title$ : PROCESSES USED IN FABRICATING A METAL-INSULATOR-SEMICONDUCTOR FIELD EFFECT TRANSISTOR

(57) Abstract: During fabrication, a second oxide layer is disposed over a first region and a second region of a structure. The second region includes a first oxide layer between the second oxide layer and an epitaxial layer. The first region corresponds to an active region of a metal-insulator-semiconductor field effect transistor (MISFET), and a first-type dopant source region, a second-type dopant body region, and a second-type dopant implant region are formed in the first region. The second region corresponds to a termination region of the MISFET. A mask is formed over the second region, and parts of the second oxide layer and the first oxide layer that are exposed through the gaps are removed, thereby exposing the epitaxial layer. Second-type dopant is deposited into the epitaxial layer through the resultant openings in the first and second oxide layers, thereby forming field rings for the MISFET.

SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, **Published**: GW, KM, ML, MR, NE, SN, TD, TG).

— with in

— with international search report (Art. 21(3))

# PROCESSES USED IN FABRICATING A METAL-INSULATOR-SEMICONDUCTOR FIELD EFFECT TRANSISTOR

# **BACKGROUND**

[0001] The manufacture of a metal-insulator-semiconductor field effect transistor (MISFET) device (e.g., a metal-oxide-semiconductor field effect transistor (MOSFET)) includes a number of critical photolithographic masking and alignment processes/steps.

[0002] U.S. Patent No. 5,302,537 discusses the use of three mask processes for fabricating the active cell region and the termination region of a low-voltage MISFET. However, the processes described in that patent are inadequate for building a reliable high-voltage (greater than 80 volts (V)) device.

[0003] Field or termination rings that terminate the planar junction of the active cell region are commonly used to achieve a high-voltage device. U.S. Patent No. 5,795,793 discusses the use of three mask processes for fabricating the active region of a MOSFET. An additional three masks are needed to form the termination rings, meaning at least six masks are needed to manufacture a high-voltage device.

[0004] Reducing the number of masks needed to manufacture a high-voltage device can decrease manufacturing costs and increase yield.

# **SUMMARY**

[0005] Embodiments according to the present invention pertain to processes used in fabricating a metal-insulator-semiconductor field effect transistor (MISFET), in particular a high-voltage (e.g., greater than 80 V) MISFET, and also pertain to devices fabricated using such processes.

[0006] In an embodiment according to the invention, during fabrication of a MISFET (e.g., a MOSFET), a second oxide layer is disposed over a first region and a second region of a structure. The structure includes a semiconductor substrate with an n-type epitaxial layer. The first region corresponds to an active region of the MISFET, and the second

region corresponds to a termination region of the MISFET. The second region includes a first oxide layer between the second oxide layer and an epitaxial layer. A first-type dopant source region, a second-type dopant body region, and a second-type dopant implant region are formed in the first region. A mask is formed over the second region, and parts of the second oxide layer and the first oxide layer in the second region that are exposed through gaps in the mask are removed, thereby exposing the epitaxial layer. Second-type dopant is deposited through the resultant openings in the first and second oxide layers into the epitaxial layer in the second region, thereby forming field rings for the MISFET.

[0007] More specifically, in one embodiment, a first oxide layer is deposited over an epitaxial layer of a structure. A first mask is formed over the first oxide layer. The first mask defines a second region corresponding to the termination region of the MISFET. The first oxide layer is removed from around the first mask to define a first region corresponding to the active region of the MISFET. After removing the first mask, a polysilicon layer is deposited over the first region and the second region. A second mask is formed over the polysilicon layer. The polysilicon layer is removed from around the second mask to form an opening in the polysilicon layer in the first region, thereby exposing the epitaxial layer. A first-type dopant source region, a second-type dopant body region, and a second-type dopant implant region are formed in the epitaxial layer through the opening. After the second mask is removed, a second oxide layer is deposited over the first region and the second region. A third mask is formed over at least the second region. The third mask includes mask elements separated by gaps, and parts of the second oxide layer and the first oxide layer that are exposed through the gaps are removed, thereby exposing the epitaxial layer. Also, in the second region, second-type dopant is deposited through the resultant openings in the first and second oxide layers into the epitaxial layer, thereby forming field rings for the MISFET. After the third mask is removed, a metal layer is deposited over the first region and the second region. A fourth mask is formed over the metal layer, and the metal layer is removed from areas around the fourth mask. After the fourth mask is removed, a passivation layer is deposited over the first region and the second region. A fifth mask is formed over the passivation layer, and the passivation layer is removed from around the fifth mask to form source and gate bond pad regions for the MISFET.

[0008] In one embodiment, the gaps in the third mask are uniformly sized and uniformly spaced. In one such embodiment, each of the gaps is between approximately 0.5 and 0.8 microns in width, and each of the mask elements has a width of approximately 1.8 microns.

[0009] In one embodiment, the third mask also includes mask elements over the first region. These mask elements are separated by a gap. Parts of the second oxide layer and the first-type dopant source region that are exposed through that gap are removed, thereby also exposing the second-type dopant implant region.

[0010] In summary, in embodiments according to the invention, five masks/mask steps are used. Generally speaking, the number of masks is reduced relative to conventional processes, from six masks to five masks, thus reducing manufacturing costs and increasing yield.

[0011] These and other objects and advantages of embodiments according to the present invention will be recognized by one skilled in the art after having read the following detailed description, which are illustrated in the various drawing figures.

# BRIEF DESCRIPTION OF THE DRAWINGS

[0012] The accompanying drawings, which are incorporated in and form a part of this specification, illustrate embodiments of the invention and, together with the description, serve to explain the principles of the invention. Like numbers denote like elements throughout the drawings and specification.

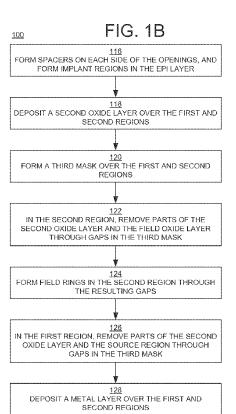

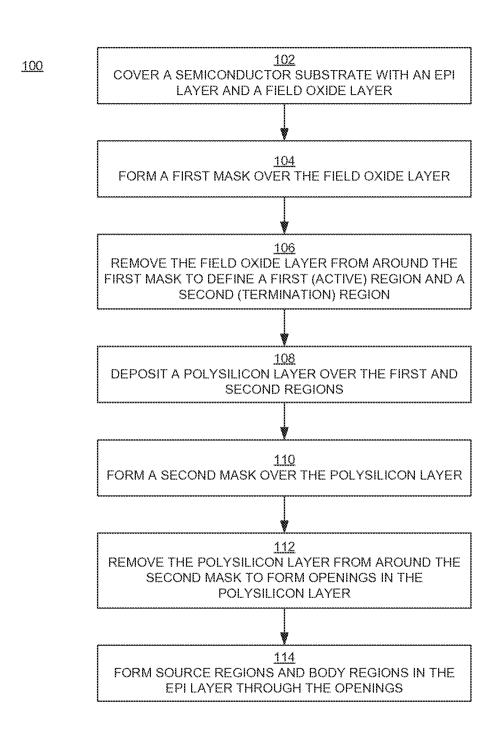

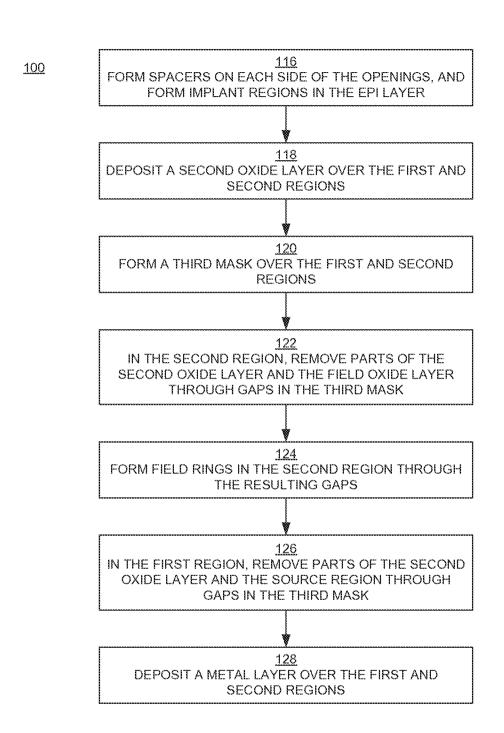

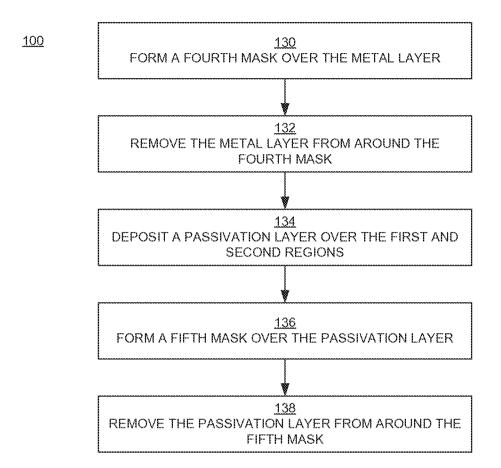

[0013] Figures 1A, 1B, and 1C are flowcharts showing examples of processes performed in fabricating a MISFET in an embodiment according to the present invention.

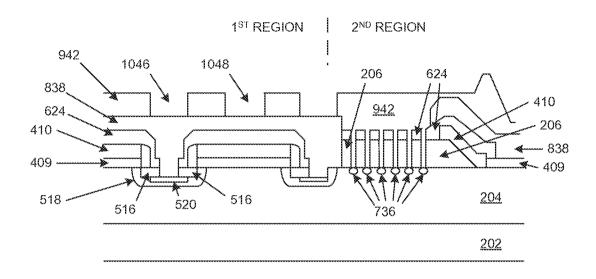

[0014] Figures 2, 3, 4, 5, 6, 7, 8, 9, and 10 are cross-sectional views of a portion of a MISFET at various points during fabrication in an embodiment according to the present invention.

#### **DETAILED DESCRIPTION**

[0015] In the following detailed description of the present invention, numerous specific details are set forth in order to provide a thorough understanding of the present invention. However, it will be recognized by one skilled in the art that the present invention may be practiced without these specific details or with equivalents thereof. In other instances, well-known methods, procedures, components, and circuits have not been described in detail as not to unnecessarily obscure aspects of the present invention.

[0016] The figures are not drawn to scale, and only portions of the structures, as well as the various layers that form those structures, may be shown in the figures.

[0017] As used herein, the letter "n" refers to an n-type dopant and the letter "p" refers to a p-type dopant. A plus sign "+" or a minus sign "-" is used to represent, respectively, a relatively high or relatively low concentration of the dopant.

[0018] The term "channel" is used herein in the accepted manner. That is, current moves within a FET in a channel, from the source connection to the drain connection. A channel can be made of either n-type or p-type semiconductor material; accordingly, a FET is specified as either an n-channel or p-channel device. The disclosure is presented in the context of an n-channel device, specifically an n-channel MISFET (e.g., a MOSFET); however, embodiments according to the present invention are not so limited. That is, the features described herein can be utilized in a p-channel device. The disclosure can be readily mapped to a p-channel device by substituting, in the discussion, n-type dopant and materials for corresponding p-type dopant and materials, and vice versa.

[0019] Figures 1A, 1B, and 1C illustrate a flowchart 100 of processes for fabricating a device (e.g., an n-channel MISFET) in an embodiment according to the present invention. As mentioned above, although the flowchart 100 is described using an n-channel device as an example, the processes can be readily adapted to manufacture a p-channel device. Also, other fabrication processes and steps may be performed along with the processes and steps discussed herein; that is, there may be a number of process steps

before, in between and/or after the steps shown and described herein. Generally speaking, embodiments according to the present invention can replace portions of a conventional fabrication process without significantly affecting peripheral processes and steps.

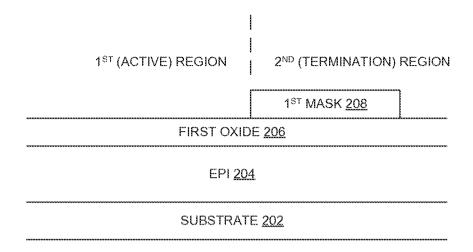

[0020] In block 102, with reference also to Figure 2, a semiconductor substrate 202 with an n-type epitaxial (epi) layer 204 is covered by a field oxide layer 206. The field oxide layer 206 may also be referred to herein as a first oxide layer. The thickness and doping profile of the epi layer 204 is specified by design to have a given breakdown voltage, particularly a breakdown voltage for a high voltage device.

[0021] In block 104, a first mask 208 is formed over the field oxide layer 206. The first mask 208 is used to define a region (which may be referred to herein as the first region) that corresponds to the active region of the device, and also defines a region (which may be referred to herein as the second region) that corresponds to the termination region of the device.

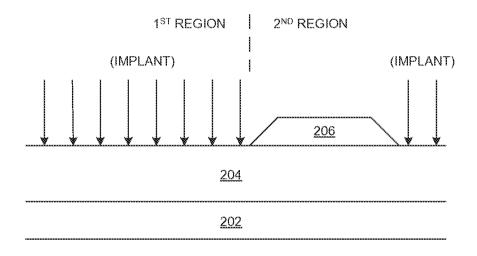

[0022] In block 106 of Figure 1A, with reference also to Figure 3, the field oxide layer 206 is removed from around the first mask 208, thereby defining the first (active) region and the second (termination) region. The field oxide layer 206 remains in the second region. The first mask 208 can then be removed.

[0023] An n-type dopant can then be implanted and driven into the first region and into the second region around the remaining field oxide layer 206 as shown in Figure 3. A high-quality gate oxide layer 409 (Figure 4) is formed after etching out the oxide formed during the drive and subsequent surface clean.

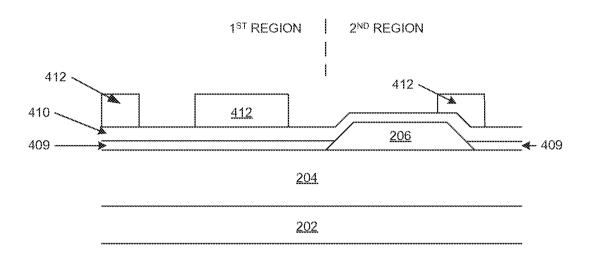

[0024] In block 108 of Figure 1A, with reference also to Figure 4, a polysilicon layer 410 is deposited over the first and second regions.

[0025] In block 110, a second mask 412 is formed over the polysilicon layer 410. The second mask 412 includes a number of mask elements separated by gaps, as shown in Figure 4.

[0026] In block 112 of Figure 1A, with reference also to Figure 5, the polysilicon layer 410 and the gate oxide layer 409 are removed from around the second mask 412 to form openings (e.g., the opening 514) in the polysilicon layer 410 in the first region, thereby exposing the epitaxial layer 204.

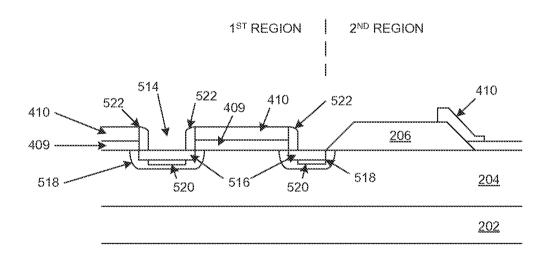

[0027] In block 114 of Figure 1A, an n-type dopant source region 516 and a p-type dopant body region 518 are formed in the epitaxial layer 204 through the opening 514 and other such openings, as shown in Figure 5. More specifically, in one embodiment, the body region 518 is formed by introducing a p-type dopant (e.g., boron) by ion implantation into the region defined by the opening 514. A succeeding drive completes formation of the body region 518. Next, a shallow n-type dopant (e.g., arsenic) is introduced through the opening 514 to form the source region 516.

[0028] In block 116 of Figure 1B, at this particular point in the process, spacers 522 are formed on each side of the opening 514 by deposition and etch-back of an oxide layer of suitable thickness. As shown in Figure 5, the spacers are in contact with the polysilicon layer 410 and also in contact with the source region 516. Next, a p-type (p+) dopant implant (e.g., boron) is used to form the implant region 520 below the source region 516, using the spacers 522 to define the boundaries of the implant region 520. The spacers 522 offset the source region 516 and implant region 520 relative to one another and prevent the implant region 520 from diffusing beyond the edge of the source region 516, which would increase the device's threshold voltage.

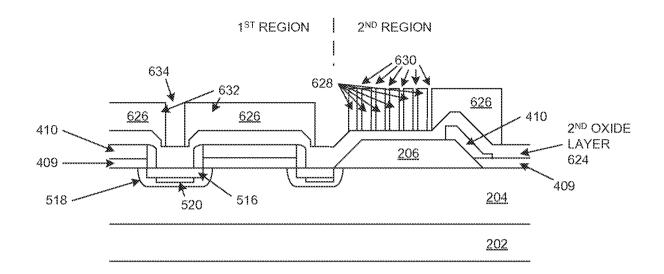

[0029] In block 118 of Figure 1B, with reference also to Figure 6, after the second mask 412 (Figure 4) is removed, a second oxide layer 624 (e.g., a low-temperature oxide (LTO) layer) is deposited over the first region and the second region.

[0030] In block 120 of Figure 1B, a third mask 626 is formed over the first region and over the second region. In the second (termination) region, the third mask 626 includes mask elements 628 that are separated by gaps 630.

[0031] In one embodiment, the gaps 630 in the third mask 626 are uniformly sized and uniformly spaced. That is, in one embodiment, the width of each of the gaps 630 in the second region is approximately the same (within design and manufacturing tolerances), and the width of each of the mask elements 628 in the second region is approximately the same (within design and manufacturing tolerances). In one such embodiment, each of the gaps 630 is between approximately 0.5 and 0.8 microns in width, and each of the mask elements 628 has a width of approximately 1.8 microns.

[0032] As described below, the third mask 626 is used to form field rings in the termination region of the device. The field rings, and hence the mask elements 628 and gaps 630, do not have to be uniformly sized and spaced. In general, the dimensions (width and spacing) of the mask elements 628 and gaps 630 are chosen so that the field rings are formed close enough to each other to allow depletion to proceed laterally from the active region to the field ring closest to the active region, then to the next closest field ring, and so on.

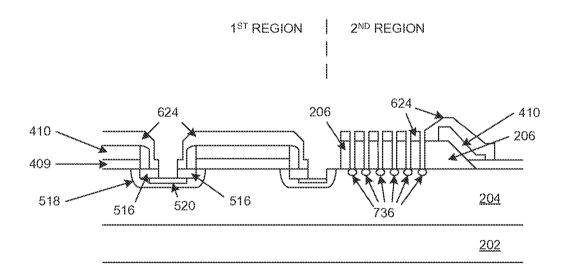

[0033] In block 122 of Figure 1B, with reference to Figure 7, parts of the second oxide layer 624 in the second region and parts of the field oxide layer 206 in the second region that are exposed through the gaps 630 are removed, thereby exposing the epitaxial layer 204 in the second region through those gaps.

[0034] In block 124, a p-type dopant is deposited (e.g., implanted and driven) into the epitaxial layer 204 in the second region through the resulting gaps in the field oxide layer 206 and the second oxide layer 624 (corresponding to the gaps 630), thereby forming field rings 736 for the MISFET. The field rings 736 can be formed in this manner before or after the third mask is removed. The p-type implant-and-drive is chosen so as to obtain a field ring junction depth that achieves the specified breakdown voltage for the high-voltage

device. In one embodiment, a metal field plate (not shown) is connected to each field ring (e.g., there is a field plate per field ring).

[0035] In one embodiment, based on the mask dimensions mentioned above, the width of each of the field rings 736 is about the same as the width of the gaps 630, and are separated from each other by a distance about the same as the width of the mask elements 628. As mentioned above, the field rings 736 do not have to be uniformly sized and spaced.

[0036] With reference back to Figure 6, the third mask 626 also includes mask elements 632 over the first region. The mask elements 632 are separated by gaps (e.g., the gap 634) that are critically aligned to the openings in the polysilicon layer 410 (e.g., the opening 514 of Figure 5) in the first region.

[0037] In block 126 of Figure 1B, parts of the second oxide layer 624 and the source region 516 in the first region that are exposed through the gaps (e.g., the gap 634) are removed, thereby also exposing the implant region 520 as shown in Figure 7.

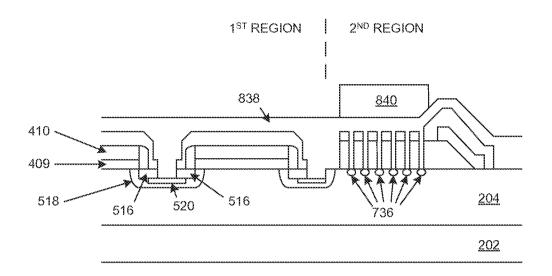

[0038] In block 128 of Figure 1B, with reference to Figure 8, after the third mask 626 (Figure 6) is removed, a metal layer 838 is deposited over the first region and the second region, in contact with the source region 516 and the implant region 520.

[0039] In block 130 of Figure 1C, a fourth mask 840 is formed over the metal layer 838.

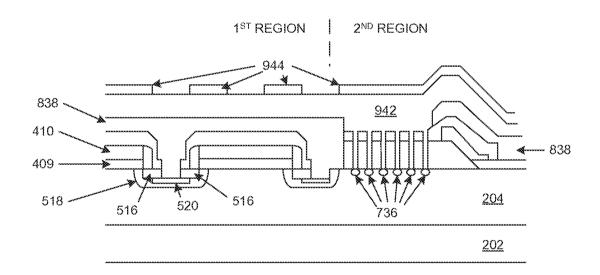

[0040] In block 132 of Figure 1C, with reference also to Figure 9, the metal layer 838 is removed from areas around the fourth mask 840.

[0041] In block 134, after the fourth mask 840 is removed, a passivation layer 942 is deposited over the first region and the second region. In the second region, the passivation layer 942 extends into the gaps between the remaining portions of the first oxide layer 206 and the second oxide layer 624, above the field rings 736.

[0042] In block 136, a fifth mask 944 is formed over the passivation layer 942.

[0043] In block 138 of Figure 1C, with reference also to Figure 10, the passivation layer 942 is removed from around the fifth mask to form source bond pad regions (e.g., the region 1046) and gate bond pad regions (e.g., the region 1048) for the device.

[0044] Thus, in embodiments according to the present invention, a high-voltage MISFET (e.g., MOSFET) can be manufactured using only five masks: the masks of block 104 (the active mask 208), block 110 (the poly mask 412), block 120 (the contact mask 626), block 130 (the metal mask 840), and block 136 (the passivation mask 944), used in that order.

[0045] Relative to conventional processes, the number of masks is reduced, from six masks to five masks, thus reducing manufacturing costs and increasing yield.

[0046] The foregoing descriptions of specific embodiments of the present invention have been presented for purposes of illustration and description. They are not intended to be exhaustive or to limit the invention to the precise forms disclosed, and many modifications and variations are possible in light of the above teaching. The embodiments were chosen and described in order to best explain the principles of the invention and its practical application, to thereby enable others skilled in the art to best utilize the invention and various embodiments with various modifications as are suited to the particular use contemplated. It is intended that the scope of the invention be defined by the claims appended hereto and their equivalents.

# **CLAIMS**

5

10

15

20

25

30

What is claimed is:

1. A process used in fabricating a metal-insulator-semiconductor field-effect transistor (MISFET), said process comprising:

depositing a second oxide layer over a first region and a second region of a structure, said second region comprising a first oxide layer between said second oxide layer and an epitaxial layer, said first region having formed therein a first-type dopant source region, a second-type dopant body region, and a second-type dopant implant region, said first region corresponding to an active region of said MISFET and said second region corresponding to a termination region of said MISFET;

forming a mask over said second region, said mask comprising a first plurality of mask elements separated by gaps;

removing parts of said second oxide layer and said first oxide layer that are exposed through said gaps, thereby exposing said epitaxial layer; and

depositing second-type dopant into said epitaxial layer through openings formed by said removing parts of said second oxide layer and said first oxide layer, thereby forming field rings for said MISFET.

- 2. The process of Claim 1, wherein said mask further comprises a second plurality of mask elements over said first region, said mask elements in said second plurality separated by a gap, said process further comprising removing parts of said second oxide layer and said first-type dopant source region that are exposed through said gap, thereby also exposing said second-type dopant implant region.

- 3. The process of Claim 2, further comprising:

depositing a metal layer over said first and second regions after said exposing said second-type dopant implant region;

forming a second mask over said metal layer; and

removing said metal layer from areas around said second mask, said metal layer in contact with said first-type dopant source region and said second-type dopant implant region.

4. The process of Claim 3, further comprising forming a passivation layer over said first and second regions, said passivation layer extending into said openings formed by said removing parts of said second oxide layer and said first oxide layer.

5. The process of Claim 1, further comprising, prior to said depositing said second oxide layer:

depositing a polysilicon layer over at least said first region;

35

40

45

50

55

60

removing a portion of said polysilicon layer to expose an area of said first region in which said first-type dopant source region, said second-type dopant body region, and said second-type dopant implant region are subsequently formed; and

after forming said first-type dopant source region and said second-type dopant body region, and before forming said second-type dopant implant region, forming a spacer in contact with a remaining portion of said polysilicon layer and also in contact with said first-type dopant source region.

- 6. The process of Claim 1, wherein said gaps are uniformly sized and uniformly spaced.

- 7. The process of Claim 1, wherein each of said gaps is between approximately 0.5 and 0.8 microns in width, and wherein each of said mask elements has a width of approximately 1.8 microns.

8. The MISFET fabricated by the process of Claim 1.

9. A method for fabricating a metal-insulator-semiconductor field-effect transistor (MISFET), said method comprising:

depositing a first oxide layer over an epitaxial layer of a structure;

forming a first mask over said first oxide layer, said first mask defining a second region corresponding to a termination region of said MISFET, said first oxide layer removed from around said first mask to define a first region corresponding to an active region of said MISFET;

after removing said first mask, depositing a polysilicon layer over said first region and said second region;

65

70

75

80

85

90

95

forming a second mask over said polysilicon layer, said polysilicon layer removed from around said second mask to form an opening in said polysilicon layer in said first region, thereby exposing said epitaxial layer, wherein a first-type dopant source region, a second-type dopant body region, and a second-type dopant implant region are formed in said epitaxial layer through said opening;

after said second mask is removed, depositing a second oxide layer over said first region and said second region;

forming a third mask over said second region, said third mask comprising a first plurality of mask elements separated by gaps, wherein parts of said second oxide layer and said first oxide layer that are exposed through said gaps are removed, thereby exposing said epitaxial layer, wherein further second-type dopant is deposited into said epitaxial layer through openings formed by removing said parts of said second oxide layer and said first oxide layer, thereby forming field rings for said MISFET;

after said third mask is removed, depositing a metal layer over said first region and said second region;

forming a fourth mask over said metal layer, said metal layer removed from areas around said fourth mask;

after said fourth mask is removed, depositing a passivation layer over said first region and said second region; and

forming a fifth mask over said passivation layer, said passivation layer removed from around said fifth mask to form source and gate bond pad regions for said MISFET.

- 10. The method of Claim 9, wherein said third mask further comprises a second plurality of mask elements over said first region, said mask elements in said second plurality separated by a gap, said method further comprising removing parts of said second oxide layer and said first-type dopant source region that are exposed through said gap, thereby also exposing said second-type dopant implant region.

- 11. The method of Claim 9, further comprising, after forming said first-type dopant source region and said second-type dopant body region, and before forming said second-

type dopant implant region, forming spacers on each side of said opening, said spacers in contact with a remaining portion of said polysilicon layer and also in contact with said first-type dopant source region.

100

115

120

125

- 12. The method of Claim 9, wherein said gaps in said third mask are uniformly sized and uniformly spaced.

- 13. The method of Claim 9, wherein each of said gaps in said third mask is betweenapproximately 0.5 and 0.8 microns in width, and wherein each of said mask elements has a width of approximately 1.8 microns.

- 14. The MISFET fabricated by the process of Claim 9.

- 15. A method for fabricating a metal-insulator-semiconductor field-effect transistor (MISFET), said method comprising:

removing a first oxide layer of a structure from around a first mask to define a first region corresponding to an active region of said MISFET and to expose an epitaxial layer underlying said first oxide layer, said first mask covering a second region corresponding to a termination region of said MISFET;

after removing said first mask and depositing a polysilicon layer over said first and second regions, removing said polysilicon layer from an area in said first region that is not covered by a second mask, thereby forming an opening in said polysilicon layer and exposing said epitaxial layer, wherein a first-type dopant source region, a second-type dopant body region, and a second-type dopant implant region are formed in said epitaxial layer through said opening;

after removing said second mask and depositing a second oxide layer over said first and second regions, removing said first oxide layer and said second oxide layer from areas in said second region that are exposed through gaps in a third mask, thereby exposing said epitaxial layer in said second region, wherein further second-type dopant is deposited into said epitaxial layer in said second region through openings formed by said removing said first oxide layer and said second oxide layer from areas in said second region, thereby forming field rings for said MISFET;

after removing said third mask and depositing a metal layer over said first and second regions, removing said metal layer from around a fourth mask; and

after removing said fourth mask and depositing a passivation layer over said first and second regions, removing said passivation layer from around a fifth mask to form source and gate bond pad regions for said MISFET.

- 135

16. The method of Claim 15, further comprising removing parts of said second oxide layer and said first-type dopant source region that are exposed through a gap in said third mask over said first region, thereby also exposing said second-type dopant implant region.

- 17. The method of Claim 15, further comprising, after forming said first-type dopant source region and said second-type dopant body region, and before forming said second-type dopant implant region, forming spacers on each side of said opening, said spacers in contact with a remaining portion of said polysilicon layer and also in contact with said first-type dopant source region.

145

130

- 18. The method of Claim 15, wherein said gaps in said third mask are uniformly sized and uniformly spaced.

- 19. The method of Claim 15, wherein each of said gaps in said third mask is between approximately 0.5 and 0.8 microns in width, and wherein each of said mask elements has a width of approximately 1.8 microns.

- 20. The MISFET fabricated by the process of Claim 15.

FIG. 1A

FIG. 1B

FIG. 1C

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

International application No. **PCT/US2015/034465**

#### A. CLASSIFICATION OF SUBJECT MATTER

H01L 21/336(2006.01)i, H01L 29/78(2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

# B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols) H01L 21/336; H01L 21/331; H01L 21/8222; H01L 29/78; H01L 23/58; H01L 21/265

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Korean utility models and applications for utility models

Japanese utility models and applications for utility models

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) eKOMPASS(KIPO internal) & Keywords: active, termination region, planar junction, mask, reduction, ring, FET and high-voltage

#### C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                         | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 2011-0284953 A1 (TAO LONG et al.) 24 November 2011<br>See abstract, paragraphs [0029]-[0053], claim 14 and figures 3, 13-19.            | 1-20                  |

| A         | US 6162695 A (JEI-FENG HWANG et al.) 19 December 2000<br>See abstract, column 3, line 35 – column 4, line 29, claim 1 and figures 5-8.     | 1-20                  |

| A         | US 6445054 B1 (TATJANA TRAIJKOVIC et al.) 03 September 2002<br>See abstract, column 3, line 6 – column 4, line 3, claim 1 and figure 2.    | 1-20                  |

| A         | US 5474946 A (JANARDHANAN S. AJIT et al.) 12 December 1995<br>See abstract, column 3, line 6 – column 4, line 40, claim 1 and figures 1-7. | 1-20                  |

| A         | US 2011-0193158 A1 (SAMUEL ANDERSON et al.) 11 August 2011 See abstract, paragraphs [0076]-[0082], claim 1 and figures 4A-4E.              | 1-20                  |

|           |                                                                                                                                            |                       |

|           |                                                                                                                                            |                       |

|           |                                                                                                                                            |                       |

| *   | Special categories of cited documents:                                    | "T" | later document published after the international filing date or priority |

|-----|---------------------------------------------------------------------------|-----|--------------------------------------------------------------------------|

| "A" | document defining the general state of the art which is not considered    |     | date and not in conflict with the application but cited to understand    |

|     | to be of particular relevance                                             |     | the principle or theory underlying the invention                         |

| "E" | earlier application or patent but published on or after the international | "X" | document of particular relevance; the claimed invention cannot be        |

|     | filing date                                                               |     | considered novel or cannot be considered to involve an inventive         |

| "L" | document which may throw doubts on priority claim(s) or which is          |     | step when the document is taken alone                                    |

|     | cited to establish the publication date of another citation or other      | "Y" | document of particular relevance; the claimed invention cannot be        |

|     | special reason (as specified)                                             |     | considered to involve an inventive step when the document is             |

| "O" | document referring to an oral disclosure, use, exhibition or other        |     | combined with one or more other such documents, such combination         |

|     | means                                                                     |     | being obvious to a person skilled in the art                             |

| "P" | document published prior to the international filing date but later       | "&" | document member of the same patent family                                |

Date of the actual completion of the international search

31 August 2015 (31.08.2015)

Date of mailing of the international search report

31 August 2015 (31.08.2015)

Name and mailing address of the ISA/KR

than the priority date claimed

International Application Division Korean Intellectual Property Office 189 Cheongsa-ro, Seo-gu, Daejeon Metropolitan City, 35208, Republic of Korea

Further documents are listed in the continuation of Box C.

Facsimile No. +82-42-472-7140

Authorized officer

CHOI, Sang Won

Telephone No. +82-42-481-8291

See patent family annex.

# INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No.

PCT/US2015/034465

| Patent document cited in search report | Publication<br>date | Patent family member(s)                                                                                                            | Publication<br>date                                                                            |

|----------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| US 2011-0284953 A1                     | 24/11/2011          | CN 102254944 A<br>US 8581336 B2                                                                                                    | 23/11/2011<br>12/11/2013                                                                       |

| US 6162695 A                           | 19/12/2000          | None                                                                                                                               |                                                                                                |

| US 6445054 B1                          | 03/09/2002          | EP 1076363 A2<br>EP 1076363 A3<br>GB 2355110 A                                                                                     | 14/02/2001<br>30/07/2003<br>11/04/2001                                                         |

| US 5474946 A                           | 12/12/1995          | GB 2298086 A<br>JP 08-250512 A<br>US 5783474 A                                                                                     | 21/08/1996<br>27/09/1996<br>21/07/1998                                                         |

| US 2011-0193158 A1                     | 11/08/2011          | US 2008-0036015 A1<br>US 2009-0233415 A1<br>US 2011-0193176 A1<br>US 7944018 B2<br>US 8129252 B2<br>US 8716829 B2<br>US 8736019 B2 | 14/02/2008<br>17/09/2009<br>11/08/2011<br>17/05/2011<br>06/03/2012<br>06/05/2014<br>27/05/2014 |