(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6735117号

(P6735117)

(45) 発行日 令和2年8月5日(2020.8.5)

(24) 登録日 令和2年7月15日(2020.7.15)

(51) Int.Cl.

F 1

HO3K 19/173 (2006.01)

HO3K 19/177 (2020.01)HO3K 19/173 130

HO3K 19/177

請求項の数 5 (全 30 頁)

(21) 出願番号 特願2016-40568 (P2016-40568)

(22) 出願日 平成28年3月3日 (2016.3.3)

(65) 公開番号 特開2016-167808 (P2016-167808A)

(43) 公開日 平成28年9月15日 (2016.9.15)

審査請求日 平成31年2月18日 (2019.2.18)

(31) 優先権主張番号 特願2015-40855 (P2015-40855)

(32) 優先日 平成27年3月3日 (2015.3.3)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 池田 隆之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 上妻 宗広

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 青木 健

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 工藤 一光

最終頁に続く

(54) 【発明の名称】電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のロジックエレメントと、

前記第1のロジックエレメントと隣接して配置された第2のロジックエレメントと、

前記第1のロジックエレメントに対応する第1のスイッチマトリクスアレイと、

前記第2のロジックエレメントに対応する第2のスイッチマトリクスアレイと、

複数の配線と、を有し、

前記第1のスイッチマトリクスアレイは、前記複数の配線から一以上を選択して、前記第1のロジックエレメントに、第1の信号を入力する構成を有し、

前記第2のスイッチマトリクスアレイは、前記複数の配線から一以上を選択して、前記第2のロジックエレメントに、第2の信号を入力する構成を有し、

前記第1のロジックエレメントは、前記第1の信号の一部又は全部を用いてコンテキスト選択信号を生成する構成を有し、

前記第1のロジックエレメントの出力は、前記第2のロジックエレメントに電気的に接続され、前記第1のロジックエレメントは前記第2のロジックエレメントに前記コンテキスト選択信号を供給する構成を有する電子機器。

## 【請求項 2】

第1のロジックエレメントと、

前記第1のロジックエレメントと隣接して配置された第2のロジックエレメントと、

前記第1のロジックエレメントに対応する第1のスイッチマトリクスアレイと、

10

20

前記第2のロジックエレメントに対応する第2のスイッチマトリクスアレイと、複数の配線と、を有し、

前記第1のスイッチマトリクスアレイは、前記複数の配線から一以上を選択して、前記第1のロジックエレメントに、第1の信号を入力する構成を有し、

前記第2のスイッチマトリクスアレイは、前記複数の配線から一以上を選択して、前記第2のロジックエレメントに、第2の信号を入力する構成を有し、

前記第1のロジックエレメントは、前記第1の信号の一部又は全部を用いてコンテキスト選択信号を生成する構成を有し、

前記第1のロジックエレメントの出力は、前記第2のロジックエレメント及び前記第2のスイッチマトリクスアレイに電気的に接続され、前記第1のロジックエレメントは前記第2のロジックエレメント及び前記第2のスイッチマトリクスアレイにそれぞれ前記コンテキスト選択信号を供給する構成を有する電子機器。

#### 【請求項3】

請求項1又は2において、

前記コンテキスト選択信号は、クロック信号を用いて生成される、電子機器。

#### 【請求項4】

請求項1乃至3のいずれか一において、

チャネル形成領域に酸化物半導体を有するトランジスタを有する、電子機器。

#### 【請求項5】

請求項1乃至4のいずれか一において、

前記第1のスイッチマトリクスアレイ又は前記第2のスイッチマトリクスアレイは、チャネル形成領域に酸化物半導体を有するトランジスタを有する、電子機器。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

この開示物は電子機器に関する。

##### 【背景技術】

##### 【0002】

瞬時にコンフィギュレーションを切り替えることのできるマルチコンテキスト方式のリコンフィギャラブルデバイスが提案されている（例えば、非特許文献1）。例えば、特許文献1乃至5には、酸化物半導体をチャネル形成領域に有するトランジスタ（以下、O Sトランジスタ）を用いた、マルチコンテキスト方式のリコンフィギャラブルな回路として機能するフィールドプログラマブルゲートアレイ（F P G A）が提案されている。

##### 【0003】

特許文献1乃至5では、コンフィギュレーションデータを記憶するコンフィギュレーションメモリとして、O Sトランジスタのメモリを利用することで、コンフィギュレーションメモリを高密度に配置することができ、コンフィギュレーションメモリの集積度を高めることができることが開示されている。そのことは、マルチコンテキスト方式は好適である。

##### 【0004】

また、マルチコンテキスト方式では、複数のコンフィギュレーションメモリのセットに非稼動のコンフィギュレーションデータを保持するため、データ保持のための消費電力の少ないO Sメモリは好適である。また、ブースティング効果により、配線間スイッチのスイッチング速度が向上することもある。

##### 【先行技術文献】

##### 【特許文献】

##### 【0005】

【特許文献1】米国特許出願公開第2013/0293263号明細書

【特許文献2】米国特許出願公開第2013/0314124号明細書

【特許文献3】米国特許出願公開第2014/0159771号明細書

10

20

30

40

50

【特許文献4】米国特許出願公開第2014/0368235号明細書

【特許文献5】米国特許出願公開第2015/0008958号明細書

【非特許文献】

【0006】

【非特許文献1】H. M. Waidyasoorya et al., "Implementation of a Partially Reconfigurable Multi-Context FPGA Based on Asynchronous Architecture", IEICE TRANSACTIONS on Electronics, Vol. E92-C, pp. 539-549, 2009

【発明の概要】

10

【発明が解決しようとする課題】

【0007】

この開示物では、新規な電子機器等が提供される。例えば、より高速で駆動できる電子機器等、より消費電力の少ない電子機器等、より集積度の高い電子機器等、より付加価値の大きな電子機器等、より利用しやすい電子機器等、より低コストな電子機器等、より汎用性の高い電子機器等、よりユーザーの要求を満たすことのできる電子機器等、より効率的な利用が可能である電子機器等のいずれか1つあるいは複数が開示されている。これらの電子機器等の解決できる課題については、実施の形態を参照することができる。

【課題を解決するための手段】

【0008】

20

開示される電子機器の一は、複数のスイッチマトリクスアレイと、スイッチマトリクスアレイのそれぞれに対応する複数のロジックエレメント（論理要素）と、複数の配線とを有し、複数のスイッチマトリクスアレイのそれぞれが、複数の配線のうちの一以上の配線を選択して、一以上の配線を伝送する信号を、対応するロジックエレメントに入力可能である構成を有し、複数のロジックエレメントの一のロジックエレメントは、一のロジックエレメントに対応する一のスイッチマトリクスアレイを除くその他の複数のスイッチマトリクスアレイと一のロジックエレメントを除く複数のロジックエレメントの一にコンテキスト選択信号を供給することができ、コンテキスト選択信号は、一のロジックエレメントに入力される複数の配線の一以上を伝送する信号を用いて生成されることを特徴とする電子機器である。あるいは、第1のロジックエレメントと、第2のロジックエレメントと、第1のロジックエレメントに対応する第1のスイッチマトリクスアレイと、第2のロジックエレメントに対応する第2のスイッチマトリクスアレイと、複数の配線と、を有し、第1のスイッチマトリクスアレイが、複数の配線から一以上を選択して、第1のロジックエレメントに、第1の信号を入力する構成と、第2のスイッチマトリクスアレイが、複数の配線から一以上を選択して、第2のロジックエレメントに、第2の信号を入力する構成と、第1のロジックエレメントが、第1の信号の一部あるいは全部を用いてコンテキスト選択信号を生成する構成と、コンテキスト選択信号が、第2のロジックエレメントと第2のスイッチマトリクスアレイの少なくとも一方に入力される構成と、を有する電子機器である。あるいは、第1の論理ブロックと、第2の論理ブロックと、を有し、第1の論理ブロックと第2の論理ブロックは、コンテキスト選択信号によって、論理構成を変更可能であり、第1の論理ブロックは、入力された第1の信号に含まれる第1のコンテキスト決定データを用いて、第1のコンテキスト選択信号を生成し、第1のコンテキスト選択信号に応じた第1の論理構成で第1の演算をおこない、第1の演算の結果を含む第2の信号を出力する構成が可能であり、第2の論理ブロックは、第2の信号に含まれる第2のコンテキスト決定データを用いて、第2のコンテキスト選択信号を生成し、第2のコンテキスト選択信号に応じた第2の論理構成で第2の演算をおこなう構成が可能であることを特徴とする電子機器である。なお、第1の論理ブロックは、複数のロジックエレメントと複数のスイッチマトリクスアレイを有してもよい。また、上記の電子機器において、コンテキスト選択信号は、クロック信号を用いて生成されてもよい。また、上記の電子機器は、チャネル形成領域に酸化物半導体を有するトランジスタを有してもよい。

30

40

50

## 【発明の効果】

## 【0009】

上記のように、新規な電子機器等が開示されている。電子機器の詳細あるいは他の形態について以下に説明される。

## 【図面の簡単な説明】

## 【0010】

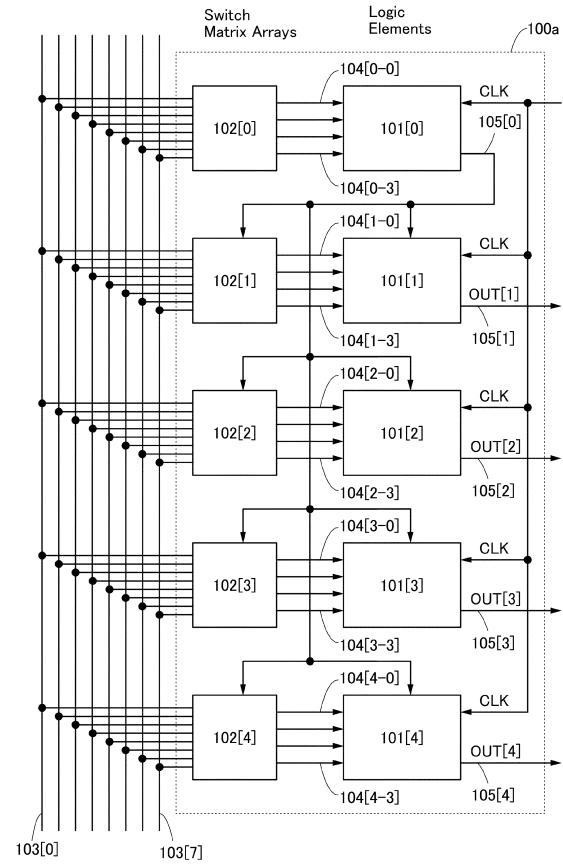

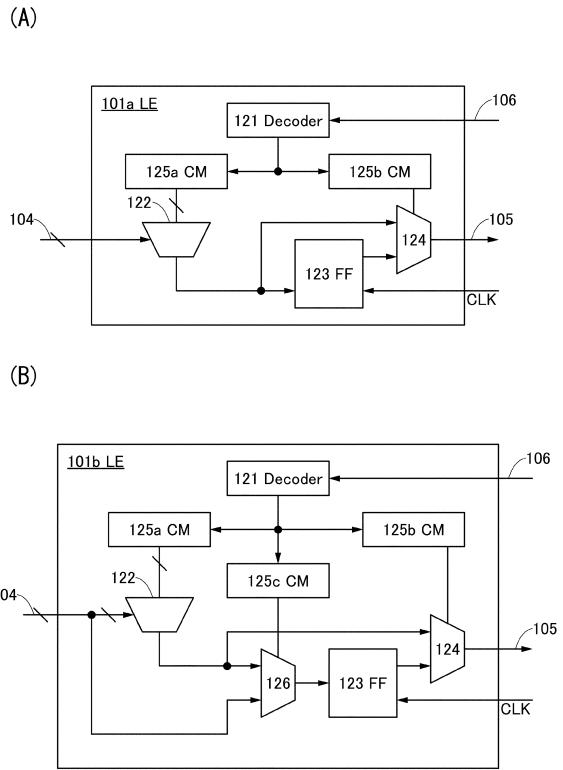

【図1】論理ブロックの構成例を説明するための図。

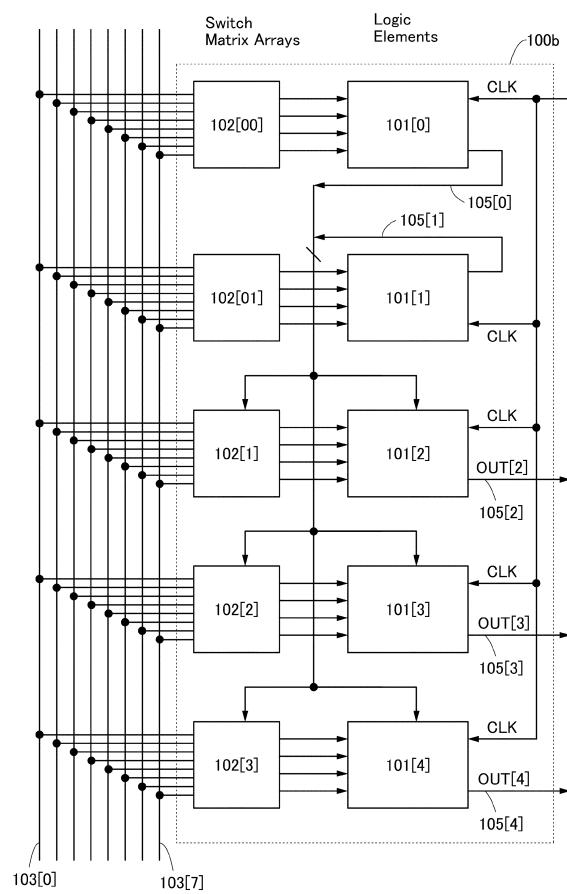

【図2】論理ブロックの構成例を説明するための図。

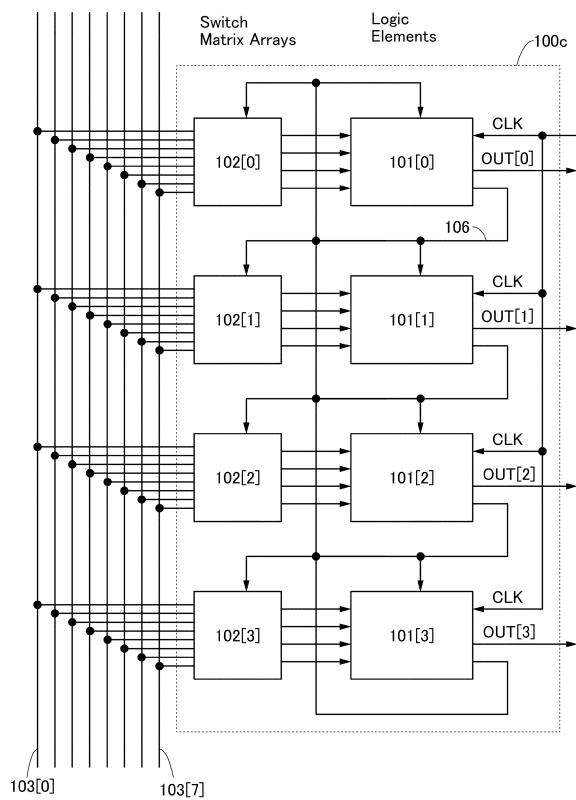

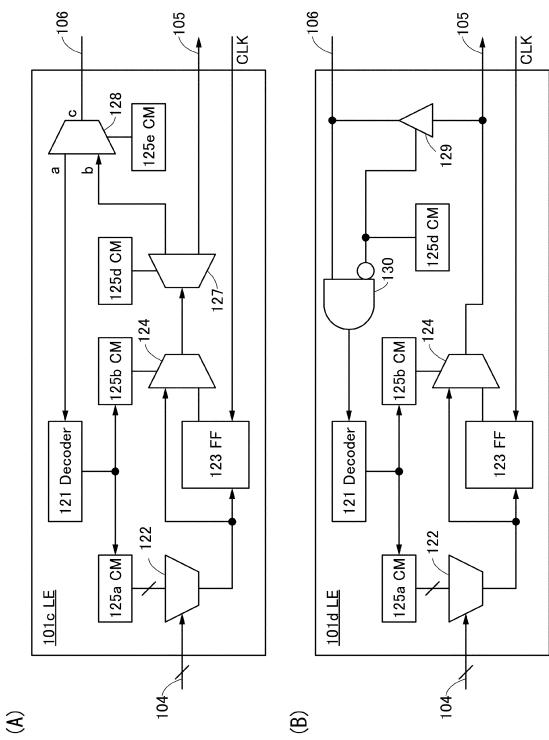

【図3】論理ブロックの構成例を説明するための図。

【図4】論理ブロックの構成例を説明するための図。

10

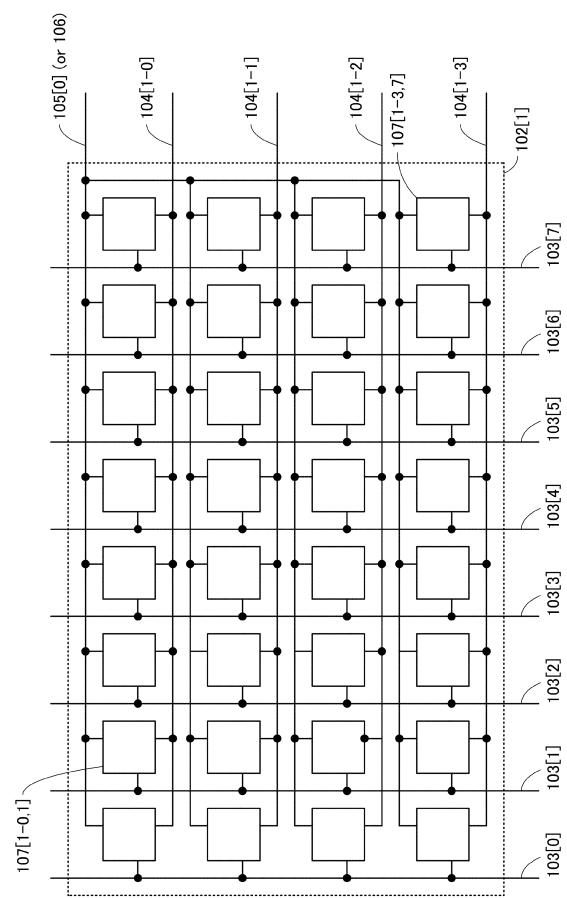

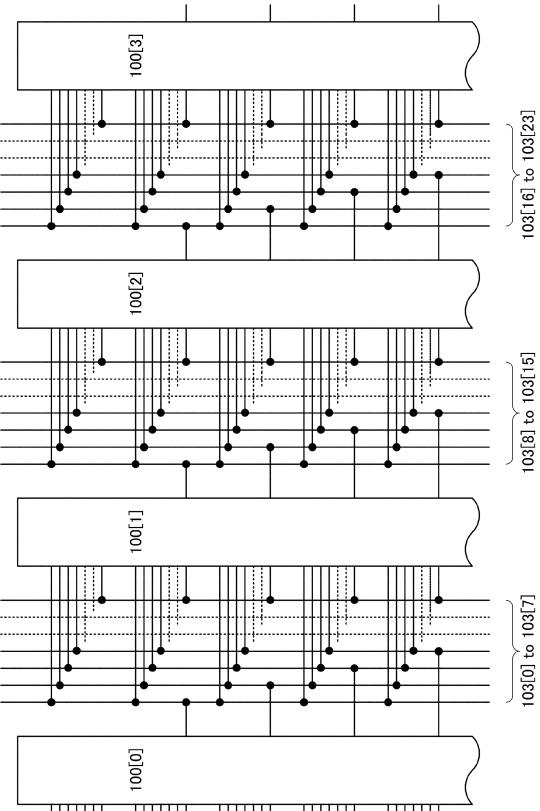

【図5】スイッチマトリクスアレイの構成例を説明するための図。

【図6】スイッチ回路の構成例を説明するための回路図。

【図7】スイッチ回路の構成例を説明するための回路図。

【図8】スイッチ回路の構成例を説明するための回路図。

【図9】デコーダの例を説明するための回路図。

【図10】ロジックエレメントの構成例を説明するためのブロック図。

【図11】ロジックエレメントの構成例を説明するためのブロック図。

【図12】電子機器の例を説明するためのブロック図。

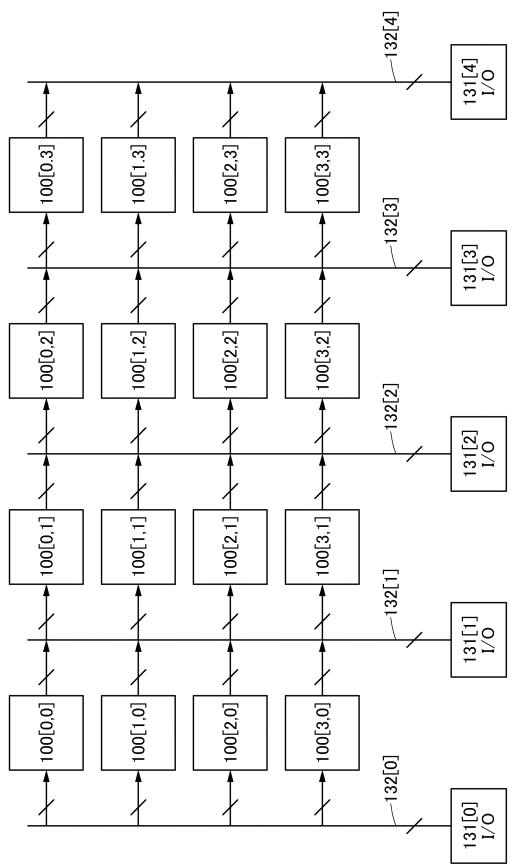

【図13】電子機器の例を説明するためのブロック図。

20

【図14】電子機器の例を説明するためのブロック図。

【図15】電子機器の例を説明するためのブロック図。

【図16】スイッチブロックの例を説明するための図。

【図17】電子機器の構造例を説明する断面図。

【図18】電子機器の構造例を説明する断面図。

【図19】電子機器の具体例。

## 【発明を実施するための形態】

## 【0011】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

30

## 【0012】

なお図面において、同一の要素又は同様な機能を有する要素、同一の材質の要素、あるいは同時に形成される要素等には同一の符号を付す場合があり、その繰り返しの説明は省略する場合がある。また、それぞれの実施の形態で開示された技術は他の実施の形態に自由に適用できる。

## 【0013】

## (実施の形態1)

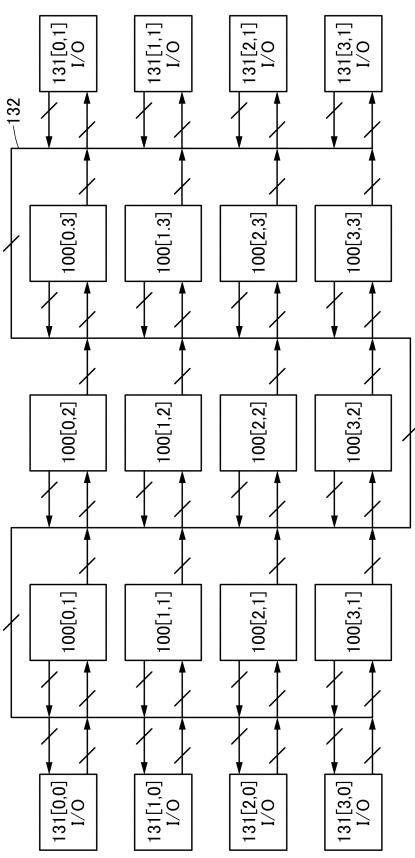

本発明の一態様の電子機器の構成について、図1を用いて説明する。図1は、電子機器に含まれる論理ブロック100aの構成を示す図である。

40

## 【0014】

図1に示す論理ブロック100aは、複数のロジックエレメント(ロジックエレメント101[0]乃至ロジックエレメント101[4])、複数のスイッチマトリクスアレイ(スイッチマトリクスアレイ102[0]乃至スイッチマトリクスアレイ102[4])、複数の配線(配線103[0]乃至配線103[7])を有する。

## 【0015】

配線103[0]乃至配線103[7]を伝送する信号は、スイッチマトリクスアレイ102[0]乃至スイッチマトリクスアレイ102[4]を経由して、ロジックエレメント101[0]乃至ロジックエレメント101[4]に入力可能である。図1の例では、各スイッチマトリクスアレイ102には、8つの配線103の信号を入力可能であり、各ス

50

イッチマトリクスアレイ 102 に記憶されているコンフィギュレーションデータおよび実行中のコンテキストにより、そのうちの 4つまでの信号が選択され、対応するロジックエレメント 101 に配線 104 を介して供給される。例えば、ロジックエレメント 101 [1] には、配線 104 [1 - 0] 乃至配線 104 [1 - 3] を介して、信号が入力される。

#### 【0016】

ロジックエレメント 101 では、記憶されているコンフィギュレーションデータおよび実行中のコンテキスト、あるいはクロック信号 CLK 等に応じて演算処理がなされ、結果が出力される。ここでは、ロジックエレメント 101 [1] 乃至ロジックエレメント 101 [4] は演算結果を出力信号 OUT [1] 乃至出力信号 OUT [4] として、配線 105 [1] 乃至配線 105 [4] に出力する。<sup>10</sup> 図示されていないが、出力信号 OUT [1] 乃至出力信号 OUT [4] は、スイッチマトリクスアレイ 102 (図示されていないものも含む) を介してロジックエレメント 101 (図示されていないものも含む) に供給されうる。出力信号 OUT [1] 乃至出力信号 OUT [4] が、間接的に配線 103 [0] 乃至配線 103 [7] に供給されることも可能である。また、ロジックエレメント 101 からの出力信号 OUT は 2 以上の配線に出力されてもよい。

#### 【0017】

これとは別に、ロジックエレメント 101 [0] でも同様に演算処理がなされるのであるが、出力 (コンテキスト選択信号) は、配線 105 [0] を介して、ロジックエレメント 101 [1] 乃至ロジックエレメント 101 [4]、スイッチマトリクスアレイ 102 [1] 乃至スイッチマトリクスアレイ 102 [4] に供給される。そして、ロジックエレメント 101 [1] 乃至ロジックエレメント 101 [4]、スイッチマトリクスアレイ 102 [1] 乃至スイッチマトリクスアレイ 102 [4] では、配線 105 [0] を介して受け取ったコンテキスト選択信号に応じて、コンフィギュレーションを変更し、指示されたコンテキストを実行する。<sup>20</sup>

#### 【0018】

図 1 の論理ブロック 100a で、複数のコンテキストを実行する例を説明する。ここでは、演算 A に引き続いで演算 B が実行される例を示す。すなわち、演算 A はコンテキスト A として、演算 B はコンテキスト B として、それぞれ実行される。したがって、演算 A が終了すると、コンテキストを変更する必要がある。<sup>30</sup>

#### 【0019】

ここでは、演算 A が終了すると、配線 103 [0] の電位が L (ロー) に、配線 103 [1] の電位が H (ハイ) になるものとする。例えば、いずれかのロジックエレメント 101 (図示されていないものも含む) あるいは入力端子 (図示されていない) から、そのような信号が供給されるように設計あるいは設定される。

#### 【0020】

コンテキスト選択信号は、ロジックエレメント 101 [0] で生成され、配線 105 [0] に出力される。例えば、(演算 A を実行するための) コンテキスト A が選択されるときには、配線 105 [0] の電位は L となるようにし、(演算 B を実行するための) コンテキスト B が選択されるときには、配線 105 [0] の電位は H となるように設定する。<sup>40</sup>

#### 【0021】

例えば、スイッチマトリクスアレイ 102 [0] は、少なくとも配線 103 [0] と配線 103 [1] の信号をロジックエレメント 101 [0] に供給するよう設定される。もちろん、スイッチマトリクスアレイ 102 [0] は、これらの配線以外の信号もロジックエレメント 101 [0] に供給するよう設定されてもよい。

#### 【0022】

ただし、ロジックエレメント 101 [0] では、配線 103 [0] の電位が L で配線 103 [1] の電位が H (演算 A が終了したことを意味する) であれば、(ロジックエレメント 101 [0] に入力されるその他の信号に関わらず) 配線 105 [0] に H を出力し、配線 103 [0] と配線 103 [1] の電位がこれら以外の場合には、(ロジックエレメ<sup>50</sup>

ント 101[0] に入力されるその他の信号に関わらず) 配線 105[0] に L を出力するように設定される。

#### 【0023】

配線 105[0] の電位は、演算 A が終了していない状態では、L である。ロジックエレメント 101[1] 乃至ロジックエレメント 101[4]、スイッチマトリクスアレイ 102[1] 乃至スイッチマトリクスアレイ 102[4] は、コンテキスト A に設定されている。演算 A が終了し、配線 105[0] の電位が H となると、ロジックエレメント 101[1] 乃至ロジックエレメント 101[4]、スイッチマトリクスアレイ 102[1] 乃至スイッチマトリクスアレイ 102[4] は、コンテキスト B に設定が変更され、演算 B が実行される。

10

#### 【0024】

このように、コンテキストを切り替えるための信号がローカルに生成されるため、コンテキストの切り替えが極めて高速で実行できる。例えば、1 クロック程度の時間で切り替えを完了できる。

#### 【0025】

図 2 には他の例を示す。図 2 に示す論理ブロック 100b は、2 つのロジックエレメント 101[0] とロジックエレメント 101[1] の出力信号が 2 ビットのコンテキスト選択信号となる点で図 1 に示す論理ブロック 100a と異なる。すなわち、ロジックエレメント 101[0] の出力信号とロジックエレメント 101[1] の出力信号は、それぞれ、配線 105[0] と配線 105[1] に供給される。

20

#### 【0026】

ロジックエレメント 101[2] 乃至ロジックエレメント 101[4]、スイッチマトリクスアレイ 102[2] 乃至スイッチマトリクスアレイ 102[4] では、2 ビットのコンテキスト選択信号に応じて、コンテキストを選択できる。すなわち、最大で 4 つのコンテキストを選択できる。同様に、コンテキスト選択信号を供給するロジックエレメント 101 を増やせば、それに応じてコンテキスト選択信号のビット数を高めることができ、選択できるコンテキスト数も増加する。

#### 【0027】

同様なことは、コンテキスト選択信号を生成するロジックエレメント 101 の複数の配線から信号が出力されることでも実行できる。例えば、ロジックエレメント 101[0] が 2 本の配線にそれぞれ 1 ビットの信号を出力することで、上記と同じく、2 ビットのコンテキスト選択信号を出力できる。

30

#### 【0028】

図 2 の論理ブロック 100b では、最大 4 つのコンテキストを選択できるので、演算 A、演算 B、演算 C、演算 D を順におこなうとすれば、例えば、演算 A をおこなうときは、配線 103[0] と配線 103[1] の電位がともに L、演算 B をおこなうときは、配線 103[0] の電位が L、配線 103[1] の電位が H、演算 C をおこなうときは、配線 103[0] の電位が H、配線 103[1] の電位が L、演算 D をおこなうときは、配線 103[0] と配線 103[1] の電位がともに H、となるように設定する。

40

#### 【0029】

そして、例えば、ロジックエレメント 101[0] は、配線 103[0] の信号が L であれば、配線 105[0] に L を出力し、配線 103[0] の信号が H であれば、配線 105[0] に H を出力するように設定される。また、ロジックエレメント 101[1] は、配線 103[1] の信号が L であれば、配線 105[1] に L を出力し、配線 103[1] の信号が H であれば、配線 105[1] に H を出力するように設定される。

#### 【0030】

配線 105[0] と配線 105[1] の信号は、ロジックエレメント 101[2] 乃至ロジックエレメント 101[4]、スイッチマトリクスアレイ 102[2] 乃至スイッチマトリクスアレイ 102[4] でデコードされ、デコードされた信号に基づいて、ロジックエレメント 101[2] 乃至ロジックエレメント 101[4]、スイッチマトリクスアレ

50

イ 1 0 2 [ 2 ] 乃至スイッチマトリクスアレイ 1 0 2 [ 4 ] のコンテキストが変更される。

。

**【 0 0 3 1 】**

図 1 や図 2 の例では、コンテキスト選択信号を生成するロジックエレメント 1 0 1 が固定されていたが、例えば、図 3 に示すように、ロジックエレメント 1 0 1 [ 0 ] 乃至ロジックエレメント 1 0 1 [ 3 ] のいずれかがコンテキスト選択信号を生成する構成でもよい。

**【 0 0 3 2 】**

図 3 に示す論理ブロック 1 0 0 c では、ロジックエレメント 1 0 1 [ 0 ] 乃至ロジックエレメント 1 0 1 [ 3 ] のそれぞれは、演算結果を出力信号 OUT [ 0 ] 乃至出力信号 OUT [ 3 ] として出力するか、コンテキスト選択信号として、コンテキスト選択信号線 1 0 6 に出力する。 10

**【 0 0 3 3 】**

具体的には、ロジックエレメント 1 0 1 [ 0 ] 乃至ロジックエレメント 1 0 1 [ 3 ] のいずれかがコンテキスト選択信号を生成し、コンテキスト選択信号線 1 0 6 にコンテキスト選択信号を出力する。なお、コンテキスト選択信号が 2 ビット以上の場合には、ロジックエレメント 1 0 1 [ 0 ] 乃至ロジックエレメント 1 0 1 [ 3 ] の複数がコンテキスト選択信号を出力し、また、コンテキスト選択信号線 1 0 6 はコンテキスト選択信号のビット数に応じて複数存在する。あるいは、ロジックエレメント 1 0 1 [ 0 ] 乃至ロジックエレメント 1 0 1 [ 3 ] のいずれかが、2 ビット以上のコンテキスト選択信号を、ビット数に応じた数のコンテキスト選択信号線 1 0 6 に出力すればよい。 20

**【 0 0 3 4 】**

また、コンテキスト選択信号を生成するロジックエレメント 1 0 1 は、コンテキスト選択信号線 1 0 6 からの信号を受け取らないように設計あるいは設定される。あるいは、コンテキスト選択信号線 1 0 6 からの信号を受け取るように設計されている場合には、コンテキスト選択信号に関わらず、同じコンフィギュレーションを維持するようなコンフィギュレーションデータが入力されていてもよい。

**【 0 0 3 5 】**

ロジックエレメント 1 0 1 [ 0 ] 乃至ロジックエレメント 1 0 1 [ 3 ] のその他は、コンテキスト選択信号を出力しない。さらに、コンテキスト選択信号線 1 0 6 からの信号を受け取るように設計あるいは設定される。すなわち、コンテキスト選択信号を出力するか否かで、ロジックエレメント 1 0 1 の回路構成や論理構成を設定すればよい。 30

**【 0 0 3 6 】**

図 3 に示すような構成によって、ロジックエレメント 1 0 1 への入力信号線の数が 4 から 5 に増えたものと同様の効果があり、ロジックエレメント 1 0 1 でより複雑な演算ができるが、その一方で、入力信号線の接続先が限定されることによりレイアウト面積の増大が抑制される。

**【 0 0 3 7 】**

図 3 に示す論理ブロック 1 0 0 c では、コンテキスト選択信号を受け入れる端子と出力する端子が異なるように表現されている。しかし、実際の回路では、1 つの端子の機能を入力にも出力にも使用できる。例えば、図 4 のような回路を構成してもよい。 40

**【 0 0 3 8 】**

図 4 に示す論理ブロック 1 0 0 d では、それぞれのロジックエレメント 1 0 1 は、コンテキスト選択信号線 1 0 6 と 1 つの端子で接続されているように表現されている。そして、コンテキスト選択信号を受け入れるか出力するかは、内部の回路構成によって決定できる。具体例はロジックエレメント 1 0 1 の構成例として後述される。

**【 0 0 3 9 】**

以上の例では、コンテキスト選択信号は、配線 1 0 3 を伝送する信号のみから生成されるが、その他の信号から生成されてもよい。例えば、一以上の配線 1 0 3 を伝送する信号とクロック信号とから生成されてもよい。

**【 0 0 4 0 】**

10

20

30

40

50

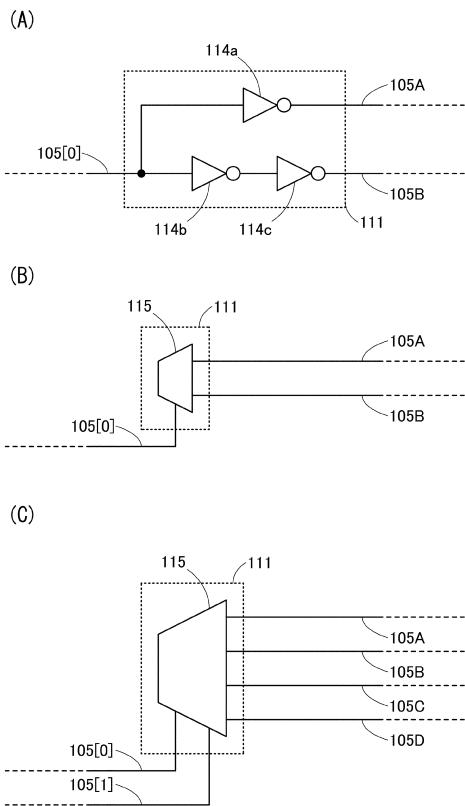

スイッチマトリクスアレイ 102 の例を図 5 に示す。図 5 に示されるスイッチマトリクスアレイ 102 [1] は、配線 103 [0] 乃至配線 103 [7] および配線 104 [1 - 1] 乃至配線 104 [1 - 4] に重なるように設けられる。配線 104 [1 - 1] 乃至配線 104 [1 - 4] は、ロジックエレメント 101 [1] に信号を供給する。

#### 【0041】

スイッチマトリクスアレイ 102 [1] は、マトリクス状に配置された、複数のスイッチ回路 107 を有する。各スイッチ回路 107 は対応する配線 103 と配線 104 の電気的な接続や切断を受け持つ。例えば、スイッチ回路 107 [1 - 0, 1] は、配線 103 [1] と配線 104 [1 - 0]との間の電気的な接続や切断を受け持ち、スイッチ回路 107 [1 - 3, 7] は、配線 103 [7] と配線 104 [1 - 3] との間の電気的な接続や切断を受け持つ。スイッチ回路 107 の動作は、配線 105 [0] (あるいはコンテキスト選択信号線 106) を伝送するコンテキスト選択信号に応じて変更できる。

#### 【0042】

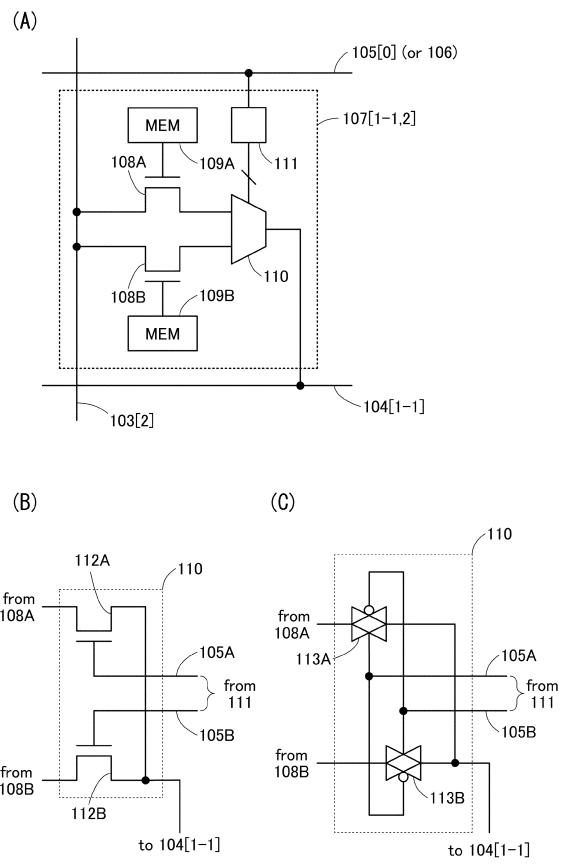

配線 103 [2] と配線 104 [1 - 1] との間の電気的な接続や切断を受け持つスイッチ回路 107 [1 - 1, 2] は、例えば、図 6 (A) に示されるように、パストランジスタ 108A とパストランジスタ 108B、メモリ 109A とメモリ 109B、2 入力のマルチプレクサ 110、デコーダ 111 を有する。図 6 (A) に示されるスイッチ回路 107 [1 - 1, 2] では、2 つのコンテキスト (コンテキスト A とコンテキスト B) のいずれかを選択し、実行できる。デコーダ 111 からは、1 以上の配線を介してマルチプレクサ 110 に信号が供給される。

#### 【0043】

マルチプレクサ 110 は、例えば、図 6 (B) に示すような、選択トランジスタ 112A と選択トランジスタ 112B を有する回路で表現できる。あるいは、図 6 (C) に示すように、相互に異なる動きをする 1 対のトランスマニアゲート (トランスマニアゲート 113A とトランスマニアゲート 113B) を用いても表現できる。なお、これらの例では、デコーダ 111 からの 2 本の配線 (制御信号線 105A、制御信号線 105B) によって、選択トランジスタ 112A と選択トランジスタ 112B やトランスマニアゲート 113A とトランスマニアゲート 113B が制御される。

#### 【0044】

配線 105 [0] (あるいはコンテキスト選択信号線 106) を伝送する信号は、デコーダ 111 でデコードされ、デコーダ 111 は、コンテキスト選択信号に応じて、制御信号線 105A と制御信号線 105B のいずれか一方が H、他方が L となるような電位を制御信号線 105A と制御信号線 105B に供給する。

#### 【0045】

例えば、配線 105 [0] の電位が L であれば、制御信号線 105A の電位が H、制御信号線 105B の電位が L となり、配線 105 [0] の電位が H であれば、制御信号線 105A の電位が L、制御信号線 105B の電位が H となるような電位が、デコーダ 111 から供給される。

#### 【0046】

図 6 (C) のように、トランスマニアゲート 113A とトランスマニアゲート 113B を用いる場合は、制御信号線 105A と制御信号線 105B の電位が上記のような関係にあると以下の点で有利である。

#### 【0047】

すなわち、1 つのトランスマニアゲートには、制御のために H と L の双方の信号を入力するが、デコーダ 111 からは、常に H と L の双方の信号が出力されている。したがって、それらの電位をトランスマニアゲート 113A とトランスマニアゲート 113B の制御に用いることができるので、より高速な動作が可能である。

#### 【0048】

パストランジスタ 108A とパストランジスタ 108B は、それぞれ、メモリ 109A とメモリ 109B の出力 (これはそれぞれに記憶されている 1 ビットデータと等価である)

10

20

30

40

50

によって、導通が制御される。

#### 【0049】

マルチプレクサ110として、図6(B)に示す回路を採用した場合、パストランジスタ108Aのソースとドレインは、配線103[2]と選択トランジスタ112Aのソース(あるいはドレイン)の間にあるような回路構成であるが、選択トランジスタ112Aのソースとドレインが、配線103[2]とパストランジスタ108Aのソース(あるいはドレイン)の間にあるように回路を設計してもよい。図6(C)に示す回路を採用した場合でも同様である。

#### 【0050】

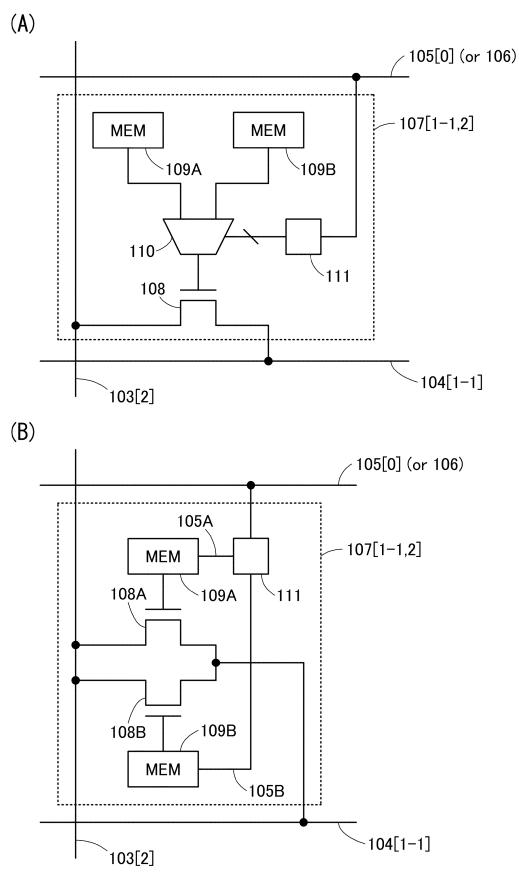

図7(A)には、変形例を示す。図7(A)に示すスイッチ回路107[1-1, 2]では、メモリ109Aとメモリ109Bの出力信号がマルチプレクサ110で選択され、それがパストランジスタ108のゲートに入力される構成を有する。マルチプレクサ110は、図6(A)の場合と同様に、デコーダ111の出力信号により制御される。

10

#### 【0051】

図7(B)には、他の変形例を示す。図7(B)に示すスイッチ回路107[1-1, 2]では、メモリ109Aとメモリ109Bの動作が制御信号線105A、制御信号線105Bを伝送するデコーダ111の出力信号により制御される。例えば、制御信号線105Aには、メモリ109Aの動作を有効にする信号が、制御信号線105Bには、メモリ109Bの動作を無効にする信号が供給される。

20

#### 【0052】

以上は、コンテキスト選択信号が1ビットの場合であるが、2ビット以上に適用するには、図6(A)あるいは図7(A)のマルチプレクサの入力端子数を増加させねばよい。あるいは、図6(B)、図6(C)あるいは図7(B)において、3以上の制御信号線を介して、その配線の数に見合うトランジスタやトランスファーゲート、メモリ等にデコーダ111から制御信号が供給されてもよい。

#### 【0053】

例えば、コンテキスト選択信号が2ビットの場合を図8に示す。ここで、スイッチ回路107[1-1, 2]は、パストランジスタ108A乃至パストランジスタ108D、メモリ109A乃至メモリ109D、選択トランジスタ112A乃至選択トランジスタ112Dを有し、パストランジスタ108Aと選択トランジスタ112Aが、配線103[2]と配線104[1-1]の間に直列にあるように回路が設計される。選択トランジスタ112A乃至選択トランジスタ112Dの代わりにトランスファーゲートあるいはそれと同等な機能を有する回路を用いてもよい。

30

#### 【0054】

配線105[0]と配線105[1]を伝送する2ビットのコンテキスト選択信号は、デコーダ111でデコードされ、制御信号線105A乃至制御信号線105Dのいずれか一のみがH、他がLとなるような電位が、制御信号線105A乃至制御信号線105Dに供給される。選択トランジスタ112A乃至選択トランジスタ112Dは、制御信号線105A乃至制御信号線105Dの電位に応じ、いずれか一のみがオンとなり、他はオフとなる。

40

#### 【0055】

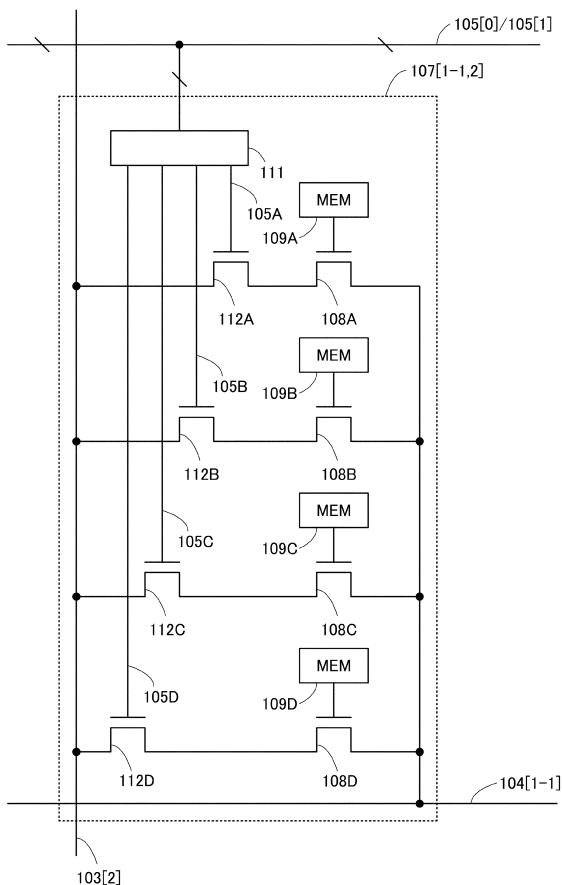

デコーダ111は、例えば、図9(A)に示すように、インバータ114a乃至インバータ114cを有する。なお、インバータ114bとインバータ114cを設けない構造でもよい。あるいは、インバータ114aに直列に、さらに2個のインバータを追加してもよい。つまり、配線105[0]がデコーダ111内で分岐したあと、制御信号線105Aにつながる配線に設けられるインバータの数(0を含む)と制御信号線105Bにつながる配線に設けられるインバータの数(0を含む)の差が奇数となるような回路であればよい。この結果、制御信号線105Aと制御信号線105Bの電位は、一方がHであれば他方がLとなる。

#### 【0056】

50

また、別の例では、図9( B )に示すように、デコーダ111は、1入力のデマルチブレクサ115を有する。デマルチブレクサ115は、配線105[0]の電位に応じて、一方がHであれば他方がLとなるような電位を制御信号線105Aと制御信号線105Bに供給する。また、別の例では、図9( C )に示すように、デコーダ111は、2入力のデマルチブレクサ115を有する。デマルチブレクサ115は、配線105[0]の電位と配線105[1]の電位に応じて、いずれか一のみがHで、他がLとなるような電位を制御信号線105A乃至制御信号線105Dに供給する。

#### 【0057】

以上の例では、コンテキスト選択信号は、ロジックエレメント101とスイッチマトリクスアレイ102の双方に入力されたが、いずれか一方にのみ入力される構成でもよい。また、デコーダ111は、ロジックエレメント101と対応するスイッチマトリクスアレイ102の双方に、それぞれ、設けられてもよいし、いずれか一方にのみ設けて、デコーダ111の出力信号(制御信号)が他方にも供給されるようにしてもよい。あるいは、デコーダ111を複数のロジックエレメント101、複数のスイッチマトリクスアレイ102に1つの割合で設けて、デコーダの設けられていないものに制御信号を供給してもよい。

#### 【0058】

次に、ロジックエレメント101について説明する。一般的に、ロジックエレメント101は1以上のルックアップテーブル、1以上のフリップフロップ(FF)、1以上のマルチブレクサ(MUX)を有する。なお、一般にルックアップテーブルはメモリを有する。

#### 【0059】

ルックアップテーブルをロジックゲートとして機能させるために、コンフィギュレーションデータが、ルックアップテーブルに入力される。換言すれば、ルックアップテーブルから出力される信号のロジックレベル(例えば「H/L」)は、コンフィギュレーションデータとルックアップテーブルへ入力される信号のロジックレベルに応じて決定される。

#### 【0060】

ルックアップテーブルから出力される信号はフリップフロップに入力される。ロジックエレメント101に含まれているフリップフロップから出力される信号は、他のロジックエレメント101に含まれているフリップフロップに入力されることがある。フリップフロップはこれらの入力信号を保持する機能を有する。

#### 【0061】

マルチブレクサの駆動を制御するために、コンフィギュレーションデータがマルチブレクサに入力される。マルチブレクサは、コンフィギュレーションデータに応じて、ルックアップテーブルあるいはフリップフロップから出力される信号のいずれかを選択する機能を有する。マルチブレクサによって選択された信号はロジックエレメント101から出力される。

#### 【0062】

また、ルックアップテーブルやマルチブレクサを制御するコンフィギュレーションデータは、コンテキスト選択信号によって、必要なものを選択することができる。

#### 【0063】

図10( A )はロジックエレメント101の具体的な構成例を示す。図10( A )のロジックエレメント101aは、デコーダ121、マルチブレクサ122、フリップフロップ123、マルチブレクサ124、マルチブレクサ122のためのコンフィギュレーションデータを格納するコンフィギュレーションメモリ125a、マルチブレクサ124のためのコンフィギュレーションデータを格納するコンフィギュレーションメモリ125bを有する。マルチブレクサ122とコンフィギュレーションメモリ125aが上述のルックアップテーブルに相当する。デコーダ121は、図9( A )乃至図9( C )で説明したデコーダ111と同じあるいは同様なものである。

#### 【0064】

マルチブレクサ122で実行される論理動作は、コンフィギュレーションメモリ125aに格納されているコンフィギュレーションデータおよびコンテキスト選択信号線106か

10

20

30

40

50

ら供給されるコンテキスト選択信号に応じて変わる。コンテキスト選択信号は、デコーダ 121 でデコードされる。デコーダ 121 の出力に応じて、コンフィギュレーションメモリ 125a、コンフィギュレーションメモリ 125b から、マルチプレクサ 122、マルチプレクサ 124 に、それぞれロードされるデータが変化する。

#### 【0065】

その結果、マルチプレクサ 122 は、例えば、一のコンテキストでは、AND ゲートとして動作するが、別のコンテキストでは、OR ゲートとして動作する、というように、その機能を変化させることができる。

#### 【0066】

マルチプレクサ 122 は、配線 104 から供給される複数の入力信号に対応した出力信号を生成する。フリップフロップ 123 は、マルチプレクサ 122 で生成された出力信号を保持し、クロック信号 CLK に同期してマルチプレクサ 122 の出力信号に対応する出力信号を出力する。10

#### 【0067】

マルチプレクサ 122 およびフリップフロップ 123 から出力される信号はマルチプレクサ 124 に入力される。マルチプレクサ 124 は、コンフィギュレーションメモリ 125b に格納されているコンフィギュレーションデータとコンテキスト選択信号に応じてこれら 2 つの出力信号のうちの一つを選択し、出力する機能を有する。マルチプレクサ 124 から出力される信号は配線 105 に供給される。

#### 【0068】

図 10 (B) は、ロジックエレメント 101 の別の具体的な構成例を示す。図 10 (B) のロジックエレメント 101b は、図 10 (A) のロジックエレメント 101a とマルチプレクサ 126 とマルチプレクサ 126 のためのコンフィギュレーションデータを格納するコンフィギュレーションメモリ 125c を有する点で異なる。20

#### 【0069】

マルチプレクサ 122 から出力される信号と他のロジックエレメント 101 から出力される信号（配線 104 から供給される）がマルチプレクサ 126 に入力される。マルチプレクサ 126 は、コンフィギュレーションメモリ 125c に格納されているコンフィギュレーションデータに応じてこれら 2 つの信号のうちの一つを選択し、出力する機能を有する。30

#### 【0070】

図 10 (B) のロジックエレメント 101b では、フリップフロップ 123 は、マルチプレクサ 126 から出力された信号を保持し、クロック信号 CLK に同期してマルチプレクサ 126 から出力された信号に対応する出力信号を出力する。

#### 【0071】

図 11 (A) には、図 4 で示される論理ブロック 100d に使用するためのロジックエレメント 101 の例を示す。図 11 (A) に示すロジックエレメント 101c は、図 10 (A) に示すロジックエレメント 101a をベースにしたものである。図 11 (A) に示すロジックエレメント 101c は、マルチプレクサ 124 の出力が、2 出力のデマルチプレクサ 127 で配線 105 と 2 入力のマルチプレクサ 128 のいずれかに出力される。デマルチプレクサ 127 としては、図 6 (B) あるいは図 6 (C) に示すマルチプレクサ 110 と同等な回路を用いてもよい。40

#### 【0072】

なお、マルチプレクサ 128 は 3 つの端子（端子 a、端子 b、端子 c）を有するが、端子 a と端子 b のうち、端子 c と接続していないものには、一定の電位が出力されるものとする。例えば、2 つのコンテキストが切り替えられる方式（コンテキスト選択信号が 1 ビット）で、コンテキスト選択信号の初期値が L である場合には、その一定の電位を L としてもよい。同様に、デマルチプレクサ 127 においても、選択されないほうの端子には、電位 L が与えられてもよい。

#### 【0073】

50

20

30

40

50

ロジックエレメント 101c がコンテキスト選択信号を生成する場合には、マルチブレクサ 124 の出力（コンテキスト選択信号）はデマルチブレクサ 127 とマルチブレクサ 128 を経由してコンテキスト選択信号線 106 に出力される。すなわち、この場合には、端子 b と端子 c が接続される。端子 a は端子 c と接続されないので、端子 a には L の電位が供給される。端子 a の出力はデコーダ 121 でデコードされて、ロジックエレメント 101c は初期のコンテキストに維持される。

#### 【0074】

ロジックエレメント 101c がコンテキスト選択信号を生成しない場合には、マルチブレクサ 124 の出力はデマルチブレクサ 127 を経由して配線 105 に出力される。また、コンテキスト選択信号線 106 とマルチブレクサ 128 を経由して、コンテキスト選択信号がデコーダ 121 に入力される。すなわち、この場合には、端子 a と端子 c が接続される。端子 b は端子 c と接続されないので、端子 b には L の電位が供給される。

10

#### 【0075】

デマルチブレクサ 127、マルチブレクサ 128 の動作は、それぞれ、コンフィギュレーションメモリ 125d、コンフィギュレーションメモリ 125e に記憶されているコンフィギュレーションデータによって設定されている。

#### 【0076】

マルチブレクサ 128 では、コンテキスト選択信号線 106 が、デコーダ 121、デマルチブレクサ 127 の出力端子のいずれと接続するかが決定される。ここで、コンテキスト選択信号線 106 がデコーダ 121 と接続するのであれば、ロジックエレメント 101c は、コンテキスト選択信号を受け入れることができる。逆に、コンテキスト選択信号線 106 がデマルチブレクサ 127 の出力端子と接続するのであれば、ロジックエレメント 101c は、コンテキスト選択信号を出力することができる。

20

#### 【0077】

なお、ロジックエレメント 101c が、コンテキスト選択信号を受け入れるか出力するかのいずれかの状態しかとらないのであれば、コンフィギュレーションメモリ 125d、コンフィギュレーションメモリ 125e に記憶されているコンフィギュレーションデータは実質的に同じものである（すなわち、一方が他方と全く同じか、全く反対かのいずれかである）ので、コンフィギュレーションメモリ 125d とコンフィギュレーションメモリ 125e を、1 つのコンフィギュレーションメモリと、必要によっては、そのメモリの出力を反転させる回路とで代替することもできる。

30

#### 【0078】

なお、マルチブレクサ 124 の出力が仮にコンテキスト選択信号であったとし、それが配線 105 に供給されたとしても、その先に存在するスイッチ（スイッチマトリクスアレイ内のスイッチ）によって、他のロジックエレメントが取り込まないようにすることができる。その場合には、デマルチブレクサ 127 は不要である。

#### 【0079】

そのような構成を有するロジックエレメントの例を図 11 (B) に示す。図 11 (B) に示されるロジックエレメント 101d は、トライステートバッファー 129 (あるいは、それと同等な機能を有する回路) と論理ゲート 130 を有する。論理ゲート 130 には、2 つの信号が入力される。論理ゲート 130 は、第 1 の入力にはそのままの信号が、第 2 の入力には反転された信号が入力される構成の AND ゲートと同等である。したがって、論理ゲート 130 は、第 1 の入力に反転した信号が、第 2 の入力にはそのままの信号が入力される NOR ゲートとも同等である。

40

#### 【0080】

ロジックエレメント 101d において、マルチブレクサ 124 の出力は、配線 105 に供給されるとともに、トライステートバッファー 129 にも供給される。トライステートバッファー 129 の出力はコンテキスト選択信号線 106 および論理ゲート 130 の一方の入力に供給される。論理ゲート 130 の他方の入力には、コンフィギュレーションメモリ 125d の出力が入力される。

50

**【0081】**

トライステートバッファー129は、コンフィギュレーションメモリ125dによって制御され、コンフィギュレーションメモリ125dの出力がHであれば、オンとなり、Lであればオフとなる。ここでは、このロジックエレメント101dが、コンテキスト選択信号を生成する場合には、コンフィギュレーションメモリ125dの出力がH、そうでない場合には、Lであるとする。

**【0082】**

例えば、コンフィギュレーションメモリ125dの出力がHの場合、トライステートバッファー129がオンであるので、配線105とコンテキスト選択信号線106と論理ゲート130の一方の入力には、マルチプレクサ124の出力（コンテキスト選択信号）が供給される。トライステートバッファー129の出力は、HかLか不明であるが、論理ゲート130の他方の入力にはHが入力されるので、論理ゲート130は常にLを出力する。したがって、トライステートバッファー129の出力によってコンテキストが変更されることはない。

10

**【0083】**

例えば、コンフィギュレーションメモリ125dの出力がLの場合、トライステートバッファー129がオフであるので、配線105にのみ、マルチプレクサ124の出力が供給される。また、コンテキスト選択信号線106を介して、他のロジックエレメントからコンテキスト選択信号が、論理ゲート130の一方の入力に供給される。論理ゲート130の他方の入力には、コンフィギュレーションメモリ125dの出力（L）が供給されるので、論理ゲート130は、コンテキスト選択信号線106の電位がHであればHを、LであればLを出力する。

20

**【0084】**

図11(B)のコンフィギュレーションメモリ125d、トライステートバッファー129、論理ゲート130の機能は、他の論理ゲートでも実現できる。例えば、第1乃至第4の端子を有し、第1の状態では、第1の端子と第3の端子が、第2の端子と第4の端子に、それぞれ接続され、第2の状態では、第1の端子が第4の端子と接続され、第3の端子と第2の端子は、他のいずれの端子とも接続されない論理ゲートでもよい。この場合、例えば、第1の端子とデコーダ121の入力とを接続し、第3の端子とマルチプレクサ124の出力とを接続し、第2の端子の電位をLとし、第4の端子とコンテキスト選択信号線106とを接続する。

30

**【0085】**

第1の状態では、デコーダ121の入力の電位はLとなり、マルチプレクサ124の出力はコンテキスト選択信号線106と接続される。第2の状態では、コンテキスト選択信号線106はデコーダ121の入力と接続される。マルチプレクサ124の出力は、第2の端子、第4の端子とも接続されないが、配線105とは第1の状態でも第2の状態でも接続されている。

**【0086】**

すなわち、第1の状態では、ロジックエレメントで生成したコンテキスト選択信号をコンテキスト選択信号線106に供給することが可能であり、第2の状態では、他のロジックエレメントで生成されたコンテキスト選択信号を受け入れて、コンテキストを変更し、演算結果を配線105に出力できる。

40

**【0087】**

なお、図10(A)、図10(B)、図11(A)あるいは図11(B)に示されるロジックエレメント101では、コンフィギュレーションデータによって使用可能なフリップフロップ123の型が決定される。特に、フリップフロップ123は、コンフィギュレーションデータにもよるが、D - フリップフロップ、T - フリップフロップ、JK - フリップフロップ、RS - フリップフロップのいずれかである。

**【0088】**

電子装置は、上記のような論理ブロック100a乃至論理ブロック100d、あるいはそ

50

れらと同等な機能を有するもの（これらを論理ブロック 100、という）のいずれか 1 あるいは 2 以上を複数組み合わせて用いられる。図 12 に示す例では、論理ブロック 100 [0] の出力信号が配線 103 [0] 乃至配線 103 [7] に供給される。論理ブロック 100 [1] には、配線 103 [0] 乃至配線 103 [7] を伝送する信号が供給され、論理ブロック 100 [1] の出力信号は配線 103 [8] 乃至配線 103 [15] に供給される。論理ブロック 100 [2] には、配線 103 [8] 乃至配線 103 [15] を伝送する信号が供給され、論理ブロック 100 [2] の出力信号は配線 103 [16] 乃至配線 103 [23] に供給される。論理ブロック 100 [3] には、配線 103 [16] 乃至配線 103 [23] を伝送する信号が供給される。

## 【0089】

10

図 12 のような構成を有する電子装置の駆動例を説明する。論理ブロック 100 [0] は、配線 103 [0] と配線 103 [1] にコンテキスト選択信号を生成するための電位を供給し、配線 103 [2] 乃至配線 103 [7] に演算に使用するためのデータを供給するとする。例えば、論理ブロック 100 [0] は、シリアルな信号列を解析して、ヘッダーを見つけ出し、ヘッダーの直後にあるコンテキスト選択信号を生成するための 2 ビットのデータ（コンテキスト決定データ）を抽出する機能を有する。そして、コンテキスト決定データに応じた電位を配線 103 [0] と配線 103 [1] に供給する。また、論理ブロック 100 [0] は、コンテキスト決定データに続く 6 ビットのデータを配線 103 [2] 乃至配線 103 [7] に供給する。コンテキスト決定データは上記のような H と L の組み合わせである。

20

## 【0090】

論理ブロック 100 [1] では、配線 103 [0] と配線 103 [1] の電位に基づいて、コンテキスト選択信号が生成され、論理ブロック 100 [1] 内のコンテキストが変更される。そして、配線 103 [2] 乃至配線 103 [7] の電位をもとに、演算がおこなわれ、配線 103 [8] 乃至配線 103 [15] に、演算結果が出力される。ここで、演算結果は、2 ビットのコンテキスト決定データと、次の演算に使用するための 6 ビットのデータよりなり、コンテキスト決定データは、配線 103 [8] と配線 103 [9] に出力され、その他のデータは、配線 103 [10] 乃至配線 103 [15] に出力される。このように、一の演算結果の中にコンテキスト決定データが含まれるようにすることで、次の論理ブロックでコンテキストが変更され、別の演算がなされる。そして、この例では、論理ブロック 100 [1] の出力が変化すると、それに応じてコンテキストも変化する。

30

## 【0091】

他の例を図 13 に示す。図 13 に示される電子装置は、論理ブロック 100 がマトリクス状に配置されている。例えば、論理ブロック 100 [0, 0] は、配線群 132 [0] から信号が供給され、配線群 132 [1] に出力する。また、配線群 132 [0] には、出入力回路 131 [0] から信号が供給される。配線群 132 は、複数の配線 103 から構成され、ここでは、1 つの配線群 132 は、32 本の配線 103 よりなる（すなわち、配線群 132 は 32 ビットである）とする。また、1 つの論理ブロック 100 は 8 ビットのデータを出力できる（すなわち、1 つの論理ブロック 100 から外部に出力できる配線 105 が 8 本ある）とする。

40

## 【0092】

例えば、配線群 132 [0] には、出入力回路 131 [0] から、シリアルな信号列が順次、入力される。この信号列には、6 ビット乃至 32 ビットのヘッダーと、それに続く 2 ビットのコンテキスト決定データと、演算に使用する 16 乃至 30 ビットのデータが含まれているとする。このようにヘッダーやデータのビット数は可変でもよい。

## 【0093】

左の 8 つの論理ブロック 100、すなわち、論理ブロック 100 [0, 0] 乃至論理ブロック 100 [3, 1] は、ヘッダーを見つけ出し、それに続くコンテキスト決定データ（第 1 のコンテキスト決定データ）と演算に使用するデータを配線群 132 [2] に供給す

50

る。

#### 【0094】

論理ブロック100[0,2]乃至論理ブロック100[3,2]では、第1のコンテキスト決定データによって、用いるコンテキストが決定され、これと演算に使用するデータを用いて演算がおこなわれる。ここで、論理ブロック100[0,2]乃至論理ブロック100[2,2]は、2ビットの第2のコンテキスト決定データと16ビットのデータを、論理ブロック100[3,2]は、2ビットの第3のコンテキスト決定データと4ビットのデータを配線群132[3]に供給するものとする。また、これとは別に、出入力回路131[3]が8ビットのデータを配線群132[3]に供給するものとする。

#### 【0095】

例えば、配線群132[3]は、配線103[3-0]乃至配線103[3-31]よりもなるものとする。ここで、論理ブロック100[0,2]、論理ブロック100[1,2]、論理ブロック100[2,2]、論理ブロック100[3,2]は、それぞれ、配線103[3-0]乃至配線103[3-7]、配線103[3-8]乃至配線103[3-15]、配線103[3-16]乃至配線103[3-23]、配線103[3-24]乃至配線103[3-31]に信号を出力可能であるとする。出入力回路131[3]は、配線103[3-0]乃至配線103[3-31]すべてに信号を供給できるものとする。

10

#### 【0096】

そして、第2のコンテキスト決定データは配線103[3-0]と配線103[3-1]に、16ビットのデータは配線103[3-2]乃至配線103[3-17]に、第3のコンテキスト決定データは配線103[3-26]と配線103[3-27]に、4ビットのデータは、配線103[3-28]乃至配線103[3-31]に、出入力回路131[3]が供給する8ビットのデータは配線103[3-18]乃至配線103[3-25]に、それぞれ供給されるとする。

20

#### 【0097】

そして、論理ブロック100[0,3]乃至論理ブロック100[2,3]のそれぞれは、配線群132[3]のうちの2本の配線（配線103[3-0]と配線103[3-1]）から第2のコンテキスト決定データを読み出し、それに付随するデータを用いて第1のコンテキストを実行する。つまり、論理ブロック100[0,3]乃至論理ブロック100[2,3]のそれれにおいて、コンテキスト選択信号を生成するロジックエレメント101（これらの論理ブロック100には、計3つ存在する）に、第2のコンテキスト決定データが供給されるように、対応するスイッチマトリクスアレイ102は、いずれも、配線103[3-0]と配線103[3-1]が、コンテキスト選択信号を生成するロジックエレメント101に電気的に接続するように設定されている。

30

#### 【0098】

なお、演算に用いるデータは、論理ブロック100[0,2]乃至論理ブロック100[2,2]が供給する16ビットのデータと、出入力回路131[3]が供給する8ビットのデータの一部（例えば、4ビットのデータ）である。

40

#### 【0099】

一方、論理ブロック100[3,3]は、配線群132[3]のうちの別の2本の配線（配線103[3-26]と配線103[3-27]）から第3のコンテキスト決定データを読み出し、それに付随するデータを用いて第2のコンテキストを実行する。このように、1つの電子機器の中で、同時に異なる領域で異なるコンテキストが実行される。また、コンテキストを実行する領域もユーザーが設定できる。

#### 【0100】

別の例では、論理ブロック100[0,2]が、第2のコンテキスト決定データと第3のコンテキスト決定データを供給することも可能である。この場合、第2のコンテキスト決定データと第3のコンテキスト決定データは、配線103[3-0]乃至配線103[3-7]のいずれかに供給される。

50

**【0101】**

上記において、第1のコンテキスト決定データ、第2のコンテキスト決定データ、第3のコンテキスト決定データは、互いに独立である。例えば、第1のコンテキスト決定データと第2のコンテキスト決定データは常に同じであるとは限らないし、常に異なるとも限らない。第1のコンテキスト決定データがある2ビットの値であるとき、必ず、第2のコンテキスト決定データが特定の2ビットの値となるわけではない。第1のコンテキスト決定データと第3のコンテキスト決定データでも同様である。また、これらから得られ、ロジックエレメント101から出力されるコンテキスト選択信号もそれぞれ互いに独立である。

**【0102】**

10

例えば、第2のコンテキスト決定データと第3のコンテキスト決定データは、論理ブロック100[0, 2]乃至論理ブロック100[3, 2]で実行された演算結果を反映する。

**【0103】**

図12に示される論理ブロック100では、信号は、左側から入力され右側に出力される。しかしながら、論理ブロック100の出力の一部は左側に出力されてもよい。例えば、論理ブロック100[1]の出力の一部は配線103[8]乃至配線103[15](の一部)に出力され、他は配線103[0]乃至配線103[7](の一部)に出力される構成でもよい。そうすることで、論理構成をより柔軟に構築できる。

**【0104】**

20

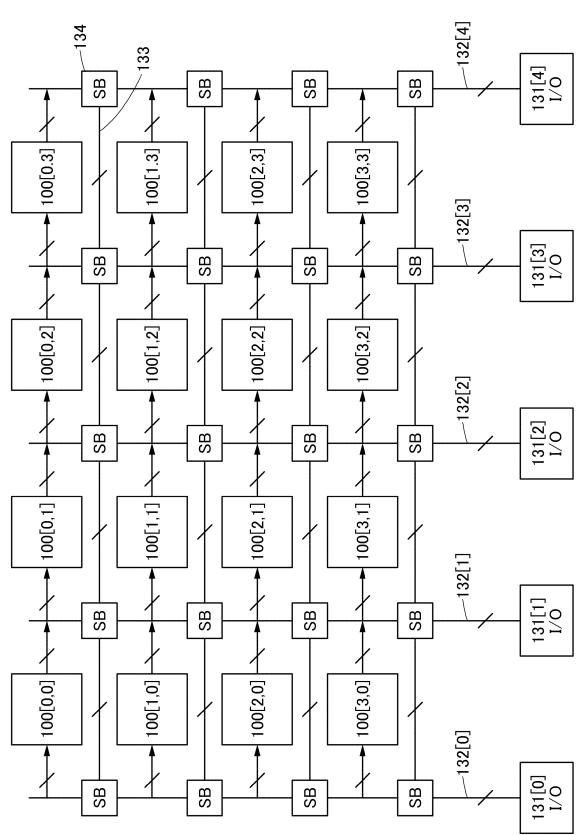

そのような構成を有する論理ブロック100を用いた電子機器の例を図14に示す。図14では、論理ブロック100および出入力回路131がマトリクス状に配置され、その間に配線群132が蛇行するように配置されている。配線群132には、さまざまな長さの配線が含まれていてもよい。詳細は特許文献2を参照できる。

**【0105】**

図15には、電子機器の別の例を示す。図15に示される電子機器は、図13に示される電子機器に、さらに、配線群132の間を結ぶことのできる配線群133と、配線群132と配線群133の交点にスイッチブロック134が追加されている。その結果、例えば、論理ブロック100[M, X]の出力を論理ブロック100[N, Y]に入力させることができ、配線リソースの利用効率を向上させることができる(ただし、XはYより大きく、MとNは、それぞれ、0、1、2、3のいずれかである)。

**【0106】**

30

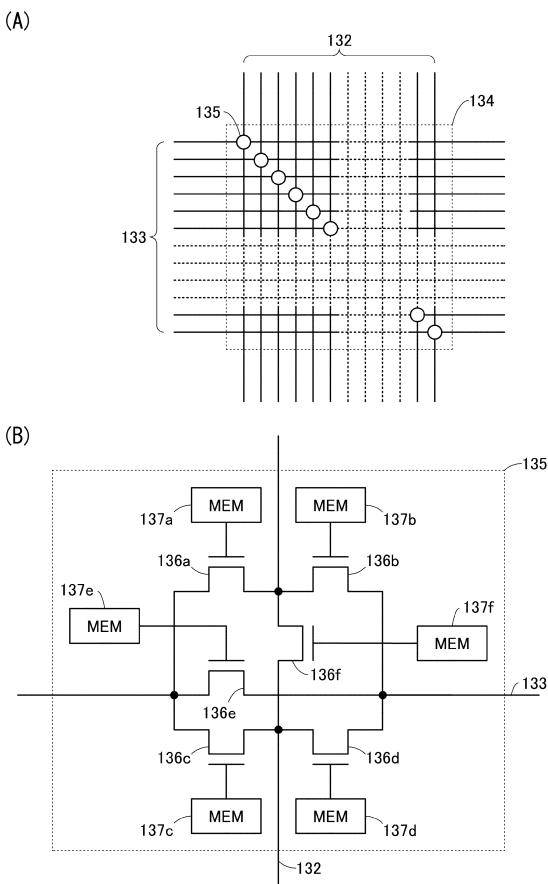

スイッチブロック134は、例えば、図16(A)に示すように、複数のクロススイッチエレメント135を有する。1つのクロススイッチエレメント135は、例えば、図16(B)に示すように、スイッチ136a乃至スイッチ136fと、その動作を制御するためのメモリ137a乃至メモリ137fを有する。スイッチ136a乃至スイッチ136fのそれぞれは、対応する2つの配線を接続あるいは切断する機能を有する。

**【0107】**

40

図16(B)に示されるクロススイッチエレメント135では、2つの配線間に1つのスイッチしか設けられていないが、マルチコンテキスト駆動できるように、2つの配線間に複数のスイッチ(と、それぞれに対応するメモリ)を有する構成としてもよい。また、各スイッチブロック134のコンテキスト選択信号は、隣接する論理ブロック100のいずれかが供給する構成でもよい。

**【0108】**

このように、マルチコンテキスト動作が実行可能なりコンフィギラブル回路を有する電子機器において、コンテキスト選択信号をローカルに生成することができる。上記のように、コンテキスト選択信号は、他の論理ブロック等の出力に含まれているコンテキスト決定データ等を用いてリコンフィギラブル回路内で生成される。そして、このコンテキスト選択信号を適用する範囲もユーザーが任意に設定できる。そのため、マルチコンテキスト動作がローカルかつ部分的に実行されることで、回路の効率的な利用が可能となる。ま

た、グローバルなマルチコンテキスト駆動と比較して、メモリの使用量も削減できる。

【0109】

(実施の形態2)

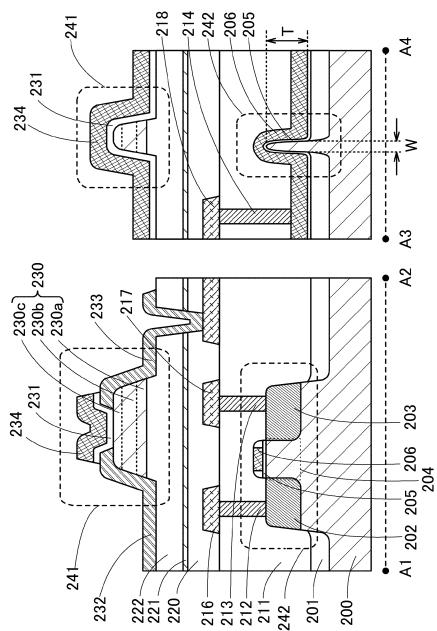

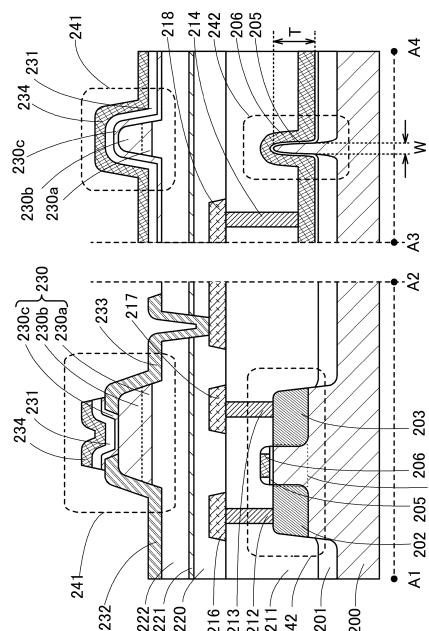

本実施の形態では、開示するトランジスタの断面構造の一例について、図面を参照して説明する。

【0110】

図17に、断面構造の一部を示す。なお、破線A1-A2で示す領域では、トランジスタ241およびトランジスタ242のチャネル長方向における構造を示しており、破線A3-A4で示す領域では、トランジスタ241およびトランジスタ242のチャネル幅方向における構造を示している。ただし、本発明の一態様では、トランジスタ241のチャネル長方向とトランジスタ242のチャネル長方向とが、必ずしも一致していないともよい。

10

【0111】

また、図17では、半導体的な特性を示す金属酸化物膜にチャネル形成領域を有するトランジスタ241が、単結晶のシリコン基板にチャネル形成領域を有するトランジスタ242上に形成されている場合を例示している。

【0112】

トランジスタ242は、非晶質、微結晶、多結晶又は单結晶である、シリコン又はゲルマニウムなどの半導体膜又は半導体基板に、チャネル形成領域を有していても良い。或いは、トランジスタ242は、半導体的な特性を示す金属酸化物膜又は金属酸化物基板に、チャネル形成領域を有していても良い。全てのトランジスタが金属酸化物膜又は金属酸化物基板に、チャネル形成領域を有している場合、トランジスタ241はトランジスタ242上に積層されていないとも良く、トランジスタ241とトランジスタ242とは、同一の層に形成されていても良い。

20

【0113】

シリコンの薄膜を用いてトランジスタ242を形成する場合、当該薄膜には、プラズマCVD法などの気相成長法若しくはスパッタリング法で作製された非晶質シリコン、非晶質シリコンをレーザーアニールなどの処理により結晶化させた多結晶シリコン、单結晶シリコンウェハに水素イオン等を注入して表層部を剥離した单結晶シリコンなどを用いることができる。

30

【0114】

トランジスタ242が形成される基板200は、例えば、シリコン基板、ゲルマニウム基板、シリコングルマニウム基板等を用いることができる。図17では、单結晶シリコン基板を基板200として用いる場合を例示している。

【0115】

また、トランジスタ242は、素子分離法により電気的に分離されている。素子分離法として、トレンチ分離法(STI法: Shallow Trench Isolation)等を用いることができる。図17では、トレンチ分離法を用いてトランジスタ242を電気的に分離する場合を例示している。具体的に、図17では、エッチング等により基板200に形成されたトレンチに、酸化珪素などが含まれる絶縁物を埋め込んだ後、当該絶縁物をエッチング等により部分的に除去することで形成される素子分離領域201により、トランジスタ242を素子分離させる場合を例示している。

40

【0116】

また、トレンチ以外の領域に存在する基板200の凸部には、トランジスタ242の不純物領域202および不純物領域203と、不純物領域202および不純物領域203に挟まれたチャネル形成領域204とが設けられている。さらに、トランジスタ242は、チャネル形成領域204を覆う絶縁膜205と、絶縁膜205を間に挟んでチャネル形成領域204と重なるゲート電極206とを有する。

【0117】

トランジスタ242では、チャネル形成領域204における凸部の側部および上部と、ゲ

50

ート電極 206 とが絶縁膜 205 を間に挟んで重なることで、チャネル形成領域 204 の側部と上部を含めた広い範囲においてキャリアが流れる。そのため、トランジスタ 242 の基板上における専有面積を小さく抑えつつ、トランジスタ 242 におけるキャリアの移動量を増加させることができる。その結果、トランジスタ 242 は、オン電流が大きくなると共に、電界効果移動度が高められる。特に、チャネル形成領域 204 における凸部のチャネル幅方向の長さ（チャネル幅）をW、チャネル形成領域 204 における凸部の膜厚をTとすると、チャネル幅Wに対する膜厚Tの比に相当するアスペクト比が高い場合、キャリアが流れる範囲はより広くなるため、トランジスタ 242 のオン電流をより大きくすることができ、電界効果移動度もより高められる。

## 【0118】

10

なお、バルクの半導体基板を用いたトランジスタ 242 の場合、アスペクト比は0.5以上であることが望ましく、1以上であることがより望ましい。

## 【0119】

トランジスタ 242 上には、絶縁膜 211 が設けられている。絶縁膜 211 には開口部が形成されている。そして、上記開口部には、不純物領域 202、不純物領域 203 にそれぞれ電気的に接続されている導電膜 212、導電膜 213 と、ゲート電極 206 に電気的に接続されている導電膜 214 とが、形成されている。

## 【0120】

そして、導電膜 212 は、絶縁膜 211 上に形成された導電膜 216 に電気的に接続されており、導電膜 213 は、絶縁膜 211 上に形成された導電膜 217 に電気的に接続されており、導電膜 214 は、絶縁膜 211 上に形成された導電膜 218 に電気的に接続されている。

20

## 【0121】

導電膜 216 乃至導電膜 218 上には、絶縁膜 220 が設けられている。そして、絶縁膜 220 上には、酸素、水素、水の拡散を防ぐプロッキング効果を有する絶縁膜 221 が設けられている。絶縁膜 221 は、密度が高くて緻密である程、また未結合手が少なく化学的に安定である程、より高いプロッキング効果を示す。酸素、水素、水の拡散を防ぐプロッキング効果を示す絶縁膜 221 として、例えば、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等を用いることができる。水素、水の拡散を防ぐプロッキング効果を示す絶縁膜 221 として、例えば、窒化シリコン、窒化酸化シリコン等を用いることができる。

30

## 【0122】

絶縁膜 221 上には絶縁膜 222 が設けられており、絶縁膜 222 上には、トランジスタ 241 が設けられている。

## 【0123】

トランジスタ 241 は、絶縁膜 222 上に、半導体的な特性を示す金属酸化物膜 230 と、金属酸化物膜 230 に電気的に接続された、ソース電極又はドレイン電極として機能する導電膜 232 および導電膜 233 と、金属酸化物膜 230 を覆っているゲート絶縁膜 231 と、ゲート絶縁膜 231 を間に挟んで金属酸化物膜 230 と重なるゲート電極 234 と、を有する。なお、絶縁膜 220 乃至絶縁膜 222 には開口部が設けられており、導電膜 233 は、上記開口部において導電膜 218 に接続されている。

40

## 【0124】

なお、図 17において、トランジスタ 241 は、ゲート電極 234 を金属酸化物膜 230 の片側において少なくとも有していれば良いが、絶縁膜 222 を間に挟んで金属酸化物膜 230 と重なるゲート電極を、さらに有していても良い。

## 【0125】

トランジスタ 241 が、一対のゲート電極を有している場合、一方のゲート電極には導通を制御するための信号が与えられ、他方のゲート電極は、電位が他の配線から与えられている状態であっても良い。この場合、一対のゲート電極に、同じ高さの電位が与えられて

50

いても良いし、他方のゲート電極にのみ接地電位などの固定の電位が与えられていても良い。他方のゲート電極に与える電位の高さを制御することで、トランジスタの閾値電圧を制御することができる。

#### 【0126】

また、図17では、トランジスタ241が、一のゲート電極234に対応した一のチャネル形成領域を有する、シングルゲート構造である場合を例示している。しかし、トランジスタ241は、電気的に接続された複数のゲート電極を有することで、一の活性層にチャネル形成領域を複数有する、マルチゲート構造であっても良い。

#### 【0127】

また、図17に示すように、トランジスタ241は、金属酸化物膜230が、絶縁膜222上において順に積層された金属酸化物膜230a乃至金属酸化物膜230cを有する場合を例示している。ただし、本発明の一態様では、トランジスタ241が有する金属酸化物膜230が、単層の金属酸化物で構成されていても良い。また、図17のような積層構造を有する場合、金属酸化物膜230aと金属酸化物膜230cは半導体として機能しなくてよい。すなわち、金属酸化物膜230bが、半導体として機能すればよい。

#### 【0128】

絶縁膜222は、加熱により酸素の一部を金属酸化物膜230a乃至金属酸化物膜230cに供給する機能を有する絶縁膜であることが望ましい。また、絶縁膜222は、欠陥が少ないことが好ましく、代表的には、ESR測定により得られる、シリコンのダンギングボンドに由来する $g = 2.001$ を持つスピノの密度が $1 \times 10^{18} \text{ spins/cm}^3$ 以下であることが好ましい。

#### 【0129】

絶縁膜222は、加熱により上記酸素の一部を金属酸化物膜230a乃至金属酸化物膜230cに供給する機能を有するため、酸化物であることが望ましく、例えば、酸化アルミニウム、酸化マグネシウム、酸化珪素、酸化窒化珪素、窒化酸化珪素、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどを用いることができる。絶縁膜222は、プラズマCVD(Chemical Vapor Deposition)法又はスパッタリング法等により、形成することができる。

#### 【0130】

なお、本明細書中において、酸化窒化物は、その組成として、窒素よりも酸素の含有量が多い材料を指し、窒化酸化物は、その組成として、酸素よりも窒素の含有量が多い材料を指す。

#### 【0131】

なお、図17に示すトランジスタ241は、チャネル領域が形成される金属酸化物膜230bの端部のうち、導電膜232および導電膜233とは重ならない端部、言い換えると、導電膜232および導電膜233が位置する領域とは異なる領域に位置する端部と、ゲート電極234とが、重なる構成を有する。金属酸化物膜230bの端部は、当該端部を形成するためのエッチングでプラズマに曝されるときに、エッチングガスから生じた塩素ラジカル、フッ素ラジカル等が、金属酸化物を構成する金属元素と結合しやすい。よって、金属酸化物膜の端部では、当該金属元素と結合していた酸素が脱離しやすい状態にあるため、酸素欠損が形成され、n型化しやすいと考えられる。しかし、図17に示すトランジスタ241では、導電膜232および導電膜233とは重ならない金属酸化物膜230bの端部と、ゲート電極234とが重なるため、ゲート電極234の電位を制御することにより、当該端部にかかる電界を制御することができる。よって、金属酸化物膜230bの端部を介して導電膜232と導電膜233の間に流れる電流を、ゲート電極234に与える電位によって制御することができる。このようなトランジスタ241の構造を、Surrounded Channel(S-Channel)構造とよぶ。

#### 【0132】

具体的に、S-Channel構造の場合、トランジスタ241がオフとなるような電位

10

20

30

40

50

をゲート電極 234 に与えたときは、当該端部を介して導電膜 232 と導電膜 233 の間に流れるオフ電流を小さく抑えることができる。そのため、トランジスタ 241 では、大きなオン電流を得るためにチャネル長を短くし、その結果、金属酸化物膜 230b の端部における導電膜 232 と導電膜 233 の間の長さが短くなても、トランジスタ 241 のオフ電流を小さく抑えることができる。よって、トランジスタ 241 は、チャネル長を短くすることで、オンのときには大きいオン電流を得ることができ、オフのときにはオフ電流を小さく抑えることができる。

#### 【 0133】

また、具体的に、S - C h a n n e l 構造の場合、トランジスタ 241 がオンとなるような電位をゲート電極 234 に与えたときは、当該端部を介して導電膜 232 と導電膜 233 の間に流れる電流を大きくすることができる。当該電流は、トランジスタ 241 の電界効果移動度とオン電流の増大に寄与する。そして、金属酸化物膜 230b の端部と、ゲート電極 234 とが重なることで、金属酸化物膜 230b においてキャリアの流れる領域が、ゲート絶縁膜 231 に近い金属酸化物膜 230b の界面近傍のみでなく、金属酸化物膜 230b の広い範囲においてキャリアが流れるため、トランジスタ 241 におけるキャリアの移動量が増加する。この結果、トランジスタ 241 のオン電流が大きくなると共に、電界効果移動度が高くなり、代表的には電界効果移動度が  $10 \text{ cm}^2 / \text{V} \cdot \text{s}$  以上、さらには  $20 \text{ cm}^2 / \text{V} \cdot \text{s}$  以上となる。なお、ここで電界効果移動度は、金属酸化物膜 230b を構成する物質の物性値としての移動度の近似値ではなく、トランジスタの飽和領域における電流駆動力の指標であり、見かけ上の電界効果移動度である。

10

20

#### 【 0134】

また、例えば、図 18 に示すような構造でもよい。図 18 に示すトランジスタ 241 は、図 17 に示すトランジスタ 241 と、金属酸化物膜 230c が導電膜 232 および導電膜 233 の上に形成されていることで異なる。この結果、より半導体的な特性を有する金属酸化物膜 230b が導電膜 232 および導電膜 233 と接することにより、ソースドレイン間の抵抗を減じることができる。

#### 【 0135】

##### ( 実施の形態 3 )

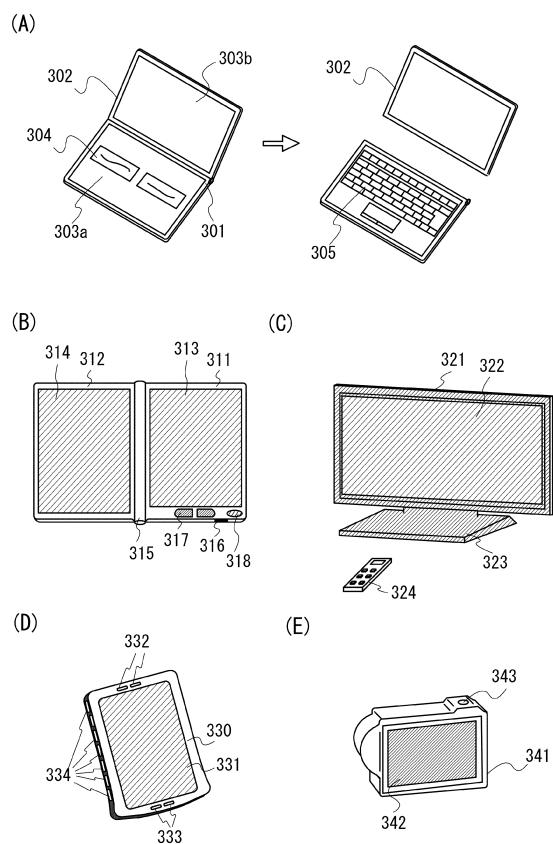

本実施の形態では、上述の実施の形態で説明した電子機器の例について、図 19 ( A ) 乃至図 19 ( E ) を用いて説明する。

30

#### 【 0136】

図 19 ( A ) は、携帯型の情報端末であり、筐体 301、筐体 302、第 1 の表示部 303a、第 2 の表示部 303b などによって構成されている。筐体 301 と筐体 302 の少なくとも一部には、先の実施の形態に示す、リコンフィギュラブルな回路として機能する論理ブロック 100 等を有する電子部品が設けられている。そのため、低消費電力化、および回路間の配線数の低減が図られた携帯型の情報端末が実現される。

#### 【 0137】

なお、第 1 の表示部 303a はタッチ入力機能を有するパネルとなっており、例えば図 19 ( A ) の左図のように、第 1 の表示部 303a に表示される選択ボタン 304 により「タッチ入力」を行うか、「キーボード入力」を行うかを選択できる。選択ボタンは様々な大きさで表示できるため、幅広い世代の人が使いやすさを実感できる。ここで、例えば「キーボード入力」を選択した場合、図 19 ( A ) の右図のように第 1 の表示部 303a にはキーボード 305 が表示される。これにより、従来の情報端末と同様に、キー入力による素早い文字入力などが可能となる。

40

#### 【 0138】

また、図 19 ( A ) に示す携帯型の情報端末は、図 19 ( A ) の右図のように、第 1 の表示部 303a および第 2 の表示部 303b のうち、一方を取り外すことができる。第 2 の表示部 303b もタッチ入力機能を有するパネルとし、持ち運びの際、さらなる軽量化を図ることができ、一方の手で筐体 302 を持ち、他方の手で操作することができるため便利である。このように電子機器の形態が変わった場合には、論理ブロック 100 等のコン

50

フィギュレーションも変化させることが可能であり、一例として、マルチコンテキスト機能を用いて、図19(A)の左図の場合とは異なる演算を実行するようにしてもよい。

#### 【0139】

図19(A)に示す携帯型の情報端末は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子など)、記録媒体挿入部などを備える構成としてもよい。

#### 【0140】

また、図19(A)に示す携帯型の情報端末は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。 10

#### 【0141】

更に、図19(A)に示す筐体302にアンテナやマイク機能や無線機能を持たせ、携帯電話として用いてもよい。

#### 【0142】

図19(B)は、電子ペーパーを実装した電子書籍であり、筐体311と筐体312の2つの筐体で構成されている。筐体311および筐体312には、それぞれ表示部313および表示部314が設けられている。筐体311と筐体312は、軸部315により接続されており、該軸部315を軸として開閉動作を行うことができる。また、筐体311は、電源316、操作キー317、スピーカー318などを備えている。筐体311、筐体312の少なくとも一には、先の実施の形態に示す、リコンフィギュラブルな回路として機能する論理ブロック100等を有する電子部品が設けられている。そのため、低消費電力化、および回路間の配線数の低減が図られた電子書籍が実現される。 20

#### 【0143】

なお、電子書籍に内蔵されている論理ブロック100等は、筐体311と筐体312の間の相対的な位置や角度に応じて、コンフィギュレーションを変化させることができあり、一例として、マルチコンテキスト機能を用いて、開いた状態と閉じた状態とで異なる演算を実行するようにしてもよい。

#### 【0144】

図19(C)は、テレビジョン装置であり、筐体321、表示部322、スタンド323などで構成されている。テレビジョン装置の操作は、筐体321が備えるスイッチや、リモコン操作機324により行うことができる。筐体321およびリモコン操作機324には、先の実施の形態に示す、リコンフィギュラブルな回路として機能する論理ブロック100等を有する電子部品が搭載されている。そのため、低消費電力化、および回路間の配線数の低減が図られたテレビジョン装置が実現される。 30

#### 【0145】

なお、テレビジョン装置に内蔵されている論理ブロック100等は、環境光や視聴者の位置に応じて、コンフィギュレーションを変化させることができあり、一例として、マルチコンテキスト機能を用いて、部屋が明るい場合と暗い場合、視聴者が近くにいる場合と離れている場合とで異なる演算を実行するようにしてもよい。 40

#### 【0146】

図19(D)は、スマートフォンであり、本体330には、表示部331と、スピーカー332と、マイク333と、操作ボタン334等が設けられている。本体330内には、先の実施の形態に示す、リコンフィギュラブルな回路として機能する論理ブロック100等を有する電子部品が設けられている。そのため低消費電力化、および回路間の配線数の低減が図られたスマートフォンが実現される。

#### 【0147】

なお、スマートフォンに内蔵されている論理ブロック100等は、環境光やユーザーの位置に応じて、コンフィギュレーションを変化させることができあり、一例として、マル

チコンテキスト機能を用いて、画像を表示している状態と表示していない状態とで異なる演算を実行するようにしてもよい。

【0148】

図19(E)は、デジタルカメラであり、本体341、表示部342、操作スイッチ343などによって構成されている。本体341内には、先の実施の形態に示す、リコンフィギュラブルな回路として機能する論理ブロック100等を有する電子部品が設けられている。そのため、低消費電力化、および回路間の配線数の低減が図られたデジタルカメラが実現される。

【0149】

なお、デジタルカメラに内蔵されている論理ブロック100等は、撮影モードに応じて、コンフィギュレーションを変化させることができあり、一例として、マルチコンテキスト機能を用いて、静止画を撮影する場合と動画を撮影する場合とで異なる演算を実行するようにしてもよい。

【0150】

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る、リコンフィギュラブルな回路として機能する論理ブロック100等を有する電子部品が搭載されている。このため、低消費電力化、および回路間の配線数の低減が図られた電子機器が実現される。

【符号の説明】

【0151】

|         |              |    |

|---------|--------------|----|

| C L K   | クロック信号       | 20 |

| O U T   | 出力信号         |    |

| 1 0 0   | 論理ブロック       |    |

| 1 0 0 a | 論理ブロック       |    |

| 1 0 0 b | 論理ブロック       |    |

| 1 0 0 c | 論理ブロック       |    |

| 1 0 0 d | 論理ブロック       |    |

| 1 0 1   | ロジックエレメント    |    |

| 1 0 1 a | ロジックエレメント    |    |

| 1 0 1 b | ロジックエレメント    | 30 |

| 1 0 1 c | ロジックエレメント    |    |

| 1 0 1 d | ロジックエレメント    |    |

| 1 0 2   | スイッチマトリクスアレイ |    |

| 1 0 3   | 配線           |    |

| 1 0 4   | 配線           |    |

| 1 0 5   | 配線           |    |

| 1 0 5 A | 制御信号線        |    |

| 1 0 5 B | 制御信号線        |    |

| 1 0 5 C | 制御信号線        |    |

| 1 0 5 D | 制御信号線        | 40 |

| 1 0 6   | コンテキスト選択信号線  |    |

| 1 0 7   | スイッチ回路       |    |

| 1 0 8   | パストランジスタ     |    |

| 1 0 8 A | パストランジスタ     |    |

| 1 0 8 B | パストランジスタ     |    |

| 1 0 8 C | パストランジスタ     |    |

| 1 0 8 D | パストランジスタ     |    |

| 1 0 9 A | メモリ          |    |

| 1 0 9 B | メモリ          |    |

| 1 0 9 C | メモリ          | 50 |

|         |                |    |

|---------|----------------|----|

| 1 0 9 D | メモリ            |    |

| 1 1 0   | マルチプレクサ        |    |

| 1 1 1   | デコーダ           |    |

| 1 1 2 A | 選択トランジスタ       |    |

| 1 1 2 B | 選択トランジスタ       |    |

| 1 1 2 C | 選択トランジスタ       |    |

| 1 1 2 D | 選択トランジスタ       |    |

| 1 1 3 A | トランスファーゲート     |    |

| 1 1 3 B | トランスファーゲート     |    |

| 1 1 4 a | インバータ          | 10 |

| 1 1 4 b | インバータ          |    |

| 1 1 4 c | インバータ          |    |

| 1 1 5   | デマルチプレクサ       |    |

| 1 2 1   | デコーダ           |    |

| 1 2 2   | マルチプレクサ        |    |

| 1 2 3   | フリップフロップ       |    |

| 1 2 4   | マルチプレクサ        |    |

| 1 2 5 a | コンフィギュレーションメモリ |    |

| 1 2 5 b | コンフィギュレーションメモリ |    |

| 1 2 5 c | コンフィギュレーションメモリ | 20 |

| 1 2 5 d | コンフィギュレーションメモリ |    |

| 1 2 5 e | コンフィギュレーションメモリ |    |

| 1 2 6   | マルチプレクサ        |    |

| 1 2 7   | デマルチプレクサ       |    |

| 1 2 8   | マルチプレクサ        |    |

| 1 2 9   | トライステートバッファー   |    |

| 1 3 0   | 論理ゲート          |    |

| 1 3 1   | 出入力回路          |    |

| 1 3 2   | 配線群            |    |

| 1 3 3   | 配線群            | 30 |

| 1 3 4   | スイッチブロック       |    |

| 1 3 5   | クロススイッチエレメント   |    |

| 1 3 6 a | スイッチ           |    |

| 1 3 6 b | スイッチ           |    |

| 1 3 6 c | スイッチ           |    |

| 1 3 6 d | スイッチ           |    |

| 1 3 6 e | スイッチ           |    |

| 1 3 6 f | スイッチ           |    |

| 1 3 7 a | メモリ            |    |

| 1 3 7 b | メモリ            | 40 |

| 1 3 7 c | メモリ            |    |

| 1 3 7 d | メモリ            |    |

| 1 3 7 e | メモリ            |    |

| 1 3 7 f | メモリ            |    |

| 2 0 0   | 基板             |    |

| 2 0 1   | 素子分離領域         |    |

| 2 0 2   | 不純物領域          |    |

| 2 0 3   | 不純物領域          |    |

| 2 0 4   | チャネル形成領域       |    |

| 2 0 5   | 絶縁膜            | 50 |

|         |         |    |

|---------|---------|----|

| 2 0 6   | ゲート電極   |    |

| 2 1 1   | 絶縁膜     |    |

| 2 1 2   | 導電膜     |    |

| 2 1 3   | 導電膜     |    |

| 2 1 4   | 導電膜     |    |

| 2 1 6   | 導電膜     |    |

| 2 1 7   | 導電膜     |    |

| 2 1 8   | 導電膜     |    |

| 2 2 0   | 絶縁膜     | 10 |

| 2 2 1   | 絶縁膜     |    |

| 2 2 2   | 絶縁膜     |    |

| 2 3 0   | 金属酸化物膜  |    |

| 2 3 0 a | 金属酸化物膜  |    |

| 2 3 0 b | 金属酸化物膜  |    |

| 2 3 0 c | 金属酸化物膜  |    |

| 2 3 1   | ゲート絶縁膜  |    |

| 2 3 2   | 導電膜     |    |

| 2 3 3   | 導電膜     |    |

| 2 3 4   | ゲート電極   |    |

| 2 4 1   | トランジスタ  | 20 |

| 2 4 2   | トランジスタ  |    |

| 3 0 1   | 筐体      |    |

| 3 0 2   | 筐体      |    |

| 3 0 3 a | 表示部     |    |

| 3 0 3 b | 表示部     |    |

| 3 0 4   | 選択ボタン   |    |

| 3 0 5   | キー ボード  |    |

| 3 1 1   | 筐体      |    |

| 3 1 2   | 筐体      |    |

| 3 1 3   | 表示部     | 30 |

| 3 1 4   | 表示部     |    |

| 3 1 5   | 軸部      |    |

| 3 1 6   | 電源      |    |

| 3 1 7   | 操作キー    |    |

| 3 1 8   | スピーカー   |    |

| 3 2 1   | 筐体      |    |

| 3 2 2   | 表示部     |    |

| 3 2 3   | スタンド    |    |

| 3 2 4   | リモコン操作機 |    |

| 3 3 0   | 本体      | 40 |

| 3 3 1   | 表示部     |    |

| 3 3 2   | スピーカー   |    |

| 3 3 3   | マイク     |    |

| 3 3 4   | 操作ボタン   |    |

| 3 4 1   | 本体      |    |

| 3 4 2   | 表示部     |    |

| 3 4 3   | 操作スイッチ  |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(56)参考文献 特開2015-29261(JP,A)

特開2007-166579(JP,A)

特開2015-26901(JP,A)

米国特許第5742180(US,A)

(58)調査した分野(Int.Cl., DB名)

H03K19/173

H03K19/177