(12)

### Übersetzung der europäischen Patentschrift

(97) EP 0 779 623 B1

(21) Deutsches Aktenzeichen: **696 32 017.7** (96) Europäisches Aktenzeichen: **96 119 545.0**

(96) Europäischer Anmeldetag: **05.12.1996**

(97) Erstveröffentlichung durch das EPA: 18.06.1997

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **31.03.2004** (47) Veröffentlichungstag im Patentblatt: **24.02.2005**

(30) Unionspriorität:

31642095 05.12.1995 JP

(73) Patentinhaber:

Pioneer Electronic Corp., Tokio/Tokyo, JP

(74) Vertreter:

Betten & Resch, 80333 München

(84) Benannte Vertragsstaaten:

DE, FR, GB, NL

(72) Erfinder:

(51) Int CI.7: G11B 20/14

Kojima, Tadashi, Yokohama-shi, Kanagawa-ken 236, JP; Hirayama, Koichi, Yokohama-shi, Kanagawa-ken 245, JP; Yamada, Hisashi, Yokohama-shi, Kanagawa-ken 244, JP; Moriyama, Yoshiaki, Tsurugashima-shi, Saitama 350-02, JP; Yokogawa, Fumihiko, Tsurugashima-shi, Saitama 350-02, JP; Arai, Takao, Yokohama-shi, Kanagawa, JP; Takeuchi, Toshifumi, Hodogaya-ku, Kanagawa, JP; Tanaka, Shinichi, Tuzukigun, Kyotofu, JP; Kurahashi, Akira, Yawatashi, Kyotofu, JP; Shimada, Toshiyuki, Kobeshi, Hyogoken, JP

(54) Bezeichnung: Digitaldatenübertragungsverfahren

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelegt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

#### **Beschreibung**

#### Gebiet der Erfindung

**[0001]** Die Erfindung bezieht sich auf ein Verfahren zum Übertragen digitaler Daten, bei dem die digitalen Daten in Sektoren gehalten werden, wovon jeder mehrere Synchronisationsrahmen umfasst, die sequentiell übertragen werden (einschließlich der Aufzeichnung der digitalen Daten).

#### Beschreibung der Hintergrundinformationen

**[0002]** Als ein lauflängenbegrenztes Codierungsverfahren (RLL-Codierungsverfahren), das ausgeführt wird, um digitale Daten zu übertragen, die Informationen anzeigen, oder um die digitalen Daten auf einem Aufzeichnungsmedium aufzuzeichnen, ist eine EFM (Acht-zu-Vierzehn-Modulation) bekannt, die für eine CD (Kompaktplatte) oder dergleichen verwendet wird.

[0003] Im EFM werden die digitalen Daten von acht Bits (einem Byte) in einen lauflängenbegrenzten Code von 14 Bits umgesetzt, der die Lauflängen-Begrenzungen erfüllt: minimaler Lauflängenparameter d = 2; maximaler Lauflängenparameter k = 10,

mit dem minimalen Lauflängenparameter d = 2 und dem maximalen Lauflängenparameter k = 10 Kanalbits, was wenigstens 2 und höchstens 10 aufeinander folgende 'Nullen' zwischen aufeinander folgenden "Einsen" bedeutet, wobei Verbindungsbits aus drei Bits zu den Intervallen zwischen den entsprechenden umgesetzten Daten hinzugefügt werden und die resultierenden Daten als ein EFM-Modulations-Signal gebildet werden. In einer Folge von EFM-Modulations-Signalen wird ebenso ein Bitzug der Verbindungsbits gesetzt, um die vorangehenden Lauflängen-Begrenzung zu erfüllen.

**[0004]** In der CD ist ein Signal, das erhalten worden ist, indem ein Synchronisationssignal zu dem EFM-Modulations-Signal hinzugefügt worden ist, aufgezeichnet worden. Die Folge der EFM-Modulations-Signale wird in einer Weise konstruiert, sodass ein sich wiederholendes Muster des maximalen Intervalls, das der maximalen Lauflänge k entspricht, nämlich ein sich wiederholendes Muster, wie z. B.

**[0005]** 11 T - 11 T, in der Folge nicht vorhanden ist, wobei das sich wiederholende Muster von 11T als ein Synchronisationssignal verwendet wird. Dabei ist T eine fundamentale Periode, die einem binären Symbol entspricht. Ein Muster  $T_{max}$ , das z. B. der maximalen Lauflänge entspricht, ist durch  $T_{max} = (k + 1)T$  definiert, während ein Muster, das der minimalen Lauflänge entspricht, durch  $T_{min} = (d + 1)T$  definiert ist.

**[0006]** In einem CD-Spieler wird das Synchronisationssignal extrahiert, indem das sich wiederholende Muster von 11T von einem von der CD ausgelesenen Signal erfasst wird.

**[0007]** In einer DVD (digitalen Videoplatte), in der die Aufzeichnungsinformationen mit einer hohen Dichte aufgezeichnet worden sind, oder bei einer Datenübertragung mit hoher Dichte wird es jedoch, wenn die Informationen gelesen werden, in hohem Maße durch eine Zwischensymbolstörung beeinflusst. Das sich wiederholende Muster von 11 T als ein Synchronisationssignal wird deshalb zu einem Muster, wie z. B. 11T – 10T oder 10T – 11T, geändert und ausgelesen. Im Gegenteil tritt ein Fall auf, in dem das Datenmuster, wie z. B. 10T – 11 T oder 11 T – 10T, als ein EFM-Modulations-Signal in das sich wiederholende Muster von 11T geändert und fälschlich als ein Synchronisationssignal erfasst wird.

**[0008]** Wie oben erwähnt worden ist, vergrößert sich in der Aufzeichnung mit hoher Dichte oder der Datenübertragung mit hoher Dichte eine Häufigkeit der Fehler, die bei der Erfassung des Synchronisationssignals auftreten, wobei, verursacht durch die fehlende Synchronisation, leicht ein Bündelfehler auftritt.

**[0009]** SCHOUHAMER IMMINK KA: 'EFMPLUS: THE CODING FORMAT OF THE MULTIMEDIA COMPACT DISC', IEEE TRANSACTIONS ON CONSUMER ELECTRONICS, Bd.41, Nr. 3, 1. August 1995, Seiten 491-497, offenbart eine alternative Acht-zu-Vierzehn-Modulation (EFM), die als EFMPlus bezeichnet wird, die als ein Codierungsformat des Vorschlags für Multimedia-Kompaktplatten übernommen worden ist. Die Rate des neuen Codes beträgt 8/16, was bedeutet, dass eine 6-7 % höhere Informationsdichte erhalten werden kann. EFMPlus ist das ganze Ebenbild des EFM (die gleiche minimale und maximale Lauflänge, Taktinhalte usw.). Computer-Simulationen haben gezeigt, dass die Niederfrequenzinhalte des neuen Codes nur ein wenig größer als sein herkömmliches EFM-Gegenstück sind.

**[0010]** EP-A-0 673 029 A1 offenbart ein Aufzeichnungsmedium, eine Signalaufzeichnungsvorrichtung dafür und eine Signalwiedergabevorrichtung dafür, wobei das Aufzeichnungsmedium einen Aufzeichnungsbereich besitzt, der als Sektoren unterteilt ist, von denen jeder aus mehreren Rahmen mit einer vorgegebenen Bitlänge besteht, worin wenigstens einer der Rahmen ein erstes Synchronisationsmuster, um die Länge des Rahmens darzustellen, ein zweites Synchronisationsmuster, das aus einem vorgegebenen Signalmuster besteht, das im Signalmuster der Anwenderdaten nicht vorhanden ist und das beschaffen ist, um die Periode des Sektors darzustellen, Kenndaten, die an einer vorgegebenen Position angeordnet sind, die dem zweiten Synchronisationsmuster entsprechenden, und beschaffen sind, um den Sektor zu identifizieren, und Fehlererfassungsdaten, um einen Fehler der Kenndaten zu erfassen, enthält und worin jeder der anderen Rahmen das erste Synchronisationsmuster, die Anwenderdaten und wenigstens vorgegebene feste Daten, in denen das zweite Synchronisationsmuster ersetzt ist und die in einem Signalmuster der Anwenderdaten vorhanden sind, die Kenndaten, die Fehlererfassungsdaten und Fehlerkorrekturdaten, um einen Fehler der Anwenderdaten zu korrigieren, enthält.

#### ZUSAMMENFASSUNG UND AUFGABE DER ERFINDUNG

**[0011]** Die Erfindung wird gemacht, um die oben erwähnten Probleme zu lösen, wobei es eine Aufgabe der Erfindung ist, ein Übertragungsverfahren für digitale Daten zu schaffen, durch das die digitalen Daten mit einer hohen Genauigkeit reproduziert werden können, selbst bei einer Aufzeichnung mit hoher Dichte oder einer Datenübertragung mit hoher Dichte.

**[0012]** Die Erfindung ist in den unabhängigen Ansprüchen definiert. Die abhängigen Ansprüche definieren besondere Ausführungsformen der Erfindung.

**[0013]** Gemäß einer Ausführungsform 1 der Erfindung wird außerdem ein Übertragungsverfahren für digitale Daten geschaffen, um die digitalen Daten in Sektoren zu speichern, die jeweils mehrere Synchronisationsrahmen enthalten, und um die digitalen Daten sequentiell zu übertragen, wobei der Synchronisationsrahmen ein Synchronisationssignal und einen lauflängenbegrenzten Code enthält, der den digitalen Daten entspricht und Begrenzungen hinsichtlich einer minimalen Lauflänge und einer maximalen Lauflänge erfüllt, wobei das Synchronisationssignal einen bestimmten Code enthält, der eine Position des Synchronisationssignals im Sektor angibt und der es ermöglicht, dass eine Gleichstromsteuerung ausgeführt wird.

**[0014]** Gemäß einer Ausführungsform umfasst der Synchronisationsrahmen, um die digitalen Daten in den Sektoren zu halten, die jeweils mehrere Synchronisationsrahmen enthalten, und um die digitalen Daten sequentiell zu übertragen, das Synchronisationssignal und den lauflängenbegrenzten Code, der die Begrenzungen der minimalen Lauflänge und der maximalen Lauflänge erfüllt, wobei das Synchronisationssignal das Synchronisationsmuster enthält, das das Bitmuster der Lauflänge, die um 3T länger als die maximale Lauflänge ist, wobei die zusätzlichen Bitmuster vor und nach dem Bitmuster angeordnet sind, wobei jedes von ihnen eine Lauflänge besitzt, die länger als die minimale Lauflänge ist. Das Synchronisationssignal enthält den bestimmten Code, der die Position im Sektor anzeigt und ermöglicht, dass die Gleichstromsteuerung ausgeführt wird.

#### KURZBESCHREIBUNG DER ZEICHNUNG

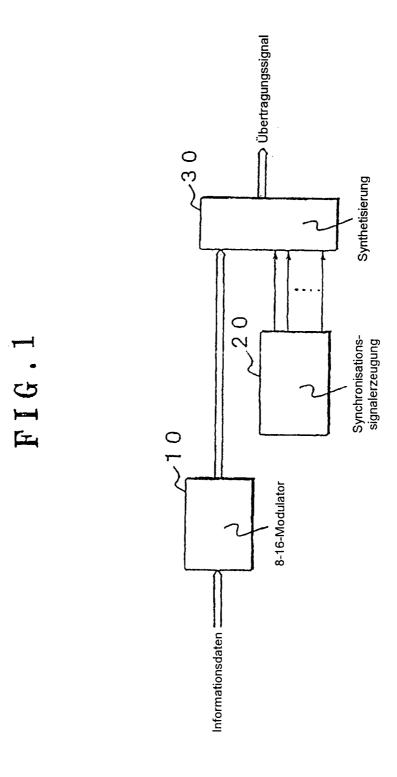

**[0015] Fig.** 1 ist eine graphische Darstellung, die eine schematische Konstruktion einer Übertragungssignal-Bildungsvorrichtung zum Bilden eines Übertragungssignals durch ein Übertragungsverfahren für digitale Daten gemäß der Erfindung zeigt;

[0016] Fig. 2 ist eine graphische Darstellung, die ein Synchronisationssignal gemäß der Erfindung zeigt;

[0017] Fig. 3 ist eine graphische Darstellung, die das Synchronisationssignal gemäß der Erfindung zeigt;

[0018] Fig. 4 ist eine graphische Darstellung, die ein Format des Synchronisationssignals zeigt;

[0019] Fig. 5 ist eine graphische Darstellung, die eine Signalform des Übertragungssignals mit einem Synchronisationsmuster zeigt;

[0020] Fig. 6 ist eine graphische Darstellung, die ein Übertragungssignalformat eines Sektors zeigt;

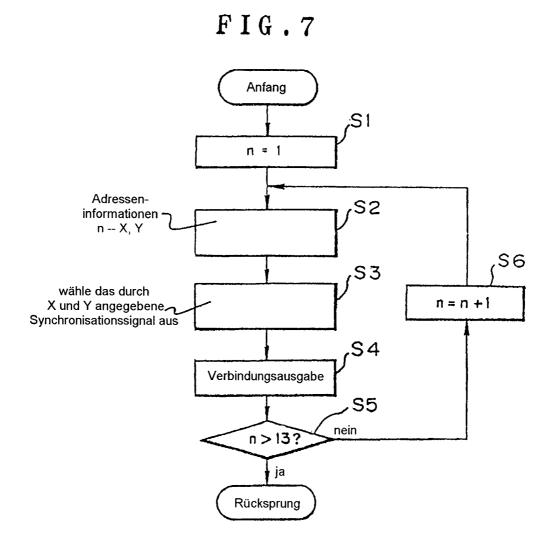

[0021] Fig. 7 ist eine graphische Darstellung, die einen Operationsfluss einer Synthetisierungsschaltung 30 zeigt; und

[0022] Fig. 8 ist eine graphische Darstellung, die die Speicherinhalte in einem Speicher zeigt.

#### AUSFÜHRLICHE BESCHREIBUNG DER BEVORZUGTEN AUSFÜHRUNGS-FORM

**[0023] Fig.** 1 ist eine graphische Darstellung, die eine Konstruktion einer Übertragungssignal-Bildungsvorrichtung zum Bilden eines Übertragungssignals durch ein Übertragungsverfahren für digitale Daten gemäß der Erfindung zeigt.

**[0024]** In **Fig.** 1 setzt ein 8-16-Modulator (Acht-zu-Sechzehn-Modulator) **10** die zu übertragenden digitalen Daten nach jeweils acht Bits in ein 8-16-Modulations-Signal (einen lauflängenbegrenzten Code) aus 16 Bits (ein Codewort) um, sodass die Lauflängen-Begrenzungen der minimalen Lauflänge d = 2T und der maximalen Lauflänge k = 10T erfüllt sind.

**[0025]** Alle durch den 8-16-Modulator **10** erhaltenen Codewörter besitzen Musterformen, die eine der folgenden Bedingungen Next\_State1 bis Next State4 erfüllen.

Next State1: Das Codewort, in dem die Anzahl der fortlaufenden 0 am Ende gleich 0 oder 1 ist.

Next\_State2: Das Codewort, in dem die Anzahl der fortlaufenden 0 am Ende gleich 2 bis 5 ist und das erste Bit und das 13. Bit des nächsten Codeworts gleich 0 sind.

Next\_State3: Das Codewort, in dem die Anzahl der fortlaufenden 0 am Ende gleich 2 bis 5 ist und wenigstens irgendeines des ersten und 13. Bits des nächsten Codeworts gleich 0 ist.

Next State4: Das Codewort, in dem die Anzahl der fortlaufenden 0 am Ende gleich 6 bis 9 ist.

[0026] Das Modulationsverfahren ist durch den folgenden Artikel veröffentlicht worden.

**[0027]** Kees A. Schouhamer Immink, "EFMPIus: The Coding format of the High-Density Compact Disc", IEEE International Conference on Consumer Electronics, WPM6.1, 1995.

[0028] Eine Synchronisationssignal-Erzeugungsschaltung 20 erzeugt 32 Synchronisationssignale mit verschiedenen Bitmustern, wie in **Fig.** 2 und 3 gezeigt ist, und überträgt sie zu einer Synthetisierungsschaltung 30, die vorzugsweise eine CPU und einen Speicher enthält, wie später beschrieben wird.

[0029] Diese 32 Synchronisationssignale sind in acht Gruppen SY0 bis SY7 unterteilt, wie in den Fig. 2 und 3 gezeigt ist.

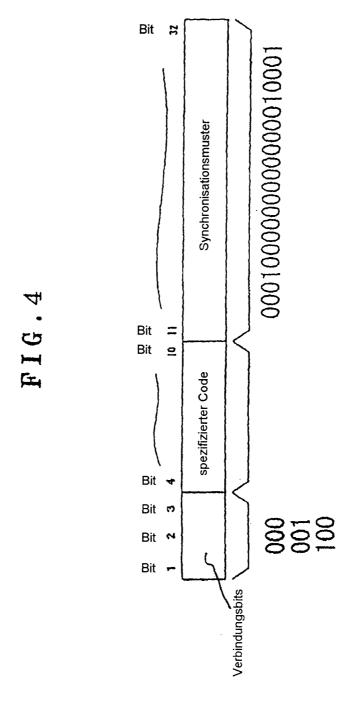

[0030] Fig. 4 ist eine graphische Darstellung, die ein Format des Synchronisationssignals zeigt.

**[0031]** In **Fig.** 4 bezeichnen die Bits 1 bis 3 des Synchronisationssignals die Verbindungsbits, die vorgesehen sind, um die vorangehenden Begrenzungen der minimalen Lauflänge d und der maximalen Lauflänge k zu erfüllen, wenn das Synchronisationssignal mit einem Codewort direkt vor ihm verbunden ist. Ein Verbindungsbitmuster durch die Bits 1 bis 3 gibt irgendeines von {000}, {001} und {100} an.

**[0032]** Ein Synchronisationsmuster, um das Synchronisationssignal zu identifizieren, ist den Bits 11 bis 32 des Synchronisationssignals zugewiesen.

**[0033]** Das Synchronisationsmuster ist ein Bitmuster einer Anordnung, wie z. B. (4T oder mehr – 14T – 4T), in der ein Muster von 14T, das um 3T größer als das maximale Intervall 11T im 8-16-Modulations-Signal ist, auf einen Kern gesetzt ist, während ein Muster mit einer festen Länge von 4T und ein Muster von 4T oder mehr nach bzw. vor dem Muster von 14T angeordnet sind, nämlich das Bitmuster {000100000000000000010001}.

**[0034]** In diesem Fall ist das Synchronisationsmuster ein festes Muster, das allen Synchronisationssignalen gemeinsam ist, wie in den **Fig.** 2 und 3 gezeigt ist.

**[0035]** Im Synchronisationsmuster wird das Muster von 14T, das um 3T größer als das maximale Intervall 11T im 8-16-Modulations-Signal ist, verwendet, selbst wenn das 11T-Muster im 8-16-Modulations-Signal, zurückzuführen auf einen Einfluss durch eine Zwischensymbolstörung, flankenverschoben und zu einer Muster von 12T geändert ist und ferner das Synchronisationsmuster selbst flankenverschoben und nur um 1T verkürzt ist, um zu ermöglichen, dass beide von ihnen zu unterscheiden sind. Das 14T-Muster bezeichnet eine kürzeste Länge, die gesetzt werden kann, wenn die Flankenverschiebung betrachtet wird.

[0036] Durch das Anordnen eines zusätzlichen Bitmusters mit einer festen Länge von 4T und eines zusätzli-

chen Bitmusters von 4T oder mehr nach und vor dem 14T-Muster wird ein Intervall geschaffen, das um wenigstens 1T größer als die kürzesten Bits von 3T ist, wobei dadurch der Einfluss einer Zwischensymbolstörung mit einer benachbarten Marke verringert wird.

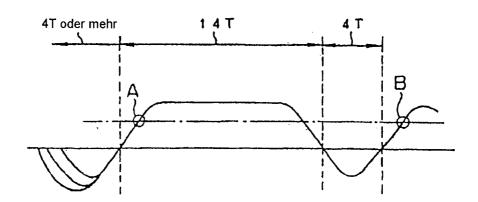

**[0037] Fig.** 5 ist eine graphische Darstellung, die eine Signalform des Übertragungssignals mit einem Synchronisationsmuster zeigt.

[0038] Wie in Fig. 5 gezeigt ist, kann, falls die Punkte der voreilenden (der nacheilenden, wenn die Signalform invertiert ist) der Kanten, nämlich ein Intervall zwischen den Punkten A und B durch einen Slice-Pegel erfasst wird, der durch eine Linie aus abwechselnden langen und kurzen Strichen gezeigt ist, selbst wenn der Slice-Pegel nicht durch eine Einschwingoperation oder dergleichen eingeschwungen ist, das Kantenintervall stabil erfasst werden. Durch das Erfassen eines 18T-Musters, in dem das 14T-Muster und das hintere 4T-Muster kombiniert sind, und durch das Auswählen des Musters, in dem das Muster von 14T vorhanden ist, kann das ausgewählte Muster als ein Signal für eine Geschwindigkeitserfassung eines Spindel-Servomotors beim Starten verwendet werden. Durch das Setzen der Markenlängen vor und nach dem 14T-Muster, sodass sie gleich oder größer als 4T sind, in denen eine Amplitude größer als die kürzeste Markenfänge ist, wird für eine Fluktuation des Slice-Pegels eine zulässige Amplitude vergrößert. Obwohl es außerdem möglich ist, gemäß der Ausführungsform eine Kombination der Marken von 5T oder mehr zu verwenden, weil ein Wirkungsgrad bevorzugt betrachtet wird, wird eine hintere Markenlänge auf 4T gesetzt, während eine vordere Markenlänge auf 4T oder mehr gesetzt wird.

**[0039]** Der Grund, warum das hintere Muster des 14T-Musters auf die feste Länge von 4T und das vordere Muster auf 4T oder mehr gesetzt wird, ist, weil, wenn ein bestimmter Code, der im Folgenden beschrieben wird, ferner vor das 14T-Muster gesetzt wird, ein Freiheitsgrad des vorderen Musters vergrößert wird und die Anzahl der Muster, die als ein bestimmter Code zu erhalten sind, ausreichend gesichert ist.

**[0040]** Wie in **Fig.** 4 gezeigt ist, ist der bestimmte Code den Bits 4 bis 10 des Synchronisationssignals zugewiesen. Abhängig von der Kombination mit den Verbindungsbits, die direkt vor dem bestimmten Code vorhanden sind, kann eine Position in einem Sektor, die im Folgenden erklärt wird, identifiziert werden.

**[0041]** Die Synthetisierungsschaltung **30** in **Fig.** 1 wählt irgendeines der durch die Synchronisationssignal-Erzeugungsschaltung **20** erzeugten Synchronisationssignale nach jedem Zug der 8-16-Modulations-Signale, die vom 8-16-Modulator **10** sequentiell geliefert werden, nämlich nach jeweils 91 Codewörtern, aus und erzeugt ein Signal, das erhalten wird, indem das ausgewählte Synchronisationssignal zum Kopf der 91 Codewörter hinzugefügt wird, als ein Übertragungssignal, das einem Synchronisationsrahmen entspricht.

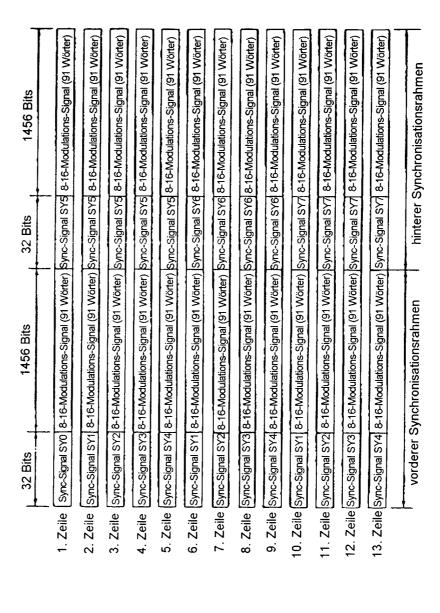

**[0042] Fig.** 6 ist eine graphische Darstellung, die ein Format des Übertragungssignals für einen Sektor zeigt, das durch die Synthetisierungsschaltung **30** erzeugt wird.

**[0043]** Wie in **Fig.** 6 gezeigt ist, umfasst ein Sektor 13 Zeilen. Jeder Zeile sind zwei Synchronisationsrahmen zugewiesen. Das jedem Synchronisationsrahmen zugewiesene Synchronisationssignal wird aus den 32 Arten der Synchronisationssignale ausgewählt, die in den **Fig.** 2 und 3 gezeigt sind. Das einem vorderen Synchronisationsrahmen der ersten Zeile zugewiesene Synchronisationssignal entspricht z. B. dem aus den 32 Arten der Synchronisationssignale ausgewählten SY0. Anschließend an die erste Zeile wird das Synchronisationssignal, dass dem vorderen Synchronisationsrahmen zugewiesen ist, in Übereinstimmung mit einer Zunahme der Zeilennummer zyklisch wiederholt, wie SY1 bis SY4. Die Unterschiede zwischen SY1 bis SY4 werden durch den bestimmten Code und die Verbindungsbits bestimmt.

**[0044]** Die Operation der Synthetisierungsschaltung **30** zum Bilden des Übertragungssignals eines Sektors wird nun unter Bezugnahme auf einen Ablauf nach **Fig.** 7 beschrieben.

**[0045]** Eine CPU (Zentraleinheit) und ein Speicher (die nicht gezeigt sind) sind in der Synthetisierungsschaltung **30** enthalten, wobei die Informationen, wie in **Fig.** 8 gezeigt ist, vorausgehend im Speicher gespeichert worden sind.

**[0046]** Im Ablauf nach **Fig.** 7 setzt die CPU in der Synthetisierungsschaltung **30** zuerst 1 als eine Anfangsadresse in ein eingebautes Register n (Schritt S1). Die CPU liest die Informationen, die der Adresse entsprechen, die im Register n gespeichert ist, jeweils aus dem in **Fig.** 8 gezeigten Speicher aus und speichert die Informationen in den Registern X und Y (Schritt S2). Wenn z. B. im Register n 1 gespeichert worden ist, werden die bei der Adresse 1 im Speicher in **Fig.** 8 gespeicherten SYO und SY5 ausgelesen und in den Registern X

bzw. Y gespeichert.

[0047] Die CPU wählt das Synchronisationssignal, das den Speicherinhalten im Register X entspricht, aus den in den Fig. 2 und 3 gezeigten 32 Arten der Synchronisationssignale aus, die von der Synchronisationssignal-Erzeugungsschaltung 20 geliefert werden. Wenn z. B. SY0 im Register X gespeichert worden ist, wird das SY0 entsprechende Signal aus den in den Fig. 2 und 3 gezeigten 32 Arten der Synchronisationssignale ausgewählt. Wenn das Codewort, das direkt vor dem Synchronisationssignal vorhanden ist, Next State1 (die Anzahl der fortlaufenden 0 am Ende ist gleich 1 oder 0) oder Next State2 (die Anzahl der fortlaufenden 0 am Ende ist gleich 2 bis 5) ist, wählt die CPU aus den in den Fig. 2 und 3 gezeigten SY0 das Synchronisationssignal aus, in dem das Verbindungsbitmuster durch die Bits 1 bis 3 auf {000} gesetzt ist. Es gibt in Fig. 2 die folgenden zwei Arten der Synchronisationssignale SY0, denen das Verbindungsbitmuster gleich {000} ist:

{0001001000001000000000000010001}

**[0048]** Das heißt, nur die Werte des Bits 10 in den bestimmten Codes unterscheiden sich in Bezug auf die zwei Synchronisationssignale SY0, wobei die Anzahl der Invertierungen von ihnen sich unterscheidet, wenn sie NZI-moduliert werden. Die CPU wählt das Muster, das für die Gleichstromunterdrückung optimal ist, aus den zwei Arten der Muster aus, und setzt das ausgewählte Muster auf das endgültige SY0.

[0049] Die CPU wählt das Synchronisationssignal aus, das den Speicherinhalten im Register Y entspricht. Wenn z. B. im Register Y SY5 gespeichert worden ist, wird das SY5 entsprechende Synchronisationssignal aus den in den Fig. 2 und 3 gezeigten 32 Arten der Synchronisationssignale ausgewählt. Wenn das Codewort, das direkt vor dem Synchronisationssignal vorhanden ist, Next\_State3 (die Anzahl der fortlaufenden 0 am Ende ist gleich 2 bis 5) oder Next\_State4 (die Anzahl der fortlaufenden 0 am Ende ist gleich 6 bis 9) ist, wählt die CPU aus den in den Fig. 2 und 3 gezeigten SY5 das Synchronisationssignal aus, in dem das Verbindungsbitmuster durch die Bits 1 bis 3 gleich {100} ist. Es gibt in Fig. 3 die folgenden zwei Arten der Synchronisationssignale, denen das Verbindungsbitmuster gleich {100} ist:

**[0050]** Das heißt, nur die Werte des Bits 5 in den bestimmten Codes unterscheiden sich in Bezug auf die beiden Muster. Die CPU wählt das Muster, das für die Gleichstromunterdrückung optimal ist, aus den zwei Arten der Muster aus, und setzt das ausgewählte Muster auf das endgültige SY5 (Schritt S3).

**[0051]** Die CPU erzeugt ein Muster, das durch das serielle Verbinden des 8-16-Modulations-Signals aus 91 Codewörtern mit jedem der auf der Grundlage der Speicherinhalte der Register X und Y ausgewählten Synchronisationssignale, wie oben erwähnt worden ist, erhalten wird, als ein Übertragungssignal einer Zeile, wie in **Fig.** 6 gezeigt des (Schritt S4).

**[0052]** Die CPU beurteilt, ob die Inhalte im Register n größer als 13 sind oder nicht (Schritt S5). Die CPU addiert 1 zu den Inhalten im Register n (Schritt S6), bis im Schritt S5 bestimmt wird, dass die Inhalte im Register n größer als 13 sind, wobei sie danach die Operationen im Schritt S2 und den nachfolgenden Schritten wiederholt ausführt. Die Übertragungssignale der ersten bis 13. Zeilen (von einem Sektor), wie in **Fig.** 6 gezeigt ist, werden durch die wiederholte Operation sequentiell erzeugt.

**[0053]** Wenn z. B. angenommen wird, dass 16 Sektoren als ein Fehlerkorrekturblock fehlerkorrektur-codiert werden und der resultierende Block übertragen wird, führt eine Decodiererseite, die das Übertragungssignal mit der Struktur empfängt, einen Fehlerkorrekturprozess unter Verwendung der Übertragungssignale aus, von denen jedes die Sektorstruktur besitzt, wie in **Fig.** 6 gezeigt ist, und die nach der Anzahl von nicht weniger als 16 Sektoren als ein Fehlerkorrekturblock gesammelt werden. Im Decodieren ist es wichtig, dass nach dem Abschluss des Empfangs des Übertragungssignals nach dem Kopf des Sektors gesucht wird, eine aufgezeichnete Adresse sofort unmittelbar ausgelesen wird und die Daten des Fehlerkorrekturblocks gesammelt werden. Wenn die Übertragung mit hoher Dichte ausgeführt wird, gibt es einen Fall, in dem das Synchronisationssignal SY0 als ein Kopf des Sektors nicht ausgelesen werden kann, oder einen Fall, in dem das andere Signal fälschlich als ein Sektorkopf ausgelesen wird, sodass eine Möglichkeit auftritt, sodass ein gravierender Fehler verursacht wird, der nicht korrigiert werden kann.

**[0054]** Im Übertragungssignal gemäß der Erfindung, wie in den **Fig.** 2 und 3 gezeigt ist, werden die 32 Arten der Synchronisationssignale mit verschiedenen Bitmustern vorbereitet, wobei ferner, wie in **Fig.** 6 gezeigt ist, das Kombinationsmuster des Synchronisationssignals, das jeder Zeile in einem Sektor zuzuweisen ist, in jeder

Zeile auf ein eindeutiges Muster gesetzt wird. Wie in **Fig.** 6 gezeigt ist, wird das Synchronisationssignal vor dem Synchronisationsrahmen, der am Kopf jeder Zeile vorhanden ist, in Übereinstimmung mit einer Zunahme der Zeilennummer zyklisch wiederholt, wie SY1 bis SY4.

**[0055]** Auf der Decodiererseite, die das Übertragungssignal mit der Struktur empfängt, kann die Zeile in einem Sektor spezifiziert werden, indem das Kombinationsmuster der Synchronisationssignafe erkannt wird, sodass die Position von SY0 am Sektorkopf vorhergesagt werden kann. Wenn die Zeile spezifiziert ist, kann ferner eine Verhinderungsfunktion für einen Lesefehler des Synchronisationssignals aufgestellt werden, indem die sich wiederholenden Muster von SY1 bis SY4 erkannt werden. Weil die Zeile auf der Grundlage des Kombinationsmusters der in einer Zeile vorhandenen zwei Synchronisationssignale spezifiziert ist, ist es ausreichend, acht Arten von SY0 bis SY7 als die Arten der Synchronisationssignale in einem Sektor zu verwenden.

**[0056]** Selbst wenn das Synchronisationssignal SY0 als ein Kopf des Sektors, verursacht durch den Einfluss durch die Übertragung mit hoher Dichte, nicht ausgelesen werden kann, wird deshalb auf der Decodiererseite die Kopfposition des Sektors auf der Grundlage des nach SY0 vorhandenen Synchronisationssignals erkannt, wobei dadurch ermöglicht wird, dass ein richtiger Fehlerkorrekturblock erkannt wird.

[0057] Wie durch die Fig. 2 und 3 offensichtlich selbstverständlich ist, wird ferner SY0 in einer Weise ausgewählt, sodass ein Zwischencodeabstand zwischen SY0 und den Kopfsynchronisationen (SY1 bis SY4) von jeder der anderen Zeilen maximal wird. Der Zwischencodeabstand bezeichnet eine Ähnlichkeit zwischen den Synchronisationssignalen. Wenn es ein Synchronisationssignal gibt, in dem sich die Anzahl der 1 von der des anderen Signals unterscheidet, wird bestimmt, dass das Synchronisationssignal ein Signal mit dem größten Abstand ist. Im Fall des Synchronisationssignals, in dem die Anzahl der 1 gleich der des anderen Synchronisationssignals ist, wird die Anzahl der Verschiebungen der Position der 1, bis das Signal mit einem Synchronisationssignal übereinstimmt, auf den Abstand zum Synchronisationssignal gesetzt. Durch das Bestimmen von SY0, wie oben erwähnt worden ist, wird die Wahrscheinlichkeit, sodass SY1 bis SY4 fehlerhaft als SY0 gelesen werden, verringert. Mit anderen Worten, dass Synchronisationssignal, dass zu SY0 relativ ähnlich ist, wird auf das Zwischen-Synchronisationssignal (SY5 bis SY7) jeder Zeile gesetzt, wobei ein gemeinsames Synchronisationssignal im Kopf und in den Mittelabschnitten der Zeile nicht verwendet wird. Wenn das gemeinsame Synchronisationssignal im Kopf und in den Mittelabschnitten der Zeile nicht verwendet wird, gibt es außerdem eine Wirkung, sodass eine Wahrscheinlichkeit, dass der Kopf und die Mittelabschnitte jeder Zeile fehlerhaft durch den Lesefehler erkannt werden, verringert ist.

**[0058]** Wie in den **Fig.** 2 und 3 gezeigt ist, werden, selbst wenn Next\_State des Codewortes direkt vor dem Synchronisationssignal irgendeinen eines Falles aus 1 oder 2 oder eines Falles aus 3 oder 4 anzeigt, zwei Arten von 32-Bit-Mustern, in denen die geraden und ungeraden Zahlen der Invertierungen (die Anzahl der 1) und die Vorzeichen des Unterschieds (ein Unterschied zwischen positiven und negativen Bits der Signalform) jeweils verschieden sind, SYO bis SY7 zugewiesen. Das heißt, im Vergleich zu einem Muster kann, weil die Polaritäten der Gleichstromkomponente des anderen Musters selbst und der Signalform des Signals am Ende des anderen Musters zu derjenigen des einen Musters entgegengesetzt sind, die Gleichstromkomponente des Signals verringert werden, indem irgendeines von ihnen ausgewählt wird.

**[0059]** Wie oben erwähnt worden ist, umfasst im Übertragungsverfahren für digitale Daten gemäß der Erfindung, wenn die digitalen Daten in den Sektoren gehalten werden, von denen jeder mehrere Synchronisationsrahmen umfasst, und sequentiell übertragen werden, der Synchronisationsrahmen das Synchronisationssignal und den lauflängenbegrenzten Code, der die Begrenzungen der minimale Lauflänge und der maximale Lauflänge erfüllt, wobei das Synchronisationssignal das Synchronisationsmuster, das das Bitmuster einer Lauflänge umfasst, die um 3T länger als die maximale Lauflänge ist, und die zusätzlichen Bitmuster, die vor und nach dem Bitmuster angeordnet sind, und von denen jedes eine Lauflänge besizt, die länger als die minimale Lauflänge ist, enthält.

**[0060]** Gemäß der Erfindung können deshalb das Synchronisationssignal mit dem Signal durch den lauflängenbegrenzten Code richtig unterschieden und erfasst werden, selbst wenn sie, verursacht durch den Einfluss einer Zwischensymbolstörurng, jeweils um 1T flankenverschoben sind.

**[0061]** Im Übertragungsverfahren für digitale Daten gemäß der Erfindung enthält das Synchronisationssignal den bestimmten Code, die Position im Sektor anzeigt und der ermöglicht, dass die Gleichstromsteuerung ausgeführt wird.

[0062] Mit der Konstruktion kann deshalb, selbst wenn das Synchronisationssignal am Kopf des Sektors nicht

ausgelesen werden kann oder das andere Signal fehlerhaft als ein Sektorkopf ausgelesen wird, ein richtiger Kopf des Sektors auf der Grundlage der anderen Synchronisationssignale vorhergesagt werden, sodass die digitalen Daten richtig reproduziert werden können.

**[0063]** Die Erfindung ist oben unter Bezugnahme auf ihre bevorzugte Ausführungsform beschrieben worden. Es ist selbstverständlich, dass durch die Fachleute auf dem Gebiet viele Modifikationen und Variationen ausgeführt werden können.

#### Patentansprüche

- 1. Übertragungsverfahren, das umfasst: Übertragen von digitalen Daten, um digitale Daten in Sektoren zu halten, die jeweils mehrere Synchronisationsrahmen enthalten, und um die digitalen Daten sequentiell zu übertragen, wobei das Format der digitalen Daten derart ist, dass

- der Synchronisationsrahmen ein Synchronisationssignal und einen lauflängenbegrenzten Code enthält, der den digitalen Daten entspricht und Begrenzungen einer minimalen Lauflänge und einer maximalen Lauflänge erfüllt, und **dadurch gekennzeichnet**, dass

- das Synchronisationssignal ein Synchronisationsmuster enthält, das ein Bitmuster einer Lauflänge, die um 3T länger als die maximale Lauflänge ist, wobei T eine fundamentale Zeitspanne ist, die einem binären Symbol entspricht, um selbst bei Auftreten einer Flankenverschiebung zwischen dem Synchronisationsmuster und der maximalen Lauflänge unterscheiden zu können, und ferner zusätzliche Bitmuster, die vor und nach dem Synchronisationsmuster angeordnet sind und wovon jedes eine Lauflänge besitzt, die länger als die minimale Lauflänge ist, umfasst.

- 2. Verfahren nach Anspruch 1, bei dem unter den zusätzlichen Bitmustern das nach dem Bitmuster angeordnete zusätzliche Bitmuster eine feste Länge besitzt.

- 3. Verfahren nach Anspruch 1, bei dem der lauflängenbegrenzte Code ein Code ist, der durch 8-16-Modulation der digitalen Daten nach jeweils acht Bits erhalten wird, um Lauflängenbegrenzungen der minimalen Lauflänge, die 2 ist, und der maximalen Lauflänge, die 10 ist, zu erfüllen, und das Synchronisationsmuster Bitmuster mit Lauflängen von (4T oder mehr 14T 4T) umfasst.

- 4. Verfahren nach Anspruch 1, bei dem die Lauflänge des Synchronisationsmusters um 3T länger als die maximale Lauflänge ist, wobei T eine fundamentale Zeitspanne ist, die einem binären Symbol entspricht.

- 5. Verfahren nach Anspruch 1, bei dem der Synchronisationsrahmen ein Synchronisationssignal und einen lauflängenbegrenzten Code umfasst, der den digitalen Daten entspricht und Begrenzungen einer minimalen Lauflänge und einer maximalen Lauflänge erfüllt, und bei dem das Synchronisationssignal einen bestimmten Code enthält, der eine Position des Synchronisationssignals in dem Sektor angibt.

- 6. Verfahren nach Anspruch 5, bei dem der Sektor mehrere Zeilen umfasst, wovon jede durch die zwei Synchronisationsrahmen gebildet ist, und eine Position in dem Sektor durch den bestimmten Code, der in jedem der zwei in jeder Zeile enthaltenen Synchronisationssignale enthalten ist, identifiziert wird.

- 7. Verfahren nach Anspruch 6, bei dem jedes der zwei in jeder Zeile enthaltenen Synchronisationssignale mit zunehmender Anzahl der Zeilen auf der Grundlage des in dem Synchronisationssignal enthaltenen bestimmten Codes zyklisch wiederholt wird.

- 8. Verfahren nach Anspruch 5, bei dem der bestimmte Code in dem Synchronisationssignal, das am Kopf einer ersten Zeile des Sektors angeordnet ist, ein Bitmuster besitzt, in dem ein Zwischencodeabstand für das am Kopf der anderen Zeile angeordnete Synchronisationssignal maximal wird.

- 9. Verfahren nach Anspruch 5, bei dem durch die Bitmuster des bestimmten Codes eine Gleichstromsteuerung ausgeführt werden kann.

- 10. Verfahren nach Anspruch 9, bei dem zwei Arten von Codes, die jeweils eine unterschiedliche Anzahl von Invertierungszeiten besitzen, wenn sie NRZImoduliert werden, als der bestimmte Code ausgewählt werden können, um dadurch die Gleichstromsteuerung auszuführen.

- 11. Verfahren nach Anspruch 6, bei dem der Sektor 13 Zeilen umfasst, wovon jede durch die beiden Synchronisationsrahmen gebildet ist, und

das Synchronisationssignal 32 Arten von Bitmustern besitzt, um die Begrenzungen der minimalen Lauflänge und der maximalen Lauflänge zu erfüllen, den Kopf des Sektors und jeder Zeile zu spezifizieren und die Gleichstromsteuerung in Verbindung mit dem lauflängenbegrenzten Code, der direkt vor dem Synchronisationssignal vorhanden ist, auszuführen.

#### 12. Verfahren nach Anspruch 8, bei dem

der Sektor 13 Zeilen umfasst, wovon jede durch die beiden Synchronisationsrahmen gebildet ist, und das Synchronisationssignal 32 Arten von Bitmustern besitzt, um die Begrenzungen der minimalen Lauflänge und der maximalen Lauflänge zu erfüllen, den Kopf des Sektors und jede Zeile zu spezifizieren und die Gleichstromsteuerung in Verbindung mit dem lauflängenbegrenzten Code, der direkt vor dem Synchronisationssignal vorhanden ist, auszuführen.

#### 13. Verfahren nach Anspruch 9, bei dem

der Sektor 13 Zeilen umfasst, wovon jede durch die beiden Synchronisationsrahmen gebildet ist, und das Synchronisationssignal 32 Arten von Bitmustern besitzt, um die Begrenzungen der minimalen Lauflänge und der maximalen Lauflänge zu erfüllen, den Kopf des Sektors und jede Zeile zu spezifizieren und die Gleichstromsteuerung in einer Verbindung mit dem lauflängenbegrenzten Code, der direkt vor dem Synchronisationssignal vorhanden ist, auszuführen.

#### 14. Übertragungsverfahren nach Anspruch 5, bei dem

der Synchronisationsrahmen ein Synchronisationssignal aus 32 Bits und einem lauflängenbegrenzten Code, der durch 8-16-Modulation der digitalen Daten nach jeweils acht Bits erhalten wird, umfasst, um Lauflängenbegrenzungen einer minimalen Lauflänge, die 2 ist, und einer maximalen Lauflänge, die 10 ist, zu erfüllen, und das Synchronisationssignal umfasst: ein Verbindungsbit aus drei Bits, die so angeordnet sind, dass die Begrenzungen der minimalen Lauflänge, die 2 ist, und der maximalen Lauflänge, die 10 ist, in einer Verbindung mit dem direkt vor dem Synchronisationssignal vorhandenen lauflängenbegrenzten Code erfüllt werden; einen bestimmten Code aus 7 Bits, der die Begrenzungen der minimalen Lauflänge, die 2 ist, und der maximalen Lauflänge, die 10 ist, erfüllt und 32 Arten von Bitmustern besitzt; und Synchronisationsmuster mit Lauflängen von (4T oder mehr – 14T – 4T).

15. Verfahren nach Anspruch 14, bei dem das Synchronisationssignal 32 Arten von Bitmustern besitzt, die in der folgenden Tabelle 1 und in der folgenden Tabelle 2 gezeigt sind, und eine Anordnung aus dem Synchronisationssignal in jeder Zeile des Sektors gleich einer Anordnung ist, die in der folgenden Tabelle 3 gezeigt ist:

Tabelle 1

| SYO  | 0001001001000100 00000000000010001      | 0001001000000100 00000000000010001 |

|------|-----------------------------------------|------------------------------------|

| SY1  | 000001000000000000000000000000000000000 | 0000010001000100 00000000000010001 |

| SY2  | 00010000000000100 00000000000010001     | 0001000001000100 00000000000010001 |

| 5Y3  | 000010000000000000000000000000000000000 | 0000100001000100 0000000000010001  |

| SY4. | 001000000000000000000000000000000000000 | 0010000001000100 00000000000010001 |

| SY5  | 0010001001000100 0000000000010001       | 0010001000000100 0000000000010001  |

| SYG  | 001001001000100 00000000000010001       | 0010000010000100 00000000000010001 |

| SY7  | 0010010001000100 000000000000010001     | 0010010000000100 0000000000010001  |

Tabelle 2

| SYI 1000010001000100000000000000000000000                                      |      | <del></del>                        |                                         |

|--------------------------------------------------------------------------------|------|------------------------------------|-----------------------------------------|

| SYI 1000010001000100000000000000000000000                                      | SYO  | 1001001000000100 0000000000010001  | 1001001001000100 000000000000001        |

| SY3 10000100100100010000000000000010001 1000010000000000000000000000000000000  | SYL  | 100010001000100 000000000010001    | 1000010000000100 00000000000010001      |

| SY3 100000100100100010000000000000010001 1000001000000000000000000000000000000 | SYZ  | 1001000001000100 00000000000010001 | 1001000000000100 0000000000010001       |

| SY4 1000100001000010000000000000000000000                                      | SY3  | 1000001001000100 0000000000010001  | 100000100000000000000000000000000000000 |

| 100000100000000000000000000000000000000                                        | SY4  | 1000100001000100 0000000000010001  | 1000100000000100 0000000000010001       |

| 2AQ 1001000010000100 00000000000001 1000000                                    | SY5  | 100010010000100 0000000000010001   | 1000000100000100 00000000000010001      |

|                                                                                | 23.6 | 100100001000100 00000000000010001  | 1000000001000100 0000000000010001       |

| SY7 100010001000100 0000000000010001 1000000                                   | SY7  | 1000100010000100 000000000010001   | 100000010000100 00000000000010001       |

Tabelle 3

|           | 32 Bits         | 1456 Bits                 | 32 Bits         | 1456 Bits                 |

|-----------|-----------------|---------------------------|-----------------|---------------------------|

| 1. Zeile  | Sync-Signal SY0 | lauflängenbegrenzter Code | Sync-Signal SY5 | lauflängenbegrenzter Code |

| 2. Zeile  | Sync-Signal SY1 | lauflängenbegrenzter Code | Sync-Signal SY5 | lauflängenbegrenzter Code |

| 3. Zeile  | Sync-Signal SY2 | lauflängenbegrenzter Code | Sync-Signal SY5 | lauflängenbegrenzter Code |

| 4. Zeile  | Sync-Signal SY3 | lauflängenbegrenzter Code | Sync-Signal SY5 | lauflängenbegrenzter Code |

| 5. Zeile  | Sync-Signal SY4 | lauflängenbegrenzter Code | Sync-Signal SY5 | lauflängenbegrenzter Code |

| 6. Zeile  | Sync-Signal SY1 | lauflängenbegrenzter Code | Sync-Signal SY6 | lauflängenbegrenzter Code |

| 7. Zeile  | Sync-Signal SY2 | lauflängenbegrenzter Code | Sync-Signal SY6 | lauflängenbegrenzter Code |

| 8. Zeile  | Sync-Signal SY3 | lauflängenbegrenzter Code | Sync-Signal SY6 | lauflängenbegrenzter Code |

| 9. Zeile  | Sync-Signal SY4 | lauflängenbegrenzter Code | Sync-Signal SY6 | lauflängenbegrenzter Code |

| 10. Zeile | Sync-Signal SY1 | lauflängenbegrenzter Code | Sync-Signal SY7 | lauflängenbegrenzter Code |

| 11. Zeile | Sync-Signal SY2 | lauflängenbegrenzter Code | Sync-Signal SY7 | lauflängenbegrenzter Code |

| 12. Zeile | Sync-Signal SY3 | lauflängenbegrenzter Code | Sync-Signal SY7 | lauflängenbegrenzter Code |

| 13. Zeile | Sync-Signal SY4 | lauflängenbegrenzter Code | Sync-Signal SY7 | lauflängenbegrenzter Code |

|           | vorderer S      | ynchronisationsrahmen     | hinterer S      | Synchronisationsrahmen    |

Es folgen 8 Blatt Zeichnungen

#### Anhängende Zeichnungen

| -          |        |        |                                                                                |            |                                       |

|------------|--------|--------|--------------------------------------------------------------------------------|------------|---------------------------------------|

|            |        | Syr    | Synchronisationssignal, wenn das Codewort direkt davor NEXT_STATE 1 oder 2 ist | ort direkl | davor NEXT_STATE 1 oder 2 ist         |

|            | Bit    |        | Bit                                                                            | Bit        | Bit                                   |

|            | 1234   |        | 101                                                                            | 1234       | 4 101 32                              |

| SYO        | 1000   | 0      | 01001000100 00000000000010001                                                  | ·          | 00010010000000100 0000000000010001    |

| SYI        | 00000  |        | 100000000000000000000000000000000000000                                        | 000        | 0000010001000100 0000000000010001     |

| SY2        | 0001   | 0      | 000000000000000000000000000000000000000                                        |            | 0001000001000100 00000000000010001    |

| <b>SY3</b> | 0000   | -      | 000000000100 00000000000010001                                                 |            | 0000100001000100 00000000000000010001 |

| <b>SY4</b> | 00100  |        | 000000000000000000000000000000000000000                                        |            | 0010000001000100 00000000000010001    |

| <b>SYS</b> | 00 100 | ~ '    | 01001000100 0000000000010001                                                   |            | 00100010000000100 00000000000010001   |

| SY6        | 0010   |        | 110010000000000000000000000000000000000                                        |            | 0010000010000100 000000000000010001   |

| SY7        | 00100  | 001001 | 31 000 1000 100 00000000000000000000000                                        |            | 00100100000000100 0000000000000010001 |

| The second of the second of the | S         | Synchronisationssignal, wenn das Codewort direkt davor NEXT_STATE 3 oder 4 ist | direkt davor NEXT_STATE 3 oder 4 ist    |

|---------------------------------|-----------|--------------------------------------------------------------------------------|-----------------------------------------|

|                                 | Bit       | Bit                                                                            | Bit                                     |

|                                 | 1234      | तः ।।।।                                                                        | 1234 1011 32                            |

| SYO                             | 100100100 | 001000000100 00000000000010001                                                 | 1001001001000100 0000000000001001       |

| SY1                             | 100001000 | 010001000100 0000000000010001                                                  | 100001000000000000000000000000000000000 |

| SY2                             | 100100000 | 000001000100 0000000000010001                                                  | 100110000000000000000000000000000000000 |

| SYS                             | 100000100 | 001001000100 00000000000010001                                                 | 100001000000000000000000000000000000000 |

| 5 Y 4                           | 100010001 | 100001000100 0000000000010001                                                  | 1,0001000000000000000000000000000000000 |

| SY5                             | 10001001  | 100100000100 00000000000010001                                                 | 100000000000000000000000000000000000000 |

| S Y 6                           | 100100001 | 000010000100 00000000000010001                                                 | 100000000000000000000000000000000000000 |

| SY7                             | 100010001 | 100010000000000000000000000000000000000                                        |                                         |

FIG.5

| 1  | SYO   | S Y 5 |

|----|-------|-------|

| 2  | SY1   | S Y 5 |

| 3  | S Y 2 | S Y 5 |

| 4  | SY3   | S Y 5 |

| 5  | SY4   | S Y 5 |

| 6  | S Y 1 | SY6   |

| 7  | S Y 2 | SY6   |

| 8  | SY3   | SY6   |

| 9  | SY4   | SY6   |

| 10 | SY1   | S Y 7 |

| 11 | 5 Y 2 | SY7   |

| 12 | S Y 3 | S Y 7 |

| 13 | S Y 4 | S Y 7 |

|    | ·     |       |