(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2011년01월28일

(11) 등록번호 10-1010320

(24) 등록일자 2011년01월17일

(51) Int. Cl.

G11C 11/15 (2006.01)

(21) 출원번호 10-2003-0025986

(22) 출원일자 2003년04월24일

심사청구일자 2008년03월31일

(65) 공개번호 10-2003-0084730

(43) 공개일자 2003년11월01일

(30) 우선권주장

10/132,998 2002년04월25일 미국(US)

(56) 선행기술조사문헌

JP03003255 A\*

JP07263631 A\*

JP14118239 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

바타차리야마노즈

미국캘리포니아주95014쿠퍼티노팜애비뉴22434

안토니토마스씨

미국캘리포니아주94087서니베일피멘토애비뉴1161

(74) 대리인

권혁수, 송윤호, 오세준

전체 청구항 수 : 총 10 항

심사관 : 윤난영

(54) 도전체 구조체

### (57) 요 약

자기 메모리용 도전체 구조체가 개시되어 있다. 도전체 구조체는 도전체(21,23)가 메모리 셀(20)을 가로지는 방향( $D_W, D_L$ )으로 메모리 셀(20)의 치수( $W, L$ )보다 작은 폭( $W_1, W_2$ )을 갖는 하나 이상의 도전체(21,23)를 포함한다. 도전체 두께( $t_1, t_2$ )는 도전체(21,23)의 단면적( $A_1, A_2$ )을 감소시키고 도전체(21,23) 내의 전류 밀도( $J_1, J_2$ )를 증가시키도록 선택된다. 메모리 셀(20)의 데이터 층(11)에서 변경 가능한 자화 배향(17)을 회전시키는 데 충분한 자기장( $H_1, H_2$ )은 증가된 전류 밀도( $J_1, J_2$ )로 인해 도전체에 흐르는 감소된 크기의 전류( $I_1, I_2$ )에 의해 발생될 수 있다. 이와 달리, 전류( $I_1, I_2$ )의 크기는 도전체(21,23)의 두께를 증가시켜 그것의 면적( $A_1, A_2$ )을 증가시키고 전자 흐름에 대한 그것의 저항을 감소시킴으로써 또한 도전체(21,23)를 부분적으로 클래딩하여 도전체(21,23) 주변의 총 자속 경로를 감소시켜 자기장( $H_1, H_2$ )을 증가시킴으로써 감소될 수 있다.

대 표 도 - 도5a

## 특허청구의 범위

### 청구항 1

폭(W), 길이(L)를 갖고, 변경가능한 자화 배향(17)에 따라 데이터 비트를 저장하는 데이터 층(11)을 포함하는 자기장 감지 메모리 셀(20)을 복수로 구비한 자기 메모리 장치용 도전체 구조체에 있어서,

폭 방향(D<sub>W</sub>)으로 상기 메모리 셀(20)을 가로지르고 그 내부를 흐르는 제 1 전류(I<sub>1</sub>)에 응답하여 제 1 자기장(H<sub>1</sub>)을 발생시키는 제 1 도전체(21)- 상기 제 1 도전체(21)는 제 1 단면적(A<sub>1</sub>)을 정의하는 제 1 폭(W<sub>1</sub>) 및 제 1 두께(t<sub>1</sub>), 상면(21t), 상기 메모리 셀(20)의 폭(W) 내에 배치된 두 개의 측면(21s), 상기 메모리 셀(20)에 인접하게 배치된 바닥면(21b)을 포함하고, 상기 제 1 도전체(21)는 S<sub>1</sub>만큼 이격된 다수의 세그먼트(22)로 분할되어 상기 각 메모리 셀(20)이 상기 다수의 세그먼트(22)와 중첩됨 -와,

길이 방향(D<sub>L</sub>)으로 상기 메모리 셀(20)을 가로지르고 그 내부를 흐르는 제 2 전류(I<sub>2</sub>)에 응답하여 제 2 자기장(H<sub>2</sub>)을 발생시키는 제 2 도전체(23)- 상기 제 2 도전체(23)는 제 2 단면적(A<sub>2</sub>)을 정의하는 제 2 폭(W<sub>2</sub>) 및 제 2 두께(t<sub>2</sub>), 상면(23t), 두 개의 측면(23s), 상기 메모리 셀(20)에 인접하게 배치된 바닥면(23b)을 포함하되, 상기 제 2 폭(W<sub>2</sub>)은 상기 메모리 셀(20)의 상기 길이(L)보다 더 크거나 동일함 -를 포함하되,

상기 제 1 및 제 2 자기장(H<sub>1</sub>, H<sub>2</sub>)은 데이터 층(11)과 협조적으로 상호 작용하여 상기 변경가능한 자화 배향(17)을 회전시키고,

상기 제 1 두께(t<sub>1</sub>) 및 제 1 폭(W<sub>1</sub>)은 상기 제 2 자기장(H<sub>2</sub>)과 협력하여 상기 변경가능한 자화 배향(17)을 회전시키는 데 충분한 크기의 제 1 자기장(H<sub>1</sub>)이 감소된 크기의 상기 제 1 전류(I<sub>1</sub>)에 의해 발생되도록 상기 제 1 단면적(A<sub>1</sub>)을 감소시키고 상기 제 1 도전체(21)의 전류 밀도(J<sub>1</sub>)를 증가시키게 사전 선택되는 도전체 구조체.

### 청구항 2

제 1 항에 있어서,

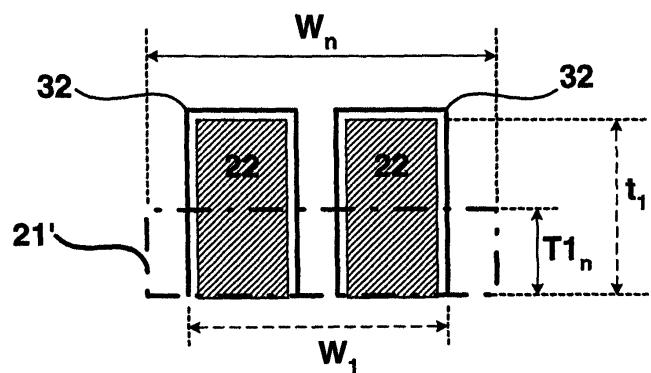

상기 제 1 폭(W<sub>1</sub>)은 표준 폭(W<sub>n</sub>)보다 작고 상기 제 1 두께(t<sub>1</sub>)는 제 1 표준 두께(T<sub>1n</sub>)보다 작은 도전체 구조체.

### 청구항 3

청구항 3은(는) 설정등록료 납부시 포기되었습니다.

제 2 항에 있어서,

상기 제 1 폭(W<sub>1</sub>)은 상기 표준 폭(W<sub>n</sub>)보다 0.60 이하의 팩터만큼 작고 상기 제 1 두께(t<sub>1</sub>)는 상기 제 1 표준 두께(T<sub>1n</sub>)보다 0.50 이하의 팩터만큼 작은 도전체 구조체.

### 청구항 4

삭제

### 청구항 5

제 1 항에 있어서,

상기 제 2 도전체(23)의 상기 두 개의 측면(23s)은 상기 메모리 셀(20)의 상기 길이(L) 내에 배치되고 상기 제 2 두께( $t_2$ ) 및 상기 제 2 폭( $W_2$ )은 상기 제1 자기장( $H_1$ )과 협력하여 상기 변경가능한 자기 배향(17)을 회전시키는 데 충분한 크기의 상기 제 2 자기장( $H_2$ )이 상기 감소된 크기의 상기 제 2 전류( $I_2$ )에 의해 발생되도록 상기 제 2 단면적( $A_2$ )을 감소시키고 상기 제 2 도전체(23)의 전류 밀도를 증가시키게 사전선택되는 도전체 구조체.

### 청구항 6

제 5 항에 있어서,

상기 제 2 폭( $W_2$ )은 표준 길이(L)보다 작고 상기 제 2 두께( $t_2$ )는 제 2 표준 두께( $T2n$ )보다 작은 도전체 구조체.

### 청구항 7

청구항 7은(는) 설정등록료 납부시 포기되었습니다.

제 6 항에 있어서,

상기 제 2 폭( $W_2$ )은 상기 표준 길이( $L_n$ )보다 0.60 이하의 팩터만큼 작고 상기 제 2 두께( $t_2$ )는 상기 제 2 표준 두께( $T2n$ )보다 0.50 이하의 팩터만큼 작은

도전체 구조체.

### 청구항 8

제 5 항에 있어서,

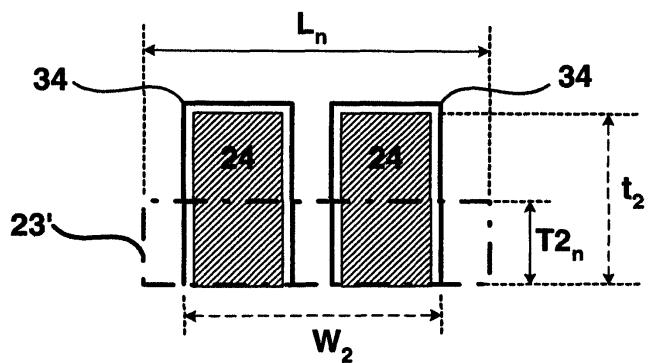

상기 제 2 도전체(23)는  $S_2$ 만큼 이격된 다수의 세그먼트(24)로 분할되는 도전체 구조체.

### 청구항 9

삭제

### 청구항 10

폭( $W$ ), 길이(L)를 갖고 변경가능한 자화 배향(17)에 따라 데이터 비트를 저장하는 데이터 층(11)을 갖는 자기장 감지 메모리 셀(20)을 구비한 자기 메모리 장치용 도전체 구조체에 있어서,

폭 방향( $D_W$ )으로 상기 메모리 셀(20)을 가로지르고 그 내부를 흐르는 제 1 전류( $I_1$ )에 응답하여 제 1 자기장( $H_1$ )을 발생시키는 제 1 도전체(21)- 상기 제 1 도전체(21)는 제 1 단면적( $A_1$ )을 정의하는 제 1 폭( $W_1$ ) 및 제 1 두께( $t_1$ ), 상면(21t), 상기 메모리 셀(20)의 폭( $W$ ) 내에 배치된 두 개의 측면(21s), 상기 메모리 셀(20)에 인접하게 배치된 바닥면(21b)을 포함함 -와,

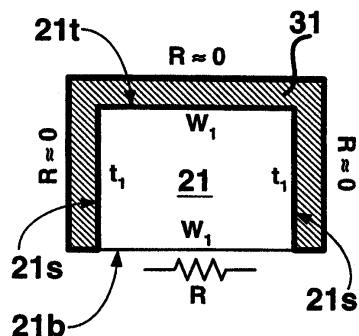

상기 상면(21t), 상기 두 개의 측면(21s), 및 상기 상면(21t)과 상기 두 개의 측면(21s)으로 구성된 그룹으로부터 선택된 한 표면 상에서 상기 제 1 도전체(21)를 커버하는 제 1 클래딩 층(31)과,

길이 방향( $D_L$ )으로 상기 메모리 셀(20)을 가로지르고 그 내부를 흐르는 제 2 전류( $I_2$ )에 응답하여 제 2 자기장( $H_2$ )을 발생시키는 제 2 도전체(23)- 상기 제 2 도전체(23)는 제 2 단면적( $A_2$ )을 정의하는 제 2 폭( $W_2$ ) 및 제 2 두께( $t_2$ ), 상면(23t), 두 개의 측면(23s), 상기 메모리 셀(20)에 인접하게 배치된 바닥면(23b)을 포함함 -를 포함하되,

상기 제 1 및 제 2 자기장( $H_1, H_2$ )은 데이터 층(11)과 협조적으로 상호 작용하여 상기 변경가능한 자화 배향(17)을 회전시키고,

상기 제 1 두께( $t_1$ )는 상기 제 1 단면적( $A_1$ )을 증가시키고 상기 제 1 도전체(21)의 저항을 감소시키도록 사전선택되고, 상기 제 1 폭( $W_1$ )은 상기 제 2 자기장( $H_2$ )과 협력하여 상기 변경가능한 자화 배향(17)을 회전시키는 데 충분한 크기의 제 1 자기장( $H_1$ )이 감소된 크기의 상기 제 1 전류( $I_1$ ) 하에서 존재하도록 사전 선택되는 도전체 구조체.

### 청구항 11

제 10 항에 있어서,

상기 제 1 폭( $W_1$ )은 표준 폭( $W_n$ )보다 작고 상기 제 1 두께( $t_1$ )는 제 1 표준 두께( $T1n$ )보다 작은 도전체 구조체.

### 청구항 12

청구항 12은(는) 설정등록료 납부시 포기되었습니다.

제 11 항에 있어서,

상기 제 1 폭( $W_1$ )은 상기 표준 폭( $W_n$ )보다 0.60 이하의 팩터만큼 작고 상기 제 1 두께( $t_1$ )는 상기 제 1 표준 두께( $T1n$ )보다 1.50 이하의 팩터만큼 큰 도전체 구조체.

### 청구항 13

제 10 항에 있어서,

상기 제 1 도전체(21)는  $S_1$ 만큼 이격되고 클래딩된 다수의 세그먼트(22)로 분할되는 도전체 구조체.

### 청구항 14

제 10 항에 있어서,

상기 상면(23t), 상기 두 개의 측면(23s), 및 상기 상면(23t)과 상기 두 개의 측면(23s)으로 구성된 그룹으로부터 선택된 표면 상에서 상기 제 2 도전체(23)를 커버하는 제 2 클래딩 층(33)- 상기 제 2 클래딩 층(33)은 상기 제 2 자기장( $H_2$ )을 증가시킴 -을 더 포함하되,

상기 제 2 도전체(23)의 상기 두 개의 측면(23s)은 상기 메모리 셀(20)의 상기 길이(L) 내에 배치되고 상기 제 2 두께( $t_2$ )는 제 2 단면적 ( $A_2$ )을 증가시키고 상기 제 2 도전체(23)의 저항을 감소시키도록 사전선택되며, 상기 제 2 폭( $W_2$ )은 상기 제 1 자기장( $H_1$ )과 협력하여 상기 변경가능한 자화 배향(17)을 회전하는 데 충분한 크기의 상기 제 2 자기장( $H_2$ )이 감소된 크기의 상기 제 2 전류( $I_2$ ) 하에서 존재하도록 사전선택되는 도전체 구조체.

### 청구항 15

제 14 항에 있어서,

상기 제 2 폭( $W_2$ )은 표준 길이( $L_n$ )보다 작고 상기 제 2 두께( $t_2$ )는 제 2 표준 두께( $T2n$ )보다 큰 도전체 구조체.

### 청구항 16

청구항 16은(는) 설정등록료 납부시 포기되었습니다.

제 15 항에 있어서,

상기 제 2 폭( $W_2$ )은 상기 표준 길이( $L_n$ )보다 0.60 이하의 팩터만큼 작고 상기 제 2 두께( $t_2$ )는 상기 제 2 표준 두께( $T_{2n}$ )보다 1.50 이상의 팩터만큼 큰 도전체 구조체.

## 청구항 17

청구항 17은(는) 설정등록료 납부시 포기되었습니다.

제 14 항에 있어서,

상기 제 2 도전체(23)는  $S_2$ 만큼 이격되고 클래딩된 다수의 세그먼트(24)로 분할되는 도전체 구조체.

## 청구항 18

청구항 18은(는) 설정등록료 납부시 포기되었습니다.

제 17 항에 있어서,

상기 제 1 도전체(21)는  $S_1$ 만큼 이격되고 클래딩된 다수의 세그먼트(22)로 분할되는 도전체 구조체.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

[0025] 본 발명은 전반적으로 자기 메모리 장치용 도전체에 대한 것으로, 보다 구체적으로 도전체의 단면적이 감소하여 도전체 내 전류 밀도가 증가하거나 단면적이 증가하여 도전체 내 전자 흐름에 대한 저항이 감소하게 되고, 자기 메모리 장치에 데이터 비트를 기록하는 데 감소된 양의 전류가 요구되도록 도전체가 부분적으로 클래딩되어 자기장을 증가시키는 자기 메모리 장치용 도전체 구조체에 관한 것이다.

[0026] 자기 랜덤 액세스 메모리(MRAM)는 종래의 데이터 저장 기술에 대안을 제공할 수 있는 새롭게 대두되는 기술이다. MRAM은 DRAM과 같은 고속 액세스 시간 및 하드 디스크 드라이브와 같은 비휘발성 데이터 보존력을 포함하는 바람직한 특성을 가진다. MRAM은 데이터 층, 저장 층 또는 데이터 막으로서 지칭되는 패터닝된 박막 자기 소자에서 변경가능한 자화 배향에 따라 데이터 비트(즉, 정보)를 저장한다. 데이터 층은 이진수 일("1") 및 이진수 영("0")을 정의하는 안정적이고 구별되는 두 개의 자기 상태를 가지도록 설계된다. 데이터 비트는 데이터 층에 저장되지만, 완전한 자기 메모리 소자를 형성하기 위해서는 조심스럽게 제어된 자기 및 유전 박막 재료로 이루어진 다수의 층이 필요하다. 자기 메모리 소자에 대한 하나의 주요 형태는 스핀 터널링 장치이다. 스핀 터널링의 물리적 현상은 복잡하며 본 주제에 대한 상당한 문헌이 존재한다.

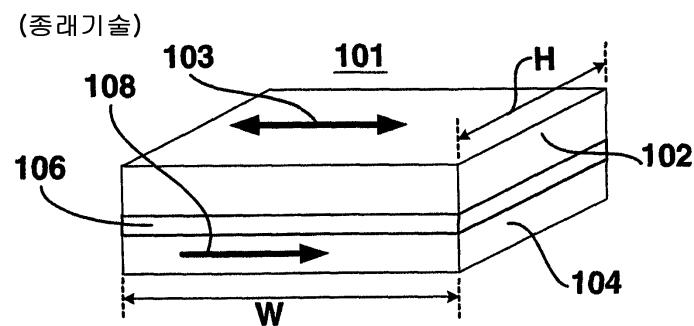

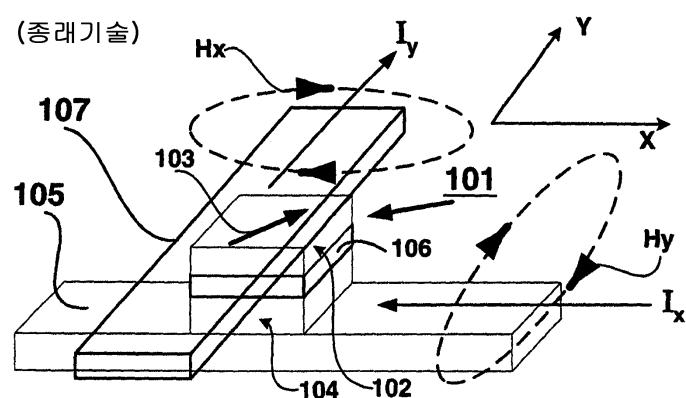

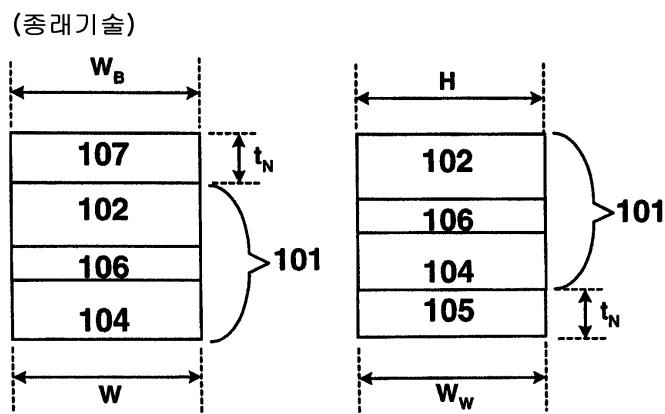

[0027] 도 1a에 있어서, 종래의 MRAM 메모리 소자(101)는 얇은 장벽 층(106)에 의해 분리되는 데이터 층(102) 및 기준 층(104)을 포함한다. 전형적으로 장벽 층(106)은 약 2.0 나노미터보다 작은 두께를 갖는다. 메모리 소자(101)는 폭( $W$ )과 높이( $H$ ) 및 종횡 비(즉, 종횡 비= $W \div H$ )를 정의하는 높이( $H$ )에 대한 폭( $W$ )의 비율을 갖는다. 터널링 자기저항(TMR) 구조체에 있어서, 장벽 층(106)은 예를 들어 알루미늄 산화물( $Al_2O_3$ )과 같은 전기적으로 비-도전성의 유전 재료이다. 이에 반해, 자이언트 자기저항(GMR) 구조체에 있어서, 장벽 층(106)은 예를 들어 구리(Cu)와 같은 도전성 재료의 얇은 층이다. 기준 층(104)은 고정된 자화 배향(108)을 갖는데, 즉 고정된 자화 배향(108)은 사전결정된 방향으로 고정되고 외부 자기장에 따라 회전하지 않는다. 이에 반해 데이터 층(102)은 외부 자기장에 따라 두 개의 배향 사이에서 회전할 수 있는 변경가능한 자화 배향(103)을 갖는다.

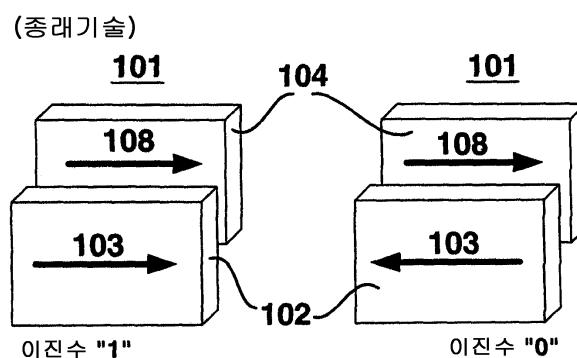

[0028] 도 1b에 있어서, 고정된 자화 배향(108) 및 변경가능한 자화 배향(103)이 동일한 방향을 가르킬 경우(즉 그들이 서로 평행할 경우) 데이터 층(102)은 이진수 일("1")을 저장한다. 또 한편으로, 고정된 자화 배향(108) 및 변경가능한 자화 배향(103)이 반대 방향을 가르킬 경우(즉 그들이 서로 반-평행(anti-parallel)할 경우) 데이터

총(102)은 이진수 영("0")을 저장한다.

[0029] 도 2에 있어서, 종래의 메모리 소자(101)는 전형적으로 두 개의 직교 도전체(105 및 107)의 교차부에 배치된다. 예를 들어, 도전체(105)는 워드 라인일 수 있고 도전체(107)는 비트 라인이 될 수 있다. 데이터 비트는 제각기의 도전체(107 및 105)에 흐르는 전류( $I_Y$  및  $I_X$ )에 의해 생성되는 두 개의 자기장( $H_X$  및  $H_Y$ )을 발생시킴으로써 메모리 소자(101)에 기록된다. 자기장( $H_X$  및  $H_Y$ )은 데이터 총(102)과 협조적으로 상호작용하여 변경가능한 자화 배향(103)을 그것의 현재의 배향에서 새로운 배향으로 회전시킨다. 그러므로, 현재의 배향이 이진수 "1"이 데이터 총(102)에 저장되도록 고정된 자화 배향(108)과 평행(즉, x축 상의 양의 x-방향)하면, 자기장( $H_X$  및  $H_Y$ )은 이진수 "0"이 데이터 총(102)에 저장되도록 변경가능한 자화 배향(103)을 반-평행 배향(즉, x축 상의 음의 x-방향)으로 회전시킬 것이다.

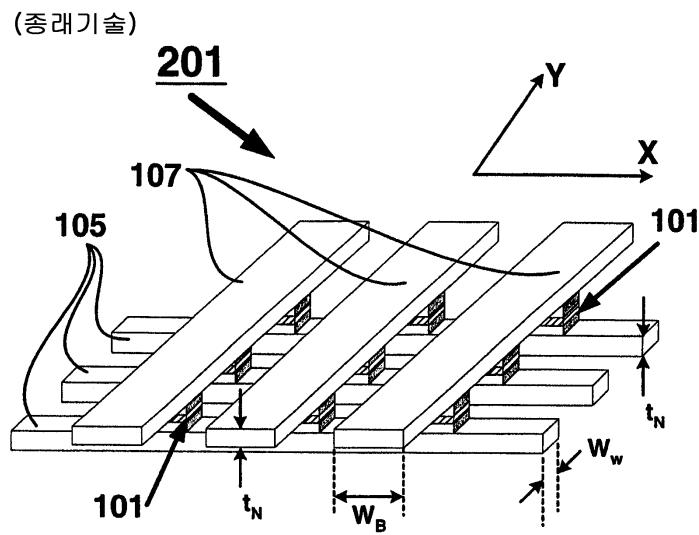

[0030] 도 3에 있어서, 종래의 메모리 소자(101)는 역시 행 및 열로 배열되는 다수의 도전체(107 및 105)의 교차부에 위치한 유사한 메모리 소자(101)의 큰 어레이(201)에 배치된다. 예시적으로, 도 3에 있어서, 도전체(107)는 비트 라인이고 도전체(105)는 워드 라인이다. 도전체(105, 107)는 메모리 소자(101)와 직접 접촉할 필요는 없다. 전형적으로, 하나 이상의 재료 층이 도전체(105, 107)를 데이터 총(102) 및 기준 총(104)으로부터 분리시킨다.

[0031] 데이터 비트는 전류( $I_Y$  및  $I_X$ )를 워드 및 비트 라인에 통과시킴으로써 워드 및 비트 라인의 교차부에 배치된 메모리 소자들(101) 중 선택된 소자에 기록된다. 정상적인 기록 동작 동안 결합 자기장( $H_X$  및  $H_Y$ )이 메모리 소자(101)의 변경가능한 자화 배향을 전환(즉, 회전)시킬만큼 충분한 크기일 경우에만 선택된 메모리 소자(101)에 기록될 것이다.

[0032] 종래의 메모리 소자(101)의 한가지 단점은 도전체(107 및 105)가  $t_N$ 으로 표시되는 표준 두께와 메모리 소자(101)의 폭( $W$ ) 및 높이( $H$ )와 실질적으로 동일한 폭( $W_B$  및  $W_W$ )을 각각 가진다는 것이다. 도 4에 있어서,  $y$ 축( $Y$ )에 따른 메모리 소자(101)의 단면도는 도전체(107)가 메모리 소자(101)의 폭( $W$ )과 실질적으로 동일한 폭( $W_B$ )을 갖는 것으로 도시되어 있다. 이와 유사하게,  $x$ 축( $X$ )에 따른 메모리 소자(101)의 단면도는 도전체(105)가 메모리 소자(101)의 높이( $H$ )와 실질적으로 동일한 폭( $W_W$ )을 갖는 것으로 도시되어 있다.

[0033] 위에서 언급한 두께( $t_N$ ) 및 폭( $W_B$  및  $W_W$ )으로 인해, 결합 자기장( $H_X$  및  $H_Y$ )을 발생시키기 위해 필요한 전류( $I_Y$  및  $I_X$ )의 크기는 높아진다. 높은 전류는 몇 가지 단점이 존재한다. 첫째, 이들 전류의 소싱(sourcing)용 트랜지스터 드라이버 회로는 필요한 전류량에 기초하여 크기가 주어진다. 따라서, 보다 큰 전류는 보다 큰 드라이버 회로를 요구한다. 메모리 소자(101)의 치수가 축소되어 면적 밀도가 증가함에 따라, 어레이(201)가 점유하는 면적의 양이 최소가 되도록 드라이버 회로의 크기도 감소시키는 것이 바람직하다.

[0034] 둘째, 전원이 전형적으로 배터리인 휴대용 전자 장치 응용에 있어서, 높은 전류 요구는 배터리 수명을 단축시키고 보다 크고 무거운 배터리를 요구할 수 있다. 무게, 크기를 감소시키고, 보다 긴 동작 시간의 배터리 수명을 증가시키는 것이 바람직하다.

[0035] 끝으로, 저 전력 응용에 있어서, 마이크로전자 장치에 의해 발생되는 폐열(waste heat)은 공급된 전류의 양에 비례한다. 그러므로, 폐열 발생은 전류가 커짐에 따라 증가한다. 과도한 폐열 발생은 장치의 온도를 상승시킬 수 있는데, 이는 종종 해로운 영향을 미친다.

[0036] Bhattacharyya 등 미국 특허 제 6,236,590 호는 도전체가 메모리 소자를 가로지르는 방향으로 메모리 소자의 폭 또는 길이 내에 도전체의 애지가 존재하도록 도전체의 폭을 감소시킴으로써 데이터 총을 스위칭하는 데 필요한 전류량이 감소되는 도전체 레이아웃 구조체를 개시한다. 그러나, 자기 메모리 소자의 치수가 지속적으로 축소됨에 따라 전류의 감소가 더 요구된다. 그러므로, MRAM 장치 내 기록 동작 동안 전류 소모를 더 감소시킬 여지가 존재한다.

[0037] 결과적으로, 메모리 셀의 데이터 총을 스위칭하기 위해 최적의 전류 사용을 제공하는 자기 메모리 셀용 도전체 구조체가 필요하다. 종래의 도전체 구조체보다 이용가능한 전류를 효과적으로 이용하는 자기 메모리 셀용 도전체 구조체가 필요하다. 높은 전류 드라이버 회로에 대한 필요성을 감소시키는 자기 메모리 셀용 도전체 구조체가 필요하다. 끝으로, 메모리 셀에 대한 기록 동작 동안 전류 소모를 더 감소시키는 자기 메모리 셀용 도전체 구조체가 필요하다.

### 발명이 이루고자 하는 기술적 과제

- [0038] 본 발명은 도전체에 흐르는 감소된 크기의 전류에 의해 메모리 셀의 데이터 층의 변경가능한 자화 배향을 스위칭하는 데 충분한 크기의 자기장이 생성될 수 있도록 도전체의 폭 및 두께가 감소되어 도전체의 전류 밀도를 증가시키는 도전체 구조체를 사용하여 위에서 언급한 필요성들을 해결한다. 본질적으로, 도전체 폭 및 두께가 감소함에 따라, 스위칭 전류 요구도 감소한다. 도전체 폭 및 두께의 감소는 표준 폭 및 표준 두께에 관련될 수 있다. 더 나아가, 도전체 폭 및 두께의 감소는 메모리 셀의 데이터 층에 데이터를 기록하는 하나 이상의 도전체에 적용할 수 있다.

- [0039] 본 발명의 또 다른 실시예에서, 도전체 내 전류 흐름에 대한 저항이 감소되도록 도전체의 폭은 감소되고 도전체의 두께는 증가된다. 도전체는 자기장이 증가되고 도전체에 흐르는 감소된 크기의 전류에 의해 메모리 셀의 데이터 층의 변경가능한 자화 배향을 스위칭하는데 충분한 크기의 자기장이 발생하도록 부드러운 자기 재료로 부분적으로 클래딩된다. 도전체 폭의 감소 및 도전체 두께의 증가는 표준 폭 및 표준 두께에 관련될 수 있다. 도전체 폭의 감소 및 도전체 두께의 증가는 메모리 셀의 데이터 층에 데이터를 기록하는 하나 이상의 도전체에 적용할 수 있다.

- [0040] 본 발명의 또 다른 실시예에서, 도전체는 두 개 이상의 이격된 세그먼트로 분할된다. 이격된 세그먼트는 부분적으로 클래딩될 수 있다.

- [0041] 본 발명의 다른 측면 및 장점은 본 발명의 원리를 예를 들어 도시하는 첨부한 도면과 연계한 후속하는 상세한 설명으로부터 분명해질 것이다.

### 발명의 구성 및 작용

- [0042] 후속하는 상세한 설명 및 몇몇 도면에 있어서, 유사한 소자는 유사한 참조 번호로 식별된다.

- [0043] 예시를 위해 도면에 도시된 바와 같이, 본 발명은 자기 메모리 장치용 도전체 구조체로 구현된다. 자기 메모리 장치는 폭, 길이 및 변경가능한 자화 배향에 따라 데이터 비트를 저장하는 데이터 층을 포함하는 자기장 감지 메모리 셀을 포함한다. 제 1 도전체는 폭 방향으로 메모리 셀을 가로지고 제 2 도전체는 길이 방향으로 메모리 셀을 가로지른다. 제 1 및 제 2 도전체는 제 1 도전체에 흐르는 제 1 전류에 응답하여 제 1 자기장을 발생시키고 제 2 도전체에 흐르는 제 2 전류에 응답하여 제 2 자기장을 발생시킨다. 제 1 및 제 2 자기장은 데이터 층과 협조적으로 상호 작용하여 변경가능한 자화 배향을 회전시켜 새로운 데이터 비트를 데이터 층에 기록한다.

- [0044] 제 1 도전체는 제 1 단면적, 상면, 메모리 셀의 폭 내에 배치되는 두 개의 측면 및 메모리 셀에 인접하게 배치되는 바닥면을 정의하는 제 1 폭 및 제 1 두께를 갖는다.

- [0045] 제 2 도전체는 제 2 단면적, 상면, 두 개의 측면 및 메모리 셀에 인접하게 배치되는 바닥면을 정의하는 제 2 폭 및 제 2 두께를 갖는다.

- [0046] 제 1 도전체의 제 1 두께는 제 1 단면적이 감소되어 제 1 도전체의 전류 밀도가 증가하도록 사전선택된다. 그 결과, 제 2 자기장과 협력하여 변경가능한 자화 배향을 회전시키는 데 충분한 크기의 제 1 자기장은 감소된 크기의 제 1 전류에 의해 발생된다. 따라서, 전력 소모는 감소하고 폐열 발생도 감소한다.

- [0047] 제 2 도전체의 두 개의 측면을 메모리 셀의 길이 내에 배치하고 제 2 단면적을 감소시키도록 제 2 두께를 사전 결정하여 제 2 도전체의 전류 밀도를 증가시킴으로써 전력 소모가 더 감소한다. 따라서, 제 1 자기장과 협력하여 변경가능한 자화 배향을 회전시키는 데 충분한 크기의 제 2 자기장은 감소된 크기의 제 2 전류에 의해 발생된다.

- [0048] 본 발명의 또 다른 실시예에서, 제 1 도전체의 두 개의 측면은 메모리 셀의 폭 내에 배치되고 제 1 도전체의 상면 및/또는 두 개의 측면은 제 1 자기장을 동작가능하게 증가시키는 제 1 클래딩 층으로 커버된다. 제 1 두께는 제 1 도전체의 저항이 감소되도록 제 1 단면적을 증가시키게 선택되고 제 2 자기장과 협력하여 변경가능한 자화 배향을 회전시키는 데 충분한 크기의 제 1 자기장은 감소된 크기의 제 1 전류에 의해 발생된다.

- [0049] 제 2 도전체의 두 개의 측면을 메모리 셀의 길이 내에 배치하고 제 2 도전체의 상면 및/또는 두 개의 측면은 제 2 자기장을 동작가능하게 증가시키는 제 2 클래딩 층으로 커버함으로써 전력 소모가 더 감소된다. 제 2 두께는

제 1 도전체의 저항이 감소되도록 제 2 단면적을 증가시키게 선택되고 제 1 자기장과 협력하여 변경가능한 자화 배향을 회전시키는 데 충분한 제 2 자기장의 크기는 감소된 크기의 제 2 전류에 의해 발생된다. 제 1 및 제 2 클래딩 층은 강자성 재료로 구성된다.

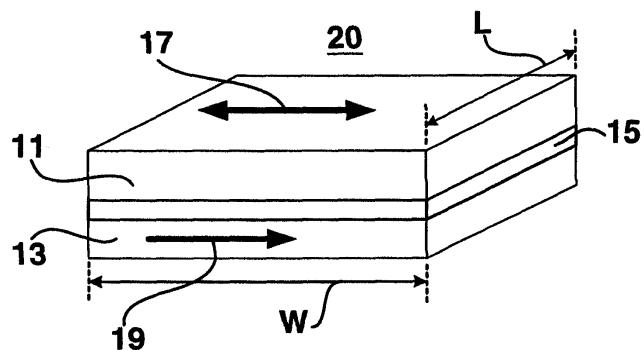

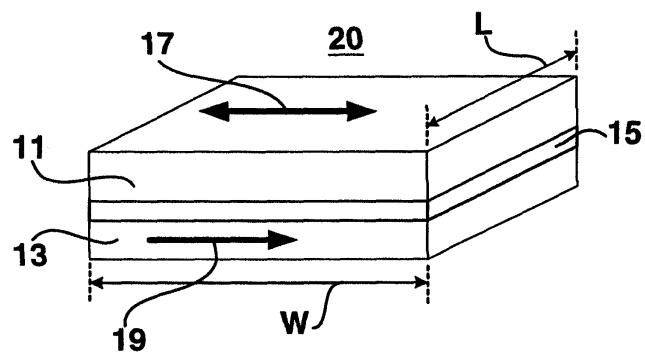

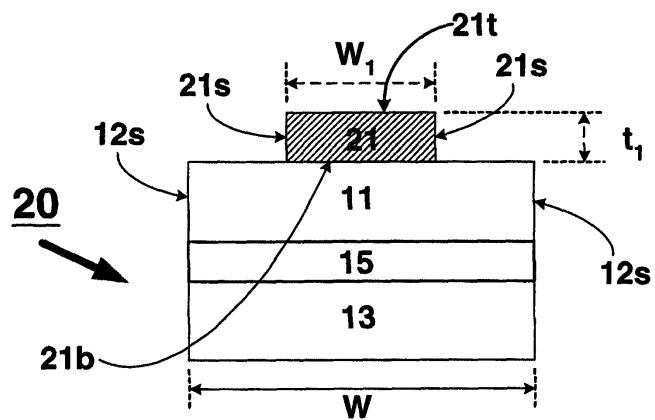

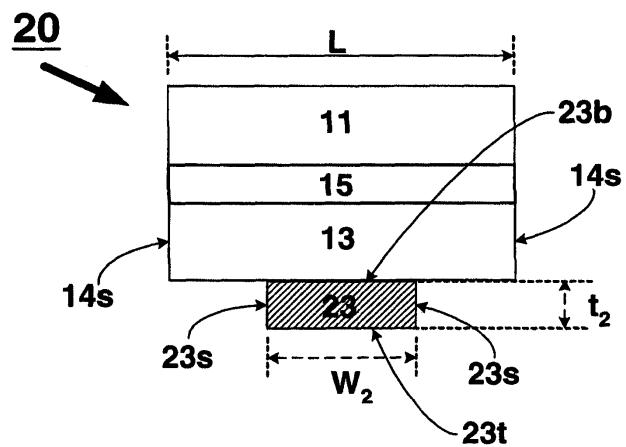

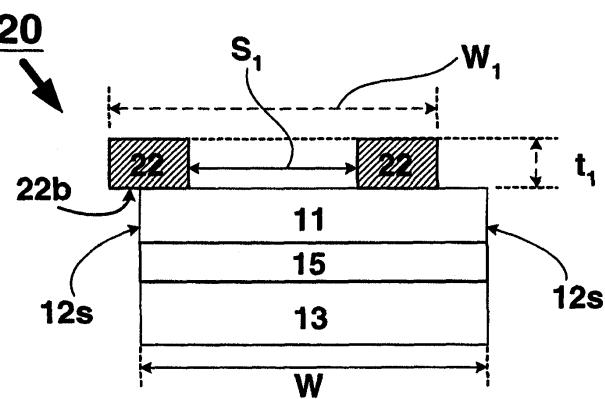

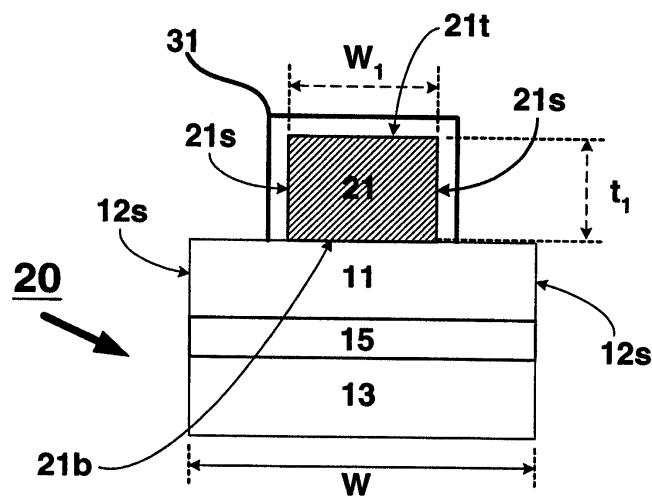

[0050] 도 5a 및 도 5b에 있어서, 자기장 감지 메모리 셀(20)은 데이터 층(11), 기준 층(13) 및 데이터 층(11)과 기준 층(13) 사이에 배치된 장벽 층(15)을 포함한다. 메모리 셀(20)은 종횡 비( $AR=W \div L$ )를 정의하는 폭( $W$ )과 길이( $L$ )를 갖는다. 데이터 층(11)은 변경가능한 자화 배향(17)을 포함하고 기준 층(13)은 고정된 자화 배향(19)을 포함한다. 데이터 비트는 데이터 층(11)에 저장된다.

[0051] 데이터 비트의 상태는 고정된 자화 배향(19)과 변경가능한 자화 배향(17) 간의 상대적 배향에 의해 결정된다. 예를 들어, 이진수 "1" 상태는 고정된 자화 배향(19)과 변경가능한 자화 배향(17)이 동일한 방향을 가리키는 평행 배향에 의해 표시될 수 있다. 반대로, 이진수 "0" 상태는 고정된 자화 배향(19)과 변경가능한 자화 배향(17)이 반대 방향을 가리키는 반-평행 배향에 의해 표시될 수 있다.

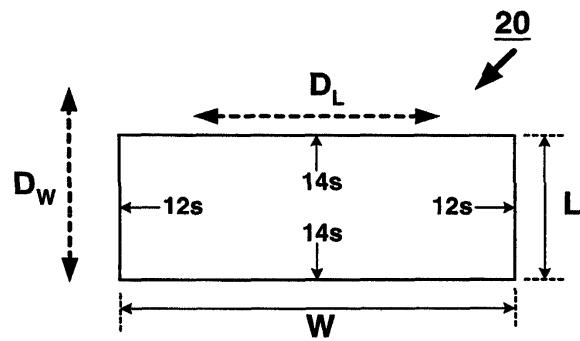

[0052] 도 5b에 있어서, 메모리 셀(20)의 폭 방향( $D_W$ )은 실질적으로 폭( $W$ ) 치수(dimension)에 수직이고 길이 방향( $D_L$ )은 실질적으로 길이( $L$ ) 치수에 수직이다. 메모리 셀(20)은 폭 방향( $D_W$ )으로 서로 마주 보는 측면(12s)과 길이 방향( $D_L$ )으로 서로 마주 보는 측면(14s)을 갖는다. 자기장 감지 메모리 셀이 다수의 박막 재료 층을 포함할 수 있다는 것은 MRAM 분야에서 쉽게 이해되고 있다. 단지 예시를 위해, 자기장 민감 메모리 셀에 포함될 수 있는 가능한 모든 층들이 도시되어 있는 것은 아니다. 예를 들어, 각각에 대해 하나의 층만이 도시되어 있지만 데이터 층(11), 기준 층(13) 및 장벽 층(15)은 몇몇 재료 층으로 구성될 수 있다. 또한, 본 명세서에서 설명한 바와 같은 제 1 및 제 2 도전체는 데이터 층(11) 및 기준 층(13)과 접촉하는 것으로 도시되어 있지만, 이를 도전체는 하나 이상의 재료 층에 의해 데이터 층(11) 및 기준 층(13)으로부터 분리될 수 있다.

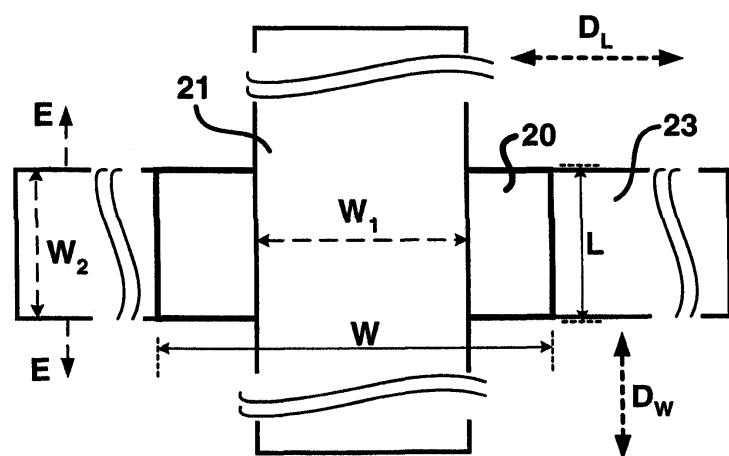

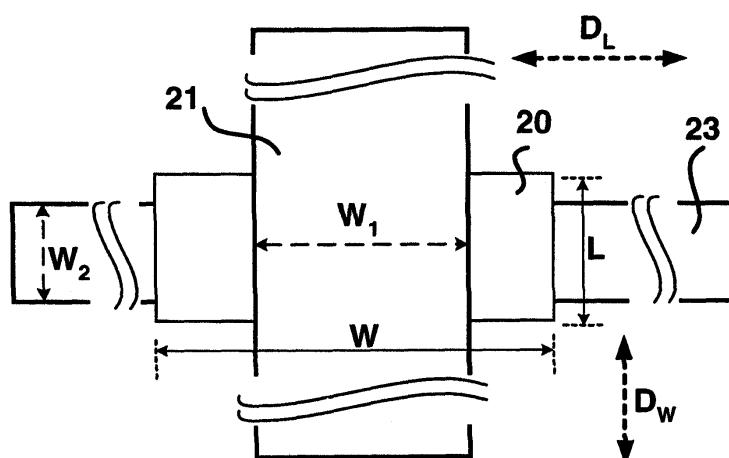

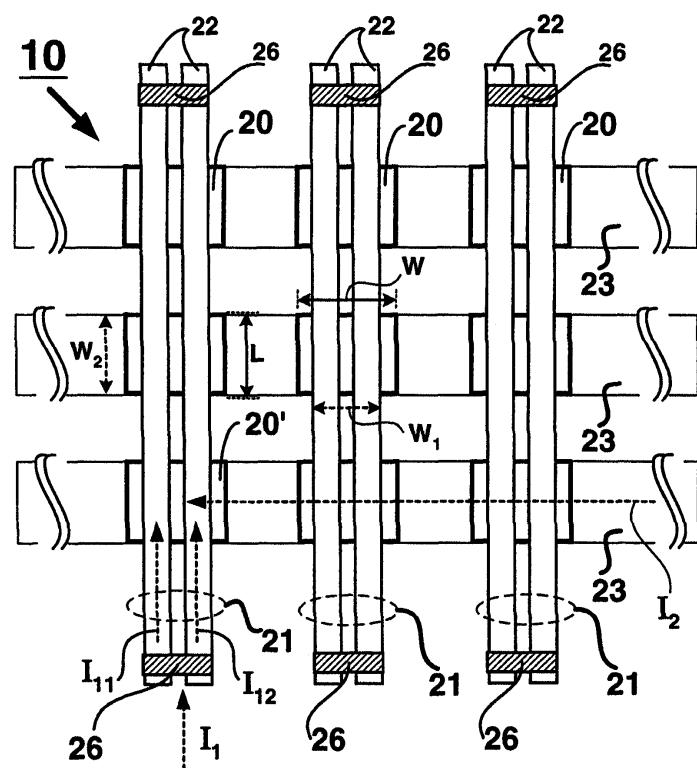

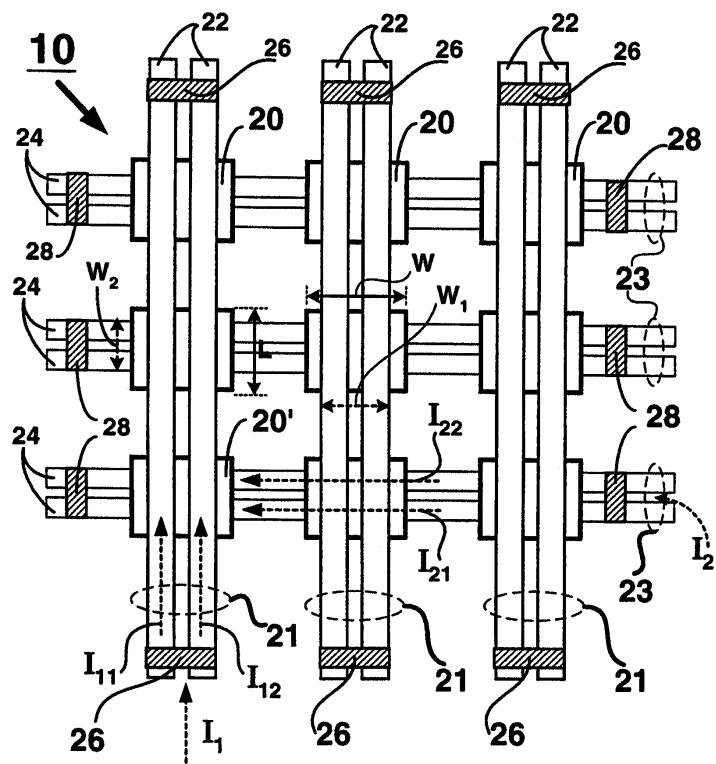

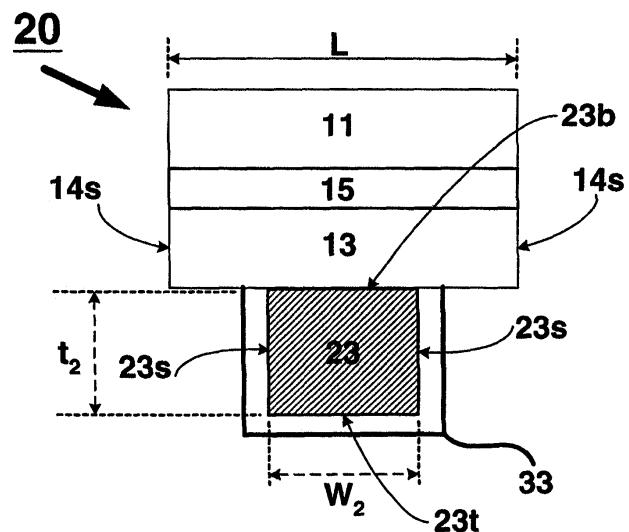

[0053] 도 5c, 6a 및 도 6c에 있어서, 자기 메모리 장치용 도전체 구조체는 메모리 셀(20), 폭 방향( $D_W$ )으로 메모리 셀(20)을 가로지르는 제 1 도전체(21) 및 길이 방향( $D_L$ )으로 메모리 셀(20)을 가로지르는 제 2 도전체(23)를 포함한다.

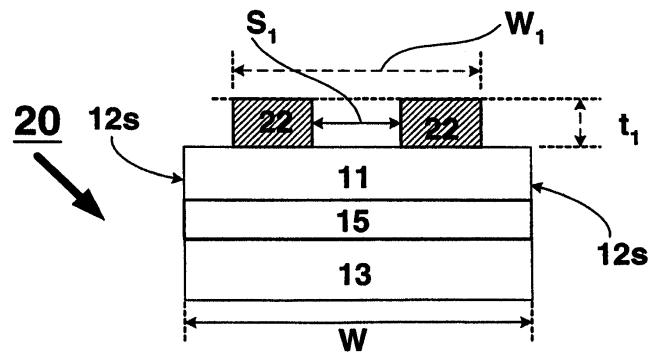

[0054] 도 6a에 있어서, 제 1 도전체(21)는 제 1 단면적( $A_1$ )(즉,  $A_1=W_1*t_1$ )을 정의하는 제 1 폭( $W_1$ ) 및 제 1 두께( $t_1$ )를 포함한다. 제 1 도전체(21)는 또한 상면(21t), 두 개의 측면(21s) 및 메모리 셀(20)에 인접한 바닥면(21b)(즉, 바닥면(21b)은 데이터 층(11)과 맞닿도록 배치됨)을 포함한다. 두 개의 측면(21s)은 메모리 셀(20)의 폭( $W$ ) 내에 배치된다. 즉, 두 개의 측면(21s)은 제 1 폭( $W_1$ )이 메모리 셀(20)의 폭( $W$ )보다 작도록(즉,  $W_1 < W$ ) 메모리 셀(20)의 마주보는 측면들(12s) 사이에 삽입된다. 제 1 도전체는 제 1 도전체(21)에 흐르는 제 1 전류( $I_1$ )(도시되지 않음)에 응답하여 제 1 자기장( $H_1$ )을 발생시킨다.

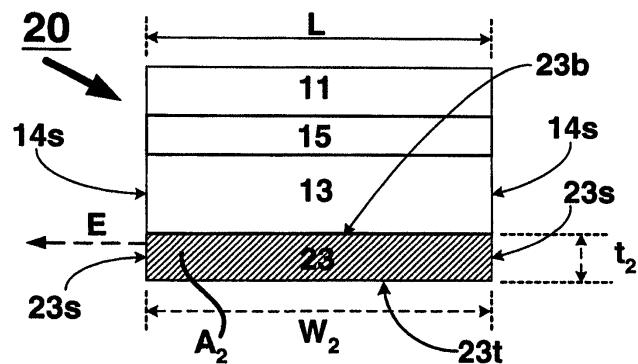

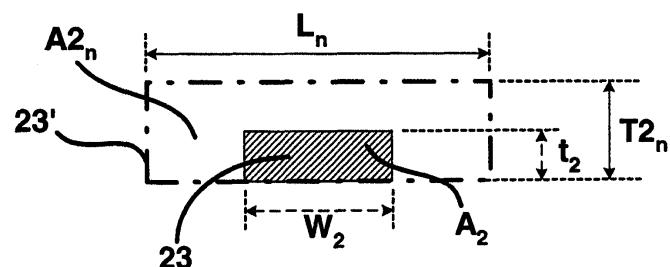

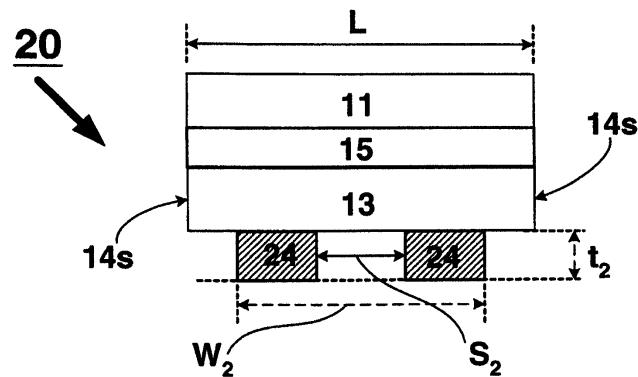

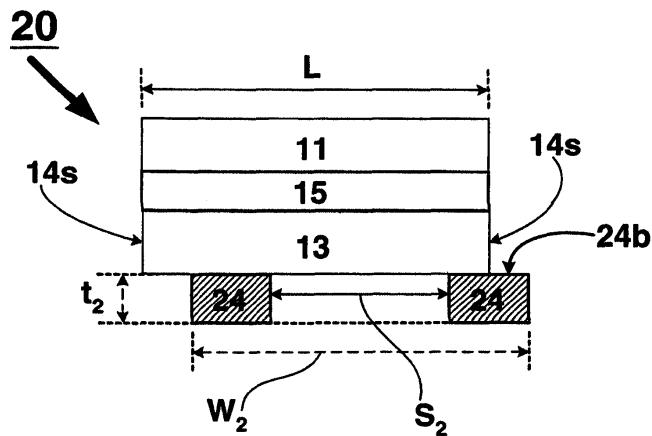

[0055] 도 6c에 있어서, 제 2 도전체(23)는 제 2 단면적( $A_2$ )(즉,  $A_2=W_2*t_2$ )을 정의하는 제 2 폭( $W_2$ ) 및 제 2 두께( $t_2$ )를 포함한다. 제 2 도전체(23)는 또한 상면(23t), 두 개의 측면(23s) 및 메모리 셀(20)에 인접한 바닥면(23b)(즉, 바닥면(23b)은 기준 층(13)과 맞닿도록 배치됨)을 포함한다. 제 2 도전체(23)는 제 2 도전체(23)에 흐르는 제 2 전류( $I_2$ )(도시되지 않음)에 응답하여 제 2 자기장( $H_2$ )을 발생시킨다. 제 1 및 제 2 자기장( $H_1, H_2$ )은 데이터 층(11)과 협조적으로 상호 작용하여 변경가능한 자화 배향(17)을 회전시킨다.

[0056] 도 5c, 6c 및 도 8a에 있어서, 제 2 폭( $W_2$ )은 메모리 셀(20)의 길이( $L$ ) 이상이다. 두 개의 측면(23s)은 메모리 셀(20)의 마주보는 측면(14s)과 실질적으로 동일 면에 배치된다. 이와 달리, 두 개의 측면(23s)은 점선의 화살표(E)로 표시한 바와 같이 마주보는 측면(12s) 밖으로 연장하도록 배치될 수 있다. 어느 경우에서라도, 제 2 폭( $W_2$ )은 메모리 셀(20)의 길이( $L$ )보다 더 크거나 또는 실질적으로 동일하다(즉,  $W_2 \geq L$ ).

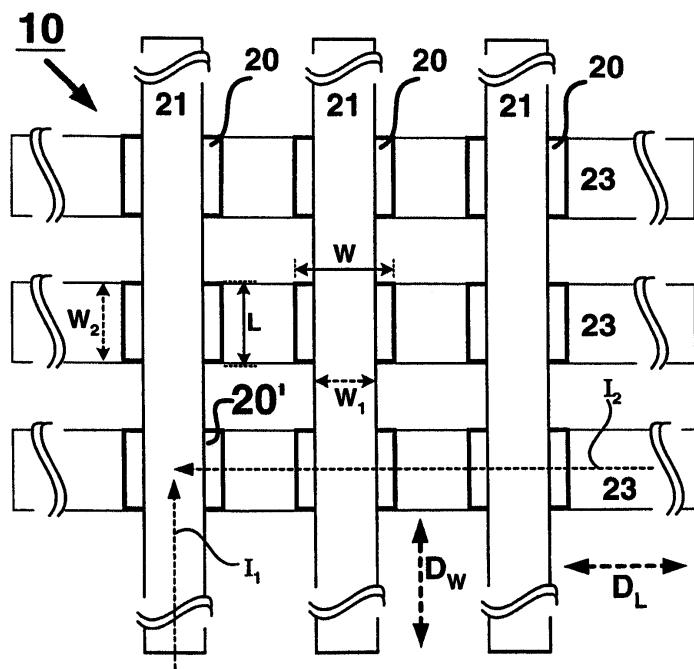

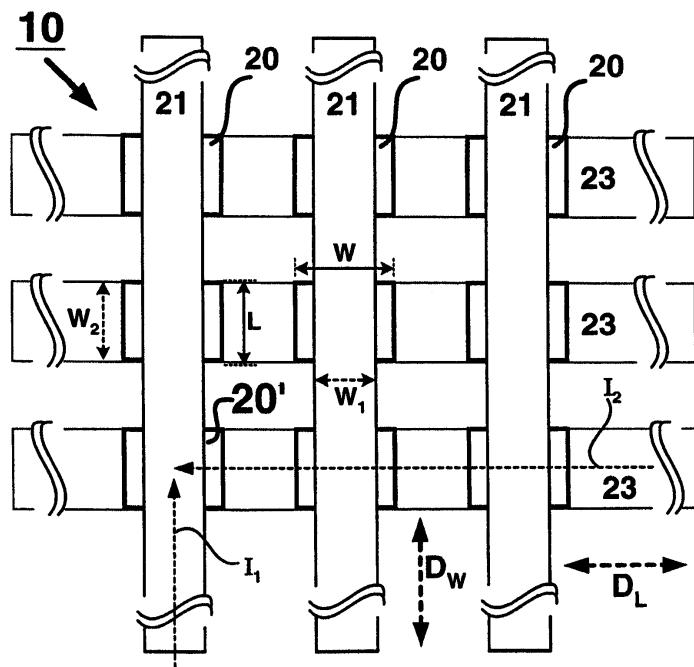

[0057] 도 5e에 있어서, 다수의 메모리 셀(20)은 행 및 열의 어레이로 배열되어 자기 메모리 장치(10)를 정의한다. 다수의 제 1 도전체(21)는 열로 배열되고 다수의 제 2 도전체(23)는 행으로 배열된다. 이와 달리, 제 1 도전체(21)가 행으로 배열될 수 있고 제 2 도전체(23)는 열로 배열될 수도 있다.

[0058] 각 메모리 셀(20)은 제 1 및 제 2 도전체(21, 23)의 교차부에 배치되고 제 1 및 제 2 도전체(21, 23) 사이의 중간에 배치된다. 데이터 비트는 제 1 도전체(21)에 제 1 전류( $I_1$ )를 통과시키고 제 2 도전체(23)에 제 2 전류( $I_2$ )를 통과시켜 이를 전류에 의해 발생된 제 1 및 제 2 자기장( $H_1, H_2$ )이 메모리 셀(20')의 데이터 층(11)과 협조

적으로 상호 작용하여 변경가능한 자화 배향(17)을 회전시킴으로써 제 1 및 제 2 도전체(21,23)의 교차부에 배치된 선택된 메모리 셀(도 5e에서 참조 번호(20')로 표시됨)에 기록된다. 위에서 언급한 기록 동작 동안의 전력 소모는 제 1 도전체(21)에 흐르는 제 1 전류( $I_1$ )의 크기를 감소시킴으로써 감소될 수 있다.

[0059] 도전체의 전류 밀도( $J$ )가  $J=I \div A$ (단위는  $A/m^2$ 임)가 되도록 도전체에 흐르는 전류( $I$ )의 크기와 도전체의 단면적( $A$ )에 의해 결정된다는 것은 전자 장치 분야에서 쉽게 이해된다. 자기장( $H$ )은 암페어의 법칙 :  $I = f H \cdot dI$  따라 도전체에 흐르는 전류( $I$ )와 관계있다. 이 식은  $I=H*P$ 로 간략화되는데, 여기서  $P$ 는 도전체 주위의 폐쇄된 자기 경로이다. 그러므로,  $I$ 가 일정하게 유지되는 경우  $P$ 의 감소에 따라  $H$ 는 증가한다.

[0060] 예를 들어, 제 1 도전체(21)에 있어서, 폐쇄된 자기 경로( $P$ )는 제 1 도전체(21) 주위의 폐쇄된 경로(즉, 제 1 도전체(21)의 주변)이고, 그러므로  $P=(2*W_1+2*t_1)$ 가 된다. 따라서, 제 1 자기장  $H_1 \approx [I_1 \div (2 * W_1 + 2 * t_1)]$ 이다. 이와 유사하게, 제 2 도전체(23)에 대해, 제 2 자기장  $H_2 \approx [I_2 \div (2 * W_2 + 2 * t_2)]$ 이다.

[0061] 데이터 층의 변경가능한 배향을 회전하는 데 충분한 크기의 전류는 데이터 층을 가로지르는 도전체의 폭을 감소시킴으로써 감소될 수 있다는 것이 MRAM 분야에서 쉽게 이해된다. 메모리 셀의 에지 내에 도전체의 에지가 존재하도록 도전체의 폭은 감소된다. 앞서 언급한 바와 같이, Bhattacharyya 등의 미국 특허 제 6,236,590 호는 폭이 감소된 도전체를 개시한다. 그러나, 도전체의 폭만의 감소로는 동일하게 큰 전류 감소를 야기하지 않는다. 예를 들어, 도전체의 폭이 팩터 2.0만큼 감소되는 경우(즉, 50%) 전류의 크기는 2.0 팩터만큼 감소하지 않는다.

[0062] 본 발명의 원리에 따라, 변경가능한 자화의 배향을 회전시키는 데 필요한 전류의 크기는 도전체의 단면적이 감소하고 도전체의 전류 밀도가 증가하도록 도전체의 두께 및 도전체의 폭을 감소시킴으로써 더 감소된다.

[0063] 도 6a에 있어서, 제 1 도전체(21)의 제 1 두께( $t_1$ ) 및 제 1 폭( $W_1$ )은 제 1 도전체(21)의 제 1 단면적( $A_1$ )을 감소시키고 전류 밀도( $J_1$ )를 증가시키도록 사전선택된다. 제 1 도전체(21) 내의 전류 밀도( $J_1$ )의 증가는 제 1 전류( $I_1$ )에 의해 발생된 제 1 자기장( $H_1$ )의 크기를 증가시킨다. 그러나, 제 1 단면적( $A_1$ )이 감소되고 제 1 전류( $I_1$ )가 일정하게 유지되는 경우, 제 1 자기장( $H_1$ )의 크기는 제 2 자기장( $H_2$ )과 협력하여 변경가능한 자화 배향(17)을 회전시키는 데 충분한 것 이상이다.

[0064] 따라서, 제 1 자기장( $H_1$ )의 크기가 변경가능한 자화 배향(17)을 회전시키는 데 필요한 실제 크기를 초과하기 때문에, 감소된 크기의 제 1 자기장( $H_1$ )이 제 2 자기장( $H_2$ )과 협력하여 변경가능한 자화 배향(17)을 회전하는 데 충분하도록 제 1 전류( $I_1$ )의 크기가 감소되어 결과적으로 제 1 자기장( $H_1$ )은 감소시킬 수 있다. 제 1 폭( $W_1$ )에 대한 사전선택된 값은 제 1 도전체(21)의 두 개의 표면(21s)이 메모리 셀(20)의 폭( $W$ ) 내에 배치되도록 야기한다(즉, 그들은 마주보는 표면(12a) 사이에 삽입됨). 제 1 도전체(21)는 마주보는 측면(12s) 사이에 중심을 두는 것으로 도시되어 있지만, 제 1 도전체(21)는 마주보는 측면(12s) 사이에서 대칭적으로 배치될 필요는 없고 마주보는 측면(12s) 내에 어디라도 배치될 수 있다.

[0065] 감소된 크기의 제 1 전류( $I_1$ )의 이점은 감소된 전력 소모, 감소된 전력 낭비(즉, 전류에 의해 발생되는 폐열) 및 제 1 전류( $I_1$ )를 공급하는 드라이버 회로의 크기 감소를 포함한다. 이하에서 설명되는 바와 같이 제 2 전류( $I_2$ )의 크기가 감소되는 경우에도 동일한 이점이 적용된다.

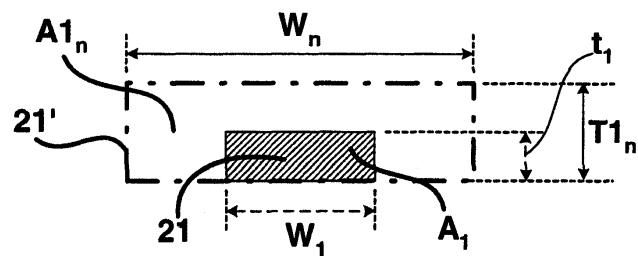

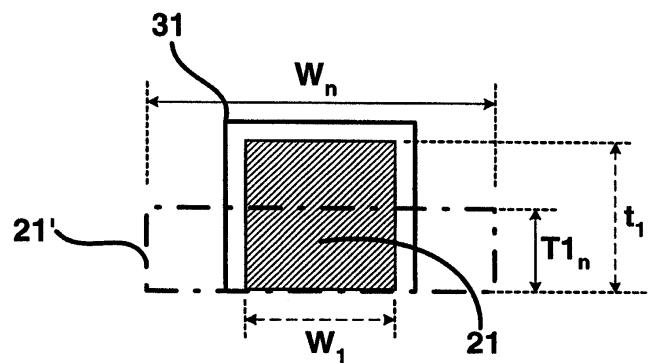

[0066] 도 6b에 있어서, 메모리 셀(20)은 표준 폭( $W_n$ ), 제 1 표준 두께( $T1n$ ) 및 제 1 표준 단면적( $A1n$ )을 갖는 표준 도전체(21')(단면도가 파선으로 도시됨)를 가질 수 있다. 이들 표준 값은 자기 메모리 장치를 제조하는 설계 규칙 세트(a set of design rules)에 의해 결정될 수 있다. 예를 들어, 제 1 표준 두께  $T1n= 0.2\mu m$ 이고 표준 폭  $W_n=1.0\mu m$ 인 경우, 제 1 표준 단면적  $A1n=W_n*T1n=0.2\mu m^2$ 이다. 표준 폭( $W_n$ )은 메모리 셀(20)의 폭( $W$ )보다 크거나 동일할 수 있다. 도 6b에 있어서, 표준 폭( $W_n$ )은  $W$ 와 동일하다. 어느 경우라도, 제 1 폭( $W_1$ )은  $W_n$ 보다 작고  $W$ 보다 작다.  $W_n, T1n$  및  $A1n$ 의 값은  $W_1$  및  $t_1$ 의 사전 선택된 값을 결정하는 데 기준으로서 사용될 수 있다.

[0067] 도 6b에 있어서, 제 1 도전체(21)의 단면도는 표준 도전체(21')의 단면도와 겹쳐져 제 1 표준 단면적  $A1n(A1n=W_n*T1n)$ 에 대한 제 1 단면적( $A_1$ )( $A_1=W_1*t_1$ )의 감소를 예시한다.

- [0068] 따라서, 제 1 단면적( $A_1$ )의 감소는 제 1 두께( $t_1$ )를 제 1 표준 두께 ( $T1n$ )보다 작도록 사전선택하고 또한 제 1 폭( $W_1$ )을 표준 폭( $W_n$ )보다 작도록 사전선택함으로써 달성될 수 있다. 분명히,  $W=W_n$ 인 경우에 제 1 폭( $W_1$ )은  $W$ 보다 작도록 사전선택될 수 있다. 예를 들어,  $A1n=Wn*T1n=0.2\mu\text{m}^2$ 에 있어서, 제 1 폭  $W_1=0.5\mu\text{m}^2$ 이고 제 1 두께  $t_1=0.1\mu\text{m}$ 인 경우, 제 1 단면적  $A_1=W_1*t_1=0.05\mu\text{m}^2$ 이고, 제 1 도전체(21) 제 1 단면적( $A_1$ )은 제 1 표준 단면적 ( $A1n$ )에 대해 1/4로 감소된다.

- [0069] 본 발명의 일 실시예에서, 제 1 폭( $W_1$ )은 표준 폭( $W_n$ )보다 약 0.60 팩터만큼 작고 제 1 두께( $t_1$ )은 제 1 표준 두께( $T1n$ )보다 약 0.50 이하의 팩터만큼 작다.

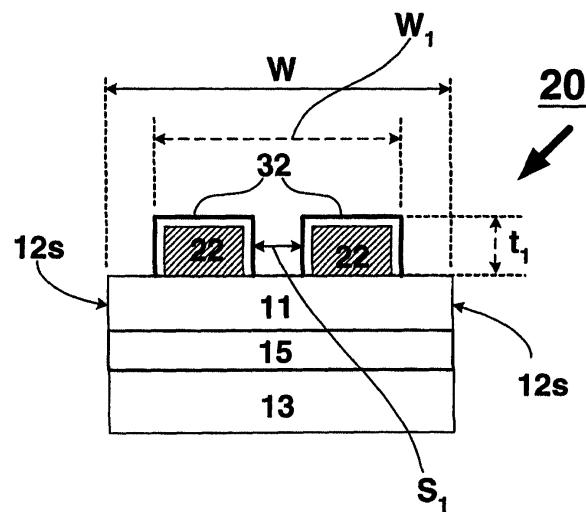

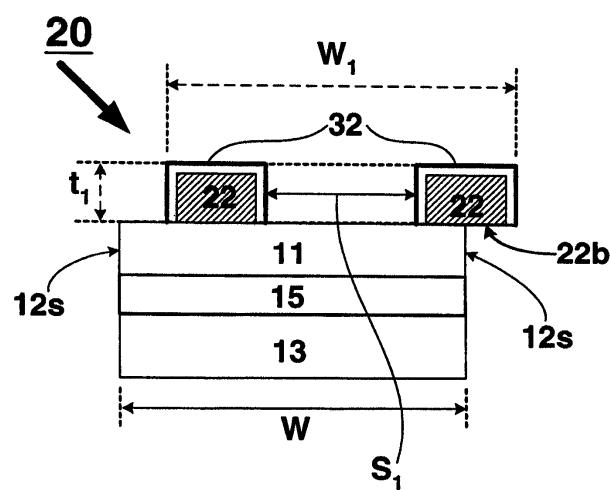

- [0070] 도 8a, 8b 및 도 8c에 있어서, 제 1 도전체(21)는 다수의 이격된 세그먼트(22)(두개가 도시되어 있음)로 분할된다. 도 8b에 있어서, 모든 세그먼트(22)는 메모리 셀(20)의 폭( $W$ ) 내에 배치된다. 세그먼트(22)는 거리( $S_1$ )만큼 이격된다. 세그먼트(22)는 위에서 언급한 바와 같이 제 1 두께( $t_1$ )를 갖는다. 세그먼트(22) 간의 거리( $S_1$ ) 때문에, 세그먼트(22)는 제 1 폭( $W_1$ )보다 작으며 폭( $W$ ) 또는 표준 폭( $W_n$ )보다 작은 총 결합 폭(total combined width)을 가질 것이다. 세그먼트들(22)은 동일한 폭을 가질 수도 있고 세그먼트들(22) 마다 서로 다른 폭을 가질 수도 있다.

- [0071] 도 8c에 도시된 바와 같이, 본 발명의 또 다른 실시예에 있어서, 적어도 하나의 세그먼트(22)는 메모리 셀(20)의 폭( $W$ ) 내에 배치되지 않는 일부분(즉, 바닥면(22b))을 가진다.

- [0072] 도 8a에 있어서, 세그먼트들(22) 중 하나에 전류( $I_{11}$ )가 흐르고 다른 세그먼트(22)에 전류( $I_{12}$ )가 흐르도록 제 1 전류( $I_1$ )가 세그먼트들(22) 사이에 분배된다. 세그먼트(22)가 실질적으로 동일한 치수(즉, 두께 및 폭)를 가지는 경우 전류( $I_{11}, I_{12}$ )는 실질적으로 서로 동일할 것이다. 다른 한편, 세그먼트들(22)이 동일한 치수를 가지지 않을 경우, 전류( $I_{11}, I_{12}$ )는 서로 동일하지 않을 수도 있다.

- [0073] 세그먼트들(22)은 전기적으로 연결하는 전기적 도전성 재료(26)에 의해 서로 전기적 통신을 하도록 연결될 수 있다. 본질적으로, 전기적 도전성 재료(26)는 세그먼트들(22)을 서로 단락시킨다. 드라이버 회로(도시되어 있지 않음)는 제 1 전류( $I_1$ )를 제 1 도전체(21)에 공급할 수 있고 제 1 전류( $I_1$ )는 분할되고 세그먼트들(22)을 통해 흐를 것이다. 그러나, 세그먼트들(22)은 서로 전기적 통신을 할 필요는 없고 각 세그먼트(22)는 전용 드라이버 회로(도시되어 있지 않음)에 전기적으로 연결될 수 있다. 바람직하게, 세그먼트들(22)은 드라이버 회로의 수가 최소가 되도록 서로 전기적 통신을 하며 연결된다.

- [0074] 도 8a 및 도 8b에 있어서, 제 1 단면적( $A_1$ )은 모든 세그먼트들(22)의 결합된 단면적을 포함한다. 제 1 도전체 (21)가 세그먼트들(22)로 분할되는 경우에도 감소된 제 1 단면적( $A_1$ )으로 인해 앞서 언급한 바와 같이 제 1 전류가 역시 감소한다.

- [0075] 본 발명의 자기 메모리 장치(10)의 전류 소모의 부가적인 감소는 제 1 도전체(21)에 대해 위에서 설명한 것과 동일한 방식으로 제 2 도전체(23)의 제 2 단면적( $A_2$ )을 감소시킴으로써 달성된다.

- [0076] 도 5d, 5f, 7a 및 도 7b에 있어서, 제 2 도전체(23)의 두 개의 측면(23s)은 메모리 셀(20)의 길이( $L$ ) 내에 배치된다(즉, 그들은 마주보는 측면(14s) 사이에 삽입됨). 제 2 두께( $t_2$ ) 및 제 2 폭( $W_2$ )은 제 2 단면적( $A_2$ )을 감소시키고 제 2 도전체(23) 내의 전류 밀도( $J_2$ )를 증가시키도록 사전선택된다. 그 결과, 제 1 자기장( $H_1$ )과 협력하여 변경가능한 자화 배향(17)을 회전시키는 데 충분한 제 2 자기장( $H_2$ )이 감소된 크기의 제 2 전류( $I_2$ )에 의해 발생된다.

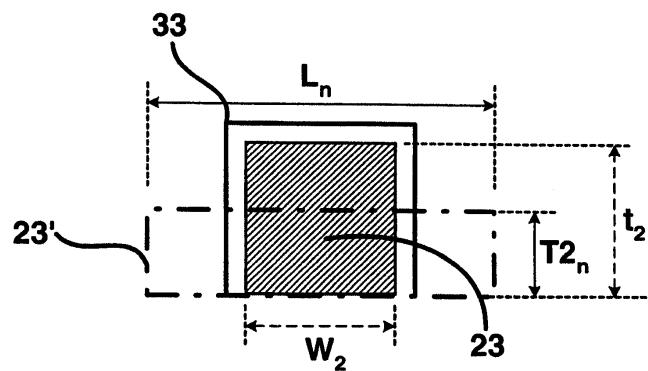

- [0077] 도 7b에 있어서, 메모리 셀(20)은 표준 길이( $L_n$ ), 제 2 표준 두께( $T2n$ ) 및 제 2 표준 단면적( $A2n$ )을 포함하는 표준 도전체(23')(단면도가 평면으로 도시됨)를 가질 수 있다. 이를 표준 값은 자기 메모리 장치를 제조하는 설계 규칙 세트에 의해 결정될 수 있다. 예를 들어, 제 2 표준 두께  $T2n=0.2\mu\text{m}^2$ 이고 표준 길이  $L_n=0.8\mu\text{m}$ 인 경우, 제 2 표준 단면적  $A2n=L_n*T2n=0.16\mu\text{m}^2$ 이다. 표준 길이( $L_n$ )은 메모리 셀(20)의 길이( $L$ )보다 크거나 동일하다. 도 7a 및 7b에 있어서, 표준 길이( $L_n$ )는 메모리 셀(20)의 길이( $L$ )와 동일하다. 어느 경우라도, 제 2 폭

$(W_2)$ 은  $L_n$ 보다 작고 또한  $L$ 보다 작다.  $L_n, T_{2n}$  및  $A_{2n}$ 의 값은  $W_2$  및  $t_2$ 의 사전 선택된 값을 결정하는 데 기준으로서 사용될 수 있다.

[0078] 도 7b에 있어서, 제 2 도전체(23)의 단면도는 표준 도전체(23')의 단면도와 겹쳐져서 제 2 표준 단면적  $A_{2n}$  ( $A_{2n}=L_n \cdot T_{2n}$ )에 대한 제 2 단면적  $A_2$  ( $A_2=W_2 \cdot t_2$ )의 감소를 나타낸다.

[0079] 따라서, 제 2 단면적( $A_2$ )의 감소는 제 2 두께( $t_2$ )를 제 2 표준 두께( $T_{2n}$ )보다 작도록 사전선택하고 또한 제 2 폭( $W_2$ )을 표준 길이( $L_n$ )보다 작도록 사전선택함으로써 달성될 수 있다.  $L=L_n$ 인 경우에, 제 2 폭( $W_2$ )은  $L$ 보다 작도록 사전선택될 수 있다. 예를 들어,  $A_{2n}=L_n \cdot T_{2n}=0.16 \mu\text{m}^2$ 에 있어서, 제 2 폭  $W_2=0.4 \mu\text{m}$ 이고 제 2 두께  $t_2=0.1 \mu\text{m}$ 인 경우, 제 2 단면적  $A_2=W_2 \cdot t_2=0.04 \mu\text{m}^2$ 이고, 제 2 도전체(23)의 제 2 단면적( $A_2$ )은 제 2 표준 단면적( $A_{2n}$ )에 대해 1/4로 감소된다.

[0080] 본 발명의 또 다른 실시예에서, 제 2 폭( $W_2$ )은 표준 길이( $L_n$ )보다 약 0.60이하의 팩터만큼 작고 제 2 두께( $t_2$ ) 제 2 표준 두께( $T_{2n}$ )보다 약 0.50 이하의 팩터만큼 작다.

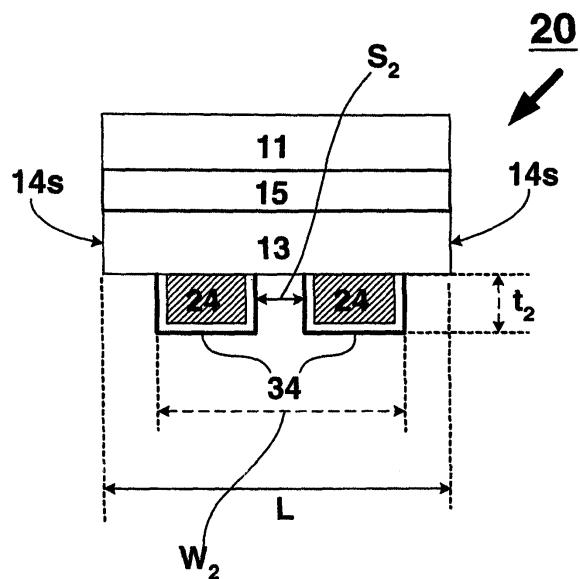

[0081] 도 9a, 9b 및 도 9c에 있어서, 제 2 도전체(23)는 다수의 이격된 세그먼트(24)(두개가 도시되어 있음)로 분할된다. 도 9b에 있어서, 모든 세그먼트(24)는 메모리 셀(20)의 길이( $L$ ) 내에 배치된다. 세그먼트(24)는 거리( $S_2$ )만큼 이격된다. 세그먼트(24)는 위에서 언급한 바와 같이 제 2 두께( $t_2$ )를 갖는다. 세그먼트(24) 간의 거리( $S_2$ ) 때문에, 세그먼트(24)는 제 2 폭( $W_1$ )보다 작으며 길이( $L$ ) 또는 표준 길이( $L_n$ )보다 작은 총 결합 폭을 가질 것이다. 세그먼트들(24)은 동일한 폭을 가질 수도 있고 그들은 세그먼트들(24) 마다 서로 다른 폭을 가질 수도 있다.

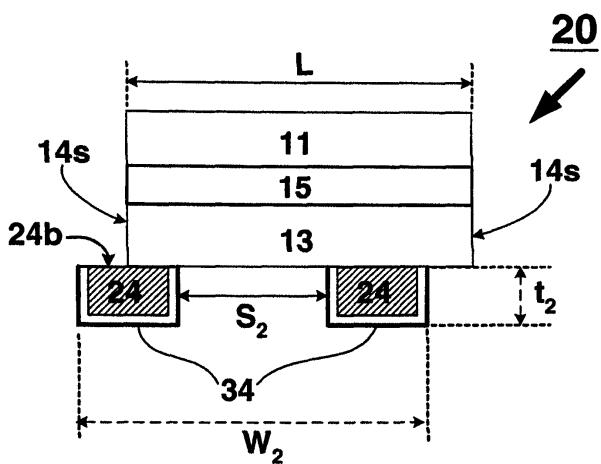

[0082] 도 9c에 도시된 바와 같이, 본 발명의 또 다른 실시예에 있어서, 적어도 하나의 세그먼트(24)는 메모리 셀(20)의 길이( $L$ ) 내에 배치되지 않는 일부분(즉, 바닥면(24b))을 가진다.

[0083] 도 9a에 있어서, 세그먼트들(24) 중 하나는 전류( $I_{21}$ )가 흐르고 다른 세그먼트(24)는 전류( $I_{22}$ )가 흐르도록 제 2 전류( $I_2$ )가 세그먼트들(24) 사이에 분배된다. 세그먼트들(24)이 실질적으로 동일한 치수(즉, 두께 및 폭)를 가지는 경우 전류( $I_{21}, I_{22}$ )는 실질적으로 서로 동일할 것이다. 다른 한편, 세그먼트들(22)이 동일한 치수를 가지지 않을 경우, 전류( $I_{21}, I_{22}$ )는 서로 동일하지 않을 수도 있다.

[0084] 세그먼트들(24)은 전기적으로 연결하는 전기적 도전성 재료(28)에 의해 서로 전기적 통신을 하도록 연결될 수 있다. 본질적으로, 전기적 도전성 재료(28)는 세그먼트들(24)을 서로 단락시킨다. 드라이버 회로(도시되어 있지 않음)는 제 2 전류( $I_2$ )를 제 2 도전체(23)에 공급할 수 있고 제 2 전류( $I_2$ )는 분할되고 세그먼트들(24)을 통해 흐를 것이다. 그러나, 세그먼트(24)는 서로 전기적 통신을 할 필요는 없고 각 세그먼트(24)는 전용 드라이버 회로(도시되어 있지 않음)에 전기적으로 연결될 수 있다. 바람직하게, 세그먼트들(24)은 드라이버 회로의 수가 최소가 되도록 서로 전기적 통신을 하며 연결된다.

[0085] 도 9a 및 도 9b에 있어서, 제 2 단면적( $A_2$ )은 모든 세그먼트들(24)의 결합된 단면적을 포함한다. 제 2 도전체(23)가 세그먼트들(24)로 분할되는 경우에도 앞서 언급한 바와 같이 감소된 제 2 단면적( $A_2$ )으로 인해 제 2 전류가 역시 감소된다.

[0086] 도 9a에도 예시된 바와 같이, 본 발명의 또 다른 실시예에서, 제 1 도전체(21)는 도 8a, 8b 및 도 8c에서 설명한 바와 같이 다수의 이격된 세그먼트(22)로 분할된다. 세그먼트(22)는 거리( $S_1$ )만큼 이격된다. 모든 세그먼트들(22)이 메모리 셀(20)의 폭( $W$ ) 내에 배치될 수 있고, 적어도 하나의 도전체(22)가 폭( $W$ ) 내에 배치되지 않는 일부분을 가질 수도 있다. 그 결과, 제 1 및 제 2 도전체(21, 23) 양자는 이격된 세그먼트들(22, 24)로 분할된다.

[0087] 도전체(21, 23)를 세그먼트들(22, 24)로 분할하면 데이터 층(11)의 하나 이상의 영역에 집중된 필드(concentrated field)가 인가된다. 예를 들어, 두 개 필드의 소스가 데이터 층(11)의 양쪽 종단에 존재할 수 있다. 이러한 배열은 데이터 층(11)의 종단 영역에서 스위칭 프로세스가 개시되도록 제한할 수 있다. 이것은 보다 재생가능한 스위칭 프로세스(a more reproducible switching process)를 생성한다.

[0088] 제 1 도전체(21) 및/또는 제 2 도전체(23)의 단면적의 감소의 결과 중 하나는 단면적( $A_1, A_2$ )이 감소함에 따라 도전체의 저항이 증가한다는 것이다. 전자의 흐름에 대한 저항( $R_c$ )과 도전체의 단면적( $A_c$ )와의 상관 관계는  $R_c = \rho * (1 \div A_c) = \rho * [1 \div (W_c * t_c)]$ 이며, 여기서  $\rho$ 는  $\Omega\text{-m}$  단위의 저항이고  $t$ 는 미터 단위의 길이다.

[0089] 그러므로, 저항( $R_c$ )을 감소시키는 한가지 방법은 도전체의 단면적( $A_c$ )이 증가되도록 두께( $t_c$ ), 폭( $W_c$ ) 또는 이를 양자를 증가시는 것이다. 도전체의 폭( $W_c$ )의 감소의 장점은 위에서 설명되었다. 따라서, 본 명세서에서 설명한 바와 같이 도전체 폭( $W_c$ )이 메모리 셀(20)의 길이( $L$ ) 또는 폭( $W$ )보다 작을 경우, 단면적( $A_c$ )을 증가시키고 또한 저항( $R_c$ )을 감소시키기 위해 두께( $t_c$ )는 증가되어야 한다.

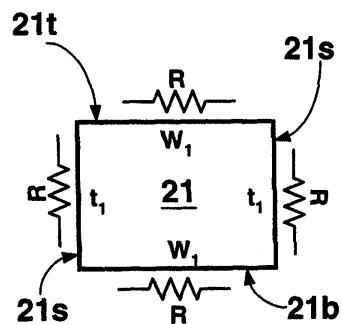

[0090] 도 14에 있어서, 제 1 도전체(21)는 제 1 도전체(21)의 주변 근처의 총 자기 경로( $P_1$ )를 가지며, 여기서  $P_1 = (2*W_1) + (2*t_1)$ 이다. 제 1 도전체(21)에 흐르는 제 1 전류( $I_1$ )에 의해 발생된 제 1 자기장( $H_1$ )은 총 자기 경로( $P_1$ )로 나눈 제 1 전류( $I_1$ )에 비례한다.

$$H_1 \approx I_1 \div P_1 \approx I_1 \div (2 * W_1 + 2 * t_1)$$

[0092] 도 14에 도시되어 있지 않지만, 제 2 도전체(23)도 주변  $P_2 = (2*W_2) + (2*t_2)$ 와 총 자기 경로( $P_2$ )로 나눈 제 2 전류( $I_2$ )에 비례적인 제 2 도전체(23)에 흐르는 제 2 전류에 의해 발생되는 제 2 자기장( $H_2$ )을 포함한다.

$$H_2 \approx I_2 \div P_2 \approx I_2 \div (2 * W_2 + 2 * t_2)$$

[0094] 도 14에 있어서, 제 1 도전체(21)의 네 개의 측면(21t, 21s 및 21b) 각각은 전기 회로에서 직렬 저항에 의해 야기된 전압 강하와 유사한 제 1 자기장( $H_1$ )에 대한 저항( $R$ )을 나타낸다. 그러므로,  $t_1$ 이 증가하면 총 자기 경로( $P_1$ )가 증가하기 때문에  $t_1$ 의 증가는 제 1 자기장( $H_1$ )의 크기를 감소시킬 것이다.

[0095] 도 15에 있어서, 제 1 도전체(21)의 총 자기 경로( $P_1$ )은 상면(21t), 측면(21s) 또는 이를 양자 모두를 (도시된 바와 같이) 제 1 클래딩 층(31)으로 커버함으로써 감소될 수 있다. 바닥면(21b)은 클래딩 층으로 커버되지 않는다(즉, 제 1 도전체(21)는 부분적으로 클래딩됨). 제 1 클래딩 층(31)은 강자성 재료로 만들어진다. 클래딩된 표면(21t, 21s)의 저항( $R$ )은 실질적으로  $R \approx 0$ 이고 클래딩되지 않은 표면(21b)의 저항은( $R$ )은  $R$ 로 남겨진다. 그 결과, 총 자기 경로( $P_1$ )는  $W_1$ 이되고 제 1 자기장  $H_1 \approx I_1 \div W_1$ 이 된다. 비트 폭( $W$ )보다 작도록 도전체 폭( $W_1$ )을 제한함으로써, 자기장( $H_1$ )은 1 비트 및 같은 길이를 갖는 도전체를 위한 값을 넘도록 증가한다. 또한, 제 1 클래딩 층(31) 때문에, 제 1 두께( $t_1$ )는 증가되어 제 1 단면적( $A_1$ )을 증가시키고 제 1 도전체(21)에서의 전자 흐름에 대한 저항을 감소시킬 수 있다.

[0096] 이와 유사하게, 제 2 도전체(23)의 총 자기 경로( $P_2$ )는 상면(23t), 측면(23s) 또는 이를 양자 모두를 제 2 클래딩 층(33)으로 커버함으로써(도 11a 참조) 감소될 수 있다. 바닥면(23b)은 클래딩 층으로 커버되지 않는다(즉, 제 2 도전체(23)는 부분적으로 클래딩됨). 제 2 클래딩 층(33)은 강자성 재료로도 만들어진다. 따라서, 총 자기 경로( $P_2$ )는  $W_2$ 가 되고 제 2 자기장  $H_2 \approx I_2 \div W_2$ 가 된다. 제 2 클래딩 층(33)은 두께( $t_2$ )가 증가되어 제 2 단면적( $A_2$ )을 증가시키고 제 2 도전체(23)에서의 전자 흐름에 대한 저항을 감소시킬 수 있다.

[0097] 제 1 및 제 2 도전체(21, 23)에 대한 감소된 도전체 폭( $W_1, W_2$ )의 이점은 제 1 및 제 2 전류( $I_1, I_2$ )의 감소 및 기록 드라이버 회로의 크기 감소를 포함한다. 감소된 저항의 이점은 전력 소모 및 전력 낭비의 감소와 제 1 및 제 2 전류( $I_1, I_2$ )를 공급하는 드라이버 회로의 공급 전압 감소를 포함한다. 또한, 증가된 도전체 단면적은 일렉트로마이그레이션 문제(electromigration concerns)를 완화시킨다.

[0098] 도 10a 및 도 10b에 도시된 바와 같이, 본 발명의 일 실시예에서, 자기 메모리 장치(10)의 도전체 구조체는 위에서 설명한 바와 같은 메모리 셀(20)을 포함한다. 제 1 도전체(21)는 폭 방향( $D_w$ )으로 메모리 셀(20)을 가로지르고 그 내부를 흐르는 제 1 전류( $I_1$ )에 응답하여 제 1 자기장( $H_1$ )을 발생시킨다. 제 1 도전체(21)는 제 1 단면적( $A_1$ )을 정의하는 제 1 폭( $W_1$ )과 제 1 두께( $t_1$ )를 갖는다. 제 1 도전체는 상면(21t), 메모리 셀(20)의 폭( $W$ ) 내에 배치된 두 개의 측면(21s)(즉, 두 개의 측면(21s)은 마주보는 측면(12s) 사이에 삽입됨) 및 메모리 셀(2

0)에 인접하게 배치된 바닥면(21b)을 포함한다.

[0099] 제 1 도전체(21)는 제 1 클래딩 층(31)을 포함한다. 제 1 클래딩 층(31)은 상면(21t), 두 개의 측면(21s) 또는 상면과 두 개의 표면(21s)을 커버할 수 있다. 제 1 클래딩 층(31)은 도 15를 참조하여 위에서 설명한 바와 같이 총 자기 경로( $P_1$ )를 감소시키고 제 1 자기장( $H_1$ )을 증가시킨다.

[0100] 제 2 도전체(23)는 길이 방향( $D_L$ )으로 메모리 셀(20)을 가로지르고 그 내부를 흐르는 제 2 전류( $I_2$ )에 응답하여 제 2 자기장( $H_2$ )을 발생시킨다. 제 2 도전체는 제 2 단면적( $A_2$ )을 정의하는 제 2 폭( $W_2$ )과 제 2 두께( $t_2$ )를 갖고, 상면(23t), 두 개의 측면(23s) 및 메모리 셀(20)에 인접하게 배치된 바닥면(23b)을 포함한다. 앞서 설명한 바와 같이, 제 1 및 제 2 자기장( $H_1, H_2$ )은 데이터 층(11)과 협조적으로 상호 작용하여 변경가능한 자화 배향(17)을 회전시킨다.

[0101] 도 10a 및 도 10b에 도시된 실시예에서, 제 1 폭( $W_1$ )은 메모리 셀의 폭( $W$ )보다 작고 제 1 두께( $t_1$ )는 제 1 단면적( $A_1$ )을 증가시키도록 사전선택된다. 도 14 및 도 15를 참조하여 위에서 설명한 바와 같이, 제 1 단면적( $A_1$ )의 증가는 제 1 도전체(21)의 저항을 감소시킨다. 감소된 도전체 폭( $W_1$ )은 제 1 자기장( $H_1$ )의 크기가 감소된 크기의 제 1 전류( $I_1$ ) 하에서 제 2 자기장( $H_2$ )과 협력하여 변경가능한 자화 배향(17)을 회전하는 데 충분하도록 보장한다.

[0102] 도 10b에는, 표준 폭( $W_n$ ) 및 제 1 표준 두께( $T1n$ )을 갖는 표준 도전체(21')의 단면도의 개략도가 도시되어 있다. 이들 표준 값은 위에서 설명한 바와 같이 자기 메모리 셀(20)을 제조하기 위한 설계 규칙 세트에 의해 결정될 수 있다. 제 1 폭( $W_1$ )은 표준 폭( $W_n$ )보다 작다. 두 개의 측면(21s)은 마주보는 측면(12s) 사이에 삽입되기 때문에, 제 1 폭( $W_1$ )은 또한 폭( $W$ )보다 작을 것이다.  $W_n$  및  $T1n$ 의 값은  $W_1$  및  $t_1$ 의 값을 결정하는 기본 값으로 사용될 수 있다.

[0103] 그러나, 도 6b에서 예시된 실시예와는 달리, 도 10b에서 제 1 단면적( $A_1$ )의 증가는 제 1 두께( $t_1$ )를 제 1 표준 두께( $T1n$ )보다 크도록 사전선택함으로써(즉,  $t_1 > T1n$ ) 달성될 수 있다. 예를 들어, 제 1 표준 두께  $T1n=0.2\mu\text{m}$ 인 경우, 제 1 두께( $t_1$ )는  $0.4\mu\text{m}$ 로 사전선택될 수 있다.

[0104] 본 발명의 일 실시예에서, 제 1 폭( $W_1$ )은 표준 폭( $W_n$ )보다 약 0.60 이하의 팩터만큼 작고 제 1 두께( $t_1$ )는 제 1 표준 두께( $T1n$ )보다 약 1.50 이상의 팩터만큼 크다.

[0105] 전력 소모의 부가적인 감소는 도 11a 및 도 11b에서 예시된 본 발명의 또 다른 실시예에 의해 실현될 수 있는데, 여기서 제 2 도전체(23)는 제 2 클래딩 층(33)을 포함한다. 제 2 클래딩 층(33)은 상면(23t), 두 개의 측면(23s) 또는 상면(23t)과 두 개의 표면(23)을 커버할 수 있다. 도 15를 참조하여 위에서 설명한 바와 같이 제 2 클래딩 층(33)은 총 자기 경로( $P_2$ )를 감소시키고 제 2 자기장( $H_2$ )을 증가시킨다.

[0106] 도 11a 및 도 11b에서 도시된 바와 같이, 두 개의 표면(23s)은 메모리 셀(20)의 길이( $L$ ) 내에 배치된다(즉, 그들은 마주보는 측면(14s) 사이에 삽입됨). 표준 길이( $L_n$ )는 메모리 셀(20)의 길이( $L$ )보다 크거나 동일하다. 제 2 폭( $W_2$ )은 메모리 셀(20)의 표준 길이( $L_n$ )보다 작을 수 있다. 두 개의 측면(23s)이 마주보는 표면(14s) 사이에 삽입되기 때문에, 제 2 폭( $W_2$ )도 길이( $L$ )보다 더 작을 것이다.

[0107] 제 2 두께( $t_2$ )는 제 2 단면적( $A_2$ )을 증가시키고 제 2 도전체(23)의 저항을 감소시키도록 사전선택된다. 감소된 도전체 폭( $W_2$ )은 제 2 자기장( $H_2$ )의 크기가 감소된 크기의 제 2 전류( $I_2$ ) 하에서 제 1 자기장( $H_1$ )과 협력하여 변경가능한 자화 배향(17)을 회전시키기에 충분하도록 보장한다.

[0108] 도 11b에 있어서, 제 2 단면적( $A_2$ )의 증가는 제 2 두께( $t_2$ )를 제 2 단면적( $T2n$ )보다 크도록 사전선택함으로써(즉,  $t_2 > T2n$ ) 달성될 수 있다. 예를 들어, 제 2 표준 두께  $T2n=0.3\mu\text{m}$ 인 경우, 제 2 두께( $t_2$ )는  $0.7\mu\text{m}$ 로 사전선택될 수 있다.

[0109] 본 발명의 일 실시예에서, 제 2 폭( $W_2$ )은 표준 길이( $L_n$ )보다 약 0.60 이하의 팩터 만큼 작고 제 2 두께( $t_2$ )는 제 2 표준 두께( $T2n$ )보다 약 1.50 이상의 팩터만큼 크다.

- [0110] 도 12a에서 도시된 바와 같이, 본 발명의 또 다른 실시예에서 제 1 도전체(21)는 이격되고 클래딩된 복수(두개가 도시되어 있음)의 세그먼트(22)로 분할된다. 제 1 도전체(21)와 동일한 방식으로, 각 클래딩된 세그먼트(22)는 상면, 두 개의 측면 및 메모리 셀(20)에 인접하게 배치된 바닥면을 갖는다. 클래딩된 세그먼트(22)는 거리( $S_1$ )만큼 이격된다.

- [0111] 클래딩 층(32)은 상면, 두 개의 측면 또는 상면과 두 개의 측면을 커버할 수 있다(즉, 클래딩된 세그먼트(22)는 부분적으로 클래딩됨). 도 12a에 있어서, 바닥면을 제외한 도전체(22)의 모든 표면은 클래딩 층(32)으로 커버된다. 위에서 설명한 바와 같이 클래딩 층(32)은 총 자속 경로( $P_1$ )를 감소시킨다. 각 클래딩된 세그먼트(22)는 제 1 단면적( $A_1$ )을 증가시켜 각 클래딩된 세그먼트(22)에서의 전자 흐름에 대한 저항을 감소시키도록 사전선택된 제 1 두께( $t_1$ )를 갖는다.

- [0112] 도 12a에 도시된 본 발명의 일 실시예에서, 클래딩된 모든 세그먼트들(22)은 메모리 셀(20)의 폭(W) 내에 배치된다. 도 12b에 예시된 본 발명의 또 다른 실시예에서는 적어도 하나의 클래딩된 세그먼트(22)가 메모리 셀(20)의 폭(W) 내에 배치되지 않는 일부분(즉 바닥면(22b))을 갖는다.

- [0113] 마찬가지로, 도 12c에 있어서, 제 2 도전체(23)는 이격되고 클래딩된 복수(두개가 도시되어 있음)의 세그먼트(24)로 분할된다. 제 2 도전체(23)와 동일한 방식으로, 각 클래딩된 세그먼트(24)는 상면, 두 개의 측면 및 메모리 셀(20)에 인접하게 배치된 바닥면을 갖는다. 클래딩된 세그먼트(24)는 거리( $S_2$ )만큼 이격된다.

- [0114] 클래딩 층(34)은 상면, 두 개의 측면 또는 상면과 두 개의 측면을 커버할 수 있다(즉, 클래딩된 세그먼트(24)는 부분적으로 클래딩됨). 도 12c에 있어서, 바닥면을 제외한 클래딩된 세그먼트(24)의 모든 표면은 클래딩 층(34)으로 커버된다. 위에서 설명한 바와 같이 클래딩 층(34)은 총 자속 경로( $P_2$ )를 감소시킨다. 각 클래딩된 세그먼트(24)는 제 2 단면적( $A_2$ )을 증가시켜 각 클래딩된 세그먼트(24)에서의 전자 흐름에 대한 저항을 감소시키도록 사전선택된 제 2 두께( $t_2$ )를 갖는다.

- [0115] 도 12c에 도시된 본 발명의 일 실시예에서 클래딩된 모든 세그먼트(24)는 메모리 셀(20)의 길이(L) 내에 배치된다. 도 12d에 예시된 본 발명의 또 다른 실시예에서, 적어도 하나의 클래딩된 세그먼트(24)가 메모리 셀(20)의 길이(L) 내에 배치되지 않는 일부분(즉 바닥면(24b))을 갖는다.

- [0116] 도 9a, 12a 및 도 12c에 예시된 본 발명의 일 실시예에서, 제 1 및 제 2 도전체(21, 23) 모두는 이격되고 클래딩된 세그먼트(22, 24)로 분할된다. 클래딩 층(32)은 클래딩된 세그먼트(22)를 커버하고 클래딩 층(34)은 클래딩된 세그먼트(24)를 커버한다.

- [0117] 도 13a 및 도 13b에 있어서, 클래딩된 세그먼트(22, 24)의 단면도는 표준 도전체(21', 23')의 단면도(파선으로 도시됨)와 겹쳐져서 표준 도전체(21', 23')의 제 1 및 제 2 표준 두께에 대하여 클래딩된 세그먼트(22, 24)의 증가된 두께( $t_1, t_2$ )를 나타낸다. 위에서 언급한 바와 같이, 증가된 두께( $t_1, t_2$ )는 클래딩된 세그먼트(22, 24)의 단면적( $A_1, A_2$ )을 증가시키고 클래딩된 세그먼트(22, 24)에서의 전자 흐름에 대한 감소된 저항을 야기한다.

- [0118] 도전체(21, 23)를 세그먼트(22, 24)로 분할하면 데이터 층(11)의 하나 이상의 영역에 집중된 필드(concentrated field)가 인가된다. 예를 들어, 두 개 필드 소스는 데이터 층(11)의 양쪽 종단에 존재할 수 있다. 이러한 배열은 데이터 층(11)의 종단 영역에서 스위칭 프로세스가 개시되도록 제한할 수 있다. 이것은 보다 재생가능한 스위칭 프로세스를 생성한다.

- [0119] 본 명세서에서 설명된 실시예에 있어서, 클래딩 층(31, 33, 32, 34)은 강유전 재료로 만들어질 수 있다. 바람직하게, 클래딩 층(31, 33, 32, 34)은 니켈 철 합금, 니켈 철 코발트 합금, 코발트 철 합금 및 퍼멀로이(PERMALLOY<sup>TM</sup>)를 포함하는 고 투자율 연성 자기 재료(hight magnetic permeability soft magnetic material)로 만들어질 수 있지만 여기에 제한되는 것은 아니다.

- [0120] 도전체(21, 23, 22, 24)는 구리, 알루미늄, 알루미늄 구리, 탄탈, 금, 은 및 이를 전기적 도전성 재료의 합금 등을 포함하는 전기적 도전성 재료로 만들어질 수 있으나 여기에 제한되는 것은 아니다. 본 명세서에서 예시된 도전체(21, 23, 22, 24)는 데이터 층(11) 또는 기준 층(13)과 접촉하는 것으로 도시되어 있지만, 이들 구성은 단지 예시를 위한 것일 뿐이고 도전체(21, 23, 22, 24)는 메모리 셀(20)용 구조체에 포함되는 하나 이상의 재료 층에 의해 데이터 층(11) 또는 기준 층(13)으로부터 분리될 수 있다.

- 본 발명의 몇몇 실시예가 개시되고 예시되었지만, 본 발명은 본 명세서에서 설명하고 예시한 부분에 대해 특정 형태 또는 구성에 제한되지 않는다.

## 발명의 효과

- 본 발명에 의하면, 도전체의 폭 및 두께가 감소되어 도전체의 전류 밀도를 증가시켜 메모리 셀의 데이터 층의 변경 가능한 자화 배향을 스위칭하는 데 충분한 자기장의 크기가 도전체에 흐르는 감소된 전류 크기에 의해 생성될 수 있는 도전체 구조체가 제공된다.

## 도면의 간단한 설명

- 도 1a 및 도 1b 각각은 종래의 자기 메모리 소자의 측면도 및 개략도,

도 2는 종래의 자기 메모리 소자용 기록 도전체 레이아웃의 측면도,

도 3은 자기 메모리 소자용 종래의 어레이의 측면도,

도 4는 종래의 기록 도전체와 종래의 자기 메모리 소자 사이의 치수적 상관관계를 도시하는 단면도,

도 5a는 본 발명에 따른 자기장 감지 메모리 셀의 측면도,

도 5b는 본 발명에 따른 메모리 셀의 폭 및 길이를 도시하는 평면도,

도 5c 및 도 5d는 본 발명에 따른 자기 메모리 셀을 가로지르는 제 1 도전체 및 제 2 도전체의 평면도,

도 5e 및 도 5f는 본 발명에 따른 자기 메모리 장치의 개략도,

도 6a 및 도 7a는 본 발명에 따른 감소된 폭 및 감소된 두께의 도전체에 대한 단면도,

도 6b 및 도 7b 각각은 본 발명에 따라 표준 폭, 표준 길이 및 표준 두께를 갖는 도전체에 관하여, 도 6a 및 도 7a의 감소된 폭 및 감소된 두께의 도전체를 도시하는 단면도,

도 6c는 본 발명에 따라 길이 방향으로 메모리 셀을 가로지르는 제 2 도전체의 단면도,

도 8a, 8b 및 도 8c는 제각기 본 발명에 따라 다수의 이격된 세그먼트로 분할되는 도전체의 평면도 및 단면도,

도 9a, 9b 및 도 9c는 제각기 본 발명에 따라 다수의 이격된 세그먼트로 분할되는 한 쌍의 도전체의 평면도 및 단면도,

도 10a 및 도 11a는 본 발명에 따라 감소된 폭 및 증가된 두께를 갖는 클래딩된 도전체의 단면도,

도 10b 및 도 11b 각각은 본 발명에 따라 표준 폭, 표준 길이 및 표준 두께를 갖는 도전체에 관하여, 도 10a 및 도 11a의 감소된 폭 및 감소된 두께의 도전체를 도시하는 단면도,

도 12a, 12b, 12c 및 도 12d는 제각기 본 발명에 따라 다수의 이격된 클래딩된 세그먼트로 분할되는 감소된 폭 및 증가된 두께를 갖는 부분적으로 클래딩된 단면도,

도 13a 및 도 13b 각각은 본 발명에 따라 표준 폭, 표준 길이 및 표준 두께를 갖는 도전체에 관하여, 도 12a 및 도 12c 및 도 12b 및 도 12d의 이격되고 부분적으로 클래딩된 세그먼트의 단면도,

도 14는 본 발명에 따라 도전체의 주변 근처의 자기 경로에 대한 단면도,

도 15는 본 발명에 따라 부분적으로 클래딩된 도전체의 단면도.

## 도면의 주요 부분에 대한 부호의 설명

- |            |                 |

|------------|-----------------|

| 11 : 데이터 총 | 13 : 기준 총       |

| 15 : 장벽 총  | 17 : 변경가능 자화 배향 |

| 20 : 메모리 셀 | 21 : 제 1 도전체    |

## 도면

## 도면1a

## 도면1b

## 도면2

## 도면3

## 도면4

## 도면5a

도면5b

도면5c

도면5d

도면5e

도면5f

도면6a

도면6b

도면6c

도면7a

도면7b

도면8a

도면8b

도면8c

도면9a

도면9b

도면9c

도면10a

도면10b

도면11a

도면11b

도면12a

도면12b

도면12c

도면12d

도면13a

도면13b

도면14

도면15