(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4939769号

(P4939769)

(45) 発行日 平成24年5月30日(2012.5.30)

(24) 登録日 平成24年3月2日(2012.3.2)

(51) Int.Cl.

F 1

|              |           |             |      |

|--------------|-----------|-------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78  | 613Z |

| HO1L 27/04   | (2006.01) | HO1L 27/04  | C    |

| HO1L 21/822  | (2006.01) | GO2F 1/1368 |      |

| GO2F 1/1368  | (2006.01) | HO1L 27/06  | 102A |

| HO1L 21/8234 | (2006.01) | HO1L 29/78  | 612Z |

請求項の数 3 (全 27 頁) 最終頁に続く

(21) 出願番号

特願2005-127336 (P2005-127336)

(22) 出願日

平成17年4月26日 (2005.4.26)

(65) 公開番号

特開2005-340791 (P2005-340791A)

(43) 公開日

平成17年12月8日 (2005.12.8)

審査請求日 平成20年4月22日 (2008.4.22)

(31) 優先権主張番号 特願2004-132813 (P2004-132813)

(32) 優先日 平成16年4月28日 (2004.4.28)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 加藤 清

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 塩野入 豊

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 棚田 一也

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁表面上の半導体膜と、電極と、前記半導体膜及び前記電極にはさまれた絶縁膜とを有し、

前記半導体膜は、n型の導電性を有する第1の領域及び第3の領域と、p型の導電性を有する第2の領域及び第4の領域と、第1のチャネル形成領域乃至第3のチャネル形成領域とを有し、

前記第1のチャネル形成領域は、前記第1の領域と前記第2の領域にはされ、

前記第2のチャネル形成領域は、前記第2の領域と前記第3の領域にはされ、

前記第3のチャネル形成領域は、前記第3の領域と前記第4の領域にはされ、

前記第1の領域乃至前記第4の領域は、電気的に接続され、

前記電極は、前記第1のチャネル形成領域乃至前記第3のチャネル形成領域上に形成されていることを特徴とする半導体装置。

## 【請求項 2】

絶縁表面上の半導体膜と、電極と、前記半導体膜及び前記電極にはさまれた第1の絶縁膜と、前記電極の側壁に接して設けられた第2の絶縁膜とを有し、

前記半導体膜は、n型の導電性を有する第1の領域及び第3の領域と、p型の導電性を有する第2の領域及び第4の領域と、前記第1の領域及び前記第3の領域より不純物濃度の低いn型の導電性を有する第5の領域及び第6の領域と、第1のチャネル形成領域乃至第3のチャネル形成領域とを有し、

10

20

前記第1のチャネル形成領域は、前記第1の領域と前記第2の領域にはさまれ、

前記第2のチャネル形成領域は、前記第2の領域と前記第3の領域にはさまれ、

前記第3のチャネル形成領域は、前記第3の領域と前記第4の領域にはさまれ、

前記第5の領域は、前記第1の領域と前記第1のチャネル形成領域にはさまれ、

前記第6の領域は、前記第3の領域と前記第3のチャネル形成領域にはさまれ、

前記第1の領域乃至前記第4の領域は、電気的に接続され、

前記電極は、前記第1のチャネル形成領域乃至前記第3のチャネル形成領域上に形成され、

前記第2の絶縁膜は、前記第5の領域及び前記第6の領域上に形成されていることを特徴とする半導体装置。

10

### 【請求項3】

請求項1又は請求項2において、

前記第1の領域乃至前記第4の領域に対して、前記電極に正の電位が与えられたとき、

前記第1の領域と前記電極との間の電位差によって前記第1のチャネル形成領域にチャネルが形成され、かつ前記第3の領域と前記電極との間の電位差によって前記第2のチャネル形成領域にチャネルが形成され、かつ前記第3の領域と前記電極との間の電位差によって前記第3のチャネル形成領域にチャネルが形成され、

前記第1の領域乃至前記第4の領域に対して、前記電極に負の電位が与えられたとき、

前記第2の領域と前記電極との間の電位差によって前記第1のチャネル形成領域にチャネルが形成され、かつ前記第2の領域と前記電極との間の電位差によって前記第2のチャネル形成領域にチャネルが形成され、かつ前記第4の領域と前記電極との間の電位差によって前記第3のチャネル形成領域にチャネルが形成されることを特徴とする半導体装置。

20

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、トランジスタを用いた容量素子に関し、さらに該容量素子を用いた半導体装置に関する。

#### 【背景技術】

#### 【0002】

容量素子は、半導体集積回路（以下、単に集積回路）、特にアナログ回路の作製において不可欠な受動素子の一つであり、具体的には、電源回路、DRAMなどのアナログ回路の他、液晶表示装置の画素の保持容量としても用いられている。容量素子は、その占有面積の増加が集積回路のコスト増に繋がるので、より小さい占有面積で大きな容量値を有することが望ましい。

30

#### 【0003】

ところでトランジスタのゲート絶縁膜は、集積回路に用いられている他の絶縁膜に比べ、薄く均一な膜厚を有し、膜中における欠陥や不純物が少なく、膜厚の割に絶縁破壊に対する耐圧が高いという優れた特質を有している。そのためゲート絶縁膜は容量素子の誘電体としても適しており、トランジスタと容量素子とを共に有する集積回路の場合、トランジスタの半導体層とゲート電極の間に形成されるMOS容量（ゲート容量）を、容量素子として用いることが多い。MOS容量を用いた容量素子（以下、MOS容量素子と呼ぶ）は、上述したような優れた特質を有するゲート絶縁膜を誘電体として用いることができ、なおかつ工程数を増やすことなくトランジスタと共に形成することができる。

40

#### 【0004】

下記特許文献1には、従来のMOS容量素子の構成について記載されている。

【特許文献1】特開平7-45789号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0005】

ところがMOS容量素子は、チャネルが半導体層に形成されることで、はじめて容量素

50

子として機能する。そのため、トランジスタをMOS容量素子として用いるには、該トランジスタの極性に合わせてゲート電極とソース領域間の電圧（ゲート電圧）を制御する必要がある。具体的には、トランジスタがn型の場合、ゲート電圧を閾値電圧より大きくし、逆にトランジスタがp型の場合、ゲート電圧を閾値電圧より小さくする必要がある。

#### 【0006】

従って上記MOS容量素子は極性を有しており、ソース領域またはドレイン領域の電位と、ゲート電極の電位との大小（正負）関係が逆転するような回路には、チャネルが形成されずに容量素子として機能しない場合が生じる。例えばRF共振回路にMOS容量素子を用いようとすると、交流の電圧がゲート電極と、ソース領域またはドレイン領域との間に印加されることになる。よって、ゲート電極の電位と、ソース領域またはドレイン領域の電位の大小関係が所定の間隔をもって反転することになり、常に容量素子として機能させることが難しい。また液晶表示装置の画素に用いられる保持容量の場合も、駆動方法によっては交流の電圧が保持容量に印加されることになるので、MOS容量素子を保持容量として用いることが難しい。10

#### 【0007】

従って、交流の電圧が印加されるような容量素子には、2つの電極間における電位の大小（正負）関係に依存せずに、容量素子として機能することができるよう、無極性の容量素子を用いる必要がある。以後、無極性の容量素子とは、2つの電極間における電位の大小（正負）関係に依存せずに機能することができる容量素子を指すものとする。しかしながら、集積回路に用いられているゲート絶縁膜以外の絶縁膜は、一般的にゲート絶縁膜に比べて膜厚が厚い。そのため、該絶縁膜を誘電体として用いて容量素子を形成すると、面積あたりの容量値が低くなってしまい、容量素子の集積回路における占有面積を抑え難くなる。また容量素子の面積あたりの容量値を高めるためだけに、膜厚がゲート絶縁膜並みに薄い絶縁膜を別途形成し、容量素子の誘電体として用いると、集積回路の作製工程の数が増加して好ましくない。20

#### 【0008】

本発明は上記問題に鑑み、半導体装置の作製工程数を増加させることなく、交流の電圧を印加しても容量素子として機能させることができる、容量素子の提供を課題とする。

#### 【課題を解決するための手段】

#### 【0009】

本発明は、MOS容量素子として用いるトランジスタにおいて、チャネル形成領域を間に挟んで存在する一対の不純物領域に、互いに極性の異なる不純物を添加し、ソース領域またはドレイン領域として用いることを特徴とする。具体的には、n型の不純物が添加された不純物領域（第1の不純物領域）をn型領域、p型の不純物が添加された不純物領域（第2の不純物領域）をp型領域とすると、本発明ではチャネル形成領域がn型領域とp型領域の間に挟まれているトランジスタを、MOS容量素子として用いる。30

#### 【0010】

上記構成を有するMOS容量素子の場合、ゲート電圧が閾値電圧より大きくなると、n型領域からの自由電子によりチャネル形成領域にnチャネルが形成される。逆にゲート電圧が閾値電圧より小さくなると、p型領域からの自由正孔によりチャネル形成領域にpチャネルが形成される。よって、上記構成を有するMOS容量素子は、いずれの場合でもチャネルを形成することができるので、ソース領域またはドレイン領域の電位と、ゲート電極の電位との大小（正負）関係に依らず、無極性の容量素子として機能することができる。40

#### 【0011】

なお上記MOS容量として用いられるトランジスタは、半導体基板を用いて形成されたトランジスタであっても良いし、SOI基板を用いて形成されたトランジスタであっても良い。或いは、ガラス基板、石英基板、プラスチック基板などの絶縁表面を有する基板上に形成された薄膜の半導体膜を用いて形成されたトランジスタであっても良い。

#### 【0012】

50

20

30

40

50

また本発明の半導体装置は、上記MOS容量素子を用いた集積回路と、上記MOS容量素子を用いた半導体表示装置とをその範疇に含む。集積回路には、マイクロプロセッサ、画像処理回路等、容量素子を用いることができる、ありとあらゆる集積回路が含まれる。また半導体表示装置には、液晶表示装置、有機発光素子(OLED)に代表される発光素子を各画素に備えた発光装置、DMD(Digital Micromirror Device)、PDP(Plasma Display Panel)、FED(Field Emission Display)等や、半導体膜を用いた回路素子を駆動回路に有しているその他の表示装置がその範疇に含まれる。半導体表示装置の場合、画素にMOS容量素子が用いられていても良いし、駆動回路に用いられていても良い。

## 【発明の効果】

10

## 【0013】

上記構成を有するMOS容量素子は、作製工程数を増加させることなく、n型のトランジスタ、p型のトランジスタと共に形成することができる。また無極性の容量素子として機能するので、交流の電圧を用いるようなアナログ回路や、半導体表示装置にも用いることができ、その用途範囲を広げることができる。

## 【0014】

さらに上記構成を有するMOS容量素子は、ゲート絶縁膜を容量素子の誘電体として用いることができる。ゲート絶縁膜は、集積回路に用いられている他の絶縁膜に比べて薄く均一な膜厚を有するため、ゲート絶縁膜を誘電体として用いることで、容量素子の面積あたりの容量値を高め、容量素子の集積回路における占有面積を抑えることができる。

20

## 【0015】

またゲート絶縁膜は、膜中における欠陥や不純物が少なく、膜厚が均一であるため、膜厚の割に絶縁破壊に対する耐圧が高いという優れた特質を有している。よって、耐圧性に優れたMOS容量素子を形成することができる。

## 【0016】

また本発明の半導体装置は、作製工程数を抑えつつ、面積あたりの容量値が高いMOS容量素子を形成することができるので、コストを抑えることができる。さらにMOS容量素子は無極性であるので、半導体装置の設計上の制約を緩和することができる。

## 【発明を実施するための最良の形態】

## 【0017】

30

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従つて、本実施の形態の記載内容に限定して解釈されるものではない。

## 【0018】

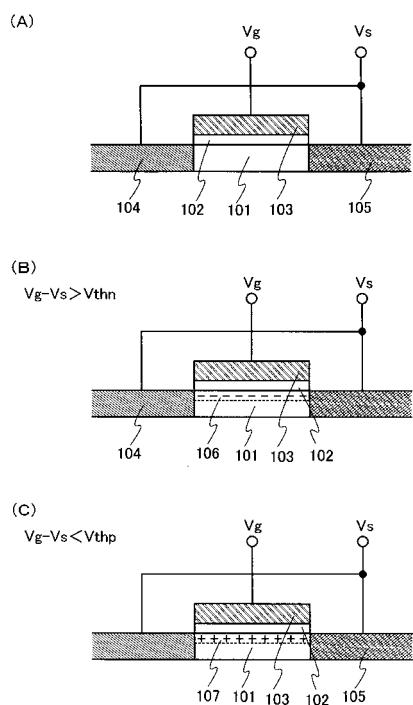

図1を用いて、本発明のMOS容量素子の構成について説明する。図1(A)は、本発明のMOS容量素子の断面を模式的に表した図であり、101はチャネル形成領域、102はゲート絶縁膜、103は電極(ゲート電極)に相当する。チャネル形成領域101とゲート電極103は、絶縁膜(ゲート絶縁膜)102を間に挟んで重なり合っている。

## 【0019】

40

また104はn型領域(第1の不純物領域)、105はp型領域(第2の不純物領域)に相当する。n型領域104は、n型の導電性を示すように半導体にn型の不純物が添加されている領域であり、p型領域105は、p型の導電性を示すように半導体にp型の不純物が添加されている領域である。チャネル形成領域101は、n型領域104とp型領域105の間に挟まれており、n型領域104とp型領域105はソース領域またはドレイン領域として機能する。

## 【0020】

そして、ゲート電極103の電圧Vgと、n型領域104またはp型領域105の電圧Vsとの差に相当するゲート電圧によって、MOS容量素子に電荷を蓄積させることができる。

50

## 【0021】

図1(B)に、nチャネルをチャネル形成領域101に形成することで、図1(A)のMOS容量素子に電荷を蓄積させている状態を示す。nチャネルを形成するための閾値電圧をV<sub>thn</sub>とすると、V<sub>g</sub> - V<sub>s</sub> > V<sub>thn</sub>とすることで、チャネル形成領域101のうち、ゲート絶縁膜102により近い領域にnチャネル106を形成させることができる。nチャネル106には、チャネル形成領域101で発生した自由電子(-)と、n型領域104からの自由電子(-)とが蓄積されているいため、n型の導電性を有する。

## 【0022】

よって、ゲート電極103と、nチャネル106或いはn型領域104との間に、電荷を蓄積することができる。

10

## 【0023】

図1(C)に、pチャネルをチャネル形成領域101に形成することで、図1(A)のMOS容量素子に電荷を蓄積させている状態を示す。pチャネルを形成するための閾値電圧をV<sub>thp</sub>とすると、V<sub>g</sub> - V<sub>s</sub> < V<sub>thp</sub>とすることで、チャネル形成領域101のうち、ゲート絶縁膜102により近い領域にpチャネル107を形成させることができる。pチャネル107には、チャネル形成領域101で発生した自由正孔(+)と、p型領域105からの自由正孔(+)とが蓄積されているいため、p型の導電性を有する。

## 【0024】

よって、ゲート電極103と、pチャネル107或いはp型領域105との間に、電荷を蓄積することができる。

20

## 【0025】

図1(B)、図1(C)に示したように、ゲート電極103の電圧V<sub>g</sub>と、n型領域104またはp型領域105の電圧V<sub>s</sub>とが逆転しても、いずれの場合においてもMOS容量素子に電荷を蓄積することができる。

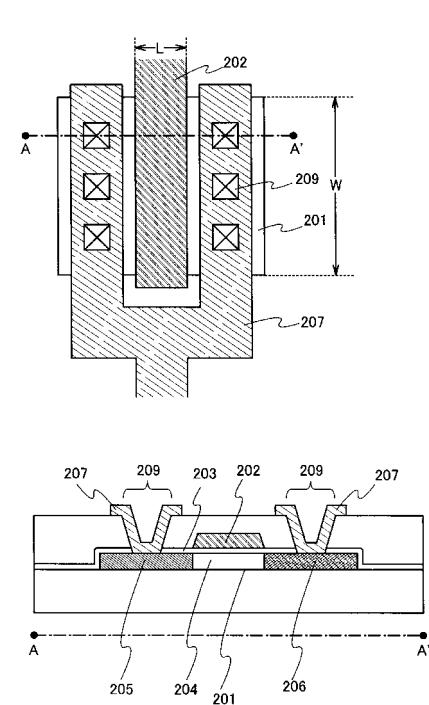

## 【0026】

次に図2(A)に、薄膜トランジスタ(TFT)を用いた場合の、MOS容量素子の上面図を示す。また図2(B)に、図2(A)に示したMOS容量素子の、A-A'における断面図を示す。201は半導体膜で形成された半導体層であり、202はゲート電極である。半導体層201は、チャネル形成領域204と、n型領域205と、p型領域206とを有しており、チャネル形成領域204はn型領域205とp型領域206の間に挟まれている。またチャネル形成領域204は、ゲート絶縁膜203を間に挟んで、ゲート電極202と重なっている。

30

## 【0027】

そして、n型領域205とp型領域206は、配線207にコンタクトホール209において接続されている。なお図2では、n型領域205とp型領域206とが配線207によって接続されているが、複数の配線によって接続されても良い。

## 【0028】

MOS容量素子に蓄積することができる電荷量は、ゲート絶縁膜203の膜厚及び誘電率に依存するが、その他にチャネル形成領域204の面積にも依存する。そしてチャネル形成領域204の面積が同じである場合、チャネル長Lが短いほど、電荷を蓄積するのに費やされる時間を短縮化することができる。

40

## 【0029】

なお図2では、半導体層にチャネル形成領域が1つだけ形成されているMOS容量素子の構成について示しているが、本発明はこの構成に限定されない。半導体層に複数のチャネル形成領域が形成されている、MOS容量素子の構成について、図3を用いて説明する。

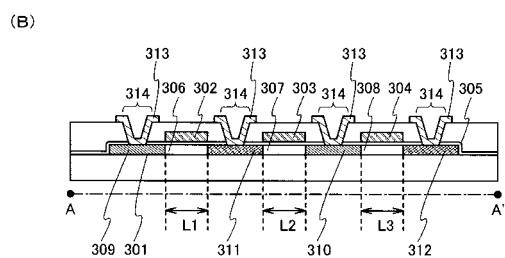

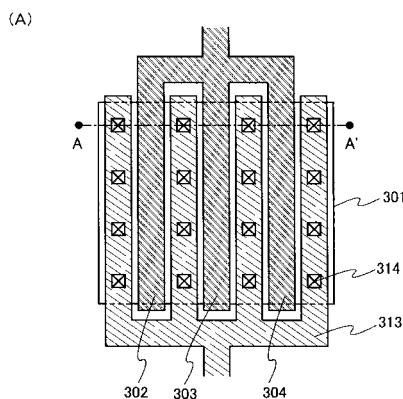

## 【0030】

次に図3(A)に、チャネル形成領域を3つ有するTFTを用いた、MOS容量素子の上面図を示す。また図3(B)に、図3(A)に示したMOS容量素子の、A-A'における断面図を示す。301は半導体層であり、302~304はゲート電極である。

50

## 【0031】

半導体層301は、チャネル形成領域306～308と、n型領域309、310と、p型領域311、312とを有している。

そして各チャネル形成領域306～308は、n型領域309、310とp型領域311、312とに挟まれている。具体的に、チャネル形成領域306はn型領域309とp型領域311の間に挟まれている。チャネル形成領域307はp型領域311とn型領域310の間に挟まれている。チャネル形成領域308はn型領域310とp型領域312の間に挟まれている。

## 【0032】

またチャネル形成領域306は、ゲート絶縁膜305を間に挟んでゲート電極302と重なっている。チャネル形成領域307は、ゲート絶縁膜305を間に挟んでゲート電極303と重なっている。チャネル形成領域308は、ゲート絶縁膜305を間に挟んでゲート電極304と重なっている。10

## 【0033】

そして、n型領域309、310、p型領域311、312は、配線313にコンタクトホール314において接続されている。なお図3では、n型領域309、310、p型領域311、312が、配線313によって互いに接続されているが、複数の配線によって接続されていても良い。

## 【0034】

またゲート電極302～304は、一続きの導電膜で形成されている。図3では、ゲート電極302～304を、一続きの導電膜で形成することで電気的に接続しているが、本発明はこの構成に限定されない。互いに独立したゲート電極302～304を、配線で電気的に接続するようにしても良い。20

## 【0035】

図3の場合、並列に接続された複数のMOS容量素子が、1つのMOS容量素子として機能する。そして図3では、図2の場合とチャネル幅Wが同じであったとしても、チャネル形成領域306～308の各チャネル長L1～L3の長さを抑えることができるので、等量の電荷を蓄積するのに費やされる時間を図2の場合よりも短縮化することができる。

## 【0036】

図3では、チャネル形成領域を3つ有するMOS容量素子の構成について示しているが、本発明はこの構成に限定されない。MOS容量素子はチャネル形成領域を2つ有していても良いし、4つ以上有していても良い。たとえば、チャネル形成領域が5つの場合には、チャネル形成領域を間に挟み合計6つ不純物領域、即ち3つのn型領域と3つのp型領域とを有し、それぞれが交互に形成された構成となる。ゲート電極は各チャネル形成領域と絶縁膜を間に挟んで重なり5つ形成される。30

## 【0037】

なお図2、図3では、TFTをMOS容量素子として用いる例について説明したが、本発明においてMOS容量素子として用いるトランジスタはTFTに限定されない。本発明のMOS容量素子は、その他のMOSトランジスタを用いることができる。

## 【0038】

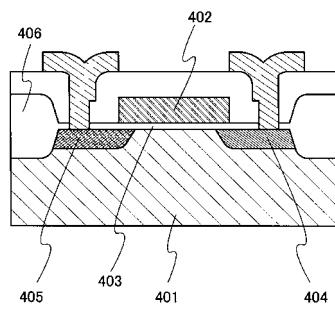

図4に、半導体基板に形成されたトランジスタを、MOS容量素子として用いる例を示す。図4において、401は半導体基板、402はゲート電極、403はゲート絶縁膜である。また半導体基板401には、n型領域404とp型領域405とが形成されている。ゲート電極402は、半導体基板401のうち、n型領域404とp型領域405で挟まれている領域と、ゲート絶縁膜403を間に挟んで重なっている。406は、素子間を電気的に分離するための、フィールド酸化膜に相当する。40

## 【0039】

そしてn型領域404またはp型領域405と、ゲート電極402との間の電圧を制御することで、半導体基板401のうち、n型領域404とp型領域405で挟まれている領域の、よりゲート絶縁膜403に近い領域に、チャネルを形成することができる。50

## 【実施例 1】

## 【0040】

本実施例では、本発明のMOS容量素子を、液晶表示装置の画素の保持容量として用いる例について説明する。

## 【0041】

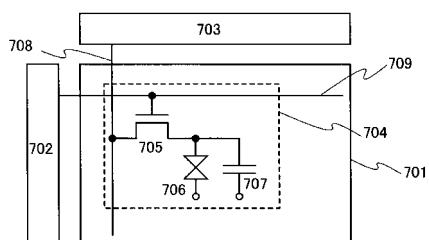

図5は、液晶表示装置の構成を示すブロック図である。図5において、701は画素部、702は走査線駆動回路、703は信号線駆動回路に相当する。画素部701には複数の画素704がマトリクス状に形成されている。なお図5では、一つの画素704のみを例示している。画素704は、スイッチング素子として機能するTFT705と、液晶セル706と、保持容量707とを有している。液晶セル706は、画素電極と、対向電極と、画素電極と対向電極の間に挟持された液晶とを有している。10

## 【0042】

また画素部701には、信号線708と走査線709が形成されている。TFT705のゲート電極は走査線709に接続されており、TFT705のソース領域またはドレイン領域は、一方が信号線708に、他方が液晶セル706の画素電極に接続されている。また保持容量707が有する2つの電極は、一方が液晶セル706の画素電極に、他方が液晶セル706の対向電極に接続されている。

## 【0043】

走査線駆動回路702は、走査線709への選択信号の入力を制御することができる。20

信号線駆動回路703は、信号線708への映像信号の入力を制御することができる。選択信号によってTFT705がオンになると、信号線708に入力された映像信号の電圧が、液晶セル706の画素電極及び保持容量707の一方の電極に供給される。液晶セル706は、画素電極と、対向電極の間の電圧により、その透過率が制御される。また液晶セル706の画素電極と対向電極の間の電圧は、保持容量707に印加され、そこで保持される。

## 【0044】

なお液晶セル706の画素電極と対向電極の間に、同じ極性の電圧が印加され続けると、液晶の劣化を引き起こしてしまう。そのため通常、一定の間隔ごとに、液晶セル706の画素電極と対向電極の間に、極性の異なる電圧を交互に印加する反転駆動が行なわれる。30

反転駆動は、対向電極を一定の電圧に保ち、画素電極の電圧を反転させる方法、画素電極を一定の電圧に保ち、対向電極の電圧を反転させる方法、画素電極の電圧と対向電極の電圧を共に変化させて反転させる方法とがある。いずれの場合においても、保持容量707に印加される電圧の極性は反転することになる。

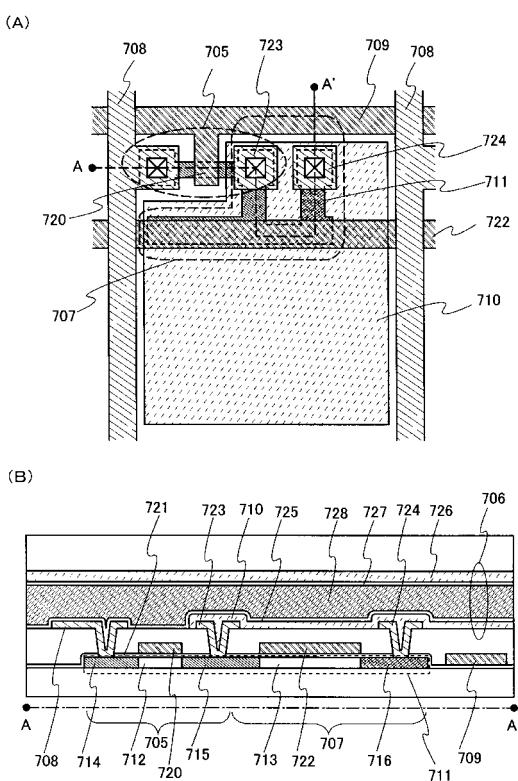

## 【0045】

図15(A)に、保持容量707に本発明のMOS容量素子を用いた場合の、画素704の上面図の一例を示す。また図15(A)のA-A'における断面図を、図15(B)に示す。図15(B)において、走査線709の一部はTFT705のゲート電極720として機能する。

## 【0046】

保持容量707は、TFT705と半導体層711を共有している。半導体層711は、TFT705のチャネル形成領域712と、保持容量707のチャネル形成領域713と、n型領域714、715と、p型領域716とを有している。そしてTFT705は、ゲート電極720がゲート絶縁膜721を間に挟んでチャネル形成領域712と重なっている。保持容量707は、ゲート電極722がゲート絶縁膜721を間に挟んでチャネル形成領域713と重なっている。40

## 【0047】

そしてチャネル形成領域712は、n型領域714、715によって挟まれており、n型領域714、715はTFT705のソース領域またはドレイン領域として機能する。またチャネル形成領域713は、n型領域715、p型領域716によって挟まれており、n型領域715、p型領域716は保持容量707のソース領域またはドレイン領域と50

して機能する。

【0048】

n型領域714は、信号線708に接続されている。n型領域715は、配線723に接続されている。p型領域716は、配線724に接続されている。また710は、液晶セル706の画素電極に相当し、配線723、724は、共に画素電極710に接続されている。画素電極710上には配向膜725が形成されている。

【0049】

また726は対向電極であり、対向電極726上には配向膜727が形成されている。液晶728は、画素電極710及び配向膜725と、対向電極726及び配向膜727との間に挟持されている。この画素電極710と、液晶728と、対向電極726とによって、液晶セル706が形成されている。10

【0050】

なお図5に示す液晶表示装置の構成は、ほんの一実施例にすぎず、本発明の半導体表示装置は図5に示した構成に限定されない。

【実施例2】

【0051】

本発明のMOS容量素子は、無線で識別情報などのデータの送受信が可能なIDチップまたはICカードなどの半導体装置において、アンテナと接続して共振回路を形成するための容量素子としても、用いることができる。なおIDチップは、無線タグ、RFID(Radio frequency identification)タグ、ICタグ、無線チップとも呼ばれている。そしてIDチップとICカードは、アンテナと集積回路とを有している。20

【0052】

IDチップまたはICカードは、電波を用いてリーダ/ライタとの間の通信を行なうことができる。具体的には、リーダ/ライタから発せられる電波によりアンテナに生じる交流の電圧(交流電圧)を用いて、集積回路を動作させ、また、集積回路から出力された信号を用いてアンテナに発生する信号を変調することで、リーダ/ライタに信号を送ることができる。

【0053】

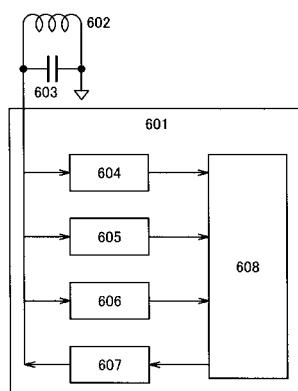

図6に、本実施例のICチップまたはIDチップの、機能的な構成の一例をブロック図で示す。図6において、601は集積回路、602はアンテナに相当する。またアンテナ602の両端子間には、容量素子603が接続されている。本発明のMOS容量素子は、容量素子603として用いることができる。30

【0054】

また集積回路601は、整流回路604、クロック生成回路605、復調回路606、変調回路607、論理回路部608とを有している。論理回路部608には各種演算回路、メモリなどが含まれていても良い。メモリには、例えばSRAM、フラッシュメモリ、ROMまたはFeRAM(Ferroelectric RAM)などを用いることができる。

【0055】

リーダ/ライタから電波として送られてきた信号は、アンテナ602において電磁誘導により交流電圧に変換される。復調回路606では該交流電圧を復調して信号を生成し、後段の論理回路部608に入力する。また整流回路604では、交流電圧を用いて電源電圧を生成し、論理回路部608に供給する。40

【0056】

論理回路部608では、復調回路606から入力された信号、供給された電源電圧を用いて各種処理を行なう。そして論理回路部608が各種処理を行なうことで、論理回路部608から変調回路607に信号が送られる。変調回路607は論理回路部608からの信号に従って、アンテナ602に発生する信号を変調することができる。リーダ/ライタは、アンテナ602で発生した変調された信号を電波で受け取ることで、結果的に論理回50

路部 608 からの信号を受信することができる。

**【0057】**

上述した動作からわかるように、アンテナ 602 の両端子間に交流の電圧が印加されるため、容量素子 603 は無極性のものを用いる必要がある。本発明の M O S 容量素子は無極性であるので、容量素子 603 として用いるのに適している。さらに本発明の M O S 容量素子は、集積回路 601 に用いられるトランジスタと共に形成することができるので、半導体装置の作製工程数を抑えることができる。

**【0058】**

なお本発明の M O S 容量素子は、アンテナ 602 の両端子間に接続する容量素子だけではなく、集積回路 601 内に形成されるその他の容量素子としても用いることができる。

10

**【0059】**

なお本実施例では、電磁誘導方式で信号の伝送を行なう半導体装置の構成について説明したが、本発明はこの構成に限定されない。本発明の範疇に含まれる、無線での通信が可能な半導体装置は、電磁結合方式、マイクロ波方式、その他の伝送方式を用いることができる。

**【実施例 3】**

**【0060】**

次に、本発明の半導体装置の 1 つである、 I D チップの詳しい作製方法について説明する。なお本実施例では、 T F T と M O S 容量素子とを半導体素子の一例として示すが、集積回路に用いられる半導体素子はこれらのみに限定されない。例えば、記憶素子、ダイオード、光電変換素子、抵抗素子、コイル、インダクタを半導体素子として用いることができる。

20

**【0061】**

まず図 7 ( A ) に示すように、耐熱性を有する第 1 の基板 500 上に剥離層 501 を形成する。第 1 の基板 500 として、例えばバリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板等を用いることができる。また、ステンレス ( S U S ) 基板を含む金属基板または半導体基板を用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板は、一般的に上記基板と比較して耐熱温度が低い傾向にあるが、作製工程における処理温度に耐え得るのであれば用いることができる。

30

**【0062】**

剥離層 501 は、非晶質珪素、多結晶珪素、単結晶珪素、微結晶珪素 ( セミアモルファスシリコンを含む ) 等、珪素を主成分とする層を用いることができる。剥離層 501 は、スパッタ法、減圧 C V D 法、プラズマ C V D 法等を用いて形成することができる。本実施例では、膜厚 50 nm 程度の非晶質珪素をプラズマ C V D 法で形成し、剥離層 501 として用いる。剥離層 501 は、スパッタ法で形成するよりもプラズマ C V D 法を用いて形成する方が、剥離層 501 に塵埃が含まれてしまうのを防ぐことができ、また剥離層 501 に含まれる A r の量を抑えることができる。従って、後の作製工程においてレーザ結晶化などを含む熱処理が剥離層 501 に加えられても、塵埃や A r 起因により、剥離層 501 が後に形成される下地膜 502 から剥離するのを抑えることができる。なお剥離層 501 は珪素に限定されず、エッチングにより選択的に除去できる材料で形成すれば良い。剥離層 501 の膜厚は、 10 ~ 100 nm とするのが望ましい。

40

**【0063】**

次に、剥離層 501 上に下地膜 502 を形成する。下地膜 502 は第 1 の基板 500 中に含まれる N a などのアルカリ金属やアルカリ土類金属が、半導体膜中に拡散し、 T F T などの半導体素子の特性に悪影響を及ぼすのを防ぐために設ける。また下地膜 502 は、後の半導体素子を剥離する工程において、半導体素子を保護する役目も有している。下地膜 502 には、例えば酸化珪素、酸化窒化珪素、窒化珪素、窒化酸化珪素などの絶縁膜を用いることができる。

**【0064】**

50

下地膜502は、単数の絶縁膜を用いたものであっても、複数の絶縁膜を積層して用いたものであっても良い。本実施例では、膜厚100nmの酸化窒化珪素膜、膜厚50nmの窒化酸化珪素膜、膜厚100nmの酸化窒化珪素膜を順に積層して下地膜502を形成するが、各膜の材質、膜厚、積層数は、これに限定されるものではない。例えば、下層の酸化窒化珪素膜に代えて、膜厚0.5~3μmのシロキサン系樹脂をスピンドルコート法、スリットコーティング法、液滴吐出法、印刷法などによって形成しても良い。また、中層の窒化酸化珪素膜に代えて、窒化珪素膜(SiNx、Si<sub>3</sub>N<sub>4</sub>等)を用いてもよい。また、上層の酸化窒化珪素膜に代えて、酸化珪素膜を用いていても良い。また、それぞれの膜厚は、0.05~3μmとするのが望ましく、その範囲から自由に選択することができる。

## 【0065】

10

或いは、剥離層501に最も近い、下地膜502の下層を酸化窒化珪素膜または酸化珪素膜で形成し、中層をシロキサン系樹脂で形成し、上層を酸化珪素膜で形成しても良い。

## 【0066】

なお、シロキサン樹脂とは、Si-O-Si結合を含む樹脂に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

## 【0067】

20

酸化珪素膜は、SiH<sub>4</sub>とO<sub>2</sub>との混合ガス、TEOS(テトラエトキシシラン)とO<sub>2</sub>等の混合ガスを用い、熱CVD、プラズマCVD、常圧CVD、バイアスECR-CVD等の方法によって形成することができる。また、窒化珪素膜は、代表的には、SiH<sub>4</sub>/NH<sub>3</sub>の混合ガスを用い、プラズマCVDによって形成することができる。また、酸化窒化珪素膜、窒化酸化珪素膜は、代表的には、SiH<sub>4</sub>とN<sub>2</sub>Oの混合ガスを用い、プラズマCVDによって形成することができる。

## 【0068】

次に、下地膜502上に半導体膜503を形成する。半導体膜503は、下地膜502を形成した後、大気に曝さずに形成することが望ましい。半導体膜503の膜厚は20~200nm(望ましくは40~170nm、好ましくは50~150nm)とする。なお半導体膜503は、非晶質半導体であっても良いし、セミアモルファス半導体であっても良いし、多結晶半導体であっても良い。また半導体は珪素だけではなくシリコンゲルマニウムも用いることができる。シリコンゲルマニウムを用いる場合、ゲルマニウムの濃度は0.01~4.5atomic%程度であることが好ましい。

30

## 【0069】

なお半導体膜503は、公知の技術により結晶化しても良い。公知の結晶化方法としては、レーザ光を用いたレーザ結晶化法、触媒元素を用いる結晶化法がある。或いは、触媒元素を用いる結晶化法とレーザ結晶化法とを組み合わせて用いることもできる。また、第1の基板500として石英のような耐熱性に優れている基板を用いる場合、電熱炉を使用した熱結晶化方法、赤外光を用いたランプアニール結晶化法、触媒元素を用いる結晶化法と、950程度の高温アニールを組み合わせた結晶法を用いても良い。

40

## 【0070】

例えばレーザ結晶化を用いる場合、レーザ結晶化の前に、レーザに対する半導体膜503の耐性を高めるために、550、4時間の加熱処理を該半導体膜503に対して行なう。そして連続発振が可能な固体レーザを用い、基本波の第2高調波~第4高調波のレーザ光を照射することで、大粒径の結晶を得ることができる。例えば、代表的には、Nd:YVO<sub>4</sub>レーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いるのが望ましい。具体的には、連続発振のYVO<sub>4</sub>レーザから射出されたレーザ光を非線形光学素子により高調波に変換し、出力10Wのレーザ光を得る。そして、好ましくは光学系により照射面にて矩形状または橢円形状のレーザ光に成形して、半導体膜503に照射する。このときのエネルギー密度は0.01~100MW/cm<sup>2</sup>程度

50

(好ましくは  $0.1 \sim 10 \text{ MW/cm}^2$ ) が必要である。そして、走査速度を  $10 \sim 20 \text{ cm/sec}$  程度とし、照射する。

#### 【0071】

また、パルス発振のレーザ光の繰り返し周波数を  $10 \text{ MHz}$  以上とし、通常用いられている数十Hz～数百Hzの周波数帯よりも著しく高い周波数帯を用いてレーザ結晶化を行なっても良い。パルス発振でレーザ光を半導体膜に照射してから半導体膜が完全に固化するまでの時間は数十nsec～数百nsecと言われている。よって上記周波数を用いることで、半導体膜がレーザ光によって溶融してから固化するまでに、次のパルスのレーザ光を照射できる。したがって、半導体膜中において固液界面を連続的に移動させることができるので、走査方向に向かって連続的に成長した結晶粒を有する半導体膜が形成される。具体的には、含まれる結晶粒の走査方向における幅が  $10 \sim 30 \mu\text{m}$ 、走査方向に対して垂直な方向における幅が  $1 \sim 5 \mu\text{m}$  程度の結晶粒の集合を形成することができる。該走査方向に沿って長く伸びた単結晶の結晶粒を形成することで、少なくとも TFT のチャネル方向には結晶粒界のほとんど存在しない半導体膜の形成が可能となる。10

#### 【0072】

なおレーザ結晶化は、連続発振の基本波のレーザ光と連続発振の高調波のレーザ光とを並行して照射するようにしても良いし、連続発振の基本波のレーザ光とパルス発振の高調波のレーザ光とを並行して照射するようにしても良い。

#### 【0073】

なお、希ガスや窒素などの不活性ガス雰囲気中でレーザ光を照射するようにしても良い。20

#### 【0074】

上述したレーザ光の照射により、結晶性がより高められた半導体膜 503 が形成される。なお、予め半導体膜 503 に、スパッタ法、プラズマ CVD 法、熱 CVD 法などで形成した多結晶半導体を用いるようにしても良い。

#### 【0075】

また本実施の形態では半導体膜 503 を結晶化しているが、結晶化せずに非晶質珪素膜または微結晶半導体膜のまま、後述のプロセスに進んでも良い。非晶質半導体、微結晶半導体を用いた TFT は、多結晶半導体を用いた TFT よりも作製工程が少ない分、コストを抑え、歩留まりを高くすることができるというメリットを有している。30

#### 【0076】

非晶質半導体は、珪化物気体をグロー放電分解することにより得ることができる。代表的な珪化物気体としては、 $\text{SiH}_4$ 、 $\text{Si}_2\text{H}_6$  が挙げられる。この珪化物気体を、水素、水素とヘリウムで希釈して用いても良い。

#### 【0077】

なおセミアモルファス半導体とは、非晶質半導体と結晶構造を有する半導体（単結晶、多結晶を含む）の中間的な構造の半導体を含む膜である。このセミアモルファス半導体は、自由エネルギー的に安定な第 3 の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を  $0.5 \sim 20 \text{ nm}$  として非単結晶半導体中に分散させて存在せしめることが可能である。セミアモルファス半導体は、そのラマンスペクトルが  $520 \text{ cm}^{-1}$  よりも低波数側にシフトしており、また X 線回折では Si 結晶格子に由来するとされる (111)、(220) の回折ピークが観測される。また、未結合手（ダンギングボンド）の中和剤として水素またはハロゲンを少なくとも 1 原子% またはそれ以上含ませている。ここでは便宜上、このような半導体をセミアモルファス半導体 (SAS) と呼ぶ。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なセミアモルファス半導体が得られる。40

#### 【0078】

また SAS は珪化物気体をグロー放電分解することにより得ることができる。代表的な珪化物気体としては、 $\text{SiH}_4$  であり、その他にも  $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 50

、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ などを用いることができる。また水素や、水素にヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素を加えたガスで、この珪化物気体を希釈して用いることで、SASの形成を容易なものとすることができる。希釈率は2倍～1000倍の範囲で珪化物気体を希釈することが好ましい。またさらに、珪化物気体中に、 $\text{CH}_4$ 、 $\text{C}_2\text{H}_6$ などの炭化物気体、 $\text{GeH}_4$ 、 $\text{GeF}_4$ などのゲルマニウム化気体、 $\text{F}_2$ などを混入させて、エネルギー bandwidth幅を1.5～2.4 eV、若しくは0.9～1.1 eVに調節しても良い。

#### 【0079】

例えれば、 $\text{SiH}_4$ に $\text{H}_2$ を添加したガスを用いる場合、或いは $\text{SiH}_4$ に $\text{F}_2$ を添加したガスを用いる場合、形成したセミアモルファス半導体を用いてTFTを作製すると、該TFTのサブスレッシュルド係数(S値)を0.35 V/sec以下、代表的には0.25～0.09 V/secとし、移動度を $10 \text{ cm}^2/\text{V sec}$ とすることができる。そして上記セミアモルファス半導体を用いたTFTで、例えば19段リングオシレータを形成した場合、電源電圧3～5 Vにおいて、その発振周波数は1 MHz以上、好ましくは100 MHz以上の特性を得ることができる。また電源電圧3～5 Vにおいて、インバータ1段あたりの遅延時間は26 ns、好ましくは0.26 ns以下とすることができます。

#### 【0080】

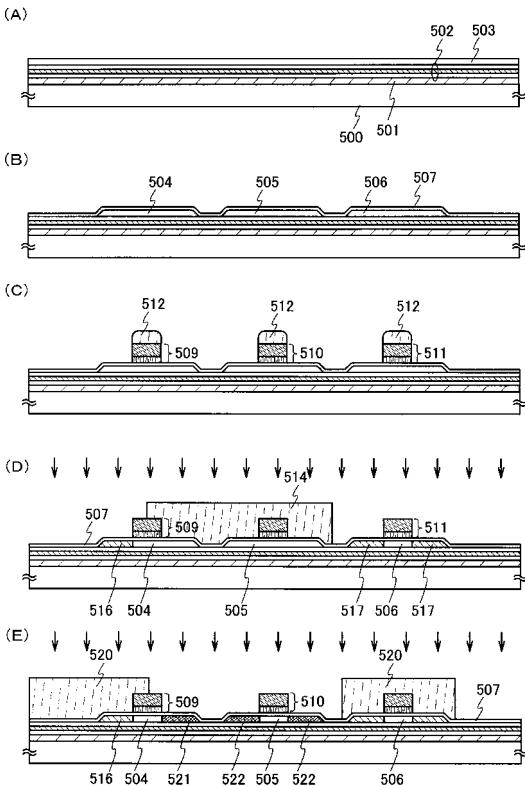

次に、図7(B)に示すように、結晶化された半導体膜503をパターニングし、島状の半導体膜504～506を形成する。そして、島状の半導体膜504～506を覆うように、ゲート絶縁膜507を形成する。ゲート絶縁膜507は、プラズマCVD法又はスパッタリング法などを用い、窒化珪素、酸化珪素、窒化酸化珪素又は酸化窒化珪素を含む膜を、単層で、又は積層させて形成することができる。積層する場合には、例えば、基板側から酸化珪素膜、窒化珪素膜、酸化珪素膜の3層構造とするのが好ましい。

#### 【0081】

次に図7(C)に示すように、ゲート電極509～511を形成する。本実施例では、n型を付与する不純物がドーピングされた珪素、WN、Wをスパッタ法で順に積層するように形成した後、マスク512をマスクとしてエッチングを行なうことにより、ゲート電極509～511を形成する。勿論、ゲート電極509～511の材料、構造、作製方法は、これに限定されるものではなく、適宜選択することができる。例えば、n型を付与する不純物がドーピングされた珪素と $\text{NiSi}$ (ニッケルシリサイド)との積層構造、n型を付与する不純物がドーピングされたSiと $\text{WSix}$ との積層構造、TaN(窒化タンタル)とW(タンゲステン)の積層構造としてもよい。また、種々の導電材料を用いて単層で形成しても良い。

#### 【0082】

また、レジストマスクの代わりに、酸化珪素等のマスクを用いてもよい。この場合、パターニングして酸化珪素、酸化窒化珪素等のマスク(ハードマスクと呼ばれる。)を形成する工程が加わるが、エッチング時におけるマスクの膜減りがレジストよりも少ないため、所望の幅のゲート電極509～511を形成することができる。また、マスク512を用いずに、液滴吐出法を用いて選択的にゲート電極509～511を形成しても良い。

#### 【0083】

導電材料としては、導電膜の機能に応じて種々の材料を選択することができる。また、ゲート電極とアンテナとを同時に形成する場合には、それらの機能を考慮して材料を選択すればよい。

#### 【0084】

なお、ゲート電極をエッチング形成する際のエッチングガスとしては、 $\text{CF}_4$ 、 $\text{Cl}_2$ 、 $\text{O}_2$ の混合ガスや $\text{Cl}_2$ ガスを用いたが、これに限定されるものではない。

#### 【0085】

次に図7(D)に示すように、マスク512を除去した後、pチャネル型TFTとなる島状の半導体膜505と、MOS容量素子となる島状の半導体膜504の一部をマスク514で覆い、さらにゲート電極509、511をマスクとして、島状の半導体膜504、

10

20

30

40

50

506に、n型を付与する不純物元素（代表的にはP（リン）又はAs（砒素））を低濃度にドープする（第1のドーピング工程）。第1のドーピング工程の条件は、ドーザ量： $1 \times 10^{13} \sim 6 \times 10^{13} / \text{cm}^2$ 、加速電圧：50～70keVとしたが、これに限定されるものではない。この第1のドーピング工程によって、ゲート絶縁膜507を介してドーピングがなされ、島状の半導体膜504に低濃度不純物領域516が、また島状の半導体膜506に、一対の低濃度不純物領域517がそれぞれ形成される。なお、第1のドーピング工程は、pチャネル型TFTとなる島状の半導体膜505と、MOS容量素子となる島状の半導体膜504の一部とを、マスク514で覆わずにあっても良い。

## 【0086】

次に図7(E)に示すように、マスク514をアッティング等により除去した後、pチャネル型TFTとなる島状の半導体膜506と、MOS容量素子となる島状の半導体膜504の低濃度不純物領域516とを覆うように、マスク520を新たに形成する。さらに、ゲート電極509、510をマスクとして用い、島状の半導体膜504、505に、p型を付与する不純物元素（代表的にはB（ホウ素））を高濃度にドープする（第2のドーピング工程）。第2のドーピング工程の条件は、ドーザ量： $1 \times 10^{16} \sim 3 \times 10^{16} / \text{cm}^2$ 、加速電圧：20～40keVとして行なう。この第2のドーピング工程によって、ゲート絶縁膜507を介してドーピングがなされ、島状の半導体膜504に、p型の高濃度不純物領域521が形成され、島状の半導体膜505に、一対のp型の高濃度不純物領域522が形成される。

## 【0087】

次に図8(A)に示すように、マスク520をアッティング等により除去した後、ゲート絶縁膜507及びゲート電極509～511を覆うように、絶縁膜530を形成する。本実施例では、膜厚100nmの酸化珪素膜をプラズマCVD法によって形成する。その後、エッチバック法により、絶縁膜530、ゲート絶縁膜507を部分的にエッティングし、図8(B)に示すように、ゲート電極509～511の側壁に接するように、サイドウォール531～533を自己整合的（セルフアライン）に形成する。エッティングガスとしては、CHF<sub>3</sub>とHeの混合ガスを用いる。なお、サイドウォールを形成する工程は、これらに限定されるものではない。

## 【0088】

なお、絶縁膜530を形成した時に、第1の基板500の裏面にも絶縁膜が形成された場合には、レジストを用い、裏面に形成された絶縁膜を選択的にエッティングし、除去するよりも良い。この場合、用いられるレジストは、サイドウォール531～533をエッチバック法で形成する際に、絶縁膜530、ゲート絶縁膜507と共にエッティングして、除去するよりも良い。

## 【0089】

次に図8(C)に示すように、pチャネル型TFTとなる島状の半導体膜505と、MOS容量素子となる島状の半導体膜504が有するp型の高濃度不純物領域521とを覆うように、マスク534を新たに形成する。さらに、ゲート電極509、511及びサイドウォール531、533をマスクとして用い、n型を付与する不純物元素（代表的にはP又はAs）を高濃度にドープする（第3のドーピング工程）。第3のドーピング工程の条件は、ドーザ量： $1 \times 10^{13} \sim 5 \times 10^{15} / \text{cm}^2$ 、加速電圧：60～100keVとして行なう。この第3のドーピング工程によって、島状の半導体膜504にn型の高濃度不純物領域536が、島状の半導体膜506に一対のn型の高濃度不純物領域537がそれぞれ形成される。

## 【0090】

なおサイドウォール531、533は、高濃度のn型を付与する不純物をドーピングし、サイドウォール531、533の下部に低濃度不純物領域（第3の不純物領域）又はノンドープのオフセット領域を形成する際のマスクとして機能するものである。よって、低濃度不純物領域又はオフセット領域の幅を制御するには、サイドウォール531、533を形成する際のエッチバック法の条件または絶縁膜530の膜厚を適宜変更し、サイドウォ

10

20

30

40

50

オール 531、533 のサイズを調整すればよい。

【0091】

次に、マスク 534 をアッティング等により除去した後、不純物領域の加熱処理による活性化を行っても良い。例えば、50nm の酸化窒化珪素膜を成膜した後、550、4 時間、窒素雰囲気下において、加熱処理を行なえばよい。

【0092】

また、水素を含む窒化珪素膜を、100nm の膜厚に形成した後、410、1 時間、窒素雰囲気下において、加熱処理を行ない、島状の半導体膜 504～506 を水素化する工程を行なっても良い。或いは、水素を含む雰囲気中で、300～450 で 1～12 時間の熱処理を行ない、島状の半導体膜 504～506 を水素化する工程を行なっても良い。

10 また、水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる）を行っても良い。この水素化の工程により、熱的に励起された水素によりダンギングボンドを終端することができる。また、後の工程において可撓性を有する第 2 の基板 559 上に半導体素子を貼り合わせた後、第 2 の基板 559 を曲げることにより半導体膜中に欠陥が形成されたとしても、水素化により半導体膜中の水素の濃度を、 $1 \times 10^{19} \sim 1 \times 10^{22} \text{ atoms/cm}^3$  好ましくは  $1 \times 10^{19} \sim 5 \times 10^{20} \text{ atoms/cm}^3$  とすることで、半導体膜に含まれている水素によって該欠陥を終端させることができる。また該欠陥を終端させるために、半導体膜中にハロゲンを含ませておいても良い。

【0093】

上述した一連の工程により、MOS 容量素子 540、p チャネル型 TFT541、n チャネル型 TFT542 が形成される。上記作製工程において、エッチバック法の条件または絶縁膜 530 の膜厚を適宜変更し、サイドウォールのサイズを調整することで、チャネル長 0.2 μm～2 μm の TFT を形成することができる。

20

【0094】

さらに、この後、MOS 容量素子 540、p チャネル型 TFT541、n チャネル型 TFT542 を保護するためのパッシベーション膜を形成しても良い。パッシベーション膜は、アルカリ金属やアルカリ土類金属の MOS 容量素子 540、p チャネル型 TFT541、n チャネル型 TFT542 への侵入を防ぐことができる、窒化珪素、窒化酸化珪素、窒化アルミニウム、酸化アルミニウム、酸化珪素などを用いるのが望ましい。具体的には、例えば膜厚 600nm 程度の酸化窒化珪素膜を、パッシベーション膜として用いることができる。この場合、水素化処理工程は、該酸化窒化珪素膜形成後に行っても良い。このように、MOS 容量素子 540、p チャネル型 TFT541、n チャネル型 TFT542 上には、酸化窒化珪素、窒化珪素、酸化窒化珪素の 3 層の絶縁膜が形成されることになるが、その構造や材料はこれらに限定されるものではない。上記構成を用いることで、MOS 容量素子 540、p チャネル型 TFT541、n チャネル型 TFT542 が下地膜 502 とパッシベーション膜とで覆われるため、Na などのアルカリ金属やアルカリ土類金属が、半導体素子に用いられている半導体膜中に拡散し、半導体素子の特性に悪影響を及ぼすのをより防ぐことができる。

30

【0095】

次に図 8 (D) に示すように、MOS 容量素子 540、p チャネル型 TFT541、n チャネル型 TFT542 を覆うように、第 1 の層間絶縁膜 543 を形成する。第 1 の層間絶縁膜 543 は、ポリイミド、アクリル、ポリアミド等の、耐熱性を有する有機樹脂を用いることができる。また上記有機樹脂の他に、低誘電率材料 (low-k 材料)、シリコン系樹脂等を用いることができる。第 1 の層間絶縁膜 543 の形成には、その材料に応じて、スピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を採用することができる。また、無機材料を用いてもよく、その際には、酸化珪素、窒化珪素、酸窒化珪素、PSG (リンガラス)、BPSG (リンボロンガラス)、アルミナ膜等を用いることができる。なお、これらの絶縁膜を積層させて、第 1 の層間絶縁膜 543 を形成しても良い。

40

50

## 【0096】

さらに本実施例では、第1の層間絶縁膜543上に、第2の層間絶縁膜544を形成する。第2の層間絶縁膜544としては、DLC(ダイヤモンドライカーボン)或いは窒化炭素(CN)等の炭素を有する膜、又は、酸化珪素膜、窒化珪素膜或いは窒化酸化珪素膜等を用いることができる。作製方法としては、プラズマCVD法や、大気圧プラズマ等を用いることができる。あるいは、ポリイミド、アクリル、ポリアミド、レジスト又はベンゾシクロブテン等の感光性又は非感光性の有機材料や、シロキサン系樹脂等を用いてもよい。

## 【0097】

なお、第1の層間絶縁膜543又は第2の層間絶縁膜544と、後に形成される配線を構成する導電材料等との熱膨張率の差から生じる応力によって、第1の層間絶縁膜543又は第2の層間絶縁膜544の膜剥がれや割れが生じるのを防ぐために、第1の層間絶縁膜543又は第2の層間絶縁膜544中にフィラーを混入させておいても良い。

10

## 【0098】

次に、第1の層間絶縁膜543及び第2の層間絶縁膜544にコンタクトホールを形成し、MOS容量素子540、pチャネル型TFT541、nチャネル型TFT542に接続する配線545～550を形成する。コンタクトホール開孔時のエッチングに用いられるガスは、CHF<sub>3</sub>とHeの混合ガスを用いたが、これに限定されるものではない。本実施例では、配線545～550を、Alで形成する。なお配線545～550をTi、TiN、Al-Si、Ti、TiNの5層構造とし、スパッタ法を用いて形成しても良い。

20

## 【0099】

なお、Alにおいて、Siを混入させることにより、配線パターニング時のレジストベークにおけるヒロックの発生を防止することができる。また、Siの代わりに、0.5%程度のCuを混入させても良い。また、TiやTiNでAl-Si層をサンドイッチすることにより、耐ヒロック性がさらに向上する。なお、パターニング時には、酸化窒化珪素等からなる上記ハードマスクを用いるのが望ましい。なお、配線の材料や、作製方法はこれらに限定されるものではなく、前述したゲート電極に用いられる材料を採用しても良い。

## 【0100】

なお、配線545は、MOS容量素子540の高濃度不純物領域536に、配線546は、MOS容量素子540の高濃度不純物領域521に、接続されている。配線547、548は、pチャネル型TFT541の高濃度不純物領域522に接続されている。配線549、550は、nチャネル型TFT542の高濃度不純物領域537に接続されている。

30

## 【0101】

次に図8(E)に示すように、配線545～550を覆うように、第2の層間絶縁膜544上に第3の層間絶縁膜552を形成する。第3の層間絶縁膜552は、配線545の一部が露出するような開口部を有する。また第3の層間絶縁膜552は、有機樹脂膜、無機絶縁膜またはシロキサン系絶縁膜を用いて形成することができる。有機樹脂膜ならば、例えばアクリル、ポリイミド、ポリアミドなど、無機絶縁膜ならば酸化珪素、窒化酸化珪素などを用いることができる。なおフォトリソグラフィ法で開口部を形成するのに用いるマスクを、液滴吐出法または印刷法で形成することができる。また第3の層間絶縁膜552自体を、液滴吐出法または印刷法で形成することもできる。

40

## 【0102】

次に、アンテナ553を第3の層間絶縁膜552上に形成する。アンテナ553は、Ag、Au、Cu、Pd、Cr、Mo、Ti、Ta、W、Al、Fe、Co、Zn、Sn、Niなどの金属、金属化合物を1つまたは複数有する導電材料を用いることができる。そしてアンテナ553は、配線545と接続されている。なお図8(E)では、アンテナ553が配線545と直接接続されているが、本発明のIDチップはこの構成に限定されない。例えば別途形成した配線を用いて、アンテナ553と配線545とを電気的に接続す

50

るようにもても良い。

#### 【0103】

アンテナ553は印刷法、フォトリソグラフィ法、めっき法、蒸着法または液滴吐出法などを用いて形成することができる。本実施例では、アンテナ553が単層の導電膜で形成されているが、複数の導電膜が積層されたアンテナ553を形成することも可能である。

#### 【0104】

印刷法、液滴吐出法を用いることで、露光用のマスクを用いずとも、アンテナ553を形成することが可能になる。また、液滴吐出法、印刷法だと、フォトリソグラフィ法と異なり、エッティングにより除去されてしまうような材料の無駄がない。また高価な露光用のマスクを用いなくとも良いので、IDチップの作製に費やされるコストを抑えることができる。

10

#### 【0105】

液滴吐出法または各種印刷法を用いる場合、例えば、CuをAgでコートした導電粒子なども用いることが可能である。なお液滴吐出法を用いてアンテナ553を形成する場合、該アンテナ553の密着性が高まるような処理を、第3の層間絶縁膜552の表面に施すことが望ましい。

#### 【0106】

密着性を高めるための処理として、具体的には、例えば触媒作用により導電膜または絶縁膜の密着性を高めることができる金属または金属化合物を第3の層間絶縁膜552の表面に付着させる方法、形成される導電膜または絶縁膜との密着性が高い有機系の絶縁膜、金属、金属化合物を第3の層間絶縁膜552の表面に付着させる方法、第3の層間絶縁膜552の表面に大気圧下または減圧下においてプラズマ処理を施し、表面改質を行なう方法などが挙げられる。また、上記導電膜または絶縁膜との密着性が高い金属として、チタン、チタン酸化物の他、3d遷移元素であるSc、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Znなどが挙げられる。また金属化合物として、上述した金属の酸化物、窒化物、酸窒化物などが挙げられる。上記有機系の絶縁膜として、例えばポリイミド、シリコサン系樹脂等が挙げられる。

20

#### 【0107】

第3の層間絶縁膜552に付着させる金属または金属化合物が導電性を有する場合、アンテナ553の正常な動作が妨げられないように、そのシート抵抗を制御する。具体的には、導電性を有する金属または金属化合物の平均の厚さを、例えば1~10nmとなるように制御したり、該金属または金属化合物を酸化により部分的に、または全体的に絶縁化したりすれば良い。或いは、密着性を高めたい領域以外は、付着した金属または金属化合物をエッティングにより選択的に除去しても良い。また金属または金属化合物を、予め基板の全面に付着させるのではなく、液滴吐出法、印刷法、ゾル-ゲル法などを用いて特定の領域にのみ選択的に付着させても良い。なお金属または金属化合物は、第3の層間絶縁膜552の表面において完全に連続した膜状である必要はなく、ある程度分散した状態であつても良い。

30

#### 【0108】

次に図9(A)に示すように、アンテナ553を覆うように、第3の層間絶縁膜552上に保護層556を形成する。保護層556は、後に剥離層501をエッティングにより除去する際に、MOS容量素子540、pチャネル型TFT541、nチャネル型TFT542及び配線545~550を保護することができる材料を用いる。例えば、水またはアルコール類に可溶なエポキシ系、アクリレート系、シリコン系の樹脂を全面に塗布することで保護層556を形成することができる。

40

#### 【0109】

本実施例では、スピンコート法で水溶性樹脂(東亜合成製:VL-WSHL10)を膜厚30μmとなるように塗布し、仮硬化させるために2分間の露光を行ったあと、紫外線を裏面から2.5分、表面から10分、合計12.5分の露光を行って本硬化させて、保

50

護層 556 を形成する。なお、複数の有機樹脂を積層する場合、有機樹脂同士では使用している溶媒によって塗布または焼成時に一部溶解したり、密着性が高くなりすぎたりする恐れがある。従って、第3の層間絶縁膜 552 と保護層 556 を共に同じ溶媒に可溶な有機樹脂を用いる場合、後の工程において保護層 556 の除去がスムーズに行なわれるよう 10 に、第3の層間絶縁膜 552 を覆うように、無機絶縁膜（窒化珪素膜、窒化酸化珪素膜、 $\text{AlN}_x$ 膜、または $\text{AlN}_x\text{O}_y$ 膜）を形成しておくことが好ましい。

#### 【0110】

次に図9(B)に示すように、IDチップどうしを分離するために溝 555 を形成する。溝 555 は、剥離層 501 が露出する程度の深さを有していれば良い。溝 555 の形成は、ダイシング、スクライビング、フォトリソグラフィ法などを用いることができる。なお、第1の基板 500 上に形成されているIDチップを分離する必要がない場合、必ずしも溝 555 を形成する必要はない。

#### 【0111】

次に図9(C)に示すように、剥離層 501 をエッティングにより除去する。本実施例では、エッティングガスとしてハロゲン化フッ素を用い、該ガスを溝 555 から導入する。本実施例では、例えば $\text{ClF}_3$ （三フッ化塩素）を用い、温度：350℃、流量：300sccm、気圧：799.8 Pa (6 Torr)、時間：3 h の条件で行なう。また、 $\text{ClF}_3$ ガスに窒素を混ぜたガスを用いても良い。 $\text{ClF}_3$ 等のハロゲン化フッ素を用いることで、剥離層 501 が選択的にエッティングされ、第1の基板 500 をMOS容量素子 540 20 、pチャネル型 TFT 541、nチャネル型 TFT 542 から剥離することができる。なおハロゲン化フッ素は、気体であっても液体であってもどちらでも良い。

#### 【0112】

次に図10(A)に示すように、剥離されたMOS容量素子 540、pチャネル型 TFT 541、nチャネル型 TFT 542 を、接着剤 558 を用いて第2の基板 559 に貼り合わせ、保護層 556 を除去する。接着剤 558 は、第2の基板 559 と下地膜 502 とを貼り合わせることができる材料を用いる。接着剤 558 は、例えば反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。

#### 【0113】

第2の基板 559 として、例えばバリウムホウケイ酸ガラスや、アルミニノホウケイ酸ガラスなどのガラス基板、可撓性を有する紙またはプラスチックなどの有機材料を用いることができる。または第2の基板 559 として、フレキシブルな無機材料を用いていても良い。プラスチック基板は、極性基のついたポリノルボルネンからなるARTON (JSR 製) を用いることができる。また、ポリエチレンテレフタレート (PET) に代表されるポリエステル、ポリエーテルスルホン (PES)、ポリエチレンナフタレート (PEN)、ポリカーボネート (PC)、ナイロン、ポリエーテルエーテルケトン (PEEK)、ポリスルホン (PSF)、ポリエーテルイミド (PEI)、ポリアリレート (PAR)、ポリブチレンテレフタレート (PBT)、ポリイミド、アクリロニトリルブタジエンスチレン樹脂、ポリ塩化ビニル、ポリプロピレン、ポリ酢酸ビニル、アクリル樹脂などが挙げられる。第2の基板 559 は集積回路において発生した熱を拡散させるために、2~30W/mK 程度の高い熱伝導率を有する方が望ましい。

#### 【0114】

次に図10(B)に示すように、接着剤 560 をアンテナ 553 及び第3の層間絶縁膜 552 上に塗布し、カバー材 561 を貼り合わせる。カバー材 561 は第2の基板 559 と同様の材料を用いることができる。接着剤 560 の厚さは、例えば 10~200 μm とすれば良い。

#### 【0115】

また接着剤 560 は、カバー材 561 とアンテナ 553 及び第3の層間絶縁膜 552 とを貼り合わせることができる材料を用いる。接着剤 560 は、例えば反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化 50

型接着剤を用いることができる。

【0116】

なお本実施例では、接着剤560を用いて、カバー材561をアンテナ553及び第3の層間絶縁膜552に貼り合わせているが、本発明はこの構成に限定されず、IDチップは必ずしもカバー材561を用いる必要はない。例えば、アンテナ553及び第3の層間絶縁膜552を樹脂等で覆うことで、IDチップの機械的強度を高めるようにも良い。或いはカバー材561を用いずに、図10(A)に示した工程までで終了としても良い。

【0117】

上述した各工程を経て、IDチップが完成する。上記作製方法によって、トータルの膜厚0.3μm以上3μm以下、代表的には2μm程度の飛躍的に薄い集積回路を第2の基板559とカバー材561との間に形成することができる。なお集積回路の厚さは、半導体素子自体の厚さのみならず、接着剤558と接着剤560間に形成された各種絶縁膜及び層間絶縁膜の厚さを含め、アンテナは含まないものとする。またIDチップが有する集積回路の占める面積を、5mm四方(25mm<sup>2</sup>)以下、より望ましくは0.3mm四方(0.09mm<sup>2</sup>)~4mm四方(16mm<sup>2</sup>)程度とすることができる。

【0118】

なお集積回路を、第2の基板559とカバー材561の間のより中央に位置させることで、IDチップの機械的強度を高めることができる。具体的には、第2の基板559とカバー材561の間の距離をdとすると、集積回路の厚さ方向における中心と第2の基板559との間の距離xが、以下の数1に示す式を満たすように、接着剤558、接着剤560の厚さを制御することが望ましい。

【0119】

【数1】

$$\frac{1}{2}d - 30\mu m < x < \frac{1}{2}d + 30\mu m$$

【0120】

また好ましくは、以下の数2に示す式を満たすように、接着剤558、接着剤560の厚さを制御する。

【0121】

【数2】

$$\frac{1}{2}d - 10\mu m < x < \frac{1}{2}d + 10\mu m$$

【0122】

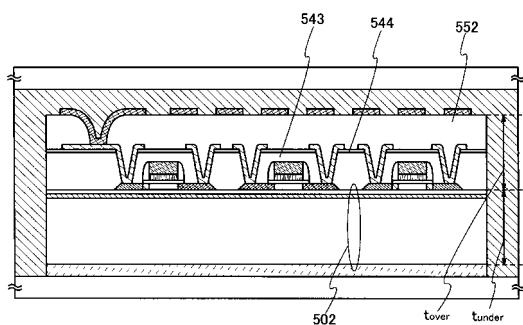

また、図11に示すように、集積回路におけるTFTの島状の半導体膜から下地膜502の下部までの距離(t<sub>under</sub>)と、島状の半導体膜から第3の層間絶縁膜552の上部までの距離(t<sub>over</sub>)が、等しく又は概略等しくなるように、下地膜502、第1の層間絶縁膜543、第2の層間絶縁膜544または第3の層間絶縁膜552の厚さを調整しても良い。このようにして、島状の半導体膜を集積回路の中央に配置せしめることで、半導体層への応力を緩和することができ、クラックの発生を防止することができる。

【0123】

またIDチップの可撓性を確保するために、下地膜502に接する接着剤558に有機樹脂を用いる場合、下地膜502として窒化珪素膜または窒化酸化珪素膜を用いることでも、有機樹脂からNaなどのアルカリ金属やアルカリ土類金属が半導体膜中に拡散するのを防ぐことができる。

【0124】

10

20

30

40

50

また対象物の表面が曲面を有しており、それにより該曲面貼り合わされたIDチップの第2の基板559が、錐面、柱面など母線の移動によって描かれる曲面を有するよう曲がってしまう場合、該母線の方向とMOS容量素子540、pチャネル型TFT541、nチャネル型TFT542のキャリアが移動する方向とを揃えておくことが望ましい。上記構成により、第2の基板559が曲がっても、それによってMOS容量素子540、pチャネル型TFT541、nチャネル型TFT542の特性に影響が出るのを抑えることができる。また、島状の半導体膜が集積回路内において占める面積の割合を、1~30%とすることで、第2の基板559が曲がっても、それによってMOS容量素子540、pチャネル型TFT541、nチャネル型TFT542の特性に影響が出るのをより抑えることができる。

10

#### 【0125】

なお一般的にIDチップで用いられている電波の周波数は、13.56MHz、2.45GHzが多く、該周波数の電波を検波できるようにIDチップを形成することが、汎用性を高める上で非常に重要である。

#### 【0126】

また本実施例のIDチップでは、半導体基板を用いて形成されたIDチップよりも電波が遮蔽されにくく、電波の遮蔽により信号が減衰するのを防ぐことができるというメリットを有している。よって、半導体基板を用いずに済むので、IDチップのコストを大幅に低くすることができる。例えば、直径12インチの半導体基板を用いた場合と、 $730 \times 920 \text{ mm}^2$ のガラス基板を用いた場合とを比較する。前者の半導体基板の面積は約 $730000 \text{ mm}^2$ であるが、後者のガラス基板の面積は約 $672000 \text{ mm}^2$ であり、ガラス基板は半導体基板の約9.2倍に相当する。後者のガラス基板の面積は約 $672000 \text{ mm}^2$ では、基板の分断により消費される面積を無視すると、1mm四方のIDチップが約672000個形成できる計算になり、該個数は半導体基板の約9.2倍の数に相当する。そしてIDチップの量産化を行なうための設備投資は、 $730 \times 920 \text{ mm}^2$ のガラス基板を用いた場合の方が直径12インチの半導体基板を用いた場合よりも工程数が少なくて済むため、額を3分の1で済ませることができる。さらに本発明では、集積回路を剥離した後、ガラス基板を再び利用できる。よって、破損したガラス基板を補填したり、ガラス基板の表面を清浄化したりする費用を踏まえても、半導体基板を用いる場合より大幅にコストを抑えることができる。またガラス基板を再利用せずに廃棄していったとしても、 $730 \times 920 \text{ mm}^2$ のガラス基板の値段は、直径12インチの半導体基板の半分程度で済むので、IDチップのコストを大幅に低くすることができることがわかる。

20

#### 【0127】

従って、 $730 \times 920 \text{ mm}^2$ のガラス基板を用いた場合、直径12インチの半導体基板を用いた場合よりも、IDチップの値段を約30分の1程度に抑えることができることがわかる。IDチップは、使い捨てを前提とした用途も期待されているので、コストを大幅に低くすることができる本発明のIDチップは上記用途に非常に有用である。

30

#### 【0128】

本実施例は、実施例1、2と組み合わせて実施することが可能である。

#### 【実施例4】

40

#### 【0129】

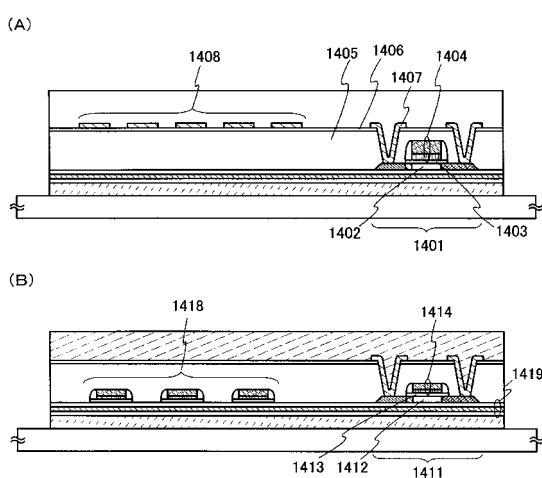

図12(A)を用いて、導電膜のパターニングにより、MOS容量素子に接続されている配線とアンテナとを共に形成する場合の、半導体装置の構成について説明する。図12(A)に、本実施例の半導体装置の断面図を示す。

#### 【0130】

図12(A)において、MOS容量素子1401は、島状の半導体膜1402と、島状の半導体膜1402に接しているゲート絶縁膜1403と、ゲート絶縁膜1403を間に挟んで島状の半導体膜1402と重なっているゲート電極1404とを有している。

#### 【0131】

またMOS容量素子1401は、第1の層間絶縁膜1405及び第2の層間絶縁膜14

50

06に覆われている。なお、本実施例では、MOS容量素子1401が、第1の層間絶縁膜1405、第2の層間絶縁膜1406の、2つの層間絶縁膜に覆われているが、本実施例はこの構成に限定されない。MOS容量素子1401は、単層の層間絶縁膜で覆われても良いし、3層以上の層間絶縁膜で覆われても良い。

#### 【0132】

そして第2の層間絶縁膜1406上に形成された配線1407は、第1の層間絶縁膜1405及び第2の層間絶縁膜1406に形成されたコンタクトホールを介して、島状の半導体膜1402に接続されている。

#### 【0133】

また第2の層間絶縁膜1406上には、アンテナ1408が形成されている。配線1407とアンテナ1408は、第2の層間絶縁膜1406上に導電膜を形成し、該導電膜をパターニングすることで、共に形成することができる。アンテナ1408を配線1407と共に形成することで、半導体装置の作製工程数を抑えることができる。10

#### 【0134】

次に図12(B)を用いて、導電膜のパターニングにより、MOS容量素子のゲート電極とアンテナとを共に形成する場合の、半導体装置の構成について説明する。図12(B)に、本実施例の半導体装置の断面図を示す。

#### 【0135】

図12(B)において、MOS容量素子1411は、島状の半導体膜1412と、島状の半導体膜1412に接しているゲート絶縁膜1413と、ゲート絶縁膜1413を間に挟んで島状の半導体膜1412と重なっているゲート電極1414とを有している。20

#### 【0136】

また下地膜1419上には、アンテナ1418が形成されている。ゲート電極1414とアンテナ1418は、ゲート絶縁膜1413上に導電膜を形成し、該導電膜をパターニングすることで共に形成することができる。アンテナ1418をゲート電極1414と共に形成することで、半導体装置の作製工程数を抑えることができる。

#### 【0137】

なお本実施例では、集積回路を剥離して、別途用意した基板に貼り合わせる例について説明したが、本発明はこの構成に限定されない。例えばガラス基板のように、集積回路の作製工程における熱処理に耐えうるような、耐熱温度を有している基板を用いる場合、必ずしも集積回路を剥離する必要はない。30

#### 【実施例5】

#### 【0138】

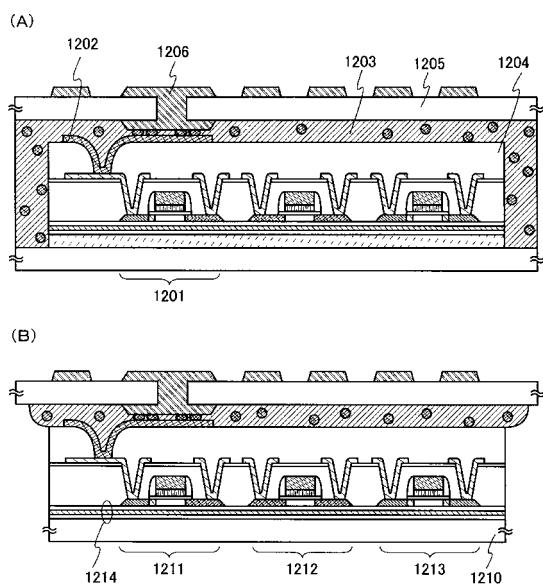

本実施例では、別の基板上に形成したアンテナと集積回路とを電気的に接続する、半導体装置の構成について説明する。

#### 【0139】

図13(A)に、本実施例の半導体装置の断面図を示す。図13(A)では、MOS容量素子1201に電気的に接続された配線1202を覆うように、接着剤1203が第3の層間絶縁膜1204上に塗布されている。そして、接着剤1203により、カバー材1205が第3の層間絶縁膜1204に貼り合わされている。40

#### 【0140】

カバー材1205には、アンテナ1206が予め形成されている。そして本実施例では、接着剤1203に異方導電性樹脂を用いることで、アンテナ1206と配線1202とが電気的に接続されている。

#### 【0141】

異方導電性樹脂は、樹脂中に導電材料を分散させた材料である。樹脂として、例えばエポキシ系、ウレタン系、アクリル系などの熱硬化性を有するもの、ポリエチレン系、ポリプロピレン系などの熱可塑性を有するもの、シロキサン系樹脂などを用いることができる。また導電材料として、例えばポリスチレン、エポキシなどのプラスチック製の粒子にNi、Auなどをめっきしたもの、Ni、Au、Ag、はんだなどの金属粒子、粒子状また50

は纖維状のカーボン、纖維状のNiにAuをめっきしたものなどを用いることができる。導電材料のサイズは、アンテナ1206と配線1202のピッチに合わせて決めることが望ましい。

#### 【0142】

またアンテナ1206と配線1202の間において、異方導電性樹脂に超音波を加えながら圧着させても良いし、紫外線の照射で硬化させながら圧着させても良い。

#### 【0143】

なお本実施例では、異方導電性樹脂を用いた接着剤1203でアンテナ1206と配線1202とを電気的に接続する例を示しているが、本発明はこの構成に限定されない。接着剤1203の代わりに、異方導電性フィルムを用い、該異方導電性フィルムを圧着することで、アンテナ1206と配線1202とを電気的に接続しても良い。10

#### 【0144】

また本実施例では、剥離された集積回路を、別途用意した基板に貼り合わせることで形成された半導体装置を、例に挙げて説明したが、本発明はこの構成に限定されない。例えばガラス基板のように、集積回路の作製工程における熱処理に耐えうるような、耐熱温度を有している基板を用いる場合、必ずしも集積回路を剥離する必要はない。図13(B)に、ガラス基板を用いて形成された、半導体装置の一形態を、断面図で示す。

#### 【0145】

図13(B)に示す半導体装置では、基板1210としてガラス基板を用いており、集積回路に用いられるMOS容量素子1211、TFT1212、1213と基板1210との間に、接着剤を間に挟まずに、下地膜1214が接するように形成されている。20

#### 【実施例6】

#### 【0146】

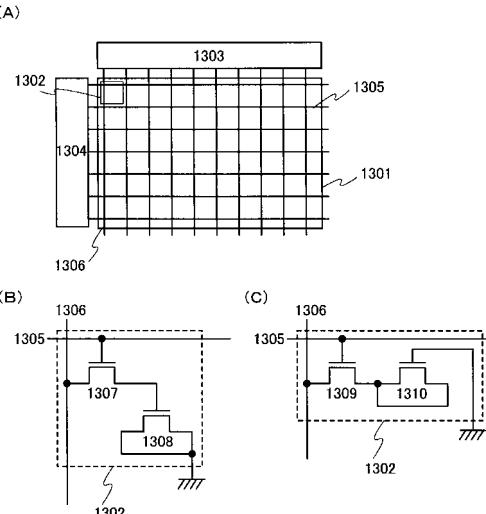

本発明のMOS容量素子は無極性であるので、交流の電圧を印加する回路のみならず、直流の電圧を印加する回路にも用いることができる。本実施例では、本発明のMOS容量素子をDRAMに用いる例について説明する。

#### 【0147】

図14(A)に、DRAMの一例をブロック図で示す。1301はセルアレイ、1303は列デコーダ、1304は行デコーダに相当する。セルアレイ1301には複数のメモリセル1302がマトリクス状に設けられている。またセルアレイ1301には、ワード線1305、ビット線1306が設けられている。30

#### 【0148】

行デコーダ1304は、ワード線1305に印加する電圧を制御することで、メモリセル1302を含む行を選択することができる。また列デコーダ1303は、ビット線1306を介して、メモリセル1302を選択し、データの書き込み、読み出しを制御することができる。

#### 【0149】

図14(B)に、メモリセル1302の具体的な回路図の一例を示す。1307はスイッチング素子として機能するトランジスタ、1308は本発明のMOS容量素子に相当する。トランジスタ1307のゲート電極はワード線1305に接続されている。またトランジスタ1307のソース領域またはドレイン領域は、一方がビット線1306に、他方がMOS容量素子1308のゲート電極に接続されている。MOS容量素子1308のソース領域及びドレイン領域には、グラウンド(GND)などの一定の電圧が供給されている。40

#### 【0150】

図14(C)に、メモリセル1302の具体的な回路図の、図14(B)とは異なる一例を示す。1309はスイッチング素子として機能するトランジスタ、1310は本発明のMOS容量素子に相当する。トランジスタ1309のゲート電極はワード線1305に接続されている。またトランジスタ1309のソース領域またはドレイン領域は、一方がワード線1306に、他方がMOS容量素子1310のソース領域及びドレイン領域に接50

続されている。MOS容量素子1310のゲート電極には、グラウンド(GND)などの一定の電圧が供給されている。

#### 【0151】

なお本発明のMOS容量素子は、DRAMのみならず、その他の集積回路にも用いることができる。

#### 【0152】

本実施例は、実施例1～実施例5と組み合わせて用いることができる。

#### 【実施例7】

#### 【0153】

次に、上述したMOS容量素子を集積回路または共振回路に用いている、本発明の半導体装置の一例について説明する。

#### 【0154】

図16(A)に、本発明の半導体装置の一つであるIDチップの一形態を、斜視図で示す。1601は集積回路、1602はアンテナに相当し、アンテナ1602は集積回路1601に接続されている。1603は基板、1604はカバー材に相当する。集積回路1601及びアンテナ1602は、基板1603上に形成されており、カバー材1604は集積回路1601及びアンテナ1602を覆うように基板1603と重なっている。なおカバー材1604は必ずしも用いる必要はないが、集積回路1601及びアンテナ1602をカバー材1604で覆うことで、IDチップの機械的強度を高めることができる。本発明により、集積回路1601またはアンテナ1602を有する共振回路を作製して、IDチップを完成させることができる。本発明のMOS容量素子は、作製工程数を抑えつつ、面積あたりの容量値が高いMOS容量素子を形成することができるので、本発明のIDチップのコストを抑えることができる。

#### 【0155】

図16(B)に、本発明の半導体装置の一つであるICカードの一形態を、斜視図で示す。1605は集積回路、1606はアンテナに相当し、アンテナ1606は集積回路1605に接続されている。1608はインレットシートとして機能する基板、1607、1609はカバー材に相当する。集積回路1605及びアンテナ1606は基板1608上に形成されており、基板1608は2つのカバー材1607、1609の間に挟まれている。なお本発明のICカードは、集積回路1605に接続された表示装置を有していても良い。本発明により、集積回路1605またはアンテナ1606を有する共振回路を作製して、ICカードを完成させることができる。本発明のMOS容量素子は、作製工程数を抑えつつ、面積あたりの容量値が高いMOS容量素子を形成することができるので、本発明のICカードのコストを抑えることができる。

#### 【図面の簡単な説明】

#### 【0156】

【図1】本発明のMOS容量素子の断面を模式的に表した図。

【図2】本発明のMOS容量素子の上面図及び断面図。

【図3】本発明のMOS容量素子の上面図及び断面図。

【図4】本発明のMOS容量素子の断面図。

【図5】本発明のMOS容量素子を用いた液晶表示装置の構成を示す図。

【図6】本発明のMOS容量素子を用いたICチップまたはIDチップの、機能的な構成のブロック図。

【図7】本発明の半導体装置の作製方法を示す図。

【図8】本発明の半導体装置の作製方法を示す図。

【図9】本発明の半導体装置の作製方法を示す図。

【図10】本発明の半導体装置の作製方法を示す図。

【図11】本発明の半導体装置の作製方法を示す図。

【図12】本発明の半導体装置の断面図。

【図13】本発明の半導体装置の断面図。

10

20

30

40

50

【図14】本発明のMOS容量素子を用いたDRAMの構成を示す図。

【図15】本発明のMOS容量素子を用いた液晶表示装置の上面図及び断面図。

【図16】本発明のMOS容量素子を用いた半導体装置の図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(51)Int.Cl. F I

H 01L 27/06 (2006.01)

H 01L 21/336 (2006.01)

(56)参考文献 特開2000-138346 (JP, A)

特開2000-223722 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01L 29/786

G 02F 1/1368

H 01L 21/336

H 01L 21/822

H 01L 21/8234

H 01L 27/04

H 01L 27/06