US 20130220396A1

# (19) United States(12) Patent Application Publication

### Janssen et al.

#### (54) PHOTOVOLTAIC DEVICE AND MODULE WITH IMPROVED PASSIVATION AND A METHOD OF MANUFACTURING

- (75) Inventors: Lars Janssen, Heerlen (NL); Jonas Koopmann, Heerlen (NL); Menno Nicolaas Van Den Donker, Heerlen (NL); Franciscus Theodorus Agricola, Heerlen (NL)

- (73) Assignee: ENERGY RESEARCH CENTRE OF THE NETHERLANDS, Petten (NL)

- (21) Appl. No.: 13/818,476

- (22) PCT Filed: Aug. 24, 2011

- (86) PCT No.: PCT/NL2011/000060

§ 371 (c)(1), (2), (4) Date: May 7, 2013

#### (30) Foreign Application Priority Data

| Aug. 24, 2010 | (NL) | <br>2005261           |

|---------------|------|-----------------------|

| Aug. 24, 2011 | (NL) | <br>PCT/NL2011/000060 |

## (10) Pub. No.: US 2013/0220396 A1 (43) Pub. Date: Aug. 29, 2013

#### **Publication Classification**

#### (57) **ABSTRACT**

A photovoltaic device, having an improved passivation of surfaces, such as a circumferential outer wall and/or an aperture wall of a back contact metal wrap-through photovoltaic device, for example, into which the pn-junction of first and second semiconductor layers extends. The passivation comprises a passivating layer of a first type, covering at least part of such wall substantially comprised by the depletion region across the pn-junction; a passivating layer of a second type, covering at least part of such wall comprised by the first semiconductor layer, and a passivating layer of a third type covering at least part of the outer wall comprised by the second semiconductor layer.

Fig. 3

Fig. 4

Fig. 5

Fig. 6

Fig. 7

Fig. 8

Fig. 9

Fig. 10

Fig. 11

#### PHOTOVOLTAIC DEVICE AND MODULE WITH IMPROVED PASSIVATION AND A METHOD OF MANUFACTURING

#### TECHNICAL FIELD

**[0001]** The present invention relates to photovoltaic devices and, in particular, to back or rear contact device concepts using the so-called metal wrap-through technology.

#### BACKGROUND

**[0002]** Photovoltaic devices or solar cells convert optical energy, such as solar radiation, into electrical energy. These devices are essentially composed of a layered structure, having a front surface for receiving optical radiation and a back or rear surface opposite to the front surface. The layered structure typically includes a first semiconductor layer of a first conductivity type and a second semiconductor layer of a second conductivity type extending contiguous to the first layer. The first and second conductivity types being of opposite polarity such that the first and second layers are separated by a pn-junction or depletion layer, also called active layer.

**[0003]** The first layer, extending adjacent to the front surface, connects to at least one electrical contact at the front surface of the layered structure, also called front contact or front electrode. The second layer connects to at least one electrical contact at the back or rear surface of the layered structure, also called rear or back contact or rear or back electrode.

**[0004]** Photons contained in solar radiation, for example, impinging the front surface of the photovoltaic device create electron-hole pairs in the device. These charge carriers get separated as a result of a voltage difference across the pn-junction, which voltage difference is available at the front and rear contacts. By connecting an electric load between the front and rear contacts, an electric current will flow through this load.

**[0005]** A single solar cell produces a relative small amount of electric energy with a relative low voltage difference between the front and rear contacts. For practical use, several solar cells have to be series connected to obtain a solar module having a higher output voltage and/or several series connected cells have to be parallel connected to obtain a solar module providing a higher output current. As cells become larger and more efficient, the output current increases and in order to limit resistive losses within this wiring, the dimensions thereof across the front surface increase. In practical photovoltaic devices and modules, among others, the electrical wiring at the front surface, in the form of bus bars or the like, contributes proportionally to shadowing losses.

**[0006]** With the Metal Wrap-Through, MWT, technology small apertures or vias are provided in the layered structure and extending from the front surface to the rear surface. At the back or rear surface of the layered structure a back or rear contact arrangement or back or rear contact grids are provided. By metallizing the apertures, i.e. by filling the apertures with an electrically conductive plug, an electrical contact path is provided connecting a front contact, or a plurality of front contacts of the solar cells, to the back contact arrangement

**[0007]** It will be appreciated that the back contact arrangement can be designed with appropriate dimensions to reduce electrical losses in the contact wiring of the solar module

without impeding the effective amount of radiation at the front surface contributing to the energy conversion.

**[0008]** To increase the effective amount of radiation at the front surface for conversion into electrical energy, light trapping schemes such as surface texturing are introduced. That is, the front surface for collecting solar radiation is effectively increased by a suitable surface treatment and/or provided with a suitable anti-reflective coating. Making the back surface reflective or diffuse reflected or scattered towards the front again, which provides additional opportunities to produce electron-hole pairs in the photovoltaic device, i.e. increased generation of electrical energy.

**[0009]** Among others, a significant loss effect known in semiconductor devices is recombination of charge carriers at the surface of a semiconductor layer. In order to prevent the surface recombination of electrons and holes, passivating layers or films are applied at the outer surfaces of a photovoltaic device. In the area of photovoltaics, a passivating surface layer reduces surface recombination by generating an electric surface field of opposite polarity at the surface of a particular semiconductor layer.

**[0010]** The first and second semiconductor layers as well as the pn-junction or depletion region formed there between may extend into the circumferential outer wall of the layered structure. Further, in a metal wrap-through cell, the first and second semiconductor layers as well as the pn-junction or depletion region formed there between extend into the aperture walls of the several apertures produced in the layered structure. Accordingly, passivation should not be restricted to the front and back surface of the layered structure but should be applied also at the outer circumferential wall and, in the case of a back contact metal wrap-through photovoltaic cell, within the apertures.

#### SUMMARY

**[0011]** It is an object to provide a photovoltaic device, in particular a back contact metal wrap-through photovoltaic and a module comprising a plurality of photovoltaic devices with improved passivation, and a method of manufacturing thereof.

[0012] In a first aspect, there is provided a photovoltaic device comprising a layered structure having a circumferential outer wall, a front surface for receiving optical radiation, a rear surface opposite to the front surface, an electrical contact arrangement, a first semiconductor layer of a first conductivity type, which first layer extending adjacent to the front surface and having at least one electrical front contact connected to the contact arrangement, and a second semiconductor layer of a second conductivity type, the second layer extending contiguous to the first layer and having at least one electrical rear contact connected to the contact arrangement. The first and second conductivity types being of opposite polarity such that the first and second layers are separated by a pn-junction, and the first and second layer extending into the outer wall. A passivating layer of a first type covering at least part of the outer wall substantially comprised by the depletion region across the pn-junction. A passivating layer of a second type covering at least part of the outer wall comprised by the first semiconductor layer, the passivating layer of the second type being contiguous to the passivating layer of the first, and a passivating layer of a third type covering at least part of the outer wall comprised by the second semiconductor layer, the passivating layer of the third type being contiguous to the passivating layer of the first type.

[0013] In a second aspect, there is provided a photovoltaic device, comprising a layered structure having a front surface for receiving optical radiation, a rear surface opposite to the front surface, an electrical contact arrangement at the rear surface, a first semiconductor layer of a first conductivity type, which first layer extending adjacent to the front surface and having at least one electrical front contact, and a second semiconductor layer of a second conductivity type, which second layer extending contiguous to the first layer and having at least one electrical rear contact connected to the contact arrangement. The first and second conductivity types being of opposite polarity such that the first and second layers are separated by a pn-junction. The layered structure comprising at least one aperture extending from the front surface to the rear surface, the aperture being bounded by an aperture wall and having an electrical contact path connecting the at least one electrical front contact to the electrical contact arrangement at the rear surface. A passivating layer of a first type extending in the at least one aperture and covering at least part of the aperture wall substantially comprised by a depletion region across the pn-junction. A passivating layer of a second type extending in the at least one aperture contiguous to the passivating layer of the first type and covering part of the aperture wall comprised by the first semiconductor layer, and a passivating layer of a third type extending in the at least one aperture contiguous to the passivating layer of the first type and covering part of the aperture wall comprised by the second semiconductor layer.

**[0014]** Both aspects may be combined resulting in a back contact metal wrap-through photovoltaic cell device comprising passivation of the circumferential outer wall according to the first aspect and aperture passivation according to the second aspect.

**[0015]** Each of the passivating layers can be individually selected and matched to a particular semiconductor layer exposed at the circumferential outer wall of the layered structure and/or in an aperture, for optimally reducing unwanted surface recombination at the outer wall and/or in the apertures. In particular, short-circuiting or shunting resistance loss due to leak currents between the semiconductor layers and/or reverse breakdown effects across the pn-junction or depletion area at the outer wall and/or in the apertures, which both form an exposed wall or area of the photovoltaic device, can be effectively prevented or reduced by selecting a suitable passivation material, preferably having a substantially electrically neutral effective surface charge density. Thereby improving the efficiency of the photovoltaic device.

**[0016]** For the purpose of the invention, passivation materials for forming a passivating layer of the first type having a suitable electrically neutral or substantially electrically neutral effective surface charge density are amorphous silicon, annealed silicon dioxide and others.

**[0017]** Suitable passivation materials for forming a passivating layer of the second and third type at the first or second semiconductor layer, respectively, should have an effective surface charge density of a type opposite and higher than the corresponding semiconductor layer.

**[0018]** For the purpose of the invention, it has been found that an effective surface charge density  $Q_f$  larger than  $10^{-10}$  cm<sup>-2</sup> provides an effective passivation, i.e. effectively reduces the unwanted surface recombination of semiconductor layers. Passivation materials of this type are, for example,

Silicon Nitride, Silicon Dioxide, Silicon Carbide, Titanium Dioxide, Aluminium Oxide, Hafnium Oxide and others.

**[0019]** Silicon Nitride, Silicon Dioxide, and Silicon Carbide, for example, are used to provide passivation of n-type semiconductor material, whereas Aluminium Oxide, Titanium Oxide, and Hafnium Oxide, for example, are used provide passivation of semiconductor material of the p-type, for example.

**[0020]** It is noted that in a back contact metal wrap-through photovoltaic device comprising passivation of the circumferential outer wall and aperture passivation as disclosed above, at least partly, different materials may be selected for the passivating layers of the first, second and third type of the circumferential outer wall and the apertures, respectively.

**[0021]** The passivating layer of the first type may cover part of the circumferential outer wall and/or the aperture wall beyond the depletion region across the pn-junction and both the passivating layers of the second and third type may cover or overlap at the passivating layer of the first type. For the purpose of the present invention and the attached claims, the term contiguous used in relation to the passivating layers has to be understood to include at least partially overlapping layers, provided that the passivating layer of the first type is overlapped by any or both of the passivating layers of the second and third type. That is, any or both of the passivating layers of the first type, as seen from the circumferential outer wall and/or the aperture wall.

**[0022]** Among others to simplify manufacturing of the photovoltaic device, it is preferred to have the passivating layer of the second type extending over the edge of the outer circumferential wall adjacent to the front surface and/or the edge of the at least one aperture adjacent to the front surface and covering the front surface of the photovoltaic device. This passivating layer or film at the same time may exhibit a transparent anti-reflective coating for improving the collection of solar radiation, as already discussed in the introduction.

**[0023]** In the case of a so-called front emitter design, in which the pn-junction is provided essentially closer to the front surface than to the back or rear surface of the photovoltaic device, it has been found that shunting resistance loss and/or reverse breakdown effects at the pn-junction at the outer circumferential wall and/or in an aperture of the photovoltaic device, are already effectively reduced by having the passivating layer of the first type identical to the passivating layer or film of the second type. That is, the passivating layer or film of the second type covers at least both the area comprised by the first semiconductor layer or emitter and the pn-junction area or depletion region.

**[0024]** Preferably, for ease of manufacturing of the photovoltaic device, the passivating layers of the first and second type are integral, i.e. it is a single layer or film which may be applied in a single process step from the front surface. The passivating layer of the third type may, at least partly, cover such an integral passivating layer.

**[0025]** In the case of a so-called back or rear emitter design, in which the pn-junction is provided essentially closer to the back or rear surface than to the front surface of the photovoltaic device, it has been found that shunting resistance loss and/or reverse breakdown effects at the pn-junction in an aperture and/or at the outer circumferential wall of the photovoltaic device, are already effectively reduced by having the passivating layer of the first type identical to the passivating layer of the third type. That is, the passivating layer or film of the third type covers both the area comprised by the second semiconductor layer or emitter and the pn-junction area or depletion region.

**[0026]** Preferably, for ease of manufacturing of the photovoltaic device, the passivating layers of the first and third type are integral, i.e. it is a single layer or film which may be applied in a single process step from the back surface. The passivating layer of the second type may cover such an integral passivating layer.

**[0027]** The electrical wiring or electric contact tracks at the front surface and the electrical contact arrangement at the rear surface may initially be applied before the application of the respective passivating layers. From a manufacturing process point of view, however, it is preferred to apply the passivating layer on either surface first.

**[0028]** In the back contact metal wrap-through photovoltaic device, in an embodiment thereof, the passivating layers in the at least one aperture cover the aperture wall such to form an electrical insulating jacket that provides an electrical insulation between the layered structure, i.e. the aperture wall, and an electrically conducting electrode or an electrically conducting plug arranged in the at least one aperture.

**[0029]** Besides the passivating layers disclosed above, a further covering layer or a stack of layers may be provided on top of a passivating layer, to improve the efficiency of the photovoltaic device.

**[0030]** An example of such a further covering layer in a back contact metal wrap-through photovoltaic device is an insulating layer extending in an aperture between the passivating layers and the electrically conducting electrode from the front to the rear surface of the device.

**[0031]** Other examples of further covering layers are Titanium Nitride, Silicon Nitride, and the like.

**[0032]** The layered structure forming the photovoltaic device according to the invention can be of any type known in practice and, in particular, of the silicon bulk type or of the thin-film type.

**[0033]** Silicon bulk type photovoltaic devices generally comprise a crystalline silicon wafer or bulk semiconductor material, such as monocrystalline silicon or poly- or multic-rystalline silicon of an n-conductivity type or a p-conductivity type, wherein the first and second semiconductor layers are formed by suitably doting of adjacent regions or volumes of the bulk. Photovoltaic devices of this type are generally plate shaped.

**[0034]** A thin-film solar cell or photovoltaic device is produced by depositing the semiconductor layers as thin layers (thin film) on a substrate. The thickness range of such a layer is wide and varies from a few nanometers to tens of micrometers. Cadmium Telluride, CdTe, Copper Indium Gallium Selenide, CIGS, and Amorphous Silicon, A-Si, are three thinfilm technologies often used for outdoor photovoltaic solar power production. Thin-film devices may have varying shapes.

**[0035]** Photovoltaic devices of the silicon bulk type and the thin-film silicon type are well known to the skilled person. For the purpose of the present invention no further elucidation is required.

**[0036]** In a third aspect, there is provided a method of manufacturing a photovoltaic device comprising a layered structure having a circumferential outer wall, a front surface for receiving optical radiation and a rear surface opposite to the front surface. The method comprising providing a first

semiconductor layer of a first conductivity type, the first layer extending adjacent to the front surface and into the outer wall, and comprising at least one electrical front contact. Providing a second semiconductor layer of a second conductivity type, the second layer extending contiguous to the first layer and into the outer wall, and comprising at least one electrical rear contact, wherein the first and second conductivity types being of opposite polarity such that the first and second layers are separated by a pn-junction. Providing an electrical contact arrangement. Electrically connecting the at least one front and rear contact to the electrical contact arrangement. The method further comprises the steps of covering at least part of the circumferential outer wall substantially comprised by a depletion region across the pn-junction by a passivating layer of a first type; covering at least part of the circumferential outer wall comprised by the first semiconductor layer by a passivating layer of a second type contiguous to the passivating layer of the first type, and covering at least part of the circumferential outer wall comprised by the second semiconductor layer by a passivating layer of a third type contiguous to the passivating layer of the first type.

[0037] In a fourth aspect, there is provided a method of manufacturing a photovoltaic device comprising a layered structure having a front surface for receiving optical radiation and a rear surface opposite to the front surface. The method comprising providing a first semiconductor layer of a first conductivity type, the first layer extending adjacent to the front surface and comprising at least one electrical front contact. Providing a second semiconductor layer of a second conductivity type, the second layer extending contiguous to the first layer and comprising at least one electrical rear contact, wherein the first and second conductivity types being of opposite polarity such that the first and second layers are separated by a pn-junction. Providing at least one aperture extending from the front surface to the rear surface, the aperture being bounded by an aperture wall. Providing an electrical contact arrangement at the rear surface. Electrically connecting the at least one rear contact to the electrical contact arrangement, and providing an electrical contact path electrically connecting the at least one electrical front contact through the at least one aperture to the electrical contact arrangement. The method further comprises the steps of covering at least part of the aperture wall substantially comprised by a depletion region across the pn-junction by a passivating layer of a first type; covering at least part of the aperture wall comprised by the first semiconductor layer by a passivating layer of a second type contiguous to the passivating layer of the first type, and covering at least part of the aperture wall comprised by the second semiconductor layer by a passivating layer of a third type contiguous to the passivating layer of the first type.

**[0038]** Both the method according to the third and fourth aspect may be combined resulting in a method for manufacturing a back contact metal wrap-through photovoltaic cell device comprising passivation of the circumferential outer wall according to the third aspect and aperture passivation according to the fourth aspect.

**[0039]** Surface passivation is generally applied using a Plasma Enhanced Chemical Vapour Deposition, PECVD, process, preferably followed by a post-deposition annealing process. However, for the purpose of the present invention other known deposition processes may be used, for example Atomic Layer Deposition, ALD, or a so-called wet process, wherein the passivating material to be deposited is contained in a liquid which is applied at a surface to be passified. Passivating layers or films may also be applied using a spraying method, for example.

[0040] The order in which the passivating layers of the first, second and third type are applied may vary. In an embodiment, the passivating layer of the first type, substantially covering the depletion region across the pn-junction, is applied from either one of the front surface and the rear surface, followed by a selective etching step, for example, to remove the passivating layer of the first type from the front or rear surface and from part of the circumferential outer wall and/or the aperture wall substantially comprised by the first semiconductor layer and/or the second semiconductor layer. Next the passivating layer of the second type may be applied from the front surface, such to be contiguous to the passivating layer of the first type or the passivating layer of the third type may be applied from the rear surface, such to be contiguous to the passivating layer of the first type. It is noted that the passivating layer of the second type and the third type may, at least partially, overlap the passivating layer of the first type. If required, the passivating layer of the second and/or the third type may be removed from the front and/or rear surface, for example by selective etching, if required.

**[0041]** The latter removal will not be applied, of course, if the passivating layer of the second type should extend over the front surface and the passivating layer of the third type should extend over the rear surface, as discussed above. In the case of a photovoltaic device of the front emitter design, it is preferred to apply the passivating layer of the second type before the passivating layer of the third type. In the case of a photovoltaic device of the back or rear emitter design, it is preferred to apply the passivating layer of the third type before the passivating layer of the third type.

**[0042]** In an embodiment wherein the passivating layers of the first and second type are integral, this passivating layer is applied before the passivating layer of the third type is applied. In an embodiment wherein the passivating layers of the first and third type are integral, this passivating layer is applied before the passivating layer of the second type is applied. The passivating layers may be formed contiguous with a partial overlap.

**[0043]** In another embodiment, the passivating layers of the second and third type may be formed first, for example from the front and rear surface, respectively, after which at least part of the passivating layers of the second and third type substantially covering part of the circumferential outer wall and/or of the aperture wall comprised by the depletion region across the pn-junction is removed. This removal can be performed, for example, by using a selective wet etching material applied at a brush or sponge or the like which is selectively swept along the circumferential outer wall and/or the aperture wall. After this removal, the passivating layer of the first type is applied on the exposed area, to be contiguous to the passivating layers of the second and third type.

**[0044]** It will be appreciated that in the method according to the invention passivating materials or compounds of the first, second and third type are used as disclosed above. Suitable etching materials for removing such passivating layers of the first, second and third type are known to the skilled person and need no further elaboration.

**[0045]** Based on the above, those skilled in the art will appreciate that the application of the passivating layers is not limited to the specific embodiments disclosed. After having applied the passivating layers as disclosed, at least one further

covering layer covering at least one of the passivating layers of the first, second and third type may be applied.

**[0046]** In a fifth aspect there is provided a photovoltaic module comprising a plurality of electrically connected photovoltaic devices of the types disclosed above.

**[0047]** Those skilled in the art will appreciate that the teachings of the invention can also be applied with multijunction or heterojunction photovoltaic devices, comprising several stacked cells of first and second semiconductor layers and their corresponding p-n junctions. Such as a top cell, a middle cell and a bottom cell, for example. Each junction or cell is tuned to a different wavelength of light, thereby increasing efficiency of the photovoltaic device as a whole.

**[0048]** The invention will now be described in more detail by means of specific embodiments, with reference to the enclosed drawings, wherein equal or like parts and/or components are designated by the same reference numerals. The invention is in no manner whatsoever limited to the embodiments disclosed.

#### BRIEF DESCRIPTION OF THE DRAWINGS

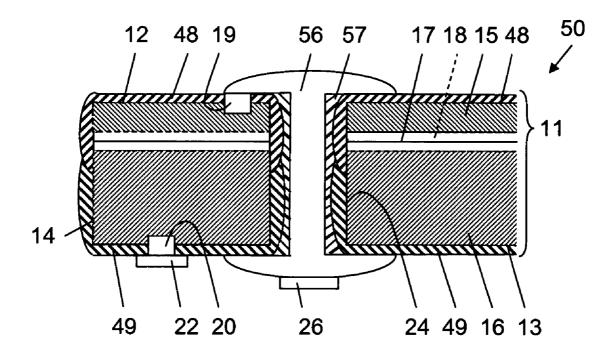

**[0049]** FIG. **1** shows schematically, not to scale, partly in cross-section, a portion of a substrate or wafer of a front emitter silicon bulk type prior art photovoltaic device.

**[0050]** FIG. **2** shows schematically, not to scale, partly in cross-section, a portion of a substrate or wafer of a front emitter silicon bulk type prior art back contact metal wrap-through photovoltaic device.

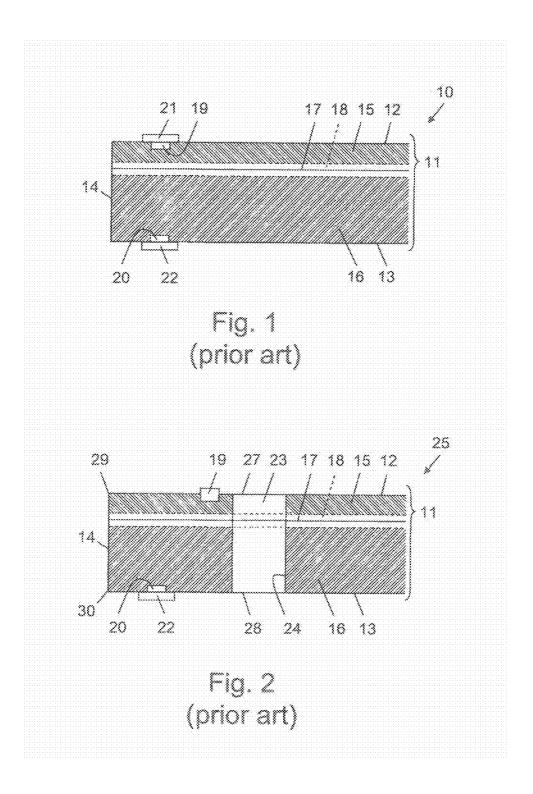

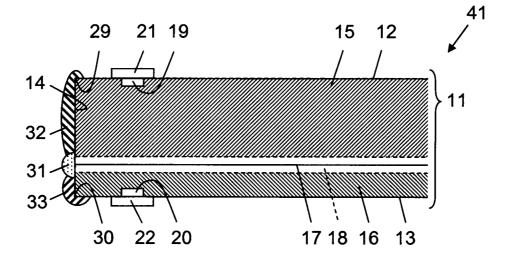

**[0051]** FIG. **3** shows schematically, not to scale, partly in cross-section, the photovoltaic device of FIG. **1** comprising outer wall passivation according to the invention.

**[0052]** FIG. **4** shows schematically, not to scale, partly in cross-section, the photovoltaic device of FIG. **2** comprising aperture wall passivation according to the invention.

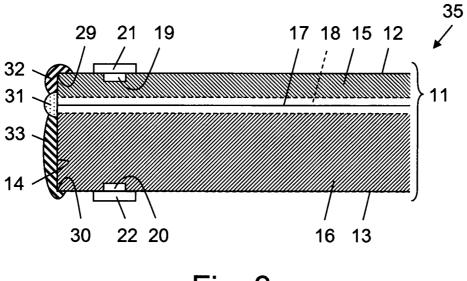

**[0053]** FIG. **5** shows schematically, not to scale, partly in cross-section, a portion of a substrate or wafer of a rear emitter silicon bulk type photovoltaic device, comprising circumferential outer wall passivation according to the invention.

**[0054]** FIG. **6** shows schematically, not to scale, partly in cross-section, a portion of a substrate or wafer of a front emitter silicon bulk type back contact metal wrap-through photovoltaic device, comprising aperture wall passivation according to the invention.

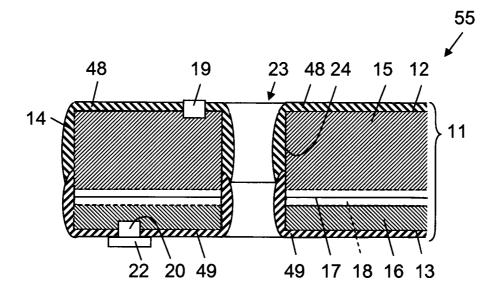

**[0055]** FIG. 7 shows schematically, not to scale, partly in cross-section, a portion of a substrate or wafer of a front emitter silicon bulk type back contact metal wrap-through photovoltaic device comprising circumferential outer wall passivation and aperture wall passivation according to an embodiment of the invention.

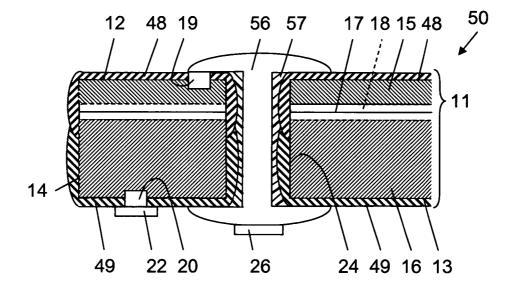

**[0056]** FIG. **8** shows schematically, not to scale, partly in cross-section, a portion of a substrate or wafer of a front emitter silicon bulk type back contact metal wrap-through photovoltaic device, comprising circumferential outer wall passivation and aperture wall passivation according to an embodiment of the invention.

**[0057]** FIG. **9** shows schematically, not to scale, partly in cross-section, a portion of a substrate or wafer of a rear emitter silicon bulk type back contact metal wrap-through photovoltaic device, comprising circumferential outer wall passivation and aperture wall passivation according to an embodiment of the invention.

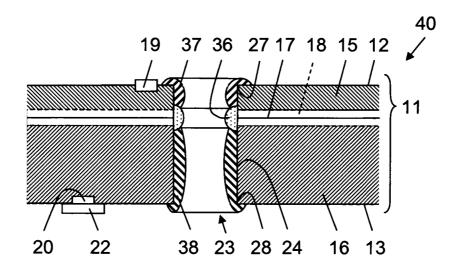

**[0058]** FIG. **10** shows schematically, not to scale, partly in cross-section, the photovoltaic device of FIG. **8**, comprising an electrically conducting plug and insulating jacket.

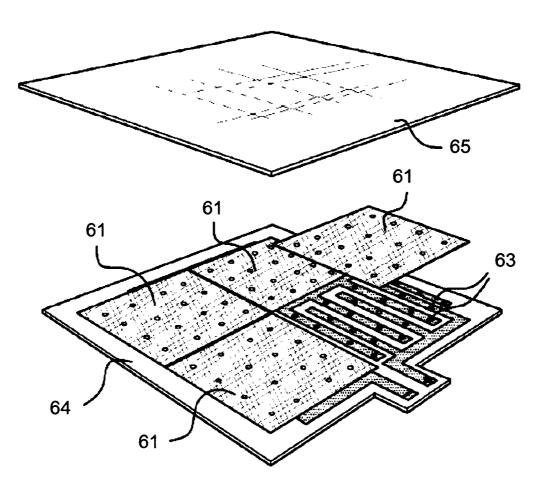

**[0059]** FIG. **11** shows schematically, not to scale, partly in exploded view, an example of a photovoltaic module comprising a plurality of electrically connected back contact metal wrap-through photovoltaic devices according to the invention.

#### DETAILED DESCRIPTION

**[0060]** FIG. 1 relates to a prior art photovoltaic device 10 of the so-called front emitter design type, comprising a plateshaped or planar silicon substrate or wafer 11, having a front surface or receiving surface 12 for receiving optical radiation, i.e. solar radiation, a back or rear surface 13 opposite to the front surface 12 and a circumferential outer wall 14.

[0061] The substrate 11 comprises a semiconductor bulk. A first volume or region of the bulk below the front surface 12 having a doping of a first polarity or first conductivity type, such as an n-type conductivity wherein electrons form the main charge carriers, forms a first semiconductor layer 15 or emitter extending adjacent to the front surface 12. A second volume or region of the bulk between the first layer 15 and the rear surface 13 comprising a doping of a second polarity or second conductivity type, opposite to the first polarity or conductivity type, such as a p-type conductivity wherein holes form the main charge carriers, forms a second semiconductor layer 16 contiguous to the first semiconductor layer 15.

[0062] The area or region separating the first and second semiconductor layers 15, 16 is a pn-junction 17 across which a depletion region 18 instantaneously forms, indicated by broken lines. The first and second semiconductor layers 15, 16 and the pn-junction 17 or depletion region 18 extend into the circumferential outer wall 14 of the substrate or wafer 11. Or in other words, the second semiconductor layers 15, 16 and the pn-junction 17 or depletion region 18 are exposed at the circumferential outer wall of the substrate or wafer 11.

[0063] At least one electrical contact 19 electrically contacts the first layer or emitter 15 and is available from the front surface 12, also called a front surface contact. At least one electrical contact 20 electrically contacts the second layer 16 and is available from the back or rear surface 13, also called a rear surface contact. Electrical energy provided by the photovoltaic device 10 is available at the front and rear surface contacts 19, 20. To this end, at both surfaces 12, 13 of the substrate 11 a contact arrangement 21 respectively 22 is provided, in the form of an electric wiring and/or electrically conducting bus bars for electrically connecting a plurality of front and rear surface contacts 19, 20, respectively.

[0064] For producing a back contact metal wrap-through photovoltaic device 25, the layered structure of first and second semiconductor layers 15, 16 and the pn-junction 17 or depletion region 18 comprises at least one via or aperture 23 extending from the front surface 12 to the rear surface 13, as shown in FIG. 2.

[0065] The at least one aperture 23 is bounded by an aperture wall 24. Although not shown for the purpose of clarity, the aperture 23 is filled with a plug of electrically conducting material providing an electrical contact path from the at least one electrical front contact 19 to an electrical contact arrangement at the rear surface 13. In practice, a plurality of apertures 23 are formed for contacting a plurality of electrical front contacts 19 to the electrical contact arrangement. [0066] As shown in FIG. 2, the first and second semiconductor layers 15, 16 and the pn-junction 17 or depletion region 18 extend into the aperture wall 24 of the at least one aperture 23. Or in other words, the second semiconductor layers 15, 16 and the pn-junction 17 or depletion region 18 are exposed at the aperture wall 24.

[0067] In practice, the first layer 15 or emitter has a thickness in the micrometer range, such as  $0.5 \ \mu m$ , whereas the aperture 25 has a diameter of a few hundred micrometers, such as 200  $\mu m$ , for example. Further, the front surface 12 may have a surface textured structure (not shown) to increase the effective amount of radiation at the front surface 12 for conversion into electrical energy. Dependent on the manufacturing process of the photovoltaic device 10, the at least one aperture 23 may be drilled, such as laser drilled, in the bulk before the first and second layers 15, 16 are produced, or the at least one aperture 23 may be drilled in the already manufactured layered structure 11.

[0068] Due to the drilling of the at least one aperture 23, and/or etching of the front and rear surfaces 12, 13 and/or texturing of the front surface 12, the edge 27 of the aperture 23 at the front surface 12 and the edge 28 of the aperture 23 at the rear surface 13 may exhibit a rounded or bevelled or otherwise knurled edge structure, resulting in a widened opening of the aperture at the front and/or rear surface 12, 13, different from the sharp edges 27, 28 shown in FIG. 2. Likewise, the outer edges 29, 30 of the circumferential outer wall 14 may be rounded or bevelled or knurled in practice.

[0069] For the purpose of the invention, part of the aperture edges 27, 28 flush to the front surface 12 or the rear surface 13, respectively, form part of the aperture wall 24 and part of the outer edges 29, 30 flush to the front surface 12 or the rear surface 13, respectively, form part of the circumferential outer wall 14.

**[0070]** In accordance with the first aspect of the invention, as schematically shown in FIG. **3**, a photovoltaic device is provided, for example a photovoltaic device **35** of the front emitter type, having the layered structure as shown in FIG. **1** and having passivating layers or films **31**, **32** and **33** applied at the circumferential outer wall **14** of the layered structure or substrate **11**.

[0071] As shown in FIG. 3, a passivating layer 31 of a first type covers at least part of the area of the circumferential outer wall 14 substantially comprised by the depletion region 18 across the pn-junction 17. A passivating layer 32 of a second type covers at least part of the area of the circumferential outer wall 14 comprised by the first semiconductor layer 15. A passivating layer 33 of a third type covers at least part of the area of the circumferential outer wall 14 comprised by the first semiconductor layer 15. A passivating layer 33 of a third type covers at least part of the area of the circumferential outer wall 14 comprised by the second semiconductor layer 16.

[0072] The passivating layer 32 of the second type is formed contiguously to the passivating layer 31 of the first type and extends partly over the outer edge 29 of the front surface 12. The passivating layer 33 of the third type is formed contiguous to the passivating layer 31 of the first type and extends partly over the outer edge 30 of the rear surface 13. For the purpose of the invention, the term contiguous used in relation to the passivating layers 31, 32, 33 has to be understood to include adjoining passivating layers as well as at least partially overlapping passivating layers. That is one or both the passivating layers 32 and 33 may overlap the passivating layer 31 of the first type as seen from the circumferential outer wall 14. That is, any or both of the passivating layers 32 and **33** are on top of the passivating layer **31** of the first type, as seen from the circumferential outer wall **14**.

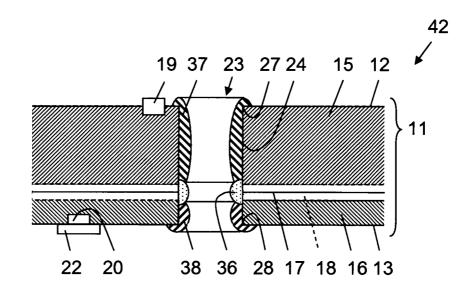

[0073] FIG. 4 schematically shows a front emitter photovoltaic device 40 of the back contact metal wrap-through type as shown in FIG. 3, and comprising passivating layers or films 36, 37 and 38 applied at the aperture wall 24 of the aperture 23, in accordance with the second aspect of the invention.

[0074] As shown in FIG. 4, a passivating layer 36 of a first type covers at least part of the area of the aperture wall 24 substantially comprised by the depletion region 18 across the pn-junction 17. A passivating layer 37 of a second type covers at least part of the area of the aperture wall 24 comprised by the first semiconductor layer 15. A passivating layer 38 of a third type covers at least part of the area of the area of the area of the aperture wall 24 comprised by the first semiconductor layer 15. A passivating layer 38 of a third type covers at least part of the area of the aperture wall 24 comprised by the second semiconductor layer 16.

[0075] In a like manner as disclosed with reference to the passivation of the circumferential outer wall 14, the passivating layer 37 of the second type is formed contiguously to the passivating layer 36 of the first type and extends partly over the aperture edge 27 of the front surface 12. The passivating layer 38 of the third type is formed contiguous to the passivating layer 36 of the first type and extends partly over the aperture edge 28 of the rear surface 13. For the purpose of the invention, the term contiguous used in relation to the passivating layers 36, 37, 38 has to be understood to include adjoining passivating layers as well as at least partially overlapping passivating layers. That is one or both the passivating layers 37 and 38 may overlap the passivating layer 36 of the first type as seen from the aperture wall 24. That is, any or both of the passivating layers 37 and 38 are on top of the passivating layer 36 of the first type, as seen from the aperture wall 24.

[0076] Those skilled in the art will appreciate that passivation of the circumferential outer wall 14 may also be applied in the back contact metal wrap-through photovoltaic device 40 comprising aperture wall passivation. In such an embodiment, in practice, the passivating layers 31 and 36 are of the same first type, the passivating layers 32 and 37 are of the same second type and the passivating layers 33, 38 are of the same third type. However, its is noted that the types of passivating layers 31, 32, 33 applied at the circumferential outer wall 14 may differ from the types of passivating layers 36, 37, 38 applied at the aperture wall 24, because the passivating layers 36, 37, 38 may have to form an electrical insulation between the layered structure, i.e. the aperture wall 24, and an electrically conducting electrode or an electrically conducting plug arranged in the at least one aperture 23.

[0077] FIG. 5 shows part of a photovoltaic device 41 of the rear emitter type, in which the pn-junction 17 is provided essentially closer to the rear surface 13 than to the front surface 12. The circumferential outer wall 14 of the photovoltaic device 41 is passified in accordance with the first aspect of the invention, in a manner comparable to the front emitter device 35, as discussed above and shown in FIG. 3.

[0078] FIG. 6 shows part of a back contact metal wrapthrough photovoltaic device 42 of the rear emitter type, comprising aperture wall passivation according to the second aspect of the invention, comparable to the front emitter device 40 discussed above and shown in FIG. 4. In the embodiment of FIG. 6, the circumferential outer wall of the photovoltaic device 42 may be passified as shown for the photovoltaic device 41 in FIG. 5.

**[0079]** As will be appreciated by those skilled in the art, in the photovoltaic devices illustrated in the FIGS. **3-6**, the front

surface 12 and the rear surface 13 may be covered with further passivating layers of a suitable type (not shown).

**[0080]** Among others to simplify manufacturing of the photovoltaic device, it is preferred to combine passivation of the circumferential outer wall and the aperture wall with surface passivation of the front surface and/or the rear surface of a photovoltaic device.

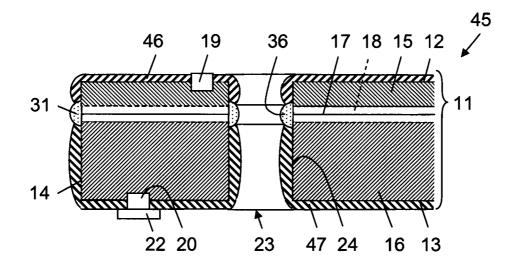

[0081] FIG. 7 shows a back contact metal wrap-through photovoltaic device 45 wherein the passivating layers 32 respectively 37 of the second type extending over the outer edge 29 of the outer circumferential wall 14 or the aperture edge 27, as shown in FIGS. 3-6, cover the front surface 12 of the photovoltaic device, indicated by reference numeral 46.

**[0082]** Likewise, the passivating layers **33** respectively 38 of the second type extending over the outer edge **30** of the outer circumferential wall **14** or the aperture edge **28**, as shown in FIGS. **3-6**, may cover the rear surface **13** of the photovoltaic device, indicated by reference numeral **47**.

**[0083]** As discussed above, the passivating layers **32** and **37** are, preferably, of the same second type, such that a single passivating layer **46** of the second type is applied. Besides its passivation properties, the passivating layer or film **46** may form a transparent anti-reflective coating for improving the collection of solar radiation by the photovoltaic device. The passivating layers **32** and **37** are, preferably, of the same second type, such that a single passivating layer **47** of the second type is applied.

[0084] In the case of a so-called front emitter design, such as shown in FIGS. 1-4 and 7, it has been found that shunting resistance loss and/or reverse breakdown effects at the pn-junction 17 at the outer circumferential wall 14 and/or in an aperture 23 of the photovoltaic device of the back contact metal wrap-through photovoltaic device, are already effectively reduced by having the passivating layer of the first type 31, 36 identical to the passivating layer of the second type 32, 37.

[0085] That is, the passivating layer or film of the second type 32, 37 covers both at least part of the area of the circumferential outer wall 14 comprised by the first semiconductor layer 15 and at least part of the area of the circumferential outer wall 14 substantially comprised by the depletion region 18 across the pn-junction 17.

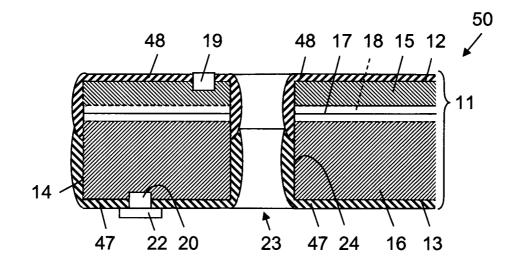

**[0086]** Preferably, for ease of manufacturing of the photovoltaic device, the passivating layers of the first and second type are integral, i.e. it is a single layer or film which may be applied in a single process step from the front surface **12**, for example. Such as illustrated in FIG. **8** for a back contact metal wrap-through photovoltaic device **50**, wherein a single passivating layer **48** of the second type extends over the front surface **12** of the photovoltaic device **50** and the passivating layer **47** of the third type extends over the rear surface **13** of the photovoltaic device **50**. The passivating layer **47** of the third type is contiguous to the passivating layer of the second type **48**, that is the passivating layers **47**, **48** adjoin each other or the passivating layer **47** partly or completely overlaps the passivating layer **48** at the circumferential outer wall **14** and the aperture wall **24**, as disclosed above.

**[0087]** In the case of a so-called back or rear emitter design as shown in FIGS. **5** and **6**, for example, it has been found that shunting resistance loss and/or reverse breakdown effects at the pn-junction **17** in an aperture **23** and/or at the outer circumferential wall **14** of the photovoltaic device, are already effectively reduced by having the passivating layer of the first type identical to the passivating layer of the third type. That is, a passivating layer or film of the third type covers both the rear surface 13 and the pn-junction 17, i.e. the depletion region 18 at the circumferential outer wall 14 and the aperture wall 24. Preferably, for ease of manufacturing of the photovoltaic device, the passivating layers of the first and second type are integral, i.e. it is a single layer or film 49 which may be applied in a single process step from the rear surface 13, for example, such as illustrated in FIG. 9 for a back contact metal wrap-through photovoltaic device 55. The passivating layer 48 of the second type is contiguous to the passivating layer 49 of the third type. That is, the passivating layers 48, 49 adjoin each other or the passivating layer 48 partly or completely overlaps or covers the passivating layer 49 at the circumferential outer wall 14 and the aperture wall 24.

**[0088]** The passivating layers of the first, second and third type may have different thicknesses ranging from a few nm, like 5 nm for ALD aluminium oxide, up to a few micrometers for silicon oxide. In the case of a front emitter design, the passivating layers of the first and second type may be thinner or less thick compared to the passivating layer of the third type. In the case of a rear emitter design, the passivating layers of the first and third type may be thinner or less thick compared to the passivating layer of the second type.

**[0089]** In the case of a back contact metal wrap-through photovoltaic device, the passivating layers in the aperture **23** may form an electrical insulating jacket covering the aperture wall **23** to provide electrical insulation of the layered structure **11** from an electrically conducting electrode arranged in the at least one aperture **23**. However, inn order to optimally select the types of passivating layers in the aperture, in an embodiment of the invention, a separate insulating jacket may be provided in the aperture **23** on top of the passivating layers, as seen from the aperture wall **24**, schematically as illustrated in FIG. **10**.

[0090] FIG. 10 shows the back contact metal wrap-through photovoltaic device 50 of FIG. 8, wherein an electrically conducting plug 56 connects the front contact 19 to a contact arrangement 26 at the rear surface 13. In the aperture 23, an electrically insulating jacket 57 surrounds the plug 56.

**[0091]** Those skilled in the art will appreciate that further layers, including further passivating layers, may be applied at a passivating layer of the first, second or third type, to improve the efficiency of a photovoltaic device. For the purpose of the present invention, such further layers are not further elucidated.

**[0092]** Instead of a silicon bulk wafer, the teachings of the invention may be likewise applied to a photovoltaic device wherein the layered structure comprises a thin-film body, and wherein the first and second semiconductor layers are applied on the thin-film body.

[0093] As discussed in the summary part, the several passivating layers 31, 32, 33; 36, 37, 38; 46, 47, 48, 49 illustrated in the drawings may be applied by any known surface passivation technique, such as a Plasma Enhanced Chemical Vapour Deposition, PECVD, process, preferably followed by a post-deposition annealing process, etching techniques, by Atomic Layer Deposition, ALD, or by a so-called wet process, wherein the passivating material to be deposited is contained in a liquid which is applied at a surface to be passified. Passivating layers or films may also be applied using a spraying method, for example.

**[0094]** The order in which the passivating layers of the first, second and third type are applied may vary. With reference to FIGS. **3**, **4** and **5**, **6**, for example, in an embodiment, one or

both the passivating layers **31**; **36** of the first type, substantially covering the depletion region **18** across the pn-junction **17**, are first applied from either one of the front surface **12** or the rear surface **13**, followed by a selective etching step, for example, to remove the amount of passivating layer **31**; **36** of the first type from the front **12** or rear surface **13** and from part of the circumferential outer wall **14** and/or the aperture wall **24** substantially comprised by the first semiconductor layer **15** and/or the second semiconductor layer **16**.

[0095] It will be appreciated that in the case of a front emitter design as shown in FIGS. 3 and 4, the passivating layer 31; 36 of the first type is preferably applied from the front surface 12. In the case of a rear emitter design, such as shown in FIGS. 5 and 6, the passivating layer of the first type is preferably applied from the rear surface 13.

[0096] Next, the passivating layer 32; 37 of the second type may be applied from the front surface 12, such to be contiguous to the passivating layer 31; 36 of the first type. The passivating layer 33; 38 of the third type may be applied from the rear surface 13, such to be contiguous to the passivating layer 31; 36 of the first type. It is noted that the passivating layer 32; 37 of the second type and the passivating layer 33; 38 of the third type may, at least partially, overlap the passivating layer 31; 36 of the first type. If required, the passivating layer of the second 32; 37 and/or the third type 33; 38 may be removed from the front 12 and/or rear surface 13, for example by selective etching, if required. For example to apply surface passivation at the front surface 12 and/or the rear surface 13 using different types of passivating layers compared to the passivating layers 31, 32, 33 and 36, 37, 38.

[0097] The latter removal will not be applied, of course, if the passivating layer 32; 37 of the second type should extend over the front surface 12 and the passivating layer 33; 38 of the third type should extend over the rear surface 13, as shown in the embodiment of FIG. 7, passivating layers 46 and 47, respectively.

[0098] In the case of a photovoltaic device of the front emitter design, it is preferred to apply the passivating layer 32; 37 of the second type before the passivating layer 33; 38 of the third type, such to ensure that the passivating layer 33; 38 of the third type is always on top of the passivating layer 32; 37 of the second type, if same overlap. In the case of a photovoltaic device of the back or rear emitter design, it is preferred to apply the passivating layer 33; 38 of the third type before the passivating layer 32; 37 of the second type, such to ensure that the passivating layer 32; 37 of the second type is always on top of the passivating layer 33; 38 of the third type, if same overlap.

**[0099]** In an embodiment of a photovoltaic device of the front emitter design, wherein the passivating layers of the first and second type are integral, such as the passivating layer **48** shown in FIG. **8**, this passivating layer **48** is applied from the front surface **12** before the passivating layer **49** of the third type is applied from the rear surface **13**.

**[0100]** In an embodiment of a photovoltaic device of the rear emitter design, wherein the passivating layers of the first and third type are integral, such as the passivating layer **49** shown in FIG. **9**, this passivating layer **49** is applied from the rear surface **13** before the passivating layer **48** of the second type is applied from the front surface **12**.

**[0101]** The passivating layers **48**, **49** may be formed contiguous with a partial overlap. Etching may be required between the successive application steps, to remove passivating material from unwanted areas of the circumferential outer wall **14** and/or the aperture wall **24**, whenever required.

[0102] In another embodiment, the passivating layers 32; 37 of the second and third 33; 38 type may be formed first, for example from the front 12 and rear surface 13, respectively, after which at least part of the passivating layers 32; 37 of the second and third 33; 38 type substantially covering part of the circumferential outer wall 14 and/or of the aperture wall 24 comprised by the depletion region 18 across the pn-junction 17 is removed. This removal can be performed, for example, by using a selective wet etching material applied at a brush or sponge or the like which is selectively swept along the passivating layer(s) covering the circumferential outer wall 14 and/or the aperture wall 24 at the position at which the passivating layer 31; 36 of the first type is to be applied. After this removal, the passivating layer 31; 36 of the first type is applied on the thus exposed area, to be contiguous to the passivating layers 32; 37 of the second and third 33; 38 type. [0103] Suitable etching materials for removing passivating layers of the first, second and third type are known to the skilled person and need no further elaboration. Those skilled in the art will appreciate that further steps may be required, such as cleaning steps, for example.

**[0104]** Each of the passivating layers can be individually selected and matched to a particular semiconductor layer exposed at the circumferential outer wall of the layered structure and/or in an aperture, for optimally reducing unwanted surface recombination at the outer wall and/or in the apertures. In particular, short-circuiting or shunting resistance loss due to leak currents between the semiconductor layers and/or reverse breakdown effects across the pn-junction or depletion area at the outer wall 14 and/or in the aperture wall 24, which both generally form an exposed wall or area of the photovoltaic device, can be effectively prevented or reduced by selecting a suitable passivation material, preferably having a substantially electrically neutral effective surface charge density.

**[0105]** For the purpose of the invention, passivation materials for forming a passivating layer of the first type having a suitable electrically neutral or substantially electrically neutral effective surface charge density are amorphous silicon, annealed silicon dioxide and others.

**[0106]** Suitable passivation materials for forming a passivating layer of the second and third type at the first or second semiconductor layer, respectively, should have an effective surface charge density of a type opposite and higher than the corresponding semiconductor layer.

**[0107]** For the purpose of the invention, it has been found that an effective surface charge density  $Q_f$  larger than  $10^{-10}$  cm<sup>-2</sup> provides an effective passivation, i.e. effectively reduces the unwanted surface recombination of semiconductor layers. Passivation materials of this type are, for example, Silicon Nitride, Silicon Dioxide, Silicon Carbide, Titanium Dioxide, Aluminium Oxide, Hafnium Oxide and others.

**[0108]** Silicon Nitride, Silicon Dioxide, and Silicon Carbide, for example, are used to provide passivation of n-type semiconductor material, whereas Aluminium Oxide, Titanium Oxide, and Hafnium Oxide, for example, are used provide passivation of semiconductor material of the p-type, for example.

**[0109]** It is noted that in a back contact metal wrap-through photovoltaic device comprising passivation of the circumferential outer wall and aperture passivation as disclosed above, at least partly, different materials may be selected for the

passivating layers of the first, second and third type of the circumferential outer wall and the apertures, respectively.

**[0110]** After having the passivation layers for passivation of the circumferential outer wall **14** and the aperture wall **24** have been applied, as discussed above, electrical wiring and the like may be applied at the front and rear surfaces **12**, **13** and further layers may be applied on top these passivating layers, for example, using any known deposition process. Such steps are well-known to the skilled person.

[0111] The invention is likewise applicable with a photovoltaic device comprising a plurality of stacked first 15 and second semiconductor layers 16 and pn-junctions 17, also called multi-junction or heterojunction photovoltaic devices, such that for each pn-junction 17 and semiconductor layer 15, 16 optimal passivating layer 31, 32, 33 or 36, 37, 38 or combinations of passivating layers is applied, following the teachings above.

**[0112]** FIG. **11** shows an embodiment of a photovoltaic module **60** comprising a plurality of electrically connected back contact metal wrap-through photovoltaic devices or solar cells **61** according to the invention. A contact arrangement **62** on a support **64** is defined to match the electrical pattern of the back contacts of the photovoltaic devices **61**. Solder paste **63** is applied to each of the contact positions, indicated by small circles, for electrically connecting the back contact of **61** and the contact arrangement **62**. The photovoltaic devices **61** are positioned onto the contact arrangement **62** such that the contact positions match. By heating the solder paste **63**, the back contacts are electrically connected to the contact arrangement **62**. A transparent plate **65**, such as a glass plate, covers and protects the photovoltaic devices **61**.

**[0113]** The invention may be practiced otherwise than as specifically described herein, and the abovementioned embodiments and examples are merely intended as an illustration to the skilled reader. The scope of the invention is only limited by the appended claims.

1-30. (canceled)

- 31. A photovoltaic device, comprising:

- a layered structure having a front surface for receiving optical radiation and a rear surface opposite to said front surface, the layered structure having a circumferential outer wall surrounding the layered structure;

- at least one electrical contact arrangement positioned at the rear surface, and optionally at the front surface, or at both the front surface and the rear surface;

- a first semiconductor layer of a first conductivity type, the first semiconductor layer extending adjacent to the front surface and to the outer wall;

- at least one electrical front contact positioned in communication with the front surface and the first semiconductor layer, the at least one electrical front contact being connected to the at least one contact arrangement on the front surface, when the at least one contact arrangement is present on the front surface;

- a second semiconductor layer of a second conductivity type, said second layer extending contiguous to the first layer and to the outer wall;

- at least one electrical rear contact in communication with the second semiconductor layer and the at least one electrical contact arrangement at the rear surface;

- the layered structure optionally comprising at least one aperture defined therein extending from the front surface to the rear surface and being bounded by an aperture

wall, the aperture defining an electrical contact path connecting the at least one electrical front contact to the at least one electrical contact arrangement at the rear surface;

- the conductivity types of the first semiconductor layer and the second semiconductor layer being of opposite polarity wherein the contact between the first semiconductor layer and the second semiconductor layer is defined by a pn-junction and a depletion region formed across the pn-junction, the pn-junction and depletion region extending to the outer wall, and to the aperture wall, when the at least one defined aperture is present;

- a passivating layer of a first type covering the part of the outer wall that is in contact with the pn-junction and depletion region;

- a passivating layer of a second type covering the part of the outer wall that is in contact with the first semiconductor layer, the passivating layer of the second type being contiguous to the passivating layer of the first type;

- a passivating layer of a third type covering the part of the outer wall that is in contact with the second semiconductor layer, the passivating layer of the third type being contiguous to the passivating layer of the first type; and when at least one aperture is defined,

- the passivating layer of the first type extends into the at least one defined aperture and covers the part of the aperture wall that is in contact with the pn-junction and depletion region; the passivating layer of the second type extends into the at least one defined aperture contiguous to the passivating layer of the first type and covers the part of the aperture wall contacting the first semiconductor layer; and the passivating layer of a third type extends into the at least one defined aperture contiguous to the passivating layer of the first type and covers the part of the aperture wall contacting the second semiconductor layer.

**32**. The photovoltaic device according to claim **31**, wherein the passivating layer of the second type extends over the front surface.

**33**. The photovoltaic device according to claim **32**, wherein the passivating layer of the second type is identical to the passivating layer of the first type.

**34**. The photovoltaic device according to claim **33**, wherein the passivating layers of the first and second type are integral.

**35**. The photovoltaic device according to claim **31**, wherein the passivating layer of the third type extends over the rear surface.

**36**. The photovoltaic device according to claim **35**, wherein the passivating layer of the third type is identical to the passivating layer of the first type.

**37**. The photovoltaic device according to claim **31**, wherein the passivating layers of the first and third type are integral.

**38**. The photovoltaic device according to claim **31**, wherein the passivating layer of the first type has a substantially neutral effective surface charge density.

**39**. The photovoltaic device according to claim **38**, wherein the passivating layer of the first type comprises at least one of amorphous silicon and annealed silicon dioxide.

**40**. The photovoltaic device according to claim **31**, wherein the passivating layer of the second type has an effective surface charge density of a type opposite to and higher than the effective surface charge density of the first semiconductor layer.

**41**. The photovoltaic device according to claim **31**, wherein the passivating layer of the third type has an effective surface charge density of a type opposite to and higher than the effective surface charge density of the second semiconductor layer.

**42**. The photovoltaic device according to claim **31**, wherein the first semiconductor layer is of an n-type conductivity and the passivating layer of the second type comprises at least one of Silicon Nitride, Silicon Dioxide, and wherein the second semiconductor layer is of a p-type conductivity and the passivating layer of the third type comprises at least one of Aluminium Oxide, Titanium Dioxide, Hafnium Oxide.

**43**. The photovoltaic device according to claim **31**, wherein the first semiconductor layer is of a p-type conductivity and the passivating layer of the second type comprises at least one of Aluminium Oxide, Titanium Dioxide, Hafnium Oxide, and wherein the second semiconductor layer is of an n-type conductivity and the passivating layer of the third type comprises at least one of Silicon Nitride, Silicon Dioxide, Silicon Carbide.

44. The photovoltaic device according to claim 31 having at least one defined aperture, wherein the passivating layers form an electrical insulating jacket covering the aperture wall of the at least one defined aperture providing an electrical insulation of the layered structure from an electrically conducting electrode arranged in the at least one defined aperture.

**45**. The photovoltaic device according to claim **31**, wherein the layered structure comprises a planar semiconductor body, and wherein each of the first semiconductor layer and the second semiconductor layer are formed by doting of adjacent regions of the semiconductor body.

**46**. The photovoltaic device according to claim **31**, wherein the layered structure comprises a thin-film body, and wherein each of the first semiconductor layer and the second semiconductor layer are applied on the thin-film body.

47. The photovoltaic device according to claim 31, further comprising at least one further covering layer covering at least one of the passivating layers of the first, second and third type.

**48**. A method of manufacturing a photovoltaic device, the method comprising the steps of:

- providing a layered structure having a circumferential outer wall, a front surface for receiving optical radiation and a rear surface opposite to the front surface having a circumferential outer wall surrounding the layered structure:

- positioning at least one electrical contact arrangement at the rear surface, and optionally at the front surface, or at both the front surface and the rear surface;

- extending a first semiconductor layer of a first conductivity type adjacent to the front surface and to the outer wall;

- positioning at least one electrical front contact in communication with the front surface and the first semiconductor layer, the at least one electrical front contact being connected to the at least one contact arrangement on the front surface, when the at least one contact arrangement is present on the front surface;

- extending a second semiconductor layer of a second conductivity type contiguous to the first semiconductor layer and to the outer wall, the conductivity types of the first semiconductor layer and the second semiconductor layer being of opposite polarity wherein the contact between the first semiconductor layer and the second semiconductor layer defines a pn-junction and a deple-

tion region formed across the pn-junction, the pn-junction and depletion region extending to the outer wall;

- placing at least one electrical rear contact in communication with the second semiconductor layer and the at least one electrical contact arrangement at the rear surface;

- applying a passivating layer of a first type to cover the part of the outer wall that is in contact with the pn-junction and depletion region;

- applying a passivating layer of a second type to cover the part of the outer wall that is in contact with the first semiconductor layer and to be contiguous to the passivating layer of the first type; and

- applying a passivating layer of a third type to cover the part of the outer wall that is in contact with the second semiconductor layer and to be contiguous to the passivating layer of the first type.

49. The method of claim 48, including the further steps of

- defining at least one aperture in the layered structure extending from the front surface to the rear surface and being bounded by an aperture wall, the aperture defining an electrical contact path connecting the at least one electrical front contact to the at least one electrical contact arrangement at the rear surface, the contact between the first semiconductor layer and the second semiconductor layer defining the pn-junction and depletion region formed across the pn-junction extending to include the aperture wall of the at least one defined aperture; and

- applying a passivating layer of the first type into the at least one defined aperture and covering the part of the aperture wall that is in contact with the pn-junction and depletion region; applying a passivating layer of the second type into the at least one defined aperture contiguous to the passivating layer of the first type and covering the part of the aperture wall contacting the first semiconductor layer; and applying a passivating layer of a third type into the at least one defined aperture contiguous to the passivating layer of the first type and covering the part of the aperture wall contacting the second semiconductor layer.

**50**. The method according to claim **48**, wherein the passivating layer of the first type is applied from either one of the front surface and the rear surface, followed by removal of the passivating layer of the first type from either one of the front and rear surface and from part of the layered structure substantially comprised by the first semiconductor layer and the second semiconductor layer, further applying the passivating layer of the second type from the first type and applying the passivating layer of the third type from the rear surface to be contiguous to the passivating layer of the first type.

**51**. The method according to claim **48**, wherein the passivating layer of the first type is applied from either one of the front surface and the rear surface, followed by removal of the passivating layer of the first type from either one of the front

and rear surface and from part of the layered structure substantially comprised by the first semiconductor layer and the second semiconductor layer, further applying the passivating layer of the second type from the front surface, such to be contiguous to the passivating layer of the first type and applying the passivating layer of the third type from the rear surface, such to be contiguous to the passivating layer of the first type, and either one of the passivating layer of the second and/or the third type is removed from either one of the front and rear surface.

**52.** The method according to claim **48**, wherein the photovoltaic device is of a front emitter design, the passivating layer of the first type is applied from either one of the front surface and the rear surface, followed by removal of the passivating layer of the first type from either one of the front and rear surface and from part of the layered structure substantially comprised by the first semiconductor layer and the second semiconductor layer, further applying the passivating layer of the second type from the first type and applying the passivating layer of the third type from the rear surface to be contiguous to the passivating layer of the first type, and the passivating layer of the second type is applied before the passivating layer of the third type.

**53**. The method according to claim **48**, wherein the photovoltaic device is of a rear emitter design, the passivating layer of the first type is applied from either one of the front surface and the rear surface, followed by removal of the passivating layer of the first type from either one of the front and rear surface and from part of the layered structure substantially comprised by the first semiconductor layer and the second semiconductor layer, further applying the passivating layer of the second type from the first type and applying the passivating layer of the third type from the rear surface to be contiguous to the passivating layer of the first type and applying the passivating layer of the third type is applied before the passivating layer of the second type.

**54**. The method according to claim **48**, wherein the passivating layers of the first and second type are integral, and the integral passivating layer is applied from the front surface after which the passivating layer of the third type is applied from the rear surface.

**55**. The method according to claim **48**, wherein the passivating layers of the first and third type are integral, and the integral passivating layer is applied from the rear surface after which the passivating layer of the second type is applied from the front surface.

**56**. A plurality of photovoltaic devices according to claim **31** arranged in stacked operative relationship with one another to form a multi junction photovoltaic device.

**57**. A plurality of photovoltaic devices according to claim **31** arranged in operative electrical connection to one another to form a photovoltaic module.

\* \* \* \* \*