(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5328276号

(P5328276)

(45) 発行日 平成25年10月30日(2013.10.30)

(24) 登録日 平成25年8月2日(2013.8.2)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/786 | (2006.01) | HO1L 29/78 | 613Z |

| HO1L 21/02  | (2006.01) | HO1L 27/12 | B    |

| HO1L 27/12  | (2006.01) | HO1L 27/04 | C    |

| HO1L 21/822 | (2006.01) | HO1L 27/04 | U    |

| HO1L 27/04  | (2006.01) | HO1L 29/78 | 626C |

請求項の数 4 (全 19 頁) 最終頁に続く

(21) 出願番号 特願2008-245254 (P2008-245254)

(22) 出願日 平成20年9月25日 (2008.9.25)

(65) 公開番号 特開2009-99965 (P2009-99965A)

(43) 公開日 平成21年5月7日 (2009.5.7)

審査請求日 平成23年8月1日 (2011.8.1)

(31) 優先権主張番号 特願2007-250356 (P2007-250356)

(32) 優先日 平成19年9月27日 (2007.9.27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100082669

弁理士 福田 賢三

(74) 代理人 100095337

弁理士 福田 伸一

(74) 代理人 100095061

弁理士 加藤 恒介

(72) 発明者 秋元 健吾

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 竹口 泰裕

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

単結晶シリコン基板上に、イットリウム酸化物を含む絶縁層、もしくはイットリウム酸化物とジルコニアム酸化物とを含む絶縁層を成膜し、

前記絶縁層に、熱処理を行って結晶化し、

水素を含むイオンを、前記絶縁層上より照射して、前記単結晶シリコン基板中に多孔質構造を有する脆化層を形成し、

前記絶縁層を島状に加工して保持容量部絶縁層を形成し、

前記単結晶シリコン基板上及び前記保持容量部絶縁層上に、保持容量部下部電極を形成し、

前記単結晶シリコン基板上、前記保持容量部絶縁層上及び前記保持容量部下部電極上に、第2の絶縁層を形成し、

前記第2の絶縁層上に、第1の絶縁層を形成し、

前記第1の絶縁層と支持基板とを貼りあわせた後、前記脆化層から前記単結晶シリコン基板の一部を分離することにより、

前記支持基板上に、

前記第1の絶縁層と、

前記第1の絶縁層上の前記第2の絶縁層と、

前記第2の絶縁層上の前記保持容量部下部電極と、

前記保持容量部下部電極上の前記保持容量部絶縁層と、

10

20

前記保持容量部絶縁層上及び前記第2の絶縁層上の、前記単結晶シリコン基板の一部である単結晶シリコン層と、を形成し、

前記単結晶シリコン層を島状に加工することにより、前記第2の絶縁層上に第1の島状単結晶シリコン層を形成するとともに、前記保持容量部絶縁層上に第2の島状単結晶シリコン層からなる保護層を形成し、

前記第1の島状単結晶シリコン層上に、ゲート絶縁膜及びゲート電極を形成し、

前記ゲート電極をマスクとして、前記第1の島状単結晶シリコン層に一導電型を付与する不純物元素を添加して、ソース領域及びドレイン領域を形成し、

前記保護層をエッチングして、前記保持容量部絶縁層の一部を露出させ、

前記第1の島状単結晶シリコン層、前記ゲート絶縁膜、前記ゲート電極を覆って、層間絶縁膜を形成し、10

前記層間絶縁膜上に、前記ソース領域及び前記ドレイン領域の一方と電気的に接続し、前記保持容量部絶縁層に接する配線を形成し、

前記配線の、前記保持容量部絶縁層に接する部分は、保持容量部上部電極となることを特徴とする半導体装置の作製方法。

#### 【請求項2】

単結晶シリコン基板上に、イットリウム酸化物を含む絶縁層、もしくはイットリウム酸化物とジルコニアム酸化物とを含む絶縁層を成膜し、

前記絶縁層に、熱処理を行って結晶化し、

水素を含むイオンを、前記絶縁層上より照射して、前記単結晶シリコン基板中に多孔質構造を有する脆化層を形成し、20

前記絶縁層を島状に加工して保持容量部絶縁層を形成し、

前記シリコン基板上及び前記保持容量部絶縁層上に、保持容量部下部電極を形成し、前記シリコン基板上、前記保持容量部絶縁層上及び前記保持容量部下部電極上に、第2の絶縁層を形成し、

前記第2の絶縁層上に、第1の絶縁層を形成し、

前記第1の絶縁層と支持基板とを貼りあわせた後、前記脆化層から前記単結晶シリコン基板の一部を分離することにより、

前記支持基板上に、

前記第1の絶縁層と、30

前記第1の絶縁層上の前記第2の絶縁層と、

前記第2の絶縁層上の前記保持容量部下部電極と、

前記保持容量部下部電極上の前記保持容量部絶縁層と、

前記保持容量部絶縁層上及び前記第2の絶縁層上の、前記単結晶シリコン基板の一部である単結晶シリコン層と、を形成し、

前記単結晶シリコン層を島状に加工することにより、前記第2の絶縁層上に第1の島状単結晶シリコン層を形成するとともに、前記保持容量部絶縁層上に第2の島状単結晶シリコン層を形成し、

前記第1の島状単結晶シリコン層上に、ゲート絶縁膜及びゲート電極を形成し、

前記ゲート電極をマスクとして、前記第1の島状単結晶シリコン層に一導電型を付与する不純物元素を添加して、ソース領域及びドレイン領域を形成するとともに、前記第2の島状単結晶シリコン層に一導電型を付与する不純物元素を添加して保持容量部上部電極を形成し、40

前記第1の島状単結晶シリコン層、前記ゲート絶縁膜、前記ゲート電極、及び前記保持容量部上部電極を覆って、層間絶縁膜を形成し、

前記層間絶縁膜上に、前記ソース領域及び前記ドレイン領域の一方と、前記保持容量部上部電極とを接続する配線を形成することを特徴とする半導体装置の作製方法。

#### 【請求項3】

請求項1または請求項2において、前記単結晶シリコン基板は、面方位が{100}、{110}、{111}のいずれかであることを特徴とする半導体装置の作製方法。50

**【請求項 4】**

請求項1乃至請求項3のいずれか一において、前記熱処理の温度は 750 以上 1400 以下であることを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は半導体装置及びその作製方法に関する。特に結晶性半導体基板から半導体層を薄片化して異種基板に接合する S O I (Silicon On Insulator) 構造を有する基板に関する。特に貼り合わせ S O I 技術に関するものであって、ガラス等の絶縁表面を有する基板に単結晶もしくは多結晶の半導体層を接合させた S O I 基板の製造方法に関する。また、このような S O I 構造を有する表示装置もしくは半導体装置に関する。10

**【背景技術】****【0002】**

単結晶半導体のインゴットを薄く切断して作製されるシリコンウエハに代わり、絶縁層の上に薄い単結晶半導体層を設けたシリコン・オン・インシュレータ (Silicon On Insulator) と呼ばれる半導体基板 (S O I 基板) が開発されており、マイクロプロセッサなどを製造する際の基板として普及しつつある。これは、S O I 基板を使った集積回路はトランジスタのドレインと基板間における寄生容量を低減し、半導体集積回路の性能を向上させ、低消費電力化を図るものとして注目されているからである。20

**【0003】**

S O I 基板を製造する方法としては、水素イオン注入剥離法が知られている（例えば、特許文献 1 参照）。水素イオン注入剥離法は、シリコンウエハに水素イオンを注入することによって表面から所定の深さに微小気泡層を形成し、該微小気泡層を劈開面として、別のシリコンウエハに薄いシリコン層 (S O I 層) を接合する。さらに S O I 層を剥離する熱処理を行うことに加え、酸化性雰囲気下での熱処理により S O I 層に酸化膜を形成した後に該酸化膜を除去し、次に 1000 以上 1300 以下の還元性雰囲気下で熱処理を行って接合強度を高める必要があるとされている。

**【0004】**

一方、ガラスなどの絶縁基板に S O I 層を形成しようとする試みもなされている。ガラス基板上に S O I 層を形成した S O I 基板の一例として、水素イオン注入剥離法を用いて、コーティング膜を有するガラス基板上に薄い単結晶シリコン層を形成したものが知られている（特許文献 2 及び特許文献 3 参照）。この場合にも、単結晶シリコン片に水素イオンを注入することによって表面から所定の深さに微小気泡層を形成し、ガラス基板と単結晶シリコン片を張り合わせ後に、微小気泡層を劈開面としてシリコン片を剥離することで、ガラス基板上に薄いシリコン層 (S O I 層) を形成している。30

**【0005】**

ガラス基板などの絶縁基板上に薄膜トランジスタ (Thin Film Transistor (TFT)) の構造として、ガラス基板上に、下地絶縁膜、活性層、ゲート絶縁膜、ゲート電極、層間絶縁膜、配線を形成した構造が挙げられる。TFT の応答速度を上げるために、TFT 全体のデザインルールを縮小することが行われている。40

**【特許文献 1】米国特許第 6372609 号****【特許文献 2】特開平 11-163363 号公報****【特許文献 3】米国特許第 7119365 号****【発明の開示】****【発明が解決しようとする課題】****【0006】**

集積回路のデザインルールを縮小して集積度を高くする場合、容量部の面積を縮小することが有効である。容量部の面積を縮小しつつ必要な容量を確保するためには容量素子の誘電体層を薄くする方法が挙げられる。しかし、誘電体層を薄くするとリーク電流が増えて50

容量素子の特性が低下してしまう。そこで、誘電体層を薄く形成することなく必要な容量を確保することで、容量部の面積を縮小することを目的の一とする。

#### 【0007】

また、ガラス基板は、概ね700以上 の高温熱処理を行うことができない。そのため、ガラス基板上に容量素子の誘電体層を成膜し、高温処理することが困難であった。そこで、本発明は耐熱温度の低い基板上であっても高温処理が必要な誘電体層を形成することを目的の一とする。

#### 【課題を解決するための手段】

#### 【0008】

本発明は、容量部に、比誘電率が10以上の材料、例えばイットリウム酸化物、若しくはイットリウム酸化物とジルコニウム酸化物とを含む誘電体層を有する半導体装置である。10

#### 【0009】

本発明の半導体装置は、保持容量部の絶縁膜を単結晶シリコン基板上に成膜し、熱処理して形成する。前記保持容量部の絶縁膜は単結晶シリコン上の特有の結晶成長を得、比誘電率を高めることで、保持容量部の面積を小さくできる。また、保持容量部の絶縁膜の膜厚を小さくせずに設計できるため、電荷保持に優れた保持容量部を形成することができる。また本発明の半導体装置の一は、前記保持容量部の絶縁膜を単結晶シリコン基板から分離し、支持基板上に設けることを特徴とする。また本発明の半導体装置の一は、前記保持容量部の絶縁膜は、支持基板上に設けられた第1の絶縁層上の、第2の絶縁層に埋め込まれていることを特徴とする。20

#### 【0010】

前記保持容量部の絶縁膜として、イットリウム酸化物、もしくはイットリウム酸化物に化学的安定のためジルコニウム酸化物を混合した材料を用いる。ここで、本発明の前記保持容量部の絶縁膜は、単結晶シリコン上にスパッタもしくはCVDにて成膜され、750以上にて熱処理された後、ガラス基板に張り合わせられる。さらに前記保持容量部の絶縁膜に接する電極と相まって、信頼性の高い保持容量という機能を実現する。

#### 【0011】

さらに前記保持容量部の絶縁膜に接する電極は、高融点金属以外に、前記単結晶シリコン層に導電性を付与する不純物を添加したもの用いてよい。30

#### 【0012】

また単結晶シリコン基板の面方位については、{100}、{110}、{111}の何れでもよい。

#### 【0013】

本明細書では、イットリウム酸化物とジルコニウム酸化物とを含む材料をYSZ(Yttrium Stabilized Zircon)と呼び、イットリウム酸化物とジルコニウム酸化物とを含む膜をYSZ膜と呼ぶ。

#### 【発明の効果】

#### 【0014】

容量部に、比誘電率が10以上の材料、例えばイットリウム酸化物、若しくはイットリウム酸化物とジルコニウム酸化物とを含む誘電体層を設けることで集積回路の容量部の面積を縮小することができる。40

#### 【0015】

単結晶シリコン基板から分離された結晶性シリコン層を支持基板へ接合する以前に、高誘電膜であるYSZ膜を単結晶シリコン基板上に形成、熱処理を行うことにより、比誘電率がより高く、集積回路の容量部の面積を縮小することができる半導体装置を得ることができる。特に所望の半導体装置を、YSZ膜に有効な熱処理温度すなわち750に比べて低い耐熱温度の支持基板上に作製したい場合でも、上記手段で達成することができる。また、保持容量部の絶縁膜の膜厚を小さくせずに設計できるため、電荷保持に優れた保持容量部を形成することができる。50

**【発明を実施するための最良の形態】****【0016】**

本発明の発明を実施するための最良の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細をさまざまに変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す記載内容に限定して解釈されるものではない。以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いることとする。

**【0017】****(実施の形態1)**

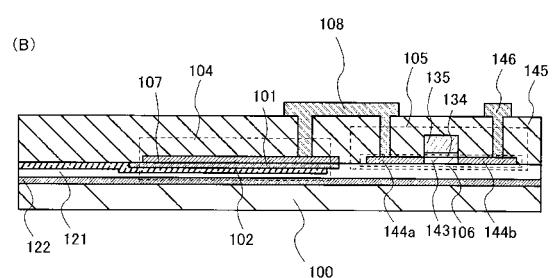

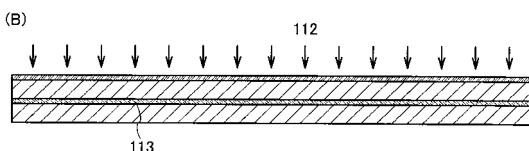

本発明で形成される、半導体装置の構造について、図1(A)～図1(B)を用いて説明する。10

**【0018】**

図1(A)は、支持基板100上に、イットリウム酸化物を含む、もしくはYSZを含む保持容量部絶縁層101と、保持容量部下部電極102と、配線103が形成されている。配線103は、保持容量部上部電極も兼ねている。保持容量部下部電極102が保持容量部絶縁層101に接する部分と、前記保持容量部絶縁層101が配線103に接する部分が、支持基板の上方からみて重なっている部分が保持容量部104となる。また同じ支持基板100に、TFT105が形成される。このTFT105は、結晶性シリコン層を活性層106とする。すなわち保持容量部下部電極102が保持容量部絶縁層101に接する面と、前記保持容量部絶縁層101が配線103に接する面は、一致する。尚、本明細書において一致とは、概略一致を含む。20

**【0019】**

図1(A)の配線103は、TFTのソース領域及びドレイン領域と電気的に接続し、かつ保持容量部絶縁層101に接しているが、回路の設計上かならずしも一つの配線103が両条件を満たす必要はない。

**【0020】**

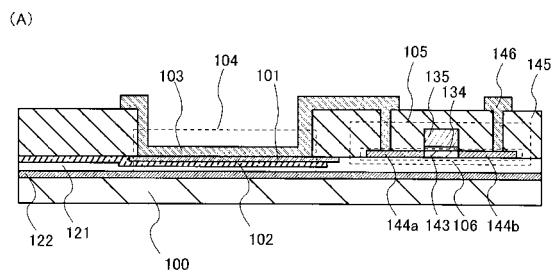

一方、図1(B)は、図1(A)と似ているものの、保持容量部絶縁層101に接して、シリコン層からなる保持容量部上部電極107が形成されている。さらに、前記保持容量部上部電極107は、配線108と接続されている。このとき、保持容量部絶縁層101と保持容量部下部電極102とが接している部分と、保持容量部絶縁層101と前記保持容量部上部電極107とが接している部分が、支持基板の上方からみて重なっている部分が保持容量部104となる。30

**【0021】**

図1(B)の配線108は、TFTのソース領域及びドレイン領域として機能する高濃度不純物領域144a、144bと電気的に接続し、かつ保持容量部上部電極107とに電気的に接続しているが、回路の設計上かならずしも一つの配線108が両方に接続する必要はない。

**【0022】**

本発明に用いる支持基板100の材料としては400以上の耐熱性があるものが望ましい。なぜなら前記結晶性シリコン層を支持基板へ接合する工程にて、400以上600以下の熱処理がされるからである。40

**【0023】**

支持基板100は絶縁性を有するものまたは絶縁表面を有するものであり、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われるガラス基板(「無アルカリガラス基板」とも呼ばれる)が適用される。

**【0024】**

すなわち、支持基板100として、熱膨張係数が $25 \times 10^{-7}$ /以上 $50 \times 10^{-7}$ /以下(好ましくは、 $30 \times 10^{-7}$ /から $40 \times 10^{-7}$ /)であって歪み点が580から680(好ましくは、600から680)のガラス基板を適用することができる。その他に石英基板、セラミック基板、表面が絶縁膜で被覆された金属基板50

なども適用可能である。

**【0025】**

TFTの活性層106は、単結晶シリコン基板を薄片化して形成されるものであり、すなわちLTSS層(Low Temperature Single crystal Semiconductor)から形成される。例えば、単結晶半導体基板として単結晶シリコン基板を用いた場合、単結晶シリコン基板の所定の深さに水素またはフッ素が添加されるようイオン照射し、その後熱処理を行って表層の単結晶シリコン層を剥離する方法で形成することができる。また、ポーラスシリコン(多孔性シリコン)上に単結晶シリコンをエピタキシャル成長させた後、ポーラスシリコン層をウォータージェットで劈開して剥離する方法を適用しても良い。LTSS層の厚さは5nm以上500nm以下、好ましくは10nm以上200nm以下の厚さである。10

**【0026】**

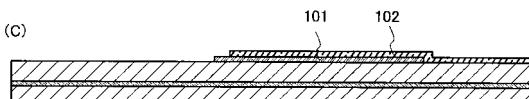

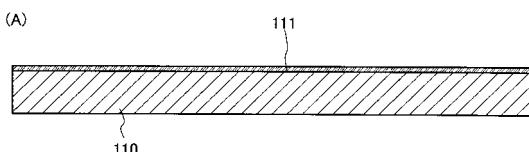

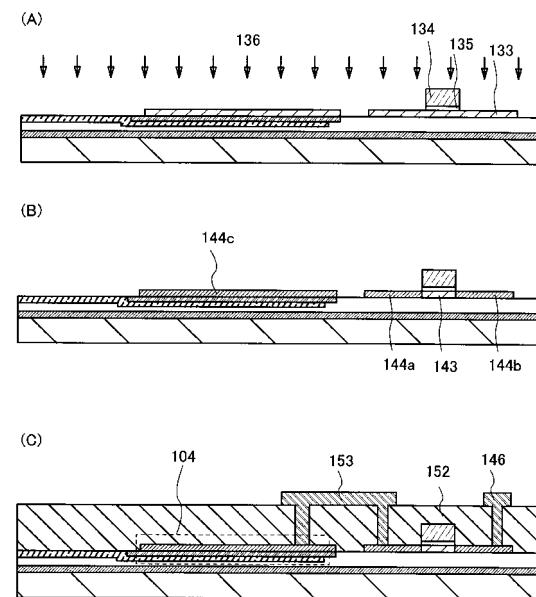

図1(A)に示すSOI構造を有する基板の作製方法について、図2(A)～図2(D)、図3(A)～図3(D)、図4(A)～図4(D)、図5(A)～図5(C)、を用いて説明する。

**【0027】**

まず単結晶シリコン基板110の表面に、イットリウム酸化物を含む絶縁層、もしくはイットリウム酸化物とジルコニウム酸化物とを含む絶縁層を形成する。ここではYSZ膜111を成膜する。ターゲットはイットリウム酸化物を92mol%、ジルコニウム酸化物を8mol%にて混合したものを用いて、スパッタ法にて、成膜ガスをアルゴン(Ar)及び酸素(O<sub>2</sub>)、成膜圧力0.4Paとして、10nm以上200nm以下、ここでは50nmの膜厚で成膜する(図2(A)参照)。尚、前記成膜時の基板温度は高いほど良いが、本発明においては基板温度が室温でも良い。また上記ターゲットに他の添加物が入っていても、結晶性が損なわれなければ本発明の目的は達成される。20

**【0028】**

また、上記ではスパッタ法にて成膜しているが、CVD法でも良い。CVD成膜の例としてはジルコニウムおよびイットリウムのDPM錯体を原料とするものが挙げられる。

**【0029】**

イットリウム酸化物、もしくはYSZは、耐熱性、化学的安定性に優れ、また結晶性シリコンを下地としたとき、特定の面方位に結晶成長しやすい特徴がある。また結晶性シリコンには、表面に非結晶状態の自然酸化膜が形成されるが、イットリウム酸化物、もしくはYSZの前記結晶成長はこれに影響されにくい。また、YSZは熱処理により比誘電率が高くなる特徴がある。30

**【0030】**

単結晶シリコンを基板として前記保持容量部の絶縁膜を成膜し熱処理する工程、その後、前記保持容量部の絶縁膜を結晶性シリコン層と共に支持基板すなわちガラス基板に接合する工程、という順にて進める必要がある。なぜなら、前記イットリウム酸化物、もしくはYSZの前記結晶成長は、750以上の熱処理が必要だからである。

**【0031】**

さらに、750以上1400以下の範囲、好ましくは850以上950以下の範囲にて加熱処理することにより、YSZ膜111は結晶化し、比誘電率が向上する。生産性、膜特性を考慮し、ここでは900で1hr熱処理する。40

**【0032】**

その後、清浄化された単結晶シリコン基板110の表面から電界で加速されたイオン112を所定の深さに添加されるようイオン照射して脆化層113を形成する(図2(B)参照)。単結晶シリコン基板110に形成される脆化層113の深さは、イオンの加速エネルギーとイオンの入射角によって制御する。単結晶シリコン基板110の表面からイオンの平均進入深さに近い深さ領域に脆化層113が形成される。例えば、LTSS層の厚さは5nm以上500nm以下、好ましくは10nm以上200nm以下の厚さであり、イオンを照射する際の加速電圧はこのような厚さを考慮して行われる。イオンの照射は50

オンドーピング装置を用いて行なうことが好ましい。すなわち、原料ガスをプラズマ化して生成された複数のイオン（イオン種）を質量分離しないで照射するドーピング方式を用いる。

#### 【0033】

本発明を実施するための最良の形態の場合、一または複数の同一の原子から成る質量数の異なるイオンを照射することが好ましい。イオンドーピングは、加速電圧 $10\text{ keV}$ から $100\text{ keV}$ 、好ましくは $30\text{ keV}$ から $80\text{ keV}$ 、ドーザ量は $1 \times 10^8 / \text{cm}^2$ から $4 \times 10^8 / \text{cm}^2$ 、ビーム電流密度が $2\text{ }\mu\text{A}/\text{cm}^2$ 以上、好ましくは $5\text{ }\mu\text{A}/\text{cm}^2$ 以上、より好ましくは $10\text{ }\mu\text{A}/\text{cm}^2$ 以上とすれば良い。

#### 【0034】

水素イオンを照射する場合には、 $\text{H}^+$ 、 $\text{H}_2^+$ 、 $\text{H}_3^+$ イオンを含ませると共に、 $\text{H}_3^+$ イオンの割合を高めておくことが好ましい。水素イオンを照射する場合には、 $\text{H}^+$ 、 $\text{H}_2^+$ 、 $\text{H}_3^+$ イオンを含ませると共に、 $\text{H}_3^+$ イオンの割合を高めておくと照射効率を高めることができ、照射時間を短縮することができる。それにより、単結晶シリコン基板110に形成される脆化層113の領域には $1 \times 10^{20} / \text{cm}^3$ （好ましくは $5 \times 10^{20} / \text{cm}^3$ ）以上の水素を含ませることが可能である。

#### 【0035】

単結晶シリコン基板110中において、局所的に高濃度の水素照射領域を形成すると、結晶構造が乱されて微小な空孔が形成され、脆化層113を多孔質構造とすることができる。この場合、比較的低温の熱処理によって脆化層113に形成された微小な空洞の体積変化が起こり、脆化層113に沿って劈開することにより薄いLTSS層を形成することができる。

#### 【0036】

イオンを質量分離して単結晶シリコン基板110に照射しても、上記と同様に脆化層113を形成することができる。この場合にも、質量数の大きいイオン（例えば $\text{H}_3^+$ イオン）を選択的に照射することは上記と同様な効果を奏すこととなり好ましい。

#### 【0037】

イオンを生成するガスとしては水素の他に重水素を選択することも可能である。このようなイオンを単結晶シリコン基板110に照射することで、微小な空孔を形成することができ上記と同様な脆化層113を単結晶シリコン基板110中に設けることができる。

#### 【0038】

脆化層113の形成に当たってはイオンを高ドーザ条件で照射する必要があり、単結晶シリコン基板110の表面が粗くなってしまう場合がある。そのためイオンが照射される表面に緻密な膜を設けておいても良い。例えば、窒化シリコン膜もしくは酸素を含むは窒化シリコン膜などによりイオン照射に対する保護膜を $50\text{ nm}$ 以上 $200\text{ nm}$ 以下の厚さで設けておいても良い。

#### 【0039】

次いでYSZ膜111を選択的に除去して、保持容量部絶縁層101を所望の形状に形成する（図2（C）参照）。前記形状に形成する方法としては、希ガスあるいはハロゲンを用いてドライエッチングする例が挙げられる。他の方法としては、化学的機械的研磨（Chemical Mechanical Polishing：CMP）を用いるものが挙げられる。この場合、予め単結晶シリコン基板110の表面に酸化珪素膜を形成し、保持容量部絶縁層101を形成したい部分を選択的に除去し、YSZ膜111を成膜後にCMPにて加工する方法をとる。

#### 【0040】

次いでタンゲステン（W）、モリブデン（Mo）、チタン、もしくはこれらを含む材料からなる保持容量部下部電極102を形成する（図2（C）参照）。この場合も、スパッタ成膜、およびハロゲン元素を加えたガスを用いてドライエッチングにて選択的に除去する。この保持容量部下部電極102と保持容量部絶縁層101とが重なる部分と、保持容

10

20

30

40

50

量部絶縁層 101 と後の工程で形成される保持容量部の上部電極と重なる部分とが、概略一致する形状であれば、支持基板上に保持容量を効果的に配置することができる。

#### 【0041】

前記保持容量部絶縁層 101 を所望の形状に形成する工程、及び保持容量部下部電極 102 を形成する工程は、脆化層 113 を形成する工程の後に行う。なぜなら、脆化層 113 を形成する工程にてイオンを所定の深さに照射する際、表面から均一の深さに添加するためには、表面が一様でなければならないからである。

#### 【0042】

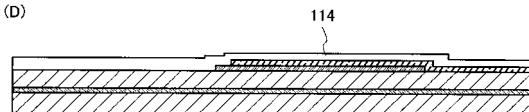

次いで絶縁膜 114 を形成する（図 2（D）参照）。前記絶縁膜 114 として、窒素を含む酸化珪素膜を膜厚 100 nm で成膜し、さらに酸素を含む窒化珪素膜を膜厚 300 nm で成膜した積層膜を形成する。

10

#### 【0043】

さらに絶縁膜 114 を、CMP を用いて研磨し、表面が平滑な絶縁膜 121 を得る（図 3（A）参照）。絶縁膜 114 は、その下に保持容量部下部電極 102 が形成されているので、段差が存在しているが、研磨によって段差を消失させる。

#### 【0044】

次に、単結晶シリコン基板 110 の支持基板 100 と接合を形成する面に接合層 122 を形成する（図 3（B）参照）。接合層 122 は平滑面を有する層、あるいは親水性表面を有する層、あるいは平滑面と親水性表面とを有する層とする。このような表面を形成可能なものとして、化学的な反応により形成される絶縁層が好ましい。例えば、熱的または化学的な反応により形成される酸化半導体膜が適している。主として化学的な反応により形成される膜であれば表面の平滑性を確保できるからである。

20

#### 【0045】

接合層 122 の下層が平滑な場合、親水性を確保するための膜厚の下限は 1 nm である。接合層 122 の下層に凹凸があれば接合層を厚くすることで平坦性を確保できるが、接合層 122 が厚すぎると接合層 122 自体に凹凸が生じる。そのため接合層 122 は 1 nm 以上 500 nm 以下の厚さで設けられる。

#### 【0046】

接合層 122 としてケミカルオキサイドを用いる場合には 1 nm から 10 nm の厚さであれば良い。また、好適には化学気相成長法により堆積される酸化シリコンを接合層 122 とすることができます。この場合、有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。

30

#### 【0047】

有機シランガスとしては、珪酸エチル（TEOS：化学式 Si(OCH<sub>3</sub>)<sub>4</sub>）、テトラメチルシリラン（TMS：化学式 Si(CH<sub>3</sub>)<sub>4</sub>）、テトラメチルシリクロテトラシロキサン（TMCTS）、オクタメチルシリクロテトラシロキサン（OMCTS）、ヘキサメチルジシラザン（HMDS）、トリエトキシシラン（SiH(OCH<sub>3</sub>)<sub>3</sub>）、トリスジメチルアミノシリラン（SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>）等のシリコン含有化合物を用いることができる。

#### 【0048】

単結晶シリコン基板 110 の支持基板 100 と接合を形成する面に設けられた接合層 122 は、支持基板 100 の表面と密接することで、室温であっても接合をすることが可能である。異種材料である支持基板 100 と接合層 122 を接合するには表面を清浄化する。支持基板 100 と接合層 122 の互いに清浄化された表面を密接させると表面間引力により接合が形成される（図 3（C）参照）。

#### 【0049】

さらに、支持基板 100 の表面に複数の親水基を付着させると、接合を形成するのにより好ましい態様となる。例えば、支持基板 100 の表面を酸素プラズマ処理もしくはオゾン処理して親水性にすることが好ましい。

#### 【0050】

10

20

30

40

50

このように支持基板 100 の表面を親水性にする処理を加えた場合には、表面の水酸基が作用して水素結合により接合が形成される。さらに清浄化された表面同士を密接させて接合を形成したものに対して、室温以上の温度で加熱すると接合強度を高めることができる。

#### 【0051】

良好な接合を形成するために、表面を活性化しても良い。例えば、接合を形成する面に原子ビームもしくはイオンビームを照射する。原子ビームもしくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビームもしくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射もしくはラジカル処理を行う。このような表面処理により 200 以上 400 以下の温度であっても異種材料間の接合強度を高めることが可能となる。

10

#### 【0052】

単結晶シリコン基板 110 と支持基板 100 を重ね合わせた状態で第 1 の熱処理を行う。第 1 の熱処理により支持基板 100 上に薄いシリコン層 (LTSS 層) を残して単結晶シリコン基板 110 の分離を行う。第 1 の熱処理は接合層 122 の成膜温度以上で行うことが好ましく、400 以上 600 未満の温度で行うことが好ましい。この温度範囲で熱処理を行うことで脆化層 113 に形成された微小な空孔に体積変化が起こり、単結晶シリコン基板 110 と支持基板 100 とを脆化層 113 にて分離することができる。接合層 122 は支持基板 100 と接合しているので、支持基板 100 上には単結晶シリコン基板 110 と同じ結晶性の LTSS 層 123 が固定された形態となる（図 3 (D) 参照）。

20

#### 【0053】

次に支持基板 100 に LTSS 層が接合された状態で第 2 の熱処理を行う。第 2 の熱処理は、第 1 の熱処理温度よりも高い温度であって支持基板 100 の歪み点を超えない温度で行うことが好ましい。或いは、第 1 の熱処理と第 2 の熱処理は同じ温度であっても、第 2 の熱処理の処理時間を長くすることが好ましい。熱処理は、熱伝導加熱、対流加熱または輻射加熱などにより支持基板 100 及び / または LTSS 層 123 が加熱されるようすれば良い。熱処理装置としては電熱炉、ランプアニール炉などを適用することができる。第 2 の熱処理は多段階に温度を変化させて行っても良い。また瞬間熱アニール (RTA) 装置を用いても良い。RTA 装置によって熱処理を行う場合には、基板の歪み点近傍またはそれよりも若干高い温度に加熱することもできる。

30

#### 【0054】

第 2 の熱処理を行うことで LTSS 層 123 に残留する応力を緩和することができる。すなわち、第 2 の熱処理は、支持基板 100 と LTSS 層 123 の膨張係数の違いにより生じる熱歪みを緩和する。また、第 2 の熱処理は、イオンを照射することによって結晶性が損なわれた LTSS 層 123 の結晶性を回復させるためにも有効である。さらに、第 2 の熱処理は、単結晶シリコン基板 110 を支持基板 100 と接合させた後、第 1 の熱処理によって分割する際に生じる LTSS 層 123 のダメージを回復させることにも有効である。また、第 1 の熱処理と第 2 の熱処理を行うことで水素結合を、より強固な共有結合に変化させることができる。

#### 【0055】

40

LTSS 層 123 の表面をより平坦化する目的で化学的機械研磨 (CMP) 処理を行っても良い。CMP 処理は第 1 の熱処理後もしくは第 2 の熱処理後に行うことができる。尤も、第 2 の熱処理前に行えば、LTSS 層 123 の表面を平坦化すると共に CMP 処理によって生じる表面の損傷層を第 2 の熱処理で修復することができる。

#### 【0056】

いずれにしても、第 1 の熱処理と第 2 の熱処理を本形態のように組み合わせて行うことで、ガラス基板のような熱的に脆弱な支持基板の上に、結晶性に優れた結晶シリコン層を設けることが可能となる。

#### 【0057】

次いで LTSS 層 123 を薄膜化して所望の膜厚の LTSS 層 124 を形成する（図 3

50

(E) 参照)。薄膜化の方法は、C M P法、あるいはエッティング法等が挙げられる。本発明を実施するための最良の形態では、ドライエッティングを用いて薄膜化する。

#### 【0058】

L T S S層124の膜厚は5nmから500nm、好ましくは10nmから200nm、より好ましくは10nmから60nmの厚さとすることが好ましい。L T S S層124の厚さは、脆化層113の深さを制御すること、及び薄膜化の条件により適宜設定できる。本発明を実施するための最良の形態では、ドライエッティングにより、L T S S層124を50nmの膜厚に形成する。

#### 【0059】

L T S S層124にはしきい値電圧を制御するために、ホウ素、アルミニウム、ガリウムなどのp型不純物元素を添加する。例えば、p型不純物元素としてホウ素を $1 \times 10^{-6} \text{ cm}^{-3}$ 以上 $1 \times 10^{-8} \text{ cm}^{-3}$ 以下の濃度で添加されていても良い。

10

#### 【0060】

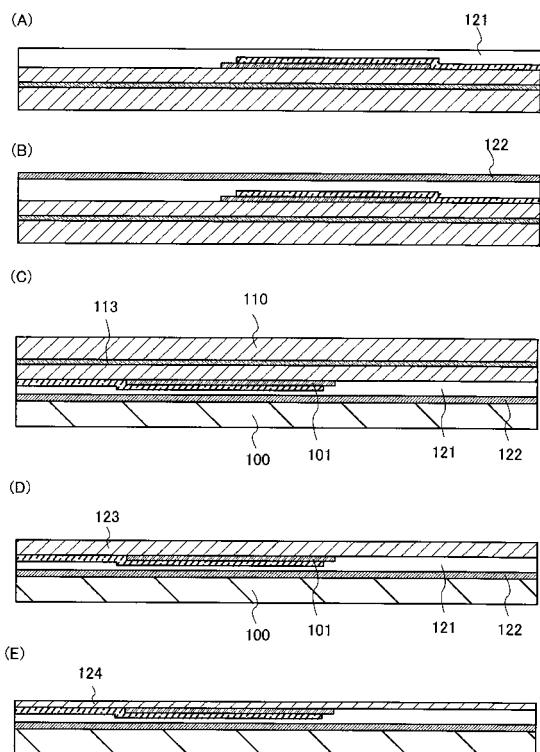

L T S S層124上にマスク131を形成し、マスク131を用いてL T S S層124をエッティングする(図4(A)参照)。活性層の配置に合わせて島状に分離した島状単結晶シリコン層133及び保持容量部絶縁層101の保護層109を形成する(図4(B)参照)。

#### 【0061】

上記の工程で形成された保持容量部下部電極102と保護層109は、互いに接触しないよう形成する。保護層は単結晶シリコンで形成されることから、保護層加工時にエッティング残りがあった場合、上部電極と下部電極が接触し電荷を逃がすことを防ぐためである。

20

#### 【0062】

そして、島状単結晶シリコン層133上に、ゲート絶縁膜134、ゲート電極135を形成する(図4(C)参照)。本発明を実施するための最良の形態では、ゲート絶縁膜134とゲート電極135と同じ幅にしたが、低濃度不純物領域を形成するために、ゲート電極135の幅よりも大きくしてもよい。

#### 【0063】

ゲート絶縁膜134は、酸化珪素膜、窒化珪素膜、窒素を含む酸化珪素膜、酸素を含む窒化珪素膜のいずれかを用いて形成すればよく、本発明を実施するための最良の形態では、酸化珪素膜を10nm以上100nm以下の膜厚で成膜したものを用いて、ゲート絶縁膜134を形成する。

30

#### 【0064】

ゲート電極135は、タンゲステン(W)、タンタル(Ta)、チタン(Ti)、アルミニウム(Al)、もしくはそれらの窒化物、もしくはその組み合わせ等を用いて形成すればよい。

#### 【0065】

次いで、ゲート電極135をマスクとして、島状単結晶シリコン層133に一導電型を付与する不純物元素136を導入する(図4(D)参照)。このとき保護層109にも不純物元素136が添加される。不純物元素136としてn型を付与する不純物元素を用いた場合は、n型を付与する不純物元素として、リン(P)、ヒ素(As)が挙げられる。また不純物元素136としてp型を付与する不純物元素を用いた場合は、p型を付与する不純物元素としては、ホウ素(B)が挙げられる。

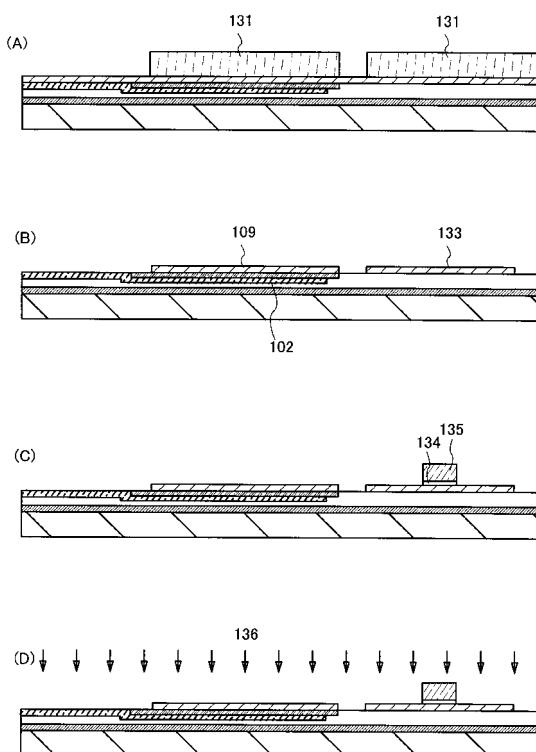

40

#### 【0066】

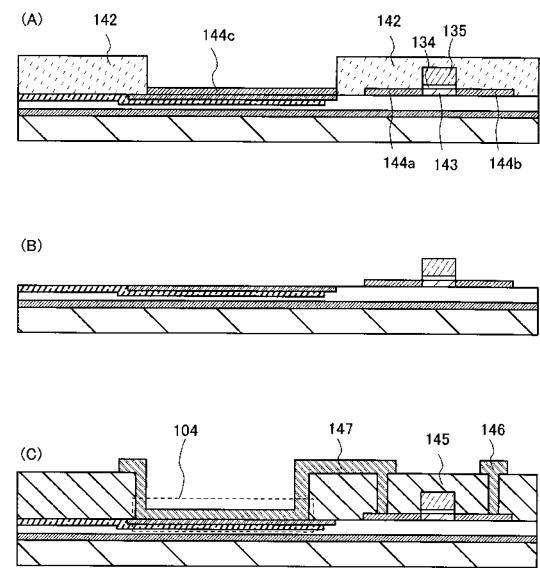

一導電型を付与する不純物元素136の添加により、ゲート電極135の下の領域にチャネル形成領域143、ゲート電極135及びゲート絶縁膜134に覆われていない領域に、ソース領域及びドレイン領域である高濃度不純物領域144a、144b、及び高濃度不純物領域144cが形成される(図5(A)参照)。

#### 【0067】

本発明を実施するための最良の形態では、例えばn型の不純物元素136としてリン(

50

P)を添加する。これにより高濃度不純物領域144a～144cには、リンが $1 \times 10^{19}$ atoms/cm<sup>3</sup>以上 $1 \times 10^{21}$ atoms/cm<sup>3</sup>以下(代表的には $1 \times 10^{20}$ atoms/cm<sup>3</sup>以上 $5 \times 10^{20}$ atoms/cm<sup>3</sup>以下)の濃度で含まれることとなる。

#### 【0068】

次いで保持容量部絶縁層101上の保護層109以外を覆うマスク142を形成し、高濃度不純物領域144cをエッチングして除去し、保持容量部絶縁層101を露出させる(図5(B)参照)。

#### 【0069】

図5(B)までの作製工程を行った後、層間絶縁膜145を形成する。層間絶縁膜145はBPSG(Boron Phosphorus Silicon Glass)膜を成膜するか、ポリイミドに代表される有機樹脂を塗布して形成する。層間絶縁膜145中に開口部を形成し、配線146及び配線147を形成する(図5(C)参照)。なお、配線147は、図1(A)の配線103に相当する。

#### 【0070】

配線146及び配線147は、活性層である島状単結晶シリコン層133及び保持容量部絶縁層101と接触抵抗の低い材料を用いて形成すればよい。本発明を実施するための最良の形態では、配線146及び配線147をアルミニウムもしくはアルミニウム合金で形成する。また上層と下層にはバリアメタルとしてモリブデン、クロム、チタンなどの金属膜で形成してもよい。

#### 【0071】

また配線146は高濃度不純物領域144bと電気的に接続されており、配線147は高濃度不純物領域144aと電気的に接続し保持容量部絶縁層101と一部重なっている。前記配線147と、保持容量部絶縁層101と、容量部下部電極102が重なった部分が、保持容量部104を形成する。

#### 【0072】

以上、図1(A)の作製工程について説明したが、以下に図1(B)の作製工程、すなわち前記保護層109を除去せず、保持容量部の上部電極として用いる構造の作製方法について図6(A)～図6(C)を用いて説明する。なお図6(A)～図6(C)において、図5(A)～図5(C)と同じものは同じ符号で示している。

#### 【0073】

まず、図3(A)～図4(C)で説明した作製方法により、島状単結晶シリコン層133上に、ゲート絶縁膜134、ゲート電極135を設けるところまで作製する。図4(D)の工程同様、ゲート電極135をマスクとして、島状単結晶シリコン層133に一導電型を付与する不純物元素136を導入する(図6(A)参照)。このとき保護層109にも不純物元素136が添加される。この保護層109の、保持容量部絶縁層101と一部重なっている部分は高濃度不純物領域144cになり、保持容量部上部電極としての機能をもつ。高濃度不純物領域144cは十分抵抗が低くなれば良く、一例ではリンが $1 \times 10^{20}$ atoms/cm<sup>3</sup>以上 $1 \times 10^{21}$ atoms/cm<sup>3</sup>以下の濃度で含まれればよい。

#### 【0074】

その後、層間絶縁膜152を形成する。層間絶縁膜152はBPSG(Boron Phosphorus Silicon Glass)膜を成膜するか、ポリイミドに代表される有機樹脂を塗布して形成する。層間絶縁膜152中に開口部を形成し、配線146及び配線153を形成する(図6(C)参照)。なお、配線153は、図1(B)配線108に相当する。

#### 【0075】

配線146及び配線153は、活性層である島状単結晶シリコン層133及び保持容量部上部電極として機能する高濃度不純物領域144cと接触抵抗の低い材料を用いて形成すればよい。

10

20

30

40

50

## 【0076】

また配線 146 は高濃度不純物領域 144b と電気的に接続されており、配線 153 は高濃度不純物領域 144a と電気的に接続し保持容量部絶縁層 101 と一部重なっている。高濃度不純物領域 144c と、保持容量部絶縁層 101 と、保持容量部下部電極 102 が重なった部分が、保持容量部 104 になる。

## 【0077】

図 1 (A) 及び図 5 (C) の構造を得るために、高濃度不純物領域 144c をプラズマエッティングする際、保持容量部絶縁層 101 の膜厚が減る、もしくは保持容量部絶縁層 101 自体にダメージを受け非結晶化する可能性がある。そこで、保持容量部の電極として図 5 (C) に示す配線 147 (図 1 (A) 配線 103 に相当する) を用いることにより、電極の抵抗が小さく高速動作が可能となる点で有利となる。また図 1 (B) 及び図 6 (C) の構造を得るために、保持容量部の電極として高濃度不純物領域 144c (図 1 (A) 保持容量部上部電極 107 に相当する) を用いており、この高濃度不純物領域 144c は図 5 (C) の配線 147 より抵抗が高いため、容量としての動作速度は小さくなる。図 5 (A) に示すような高濃度不純物領域 144c をプラズマエッティングするためのマスク 142 が不要になるため、工程数を減らすことができ、さらに保持容量部絶縁層 101 の膜厚が減ることなく、また保持容量部絶縁層 101 がプラズマに曝されない点で有利となる。このように、本実施の形態を選択することにより、動作速度の向上と、生産性の向上と、のいずれかをより好適に達成することが出来る。

## 【0078】

以上により、比誘電率の高い YSZ 膜を保持容量部に用いることで、駆動速度が速く、信頼性の高い半導体装置を得ることができる。また同様の理由で、保持容量部の面積を小さくすることができる。

## 【0079】

本発明を実施するための最良の形態によれば、ガラス基板等の耐熱温度が 750 未満の支持基板 100 であっても接合部の接着力が強固な LTSS 層を得ることができる。支持基板 100 として、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスの如き無アルカリガラスと呼ばれる電子工業用に使われる各種ガラス基板を適用することが可能となる。すなわち、一辺が 1 メートルを超える基板上に単結晶シリコン層を形成することができる。このような大面積基板を使って液晶ディスプレイのような表示装置のみならず、半導体集積回路を製造することができる。

## 【0080】

## (実施の形態 2)

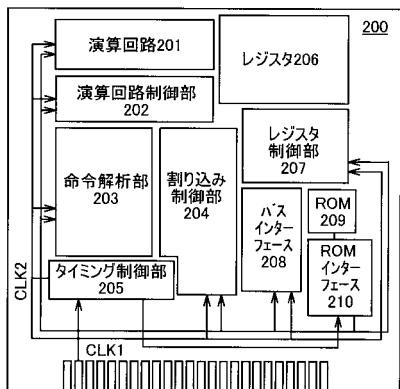

本実施の形態では、SOI 基板及び TFT を組み込んだ半導体装置について、図 7 及び図 8 を用いて説明する。

## 【0081】

図 7 では半導体装置の一例として、マイクロプロセッサ 200 を示す。このマイクロプロセッサ 200 は、演算回路 201 (Arithmetic logic unit; ALU ともいう)、演算回路制御部 202 (ALU Controller)、命令解析部 203 (Instruction Decoder)、割り込み制御部 204 (Interrupt Controller)、タイミング制御部 205 (Timing Controller)、レジスタ 206 (Register)、レジスタ制御部 207 (Register Controller)、バスインターフェース 208 (Bus I/F)、ROM 209 (Read Only Memory: 読み出し専用メモリ)、及び ROM インターフェース 210 (ROM I/F) を有している。

## 【0082】

バスインターフェース 208 を介してマイクロプロセッサ 200 に入力された命令は命令解析部 203 に入力され、デコードされた後に演算回路制御部 202、割り込み制御部 204、レジスタ制御部 207、タイミング制御部 205 に入力される。演算回路制御部 202、割り込み制御部 204、レジスタ制御部 207、タイミング制御部 205 は、デ

コードされた命令に基づき各種制御を行う。具体的に演算回路制御部 202 は、演算回路 201 の動作を制御するための信号を生成する。

#### 【0083】

また、割り込み制御部 204 は、マイクロプロセッサ 200 のプログラム実行中に、外部の入出力装置や周辺回路からの割り込み要求を、その優先度やマスク状態から判断して処理する。レジスタ制御部 207 は、レジスタ 206 のアドレスを生成し、マイクロプロセッサ 200 の状態に応じてレジスタ 206 の読み出しや書き込みを行う。タイミング制御部 205 は、演算回路 201、演算回路制御部 202、命令解析部 203、割り込み制御部 204、レジスタ制御部 207 の動作のタイミングを制御する信号を生成する。例えばタイミング制御部 205 は、基準クロック信号 CLK1 を元に、内部クロック信号 CLK2 を生成する内部クロック生成部を備えており、クロック信号 CLK2 を上記各種回路に供給する。10

#### 【0084】

なお、図 7 に示すマイクロプロセッサ 200 は、その構成を簡略化して示した一例にすぎず、実際にはその用途によって多種多様な構成を備えることができる。

#### 【0085】

このようなマイクロプロセッサ 200 は、支持基板に接合された結晶方位が一定の単結晶シリコン層 (LTSS 層) を有する TFT により集積回路が形成されているので、処理速度の高速化を図ることができる。また、高い比誘電率の YSZ 膜を用いることで保持容量の電極面積を小さくしているので、素子全体の縮小化が出来る。20

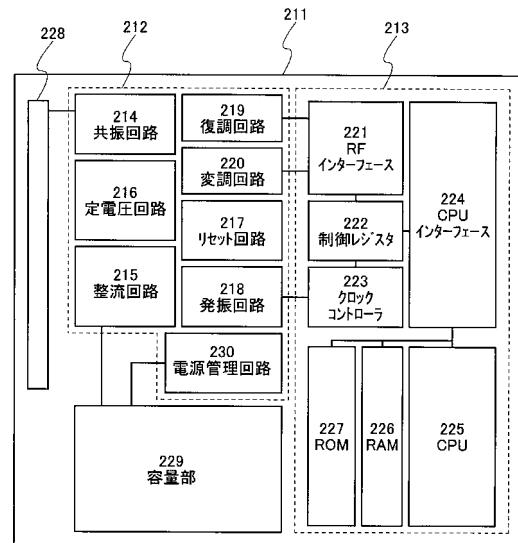

#### 【0086】

次に、非接触でデータの送受信を行うことのできる演算機能を備えた半導体装置の一例について、図 8 を参照して説明する。

#### 【0087】

図 8 は無線通信により外部装置と信号の送受信を行って動作するコンピュータ（以下、「RFCPU」という）の一例を示す。RFCPU211 は、アナログ回路部 212 とデジタル回路部 213 を有している。アナログ回路部 212 として、共振容量を有する共振回路 214、整流回路 215、定電圧回路 216、リセット回路 217、発振回路 218、復調回路 219 と、変調回路 220 を有している。デジタル回路部 213 は、RF インターフェース 221、制御レジスタ 222、クロックコントローラ 223、CPU インターフェース 224、CPU225 (Central Processing Unit : 中央処理ユニット)、RAM226 (Random Access Memory : ランダムアクセスメモリ)、ROM227 (Read Only Memory : 読み出し専用メモリ) を有している。30

#### 【0088】

このような構成の RFCPU211 の動作は以下の通りである。アンテナ 228 が受信した信号は共振回路 214 により誘導起電力を生じる。誘導起電力は整流回路 215 を経て容量部 229 に充電される。この容量部 229 はセラミックコンデンサーや電気二重層コンデンサーなどのキャパシタで形成されていることが好ましい。

#### 【0089】

容量部 229 は本発明の作製方法で形成された YSZ 膜を用いることができるが、RFCPU211 と一体形成されている必要はなく、別部品として RFCPU211 を構成する絶縁表面を有する基板に取り付けられていれば良い。40

#### 【0090】

リセット回路 217 は、デジタル回路部 213 をリセットし初期化する信号を生成する。例えば、電源電圧の上昇に遅延して立ち上がる信号をリセット信号として生成する。発振回路 218 は定電圧回路 216 により生成される制御信号に応じて、クロック信号の周波数とデューティ比を変更する。ローパスフィルタで形成される復調回路 219 は、例えば振幅変調 (ASK) 方式の受信信号の振幅の変動を二値化する。

#### 【0091】

10

20

30

40

50

変調回路 220 は、送信データを振幅変調（ASK）方式の送信信号の振幅を変動させて送信する。変調回路 220 は、共振回路 214 の共振点を変化させることで通信信号の振幅を変化させている。クロックコントローラ 223 は、電源電圧又はCPU225 における消費電流に応じてクロック信号の周波数とデューティ比を変更するための制御信号を生成している。電源電圧の監視は電源管理回路 230 が行っている。

#### 【0092】

アンテナ 228 から RF CPU 211 に入力された信号は復調回路 219 で復調された後、RF インターフェース 221 で制御コマンドやデータなどに分解される。制御コマンドは制御レジスタ 222 に格納される。制御コマンドには、ROM 227 に記憶されているデータの読み出し、RAM 226 へのデータの書き込み、CPU 225 への演算命令などが含まれている。10

#### 【0093】

CPU 225 は、CPU インターフェース 224 を介して ROM 227、RAM 226、制御レジスタ 222 にアクセスする。CPU インターフェース 224 は、CPU 225 が要求するアドレスより、ROM 227、RAM 226、制御レジスタ 222 のいずれかに対するアクセス信号を生成する機能を有している。

#### 【0094】

CPU 225 の演算方式は、ROM 227 に OS（オペレーティングシステム）を記憶させておき、起動とともにプログラムを読み出し実行する方式を採用することができる。また、専用回路で演算回路を構成して、演算処理をハードウェア的に処理する方式を採用することもできる。ハードウェアとソフトウェアを併用する方式では、専用の演算回路で一部の処理を行い、残りの演算はプログラムを使って CPU 225 が実行する方式を適用することができる。20

#### 【0095】

このような RF CPU 211 は、絶縁表面接合された結晶方位が一定の単結晶シリコン層（LTS S 層）が形成されているので、処理速度の高速化を図ることができる。また、高い比誘電率の YSZ 膜を用いることで保持容量の電極面積を小さくしているので、素子全体の縮小化が出来る。

#### 【0096】

図 8 では RF CPU の形態について示しているが、通信機能、演算処理機能、メモリ機能を備えたものであれば、IC タグのようなものであっても良い。30

#### 【図面の簡単な説明】

#### 【0097】

【図 1】SOI 構造を有する基板の構成を示す断面図。

【図 2】SOI 構造を有する基板の作製方法を説明する断面図。

【図 3】SOI 構造を有する基板の作製方法を説明する断面図。

【図 4】SOI 構造を有する基板の作製方法を説明する断面図。

【図 5】SOI 構造を有する基板の作製方法を説明する断面図。

【図 6】SOI 構造を有する基板の作製方法を説明する断面図。

【図 7】SOI 構造を有する基板により得られるマイクロプロセッサの構成を示すブロック図。40

【図 8】SOI 構造を有する基板により得られる RF CPU の構成を示すブロック図。

#### 【符号の説明】

#### 【0098】

100 支持基板

101 保持容量部絶縁層

102 保持容量部下部電極

103 配線

104 保持容量部

105 TFT

|         |               |    |

|---------|---------------|----|

| 1 0 6   | 活性層           |    |

| 1 0 7   | 保持容量部上部電極     |    |

| 1 0 8   | 配線            |    |

| 1 0 9   | 保護層           |    |

| 1 1 0   | 単結晶シリコン基板     |    |

| 1 1 1   | YSZ膜          |    |

| 1 1 2   | イオン           |    |

| 1 1 3   | 脆化層           |    |

| 1 1 4   | 絶縁膜           |    |

| 1 2 1   | 絶縁膜           | 10 |

| 1 2 2   | 接合層           |    |

| 1 2 3   | L T S S 層     |    |

| 1 2 4   | L T S S 層     |    |

| 1 3 1   | マスク           |    |

| 1 3 3   | 島状単結晶シリコン層    |    |

| 1 3 4   | ゲート絶縁膜        |    |

| 1 3 5   | ゲート電極         |    |

| 1 3 6   | 不純物元素         |    |

| 1 4 2   | マスク           |    |

| 1 4 3   | チャネル形成領域      | 20 |

| 1 4 4 a | 高濃度不純物領域      |    |

| 1 4 4 b | 高濃度不純物領域      |    |

| 1 4 4 c | 高濃度不純物領域      |    |

| 1 4 5   | 層間絶縁膜         |    |

| 1 4 6   | 配線            |    |

| 1 4 7   | 配線            |    |

| 1 5 2   | 層間絶縁膜         |    |

| 1 5 3   | 配線            |    |

| 2 0 0   | マイクロプロセッサ     |    |

| 2 0 1   | 演算回路          | 30 |

| 2 0 2   | 演算回路制御部       |    |

| 2 0 3   | 命令解析部         |    |

| 2 0 4   | 制御部           |    |

| 2 0 5   | タイミング制御部      |    |

| 2 0 6   | レジスタ          |    |

| 2 0 7   | レジスタ制御部       |    |

| 2 0 8   | バスインターフェース    |    |

| 2 0 9   | R O M         |    |

| 2 1 0   | R O Mインターフェース |    |

| 2 1 1   | R F C P U     | 40 |

| 2 1 2   | アナログ回路部       |    |

| 2 1 3   | デジタル回路部       |    |

| 2 1 4   | 共振回路          |    |

| 2 1 5   | 整流回路          |    |

| 2 1 6   | 定電圧回路         |    |

| 2 1 7   | リセット回路        |    |

| 2 1 8   | 発振回路          |    |

| 2 1 9   | 復調回路          |    |

| 2 2 0   | 変調回路          |    |

| 2 2 1   | R F インターフェース  | 50 |

- 2 2 2 制御レジスタ

2 2 3 クロックコントローラ

2 2 4 C P U インターフェース

2 2 5 C P U

2 2 6 R A M

2 2 7 R O M

2 2 8 アンテナ

2 2 9 容量部

2 3 0 電源管理回路

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/336 (2006.01) H 01 L 29/78 627D

G 02 F 1/1368 (2006.01) G 02 F 1/1368

(56)参考文献 国際公開第1999/030370 (WO, A1)

特開2003-218352 (JP, A)

特開平07-142607 (JP, A)

特開平09-055486 (JP, A)

国際公開第2004/086484 (WO, A1)

特開平08-255875 (JP, A)

特開2000-276076 (JP, A)

特開2006-173354 (JP, A)

特開2007-201430 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/336、29/786