(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7291561号**

**(P7291561)**

(45)発行日 令和5年6月15日(2023.6.15)

(24)登録日 令和5年6月7日(2023.6.7)

(51)国際特許分類

|                         |     |               |

|-------------------------|-----|---------------|

| H 04 N 25/70 (2023.01)  | F I | H 04 N 25/70  |

| H 04 N 25/13 (2023.01)  |     | H 04 N 25/13  |

| H 01 L 27/146 (2006.01) |     | H 01 L 27/146 |

A

請求項の数 13 (全27頁)

(21)出願番号 特願2019-136021(P2019-136021)

(22)出願日 令和1年7月24日(2019.7.24)

(65)公開番号 特開2020-17955(P2020-17955A)

(43)公開日 令和2年1月30日(2020.1.30)

審査請求日 令和3年7月26日(2021.7.26)

(31)優先権主張番号 10-2018-0086453

(32)優先日 平成30年7月25日(2018.7.25)

(33)優先権主張国・地域又は機関

韓国(KR)

(73)特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 12

9

129, Samsung-ro, Yeo

ngtong-gu, Suwon-si

, Gyeonggi-do, Repub

lic of Korea

110000051

弁理士法人共生国際特許事務所

李允基

大韓民国 京畿道 華城市 東灘中央路 2

20 D棟 2203号

最終頁に続く

(54)【発明の名称】 イメージセンサー

**(57)【特許請求の範囲】****【請求項1】**

第1面及び前記第1面の反対側の第2面を有する基板と、

前記基板内の第1光電変換領域及び第2光電変換領域と、

第1開口部及び前記第1開口部から第1方向に離隔した第2開口部を含み、前記第2面

を覆うように配置された第1層と、

第3開口部及び前記第3開口部から前記第1方向に離隔した第4開口部を含み、前記第

1層上に配置された第2層と、

前記第2層上に配置された平坦化層と、

前記第1光電変換領域に対応する第1レンズと、前記第2光電変換領域に対応する第2

レンズと、を備え、

前記第1開口部は前記第3開口部と垂直に整合(align)され、前記第2開口部は

前記第4開口部と垂直に整合され、

前記第1開口部は、前記第1光電変換領域の中心と垂直に整合され、

前記第3開口部の前記第1方向の幅は、前記第1開口部の前記第1方向の幅よりも大き

く、

前記第4開口部の前記第1方向の幅は、前記第2開口部の前記第1方向の幅よりも大き

く、

前記第1開口部と前記第2開口部は前記第1方向に配置され、前記第3開口部と前記第

4開口部は前記第1方向に配置され、

10

20

前記第1開口部の前記第1方向の幅は、前記第1光電変換領域の前記第1方向の幅よりも小さく、前記第2開口部の前記第1方向の幅は、前記第2光電変換領域の前記第1方向の幅よりも小さく、

前記第3開口部の前記第1方向の幅は、前記第1光電変換領域の前記第1方向の幅よりも小さく、前記第4開口部の前記第1方向の幅は、前記第2光電変換領域の前記第1方向の幅よりも小さいことを特徴とするイメージセンサー。

**【請求項2】**

前記第3開口部の前記第1方向の幅は、前記第1開口部の前記第1方向の幅よりも大きいことを特徴とする請求項1に記載のイメージセンサー。

**【請求項3】**

前記第1開口部は、前記第1方向に垂直な第2方向に第1高さを有し、前記第3開口部は、前記第2方向に第2高さを有し、

第2高さは第1高さよりも大きいことを特徴とする請求項2に記載のイメージセンサー。

**【請求項4】**

前記第1光電変換領域と前記第2光電変換領域との間に、第3光電変換領域をさらに備え、

前記第3光電変換領域は、前記第1層で覆われていることを特徴とする請求項3に記載のイメージセンサー。

**【請求項5】**

前記第1層は第1厚さを有し、前記第2層は前記第1厚さよりも大きい第2厚さを有することを特徴とする請求項1に記載のイメージセンサー。

**【請求項6】**

第1面及び前記第1面の反対側の第2面を有する基板と、

前記基板内の第1光電変換領域及び前記第1光電変換領域から第1方向に離隔した第2光電変換領域と、

第1開口部及び前記第1開口部から前記第1方向に離隔した第2開口部を含み、前記第2面を覆うように配置された第1層と、

第3開口部及び前記第3開口部から前記第1方向に離隔した第4開口部を含み、前記第1層上に配置された第2層と、

第5開口部及び前記第5開口部から前記第1方向に離隔した第6開口部を含み、前記第2層上に配置された第3層と、

前記第3層上に配置された平坦化層と、

前記第1光電変換領域に対応する第1レンズと、前記第2光電変換領域に対応する第2レンズと、を備え、

前記第1開口部は前記第1光電変換領域の中心と垂直に整合(align)され、前記第2開口部は前記第2光電変換領域の中心と垂直に整合され、

前記第1方向における前記第1光電変換領域と前記第2光電変換領域との間の距離は、前記第1方向における前記第1開口部の幅よりも大きく、

前記第1開口部は前記第3開口部及び前記第5開口部と垂直に整合し、

前記第2開口部は前記第4開口部及び前記第6開口部と垂直に整合し、

前記第1開口部の前記第1方向の幅は、前記第1光電変換領域の前記第1方向の幅よりも小さく、前記第2開口部の前記第1方向の幅は、前記第2光電変換領域の前記第1方向の幅よりも小さいことを特徴とするイメージセンサー。

**【請求項7】**

前記第1開口部は、円形であることを特徴とする請求項6に記載のイメージセンサー。

**【請求項8】**

前記第1層は、前記第1方向に垂直な第2方向に第1厚さを有し、前記第2層は、前記第2方向に第2厚さを有し、

前記第2厚さは前記第1厚さよりも大きいことを特徴とする請求項7に記載のイメージセンサー。

10

20

30

40

50

**【請求項 9】**

前記第3層は、前記第2方向に第3厚さを有し、前記第2厚さは前記第3厚さよりも大きいことを特徴とする請求項8に記載のイメージセンサー。

**【請求項 10】**

前記第2層と前記第3層との間に第4層をさらに有することを特徴とする請求項9に記載のイメージセンサー。

**【請求項 11】**

前記第5開口部の前記第1方向の幅は、前記第1開口部の前記第1方向の幅よりも大きいことを特徴とする請求項9に記載のイメージセンサー。

**【請求項 12】**

前記第1光電変換領域と前記第2光電変換領域との間に、第3光電変換領域をさらに備え、

前記第3光電変換領域は、前記第1層で覆われていることを特徴とする請求項9に記載のイメージセンサー。

**【請求項 13】**

第1面及び前記第1面の反対側の第2面を有する基板と、

前記基板内の第1光電変換領域及び前記第1光電変換領域から第1方向に離隔した第2光電変換領域と、

第1開口部及び第2開口部を含み、前記第2面を覆うように配置された第1層と

前記第1層上に配置された第2層と、

前記第2層上に配置された第3層と、

前記第3層上に配置された平坦化層と、

前記第1光電変換領域に対応する第1レンズと、前記第2光電変換領域に対応する第2レンズと、を備え、

前記第1開口部は前記第1光電変換領域の中心と垂直に整合(align)され、前記第2開口部は前記第2光電変換領域の中心と垂直方向に整列され、

前記第1方向における前記第1光電変換領域と前記第2光電変換領域との間の距離は、前記第1方向における第1開口部の幅よりも大きく、

前記第1層は前記第1方向に垂直な第2方向に第1厚さを有し、前記第2層は前記第2方向に第2厚さを有し、

前記第2厚さは前記第1厚さよりも大きく、

前記第1開口部の前記第1方向の幅は、前記第1光電変換領域の前記第1方向の幅よりも小さく、前記第2開口部の前記第1方向の幅は、前記第2光電変換領域の前記第1方向の幅よりも小さいことを特徴とするイメージセンサー。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、イメージセンサーに関し、特に、電気的特性がより向上したイメージセンサーに関する。

**【背景技術】****【0002】**

イメージセンサーは、光学映像を電気信号に変換させる。

近年、コンピュータ産業と通信産業の発達につれてスマートフォン、ウェアラブル(wearable)機器、デジタルカメラ、P C S ( P e r s o n a l C o m m u n i c a t i o n S y s t e m )、ゲーム機器、警備用カメラ、医療用マイクロカメラ等多様な分野で性能が向上したイメージセンサーの需要が増大している。

**【0003】**

イメージセンサーとしては、電荷結合素子(Charge Coupled Device: CCD)及びCMOSイメージセンサーがある。

この中で、CMOSイメージセンサーは駆動方式が簡単であり、信号処理回路を单一チ

10

20

30

40

50

ップに集積できるので、製品の小型化が可能である。

また、CMOSイメージセンサーは、電力消費が非常に低いので、バッテリー容量が制限的である製品に適用が容易である。

したがって、CMOSイメージセンサーは、技術開発と共に高解像度が具現可能であるので、その使用が急激に増加している。

#### 【0004】

したがって、高性能のCMOSイメージセンサーの需要に伴い、CMOSイメージセンサーの電気的特性等の改良、開発が常に課題となっている。

#### 【先行技術文献】

##### 【特許文献】

##### 【0005】

【文献】米国特許第9,349,762号明細書

米国特許出願公開第2016/0219232号明細書

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0006】

本発明は上記従来のCMOSイメージセンサーにおける課題に鑑みてなされたものであって、本発明の目的は、より向上した電気的特性を有するイメージセンサーを提供することにある。

##### 【課題を解決するための手段】

##### 【0007】

上記目的を達成するためになされた本発明によるイメージセンサーは、複数の第1光電変換素子と、前記第1光電変換素子と隣接する複数の第2光電変換素子と、を含む光電変換層と、前記光電変換層上に配置され、複数のマイクロレンズを含むマイクロレンズアレイと、前記光電変換層と前記マイクロレンズアレイとの間に配置され、前記各々の第1光電変換素子に各々対応して配置される複数の開口部(opening)を有する遮光膜と、を有し、前記マイクロレンズの各々は、平面視で前記第1光電変換素子の中の少なくとも1つ及び前記第2光電変換素子の中の少なくとも1つと重畳することを特徴とする。

##### 【0008】

また、上記目的を達成するためになされた本発明によるイメージセンサーは、複数の第1光電変換素子と、複数の第2光電変換素子と、を含む半導体基板と、前記半導体基板上に配置され、前記各々の第1光電変換素子に各々対応して配置される複数の開口部を有する遮光膜と、を有し、前記第2光電変換素子の各々は、平面視で互いに隣接する前記開口部間に配置されることを特徴とする。

##### 【0009】

また、上記目的を達成するためになされた本発明によるイメージセンサーは、複数の行及び複数の列に沿って配列され、各々が、少なくとも1つの受光ピクセルと、少なくとも1つの基準ピクセルと、を含む複数の単位ピクセルを含むピクセルアレイと、前記ピクセルアレイを覆い、互いに離隔して配列される複数の開口部を有する遮光膜と、を有し、前記開口部は、前記単位ピクセルの前記受光ピクセルの各々に対応して配置されることを特徴とする。

##### 【発明の効果】

##### 【0010】

本発明に係るイメージセンサーによれば、基準信号を提供する基準ピクセルの数が増加するので、センシングピクセルで入射光に比例して出力される電気的信号を処理する時、より正確な基準信号を提供することができる。

また、基準ピクセルがピクセルアレイ領域でセンシングピクセルと共に配置されるので、イメージセンサーをより小型化することができる。

さらに、本発明に係るイメージセンサーは、電子装置に搭載されて認証された使用者にサービスを提供するために指紋検出の機能を遂行することができ、イメージセンサーが小

10

20

30

40

50

型化することができるので、電子装置でイメージセンサーが占める面積を減少させることができるもの。

**【図面の簡単な説明】**

**【0011】**

【図1】本発明の実施形態に係るイメージセンサーの概略構成を示すブロック図である。

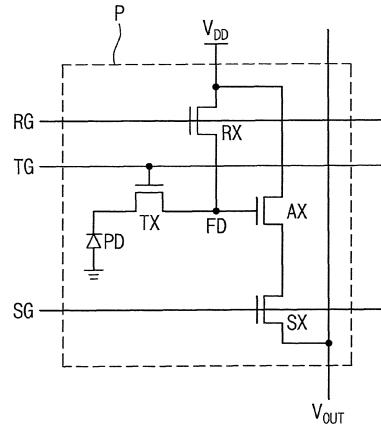

【図2】本発明の実施形態に係るイメージセンサーの単位ピクセルの構成を示す回路図である。

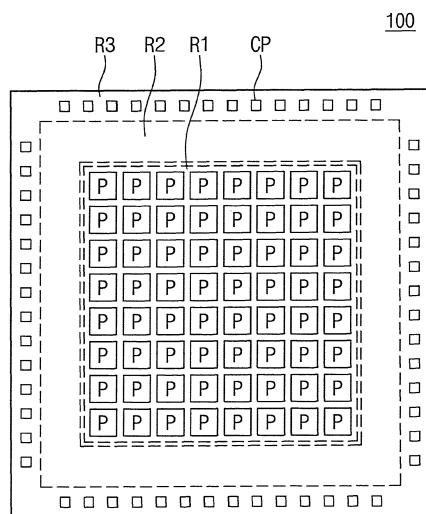

【図3】本発明の実施形態に係るイメージセンサーの概略的な平面図である。

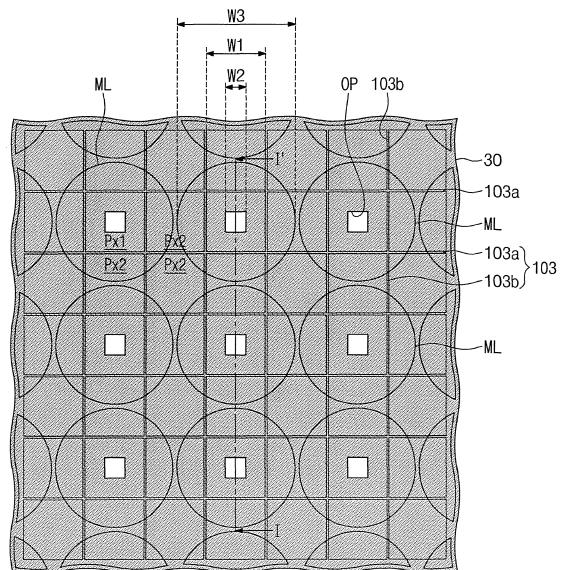

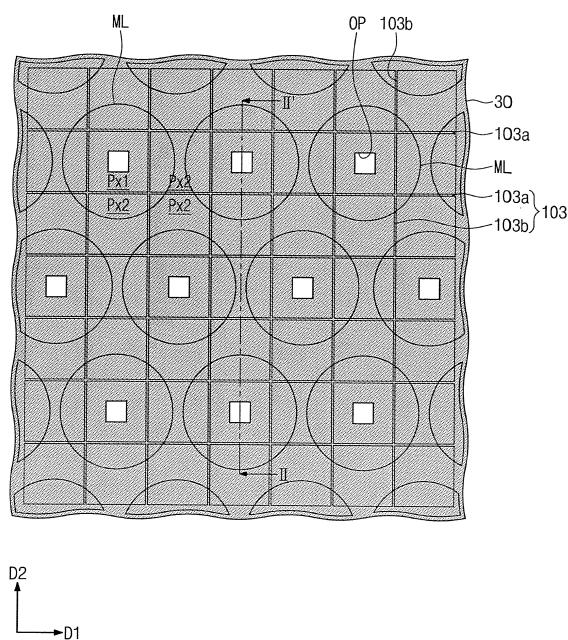

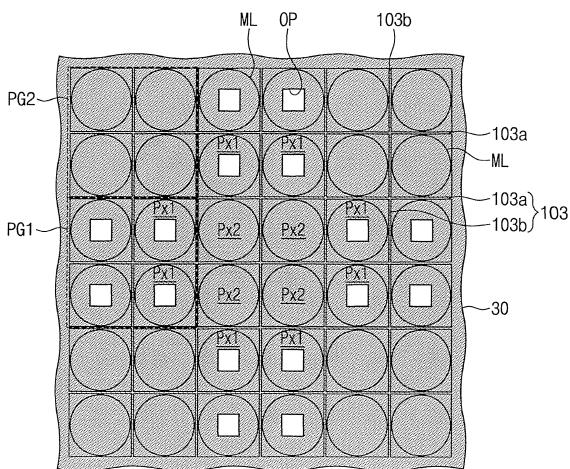

【図4】本発明の第1の実施形態に係るイメージセンサーの部分平面図である。

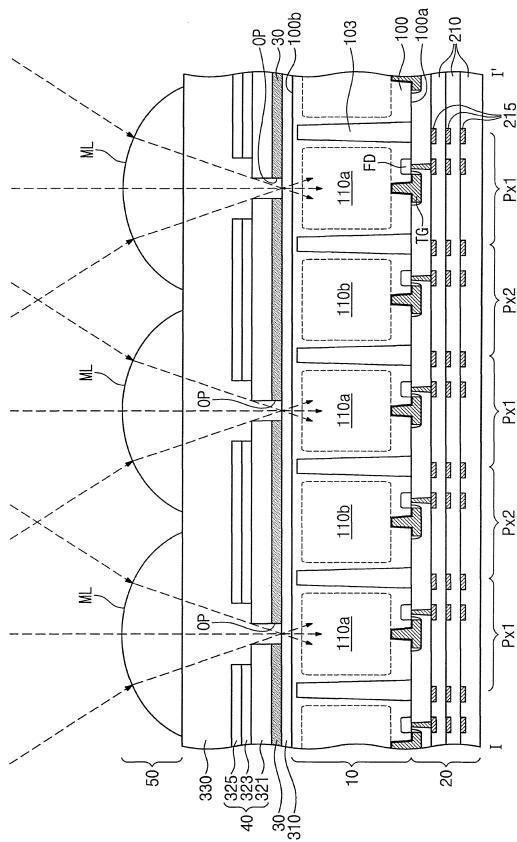

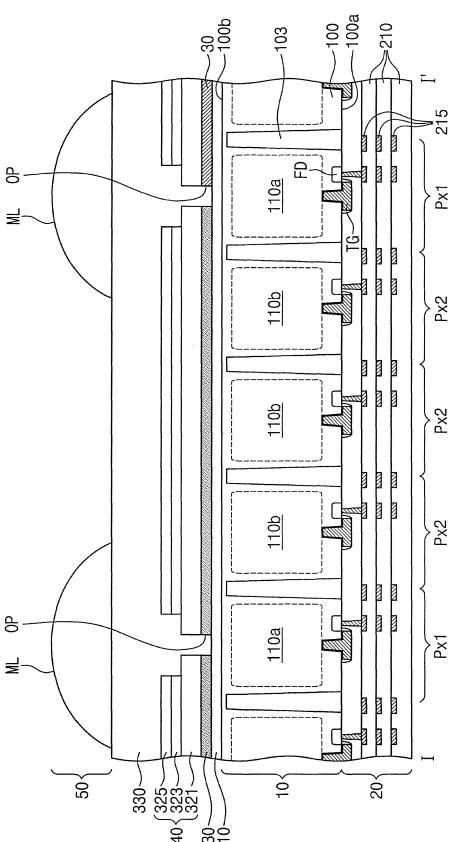

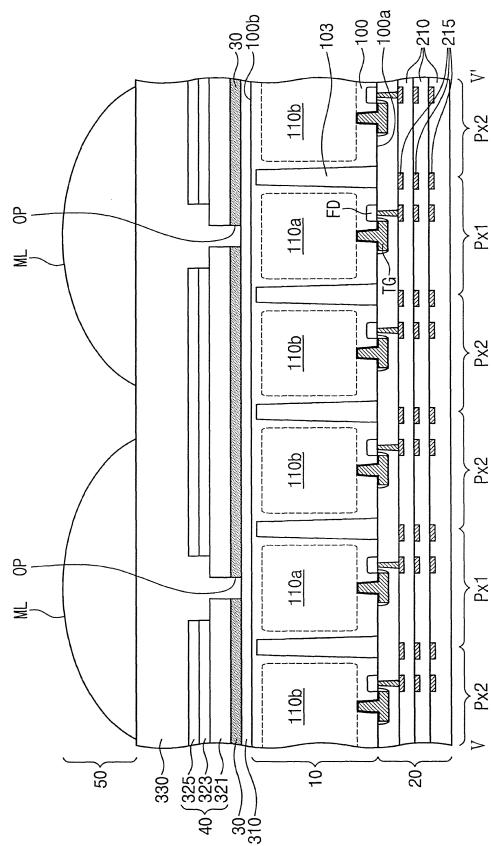

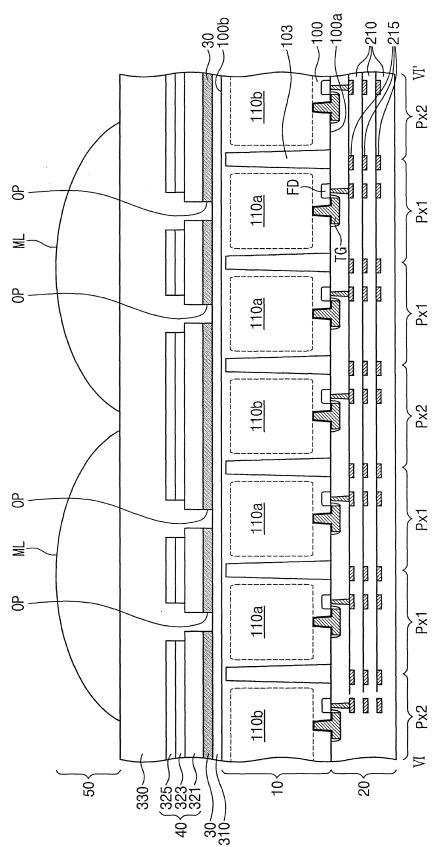

【図5A】本発明の第1の実施形態に係るイメージセンサーの断面図であって図4のI-I'線に沿って切断した断面図である。10

【図5B】本発明の第2の実施形態に係るイメージセンサーの断面図であって図4のI-I'線に沿って切断した断面図である。

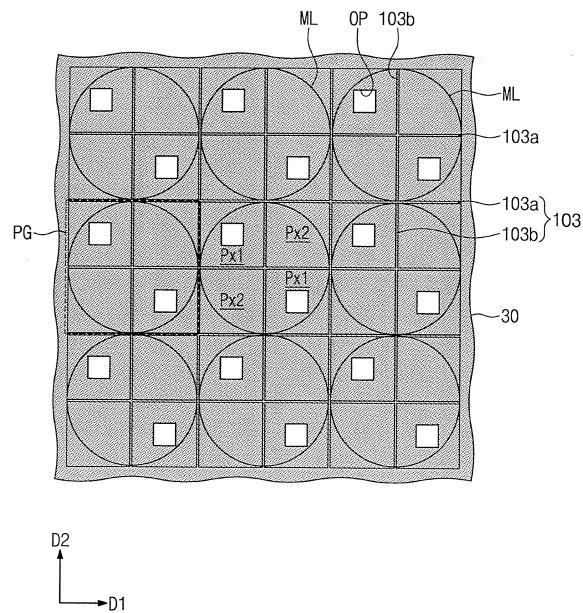

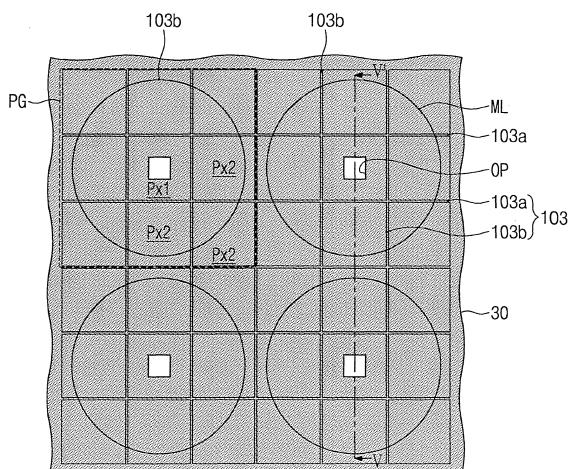

【図6】本発明の第3の実施形態に係るイメージセンサーの部分平面図である。

【図7】本発明の第3の実施形態に係るイメージセンサーの断面図であって図6のII-II'線に沿って切断した断面図である。

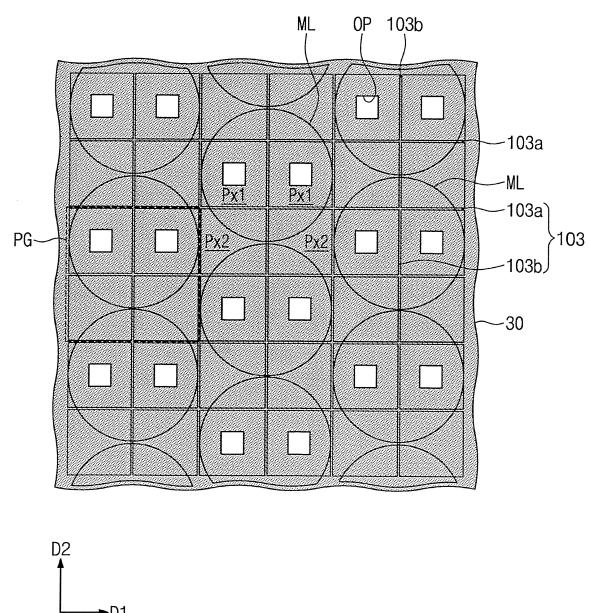

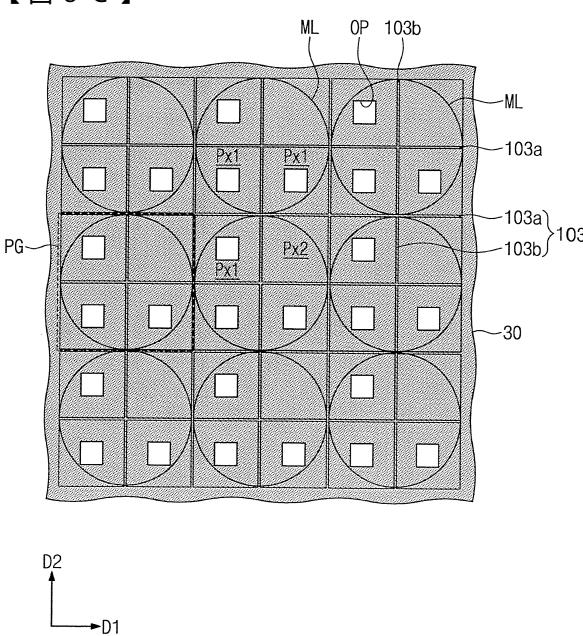

【図8A】本発明の第4の実施形態に係るイメージセンサーの部分平面図である。

【図8B】本発明の第5の実施形態に係るイメージセンサーの部分平面図である。

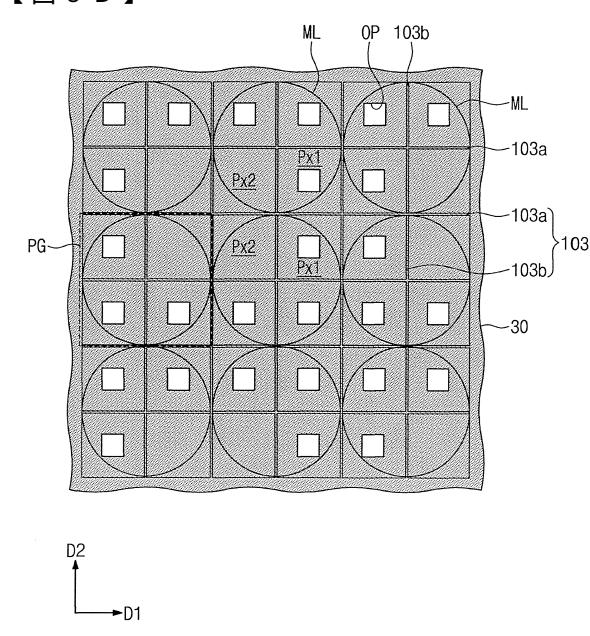

【図8C】本発明の第6の実施形態に係るイメージセンサーの部分平面図である。

【図8D】本発明の第7の実施形態に係るイメージセンサーの部分平面図である。20

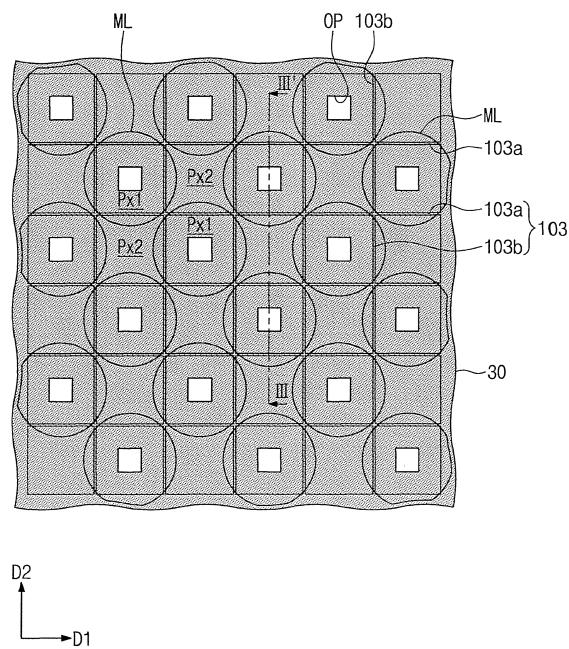

【図9】本発明の第8の実施形態に係るイメージセンサーの部分平面図である。

【図10】本発明の第8の実施形態に係るイメージセンサーの断面図であって図9のII-II'-III-III'線に沿って切断した断面図である。

【図11A】本発明の第9の実施形態に係るイメージセンサーの部分平面図である。

【図11B】本発明の第10の実施形態に係るイメージセンサーの部分平面図である。

【図12】本発明の第9、10の実施形態に係るイメージセンサーの断面図であって図11A及び図11BのIV-IV'線に沿って切断した断面図である。

【図13A】本発明の第11の実施形態に係るイメージセンサーの部分平面図である。

【図13B】本発明の第12の実施形態に係るイメージセンサーの部分平面図である。

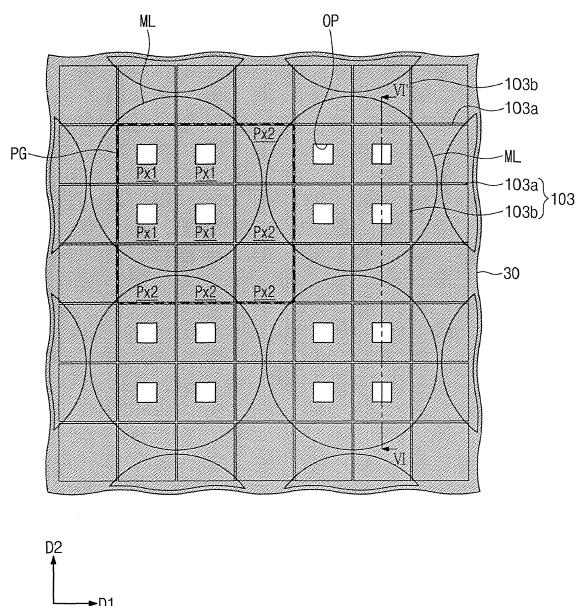

【図14】本発明の第13の実施形態に係るイメージセンサーの部分平面図である。30

【図15】本発明の第13の実施形態に係るイメージセンサーの断面図であって図14のV-V'線に沿って切断した断面図である。

【図16】本発明の第14の実施形態に係るイメージセンサーの部分平面図である。

【図17】本発明の第14の実施形態に係るイメージセンサーの断面図であって図16のVI-VI'線に沿って切断した断面図である。

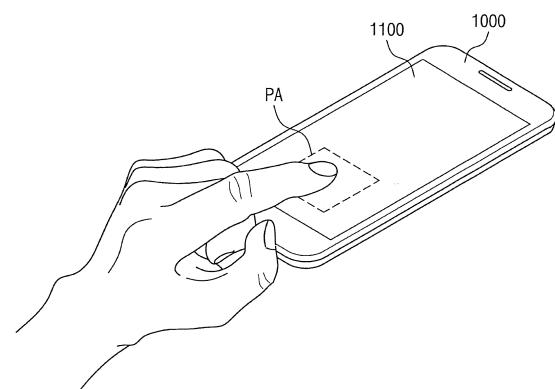

【図18】本発明の実施形態に係るイメージセンサーを含む電子装置の概略を示す斜視図である。

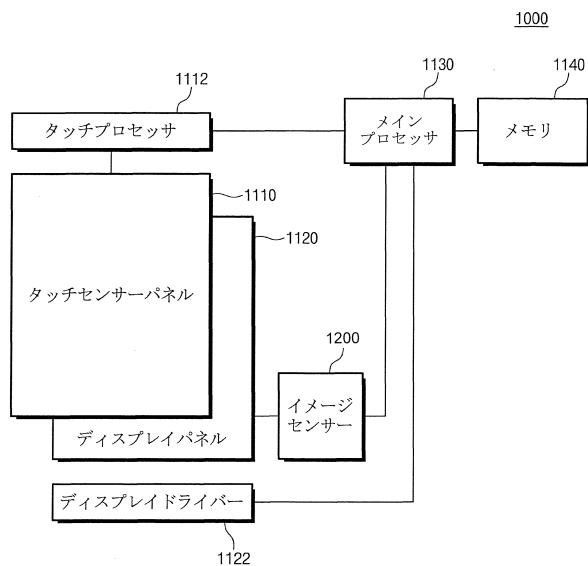

【図19】本発明の実施形態に係るイメージセンサーを含む電子装置の概略構成を示すブロック図である。

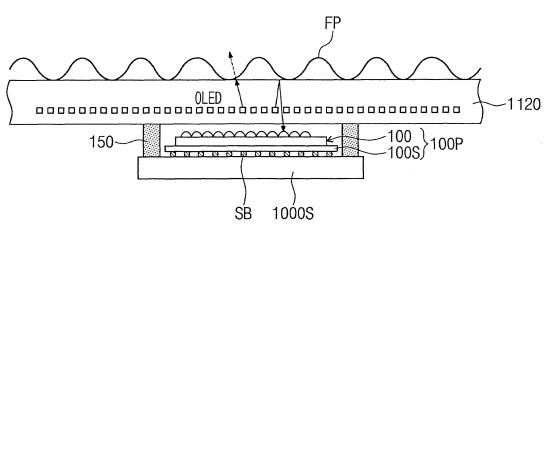

【図20】本発明の実施形態に係るイメージセンサーを含む電子装置の構成の一部を示す断面図である。40

【図21】図20に示した電子装置をより詳細に示す断面図である。

**【発明を実施するための形態】**

**【0012】**

次に、本発明に係るイメージセンサーを実施するための形態の具体例を図面を参照しながら説明する。

**【0013】**

図1は、本発明の実施形態に係るイメージセンサーの概略構成を示すブロック図である。

図1を参照すると、イメージセンサーは、アクティブピクセルセンサーアレイ(Active Pixel Sensor array)1、行デコーダー(row decoder)50

er ) 2、行ドライバー (row driver) 3、列デコーダー (column decoder) 4、タイミング発生器 (timing generator) 5、相関二重サンプラー (Correlated Double Sampler : CDS) 6、アナログデジタルコンバーター (Analog to Digital Converter : ADC) 7、及び入出力バッファ (I/O buffer) 8を含む。

#### 【0014】

アクティブピクセルセンサーアレイ1は、2次元に配列された複数の単位ピクセルを含み、光信号を電気的信号に変換する。

アクティブピクセルセンサーアレイ1は、行ドライバー3からのピクセル選択信号、リセット信号、及び電荷伝送信号のような複数の駆動信号によって駆動される。

また、変換された電気的信号は、相関二重サンプラー6に提供される。

行ドライバー3は、行デコーダー2でデコーディングされた結果に応じて複数の単位ピクセルを駆動するための複数の駆動信号をアクティブピクセルセンサーアレイ1に提供する。

単位ピクセルが行列形状に配列された場合には、各行別に駆動信号が提供される。

タイミング発生器5は、行デコーダー2及び列デコーダー4にタイミング (timing) 信号及び制御信号を提供する。

#### 【0015】

相関二重サンプラー (CDS) 6は、アクティブピクセルセンサーアレイ1で生成された電気信号を受信して維持 (hold) 及びサンプリングを実行する。

相関二重サンプラー6は、特定の雑音レベル (noise level) と電気的信号による信号レベルを二重にサンプリングして、雑音レベルと信号レベルの差に該当する差レベルを出力する。

アナログデジタルコンバーター (ADC) 7は、相関二重サンプラー6から出力された差レベルに該当するアナログ信号をデジタル信号に変換して出力する。

入出力バッファ8は、デジタル信号をラッチ (latch) し、ラッチされた信号は、列デコーダー4でのデコーディング結果に応じて順次に映像信号処理部 (未図示) にデジタル信号を出力する。

#### 【0016】

図2は、本発明の実施形態に係るイメージセンサーの単位ピクセルの構成を示す回路図である。

図2を参照すると、単位ピクセルPは、トランスマートランジスタTX及びロジックトランジスタ (RX、SX、DX) を含む。

ここで、ロジックトランジスタは、リセット (reset) トランジスタRX、選択 (selection) トランジスタSX)、及びソースフォロワ (source follower) トランジスタAX、又は増幅トランジスタを含む。

#### 【0017】

トランスマートランジスタTXは、トランスマートゲート電極、光電変換素子PD、及び電荷格納ノードFD (即ち、フローティング拡散領域 (Floating Diffusion region)) を含む。

光電変換素子PDは、外部から入射した光の量に比例して光電荷を生成し、蓄積する。

本実施形態で、光電変換素子PDは、フォトダイオード (photo diode)、フォトトランジスタ (photo transistor)、フォトゲート (photo gate)、ピンドフォトダイオード (Pinned Photo Diode : PPD)、及びこれらの組み合わせを使用することができる。

#### 【0018】

トランスマートランジスタTXは、光電変換素子PDに蓄積された電荷を電荷格納ノードFDに伝送する。

トランスマートランジスタTXは、電荷伝送ラインTGを通じて提供される電荷伝送信号によって制御される。

10

20

30

40

50

電荷格納ノード F D は、光電変換素子 P D で生成された電荷を受信して累積的に格納することができ、電荷格納ノード F D に蓄積された光電荷の量に応じてソースフォロワトランジスタ A X のゲート電極の電位を変化させることができる。

#### 【 0 0 1 9 】

リセットトランジスタ R X は、電荷格納ノード F D に蓄積された電荷を周期的にリセットさせる。

詳細には、リセットトランジスタ R X のゲート電極は、リセット信号が提供されるリセット信号ライン R G に接続される。

リセットトランジスタ R X のドレーンは、電荷格納ノード F D と接続され、リセットトランジスタ R X のソースは、電源電圧 V<sub>DD</sub> に接続される。

リセット信号によってリセットトランジスタ R X がターンオンされれば、リセットトランジスタ R X のソースと接続された電源電圧 V<sub>DD</sub> が電荷格納ノード F D に伝達される。

したがって、リセットトランジスタ R X がターンオンされた時、電荷格納ノード F D に蓄積された光電荷が排出されて電荷格納ノード F D がリセットされる。

#### 【 0 0 2 0 】

ソースフォロワトランジスタ A X は、電荷格納ノード F D での電位変化を増幅し、選択トランジスタ S X を通じて増幅された、又はピクセル信号を出力ライン V<sub>OUT</sub> に出力する。

ソースフォロワトランジスタ A X は、ゲート電極に入力される光電荷量に比例してソース - ドレーン電流を発生させるソースフォロワバッファ増幅器 ( source follower buffer amplifier ) である。

ソースフォロワトランジスタ A X のゲート電極は、電荷格納ノード F D に接続され、ソースフォロワトランジスタ A X のドレーンは、電源電圧 V<sub>DD</sub> に接続され、ソースフォロワトランジスタ A X のソースは、選択トランジスタ S X のドレーンと接続される。

#### 【 0 0 2 1 】

選択トランジスタ S X は、行単位に読み出す単位ピクセルを選択する。

選択トランジスタ S X の選択ゲート電極は選択信号を提供する選択ライン S G に接続される。

選択信号によって選択トランジスタ S X がターンオンされた時、ソースフォロワトランジスタ A X のソース端子から出力されるピクセル信号が出力ライン V<sub>OUT</sub> に出力される。

なお、図 2 に示した実施形態によれば、単位ピクセル P が 4 つのトランジスタ構造からなされた場合を示しているが、単位ピクセル P は、3 つのトランジスタ構造、5 つのトランジスタ構造、又は 4 つのトランジスタ構造と同様のフォトゲート構造で構成されてもよい。

#### 【 0 0 2 2 】

図 3 は、本発明の実施形態に係るイメージセンサーの概略的な平面図である。

図 3 を参照すると、イメージセンサーは、ピクセルアレイ領域 R 1 、制御回路領域 R 2 、及びパッド領域 R 3 を含む。

ピクセルアレイ領域 R 1 に、行及び列に沿って 2 次元的に配列された複数の単位ピクセル P が配置される。

#### 【 0 0 2 3 】

ピクセルアレイ領域 R 1 の単位ピクセル P は、入射光 ( incident light ) によって発生した電気的信号を出力する。

本実施形態で、単位ピクセル P は、センシングピクセル及び基準ピクセルを含む。

センシングピクセルは、入射光を電気的信号に変換する。

基準ピクセルは、光が入射しない単位ピクセルで発生する電気的信号を出力する。

#### 【 0 0 2 4 】

制御回路領域 R 2 は、ピクセルアレイ領域 R 1 の周囲に配置され、制御回路領域 R 2 にピクセルアレイ領域 R 1 の単位ピクセル P を制御する制御回路（図示せず）が配置される。

一例として、図 1 を参照して説明した行デコーダー 2 、行ドライバー 3 、列デコーダー

4、タイミング発生器 5、相関二重サンプラー 6、アナログデジタルコンバーター 7、及び入出力バッファ 8 のような制御回路が制御回路領域 R 2 に配置され得る。

【0025】

パッド領域 R 3 に制御信号及び光電信号等を入出力するのに利用される複数の導電パッド C P が配置される。

パッド領域 R 3 は、外部素子との電気的接続が容易になるようにイメージセンサーの周縁部分 (edge portion) に配置される。

【0026】

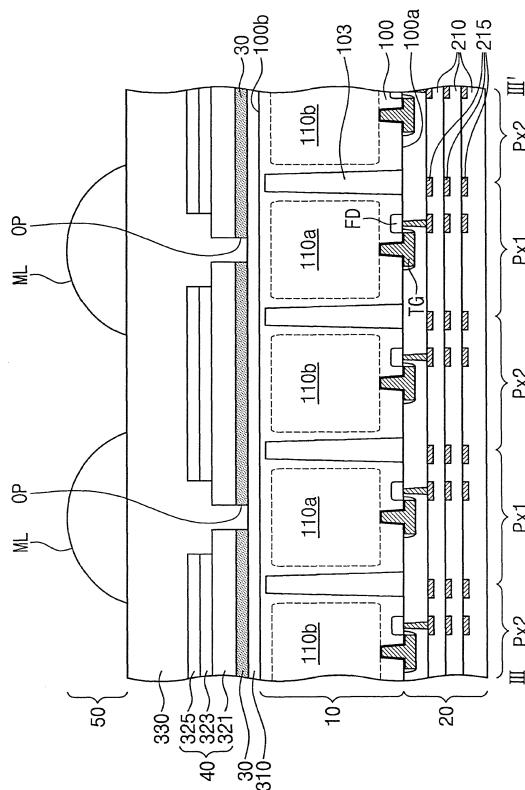

図 4 は、本発明の第 1 の実施形態に係るイメージセンサーの部分平面図であり、図 5 A は、本発明の第 1 の実施形態に係るイメージセンサーの断面図であって図 4 の I - I' 線に沿って切断した断面図であり、図 5 B は、本発明の第 2 の実施形態に係るイメージセンサーの断面図であって図 4 の I - I' 線に沿って切断した断面図である。 10

【0027】

図 4 及び図 5 A を参照すると、本発明の第 1 の実施形態に係るイメージセンサーは、光電変換層 10、読出回路層 20、遮光膜 30、カラーフィルター層 40、及びマイクロレンズアレイ 50 を含む。

本実施形態で、光電変換層 10 は、垂直方向から見て、読出回路層 20 と遮光膜 30 との間に配置される。

遮光膜 30 は、垂直方向から見て、光電変換層 10 とマイクロレンズアレイ 50 との間に配置される。 20

カラーフィルター層 40 は、垂直方向から見て、遮光膜 30 とマイクロレンズアレイ 50 との間に配置される。

【0028】

光電変換層 10 は、半導体基板 100 及び半導体基板 100 内に提供された光電変換領域 (110a、110b) を含む。

半導体基板 100 は、互いに対向する第 1 面 100a (又は前面) 及び第 2 面 100b (又は後面) を有する。

光電変換領域 (110a、110b) は、第 1 導電型の半導体基板 100 と反対である第 2 導電型 (例えば、n 型) の不純物がドーピングされた不純物領域である。

外部から入射した光は、光電変換領域 (110a、110b) で電気的信号に変換される。 30

【0029】

読出回路層 20 が半導体基板 100 の第 1 面 100a 上 (図 4 では下方) に配置される。 読出回路層 20 は、光電変換層 10 と接続される読出回路 (例えば、MOS トランジスタ) を含む。

光電変換層 10 で変換された電気的信号は、読出回路層 20 で信号処理される。

より詳細には、半導体基板 100 の第 1 面 100a 上に MOS トランジスタ及び MOS トランジスタに接続される接続配線 215 が配置される。

接続配線 215 は、層間絶縁膜 210 を介在して積層され、互いに異なるレベルに位置する接続配線 215 は、コンタクトプラグを通じて互いに接続される。 40

【0030】

遮光膜 30 が半導体基板 100 の第 2 面 100b の上方に第 2 面 100b の全体を覆うように配置される。

言い換えれば、遮光膜 30 は、互いに交差する第 1 方向 D 1 及び第 2 方向 D 2 に延長されたプレート形状を有する。

さらに、遮光膜 30 は、光電変換領域 (110a、110b) の内の一部を露出させる開口部 O P を有する。

遮光膜 30 の開口部 O P は、第 1 方向 D 1 及び第 2 方向 D 2 に沿って互いに離隔して配列される。

【0031】

10

20

30

40

50

カラーフィルター層 40 は、遮光膜 30 上に順次に積層された第 1 カラーフィルター層 321、第 2 カラーフィルター層 323、及び第 3 カラーフィルター層 325 を含む。

第 1、第 2、及び第 3 カラーフィルター層 (321、323、325) は、互いに異なる色を有し、3つの色が混合して黒色 (black) を帯びる。

マイクロレンズアレイ 50 は、外部から入射する光を集光する複数のマイクロレンズ M<sub>L</sub> を含む。

マイクロレンズ M<sub>L</sub> は、互いに交差する第 1 及び第 2 方向 (D1、D2) に沿って 2 次元的に配列される。

#### 【0032】

より詳細には、半導体基板 100 は、第 1 導電型 (例えば、p 型) バルク (bulk) シリコン基板上に第 1 導電型エピタキシャル層が形成された基板であり、イメージセンサーの製造工程上、バルクシリコン基板が除去されて、p 型エピタキシャル層のみが残留する基板である。

また、半導体基板 100 は、第 1 導電型のウェルを含むバルク半導体基板である。

半導体基板 100 は、ピクセル分離構造体 103 によって定義される複数のピクセル領域 (P<sub>x</sub>1、P<sub>x</sub>2) を含む。

複数のピクセル領域 (P<sub>x</sub>1、P<sub>x</sub>2) は、互いに交差する第 1 方向 D1 及び第 2 方向 D2 に沿ってマトリックス状に配列される。

#### 【0033】

ピクセル分離構造体 103 は、平面視でピクセル領域 (P<sub>x</sub>1、P<sub>x</sub>2) の各々を囲む。

詳細には、ピクセル分離構造体 103 は、互いに並行して第 1 方向 D1 に延長される複数の第 1 ピクセル分離膜 103a 及び第 1 ピクセル分離膜 103b を横切って互いに並行して第 2 方向 D2 に延長される第 2 ピクセル分離膜 103b を含む。

第 1 ピクセル分離膜 103a は、第 2 方向 D2 に沿って第 1 間隔 W1 にて互いに離隔され、第 2 ピクセル分離膜 103b は、第 1 方向 D1 に沿って第 1 間隔 W1 にて互いに離隔される。

本実施形態で、ピクセル領域 (P<sub>x</sub>1、P<sub>x</sub>2) の各々の幅 W1 は、互いに隣接する第 1 又は第 2 ピクセル分離膜 (103a、103b) の間の間隔 W1 に相当する。

#### 【0034】

ピクセル分離構造体 103 は、半導体基板 100 (例えば、シリコン) より屈折率が低い絶縁物質で形成することができ、1つ又は複数の絶縁膜を含むことができる。

例えば、ピクセル分離構造体 103 は、シリコン酸化膜、シリコン窒化膜、アンドープされたポリシリコン膜、空気 (air)、又はこれらの組み合わせからなる。

このようなピクセル分離構造体 103 は、半導体基板 100 の第 1 面 100a 及び / 又は第 2 面 100b をパターニングして深いトレンチを形成した後、深いトレンチ内に絶縁物質を埋め込んで形成される。

#### 【0035】

ピクセル分離構造体 103 は、垂直視で半導体基板 100 の第 1 面 100a から第 2 面 100b の方向に垂直的に延長され、半導体基板 100 の第 2 面 100b と離隔される。

言い換えれば、ピクセル分離構造体 103 の垂直厚さ (高さ) は、半導体基板 100 の垂直厚さより小さい。

これとは異なり、ピクセル分離構造体 103 は、半導体基板 100 を貫通してもよい。

即ち、ピクセル分離構造体 103 の垂直厚さは、半導体基板 100 の垂直厚さと実質的に同一であってもよい。

他の例として、ピクセル分離構造体 103 は、第 1 導電型の半導体基板 100 内に第 1 導電型の不純物をドーピングして形成された不純物領域であってもよい。

#### 【0036】

本実施形態によれば、ピクセル分離構造体 103 によって定義されたピクセル領域 (P<sub>x</sub>1、P<sub>x</sub>2) は、複数の第 1 ピクセル領域 P<sub>x</sub>1 及び複数の第 2 ピクセル領域 P<sub>x</sub>2 を含む。

10

20

30

40

50

第1ピクセル領域 P × 1 は、入射光に比例して発生した電気的信号を出力するセンシングピクセルである。

第1ピクセル領域 P × 1 から出力される電気的信号は、光電信号のみならず、ノイズ信号を含む。

第2ピクセル領域 P × 2 は、光が入射しない状態で熱発生等によって生成される電子によって発生する電気的信号（即ち、基準（reference）信号）を出力する基準ピクセルである。

#### 【0037】

第2ピクセル領域 P × 2 から出力される基準信号は、第1ピクセル領域 P × 1 から出力される電気的信号の基準値として提供される。 10

第2ピクセル領域 P × 2 で発生した基準信号は、正確性のために第2ピクセル領域 P × 2 の単位ピクセルから出力した電気的信号の平均値である。

実施形態によれば、第2ピクセル領域 P × 2 で発生した基準信号は、正確度を高めるために第2ピクセル領域 P × 2 の数が変更することができる。

一例として、第2ピクセル領域 P × 2 の数が第1ピクセル領域 P × 1 の数より多い。

具体的には、1つの第1ピクセル領域 P × 1 と3つの第2ピクセル領域 P × 2 とで1つのピクセルグループを構成し、複数のピクセルグループが第1方向 D 1 及び第2方向 D 2 に沿って配列される。

#### 【0038】

半導体基板 100 のピクセル領域（P × 1、P × 2）内に光電変換領域（110a、110b）が各々提供される。 20

光電変換領域（110a、110b）の各々は、平面視でピクセル分離構造体 103 によって囲まれる。

実施形態によれば、光電変換領域（110a、110b）は、第1ピクセル領域 P × 1 に提供された第1光電変換領域 110a 及び第2ピクセル領域 P × 2 に提供された第2光電変換領域 110b を含む。

第1及び第2光電変換領域（110a、110b）は、実質的に同一の構造及び物質を有する。

#### 【0039】

詳細には、第1及び第2光電変換領域（110a、110b）は、第1導電型の半導体基板 100 と反対の第2導電型を有する不純物を半導体基板 100 内にイオン注入して形成される。 30

第1導電型の半導体基板 100 と第2導電型の第1、第2光電変換領域（110a、110b）との接合（junction）によってフォトダイオードが形成される。

各々のピクセル領域（P × 1、P × 2）で、半導体基板 100 の第1面 100a 上にトランスマルチゲート電極 TG が配置され、図 2 を参照して説明した読み出し回路が共に提供される。

#### 【0040】

トランスマルチゲート電極 TG は、平面視で各ピクセル領域の中心部に位置する。

トランスマルチゲート電極 TG の一部は、半導体基板内に配置され、トランスマルチゲート電極 TG と半導体基板 100 との間にはゲート絶縁膜が介在する。 40

トランスマルチゲート電極 TG の一側の半導体基板 100 内にフローティング拡散領域 FD が提供される。

フローティング拡散領域 FD は、半導体基板と反対の不純物をイオン注入して形成される。

例えば、フローティング拡散領域 FD は、n 型不純物領域である。

#### 【0041】

層間絶縁膜 210 が半導体基板 100 の第1面 100a 上に積層され、層間絶縁膜 210 は、読み出し回路を構成する MOS トランジスタ及びトランスマルチゲート電極 TG を覆う。

層間絶縁膜は、例えばシリコン酸化物、シリコン窒化物、及び / 又はシリコン酸窒化物

10

20

30

40

50

を含み得る。

各々の層間絶縁膜 210 上に接続配線 215 が配置され、接続配線 215 はコンタクト プラグを通じて読み出し回路と電気的に接続される。

#### 【0042】

半導体基板 100 の第 2 面 100b 上にバッファ絶縁膜 310 が配置される。

バッファ絶縁膜 310 は、半導体基板 100 の第 2 面 100b に存在する欠陥によって生成される電荷（即ち、電子或いは正孔）が光電変換領域（110a、110b）に移動することを防止する。

バッファ絶縁膜 310 は、単一膜又は多層膜を含むことができる。

バッファ絶縁膜 310 は、アルミニウム酸化物及び／又はハフニウム酸化物のような金属酸化物を含み得る。 10

#### 【0043】

遮光膜 30 がバッファ絶縁膜 310 上に配置される。

遮光膜 30 は、第 1 方向 D1 及び第 2 方向 D2 に沿って延長されるプレート形状を有し、第 1 ピクセル領域 P × 1、即ち、第 1 光電変換領域 110a に対応する開口部 OP を有する。

遮光膜 30 の開口部 OP は、平面視で第 1 光電変換領域 110a の一部分と各々重畠される。

即ち、遮光膜 30 の開口部 OP を通じて第 1 光電変換領域 110a に光が入射される。

遮光膜 30 は、第 1 光電変換領域 110a 上及び第 2 光電変換領域 110b 上に第 1 方向 D1 及び第 2 方向 D2 に沿って連続的に延長される。 20

即ち、遮光膜 30 は、平面視で第 2 光電変換領域 110b と完全に重畠する。

#### 【0044】

遮光膜 30 は、開口部 OP を除外した全体で、半導体基板 100 の第 2 面 100b に入射する光を反射及び遮断させる。

即ち、第 2 光電変換領域 110b に入射する光を遮断する。

遮光膜 30 は、例えばタンクスチン又はアルミニウムのような金属物質からなる。

実施形態で、遮光膜 30 の開口部 OP は、方形状を有するものとして示したが、円形であってもよい。

遮光膜 30 の開口部 OP は、第 1 方向 D1 及び第 2 方向 D2 に沿って互いに離隔して配列される。 30

開口部 OP の各々の中心は、第 1 ピクセル領域の中心又は第 1 光電変換領域の中心と整合（align）される。

#### 【0045】

実施形態で、開口部 OP の幅は、第 1 光電変換領域 110a に入射される光の入射角が一定入射角より大きくならないように調節することができ、したがって、近接する物体の撮像を可能にすることができる。

詳細には、開口部 OP の幅 W2 は、ピクセル領域（P × 1、P × 2）の幅 W1 より小さく、互いに隣接する開口部 OP 間の間隔より小さい。

開口部 OP の幅 W2 は、遮光膜 30 と光電変換領域（110a、110b）との間の垂直距離、遮光膜 30 とマイクロレンズ ML との間の垂直距離、及びマイクロレンズ ML の曲率に沿って最適化される。 40

#### 【0046】

一例として、遮光膜 30 の開口部 OP は、平面視で第 1 方向 D1 及び第 2 方向 D2 に沿って第 2 ピクセル領域 P × 2 の間に各々配置され得る。

また、遮光膜 30 の開口部 OP は、第 1 方向 D1 及び第 2 方向 D2 に沿って一定な間隔に離隔され得る。

言い換えれば、平面視で第 1 ピクセル領域 P × 1 の各々の周囲に第 2 ピクセル領域 P × 2 が配置される。

#### 【0047】

遮光膜30上にカラーフィルター層40が配置される。

カラーフィルター層40は、遮光膜30のように半導体基板100の第2面100bの全体を覆い、遮光膜30の開口部OPを露出させる。

より詳細には、カラーフィルター層40は、先に説明したように順次に積層された第1カラーフィルター層321、第2カラーフィルター層323、及び第3カラーフィルター層325を含む。

第1カラーフィルター層321は、遮光膜30の開口部OPに対応する第1開口を有する。

ここで、第1カラーフィルター層321の第1開口の内壁は、遮光膜30の開口部OPの内壁と垂直に整合される。

第2及び第3カラーフィルター層(323、325)は、また遮光膜30の開口部OPに対応する第2開口を有し、第2及び第3カラーフィルター層(323、325)の第2開口の幅は、開口部OPの幅W2より大きい。

#### 【0048】

一例として、第1カラーフィルター層321は緑色カラーフィルター層であり、第2カラーフィルター層323は赤色カラーフィルター層であり、第3カラーフィルター層325は青色カラーフィルター層である。

これとは異なって、第1カラーフィルター層321はシアン(cyan)カラーフィルター層であり、第2カラーフィルター層323はマゼンタ(magenta)カラーフィルター層であり、第3カラーフィルター層325は黄色(yellow)カラーフィルター層である。

また、他の例として、カラーフィルター層40で第2及び第3カラーフィルター層(323、325)を省略することもでき、第1カラーフィルター層321のみを含むこともできる。

また、第2の実施形態として、図5Bに示すように、遮光膜30上でカラーフィルター層を省略することができ、平坦絶縁膜330が遮光膜30を直接覆い得る。

#### 【0049】

続いて図5Aを参照すると、平坦絶縁膜330がカラーフィルター層40上に配置され得、遮光膜30の開口部OP及び第1～第3カラーフィルター層(321、323、325)の開口を満たす。

平坦絶縁膜330は、光感度を向上させるためにシリコン酸化物より屈折率が大きい物質で形成される。

平坦絶縁膜330は、例えば約1.4～約4.0の屈折率を有する物質で形成される。

平坦絶縁膜330は、例えばAl<sub>2</sub>O<sub>3</sub>、CeF<sub>3</sub>、HfO<sub>2</sub>、ITO、MgO、Ta<sub>2</sub>O<sub>5</sub>、TiO<sub>2</sub>、ZrO<sub>2</sub>、Si、Ge、ZnSe、ZnS、又はPbF<sub>2</sub>等が使用される。

#### 【0050】

これとは異なって、平坦絶縁膜330は、高屈折率の有機物で形成することもでき、例えば、シロキサン樹脂(Siloxane Resin)、BCB(Benzocyclobutene)、polyimide系列、acryl系列、Parylene C、PMMA(Poly(methyl methacrylate))、PET(Polyethylene terephthalate)等が使用され得る。

また、平坦絶縁膜330は、例えば「strontium titanate」(SrTiO<sub>3</sub>)、「polycarbonate」、「glass」、「bromine」、「sapphire」、「cubic zirconia」、「potassium niobate」(KNbO<sub>3</sub>)、「moissanite」(SiC)、「gallium(III) phosphide」(GaP)、「gallium(III) arsenide」(GaAs)等でも形成され得る。

#### 【0051】

平坦絶縁膜330上に複数のマイクロレンズMLが第1及び第2方向D1、D2に沿つ

10

20

30

40

50

て 2 次元的に配列される。

マイクロレンズ M L の各々は、第 1 光電変換領域 1 1 0 a に対応して配置される。

マイクロレンズ M L は、上に膨らんでいる（上に凸）形状を有し、所定の曲率半径を有する。

マイクロレンズ M L は、イメージセンサーに入射する光の経路を変更させて遮光膜 3 0 の開口部 O P に光を集光させる。

マイクロレンズ M L は、光透過性樹脂で形成され得る。

実施形態によれば、マイクロレンズ M L は、遮光膜 3 0 の開口部 O P に各々対応して配置される。

マイクロレンズ M L の中心は、入射光が遮光膜 3 0 の開口部 O P に集光されるように遮光膜 3 0 の開口部 O P の中心に整合される。 10

#### 【 0 0 5 2 】

マイクロレンズ M L は、遮光膜 3 0 の開口部 O P の幅 W 2 より大きい直径 W 3 を有する。

マイクロレンズ M L の直径 W 3 は、各ピクセル領域（P × 1、P × 2）の幅 W 1 より大きい。

一例として、マイクロレンズ M L の直径 W 3 は、各ピクセル領域（P × 1、P × 2）の幅 W 1 の約 2 倍である。

一例として、マイクロレンズ M L の各々は、平面視で第 1 光電変換領域 1 1 0 a と完全に重畠され、第 2 光電変換領域 1 1 0 b と部分的に重畠される。

言い換えれば、マイクロレンズ M L 間の境界が第 2 光電変換領域 1 1 0 b 上に配置される。 20

実施形態で、マイクロレンズ M L の曲率は、遮光膜 3 0 の開口部 O P の幅 W 2、遮光膜 3 0 と光電変換領域（1 1 0 a、1 1 0 b）との間の垂直的距離、及び遮光膜 3 0 とマイクロレンズ M L との間の垂直的距離に基づいて最適化することができる。

#### 【 0 0 5 3 】

以下、図 6～図 17 を参照して本発明の多様な実施形態に係るイメージセンサーに対して説明する。

説明を簡易にするために、図 4、図 5 A、及び図 5 B を参照して説明した構成に対しては同一の参考番号を附し、同様の技術的特徴に対する説明は省略し、相違点に対してのみ説明する。 30

#### 【 0 0 5 4 】

図 6 は、本発明の第 3 の実施形態に係るイメージセンサーの部分平面図であり、図 7 は、本発明の第 3 の実施形態に係るイメージセンサーの断面図であって図 6 の I I - I I ' 線に沿って切断した断面図である。

図 6 及び図 7 を参照すると、先に説明したように、第 1 ピクセル領域 P × 1 の各々の周囲に第 2 ピクセル領域 P × 2 が配置される。

遮光膜 3 0 の開口部 O P が、平面視でジグザグ形状に配列される。

言い換えれば、偶数列の開口部 O P と奇数列の開口部 O P がずれるように配列される。

したがって、第 1 方向 D 1 に隣接する開口部 O P の間隔と第 2 方向 D 2 に隣接する開口部 O P の間の間隔が異なる。

遮光膜 3 0 の開口部 O P に各々対応するマイクロレンズ M L もまたジグザグ形状に配列される。 40

マイクロレンズ M L の各々は、第 1 光電変換領域 1 1 0 a と完全に重畠され、第 2 光電変換領域 1 1 0 b と部分的に重畠される。

#### 【 0 0 5 5 】

図 8 A～図 8 D は、本発明の第 4～第 7 の実施形態に係るイメージセンサーの部分平面図である。

図 8 A 及び図 8 B を参照すると、イメージセンサーは、ピクセル分離構造体 1 0 3 によって定義された複数の第 1 ピクセル領域 P × 1 及び第 2 ピクセル領域 P × 2 を含む。

半導体基板 1 0 0 上の遮光膜 3 0 は、第 1 ピクセル領域 P × 1 の各々に対応して開口部

10

20

30

40

50

O P を有する。

さらに、第 1 ピクセル領域 P × 1 の数と第 2 ピクセル領域 P × 2 の数が同数に提供される。

先に説明したように、第 1 ピクセル領域 P × 1 は、遮光膜 3 0 の開口部 O P を通じて光が入射されるセンシングピクセルであり、第 2 ピクセル領域 P × 2 は遮光膜 3 0 によって光が遮断される基準ピクセルである。

#### 【 0 0 5 6 】

図 8 A を参照すると、2 つの第 1 ピクセル領域 P × 1 と 2 つの第 2 ピクセル領域 P × 2 が 1 つのピクセルグループ P G を構成し、第 1 ピクセル領域 P × 1 は互いに対角線方向に隣接し、第 2 ピクセル領域 P × 2 も互いに対角線方向に隣接する。

このような複数のピクセルグループ P G は、第 1 方向 D 1 及び第 2 方向 D 2 に沿って配列される。

マイクロレンズ M L の各々は、各ピクセルグループ P G の中心に整列される。

即ち、各々のマイクロレンズ M L が 2 つの開口部 O P と重畠される。

#### 【 0 0 5 7 】

図 8 B を参照すると、2 つの第 1 ピクセル領域 P × 1 と 2 つの第 2 ピクセル領域 P × 2 が 1 つのピクセルグループ P G を構成する。

第 1 方向 D 1 に隣接する 2 つの第 2 ピクセル領域 P × 2 と 2 つの第 2 ピクセル領域 P × 2 との間に 2 つの第 1 ピクセル領域 P × 1 が配置され、第 2 方向 D 2 に隣接する第 2 ピクセル領域 P × 2 の間に 1 つの第 1 ピクセル領域 P × 1 が配置される。

#### 【 0 0 5 8 】

図 8 C 及び図 8 D を参照すると、3 つの第 1 ピクセル領域 P × 1 と 1 つの第 2 ピクセル領域 P × 2 が 1 つのピクセルグループ P G を構成し、複数のピクセルグループ P G が第 1 方向 D 1 及び第 2 方向 D 2 に沿って配列される。

この実施形態では、第 1 ピクセル領域 P × 1 の数が第 2 ピクセル領域 P × 2 の数より多い。

マイクロレンズ M L は、ピクセルグループ P G の各々に対応して配置される。

#### 【 0 0 5 9 】

図 8 C を参照すると、奇数行での第 1 ピクセル領域 P × 1 の数と偶数行での第 2 ピクセル領域 P × 2 の数が異なる。

また、第 2 ピクセル領域 P × 2 の各々の周囲に第 1 ピクセル領域 P × 1 が配置される。

ここで、マイクロレンズ M L の各々は、3 つの開口部 O P と重畠される。

#### 【 0 0 6 0 】

図 8 D を参照すると、4 つの第 2 ピクセル領域 P × 2 が上下左右にひとかたまりとなつた各々の周囲に、第 1 ピクセル領域 P × 1 が配置される。

#### 【 0 0 6 1 】

図 9 は、本発明の第 8 の実施形態に係るイメージセンサーの平面図であり、図 10 は、本発明の第 8 の実施形態に係るイメージセンサーの断面図であって図 9 の I I I - I I I ' 線に沿って切断した断面図である。

図 9 及び図 10 を参照すると、イメージセンサーは、ピクセル分離構造体 1 0 3 によって定義された複数の第 1 ピクセル領域 P × 1 及び第 2 ピクセル領域 P × 2 を含み、第 1 方向 D 1 に沿って第 1 及び第 2 ピクセル領域 ( P × 1, P × 2 ) が交互に配列され、第 2 方向 D 2 に沿って第 1 及び第 2 ピクセル領域 ( P × 1, P × 2 ) が交互に配列される。

#### 【 0 0 6 2 】

遮光膜 3 0 の開口部 O P が第 1 ピクセル領域 P × 1 の各々に対応して配置される。

第 2 光電変換領域 1 1 0 b の各々は、第 1 方向 D 1 及び第 2 方向 D 2 に隣接する開口部 O P の間に配置される。

マイクロレンズ M L は、マイクロレンズ M L の中心が開口部 O P の中心に整合するよう配置される。

マイクロレンズ M L の各々は、平面視で各第 1 ピクセル領域 P × 1 に提供された第 1 光

電変換領域 110a と完全に重畠される。

マイクロレンズ ML は、各ピクセル領域 ( $P \times 1$ 、 $P \times 2$ ) の幅 (図 4 の W1 参照) の約 2 倍より小さい直径を有する。

#### 【0063】

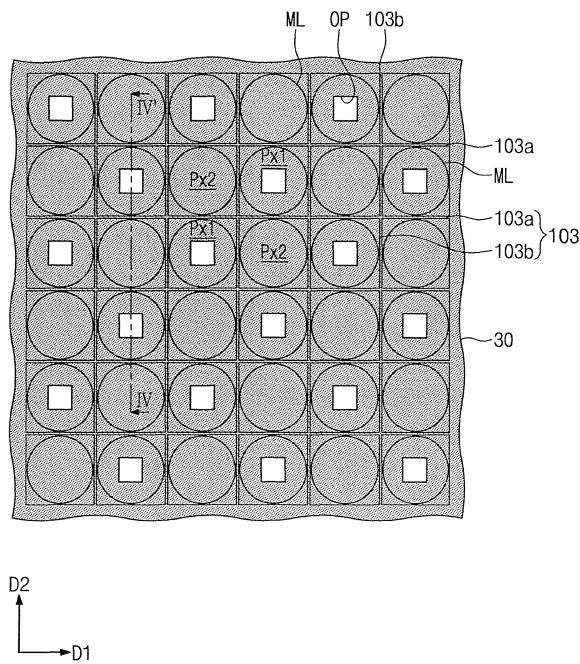

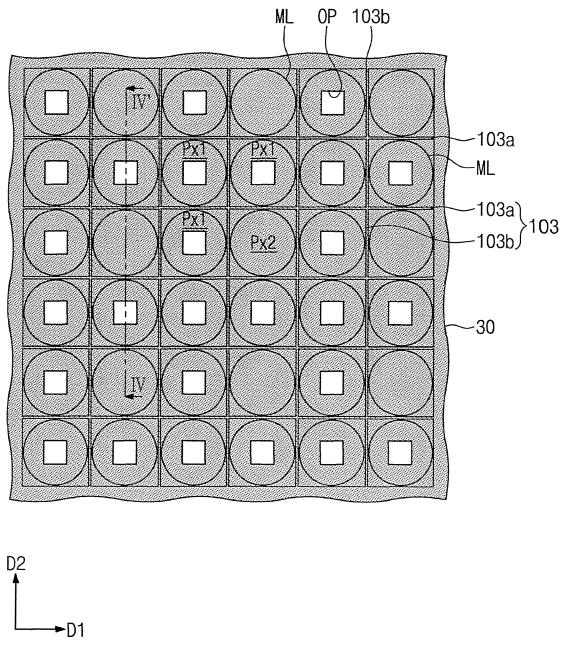

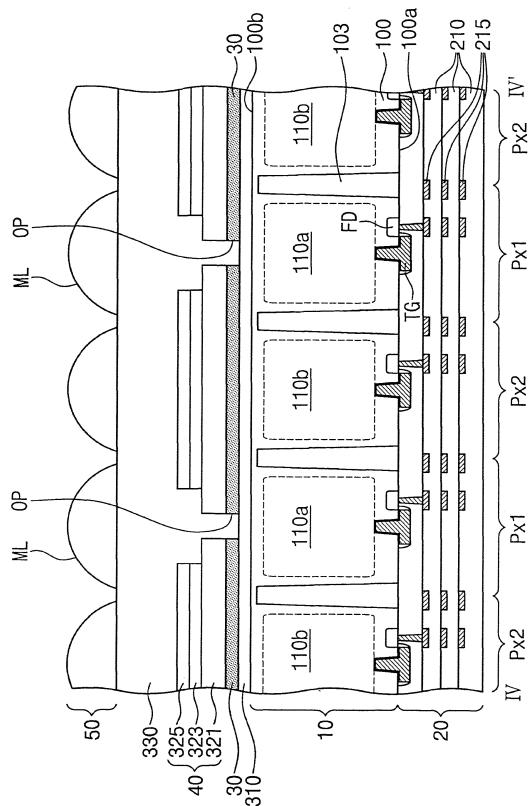

図 11A は、本発明の第 9 の実施形態に係るイメージセンサーの部分平面図であり、図 11B は、本発明の第 10 の実施形態に係るイメージセンサーの部分平面図であり、図 12 は、本発明の第 9、10 の実施形態に係るイメージセンサーの断面図であって図 11A 及び図 11B の IV-IV' 線に沿って切断した断面図である。

図 11A、図 11B、及び図 12 を参照すると、マイクロレンズ ML がピクセル領域 ( $P \times 1$ 、 $P \times 2$ ) の各々に対応して配置される。

10

#### 【0064】

即ち、マイクロレンズ ML の直径は、各ピクセル領域 ( $P \times 1$ 、 $P \times 2$ ) の幅 (図 4 の W1 参照) と実質的に同一であるか、或いは小さい。

また、マイクロレンズ ML の中心が開口部 OP の中心に整合される。

第 2 光電変換領域 110b の各々は、第 1 方向 D1 及び第 2 方向 D2 に隣接する開口部 OP の間に配置される。

#### 【0065】

図 11A を参照すると、第 1 方向 D1 に沿って第 1 及び第 2 ピクセル領域 ( $P \times 1$ 、 $P \times 2$ ) が交互に配列され、第 2 方向 D2 に沿って第 1 及び第 2 ピクセル領域 ( $P \times 1$ 、 $P \times 2$ ) が交互に配列される。

図 11B を参照すると、第 2 ピクセル領域  $P \times 2$  の各々の周囲に第 1 ピクセル領域  $P \times 1$  が配置される。

20

#### 【0066】

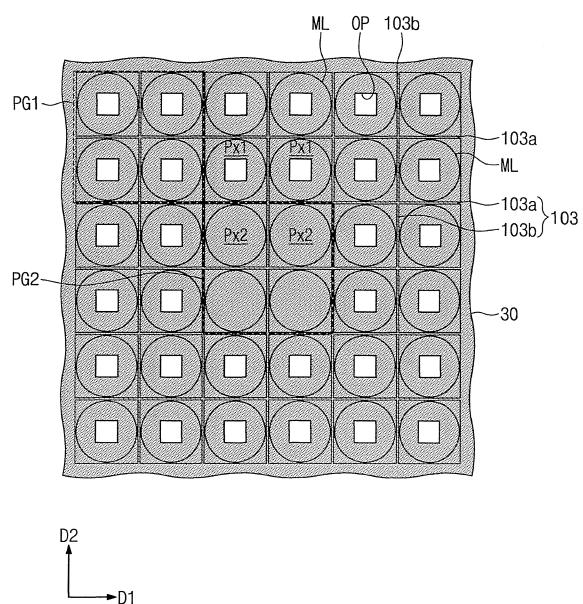

図 13A は、本発明の第 11 の実施形態に係るイメージセンサーの部分平面図であり、図 13B は、本発明の第 12 の実施形態に係るイメージセンサーの部分平面図である。

図 13A 及び図 13B を参照すると、4 つの第 1 ピクセル領域  $P \times 1$  が 1 つの第 1 ピクセルグループ PG1 を構成し、4 つの第 2 ピクセル領域  $P \times 2$  が 1 つの第 2 ピクセルグループ PG2 を構成する。

さらに、マイクロレンズ ML が第 1 及び第 2 ピクセル領域 ( $P \times 1$ 、 $P \times 2$ ) の各々に対応して配置される。

30

即ち、マイクロレンズ ML の直径は、各ピクセル領域 ( $P \times 1$ 、 $P \times 2$ ) の幅 (図 4 の W1 参照) と実質的に同一であるか、或いは小さい。

#### 【0067】

図 13A を参照すると、1 つの第 2 ピクセルグループ PG2 の周囲に複数の第 1 ピクセルグループ PG1 が提供される。

言い換えれば、複数の第 1 ピクセルグループ PG1 が、平面視で 1 つの第 2 ピクセルグループ PG2 を囲む。

図 13B を参照すると、第 1 方向 D1 に沿って第 1 ピクセルグループ PG1 と第 2 ピクセルグループ PG2 が交互に配列され、第 2 方向 D2 に沿って第 1 ピクセルグループ PG1 と第 2 ピクセルグループ PG2 が交互に配列される。

40

#### 【0068】

図 14 は、本発明の第 13 の実施形態に係るイメージセンサーの部分平面図であり、図 15 は、本発明の第 13 の実施形態に係るイメージセンサーの断面図であって図 14 の V-V' 線に沿って切断した断面図である。

図 14 及び図 15 に示す実施形態によれば、イメージセンサーで第 2 ピクセル領域  $P \times 2$  の数が第 1 ピクセル領域  $P \times 1$  の数より多い。

#### 【0069】

詳細には、図 14 及び図 15 を参照すると、「 $3 \times 3$ 」ピクセル領域が 1 つのピクセルグループ PG を構成し、複数のピクセルグループ PG が第 1 方向 D1 及び第 2 方向 D2 に沿って配列される。

50

ここで、1つのピクセルグループPGは、1つの第1ピクセル領域Px1を含み、その周囲に第2ピクセル領域Px2が配置され、遮光膜30は、第1ピクセル領域Px1に各々対応して開口部OPを有する。

一例として、第1又は第2方向(D1、D2)に互いに隣接する開口部OPの間に2つの第2光電変換領域110bが配置される。

マイクロレンズMLは、ピクセルグループPGの各々に対応して配置され、マイクロレンズMLの中心が開口部OPの中心に整合される。

さらに、マイクロレンズMLの直径は、各ピクセル領域(Px1、Px2)幅(図4のW1)の約2倍より大きい。

#### 【0070】

図16は、本発明の第14の実施形態に係るイメージセンサーの部分平面図であり、図17は、本発明の第14の実施形態に係るイメージセンサーの断面図であって図16のV-I-VI'線に沿って切断した断面図である。

図16及び図17を参照すると、「3×3」ピクセル領域が1つのピクセルグループPGを構成し、複数のピクセルグループPGが第1方向D1及び第2方向D2に沿って配列される。

ここで、1つのピクセルグループPGは、4つの第1ピクセル領域Px1を含み、マイクロレンズMLの各々は、4つの第1ピクセル領域Px1と重畠するように配置される。

#### 【0071】

図18は、本発明の実施形態に係るイメージセンサーを含む電子装置の概略を示す斜視図である。

図18を参照すると、電子装置1000は、パネル(タッチセンサーパネル)1100及びパネル1100の一部領域PA下に提供されるイメージセンサーを含む。

本実施形態の例示としては、電子装置1000は、スマートフォン、タブレット、コンピュータ等のような個人用携帯端末機又は移動式電子装置である。

#### 【0072】

イメージセンサーは、先に説明した実施形態に係るイメージセンサーとして、使用者の指紋を感知し、感知した指紋に基づいて認証動作を実行する。

即ち、イメージセンサーは、使用者認証機能を提供する指紋感知センサー又は指紋認識センサーである。

パネル1100は、使用者とのインターフェイシングを提供する。

例えば、使用者は、パネル1100を通じて電子装置1000で提供される多様な情報を見ることができる。

又は、使用者は、パネル1100を通じて電子装置1000に多様な情報を入力することができる。

このために、パネル1100は、使用者のタッチを感知するためのタッチパネル又は使用者に情報を表示するためのディスプレイパネルを含み得る。

#### 【0073】

電子装置1000は、認証された使用者にサービスを提供するために指紋検出の機能を実行する。

電子装置1000は、使用者の指紋に関する情報を収集及び格納することができる。

電子装置1000は、格納された指紋情報に基づいて認証される使用者のみにサービスを提供する。

電子装置1000は、使用者の指紋を検出するために、パネル1100の下部に配置されるイメージセンサーを利用する。

#### 【0074】

電子装置1000の使用者は、客体(object)を通じて電子装置1000に接触する。

例として、客体は使用者の指を含む。

電子装置1000は、パネル1005上の客体の接触(contact)又は近接(P

10

20

30

40

50

`r o x i m i t y`)に応答して、客体を認識する。

パネル1100の一部領域PAに使用者の指が一部領域PAに接触又は近接する時、イメージセンサーは一部領域PAに接触又は近接した指の指紋と関連するイメージを取得する。

電子装置1000は、取得したイメージに基づいて、一部領域PAに接触又は近接した指の指紋が認証された使用者の指紋であるか否かを判別する。

#### 【0075】

図19は、本発明の実施形態に係るイメージセンサーを含む電子装置の概略構成を示すプロック図である。

図19を参照すると、電子装置1000は、タッチセンサーパネル1110、タッチプロセッサ1112、ディスプレイパネル1120、ディスプレイドライバー1122、メインプロセッサ1130、メモリ1140、及びイメージセンサー1200を含む。 10

#### 【0076】

タッチセンサーパネル1110は、客体(例えば、使用者の指)の接触又は近接を感知することができる。

例として、タッチセンサーパネル1110は、客体の接触又は近接に応答して、感知信号を生成する。

幾つかの実施形態で、タッチセンサーパネル1110は、列(Row)及び行(Column)に沿って形成される複数の感知キャパシターを含み得る。

タッチプロセッサ1112は、タッチセンサーパネル1110から出力される感知信号に基づいて、客体の接触又は近接に関する動作を処理する。 20

一例として、感知信号が特定アプリケーションの実行又は動作と関連する場合、タッチプロセッサ1112は、この特定アプリケーションが実行されるか、或いは動作するようメインプロセッサ1130に命令を出力する。

#### 【0077】

ディスプレイパネル1120は、イメージを表示するために、列及び行に沿って配列される複数のピクセルを含む。

ディスプレイパネル1120の各ピクセルは、イメージを形成する特定色相の光を放射(Emit)するように構成される。

複数のピクセルが共に光を放射することによって、ディスプレイパネル1120は意図したイメージを表示することができる。 30

図にはタッチセンサーパネル1110とディスプレイパネル1120が別個に示してあるが、タッチセンサーパネル1110及びディスプレイパネル1120は1つのパネルで具現されてもよい。

ディスプレイドライバー1122は、ディスプレイパネル1120を駆動させる。

ディスプレイドライバー1122は、メインプロセッサ1130の命令に応答して、意図したイメージが表示されるようにディスプレイパネル1120の各ピクセルを駆動させる。

#### 【0078】

メインプロセッサ1130は、電子装置1000の機能を提供するために多様な計算/論理演算を実行/処理することができる。 40

メインプロセッサ1130は、マイクロプロセッサ(microprocessor)、中央処理装置(central processing unit(CPU))を含む。

メインプロセッサ1130は、アドレスバス(Address bus)、制御バス(Control bus)及びデータバス(Data bus)を通じてタッチプロセッサ1112、ディスプレイドライバー1122、メモリ1140、及びイメージセンサー1200と通信を実行する。

#### 【0079】

メモリ1140は、電子装置1000の動作に必要であるデータを格納する。

例えば、メモリ1140は、DRAM(dynamic random access

50

memory (RAM) )、モバイル (mobile) DRAM、SRAM (static RAM)、又はフラッシュメモリ (Flash Memory) 等を含む。

イメージセンサー 1200 は、ディスプレイパネル 1120 から放射される光に基づいて、ディスプレイパネル 1120 の一部領域 PA 上の客体に関するイメージ信号（例えば、指の指紋を指示するイメージを形成するための信号）を生成 / 出力する。

#### 【0080】

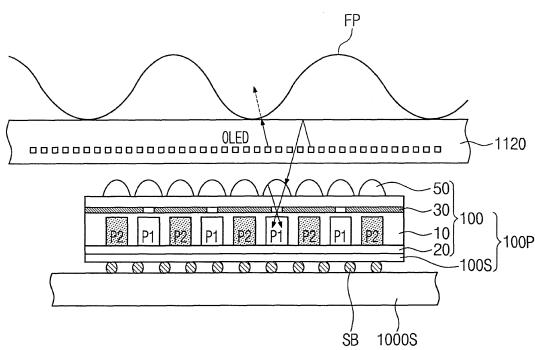

図 20 は、本発明の実施形態に係るイメージセンサーを含む電子装置の構成の一部を示す断面図であり、図 21 は、図 20 に示した電子装置をより詳細に示す断面図である。

図 20 及び図 21 を参照すると、電子装置 1000 は、ディスプレイパネル 1120、イメージセンサーパッケージ 100P、及びボード 1000S を含む。

10

#### 【0081】

ディスプレイパネル 1120 は、1つ又は複数のカラーを有する光を発光してディスプレイ動作を実行する OLED (Organic Light-Emitting Diode) を含む OLED ディスプレイパネルである。

しかし、本発明はこれに制限されず、LCD ディスプレイパネル等多様な種類のディスプレイパネルを利用することができます。

イメージセンサーパッケージ 100P は、パッケージ基板 100S 及びパッケージ基板 100S 上に実装されたイメージセンサーを含む。

イメージセンサーパッケージ 100P は、接着剤 150 によってディスプレイパネル下に付着され得る。

20

#### 【0082】

パッケージ基板 100S は、印刷回路基板 PCB であり、パッケージ基板 100S の下面に複数のソルダボール SB が付着され得る。

パッケージ基板 100S の上面にソルダボールと電気的に接続された接続パッドが形成される。

パッケージ基板 100S の接続パッドは、貫通ビアを通じてイメージセンサー 1200 の読み出回路層 20 と電気的に接続される。

したがって、入射光によってイメージセンサー 1200 から出力される電気的信号がパッケージ基板 100S のソルダボール SB を通じて他の外部装置（例えば、メインプロセッサ）に伝達され得る。

30

#### 【0083】

イメージセンサー 1200 は、先に説明したように、複数のセンシングピクセル P1 及び基準ピクセル P2 を含む。

指紋 FP によって反射された光がマイクロレンズアレイ 50 を通じて入射され、遮光層 30 の開口を通じてセンシングピクセル P1 に入射される。

センシングピクセル P1 は、指紋 FP の互いに異なる領域によって反射された光をセンシングし、センシングされた光に対応する電気信号を出力する。

センシングピクセル P1 は、指紋 FP のリッジ (ridge) で反射した光に対応する電気信号を発生するか、或いはリッジ間の谷 (valley) で反射した光に対応する電気信号を発生する。

40

#### 【0084】

光が反射された指紋 FP の形状に応じて光電変換素子でセンシングされた光の量は変化し、センシングされた光の量に応じて互いに異なるレベルを有する電気信号が生成される。

即ち、センシングピクセル P1 から出力される電気的信号は、各々明暗情報（又は、イメージ情報）を含み、センシングピクセル P1 及び基準ピクセル P2 から出力される電気的信号に基づく信号処理を通じて各センシングピクセル P1 に対応する領域がリッジであるか、又は谷であるかが判断され、判断された情報を組み合わせることによって全体的な指紋イメージが構成される。

#### 【0085】

ボード 1000S は、スマートフォン等の PCB のようなマザーボード (mother

50

**b o a r d**)に該当し得、イメージセンサーパッケージ100Pがボード1000Sと接続されることによって、イメージセンサーパッケージ100Pはチップ・オン・ボード(**c h i p o n b o a r d**)形態に実装される。

また、イメージセンサーパッケージ100Pの一面に形成された接続端子を通じてイメージデータをボード1000Sに提供することができ、一実施形態によれば、イメージデータは、イメージセンサーパッケージ100Pの一面に提供されたソルダボールSBを通じてボード1000Sにイメージデータを提供する。

#### 【0086】

尚、本発明は、上述の実施形態に限られるものではない。本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

10

#### 【符号の説明】

##### 【0087】

- |             |                  |    |

|-------------|------------------|----|

| 1           | アクティブピクセルセンサーアレイ |    |

| 2           | 行デコーダー           |    |

| 3           | 行ドライバー           |    |

| 4           | 列デコーダー           |    |

| 5           | タイミング発生器         |    |

| 6           | 相関二重サンプラー        |    |

| 7           | アナログデジタルコンバーター   |    |

| 8           | 出入力バッファ          |    |

| 10          | 光電変換層            | 20 |

| 20          | 読出回路層            |    |

| 30          | 遮光膜              |    |

| 40          | カラーフィルター層        |    |

| 50          | マイクロレンズアレイ       |    |

| 100         | 半導体基板            |    |

| 103         | ピクセル分離構造体        |    |

| 103a        | 第1ピクセル分離膜        |    |

| 103b        | 第2ピクセル分離膜        |    |

| 110a、110b   | (第1、第2)光電変換領域    | 30 |

| 210         | 層間絶縁膜            |    |

| 215         | 接続配線             |    |

| 310         | バッファ絶縁膜          |    |

| 321、323、325 | (第1～第3)カラーフィルター層 |    |

| 330         | 平坦絶縁膜            |    |

| 1000        | 電子装置             |    |

| 1110        | パネル(タッチセンサーパネル)  |    |

| 1112        | タッチプロセッサ         |    |

| 1120        | ディスプレイパネル        |    |

| 1122        | ディスプレイドライバー      | 40 |

| 1130        | メインプロセッサ         |    |

| 1140        | メモリ              |    |

| 1200        | イメージセンサー         |    |

| C P         | 導電パッド            |    |

| M L         | マイクロレンズ          |    |

| O P         | 開口部              |    |

| P           | 単位ピクセル           |    |

| P X 1、P X 2 | (第1、第2)ピクセル領域    |    |

| R 1         | ピクセルアレイ領域        |    |

| R 2         | 制御回路領域           | 50 |

## R 3 パッド領域

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図 5 A】

【図 5 B】

10

20

30

40

【図 6】

【図 7】

50

【図 8 A】

【図 8 B】

10

20

【図 8 C】

【図 8 D】

30

40

50

【図9】

【図10】

10

20

30

40

【図11A】

【図11B】

50

【図 1 2】

【図 1 3 A】

10

【図 1 3 B】

20

【図 1 4】

30

40

50

【図15】

【図16】

10

20

【図17】

【図18】

30

40

50

【図19】

【図20】

10

【図21】

20

30

40

50

---

フロントページの続き

- (72)発明者 金 範 錫

大韓民国 京畿道 華城市 石隅洞 イエダンマウル ウミリンジェイルプンギョンチェアパート 1

12棟 2703号

- (72)発明者 朴 鐘 勳

大韓民国 ソウル特別市 松坡区 忠愍路四街 6 804棟 1702号

- (72)発明者 朴 俊 城

大韓民国 京畿道 華城市 東灘示範ハンビットギル 38 215棟 802号

- 審査官 三沢 岳志

- (56)参考文献 国際公開第2017/045130 (WO, A1)

特表2014-527307 (JP, A)

特開2009-267637 (JP, A)

特開2011-066801 (JP, A)

特開2012-222483 (JP, A)

特開2012-222484 (JP, A)

特開2013-157442 (JP, A)

特開2017-157804 (JP, A)

国際公開第2017/073321 (WO, A1)

特開2008-205940 (JP, A)

- (58)調査した分野 (Int.Cl., DB名)

H04N 25/70

H04N 25/13

H01L 27/146