# (10) **DE 11 2012 001 870 B4** 2018 09 13

(12)

## **Patentschrift**

(21) Deutsches Aktenzeichen: 11 2012 001 870.2

(86) PCT-Aktenzeichen: PCT/US2012/043052

(87) PCT-Veröffentlichungs-Nr.: WO 2012/177585

(86) PCT-Anmeldetag: 19.06.2012

(87) PCT-Veröffentlichungstag: 27.12.2012

(43) Veröffentlichungstag der PCT Anmeldung in deutscher Übersetzung: **27.03.2014**

(45) Veröffentlichungstag

der Patenterteilung: 13.09.2018

(51) Int Cl.: **H01L 23/522** (2006.01)

**H01L 21/768** (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

13/167,107 23.06.2011 US

(73) Patentinhaber:

**GLOBALFOUNDRIES Inc., Grand Cayman, KY**

(74) Vertreter:

Richardt Patentanwälte PartG mbB, 65185 Wiesbaden, DE

(72) Erfinder:

Andry, Paul S., Yorktown Heights, N.Y., US; Farooq, Mukta G., Hopewell Junction, N.Y., US; Hannon, Robert, Hopewell Junction, N.Y., US; lyer, Subramanian S., Hopewell Junction, N.Y., US; Kinser, Emily R., Hopewell Junction, N.Y., US; Tsang, Cornelia K., Yorktown Heights, N.Y., US; Volant, Richard P., Hopewell Junction, N.Y., US

(56) Ermittelter Stand der Technik:

| US | 2007 / 0 293 040 | <b>A</b> 1 |

|----|------------------|------------|

| US | 2009 / 0 032 951 | <b>A1</b>  |

| US | 2010 / 0 237 472 | <b>A</b> 1 |

| WO | 2007/ 110 799    | <b>A2</b>  |

| WO | 2010/ 120 448    | <b>A2</b>  |

|    |                  |            |

## (54) Bezeichnung: Optimierter ringförmiger Kupfer-TSV

- (57) Hauptanspruch: Integrierte Schaltkreisstruktur, die aufweist:

- ein Substrat mit wenigstens einer Halbleitereinheit, die in einer Oberseite desselben ausgebildet ist, sowie einer ersten dielektrischen Schicht, die über der Oberseite abgeschieden ist:

- einen ringförmigen Graben durch die erste dielektrische Schicht hindurch, der sich durch das Substrat hindurch erstreckt, wobei das Substrat innere und äußere Seitenwände des Grabens bildet, wobei die inneren und äußeren Seitenwände durch einen Abstand innerhalb des Bereichs von 5 bis 10 Mikrometern separiert sind;

- einen leitfähigen Pfad innerhalb des Grabens, der sich von einer oberen Fläche der ersten dielektrischen Schicht durch das Substrat hindurch erstreckt, wobei der Pfad Kupfer oder eine Kupfer-Legierung aufweist;

- wobei sich die inneren und äußeren Seitenwände unter einem Winkel innerhalb von 85 bis 90 Grad relativ zu der Oberseite nach innen neigen;

- eine zweite dielektrische Schicht, die eine Zwischenverbindungs-Metallisierung enthält, wobei die Zwischenverbindungs-Metallisierung mit dem leitfähigen Pfad leitfähig verbunden ist, wobei die zweite dielektrische Schicht direkt

auf der ersten dielektrischen Schicht ausgebildet ist und über dem ringförmigen Graben liegt.

#### **Beschreibung**

## Gebiet der Erfindung

**[0001]** Diese Erfindung bezieht sich allgemein auf einen Substrat-Durchkontakt (TSV, Through Substrate Via) in einem integrierten Schaltkreis, spezieller auf einen TSV in einem dreidimensionalen integrierten Schaltkreis mit wenigstens zwei Substraten, die vertikal gestapelt sind.

#### Hintergrund der Erfindung

[0002] Um eine Verbesserung der Leistungsfähigkeit und der Funktionalität von integrierten Schaltkreisen fortzusetzen, hat die Industrie in letzter Zeit eine Technologie entwickelt, um eine vertikale Integration von Chips mit Halbleitereinheiten möglich zu machen, die allgemein als dreidimensionale (3D) Stapeltechnologie bekannt ist. Die gestapelten Substrate können vollständige oder unvollständige Wafer sein, wobei jeder typischerweise mehrere Chips aufweist. Ein 3D-Stapel kann nach einem Bonden in Einzelchips zertrennt werden, um die Einheiten zu separieren, wobei jede Einheit zwei oder mehr Chips aufweist, die vertikal aneinander gebondet sind. Typischerweise beinhaltet ein Halbleiterchip mehrere Schichten von integrierten Schaltungen (z.B. Prozessoren, programmierbare Einheiten, Speichereinheiten etc.), die auf einem Halbleitersubstrat aufgebaut sind. Eine obere Schicht des gebondeten Stapels kann mit einer unteren Schicht des Stapels verbunden sein, indem Substrat-Durchverbindungen oder Substrat-Durchkontakte (TSVs) verwendet werden. Die Bildung des TSV wird als eine besondere Herausforderung verstanden (siehe z.B. Dukovic, et al., Through-Silicon-Via Technology for 3D Integration).

[0003] Unter weiteren Problemen muss ein Durchkontakt, der sich durch ein Halbleitersubstrat hindurch erstreckt, im Allgemeinen ein hohes Aspektverhältnis aufweisen. Das Bilden eines derartigen tiefen Elements ohne ein Schädigen des verbleibenden Substrats und das anschließende Bilden eines leitfähigen Pfades innerhalb des tiefen Elements, der von dem Substrat elektrisch isoliert ist, ist extrem schwierig. Manche haben vorgeschlagen, die Offnung in das Substrat zu ätzen und anschließend das Substrat sehr hohen Temperaturen auszusetzen, wodurch über den gesamten freigelegten Oberflächen eine Oxidschicht gebildet wird, die eine zuverlässige isolierende Schicht ist. Derartige Temperaturen sind inkompatibel mit einem CMOS-BEOL(Back-End-Of-the-Line)-Prozessablauf, so dass ein derartiges Bilden einer Oxidschicht in einer "Durchkontaktzuerst"-Konfiguration erfolgen muss, bevor irgendwelche Halbleitereinheiten (FEOL) oder Zwischenverbindungsverdrahtungen (BEOL) gebildet werden (siehe Andry et al., US 2010/0032764 A1). Kupfer ist aufgrund seiner hohen Leitfähigkeit für TSVs bevorzugt. 'Durchkontakt-zuerst'-Konfigurationen sind jedoch bei Kupfer-Durchkontakten problematisch, da Halbleitereinheiten äußerst anfällig gegen eine Schädigung als Resultat einer Migration von Kupfer in das Substrat sind.

[0004] Kupfer ist in höherem Maße kompatibel mit einem Back-End- oder ,Durchkontakt-in-der-Mitte'-Prozessablauf, die Diskrepanz der thermischen Ausdehnung zwischen dem Kupfer eines TSV und den umgebenden Materialien kann jedoch eine übermäßige thermische Beanspruchung erzeugen und eine Rissbildung verursachen. Edelstein et al., US 7 276 787 B2 ("die '787"), schlägt vor, dieses Problem mittels Verwenden eines ringförmigen TSV anzugehen. Im Besonderen lehrt die '787, eine große Öffnung zu ätzen, eine Serie von Schichten auf den Seitenwänden zu bilden, ohne die Öffnung zu füllen (z.B. einen elektrischen Isolator, verschiedene Barrierenschichten, eine leitfähige Schicht und weitere Isolationsschichten). Zum Abschluss kann der Kern der Öffnung mittels eines Materials gefüllt werden, das so ausgewählt ist, dass es thermische Eigenschaften aufweist, die ähnlich jenen des Substrats sind, so dass die Gesamtstruktur einen effektiven CTE aufweist, der genau zu dem CTE und dem Elastizitätsmodul des Substrats passt.

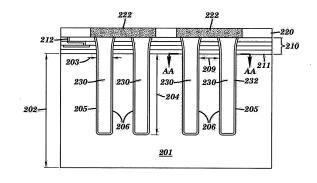

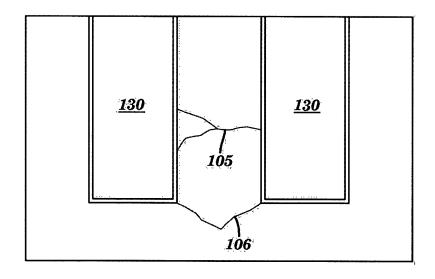

[0005] Selbst ein ringförmiger Kupfer-TSV neigt jedoch dazu, zu extrudieren, wenn er während des CMOS-BEOL-Prozessablaufs thermischen Zyklen unterworfen wird (siehe z.B. Cho, "Technical Challenges in TSV Integration"). Eine Extrusion durch einen TSV kann darüber liegende Metallisierungsschichten beanspruchen, wobei jegliche eingebettete Zwischenverbindungsverdrahtung geschwächt oder kurzgeschlossen wird. Cho stellt SEM-Aufnahmen bereit, die eine Extrusion eines Kupfer-TSV zeigen, die daraus resultieren, dass er zur Bildung einer Zwischenverbindungs-Metallisierung (BEOL) Prozesstemperaturen ausgesetzt war. Die durch eine derartige Extrusion verursache Schädigung ist in den Fig. 1A und Fig. 1B aufgezeigt. Fig. 1A zeigt, dass der Kupferkern eines massiven TSV 110 über die CMP'd-Oberfläche 104 der Passivierungsschicht 102 extrudiert ist, wobei er darüber liegende Schichten 120 anhebt und die darin eingebettete Zwischenverbindungsverdrahtung 122 beansprucht. Fig. 1B stellt einen Riss 105 durch den inneren Kern und einen Riss 106 dar, der an den unteren inneren Ecken eines ringförmigen Kupfer-TSV 130 beginnt. Cho empfiehlt, die Kupfer-Extrusion zu minimieren, indem der Durchkontakt zuletzt gebildet wird.

[0006] Wenngleich ein 'Durchkontakt-zuletzt'-Prozessablauf im Allgemeinen bei Temperaturen stattfindet, die niedrig genug sind, um eine Kupfer-Extrusion zu vermeiden, braucht 'Durchkontakt-zuletzt' das gesamte TSV-Profil durch sämtliche BEOL-Schichten hindurch, was es für die Zwecke der Prozessin-

tegration und der Chip-Auslegung weit weniger effizient macht. Es wäre äußerst vorteilhaft, eine Technik ausfindig zu machen, um einen zuverlässigen Kupfer-TSV zu bilden, der während des BEOL-Prozessablaufs gebildet werden kann.

[0007] Die US 2010 / 0237472 A1 offenbart mindestens einen Substrat-Durchkontakt, der um den Umfang eines Halbleiterchips ausgebildet ist. Der mindestens eine Substrat-Durchkontakt kann ein einzelner Substrat-Durchkontakt sein, der den Halbleiterchip lateral umgibt, oder kann eine Vielzahl von Substrat-Durchkontakten umfassen, die die Peripherie mit mindestens einer Lücke zwischen den Substrat-Durchkontakten umgeben. Ein Stapel von Back-End-of-Line (BEOL) -Metallstrukturen, die den Halbleiterchip seitlich umgeben, ist direkt auf den Substratkontakt-Durchkontaktierungen ausgebildet und elektrisch mit dem mindestens einen Substrat-Durchkontakt verbunden. Eine metallische Schicht ist auf der Rückseite des Halbleitersubstrats einschließlich des mindestens einen Substrat-Durchkontakts ausgebildet. Die leitende Struktur, die die metallische Schicht, den mindestens einen Substrat-Durchkontakt und den Stapel der BEOL-Metallstrukturen umfasst, fungiert als eine elektrische Masse, die in den Halbleiterchip eingebaut ist.

[0008] Die WO 2010 / 120448 A2 offenbart Substrat-Durchkontakte, die nach im Wesentlichen allen Hochtemperaturoperationen bereitgestellt werden, die benötigt werden, um einen Vorrichtungsbereich mit einer ersten Dicke in der Nähe der Vorderfläche eines Substratwafers zu bilden, durch: (i) Bilden, von der Vorderfläche aus, vergleichsweise flacher Durchkontaktierungen mit einem ersten Seitenverhältnis, die erste Leiter enthalten, die sich vorzugsweise durch die erste Dicke, aber nicht durch die ursprüngliche Waferdicke erstrecken, (ii) Entfernen von Material von der hinteren Oberfläche, um einen modifizierten Wafer mit kleinerer Enddicke mit einer neuen hinteren Oberfläche zu bilden, und (iii) Ausbilden von viel tieferen Durchkontaktierungen mit zweiten Seitenverhältnissen unterhalb der Vorrichtungszone von der neuen Rückfläche aus, wobei zweite Leiter die ersten Leiter kontaktieren, wodurch Front-to-Back-Verbindungen bereitgestellt werden, ohne die Robustheit des Wafers während des Herstellungs- und Vorrichtungsbereichs wesentlich zu beeinflussen. Beide Aspektverhältnisse sind wünschenswerterweise etwa < 40, zweckmäßigerweise < 10 und vorzugsweise < 5.

[0009] Die US 2007 / 0293040 A1 offenbart ein Verfahren zum Füllen eines leitfähigen Materials in ein dreidimensionales Integrationsmerkmal, das auf einer Oberfläche eines Wafers ausgebildet ist. Das Merkmal wird wahlweise mit dielektrischen und / oder Adhäsions- / Sperrschichten ausgekleidet und dann mit einem flüssigen Gemisch gefüllt, das einen leitfähigen Precursor enthält, etwa eine Lösung mit gelös-

tem Ruthenium-Precursor oder eine Dispersion oder Suspension mit leitfähigen Teilchen (z. B. Gold, Silber, Kupfer). Das Substrat wird gedreht, während sich die Mischung auf ihrer Oberfläche befindet. Dann wird der flüssige Träger von dem Merkmal getrocknet, wobei eine leitfähige Schicht in dem Merkmal zurückbleibt. Diese zwei Schritte werden gegebenenfalls wiederholt, bis das Merkmal mit dem Leiter gefüllt ist. Dann wird der Leiter in dem Merkmal getempert, wodurch eine dichte, leitende Verschlusskappe in dem Merkmal gebildet wird.

### Kurzdarstellung der Erfindung

**[0010]** In einem Aspekt der Erfindung wird eine TSV-Struktur bereitgestellt, wobei der TSV während des BEOL-Prozessablaufs gebildet werden kann und eine Belastung durch weitere BEOL-Prozessabläufe tolerieren kann.

[0011] In einer Ausführungsform der vorliegenden Erfindung wird eine integrierte Schaltkreisstruktur bereitgestellt, die einen TSV beinhaltet. Die Struktur beinhaltet ein Substrat mit wenigstens einer Halbleitereinheit, die in einer Oberseite ausgebildet ist, sowie eine erste dielektrische Schicht, die auf einer derartigen Oberseite abgeschieden ist. Der TSV bildet einen ringförmigen Graben, der sich durch das Substrat und die erste dielektrische Schicht hindurch erstreckt, wobei das Substrat die inneren und äußeren Seitenwände des Grabens definiert, wobei die Seitenwände durch einen Abstand innerhalb des Bereichs von 5 bis 10 Mikrometern separiert sind. Ein leitfähiger Pfad. der Kupfer oder eine Kupfer-Legierung aufweist, erstreckt sich innerhalb des Grabens von einer oberen Fläche der ersten dielektrischen Schicht durch das Substrat hindurch, das eine Dicke von 90 Mikrometern oder weniger aufweisen kann. Eine zweite dielektrische Schicht mit einer Zwischenverbindungsmetallisierung, die mit dem leitfähigen Pfad leitfähig verbunden ist, ist direkt auf der ersten dielektrischen Schicht ausgebildet und liegt über dem ringförmigen Graben. Der Innendurchmesser des Grabens kann im Bereich von 4 bis 9 Mikrometern liegen. Die Separation der Seitenwände kann innerhalb des Bereichs von 5,5 und 9 Mikrometern liegen, und der Innendurchmesser des Grabens kann im Bereich von 5 bis 8 Mikrometern liegen. Die Seitenwände weisen eine leichte Neigung auf, die innerhalb von 85 und 90 Grad relativ zu der Oberseite liegt, mit einem bevorzugten Bereich zwischen 87 und 90 Grad. Der leitfähige Pfad kann eine mittlere Kornabmessung von über 2 Mikrometern aufweisen. Ein dielektrischer Überzug mit einer Dicke im Bereich von 0,4 bis 1,5 Mikrometern kann den leitfähigen Pfad von dem Substrat separieren.

**[0012]** In einer Ausführungsform der vorliegenden Erfindung wird ein integrierter Schaltkreis (IC) bereitgestellt, der ein Halbleitersubstrat mit wenigstens

einer Halbleitereinheit, die in einer Oberseite desselben ausgebildet ist, sowie einer ersten dielektrischen Schicht über der Oberseite beinhaltet. Der IC beinhaltet des Weiteren einen ringförmigen Graben, der sich von einer oberen Fläche der ersten dielektrischen Schicht bis zu einer Unterseite des Substrats erstreckt, wobei ein derartiger ringförmiger Graben eine innere Seitenwand aufweist, die einen Substratkern mit einem Durchmesser an der Oberseite zwischen 5 und 8 Mikrometern definiert, wobei die innere Seitenwand zwischen 85 und 90 Grad relativ zu der Oberseite geneigt ist. Der IC beinhaltet einen leitfähigen Pfad innerhalb des ringförmigen Grabens, wobei der Pfad durch einen dielektrischen Überzug von dem Halbleitersubstrat isoliert ist. Der IC beinhaltet eine zweite dielektrische Schicht, die eine Zwischenverbindungsmetallisierung enthält, die mit wenigstens einer Halbleitereinheit leitfähig verbunden ist und über dem ringförmigen Graben liegt. In Ausführungsformen weist der leitfähige Pfad Kupfer oder eine Kupfer-Legierung auf, und das Halbleitersubstrat weist einkristallines Silicium auf. Der dielektrische Überzug kann in der Nähe des Bodens des Grabens eine Dicke aufweisen, die wenigstens 50 Prozent von jener in der Nähe der Oberseite beträgt. Der dielektrische Überzug kann durch eine Kombination von SACVD und PECVD gebildet werden und kann eine Dielektrizitätskonstante, oder einen k-Wert, von 5 oder weniger aufweisen.

[0013] Gemäß einer weiteren Ausführungsform der vorliegenden Erfindung wird ein Verfahren zum Bilden einer widerstandsfähigen TSV-Struktur bereitgestellt. Das Verfahren beinhaltet ein Bilden eines ringförmigen Grabens in einem Substrat, wobei das Substrat wenigstens eine Halbleitereinheit beinhaltet, die in einer Oberseite desselben ausgebildet ist, und der Graben eine innere Seitenwand und eine äußere Seitenwand aufweist, die durch weniger als 10 Mikrometer separiert sind, und sich bis in eine Tiefe von 90 Mikrometern oder weniger erstreckt. Das Verfahren beinhaltet ein Überziehen der inneren und der äußeren Seitenwand mit einem konformen dielektrischen Überzug, ein Füllen des Grabens mit einem leitfähigen Material, das Kupfer oder eine Kupfer-Legierung aufweist; sowie ein Tempern des gefüllten Grabens über 350 °C während wenigstens 20 Minuten. Dabei neigen sich die innere und die äußere Seitenwand unter einem Winkel innerhalb von 85 bis 90 Grad relativ zu der Oberseite nach innen. Der Tempervorgang kann bei einer Temperatur zwischen 350 °C und 430 °C stattfinden und kann sich über eine Stunde oder mehr erstrecken. Ausführungsformen des Verfahrens können ein Bilden des ringförmigen Grabens durch wenigstens eine BEOL-Schicht hindurch, die über der Oberseite aufgebracht ist, sowie ein Bilden einer zweiten BEOL-Schicht auf der wenigstens einen BEOL-Schicht und über dem ringförmigen Graben beinhalten. Das Verfahren kann des Weiteren ein Verringern der Dicke an der Rückseite des Substrats

aufweisen, um das leitfähige Material des gefüllten Grabens freizulegen.

#### Figurenliste

**[0014]** Die exemplarischen Ausführungsformen sowohl bezüglich der Organisation als auch des Betriebsverfahrens können am besten durch Bezugnahme auf die detaillierte Beschreibung, die folgt, in Verbindung mit den begleitenden Figuren verstanden werden.

Fig. 1 A und Fig. 1B stellen eine Schädigung dar, die von einem herkömmlichen TSV verursacht wurde, der einem CMOS-Prozessablauf ausgesetzt war.

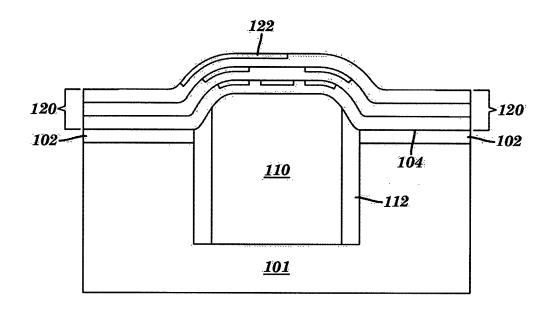

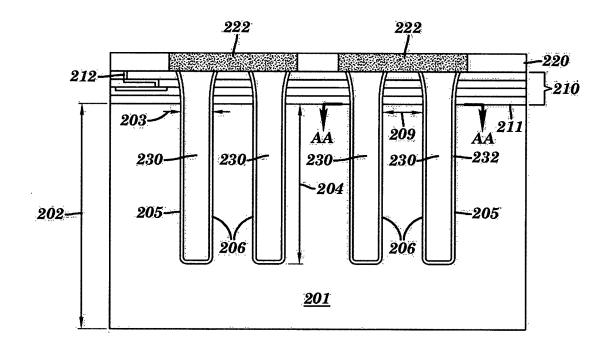

**Fig. 2A** ist eine vertikale Schnittansicht eines ringförmigen TSV gemäß der vorliegenden Offenbarung.

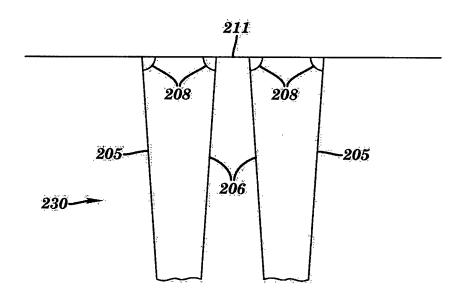

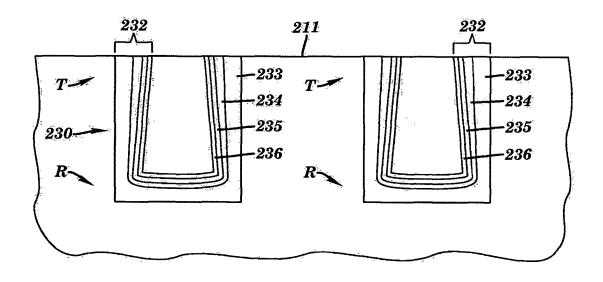

**Fig. 2B** und **Fig. 2D** sind Detailansichten des TSV gemäß der vorliegenden Offenbarung.

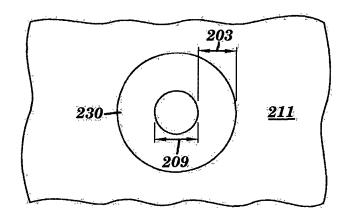

Fig. 2C ist ein Querschnitt bei AA eines TSV von Fig. 2A.

Detaillierte Beschreibung der Erfindung

[0015] Die vorliegende Offenbarung stellt einen thermo-mechanisch zuverlässigen Kupfer-TSV und eine Technik zum Bilden eines derartigen TSV während eines BEOL-Prozessablaufs bereit, der nunmehr mit begleitenden Figuren detailliert beschrieben wird. Es ist anzumerken, dass sich ähnliche Bezugszeichen über verschiedene Ausführungsformen hinweg auf ähnliche Elemente beziehen. Die Zeichnungen sind nicht notwendigerweise maßstabsgetreu gezeichnet.

[0016] Es versteht sich, dass, wenn ein Element, wie eine Schicht, ein Bereich oder ein Substrat, als "auf" oder "über" einem anderen Element liegend bezeichnet wird, dieses direkt auf dem anderen Element liegen kann oder auch zwischenliegende Elemente vorhanden sein können. Im Gegensatz dazu sind keine zwischenliegenden Elemente vorhanden, wenn ein Element als "direkt auf" oder "direkt über" einem anderen Element liegend bezeichnet wird. Es versteht sich außerdem, dass, wenn ein Element als "verbunden" oder "gekoppelt" mit einem anderen Element bezeichnet wird, dieses direkt mit dem anderen Element verbunden oder gekoppelt sein kann oder zwischenliegende Elemente vorhanden sein können. Im Gegensatz dazu sind keine zwischenliegenden Elemente vorhanden, wenn ein Element als "direkt verbunden" oder "direkt gekoppelt" mit einem anderen Element bezeichnet wird.

[0017] Wie angemerkt, zeigt die vorliegende Erfindung eine TSV-Struktur und ein Verfahren für ein zuverlässiges Bilden derselben auf, wobei die Struktur thermischen Zyklen von CMOS BEOL ohne Rissbil-

dung in umgebenden Materialien standhalten kann, wodurch für einen zuverlässigen integrierten 3D-Schaltkreis gesorgt wird.

[0018] Nunmehr bezugnehmend auf Fig. 2A ist ein Halbleitersubstrat 201 mit einer anfänglichen Dicke 202 dargestellt. Eine oder mehrere Halbleitereinheiten (nicht gezeigt) können in und auf einer Oberseite 211 des Substrats gebildet werden. Eine oder mehrere dielektrische Schichten 210 können über der Oberseite 211 abgeschieden werden. Ein ringförmiger Graben 230 kann durch die dielektrischen Schichten 210 hindurch gebildet werden, der sich durch die Oberseite 211 hindurch und in das Substrat 201 hinein erstreckt, wobei herkömmliche back-end-kompatible Lithographie- und Ätzvorgänge verwendet werden. Typischerweise wird der Graben 230 mittels eines Bosch-Atzvorgangs gebildet, der durch ein Alternieren zwischen anisotropen reaktiven Ionenätz- und Polymerabscheidungsschritten abläuft, die Erfindung ist jedoch nicht darauf beschränkt. Der ringförmige Graben 230 kontaktiert zu diesem Zeitpunkt an seinem unteren Ende kein anderes Element, so dass er als ein ,Blind-Durchkontakt' bezeichnet werden kann.

[0019] Das Substrat hierin kann irgendeinen Halbleiter aufweisen, wie beispielsweise Si, SiGe, SiGeC, SiC, Ge-Legierungen, GaAs, InAs, InP und andere III/V- oder II/VI-Verbindungshalbleiter. Zusätzlich zu diesen aufgelisteten Typen von halbleitenden Materialien fasst die vorliegende Erfindung auch Fälle ins Auge, in denen das Halbleitersubstrat ein geschichteter Halbleiter ist, wie beispielsweise Si/SiGe, Si/SiC, Silicium-auf-Isolatoren (SOIs) oder Silicium-Germanium-auf-Isolatoren (SGOIs). Des Weiteren kann das Substrat **201** einkristallin, polykristallin, amorph sein oder eine Kombination von wenigstens zwei von einem einkristallinen Anteil, einem polykristallinen Anteil und einem amorphen Anteil aufweisen. In einer bevorzugten Ausführungsform weist das Substrat 201 einen einkristallinen Silicium-Anteil auf.

[0020] Die dielektrische Schicht 210 kann eine direkt auf dem Halbleitersubstrat aufgebrachte Passivierungsschicht beinhalten, die z.B. SiO<sub>2</sub> aufweist. Optional kann die dielektrische Schicht 210 eine oder mehrere zusätzliche Schichten beinhalten, die eine Kombination von dielektrischen und leitfähigen Materialien 212 aufweisen, z.B. eine oder mehrere BEOL-Zwischenverbindungsebenen einer mehrschichtigen Zwischenverbindungsstruktur, die über der Passivierungsschicht aufgebracht ist. Die dielektrische Schicht 210 kann von einem oder von Kombinationen von irgendeinem auf dem Fachgebiet bekannten, dielektrischen Material gebildet werden, wie beispielsweise einem organischen Isolator (z.B. Polyimid), einem anorganischen Isolator (z.B. Siliciumnitrid oder Siliciumdioxid), einem Low-k-Dielektrikum, wie beispielsweise SiLK™, einem dotierten oder undotierten Silicatglas, einem Organosilicat, BLoK™,

NBLoK<sup>™</sup>, wärmehärtbaren Polyarylenethern (bezugnehmend auf funktionelle Aryl-Gruppen oder inert substituierte funktionelle Aryl-Gruppen, die mittels Bindungen, geschmolzener Ringe oder inert verbindenden Gruppen miteinander verbunden sind, wie zum Beispiel Sauerstoff, Schwefel, Sulfon, Sulfoxid, Carbonyl und dergleichen) oder irgendeinem anderen Typ von dielektrischem Material, das auf einem Substrat abgeschieden oder gebildet werden kann. In Ausführungsformen weist das dielektrische Material einen k-Wert von 5 oder weniger auf.

[0021] Wiederum bezugnehmend auf Fig. 2A ist die Länge 204 des ringförmigen Grabens 230 geringer als die ursprüngliche Dicke 202 des Substrats 201. Die Länge 204 kann weniger als 90 Mikrometer betragen und liegt vorzugsweise im Bereich von 60 Mikrometern oder weniger. An der Oberseite 211 liegt die Breite 203 des ringförmigen Grabens, welche die Separation der inneren Seitenwand 206 und der äußeren Seitenwand 205 ist, innerhalb des Bereichs von 5 bis 10 Mikrometern. Die innere und die äußere Seitenwand des ringförmigen Grabens sind an der Oberseite 211 vorzugsweise durch einen Abstand innerhalb des Bereichs von 5,5 bis 9 Mikrometern separiert.

[0022] Der Ätzprozess zum Bilden des ringförmigen Grabens 230 kann nominell gerade Seitenwände bilden, obwohl die Seitenwände tatsächlich eine ausgekehlte Kontur aufweisen können, wobei jede "Auskehlung' einem einzelnen Ätz-/ Polymerabscheidungs-Zyklus eines Bosch-Prozesses entspricht. Die Höhenabweichung entlang der Oberfläche der Seitenwand oder die "Rauigkeit" ist vorzugsweise minimal, wie beispielsweise zwischen 0 und 0,5 Mikrometer. Insbesondere weicht die Breite des Grabens für eine gegebene vertikale Länge einer einzelnen Auskehlung ,S' um weniger als 10 Prozent ab, d.h. weniger als oder gleich 0,2\*S (was verantwortlich für eine Veränderlichkeit von 10 Prozent auf beiden Seitenwänden ist). Die Seitenwände können senkrecht zu der Oberseite 211 sein oder können leicht geneigt sein. Bezugnehmend auf Figur 2B können die Seitenwände 205 und 206 die gleiche Neigung relativ zu der im Allgemeinen planaren Oberseite 211 aufweisen, es ist jedoch nicht notwendig, dass 205 und 206 die gleiche Neigung aufweisen. Jede Seitenwand und die Oberseite 211 bilden vorzugsweise einen Winkel 208 im Bereich von 87 bis 90 Grad. Gemäß Ausführungsformen der vorliegenden Erfindung sind die Seitenwände 205 und 206 in Richtung der Mitte des Grabens derart angewinkelt, dass sich der ringförmige Durchkontakt 230 mit der Tiefe verengt.

[0023] Fig. 2C ist eine Schnittansicht bei AA von Fig. 2A. Der ringförmige Graben 230 definiert einen inneren Substratkern, der einen kreisförmigen Querschnitt aufweisen kann, so dass der Kern eine im Allgemeinen zylindrische Gestalt bildet. Der Durchmes-

ser **209** des Substratkerns an der Oberseite **211** kann im Bereich von 4 bis 9 Mikrometern liegen und liegt vorzugsweise im Bereich von 5 bis 8 Mikrometern. Der Außendurchmesser des ringförmigen Grabens **230** an der Oberseite **211** kann im Bereich von 18 bis 25 Mikrometern liegen und liegt vorzugsweise im Bereich von 19 bis 23 Mikrometern.

[0024] Eine vergrößerte Ansicht der Schicht 232 ist in Fig. 2D dargestellt. Die Schicht 232 beinhaltet einen isolierenden Überzug 233 und kann außerdem mehrere weitere Schichten für verschiedene Funktionen beinhalten, wie beispielsweise um eine Diffusion zu verhindern. Der isolierende Überzug 233 kann eine hohe Konformität aufweisen und kann zum Beispiel mittels sub-atmosphärischer CVD(SACVD, Sub-Atmospheric CVD)-Abscheidung von SiO<sub>2</sub> oder mittels einer Abscheidung eines fließfähigen Oxids gebildet werden. In bestimmten Ausführungsformen ist die isolierende Schicht 233 am ersten (oder oberen) Ende "T" zwischen 0,4 und 1,5 Mikrometer dick. Der isolierende Überzug 233 kann auf den Seitenwänden des ringförmigen Grabens 230 derart gebildet werden, dass die Dicke auf den Seitenwänden angrenzend an das entfernt liegende Ende "R" relativ zu der Dicke auf den Seitenwänden angrenzend an die Oberseite 211 wenigstens 50 Prozent oder zwischen 65 Prozent und 100 Prozent beträgt. In Ausführungsformen kann der isolierende Überzug 233 einen k-Wert von 5 oder weniger aufweisen.

[0025] Eine dielektrische Abdeckung 234 kann gebildet werden, um den isolierenden Überzug 233 zu schützen. In Ausführungsformen kann eine Abdeckung 234 aus Oxid so gebildet werden, dass sie den isolierenden Überzug 233 innerhalb des Grabens 230 vollständig bedeckt. Die Abdeckschicht 234 kann mittels plasma-unterstützter CVD (PECVD) bis zu einer nominellen Dicke zwischen 100 und 500 nm (1000 und 5000 Å), gemessen auf den Seitenwänden angrenzend an die Oberseite 211, und einer Dicke an dem entfernt liegenden Ende von wenigstens 15 Prozent oder im Bereich von 20 Prozent bis 30 Prozent der nominellen Dicke gebildet werden.

[0026] Die Schicht 232 kann eine oder mehrere Barrieren- oder Haftschichten 235 beinhalten. Eine Barrierenschicht kann zum Beispiel Ta, TaN, Ti, TiN, Ru, RuN, RuTa, RuTaN, W, WN oder irgendein anderes Material aufweisen, das als eine Barriere dienen kann, um zu verhindern, dass ein leitfähiges Material dort hindurch diffundiert. Die tatsächlichen Materialien für eine Barriere können auf der Grundlage von Materialien des leitfähigen TSV-Kerns (z.B. Kupfer) und des isolierenden Überzugs 233 ausgewählt werden. In bestimmten Ausführungsformen kann eine Barriere 235 mittels einer Abscheidung von Ta/TaN mit einer Dicke zwischen 2 bis etwa 50 nm (20 bis etwa 500 Å) gebildet werden, wobei eine Dicke von etwa 5 bis etwa 20 nm (50 bis etwa 200 Å) typischer ist.

Die Diffusionsbarriere kann mittels bekannter Verfahren gebildet werden, wie beispielsweise plasma-unterstützter CVD (PECVD), ALD, PVD, Sputtern, Abscheidung aus einer chemischen Lösung oder Plattieren. Für ein Plattieren beinhaltet die Schicht 232 außerdem eine Keimschicht 236. Für einen Kupfer-TSV kann die Keimschicht 236 mittels herkömmlicher Prozesse, zum Beispiel mittels PVD oder ALD, bis zu einer Dicke innerhalb des Bereichs von 100 bis 900 nm (1000 bis 9000 Å) oder im Bereich von 150 bis 800 nm (1500 bis 8000 Å) gebildet werden.

[0027] Um den TSV mit Kupfer zu füllen, kann ein Prozess für ein Füllen frei von Hohlräumen verwendet werden, wie beispielsweise von Novellus oder Nexx erhältlich. Die leitfähige Füllung kann Kupfer oder irgendein anderes leitfähiges Metall, eine Legierung, die wenigstens ein leitfähiges Metall aufweist, ein leitfähiges Metallsilicid oder Kombinationen derselben aufweisen. Das leitfähige Material ist vorzugsweise ein leitfähiges Metall, wie beispielsweise Cu, W oder Al, wobei Cu oder eine Cu-Legierung (wie beispielsweise AlCu) in der vorliegenden Erfindung äußerst bevorzugt sind. Der Füllprozess kann so gesteuert werden, dass er in einer minimalen Überladung resultiert. Optional kann die Überladung unter Verwendung eines chemischen Nassätzvorgangs auf etwa 2 Mikrometer oder weniger verringert werden.

[0028] Anschließend wird die Struktur getempert, um die mittlere Kornabmessung auf über 2 Mikrometer oder auf eine Abmessung im Bereich von 3 bis 5 Mikrometer zu erhöhen. Das Tempern kann bei einer Temperatur über 300 °C stattfinden. Die Struktur kann während über 15 Minuten oder im Bereich von 20 bis 120 Minuten auf einer hohen Temperatur gehalten werden. In einigen Ausführungsformen wird die Struktur während wenigstens 50 Minuten im Bereich von 335 bis 410 °C gehalten. Die Struktur kann während 20 bis 100 Minuten im Bereich von 350 bis 430 °C gehalten werden.

[0029] Nach dem Tempern kann die verbleibende Überladung entfernt werden. Typischerweise wird die Überladung mittels CMP entfernt, gefolgt von einem Poliervorgang. Optional können mittels eines herkömmlichen BEOL-Prozessablaufs weitere BEOL-Schichten über dem oberen Ende des TSV gebildet werden. An der Oberseite kann eine Struktur angebracht werden, um eine Waferhandhabung zu ermöglichen. Die Rückseite kann geschliffen oder bis zu einer Dicke von 60 bis 90 Mikrometern oder weniger geätzt werden, so dass das untere Ende des TSV freigelegt ist, nach Wunsch gefolgt von einem Bilden von Rückseitenverbindungen an den TSV, die z.B. Passivierungs- und Kontaktstellen beinhalten.

#### **BEISPIEL 1**

[0030] Ringförmige, mit Kupfer plattierte TSVs wurden mit einer minimalen Prozesskomplexität integriert, um die Verdrahtbarkeit zu maximieren. Mittels eines Bosch-Prozesses wurden Blind-Durchkontakte mit einer Tiefe von weniger als 100 Mikrometern bei einem minimalen Rastermaß von 50 Mikrometern mit nahezu vertikalen Seitenwänden hergestellt. Zur Isolation wurde ein abgeschiedenes konformes Oxid mit einer ausgezeichneten Bedeckung an dem Boden des TSV verwendet. Für eine Barrieren- und Keimschicht wurde eine Sputter-Abscheidung verwendet, anschließend eine von Hohlräumen freie Kupfer-Plattierung von unten nach oben, ein Tempervorgang und ein CMP-Vorgang, um die minimale plattierte Überladung zu entfernen. Eine dicke Cu-Verdrahtungsebene nutzt den Vorteil der geringeren Spannungsabfälle, die bei TSVs beobachtet werden, resultiert jedoch in einer zusätzlichen Wölbung. Ein Prozess, der eine äußerst zusammendrückende ILD-Dünnschicht mit einbezieht, wurde an Schlüssel-Durchkontaktebenen verwendet, um die vergrößerte Wölbung zu kompensieren. Fertiggestellte Wafer wurden an Handhaber aus Glas gebondet und die Dicke mittels Schleifen, Polieren, RIE verringert. Es wurde ein PECVD-Oxid/ Nitrid abgeschieden. Nach einem CMP-Vorgang zum Freilegen des TSV-Metalls wurde Kupfer mittels einer Elektroabscheidung aufgebracht, und es wurde eine Rückseiten-Neuverteilungsebene definiert. Die Wafer wurden in Einzelchips zertrennt und unter Verwendung eines Die-Level-C4-Verbindens auf organischen Laminaten montiert. Es wurde ein Prüfen der Zuverlässigkeit durchgeführt. Nach einer Haltezeit bei 399 °C verblieb eine dünne (< 100 nm (1000 Å) Deck(Oberseiten)-Schicht aus SiN intakt. Prüfungen hinsichtlich einer ILD-Schädigung stellten nach thermischen Zyklen zwischen -65 °C und 150 °C während 500 Zyklen keine Änderung in der Leckage zwischen Verdrahtungsebenen fest. Thermische Zyklen zeigten außerdem keine Degradation im Widerstand des TSV oder der Funktionalität von Einheiten in der Nähe des TSV.

#### Patentansprüche

- 1. Integrierte Schaltkreisstruktur, die aufweist:

- ein Substrat mit wenigstens einer Halbleitereinheit, die in einer Oberseite desselben ausgebildet ist, sowie einer ersten dielektrischen Schicht, die über der Oberseite abgeschieden ist;

- einen ringförmigen Graben durch die erste dielektrische Schicht hindurch, der sich durch das Substrat hindurch erstreckt, wobei das Substrat innere und äußere Seitenwände des Grabens bildet, wobei die inneren und äußeren Seitenwände durch einen Abstand innerhalb des Bereichs von 5 bis 10 Mikrometern separiert sind;

- einen leitfähigen Pfad innerhalb des Grabens, der sich von einer oberen Fläche der ersten dielektri-

- schen Schicht durch das Substrat hindurch erstreckt, wobei der Pfad Kupfer oder eine Kupfer-Legierung aufweist:

- wobei sich die inneren und äußeren Seitenwände unter einem Winkel innerhalb von 85 bis 90 Grad relativ zu der Oberseite nach innen neigen;

- eine zweite dielektrische Schicht, die eine Zwischenverbindungs-Metallisierung enthält, wobei die Zwischenverbindungs-Metallisierung mit dem leitfähigen Pfad leitfähig verbunden ist, wobei die zweite dielektrische Schicht direkt auf der ersten dielektrischen Schicht ausgebildet ist und über dem ringförmigen Graben liegt.

- 2. Struktur nach Anspruch 1, wobei die inneren und äußeren Seitenwände durch einen Abstand innerhalb des Bereichs von 5,5 und 9 Mikrometer separiert sind und der Durchmesser im Bereich von 5 bis 8 Mikrometern liegt.

- 3. Struktur nach Anspruch 1, wobei der leitfähige Pfad eine mittlere Kornabmessung von größer als 2 Mikrometern aufweist.

- 4. Integrierter Schaltkreis, der aufweist: ein Halbleitersubstrat mit wenigstens einer Halbleitereinheit, die in einer Oberseite desselben ausgebildet ist:

einen ringförmigen Graben, der sich von der Oberseite zu einer Unterseite des Halbleitersubstrats erstreckt, wobei der ringförmige Graben eine innere Seitenwand aufweist, die einen Kern des Halbleitersubstrats definiert, wobei der Kern an der Oberseite einen Durchmesser zwischen 5 und 8 Mikrometern aufweist, wobei die innere Seitenwand zwischen 87 und 90 Grad relativ zu der Oberseite geneigt ist;

einen leitfähigen Pfad innerhalb des ringförmigen Grabens, wobei der leitfähige Pfad durch einen dielektrischen Überzug von dem Halbleitersubstrat isoliert ist;

eine dielektrische Schicht, die eine Zwischenverbindungs-Metallisierung enthält, die mit der wenigstens einen Halbleitereinheit leitfähig verbunden ist, wobei die dielektrische Schicht über dem ringförmigen Graben liegt.

- 5. Struktur nach Anspruch 4, wobei der leitfähige Pfad Kupfer oder eine Kupfer-Legierung aufweist und

- das Halbleitersubstrat einkristallines Silicium aufweist und

- der dielektrische Überzug eine Dicke auf der inneren Seitenwand aufweist, wobei die Dicke in der Nähe der Unterseite wenigstens 50 Prozent der Dicke an der Oberseite beträgt.

- 6. Struktur nach Anspruch 4, wobei der Außendurchmesser des ringförmigen Grabens an der Oberseite zwischen 19 und 23 Mikrometer beträgt.

- 7. Verfahren zum Bilden einer widerstandsfähigen TSV-Struktur, wobei das Verfahren aufweist: Bilden eines ringförmigen Grabens in einem Substrat, wobei das Substrat wenigstens eine Halbleitereinheit aufweist, die in einer Oberseite desselben ausgebildet ist, wobei der Graben eine innere Seitenwand und eine äußere Seitenwand aufweist, die um weniger als 10 Mikrometer separiert sind, und sich bis zu einer Tiefe von 90 Mikrometern oder weniger erstreckt, wobei sich die innere und die äußere Seitenwand unter einem Winkel innerhalb von 85 bis 90 Grad relativ zu der Oberseite nach innen neigen: Überziehen der inneren und äußeren Seitenwände mit einem konformen dielektrischen Überzug; Füllen des Grabens mit einem leitfähigen Material, das Kupfer oder eine Kupfer-Legierung aufweist; Tempern des gefüllten Grabens über 350 °C während wenigstens 20 Minuten.

- 8. Verfahren nach Anspruch 7, das des Weiteren ein Verringern der Dicke an der Rückseite des Substrats aufweist, um das leitfähige Material des gefüllten Grabens freizulegen.

- 9. Verfahren nach Anspruch 7, wobei die Seitenwände eine ausgekehlte Kontur mit einer Rauigkeit von weniger als 10 Prozent aufweisen.

Es folgen 3 Seiten Zeichnungen

# Anhängende Zeichnungen

FIG. 1A

FIG. 1B

FIG. 2A

FIG. 2B

FIG. 2C

FIG. 2D