(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-221915

(P2007-221915A)

(43) 公開日 平成19年8月30日(2007.8.30)

(51) Int.C1.

HO2M 3/28

(2006.01)

F1

HO2M 3/28

Q

テーマコード(参考)

5H73O

審査請求 未請求 請求項の数 4 O L (全 14 頁)

(21) 出願番号

特願2006-39418 (P2006-39418)

(22) 出願日

平成18年2月16日 (2006.2.16)

(71) 出願人 592018685

株式会社ウインズ

静岡県沼津市米山町2番24号

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100075672

弁理士 峰 隆司

(74) 代理人 100109830

弁理士 福原 淑弘

最終頁に続く

(54) 【発明の名称】 DC - DC コンバータ

## (57) 【要約】

【課題】小出力時においても高い変換効率を有し、部品点数が削減されたDC - DCコンバータを提供するにある。

【解決手段】DC - DCコンバータは、電圧共振回路を備え、この電圧共振回路には、低電圧直流電源からの電力が入力され、ゼロ電圧スイッチングによりDC - AC変換される。AC変換された電力は、絶縁型高周波トランスに供給され、トランスの2次側に配置された電流共振回路で電流共振されて倍電圧整流回路及びスイッチング回路で倍電圧に変換される。変換された倍電圧は、平滑回路で平滑化されて出力される。

【選択図】図1

図1

## 【特許請求の範囲】

## 【請求項 1】

出力電圧が変動する低電圧直流電源から直流電力が入力され、DC - AC変換して出力する第1の電圧共振回路と、

1次側及び2次側を有し、その1次側に前記第1の電圧共振回路からの出力電圧が入力される第1の絶縁型高周波トランスと、

前記第1のトランスの2次側の第1端子に接続されるチョークコイル及びこのチョークコイルに夫々直列に接続される第1及び第2キャパシタから成る第1の電流共振回路と、

第1及び第2のダイオードが直列接続された第1のダイオード接続、この第1のダイオード接続に並列に接続された第3キャパシタ、第2及び第3のダイオードが直列接続された第2のダイオード接続、この第2のダイオード接続に並列に接続された第4キャパシタとから構成され、この第1及び第2のダイオード接続間の接続点並びに第3及び第4のキャパシタ間の接続点が前記第1のトランスの2次側の第2端子に接続され、前記第3キャパシタが前記第1及び第2のダイオード間の接続点に接続され、前記第4キャパシタが前記第3及び第4のダイオード間の接続点に接続されている倍電圧回路と、

前記第3及び第4キャパシタの一方の電圧或いは前記第3及び第4キャパシタの直列接続の電圧を切り替えるスイッチング回路と、

このスイッチング回路からの出力を平滑化して出力する平滑回路と、

を具備することを特徴とするDC - DCコンバータ。

## 【請求項 2】

前記第1及び第2の電圧共振回路は、夫々スイッチング素子を含み、ゼロ電圧スイッチングによりDC - AC変換して高周波の電圧を出力することを特徴とする請求項1のDC - DCコンバータ。

## 【請求項 3】

前記第1及び第2の電圧共振回路は、ブリッジ型又はブッシュプル型のいずれかであることを特徴とする請求項2に記載のDC - DCコンバータ。

## 【請求項 4】

前記スイッチング回路は、前記第3及び第4キャパシタの一方に並列に接続されたダイオード及びスイッチング素子の直列回路から構成され、前記平滑回路は、前記第3及び第4キャパシタの直列接続に並列接続されたチョークコイル及び第5のキャパシタから構成され、この第5のキャパシタの両端電圧が出力されることを特徴とする請求項1に記載のDC - DCコンバータ。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

この発明は、DC - DCコンバータに係り、特に、分散型直流電源からの電力を1kW以下の中電力容量の電力に変換する分散型電源用の絶縁型DC - DCコンバータ及びこのDC - DCコンバータを用いた連系インバータに関する。

## 【背景技術】

## 【0002】

分散型直流電源、例えば、家庭用燃料電池、太陽光発電或いは風力発電システムから電力を中電力容量(0.3kW ~ 10kW)の電力に変換する分散型電源システムは、インバータなどの電力変換装置を備え、この電力変換装置では、入力(1次側)と系統(2次側)との絶縁が望まれている。このような電力変換装置に、高周波絶縁型のコンバータが使用されても、非絶縁型のコンバータに比較して、効率が悪化する問題がある。

## 【0003】

DC - DCコンバータに関しては、特許文献1、特許文献2及び特許文献3が知られている。この特許文献1、特許文献2及び特許文献3には、スイッチング回路を用いて入力信号をスイッチングして変圧器の1次側に入力し、変圧器の2次側からの出力を整流して直流電圧として出力する電源回路を開示している。

10

20

30

40

50

【特許文献1】2001-128452

【特許文献2】特開平9-163734

【特許文献3】特願平11-306724

【発明の開示】

【発明が解決しようとする課題】

【0004】

また、燃料電池などの電源では、定格未満の出力で運転する頻度が必然的に多くなることから、上記のような定格出力時における効率向上はもとより、定格出力の50%以下の小電力の小出力運転時の効率を向上することが重要な課題となっている。

【0005】

このような要請に対して、特許文献1、特許文献2及び特許文献3に開示された電源回路では、単に入力された直流電圧がスイッチングされてトランスを介して出力されることから効率が悪く、出力も安定しない問題があることが指摘されている。

【0006】

このような背景から発明者らは、既に特願2005-077858で小出力運転時の効率を向上することができるDC-DCコンバータを提案している。この提案に係るDC-DCコンバータでは、良好に変換効率を向上できることが判明しているが、更に、回路を構成する部品点数の削減並びに効率向上が望まれている。

【課題を解決するための手段】

【0007】

本発明は、上記問題点を解決するためになされたものであり、その目的は、小出力時においても高い変換効率を有し、部品点数が削減されたDC-DCコンバータを提供することにある。

【0008】

この発明によれば、

出力電圧が変動する低電圧直流電源から直流電力が入力され、DC-AC変換して出力する第1の電圧共振回路と、

1次側及び2次側を有し、その1次側に前記第1の電圧共振回路からの出力電圧が入力される第1の絶縁型高周波トランスと、

前記第1のトランスの2次側の第1端子に接続されるチョークコイル及びこのチョークコイルに夫々直列に接続される第1及び第2キャパシタから成る第1の電流共振回路と、

第1及び第2のダイオードが直列接続された第1のダイオード接続、この第1のダイオード接続に並列に接続された第3キャパシタ、第2及び第3のダイオードが直列接続された第2のダイオード接続、この第2のダイオード接続に並列に接続された第4キャパシタとから構成され、この第1及び第2のダイオード接続間の接続点並びに第3及び第4のキャパシタ間の接続点が前記第1のトランスの2次側の第2端子に接続され、前記第3キャパシタが前記第1及び第2のダイオード間の接続点に接続され、前記第4キャパシタが前記第3及び第4のダイオード間の接続点に接続されている倍電圧回路と、

前記第3及び第4キャパシタの一方の電圧或いは前記第3及び第4キャパシタの直列接続の電圧を切り替えるスイッチング回路と、

このスイッチング回路からの出力を平滑化して出力する平滑回路と、

を具備することを特徴とするDC-DCコンバータが提供される。

【発明の効果】

【0009】

この発明のDC-DCコンバータによれば、部品点数を削減し、回路部品の特性の相違に基づいて共振点がシフトされることを防止し、結果としてスイッチングロスのない高効率の変換を実現することができる。

【発明を実施するための最良の形態】

【0010】

以下、必要に応じて図面を参照しながら、この発明の一実施の形態に係るDC-DCコ

10

20

30

40

50

ンバータを説明する。

【0011】

この発明の一実施の形態に係るコンバータ部（DC - DCコンバータ）は、連系インバータに適用されて分散型電源システムを構成する。分散型電源システムにおいては、出力に変動を伴う直流電源、例えば、燃料電池、太陽電池、或いは、風力発電からの出力（直流電力）がパワーコンディショナーとしての連系インバータに入力され、連系インバータ内のコンバータ部でDC - DC変換され、変換されたDC出力がDC - AC変換を行いうインバータ部で交流出力、比較的小出力（例えば、0.3 kW～数10 kW程度）に変換されて、負荷に、例えば、家庭内の負荷に商用電圧（系統電圧）として出力される。ここで、商用電圧（系統電圧）は、日本では、101V或いは202V（単相3線接続の場合）に相当し、米国では、115V或いは230Vに相当している。

10

【0012】

尚、燃料電池システムでは、コンバータ部に入力電圧として80V以下、現状では、20V～60Vの電圧が入力され、無負荷の際にその出力電圧Voutが最も高く、負荷が大きくなるにつれて電圧が25%～30%程度低下する特性を有している。また、太陽電池モジュールを備える太陽光発電システムでは、1枚の太陽電池モジュールで17～21Vの電圧が出力され、システムとしては、170V～350Vが出力される。その出力電圧Voutは、120V～450Vの範囲で変動される。更に、風力発電システムでは、50V程度の出力電圧Voutが発生されるが、羽根が回転している際には、30V～50Vの範囲で出力が変動される。

20

【0013】

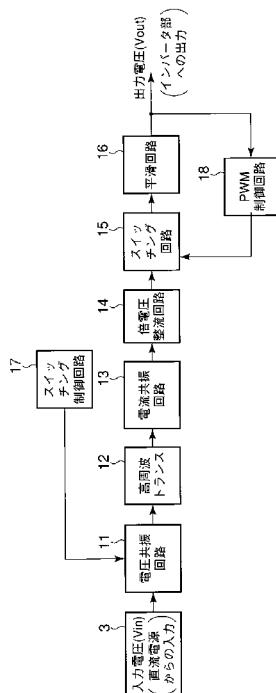

図1は、上述した連系インバータに適用可能なこの発明の一実施の形態に係るコンバータ部の回路構成を示している。

【0014】

図1に示すコンバータ部は、高周波絶縁型のDC - DCコンバータであって、出力に変動を伴う直流電源3からの電圧が入力される電圧共振回路11を備えている。この電圧共振回路11からは、高周波の電圧が出力され、この高周波電圧が高周波トランス12の1次側に入力される。高周波トランス12の二次側には、電流共振回路13が配置され、高周波トランス12から供給される電流がこの電流共振回路13で電流共振される。電流共振回路13の出力電圧は、倍電圧整流回路14に与えられ、倍電圧整流回路14からの出力電圧がスイッチング回路15でスイッチングされることから電流共振回路13の出力電圧は、倍電圧に変換されて平滑回路16を介して出力される。従って、図1に示すコンバータ部には、出力が変動される電圧が入力され、コンバータ部からは、平滑された出力電圧が出力される。

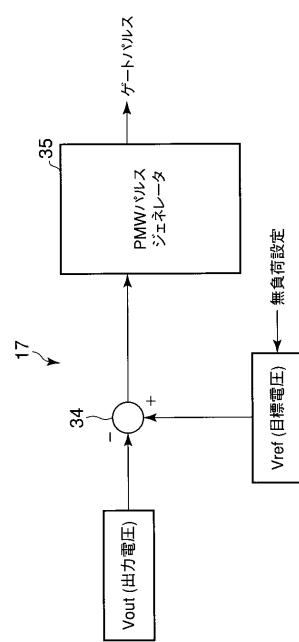

30

【0015】

スイッチング回路15は、この平滑回路16からの出力電圧Voutに応じてスイッチング回路15を制御するパルス幅変調制御回路18（PWM制御回路：Pulse Width Modulation制御回路）を備え、出力電圧Voutに応じて安定して平滑回路15に与えられる。従って、安定した出力電圧が平滑回路16から出力される。

40

【0016】

図1に示されるDC - DCコンバータでは、比較的低電圧な電源3に適用されるため、電圧共振回路11が高周波トランス12の一次側に配置され、高電圧が出力される高周波トランス12の二次側に電流共振回路13が配置されている。一次側に配置された電圧共振回路11は、FET（電界効果トランジスタ）或いはIGBT（絶縁ゲート・バイポーラトランジスタ）等のスイッチング素子を備え、スイッチング素子のソース・ドレイン間（IGBTの場合にはエミッタ・コレクタ間）にキャパシタが接続され、電圧共振回路11が電圧共振するように構成される。また、二次側に配置された電流共振回路13は、直列共振により、電流共振するように構成される。従って、高効率のDC - DCコンバータを実現することができる。

【0017】

50

図1に示される電圧共振回路11は、

- (1) フルブリッジ

- (2) ハーフブリッジ

- (3) プッシュプル

の3通りの回路構成を採用することができる。これら電圧共振回路の具体的な回路例が図2から図4に示されている。

【0018】

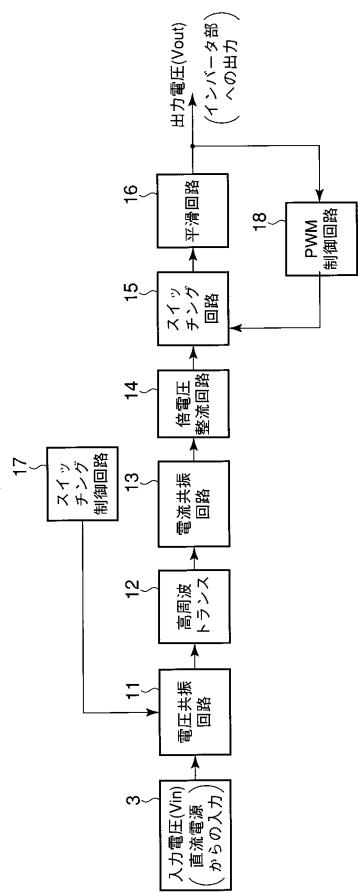

図1に示す電流共振回路13は、倍電圧整流回路14の回路構成を採用することができる。図2から図4を参照して電圧共振回路11の回路例を説明する。尚、図2から図4において、蓄電用のキャパシタC1は、通常電解コンデンサが使用されるが、各回路において共通であるので、説明を省略する。また、スイッチング素子として、FETを用いた場合を説明する。

【0019】

図2は、フルブリッジ回路で電圧共振回路11を構成した第1の回路例を示している。図2に示す電圧共振回路においては、蓄電用のキャパシタC1が直流電源のプラス及びマイナス側の間に接続され、スイッチング素子Q1及びスイッチング素子Q2が直列接続され、スイッチング素子Q3及びスイッチング素子Q4が直列接続されている。スイッチング素子Q1～Q4には、キャパシタC2～C5が夫々スイッチング素子Q1～Q4のソース・ドレイン間に並列に接続されている。また、スイッチング素子Q1、Q2の直列回路及びスイッチング素子Q3、Q4の直列回路がフルブリッジ回路を構成するように夫々入力側の直流電源に並列接続されている。従って、フルブリッジ回路とキャパシタC1とは、直流電源に並列接続されている。即ち、スイッチング素子Q1、Q3のドレインが電源のプラス側に接続され、スイッチング素子Q2、Q4のソースが電源のマイナス側に接続されている。また、スイッチング素子Q1及びスイッチング素子Q2間の接続部が出力側のトランジスタT1の一端部に接続され、スイッチング素子Q3及びスイッチング素子Q4の接続部がトランジスタT1の他端部に接続されている。

【0020】

図2に示すフルブリッジ回路には、スイッチング素子Q1～Q4を所定のタイミングでオン・オフするためにスイッチング制御部17が設けられている。このスイッチング制御部17は、ドライバDR1、DR2、MCU(マイクロコントロールユニット)18から構成されている。このスイッチング制御部17においては、電流共振回路に適する周波数のゲートパルスをスイッチング素子Q1～Q4に与えている。

【0021】

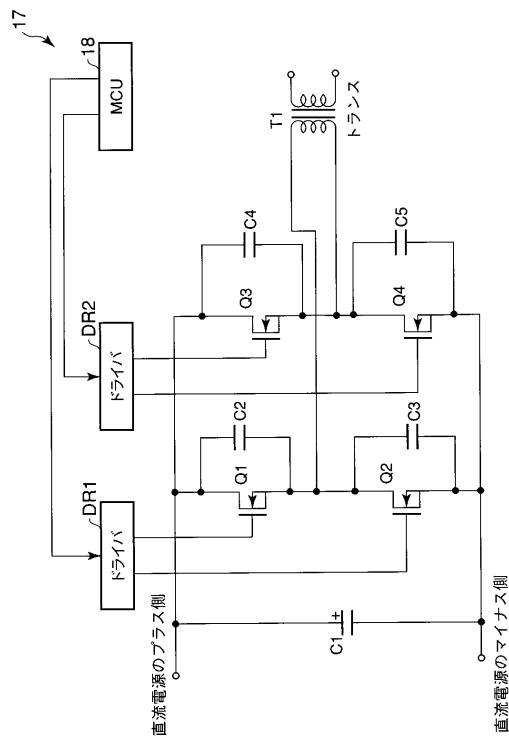

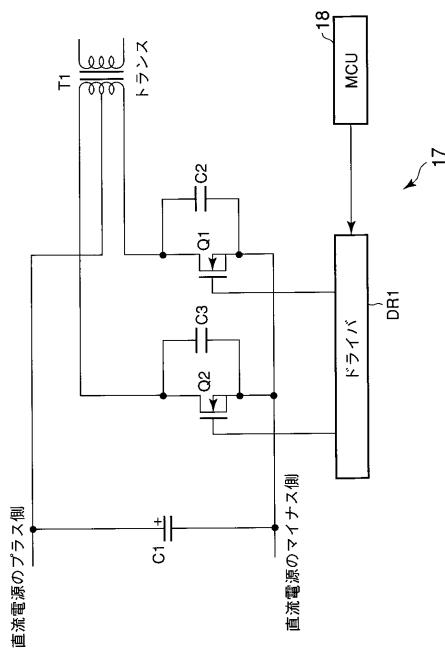

図3は、ハーフブリッジ回路で電圧共振回路11を構成した第2の回路例を示している。図3においては、図2と同一回路部品及び同一部分には、同一符号を付している。

【0022】

図3に示す電圧共振回路においては、スイッチング素子Q1及びスイッチング素子Q2が直列接続され、スイッチング素子Q1、Q2には、キャパシタC2、C3がそれぞれスイッチング素子のソース・ドレイン間に並列に接続されている。また、スイッチング素子Q1、Q2の直列回路には、直列接続されたキャパシタC6、C7が並列接続されてハーフブリッジ回路を構成している。

【0023】

そして、スイッチング素子Q1及びスイッチング素子Q2の接続部がトランジスタT1の一端部に接続され、キャパシタC6及びキャパシタC7の接続部がトランジスタT1の他端部に接続されている。

【0024】

図3に示すハーフブリッジ回路には、スイッチング素子Q1、Q2を所定のタイミングでオン・オフするために、ドライバDR1が設けられている。同様に、電流共振回路に適する周波数のゲートパルスがスイッチング素子Q1、Q2に与えられている。

【0025】

10

20

30

40

50

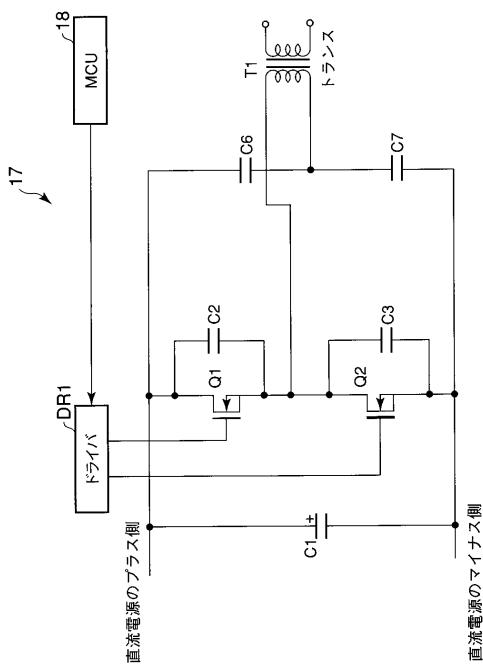

図4は、プッシュプル型で電圧共振回路11を構成した第3の回路例を示している。図4は、プッシュプル型の電圧共振回路を示している。図4においては、図2と同一回路部品及び同一部分には、同一符号を付している。

【0026】

図4において、スイッチング素子Q1のドレインがトランジスト1の一端部に接続され、スイッチング素子Q2のドレインがトランジスト1の他端部に接続され、スイッチング素子Q1、Q2のソースは、直流電源のマイナス側に接続されている。また、直流電源のプラス側は、トランジスト1の一端部と他端部の中間部に接続されている。

【0027】

図4に示すプッシュプル型で電圧共振回路11には、スイッチング素子Q1、Q2を所定のタイミングでオン・オフするために、ドライバDR1が設けられている。スイッチング素子Q1、Q2には、同様に、電流共振回路に適する周波数のゲートパルスが与えられている。

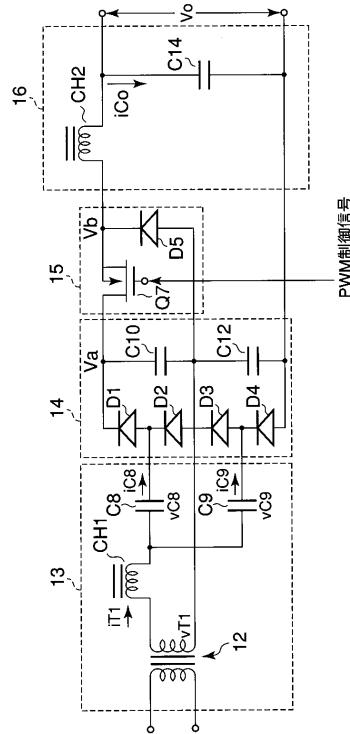

【0028】

図1に示される電流共振回路13、倍電圧整流回路14、スイッチング回路15及び平滑回路16は、一例として図5に示すように構成される。図5に示す回路では、高周波トランジスト12の2次側の高電圧端子にチョークコイルCH1が接続され、また、この2次側の高電圧端子は、2分岐されて夫々にキャパシタC8、C9が接続されて電流共振回路13が構成されている。即ち、高周波トランジスト12の2次側の高電圧端子には、チョークコイルCH1及びキャパシタC8から構成される第1の直列共振回路及びチョークコイルCH1及びキャパシタC9から構成される第2の直列共振回路が接続されている。

【0029】

この第1及び第2の直列共振回路は、倍電圧整流回路14を構成するダイオードD1、D2間の接続点及びダイオードD3、D4間の接続点に夫々接続されている。倍電圧整流回路14では、ダイオードD1、D2の直列回路にダイオードD3、D4の直列回路が接続され、両直列回路間に高周波トランジスト12の2次側の低電圧端子が接続されている。また、ダイオードD1、D2の直列回路には、並列にキャパシタC10が接続され、ダイオードD3、D4の直列回路には、並列にキャパシタC12が接続されて倍電圧整流回路14が構成されている。

【0030】

ダイオードD1、D2の直列回路には、並列にフライホイールダイオードD5及びスイッチングトランジスタQ7の直列回路が接続されてスイッチング回路15が構成されている。このスイッチング回路15では、スイッチングトランジスタQ7がオフされると、フライホイールダイオードD5が高周波トランジスト12の2次側の低電圧端子に接続され、フライホイールダイオードD5のカソードから低電位がチョークコイルCH2に与えられる。これに対して、スイッチングトランジスタQ7がオンされると、キャパシタC8及びダイオードD1を介して高周波トランジスト12の2次側の高電圧電位がキャパシタC10に与えられる。従って、キャパシタC10、C12の直列回路には、倍電圧の電位差が生じ、フライホイールダイオードD5のカソードからは、倍電圧に相当する電位が出力される。

【0031】

フライホイールダイオードD5のカソードには、チョークコイルCH2が接続され、キャパシタC10、C12の直列回路にスイッチングトランジスタQ7を介して並列にチョークコイルCH2及びキャパシタC14の直列回路が接続されている。キャパシタC14の両側は、出力端子に接続されて平滑回路16が構成されている。即ち、図5に示す回路においては、スイッチングトランジスタQ7のオン及びオフ周期に応じて、キャパシタC10、C12の直列回路には、電位差なし及び倍電圧が交互に生じ、倍電圧の振幅を有する交流電圧が平滑回路16に印加されて平滑化された倍電圧が平滑回路16から出力される。

【0032】

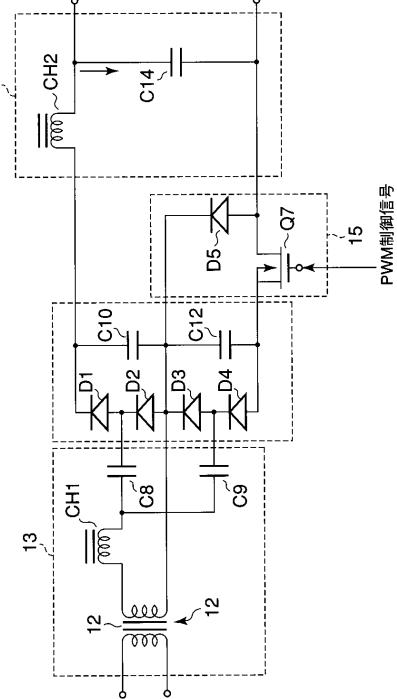

図5に示すフライホイールダイオードD5及びスイッチングトランジスタQ7の直列回

10

20

30

40

50

路からなるスイッチング回路 15 は、図 6 に示されるようにキャパシタ C12 に並列に接続されても良い。即ち、図 6 に示す回路では、スイッチングトランジスタ Q7 がオフされると、フライホイールダイオード D5 が高周波トランス 12 の 2 次側の低電圧端子に接続され、フライホイールダイオード D5 のアノードに低電位が与えられ、ダイオード D1 のアノード側も低電位に維持される。これに対して、スイッチングトランジスタ Q7 がオンされると、キャパシタ C10, C12 間の接続点の電位がキャパシタ C9 及びダイオード D4 を介して高周波トランス 12 の 2 次側の高電圧側電位にまで上昇される。また、キャパシタ C8 及びダイオード D1 を介して高周波トランス 12 の 2 次側の高電圧電位が更にキャパシタ C10 に与えられることから、キャパシタ C10, C12 の直列回路には、倍電圧の電位差が生じ、倍電圧に相当する電位がチョークコイル CH2 に与えられる。

10

### 【0033】

尚、DC - DC コンバータにおいては、図 5 に示されるスイッチングトランジスタ Q7 に PWM 制御信号が与えられて出力が抑制される。

### 【0034】

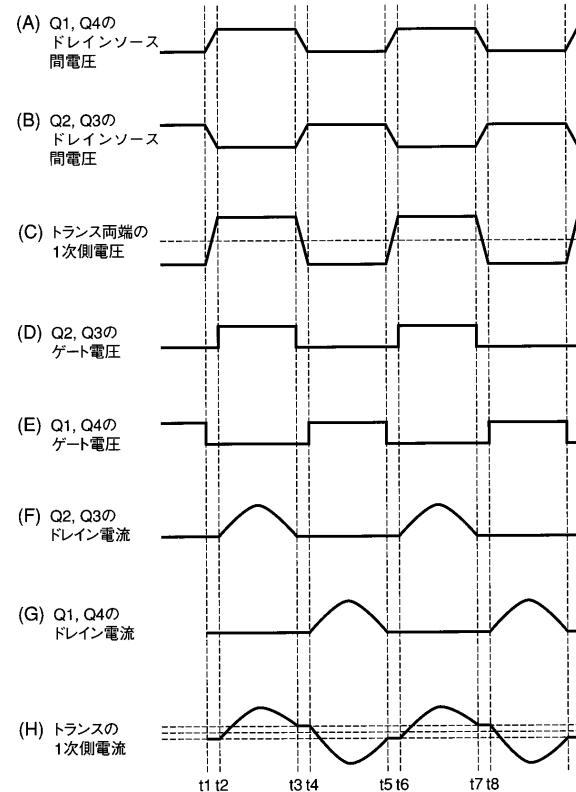

図 2 及び図 8 (A) ~ 図 8 (H) を参照して直流電源 3 が定格で出力電圧 (目標電圧  $V_{out}$ ) を発生する定格出力モードでの DC - DC コンバータの動作について説明する。無負荷モード及び小出力モードでは、各部の電圧並びに電流波形が異なるのみで定格モードでの動作と同様に動作されることからその説明は省略する。

### 【0035】

DC - DC コンバータが図示せぬスイッチを介して直流電源 3 に接続されると、キャパシタ C1 の充電が開始される。同様に、キャパシタ C1 に対して並列に接続されているキャパシタ C2, C3 の直列回路及びキャパシタ C4, C5 の直列回路の充電も開始される。

20

### 【0036】

ある時点  $t_1$  で制御パルス信号がドライバ回路 DR1, DR2 に与えられてドライバ回路 DR1, DR2 が動作される。この時点  $t_1$  において、制御パルス信号に同期して図 8 (E) に示す第 1 及び第 4 のゲート信号が高レベルから低レベルに切り替えられる。従って、図 8 (A) に示すように、第 1 及び第 4 のゲートパルスが与えられていた FETQ1, Q4 は、オフに維持される。

30

### 【0037】

時点  $t_1$  後、トランスの励磁電流によって、FETQ2, Q3 のソース・ドレイン間の電圧が図 8 (B) に示すように低下し始め、図 8 (A) に示すように、FETQ1, Q4 のソース・ドレイン間の電圧が上昇し始める。また、図 8 (C) に示すように、高周波トランス T1 の一次側電圧も降下を開始する。

### 【0038】

時点  $t_1$  から所定時間  $t$  だけ経過した時点  $t_2$  に達すると、FETQ2, Q3 のゲートに図 8 (D) に示される第 2 及び第 3 のゲート信号が与えられ、そのソース・ドレイン間が図 8 (B) に示されるように導通され、FETQ2, Q3 のソース・ドレイン間電圧がゼロに低下され、FETQ2, Q3 は、オン状態に維持される。また、オフに維持される FETQ1, Q4 のソース・ドレイン間電圧は、図 8 (A) に示すように入力電圧に達する。従って、図 8 (C) に示すように高周波トランス T1 の一次側電圧もある所定の電圧に達し、FETQ2, Q3 に電流が供給され、そのドレイン電流が図 8 (F) に示すように増加される。この電流が励磁電流として高周波トランス T1 の一次側に供給され、その結果、その二次側に誘起電圧が発生される。

40

### 【0039】

尚、高周波トランス T1 の 2 次側に接続される電流共振回路のインピーダンスは、FETQ2, Q3 がオンした直後は高いことから、FETQ2, Q3 のドレイン電流はゼロから緩やかに増加される。また、時点  $t_2$  ~ 時点  $t_3$  には、この高周波トランス T1 の 2 次側に接続される電流共振回路の共振周波数に応じて半波の正弦波となるドレイン電流が生ずることとなる。

50

## 【0040】

時点  $t_3$  において、FET Q2, Q3 に与えられていた第2及び第3のゲート信号がオフされると、FET Q2, Q3 がオフされ、ドレイン電流が図8(F)に示すようにゼロとなる。従って、高周波トランスト1の2次側へのエネルギーの供給が停止される。また、図8(B)に示すようにオフされたFET Q2, Q3 のソース・ドレイン間電圧が次第に上昇され、図8(A)に示すようにオフされているFET Q2, Q3 のソース・ドレイン間電圧が次第に上昇される。FET Q2, Q3 のソース・ドレイン間電圧の上昇に伴ってこのFET Q1, Q4 のソース・ドレイン間の電圧が低下する。従って、高周波トランスト1の一次側電圧も次第に低下される。

## 【0041】

時点  $t_3$  から所定時間  $t$  だけ経過した時点  $t_4$  に達すると、FET Q1, Q4 のゲートに図8(E)に示される第1及び第4のゲート信号が与えられ、そのソース・ドレイン間が図8(A)に示されるように導通され、FET Q1, Q4 のソース・ドレイン間電圧がゼロに低下される。時点  $t_4$  から時点  $t_5$  までは、FET Q1, Q4 はオン状態に維持される。また、オフに維持されるFET Q2, Q3 のソース・ドレイン間電圧は、図8(B)に示すように入力電圧に達する。従って、図8(C)に示すように高周波トランスト1の一次側電圧もマイナス側のある所定の電圧に達し、キャパシタC1, C2, C3 から導通したFET Q2, Q3 に電流が供給され、そのドレイン電流が図8(G)に示すように増加される。この電流が励磁電流として高周波トランスト1の一次側に供給され、その結果、その二次側に誘起電圧が発生される。

## 【0042】

ここで、時点  $t_3 \sim t_4$  においては、FET Q1, Q4 に並列に接続されているキャパシタC2, C5 は、緩やかに放電され、従って、FET Q1, Q4 のソース・ドレイン間電圧も緩やかに降下される。その後時点  $t_4$  でFET Q1, Q4 がオンされるが、スイッチングした瞬間ににおけるFET Q1, Q4 のソース・ドレイン間電圧の変化がきわめて少なく、実質的なゼロ電圧共振スイッチング(ZVS)が実現される。

## 【0043】

時点  $t_5$  からは、再び時点  $t_1 \sim t_4$  におけると同様の動作が繰り返されて高周波トランスト1の二次側に誘起電圧が発生される。ここで、時点  $t_5, t_6, t_7, t_8$  は、夫々時点  $t_1, t_2, t_3, t_4$  に相当し、対応する時点の説明を参照されたい。

## 【0044】

ここで、時点  $t_5 \sim t_6$  においても、FET Q1, Q4 に並列に接続されているキャパシタC2, C5 は、同様に緩やかに充電され、従って、FET Q1, Q4 のソース・ドレイン間電圧も緩やかに上昇される。その後時点  $t_6$  でFET Q2, Q3 がオンされるが、スイッチングした瞬間ににおけるFET Q2, Q3 のソース・ドレイン間電圧の変化がきわめて少なく、実質的なゼロ電圧共振スイッチング(ZVS)が実現される。

## 【0045】

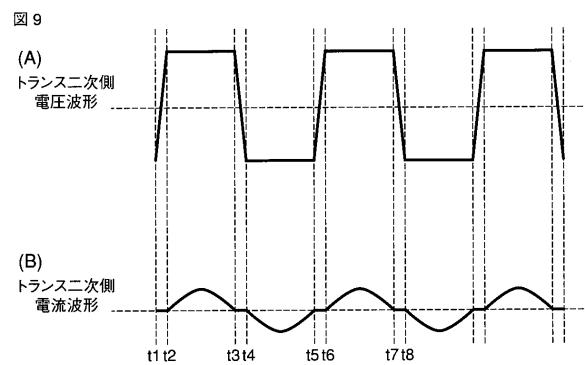

上述したように電圧共振回路が動作されることによって高周波トランスト1の2次側には、図9(A)及び9(B)に示すような電圧波形及び電流波形が出力される。即ち、図8(C)に示される高周波トランスト1の1次側の電圧波形に対応して図9(A)に示すように台形波の電圧が高周波トランスト1の2次側に現れ、また、図8(H)に示される高周波トランスト1の1次側の電流波形に対応して図9(B)に示すように正弦波の電流が高周波トランスト1の2次側に現れる。

## 【0046】

図3に示すハーフブリッジ電圧共振回路11及び図4に示すプッシュプル型電圧共振回路11についての動作は、同様にゼロ電圧共振スイッチング(ZVS)で動作され、図2のフルブリッジ電圧共振回路11の説明を参照すれば当業者であれば、容易に理解することができるところからその説明は省略する。

## 【0047】

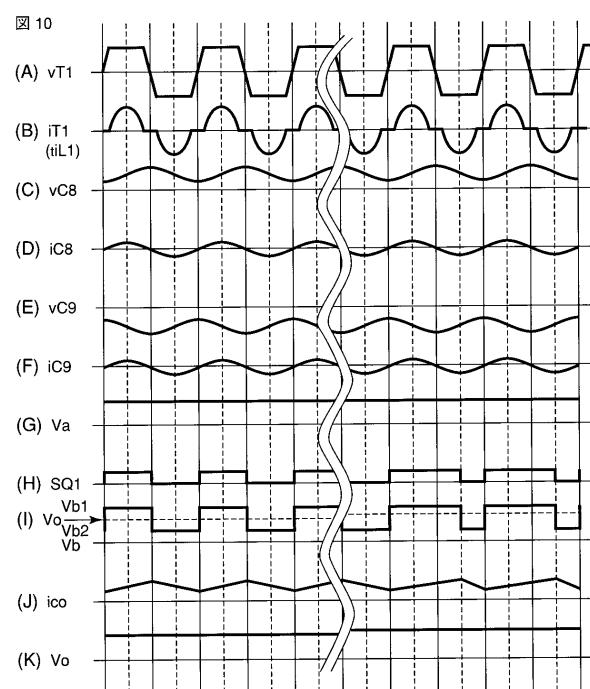

次に図5及び図10(A)～図10(K)を参照して図5に示す回路の動作を説明する

10

20

30

40

50

。

## 【0048】

尚、図6に示される回路も図5に示す回路と略同様に動作されることから、その説明は省略する。

## 【0049】

トランス12の2次側に図10(A)及び10(B)に示すような電圧 $V_{T1}$ 及び電流 $i_{T1}$ が発生されると、電流 $i_{T1}$ がチョークコイルCH1に電流 $i_{L1}$ として流入し、チョークコイルCH1を介してキャパシタC8, C9に供給される。従って、キャパシタC8, C9の両端には、夫々図10(C)及び図10(E)に示すような交流電圧 $v_{C8}$ 、 $v_{C9}$ が生じるとともにキャパシタC8, C9からは、夫々図10(D)及び図10(F)に示すような交流電流 $i_{C8}$ 、 $i_{C9}$ がダイオードD1、D2の接続点及びダイオードD3、D4の接続点に供給される。ダイオードD1を介してキャパシタC10が電流 $i_{C8}$ で充電されるとともにダイオードD3を介してキャパシタC12が電流 $i_{C9}$ で充電される。従って、ダイオードD1の電位が図10(G)に示すように電位 $V_a$ に維持される。ここで、電位 $V_a$ は、キャパシタC10、C12間の電位にキャパシタC10の電圧を加算した実質的な4倍電圧に相当している。10

## 【0050】

図10(H)に示すようにスイッチング素子Q7にPWM制御信号としてスイッチング信号SQ1が与えられると、スイッチング素子Q7がオン及びオフに応じて、電位 $V_b$ がフライホイールダイオードD5のアノードに生ずる。スイッチング素子Q7がオフの際には、電位 $V_a$ がスイッチング素子SQ7を介してフライホイールダイオードD5のカソードに与えられず、図10(I)に示すようにキャパシタC10及びC12間の電位 $V_{b2}$ に対応した電位 $V_b$ がフライホイールダイオードD5のアノードに生ずる。これに対して、スイッチング素子Q7がオンの際には、電位 $V_a$ がスイッチング素子SQ7を介してフライホイールダイオードD5のカソードに与えられ、図10(I)に示すように電位 $V_a$ に対応した電位 $V_{b1}$ がフライホイールダイオードD5のカソードに与えられる。従って、フライホイールダイオードD5のカソード側の電位 $V_b$ は、スイッチング素子Q7のオン及びオフに応じて、電位 $V_{OUT}$ を基準として電位 $V_{b1}$ 及び電位 $V_{b2}$ 間で矩形波として変動される。図10(I)に示される矩形波電位 $V_b$ は、チョークコイルCH2及びキャパシタC14から成る平滑回路16に与えられる。従って、図10(J)に示されるようにこの平滑回路では、平滑電流 $i_{C0}$ でキャパシタC14が充電され、図10(K)に示される出力電圧 $V_{OUT}$ がキャパシタC14の両端電圧として出力される。20

## 【0051】

尚、キャパシタC8、C9は、チョークコイルCH1とで共振回路を構成すると、同時にチャージポンプとして働き、倍電圧整流を実現している。この時、電圧 $V_a$ は、次のように示すことができる。

## 【0052】

$$V_a = 2 \times V_{T10} + 2 \times V_{T12}$$

$V_{T10}$ は、高周波トランス12の正端子電圧であり、 $V_{T12}$ は、高周波トランス12の負端子電圧である。40

## 【0053】

PWM制御において、スイッチング素子Q7をオンとするデューティをdとすると、出力電圧 $V_{OUT}$ は次式にて示すことができる。

## 【0054】

$$V_{OUT} = 2 \times V_{T10} \times d + 2 \times V_{T12}$$

上述したコンバータ回路においては、PWM信号のパルス幅に応じて図10(K)に示されるように平滑回路16からは平滑化された出力電圧 $V_{OUT}$ が出力される。ここで、PWM信号のパルス幅が大きければ、平滑回路16からの出力電圧 $V_{OUT}$ が大きくなり、PWM信号のパルス幅が小さければ、平滑回路16からの出力電圧 $V_{OUT}$ が小さくなる。従って、平滑回路16からの出力電圧がPWM信号発生器18で検出され、適切なパルス幅が選定50

されることによって平滑回路 16 の出力を一定とすることができます。

【0055】

図 5 に示す回路では、トランスの 2 次側には、2 回路ではなく、单一回路が設けられるのみで構成されている。通常、1 つのトランスにおいて、2 次側に 2 回路の 2 次巻き線を施した場合、リーケージインダクタンスの差により、共振周波数のずれが生じてしまう。このリーケージインダクタンスの差を極力少なくするには 2 個のトランスを必要とする。しかし、トランスの 2 次側が单一回路で構成されることから、小出力時においても高い変換効率を有する DC - DC コンバータを提供することができる。

【0056】

以上のように、定格出力時はもちろんのこと、小出力時においても高い変換効率を有する DC - DC コンバータを提供することができる。

【0057】

この発明は、上記各実施の形態に限ることなく、その他、実施段階ではその要旨を逸脱しない範囲で種々の変形を実施し得ることが可能である。さらに、上記各実施形態には、種々の段階の発明が含まれており、開示される複数の構成要件における適宜な組合せにより種々の発明が抽出され得る。

【0058】

また、例えば各実施形態に示される全構成要件から幾つかの構成要件が削除されても、発明が解決しようとする課題の欄で述べた課題が解決でき、発明の効果で述べられている効果が得られる場合には、この構成要件が削除された構成が発明として抽出され得る。

【図面の簡単な説明】

【0059】

【図 1】この発明の一実施の形態にかかる DC - DC コンバータ部の回路構成を示すブロック図である。

【図 2】図 1 に示す電圧共振回路の 1 例を示す回路図である。

【図 3】図 1 に示す電圧共振回路の他の例を示す回路図である。

【図 4】図 1 に示す電圧共振回路の更に他の例を示す回路図である。

【図 5】図 1 に示す電流共振回路、倍電圧回路、スイッチング回路及び平滑回路の回路例を示す回路図である。

【図 6】図 1 に示す電流共振回路、倍電圧回路、スイッチング回路及び平滑回路の他の回路例を示す回路図である。

【図 7】図 5 に示すスイッチング制御回路の MCU の機能を示す制御部ブロック図である。

【図 8】(A) ~ (H) は、図 2 に示す電圧共振回路における各部の波形を示す波形図である。

【図 9】(A) 及び (B) は、図 2 に示す高周波トランスから電圧並びに電流出力を示す波形図である。

【図 10】(A) ~ (K) は、図 5 に示す回路における各部の波形を示す波形図である。

【符号の説明】

【0060】

C 1 ~ C 14 ... キャパシタ、Q 1 ~ Q 7 ... スイッチング素子、D R 1、D R 2 ... ドライバ、D 1 ~ D 5 ... ダイオード、C H 1、C H 2 ... チョークコイル、1 1 ... 電圧共振回路、1 2 ... 高周波トランス、1 3 ... 電流共振回路、1 4 ... 整流回路、1 5 ... スイッチング回路、1 6 ... 平滑回路、1 8 ~ 17 ... PWM 制御回路、1 7 ... スイッチング制御回路

10

20

30

40

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

【図10】

---

フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 堀内 彰二

静岡県沼津市米山町2番24号 株式会社ウインズ内

(72)発明者 中村 良道

静岡県沼津市米山町2番24号 株式会社ウインズ内

(72)発明者 丹 希

静岡県沼津市米山町2番24号 株式会社ウインズ内

F ターム(参考) 5H730 AA14 AS01 BB26 BB27 BB57 BB77 DD04 DD32 EE06 EE30

FD01 FG05