### (19) **日本国特許庁(JP)**

# (12)公表特許公報(A)

(11)特許出願公表番号

特表2012-523618 (P2012-523618A)

最終頁に続く

(43) 公表日 平成24年10月4日(2012.10.4)

(51) Int.Cl. F I テーマコード (参考)

**GO 6 F 12/16 (2006.01)** GO 6 F 12/16 3 2 O L 5 B O 1 8 **GO 6 F 3/08 (2006.01)** GO 6 F 3/08 H 5 B O 6 5

### 審査請求 有 予備審査請求 未請求 (全 27 頁)

(21) 出願番号 特願2012-504716 (P2012-504716) (71) 出願人 502208397 グーグル インコーポレイテッド (86) (22) 出願日 平成22年4月1日(2010.4.1) (85) 翻訳文提出日 平成23年12月5日 (2011.12.5) アメリカ合衆国 カリフォルニア州 94 PCT/US2010/029677 (86) 国際出願番号 043 マウンテン ビュー アンフィシ (87) 国際公開番号 W02010/117877 アター パークウェイ 1600 (87) 国際公開日 平成22年10月14日 (2010.10.14) (74)代理人 100097456 (31) 優先権主張番号 61/167,709 弁理士 石川 徹 (32) 優先日 平成21年4月8日(2009.4.8) (72) 発明者 アルベルト ティー ボルクヘルス (33) 優先権主張国 米国(US) アメリカ合衆国 カリフォルニア州 95 060 サンタ クルズ ニクホルズ ド (31) 優先権主張番号 61/187,835 ライブ 60 (32) 優先日 平成21年6月17日 (2009.6.17) ロベルト エス. スプリンクレ (33) 優先権主張国 米国(US) (72) 発明者 アメリカ合衆国 カリフォルニア州 94 (31) 優先権主張番号 12/537,719 O41 モウンタイン ブイエウ オアク (32) 優先日 平成21年8月7日(2009.8.7) (33) 優先権主張国 米国(US) ストリート 549

(54) 【発明の名称】データストレージデバイス

## (57)【要約】

データストレージデバイスは、第1のメモリボード及び第2のメモリボードを含むことができ、第1のメモリボード及び第2のメモリボードは各々、複数のメモリチップを備える。データストレージデバイスは、第1のメモリボード及び第2のメモリボードに機能的に接続するように配置され構成されるコントローラボードを含むことができ、コントローラボードは、高速インターフェイスと、高速インターフェイスを使用してホストからコマンドを受信し、コマンドを実行するように配置され構成されるコントローラとを含み、第1のメモリボード及び第2のメモリボードは各々、コントローラボードから別個に取り外し可能である。

【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

第1(104a)のメモリボードと、

第2(104b)のメモリボードであって、

該第1(104a)のメモリボード及び該第2(104b)のメモリボードが各々、複数のメモリチップを備える、前記メモリボードと、

該第1(104a)のメモリボード及び該第2(104b)のメモリボードに機能的に接続するように配置され構成されるコントローラボード(102)とを備え、該コントローラボード(102)が、 高速インターフェイス(108)と、

該高速インターフェイス(108)を使用してホスト(106)からコマンドを受信し、該コマンドを実行するように配置され構成されるコントローラ(110)とを備え、

該第1(104a)のメモリボード及び該第2(104b)のメモリボードが各々、該コントローラボード(102)から別個に取り外し可能である、データストレージデバイス(100)。

## 【請求項2】

前記コントローラ(110)が、フィールドプログラマブルゲートアレイ(FPGA)コントローラ(610)である、請求項1記載のデータストレージデバイス(100)。

### 【請求項3】

前記メモリチップがフラッシュメモリチップ(118a、118b)を備える、請求項1又は2記載のデータストレージデバイス(100)。

### 【請求項4】

前記フラッシュメモリチップ(118a、118b)がシングルレベルセル(SLC) NANDフラッシュメモリチップである、請求項3記載のデータストレージデバイス(100)。

### 【請求項5】

前記フラッシュメモリチップ(118a、118b)がマルチレベルセル(MLC) NANDフラッシュメモリチップである、請求項3記載のデータストレージデバイス(100)。

### 【請求項6】

前記高速インターフェイス (108) がPCI-eインターフェイス (408) である、請求項1から5のいずれか1項記載のデータストレージデバイス (100)。

### 【請求項7】

前記第1(104a)のメモリボード、前記第2(104b)のメモリボード、及び前記コントローラボード(102)が、サーバ(330)のドライブベイ(335)に適合するように配置され構成される、請求項1から6のいずれか1項記載のデータストレージデバイス(100)。

### 【請求項8】

前記第1(104a)のメモリボードは前記コントローラボード(102)の上側に機能的に接続され、前記第2(104b)のメモリボードは該コントローラボード(102)の下側に機能的に接続される、請求項1から7のいずれか1項記載のデータストレージデバイス(100)。

### 【請求項9】

前記メモリチップがダイナミックランダムアクセスメモリ(DRAM)チップを備える、請求 項1から8のいずれか1項記載のデータストレージデバイス(100)。

### 【請求項10】

前記メモリチップが相変化メモリ(PCM)チップを備える、請求項1から9のいずれか1項記載のデータストレージデバイス(100)。

### 【請求項11】

前記フラッシュメモリチップ(118a、118b)がNANDフラッシュメモリチップであり、

前 記 高 速 イ ン タ ー フ ェ イ ス (108) がPCI - e イ ン タ ー フ ェ イ ス (408) で あ り 、

前記コントローラ(110)がフィールドプログラマブルゲートアレイ(FPGA)コントローラ(610)である、請求項3から5のいずれか1項記載のストレージデバイス(100)。

### 【請求項12】

前記第1(104a)のメモリボード及び前記第2(104b)のメモリボードが、取り外され複数のメモリチップを備える別のメモリボードに置き換えられるように配置され構成されるモジ

10

20

30

40

ュール式ボードである、請求項1から11のいずれか1項記載のデータストレージデバイス(1 00)。

## 【請求項13】

前記コントローラ(110)が電源モジュールを備え、

異なる電圧を有する複数のメモリチップのコマンド処理を制御し、

前記第1(104a)のメモリボード及び前記第2(104b)のメモリボード上の該メモリチップの 電圧を自動的に認識し、

該メモリチップの該認識された電圧で動作するよう該電源モジュールを構成し、

前記インターフェイス(108)を使用して前記ホスト(106)からコマンドを受信し、

該メモリチップを使用して該コマンドを実行するように配置され構成される、請求項1から12のいずれか1項記載のデータストレージデバイス(100)。

#### 【請求項14】

前記コントローラ(110)が、

複数の異なるタイプのメモリチップのコマンド処理を制御し、

前記第1(104a)のメモリボード及び前記第2(104b)のメモリボード上の該メモリチップのタイプを自動的に認識し、

前記インターフェイス(108)を使用して前記ホスト(106)からコマンドを受信し、

該メモリチップを使用して該コマンドを実行するように配置され構成される、請求項1から13のいずれか1項記載のデータストレージデバイス(100)。

## 【請求項15】

前記コントローラ(110)が複数のチャネルを含み、各々の該チャネルが1つ以上の前記メモリチップに関連付けられ、各々の該メモリチップが該チャネルの1つに関連付けられる、請求項1から14のいずれか1項記載のデータストレージデバイス(100)。

#### 【請求項16】

前記コントローラ(110)が、各々の前記チャネルのチャネルコントローラ(450)をさらに備える、請求項15記載のデータストレージデバイス(100)。

### 【請求項17】

ホスト(106)と、

データストレージデバイス(100)と

を備え、該データストレージデバイス(100)が、

第1(104a)のメモリボードと、

第2(104b)のメモリボードであって、

該第1(104a)のメモリボード及び該第2(104b)のメモリボードが各々、 複数のメモリチップを備える、前記メモリボードと、

該第1(104a)のメモリボード及び該第2(104b)のメモリボードに機能的に接続するように配置され構成されるコントローラボード(102)とを備え、該コントローラボード(102)が

高速インターフェイス(108)と、

該高速インターフェイス(108)を使用して該ホスト(106)からコマンドを受信し、該コマンドを実行するように配置され構成されるコントローラ(110)とを備え、

該第1(104a)のメモリボード及び該第2(104b)のメモリボードが各々、該コントローラボード(102)から別個に取り外し可能である、コンピューティングデバイス。

### 【請求項18】

前記コントローラ(110)がフィールドプログラマブルゲートアレイ(FPGA)コントローラ(610)である、請求項17記載のコンピューティングデバイス。

## 【請求項19】

前記メモリチップがフラッシュメモリチップ(118a、118b)を備える、請求項17又は18記載のコンピューティングデバイス。

### 【請求項20】

前記フラッシュメモリチップ(118a、118b)がシングルレベルセル(SLC) NANDフラッシュ

20

10

30

- -

40

メモリチップである、請求項19記載のコンピューティングデバイス。

### 【請求項21】

前記フラッシュメモリチップ(118a、118b)がマルチレベルセル(MLC) NANDフラッシュメモリチップである、請求項19記載のコンピューティングデバイス。

### 【請求項22】

前記高速インターフェイス(108)がPCI-eインターフェイス(408)である、請求項1から21のいずれか1項記載のコンピューティングデバイス。

### 【請求項23】

前記第1(104a)のメモリボード、前記第2(104b)のメモリボード、及び前記コントローラボード(102)が、サーバ(330)のドライブベイ(335)に適合するように配置され構成される、請求項1から22のいずれか1項記載のコンピューティングデバイス。

### 【請求項24】

前記フラッシュメモリチップ (118a、118b) がNANDフラッシュメモリチップであり、

前記高速インターフェイス(108)がPCI-eインターフェイス(408)であり、

前記コントローラ(110)がフィールドプログラマブルゲートアレイ(FPGA)コントローラ(610)である、請求項19から21のいずれか1項記載のコンピューティングデバイス。

### 【請求項25】

前記第1(104a)のメモリボード及び前記第2(104b)のメモリボードが、取り外され複数のメモリチップを備える別のメモリボードに置き換えられるように配置され構成されるモジュール式ボードである、請求項1から24のいずれか1項記載のコンピューティングデバイス

## 【請求項26】

前記メモリチップがダイナミックランダムアクセスメモリ(DRAM)チップを備える、請求 項1から25のいずれか1項記載のコンピューティングデバイス。

#### 【請求項27】

前記メモリチップが相変化メモリ(PCM)チップを備える、請求項1から26のいずれか1項記載のコンピューティングデバイス。

#### 【請求項28】

データストレージデバイス(100)をアセンブルするための方法であって、

複数のメモリチップを第1(104a)のメモリボードに固定すること(510)と、

複数のメモリチップを第2(104b)のメモリボードに固定すること(520)と、

高速インターフェイス (108) 及びコントローラ (110) をコントローラボード (102) に取り付けること (530) と、

該 第1(104a) の メ モ リ ボ ー ド を 該 コ ン ト ロ ー ラ ボ ー ド (102) に 機 能 的 に (540) 接 続 す る こ と と 、

該第2のメモリボード(104b)を該コントローラボード(102)に機能的に(550)接続することとを備え、該第1(104a)のメモリボード及び該第2(104b)のメモリボードが各々、該コントローラボード(102)から別個に取り外し可能である、前記方法。

## 【請求項29】

複数のメモリチップを第3のメモリボードに固定することと、

前記第1(104a)のメモリボード又は前記第2(104b)のメモリボードのうちの1つを前記コントローラボード(102)から切断することと、

該第3のメモリボードを該コントローラボード(102)に機能的に接続することとをさらに備える、請求項28記載の方法。

#### 【請求項30】

前記第1(104a)のメモリボードを前記コントローラボード(102)に機能的に接続すること、及び前記第2(104b)のメモリボードを該コントローラボード(102)に機能的に接続することが、ドライブベイフォームファクタがサーバ(330)のドライブベイ(335)に適合するよう構成されるように、該第1(104a)のメモリボード、該第2(104b)のメモリボード、及び該コントローラボード(102)の該ドライブベイフォームファクタを形成することを含む、請求

10

20

30

40

20

30

40

50

項28又は29記載の方法。

### 【請求項31】

前記第1(104a)のメモリボードを前記コントローラボード(102)に機能的に接続することが、該第1(104a)のメモリボードを該コントローラボード(102)の上側に機能的に接続することを含み、

前記第2(104b)のメモリボードを該コントローラボード(102)に機能的に接続することが、該第2(104b)のメモリボードを該コントローラボード(102)の下側に機能的に接続することを含む、請求項28又は29記載の方法。

### 【請求項32】

前記メモリチップがダイナミックランダムアクセスメモリ(DRAM)チップを備える、請求項28から31のいずれか1項記載の方法。

#### 【請求項33】

前記メモリチップが相変化メモリ(PCM)チップを備える、請求項28から32のいずれか1項記載の方法。

### 【請求項34】

前記メモリチップがフラッシュメモリチップ(118a、118b)を備える、請求項28から33の いずれか1項記載の方法。

#### 【請求項35】

前記第1(104a)のメモリボード及び前記第2(104b)のメモリボード上の前記フラッシュメモリチップ(118a、118b)がNANDフラッシュメモリチップであり、

前記高速インターフェイス(108)がPCI-eインターフェイス(408)であり、

前記コントローラ(110)がフィールドプログラマブルゲートアレイ(FPGA)コントローラ(610)である、請求項34記載の方法。

【発明の詳細な説明】

### 【技術分野】

[0001]

### (関連出願の相互参照)

本出願は、引用により全体として本明細書中に組み込まれている、2009年4月8日に出願された「データストレージデバイス(DATA STORAGE DEVICE)」と題する米国仮出願第61/167,709号、及び2009年6月17日に出願された「フラッシュメモリデータストレージデバイスにおけるパーティショニング及びストライピング(PARTITIONING AND STRIPING IN A FLASH MEMORY DATA STORAGE DEVICE)」と題する米国仮出願第61/187,835号の利益を主張するものである。

### [0002]

# (技術分野)

この説明は、データストレージデバイスに関する。

## 【背景技術】

### [0003]

## (背景)

データストレージデバイスは、データを格納するために使用することができる。データストレージデバイスは、コンピューティングデバイスのデータストレージの必要性に備えるためにコンピューティングデバイスと共に使用することができる。場合によっては、膨大量のデータをデータストレージデバイスに格納することが望ましいこともある。また、データストレージデバイスとの間でデータの迅速な読み取り及び書き込みを行うためのコマンドを実行することが望ましい場合もある。

### 【発明の概要】

【課題を解決するための手段】

### [0004]

### (要旨)

本文書は、1つ以上のメモリボードを含むデータストレージデバイスであって、各メモ

20

30

40

50

リボードが複数のフラッシュメモリチップを含むデータストレージデバイスを説明する。 データストレージデバイスは、メモリボードが機能的に接続するコントローラボードを含む。データストレージデバイスは、インターフェイスを使用してホストと通信し、ホストからコマンドを受信して、それらのコマンドをフラッシュメモリチップを使用して処理するように構成されてもよい。たとえば、フラッシュメモリチップを使用してデータのブロックの読み取り、書き込み、コピー、及び削除を行うコマンドを、ホストは送信することができ、コントローラボードは受信することができる。

### [00005]

1つの例示的な実施態様において、コントローラは、フィールドプログラマブルゲートアレイ(FPGA)(field-programmable gate array)コントローラを含み、ホストとコントローラボードとの間のインターフェイスは、たとえば(PCIe)(Peripheral Component Interconnect Express)インターフェイスのような高速インターフェイスであってもよい。このように、データストレージデバイスは、高ストレージボリュームを含むことができ、ホストとフラッシュメモリチップ間の高パフォーマンス及び高速のデータ転送を達成するように構成されてもよい。

### [0006]

1つの例示的な実施態様において、データストレージデバイスは、メモリボードが各々複数のフラッシュメモリチップを含む2つのメモリボードで構成されてもよい。コントローラボード及び2つのメモリボードを含むデータストレージデバイスは、データストレージデバイスがコンピューティングデバイスの内蔵ドライブスロットに適合するように、ディスクドライブの形態で構成されてもよい。たとえば、データストレージデバイスは、サーバのデータストレージ容量をもたらすためにサーバの内蔵ドライブスロットに適合するように構成されてもよい。データストレージデバイスは、コンピューティングデバイスから容易に取り外すことができ、別のコンピューティングデバイスの内蔵ドライブスロットに挿入できるように、取り外し可能に構成されてもよい。

### [0007]

また、データストレージデバイスは、メモリボードがコントローラボードから切断されて、他のメモリボードに置き換えられてもよく、他のメモリボードも複数のフラッシュメモリチップを含むことができるような、モジュール方式であってもよい。コントローラボード上のコントローラは、1つ以上のメモリボードが切断されて、他のメモリボードで置き換えられたことを認識するように構成可能であってもよい。コントローラは、メモリボードのこのタイプのスワップアウトを認識するように構成されてもよく、ホストと他のメモリボードとの間のコマンドを処理することができる。このように、コントローラボードは、1つ以上のメモリボードがもはや使用可能ではなくなった場合であっても、引き続き使用することができる。同じコントローラボード及びコントローラボード上の同じコンポーネントを引き続き使用しながら、使用不可能なメモリボードはコントローラボードから切断されてもよく、別のメモリボードで置き換えられてもよい。

### [0008]

1つの例示的な実施態様において、データストレージデバイスは、さまざまなタイプのフラッシュメモリチップを扱うように構成可能であってもよい。たとえば、コントローラボード上のコントローラは、メモリボード上のさまざまなタイプのフラッシュメモリチップを認識して動作するように構成されてもよい。たとえば、コントローラは、たとえばシングルレベルセル(SLC)フラッシュメモリチップ、マルチレベルセル(MLC)フラッシュメモリチップ、VORフラッシュメモリチップ、及びその他のタイプのフラッシュメモリチップを含む、さまざまなタイプのフラッシュメモリチップを認はするように構成されるFPGAコントローラであってもよい。コントローラは、さまざまなタイプのフラッシュメモリチップを認識して、メモリボード上のフラッシュメモリチップのタイプに基づいてコマンドを変換することによってフラッシュメモリチップを使用してホストからのコマンドを実行するように構成され

20

30

40

50

てもよい。したがって、ホストは、コマンドを変換する必要がないか、又はフラッシュメモリチップのタイプにより異なるコマンドを送信する必要がない。コントローラは、ホストからのコマンドを、特定のタイプのフラッシュメモリチップのネイティブコマンドに変換するように構成されてもよい。

### [0009]

このように、同一のコントローラを有する同一のコントローラボードは、異なるタイプのフラッシュメモリチップを有するメモリボードと共に使用することができる。たとえば、第1のメモリボード及び第2のメモリボードは、コントローラボードに接続されてもよく、各々のボードは、1つのベンダーにより製造されたSLC NANDフラッシュメモリチップを含むことができる。第1のメモリボード及び第2のメモリボードは、切断されて、2つの別のメモリボードに置き換えられてもよく、別のメモリボードは異なるベンダーにより製造されたMLC NANDフラッシュメモリチップを含む。コントローラは、その他のメモリボード上のフラッシュメモリチップを自動的に認識して、その他のメモリボード上のフラッシュメモリチップを自動的に認識して、その他のメモリボード上のフラッシュメモリチップを使用してホストからのコマンドを実行するように構成されてもよい。このように、データストレージデバイスは、ホスト上の1つ以上のアプリケーションの特性に応じて、及びホスト上の1つ以上のアプリケーションにより所望されるデータストレージデバイスの特徴に応じて、メモリボード上のさまざまなフラッシュメモリチップで調整され構成されてもよい。

## [0010]

その他の例示的な実施態様において、各々のメモリボードは、フラッシュメモリチップ以外のメモリデバイスを含むことができる。たとえば、各々のメモリボードは、複数のダイナミックランダムアクセスメモリ(DRAM)チップを含むことができる。フラッシュメモリチップに関する上記の説明と同様に、データストレージデバイスは、さまざまなタイプのDRAMチップを扱うように構成可能であってもよい。たとえば、コントローラボード上のコントローラは、メモリボード上のさまざまなタイプのDRAMチップを認識して動作するように構成されてもよい。DRAMチップの1つのメモリボードは、データストレージデバイスから取り外して、異なるタイプのDRAMチップを有するメモリボードに置き換えることができる。コントローラは、メモリボード上のDRAMチップのタイプに基づいてコマンドを変することによって異なるタイプのDRAMチップを使用してホストからのコマンドを実行することができる。その他の例示的な実施態様において、メモリボードは、たとえば相変化メモリ(PCM)チップ及びその他のタイプのメモリデバイスを含む、その他のタイプのメモリデバイスを含むことができる。

### [0011]

もう1つの例示的な実施態様において、コントローラボード上のコントローラは、1つのメモリボード上の1つのタイプのメモリデバイスを認識して動作し、しかも同時に他のメモリボード上の異なるタイプのメモリデバイスで動作するように構成されてもよい。たとえば、メモリボードの1つはフラッシュメモリチップを含み、もう1つのメモリボードはDRAMチップを含むことができる。

### [0012]

1つの例示的な実施態様において、データストレージデバイスは、さまざまな電圧を有するフラッシュメモリチップを扱うように構成可能であってもよい。たとえば、コントローラボード上のコントローラは、メモリボード上のさまざまな電圧を有するフラッシュメモリチップを認識して動作するように構成されてもよい。たとえば、コントローラは、フラッシュメモリチップの電圧を感知して、必要な電圧を供給するように電力制御回路を構成することができる。たとえば、コントローラは、メモリボード上のフラッシュメモリチップに適切な電圧を供給するように構成され、感知した電圧に基づいてフラッシュメモリチップに適切な電圧を供給するようにコントローラボード上の電源モジュールを構成するように構成されるFPGAコントローラであってもよい。コントローラは、フラッシュメモリチップの電圧に基づいてコマンドを変換する必要なく、フラッシュメモリチップを使用してホストからのコマンドを実行す

るように構成されてもよい。

### [0013]

このように、同一のコントローラを有する同一のコントローラボードは、異なる電圧のフラッシュメモリチップを有するメモリボードと共に使用することができる。たとえば、第1のメモリボード及び第2のメモリボードは、コントローラボードに接続されてもよく、各々のボードは、第1の電圧で動作するフラッシュメモリチップを含むことができる。第1のメモリボード及び第2のメモリボードは、切断されて、2つの別のメモリボードに置き換えられてもよく、別のメモリボードは第2の電圧で動作するフラッシュメモリチップを含み、第2の電圧は第1の電圧とは異なる。コントローラは、その他のメモリボード上のフラッシュメモリチップの第2の電圧を自動的に感知して、第2の電圧で動作するよう電源モジュールを構成し、その他のメモリボード上のフラッシュメモリチップを使用してホストからのコマンドを実行するように構成されてもよい。このように、データストレージデバイスは、ホスト上の1つ以上のアプリケーションの特性に応じて、及びホスト上の1つ以上のアプリケーションの特性に応じて、及びホスト上の1つ以上のアプリケーションの特性に応じて、及びホスト上の1つ以上のアプリケーションの特性に応じて、及びホスト上の1つ以上のアプリケーションの特性に応じて、及びホスト上の1つ以上のアプリケーションの特性に応じて、及びホスト上の1つ以上のアプリケーションの特性に応じて、及びホスト上の1つ以上のアプリケーションの特徴に応じて、その他のメモリボード上のさまざまなフラッシュメモリチップで調整され構成されてもよい。

#### [0014]

メモリボード上にあるフラッシュメモリチップとは異なるボード上にある単一のコントローラボードを使用することで、データストレージデバイスを構成する際の柔軟性が実現する。たとえば、異なるタイプのフラッシュメモリチップを認識して動作するように、及び/又は異なる電圧を有するフラッシュメモリチップを認識して動作するように構成されるボード上の単一コントローラを有する単一のコントモリボードを使用することで、データストレージデバイスは、さまざまなフラッシュメモリチップ技術を使用して設計することが可能になる。また、特定のアプリケーショメ・ップ技術を使用して設計することが可能になる。またのアプリケーショメ・ップは、データストレージデバイスとインターフェイスをとるホスト上のアプリケーショナなイプに基づいて、メモリボード上で選択されてもよい。また、フラッシュメモリチップを受け入れるように構成可能なユニバーサルコントローラボード及びコントローラと見なすことができる。

## [0015]

1つの一般的な態様によれば、データストレージデバイスは、第1のメモリボード及び第2のメモリボードを含むことができ、第1のメモリボード及び第2のメモリボードは各々、複数のメモリチップを備える。データストレージデバイスは、第1のメモリボード及び第2のメモリボードに機能的に接続するように配置され構成されるコントローラボードを含むことができ、コントローラボードは、高速インターフェイスと、高速インターフェイスを使用してホストからコマンドを受信し、コマンドを実行するように配置され構成されるコントローラとを含み、第1のメモリボード及び第2のメモリボードは各々、コントローラボードから別個に取り外し可能である。データストレージデバイスは、コンピュータプログラム製品として実施されてもよい。

#### [0016]

実施態様は、1つ以上の以下の特徴を含むことができる。たとえば、コントローラは、フィールドプログラマブルゲートアレイ(FPGA)コントローラであってもよい。メモリチップは、フラッシュメモリチップを含むことができる。フラッシュメモリチップは、シングルレベルセル(SLC)NANDフラッシュメモリチップ及び/又はマルチレベルセル(MLC)NANDフラッシュメモリチップを含むことができる。高速インターフェイスは、PCI-eインターフェイスを含むことができる。1つの例示的な実施態様において、フラッシュメモリチップはNANDフラッシュメモリチップを含むことができ、高速インターフェイスはPCI-eインターフェイスであってもよく、コントローラはフィールドプログラマブルゲートアレイ(FPG

10

20

30

40

A)であってもよい。

### [0017]

第1のメモリボード、第2のメモリボード、及びコントローラボードは、サーバのドライブベイに適合するように配置され構成されてもよい。第1のメモリボードはコントローラボードの上側に機能的に接続されてもよく、第2のメモリボードはコントローラボードの下側に機能的に接続されてもよい。

#### [0018]

1つの例示的な実施態様において、メモリチップは、ダイナミックランダムアクセスメモリ(DRAM)チップを含むことができる。もう1つの例示的な実施態様において、メモリチップは、相変化メモリ(PCM)チップを備える。

#### [0019]

第1のメモリボード及び第2のメモリボードは、取り外されて、複数のメモリチップを含む別のメモリボードに置き換えられるように配置され構成されるモジュール式ボードであってもよい。コントローラは電源モジュールを含むことができ、異なる電圧を有する複数のメモリチップのコマンド処理を制御し、第1のメモリボード及び第2のメモリボード上のメモリチップの電圧を自動的に認識し、メモリチップの認識された電圧で動作するよう電源モジュールを構成し、インターフェイスを使用してホストからコマンドを受信し、メモリチップを使用してコマンドを実行するように配置され構成されてもよい。

### [0020]

コントローラは、複数の異なるタイプのメモリチップのコマンド処理を制御し、第1のメモリボード及び第2のメモリボード上のメモリチップのタイプを自動的に認識し、インターフェイスを使用してホストからコマンドを受信し、メモリチップを使用してコマンドを実行するように配置され構成されてもよい。

#### [0021]

コントローラは複数のチャネルを含むことができ、各々のチャネルは1つ以上のメモリチップに関連付けられ、各々のメモリチップはチャネルの1つに関連付けられる。コントローラは、チャネルごとにチャネルコントローラを含むことができる。

#### [0022]

もう1つの一般的な態様において、コンピューティングデバイスは、ホストと、データストレージデバイスとを含むことができる。データストレージデバイスは、第1のメモリボードと、第2のメモリボードであって、第1のメモリボード及び第2のメモリボードは各々、複数のメモリチップを備えるメモリボードと、第1のメモリボード及び第2のメモリボードとで含むことができる。コントローラボードは、高速インターフェイスと、高速インターフェイスを使用してホストからコマンドを受信し、コマンドを実行するように配置され構成されるコントローラ ボードは、コマンドを実行するように配置され構成されるコントローラとを含み、第1のメモリボード及び第2のメモリボードは各々、コントローラボードから別個に取り外し可能である。場合によっては、コンピューティングデバイスは、コンピュータシステムとして、又はコンピュータシステムの一部として実施されてもよい。実施態様は、上記及び以下で説明される1つ以上の特徴を含むことができる。

### [0023]

もう1つの一般的な態様において、データストレージデバイスをアセンブルするための方法は、複数のメモリチップを第1のメモリボードに固定することと、複数のメモリチップを第2のメモリボードに固定することと、高速インターフェイス及びコントローラをコントローラボードに取り付けることと、第1のメモリボードをコントローラボードに機能的に接続することと、第2のメモリボードをコントローラボードに機能的に接続することとを含むことができ、第1のメモリボード及び第2のメモリボードは各々、コントローラボードから別個に取り外し可能である。

### [0024]

実施態様は、1つ以上の以下の特徴を含むことができる。たとえば、方法は、複数のメモリチップを第3のメモリボードに固定することと、第1のメモリボード又は第2のメモリ

10

20

30

40

ボードのうちの1つをコントローラボードから切断することと、第3のメモリボードをコントローラボードに機能的に接続することとをさらに含むことができる。第1のメモリボードをコントローラボードに機能的に接続すること、及び第2のメモリボードをコントローラボードに機能的に接続することは、ドライブベイのフォームファクタがサーバのドライブベイに適合するよう構成されるように、第1のメモリボード、第2のメモリボード、及びコントローラボードのドライブベイのフォームファクタを形成することを含むことができる。第1のメモリボードをコントローラボードに機能的に接続することは、第1のメモリボードをコントローラボードに機能的に接続することを含むことができ、第2のメモリボードをコントローラボードに機能的に接続することを含むことができる。

[0025]

1つの実施態様において、メモリチップは、ダイナミックランダムアクセスメモリ(DRAM)チップを含むことができる。もう1つの実施態様において、メモリチップは、相変化メモリ(PCM)チップを含むことができる。もう1つの実施態様において、メモリチップは、フラッシュメモリチップを含むことができる。第1のメモリボード及び第2のメモリ上のフラッシュメモリチップは、NANDフラッシュメモリチップを含むことができ、高速インターフェイスは、PCI-eインターフェイスを含むことができ、コントローラは、フィールドプログラマブルゲートアレイ(FPGA)コントローラであってもよい。

[0026]

1つ以上の実施態様の詳細は、添付の図面及び以下の説明において示される。その他の特徴は、説明及び図面、並びに特許請求の範囲から明らかとなろう。

【図面の簡単な説明】

[0027]

【図1】データストレージデバイスを示す例示的なブロック図である。

[0028]

【図2】データストレージデバイスのプリント基板を示す例示的な透視ブロック図である

[0029]

【図3】図1のデータストレージデバイスと共に使用する例示的なコンピューティングデバイスを示す例示的なブロック図である。

[0030]

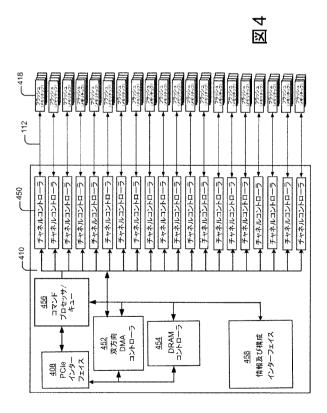

【図4】コントローラを示す例示的なブロック図である。

[ 0 0 3 1 ]

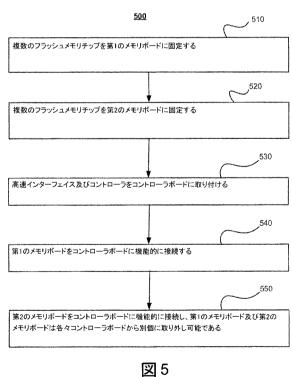

【図 5 】図1のデータストレージデバイスの例示のアセンブリを示す例示的な流れ図である。

[0032]

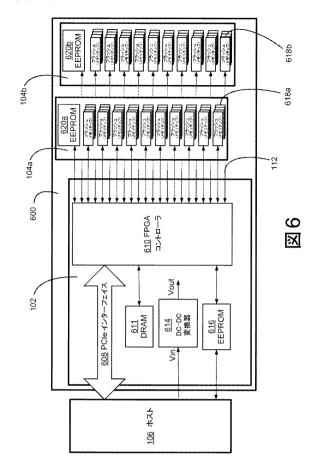

【 図 6 】 図1のデータストレージデバイスの例示の実施態様を示す例示的なブロック図である。

[0033]

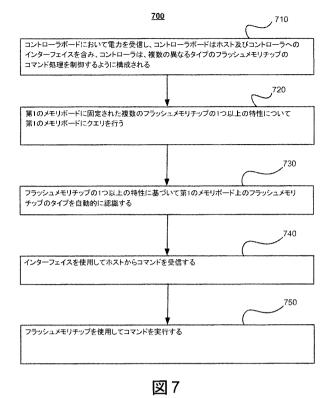

【図7】図1のデータストレージデバイスの例示の動作を示す例示的な流れ図である。

[ 0 0 3 4 ]

【図8】図1のデータストレージデバイスの例示の動作を示す例示的な流れ図である。

【発明を実施するための形態】

[0035]

(詳細な説明)

本文書は、データストレージのための装置、(1つ以上の)システム、及び技法を説明する。そのようなデータストレージ装置は、1つ以上の異なるメモリボードと共に使用されうるコントローラを有するコントローラボードを含むことができ、メモリボードは各々複数のフラッシュメモリチップを有する。データストレージ装置は、コントローラボード上のインターフェイスを使用してホストと通信することができる。このように、コントロー

10

20

30

40

20

30

40

50

ラボード上のコントローラは、インターフェイスを使用してホストからコマンドを受信し、メモリボード上のフラッシュメモリチップを使用してそれらのコマンドを実行するように構成されてもよい。

### [0036]

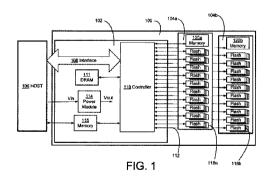

図1は、データストレージデバイス100を示すブロック図である。データストレージデバイス100は、コントローラボード102及び1つ以上のメモリボード104a及び104bを含むことができる。データストレージデバイス100は、インターフェイス108を介してホスト106と通信することができる。インターフェイス108は、ホスト106とコントローラボード102の間にあってもよい。コントローラボード102は、コントローラ110、DRAM 111、複数のチャネル112、電源モジュール114、及びメモリモジュール116を含むことができる。メモリボード104a及び104bは、各メモリボード上に複数のフラッシュメモリチップ118a及び118bを含むことができる。メモリボード104a及び104bはまた、メモリデバイス120a及び120bを含むことができる。

## [0037]

一般に、データストレージデバイス100は、フラッシュメモリチップ118a及び118b上にデータを格納するように構成されてもよい。ホスト106は、フラッシュメモリチップ118a及び118bとの間でデータの書き込み及び読み取りを行うことができ、さらにフラッシュメモリチップ118a及び118bに関してその他の操作を実行させるようにすることができる。ホスト106とフラッシュメモリチップ118a及び118bとの間のデータの読み取り及び書き込み、並びにその他の操作は、コントローラボード102上のコントローラ110を通じて処理され、制御されてもよい。コントローラ110は、ホスト106からコマンドを受信して、メモリボード104a及び104b上のフラッシュメモリチップ118a及び118bを使用してそれらのコマンドを実行させてもよい。ホスト106とコントローラ110との間の通信は、インターフェイス108を通じて行われてもよい。コントローラ110は、チャネル112を使用して、フラッシュメモリチップ118a及び118bと通信することができる。

### [0038]

コントローラボード102は、DRAM 111を含むことができる。DRAM 111は、コントローラ1 10に機能的に結合されてもよく、情報を格納するために使用されてもよい。たとえば、DR AM 111は、論理アドレスから物理アドレスへのマップ及び不良ブロックの情報を格納するために使用されてもよい。DRAM 111はまた、ホスト106とフラッシュメモリチップ118a及び118bとの間のバッファとして機能するように構成されてもよい。

## [0039]

1つの例示的な実施態様において、コントローラボード102及び各々のメモリボード104a及び104bは、物理的に別個のプリント基板 (PCB)である。メモリボード104aは、コントローラボード102のPCBに機能的に接続されている1つのPCB上にあってもよい。たとえば、メモリボード104aは、コントローラボード102に物理的及び/又は電気的に接続されてもよい。同様に、メモリボード104bは、メモリボード104aから分離されたPCBでもよく、コントローラボード102のPCBに機能的に接続されてもよい。たとえば、メモリボード104bは、コントローラボード102に物理的及び/又は電気的に接続されてもよい。メモリボード104a及び104bは各々、コントローラボード102から別個に切断されて取り外し可能であってもよい。たとえば、メモリボード104aは、コントローラボード102から切断されて、別のメモリボード(図示せず)に置き換えられてもよく、その別のメモリボードはコントローラボード102に機能的に接続される。この例において、メモリボード104a及び104bのいずれか又は両方は、他のメモリボードが同じコントローラボード102及びコントローラ110で動作できるように、他のメモリボードでスワップアウトされてもよい。

## [0040]

1つの例示的な実施態様において、コントローラボード102及び各々のメモリボード104a及び104bは、ディスクドライブフォームファクタで物理的に接続されてもよい。ディスクドライブフォームファクタは、たとえば3.5 "ディスクドライブフォームファクタ及び2.5 "ディスクドライブフォームファクタのような、さまざまなサイズを含むことができる。

20

30

40

50

### [0041]

1つの例示的な実施態様において、コントローラボード102及び各々のメモリボード104a及び104bは、高密度ボールグリッドアレイ(ball grid array)(BGA)コネクタを使用して電気的に接続されてもよい。たとえば、ファインボールグリッドアレイ(fine ball grid array)(FBGA)コネクタ、ウルトラファインボールグリッドアレイ(ultra fine ball grid array)(UBGA)コネクタ、及びマイクロボールグリッドアレイ(micro ball grid array)(MBGA)を含むその他のBGAコネクタの変種が使用されてもよい。その他のタイプの電気接続手段が使用されてもよい。

## [0042]

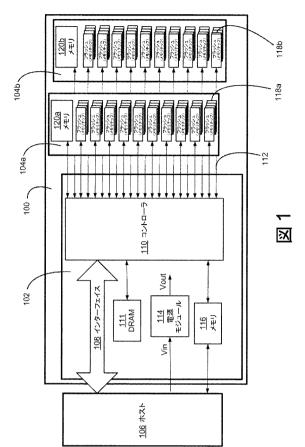

1つの例示的な実施態様において、自身のPCBであるコントローラボード102は、自身の別個のPCBである各々のメモリボード104a及び104bの間に物理的に配置されてもよい。また、図2をさらに参照すると、データストレージデバイス100は、1つのPCB上にメモリボード104a、第2のPCB上にコントローラボード102、及び第3のPCB上にメモリボード104bを含むことができる。メモリボード104aは複数のフラッシュメモリチップ118aを含み、メモリボード104bは複数のフラッシュメモリチップ118bを含む。コントローラボード102は、コントローラ110、及びホスト(図示せず)へのインターフェイス108、並びにその他のコンポーネント(図示せず)を含む。

### [0043]

図2に示される例において、メモリボード104aは、コントローラボード102に機能的に接続され、コントローラボード102の片側220aに配置されてもよい。たとえば、メモリボード104aは、コントローラボード102の上側220aに接続されてもよい。メモリボード104bは、コントローラボード102に機能的に接続され、コントローラボード102の第2の側220bに配置されてもよい。たとえば、メモリボード104bは、コントローラボード102の下側220bに接続されてもよい。

### [0044]

メモリボード104a及び104bとコントローラボード102との間のその他の物理的及び/又は電気的な接続配列が可能である。図2は、単に1つの例示的な配列を示すにすぎない。たとえば、データストレージデバイス100は、3つのメモリボード、4つのメモリボード、又はそれ以上のメモリボードのような、3つ以上のメモリボードを含むことができ、すべてのメモリボードは単一のコントローラボードに接続される。このように、データストレージデバイスは、ディスクドライブフォームファクタでさらに構成されてもよい。また、メモリボードは、たとえばコントローラボードが上部でメモリカードが下部、又はコントローラボードが下部でメモリカードが上部のように、その他の配列でコントローラボードに接続されてもよい。

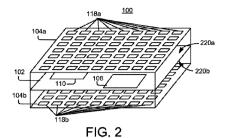

# [0045]

データストレージデバイス100は、コンピューティングデバイスと協働するように配置され構成されてもよい。1つの例示的な実施態様において、コントローラボード102及びメモリボード104a及び104bは、コンピューティングデバイスのドライブベイ内に適合するように配置され構成されてもよい。図3を参照すると、2つの例示的なコンピューティングデバイス、すなわちサーバ330及びサーバ340が示される。サーバ330及び340は、さまざまな異なるタイプのコンピューティングデバイスを提供するように配置され構成されてもよい。サーバ330及び340は、サーバ330及び340の1つ以上のプロセッサにコンピューティングサービスを提供させる命令を有するコンピュータプログラム製品を含むホスト(たとえば、図1のホスト106)を含むことができる。サーバのタイプは、サーバ上で動作している1つ以上のアプリケーションプログラムによって異なる。たとえば、サーバ330及び340は、アプリケーションサーバ、Webサーバ、Eメールサーバ、検索サーバ、ストリーミングメディアサーバ、Eコマースサーバ、ファイル転送プロトコル(FTP)サーバ、その他のタイプのサーバ、又はそれらのサーバの組み合わせであってもよい。サーバ330は、サーバラック内で動作するラックマウント型サーバとなるように構成されてもよい。

20

30

40

50

サーバ340がサーバラック内にはない場合であっても、他のサーバと共に動作するように構成されてもよく、他のサーバに機能的に接続されてもよい。サーバ330及び340は、例示のコンピューティングデバイスを説明するために示され、その他のタイプのサーバを含む他のコンピューティングデバイスを使用してもよい。

### [0046]

1つの例示的な実施態様において、図1及び図2のデータストレージデバイス100は、サーバ330及び340のデータストレージ機能をもたらすために、サーバ330のドライブベイ335及びサーバ340のドライブベイ345内に適合するようにサイズ調整されてもよい。たとえば、データストレージデバイス100は、ドライブベイ335及び345に適合するように、3.5"ディスクドライブフォームファクタにサイズ調整されてもよい。データストレージデバイス100は、インターフェイス108を使用してサーバ330及び340に機能的に接続されて通信することができる。このように、ホストは、インターフェイス108を使用してコントローラボード102にコマンドを伝達することができ、コントローラ110は、メモリボード104a及び104b上のフラッシュメモリチップ118a及び118bを使用してコマンドを実行することができる。

#### [0047]

図1に戻って参照すると、インターフェイス108は、コントローラ110とホスト106との間の高速インターフェイスを含むことができる。高速インターフェイスは、ホスト106とフラッシュメモリチップ118a及び118bとの間のデータの高速転送を可能にすることができる。1つの例示的な実施態様において、高速インターフェイスは、PCIeインターフェイスを含むことができる。たとえば、PCIeインターフェイスは、PCIe x4インターフェイス又はPCIe x8インターフェイスであってもよい。PCIeインターフェイス108は、ホスト106へPCIeコネクタケーブルアセンブリを含むことができる。その他の高速インターフェイス、コネクタ及びコネクタアセンブリが使用されてもよい。

#### [0048]

1つの例示的な実施態様において、コントローラボード102とメモリボード104a及び104b上のフラッシュメモリチップ118a及び118bとの間の通信は、複数のチャネル112に配置されて構成されてもよい。各々のチャネル112は、1つ以上のフラッシュメモリチップ118a及び118bと通信することができる。コントローラ110は、ホスト106から受信されたコマンドが、各々のチャネル112を使用して、同時に、又は少なくとも実質的に同時にコントローラ110によって実行されうるように構成されてもよい。このように、複数のコマンドは、異なるチャネル112で同時に実行することができ、データストレージデバイス100のスループットを向上させることができる。

### [0049]

図1の例において、20個のチャネル112が示される。完全な実線は、コントローラ110とメモリボード104a上のフラッシュメモリチップ118aとの間の10個のチャネルを示す。実線及び破線の混合線は、コントローラ110とメモリボード104b上のフラッシュメモリチップ118bとの間の10個のチャネルを示す。図1に示すように、各々のチャネル112は、複数のフラッシュメモリチップをサポートすることができる。たとえば、各々のチャネル112は、最大32個のフラッシュメモリチップをサポートすることができる。1つの例示的な実施態様において、20個のチャネルは各々、6個のフラッシュメモリチップをサポートして通信するように構成されてもよい。この例において、各々のメモリボード104a及び104bは、それぞれ60個のフラッシュメモリチップを含むことができる。フラッシュメモリチップ118a及び118bのタイプ及び数に応じて、データストレージ100デバイスは、最大多数テラバイトのデータまで格納するように構成されてもよい。

## [0050]

コントローラ110は、マイクロコントローラ、FPGAコントローラ、その他のタイプのコントローラ、又はそれらのコントローラの組み合わせを含むことができる。1つの例示的な実施態様において、コントローラ110はマイクロコントローラである。マイクロコントローラは、ハードウェア、ソフトウェア、又はハードウェア及びソフトウェアの組み合わ

20

30

40

50

せで実施されてもよい。たとえば、マイクロコントローラは、実行されると、特定の方法でマイクロコントローラに実行させることができる命令を含むコンピュータプログラム製品がメモリ(たとえば、メモリモジュール116)からロードされてもよい。マイクロコントローラは、インターフェイス108を使用してホスト106からコマンドを受信し、コマンドを実行するように構成されてもよい。たとえば、コマンドは、フラッシュメモリチップ118a及び118bを使用してデータのブロックの読み取り、書き込み、コピー、及び削除を行うコマンド、並びにその他のコマンドを含むことができる。

### [0051]

もう1つの例示的な実施態様において、コントローラ110はFPGAコントローラである。FPGAコントローラは、ハードウェア、ソフトウェア、又はハードウェア及びソフトウェアの組み合わせで実施されてもよい。たとえば、FPGAコントローラは、実行されると、特定の方法でFPGAコントローラに実行させることができる命令を含むファームウェアがメモリ(たとえば、メモリモジュール116)からロードされてもよい。FPGAコントローラは、インターフェイス108を使用してホスト106からコマンドを受信し、コマンドを実行するように構成されてもよい。たとえば、コマンドは、フラッシュメモリチップ118a及び118bを使用してデータのブロックの読み取り、書き込み、コピー、及び削除を行うコマンド、並びにその他のコマンドを含むことができる。

### [0052]

1つの例示の実施態様において、FPGAコントローラは、ホスト106との複数のインターフェイス108をサポートすることができる。たとえば、FPGAコントローラは、ホスト106との複数のPCIe x4又はPCIe x8インターフェイスをサポートするように構成されてもよい。

#### [0053]

メモリモジュール116は、コントローラ110にロードされうるデータを格納するように構成されてもよい。たとえば、メモリモジュール116は、FPGAコントローラの1つ以上のイメージを格納するように構成されてもよく、イメージはFPGAコントローラによって使用されるファームウェアを含む。メモリモジュール116は、ホスト106と通信するために、ホスト106とのインターフェイスをとることができる。メモリモジュール116は、ホスト106と直接インターフェイスをとることができる、及び/又はコントローラ110を通じてホスト106と間接的にインターフェイスをとることができる。たとえば、ホスト106は、ファームウェアの1つ以上のイメージを、格納のためにメモリモジュール116に伝達することができる。1つの例示的な実施態様において、メモリモジュール116は、電気的消去可能プログラマブルROM(electrically erasable programmable read-only memory)(EEPROM)を含む。メモリモジュール116はまた、その他のタイプのメモリモジュールを含むことができる。

### [0054]

電源モジュール114は、電力(Vin)を受信し、受信した電力の任意の変換を実行し、出力電力(Vout)を出力するように構成されてもよい。電源モジュール114は、ホスト106から、又は別の電源から、電力(Vin)を受信することができる。電源モジュール114は、コントローラボード102、及びコントローラ110を含むコントローラボード102上のコンポーネントに電力(Vout)を提供することができる。電源モジュール114はまた、メモリボード104a及び104b、並びにフラッシュメモリチップ118a及び118bを含むメモリボード104a及び104b上のコンポーネントに電力(Vout)を提供することができる。

#### [0055]

1つの例示的な実施態様において、電源モジュール114は、1つ以上のDC(直流)-DC変換器を含むことができる。DC-DC変換器は、入力電力(Vin)を受信して、電力を1つ以上の異なる電力レベル(Vout)に変換するように構成されてもよい。たとえば、電源モジュール114は、+12V(Vin)を受信し、電力を3.3V、1.2V、又は1.8Vに変換して、出力電力(Vout)をコントローラボード102並びにメモリボード104a及び104bに供給するように構成されてもよい。

### [0056]

メモリボード104a及び104bは、さまざまなタイプのフラッシュメモリチップ118a及び11

8bを扱うように構成されてもよい。1つの例示的な実施態様において、フラッシュメモリチップ118a及びフラッシュメモリチップ118bは、電源モジュール114から同じ電圧を必要とすること、及び同じフラッシュメモリチップベンダーのものであることを含む同じタイプのフラッシュメモリチップであってもよい。ベンダー及び製造元という用語は、本文書全体を通じて同義的に使用される。

## [0057]

1つの例示的な実施態様において、メモリボード104a上のフラッシュメモリチップ118a は、メモリボード104b上のフラッシュメモリチップ118bとは異なるタイプであってもよい。たとえば、メモリボード104aはSLC NANDフラッシュメモリチップを含むことができ、メモリボード104bはMLC NANDフラッシュメモリチップを含むことができる。もう1つの例において、メモリボード104aはあるフラッシュメモリチップ製造元によるラッシュメモリチップを含むこともあり、メモリボード104bは別のフラッシュメモリチップ製造元によるフラッシュメモリチップを含むこともある。すべて同じタイプのフラッシュメモリチップを備えるか、又は異なるタイプのフラッシュメモリチップを備えるという柔軟性があるため、データストレージデバイス100は、ホスト106に使用されているさまざまなアプリケーションに合わせて調整することができる。

### [0058]

もう1つの例示的な実施態様において、メモリボード104a及び104bは、同じメモリボード上に異なるタイプのフラッシュメモリチップを含むことができる。たとえば、メモリボード104aは、同じPCB上にSLC NANDチップとMLC NANDチップの両方を含むことができる。同様に、メモリボード104bは、SLC NANDチップとMLC NANDチップの両方を含むことができる。このように、データストレージデバイス100は、ホスト106の仕様に適合するように有利に調整されてもよい。

### [0059]

もう1つの例示的な実施態様において、メモリボード104a及び104bは、フラッシュメモリ以外のチップを含む、その他のタイプのメモリデバイスを含むことができる。たとえば、メモリボード104a及び104bは、たとえばダイナミックRAM(DRAM)及びスタティックRAM(SRAM)のようなランダムアクセスメモリ(RAM)、並びにその他のタイプのRAM及びその他のタイプのメモリデバイスを含むこともできる。1つの例示的な実施態様において、メモリボード104a及び104はいずれも、RAMを含むことができる。もう1つの例示的な実施態様において、メモリボードの一方はRAMを含み、もう一方のメモリボードはフラッシュメモリチップを含むことができる。また、メモリボードの一方は、RAM及びフラッシュメモリチップの両方を含むことができる。

### [0060]

メモリボード104a及び104b上のメモリモジュール120a及び120bは、それぞれフラッシュメモリチップ118a及び118bに関連する情報を格納するために使用されてもよい。1つの例示的な実施態様において、メモリモジュール120a及び120bは、フラッシュメモリチップのデバイス特性を格納することができる。デバイス特性は、チップがSLCチップ又はMLCのいずれであるか、チップがNAND又はNORチップのいずれであるか、チップセレクトの数、ブロックの数、ブロックあたりのページの数、ページあたりのバイトの数、及びチップの速度を含むことができる。

#### [0061]

1つの例示的な実施態様において、メモリモジュール120a及び120bは、シリアルEEPROMを含むことができる。EEPROMは、デバイス特性を格納することができる。デバイス特性は、任意の所定のタイプのフラッシュメモリチップに対して1回コンパイルされてもよく、適切なEEPROMイメージがデバイス特性と共に生成されてもよい。メモリボード104a及び104bがコントローラボード102に機能的に接続される場合、デバイス特性は、コントローラ10が制御しているフラッシュメモリチップ118a及び118bのタイプをコントローラ110が自動的に認識できるように、EEPROMから読み取られてもよい。加えて、デバイス特性は、特定の1つ以上のタイプのフラッシュメモリチップ118a及び118bの適切なパラメータにコン

10

20

30

トローラ110を構成するために使用されてもよい。

### [0062]

上記で説明されるように、コントローラ110は、FPGAコントローラを含むことができる。図4を参照すると、FPGAコントローラ410を示す例示的なブロック図が示される。FPGAコントローラは、図1のコントローラ110に関して上記で説明されたように動作するよう構成されてもよい。FPGAコントローラ410は、複数のチャネル112をフラッシュメモリチップ418に接続するために複数のチャネルコントローラ450を含むことができる。フラッシュメモリチップ418は、各々のチャネルコントローラ450に接続する複数のフラッシュメモリチップとして示される。フラッシュメモリチップ418は、図1の別個のメモリボード104a及び104b上にある、図1のフラッシュメモリチップ118a及び118bの代表である。別個のメモリボードは、図4の例には示されていない。FPGAコントローラ410は、PCIeインターフェイスモジュール408、双方向ダイレクトメモリアクセス(DMA)コントローラ452、ダイナミックランダムアクセスメモリ(DRAM)コントローラ454、コマンドプロセッサ/キュー456、及び情報及び構成インターフェイスモジュール458を含むことができる。

### [0063]

情報は、インターフェイスを使用してホスト(たとえば、図1のホスト106)との間で伝達されてもよい。図4のこの例において、FPGAコントローラ410は、ホスト及びPCIeインターフェイスモジュール408と通信するためにPCIeインターフェイスを含む。PCIeインターフェイスモジュール408は、ホストからコマンドを受信して、ホストにコマンドを送信するように、配置され構成されてもよい。PCIeインターフェイスモジュール408は、ホストとデータストレージデバイスとの間のデータフロー制御をもたらすことができる。PCIeインターフェイスモジュール408は、ホストとコントローラ410、及び最終的にはフラッシュメモリチップ418との間のデータの高速転送を可能にすることができる。1つの例示的な実施態様において、PCIeインターフェイス及びPCIeインターフェイスモジュール408は、64ビットバスを含むことができる。

### [0064]

双方向DMAコントローラ452は、PCIeインターフェイス408、コマンドプロセッサ/キュー456、及び各々のチャネルコントローラ450とのインターフェイスをとるように構成されてもよい。双方向DMAコントローラ452は、ホストとフラッシュメモリチップ418との間の双方向ダイレクトメモリアクセスを可能にする。

### [0065]

DRAMコントローラ454は、論理アドレスから物理アドレスへの変換を制御するように配置され構成されてもよい。たとえば、DRAMコントローラ454は、コマンドプロセッサ/キュー456が、ホストに使用されている論理アドレス及びフラッシュメモリチップ418との間で書き込み中又は読み取り中のデータに関連するフラッシュメモリチップ418内の実際の物理アドレスを変換する操作を補助することができる。ホストから受信された論理アドレスは、フラッシュメモリチップ418の1つの位置の物理アドレスに変換されてもよい。同様に、フラッシュメモリチップ418の1つの位置の物理アドレスは、論理アドレスに変換されて、ホストに伝達されてもよい。

### [0066]

コマンドプロセッサ/キュー456は、PCIeインターフェイスモジュール408を通じてホストからコマンドを受信し、チャネルコントローラ450を通じてコマンドの実行を制御するように、配置され構成されてもよい。コマンドプロセッサ/キュー456は、実行されるべき複数のコマンドのキューを保持することができる。このように、複数のコマンドは同時に実行されてもよく、各々のチャネル112は、同時に、又は少なくとも実質的に同時に使用されてもよい。

### [0067]

コマンドプロセッサ/キュー456は、異なるチャネル112のコマンドを順不同に処理して、チャネルごとのコマンド順序付けを保持するように構成されてもよい。たとえば、ホストから受信されて、異なるチャネルに指定されているコマンドは、コマンドプロセッサ/

10

20

30

40

20

30

40

50

キュー456によって順不同に処理されてもよい。このように、チャネルはビジー状態の場合もある。同じチャネルで処理されるようにホストから受信されるコマンドは、コマンドがホストからコマンドプロセッサ/キュー456によって受信された順序で処理されてもよい。1つの例示的な実施態様において、コマンドプロセッサ/キュー456は、コマンドが確実に適時に実行されるようにするため、古いもの順でホストから受信されたコマンドのリストを保持するように構成されてもよい。

#### [0068]

チャネルコントローラ450は、コマンドプロセッサ/キュー456からのコマンドを処理するように配置されて構成されてもよい。各々のチャネルコントローラ450は、複数のフラッシュメモリチップ418のコマンドを処理するように構成されてもよい。1つの例示的な実施態様において、各々のチャネルコントローラ450は、最大32個のフラッシュメモリチップ418のコマンドを処理するように構成されてもよい。

### [0069]

チャネルコントローラ450は、コマンドプロセッサ/キュー456によって指定された順序で、コマンドプロセッサ/キュー456からのコマンドを処理するように構成されてもよい。処理されうるコマンドの例は、フラッシュページの読み取り、フラッシュページのプログラミング、フラッシュページのコピー、フラッシュブロックの消去、フラッシュブロックのメタデータの読み取り、フラッシュメモリチップの不良ブロックのマッピング、フラッシュメモリチップのリセットを含むが、これらに限定されることはない。

## [0070]

情報及び構成インターフェイスモジュール458は、FPGAコントローラ410の構成情報を受信するために、メモリモジュール(たとえば、図1のメモリモジュール116)とのインターフェイスをとるように配置され構成されてもよい。たとえば、情報及び構成インターフェイスモジュール458は、ファームウェアをFPGAコントローラ410に提供するために、メモリモジュールから1つ以上のイメージを受信することができる。イメージ及びファームウェアへの変更は、ホストにより情報及び構成インターフェイスモジュール458を通じてコントローラ410に提供されてもよい。情報及び構成インターフェイスモジュール458を通じて受信された変更は、たとえば、PCIeインターフェイスモジュール408、双方向DMAコントローラ452、DRAMコントローラ454、コマンドプロセッサ/キュー456、及びチャネルコントローラ450を含むコントローラ410のコンポーネントのいずれかに適用されてもよい。情報及び構成インターフェイスモジュール458は、1つ以上のレジスタを含むことができ、レジスタはホストからの命令により必要に応じて変更されてもよい。

#### [0071]

FPGAコントローラ410は、ホストと共に協働してコマンドを処理するように配置されて構成されてもよい。FPGAコントローラ410は、エラー訂正、不良ブロック管理、論理から物理へのマッピング、ガーベッジコレクション、消耗平準化、パーティショニング、及びフラッシュメモリチップ418に関連する低レベルフォーマッティングを実行することができるか、又は少なくともその操作を補助することができる。

## [0072]

図5を参照すると、データストレージデバイスをアセンブルするためのプロセス500が示される。プロセス500は、複数のフラッシュメモリチップを第1のメモリボードに固定すること(510)と、複数のフラッシュメモリチップを第2のメモリボードに固定すること(520)とを含むことができる。たとえば、図1をさらに参照すると、複数のフラッシュメモリチップ118aはメモリボード104aに固定されてもよく、複数のフラッシュメモリチップ118bはメモリボード104bに固定されてもよい。メモリボード104a及び104bは、それぞれフラッシュメモリチップ118a及び118bが取り付けられるプリント基板(PCB)であってもよい。各メモリボード104a及び104bのストレージ容量は、個々に、及び集合的に、メモリボード104a及び104bに固定されたフラッシュメモリチップ118a及び118bのタイプ及び数によって異なっていてもよい。フラッシュメモリチップ118a及び118bは、上記で説明されるように単一のチャネルが複数のフラッシュメモリチップのコマンド処理を制御できるように、1つ以

上のチャネルに配列されてもよい。

### [0073]

フラッシュメモリチップ118a及び118bは、同じタイプのフラッシュメモリチップであってもよいか、又はメモリボード104a上のフラッシュメモリチップは、メモリボード104b上のフラッシュメモリチップと異なっていてもよい。また、メモリボード104a及び104bは、各々のメモリボード上に異なる数のフラッシュメモリチップを含むことができる。たとえば、メモリボード104aは60個のフラッシュメモリチップを含むことができ、メモリボード104bは80個のフラッシュメモリチップを含むことができるが、メモリボード104a上のフラッシュメモリチップは、メモリボード104b上のフラッシュメモリチップと同じタイプ又は異なるタイプのフラッシュメモリチップであってもよい。

### [0074]

プロセス500は、高速インターフェイス及びコントローラをコントローラボードに取り付けること(530)と、第1のメモリボードをコントローラに機能的に接続すること(540)と、第2のメモリボードをコントローラボードに機能的に接続することとを含むことができ、第1のメモリボード及び第2のメモリボードは各々、コントローラボードから別個に取り外し可能である(550)。たとえば、インターフェイス108は、高速インターフェイスであってもよく、コントローラボード102に取り付けられてもよい(530)。コントローラ110は、コントローラボード102に取り付けられてもよい。コントローラボード102は、高速インターフェイス及びコントローラが取り付けられるPCBであってもよい。

## [ 0 0 7 5 ]

メモリボード104aは、コントローラボード102に機能的に接続されてもよく(540)、メモリボード104bは、コントローラボードに機能的に接続されてもよい(550)。メモリボード104a及び104bは、メモリボード104bとは別個の異なるメモリボードであり、メモリボード104a及び104bは各々、コントローラボード102から別個に取り外し可能であってもよい。アセンブルされたコントローラボード102、並びに2つのメモリボード104a及び104bは、共にデータストレージデバイス100を形成することができる。

### [0076]

1つの例示的な実施態様において、メモリボード104a及び104bは、コントローラボード102から切断されてもよく、他のメモリボードに取り付けられたフラッシュメモリチップを有する2つの他のメモリボードに置き換えられてもよい。他のフラッシュメモリボードは、メモリボード104a及び104b上のフラッシュメモリチップ118a及び118bと同じタイプのフラッシュメモリチップ含むことができるか、又は他のフラッシュメモリボードは、異なるタイプのフラッシュメモリチップを含むことができる。他のフラッシュメモリボードはまた、メモリボード104a及び104bとは異なる数のフラッシュメモリチップを含むことができる。

## [0077]

1つの例示的な実施態様において、コントローラボード102に接続されたメモリボード104a及び104bを含むアセンブリされたデータストレージデバイス100は、コンピューティングデバイスのドライブベイ内に適合するように構成されるドライブベイフォームファクタを形成することができる。たとえば、図2及び図3を参照すると、図2のデータストレージデバイス100は、たとえばサーバ330のドライブベイスロット335又はサーバ340のドライブベイスロット345のような、コンピューティングデバイスのドライブベイスロット内に適合するように構成されてもよい。

## [ 0 0 7 8 ]

図6を参照すると、図1のデータストレージデバイス100の例示的な実施態様は、データストレージデバイス600として示される。データストレージデバイス600は、ホスト106とのPCIeインターフェイス608、FPGAコントローラ610、DRAM 611、DC-DC変換器614、及びEE PROM 616を含むコントローラボード102を含むことができる。データストレージデバイスはまた、それぞれフラッシュメモリチップ618a及び618bを有するメモリボード104a及び104bを含むことができる。1つの実施態様において、フラッシュメモリチップ618a及び618b

10

20

30

40

は、NANDフラッシュメモリチップである。図1におけるように、FPGAコントローラ610は、 複数のチャネル112を使用してフラッシュメモリチップ618a及び618bを制御することがで き、複数のチャネル112は各々1つ以上のフラッシュメモリチップ618a及び618bを制御する ことができる。

### [0079]

図1に戻って参照すると、コントローラ110(例として、図4のFPGAコントローラ410、及び図6のFPGAコントローラ610を含む)は、複数の異なるタイプのフラッシュメモリチップ118a及び118bのコマンド処理を制御し、フラッシュメモリボード104a及び104b上のフラッシュメモリチップ118a及び118bを使用して受信したコマンドを実行するように配置され構成されてもよい。コントローラ110は、コマンドを、ネイティブのフラッシュメモリチップのコマンドを処理するように構成されてもより、異なるタイプのフラッシュメモリチップのコマンドを処理するように構成されてもよい。コントローラがホストのコマンドを引き受け、必要に応じてホストのコマンドをネイティブのフラッシュメモリチップのコマンドに変換するので、ホストは、ネイティブのフラッシュメモリチップのコマンドに変換するので、ホストは、ネイティブのフラッシュメモリチップのコマンドを考慮に入れる必要はない。たとえば、ホストから受信された読み取りコマンドは、特定のベンダー製のフラッシュメモリチップで動作できるように、ホストが読み取りコマンドを別のコマンドに変換する必要なく、コントローラ110によって処理されることができる。

## [0800]

図7を参照すると、プロセス700は、コントローラ110が異なるタイプのフラッシュメモリチップを自動的に認識して動作するように構成されてもよいことを示す。プロセス700は、コントローラボードにおいて電力を受信することを含み、コントローラボードはホスト及びコントローラへのインターフェイスを含む(710)。コントローラは、複数の異なるタイプのフラッシュメモリチップのコマンド処理を制御するように構成されてもよい(710)。たとえば、コントローラボード102は、電源モジュール114において電力(Vin)を受信することができる。1つの例示的な実施態様において、電源モジュール114は、1つ以上のDC-DC変換器(たとえば、図6のDC-DC変換器614)を含むことができる。コントローラボード102は、インターフェイス108及びコントローラ110を含むことができる。コントローラ110は、複数の異なるタイプのフラッシュメモリチップ118a及び118bのコマンド処理を制御するように構成されてもよい。

### [0081]

プロセス700は、第1のメモリボードに固定された複数のフラッシュメモリチップの1つ以上の特性について第1のメモリボードにクエリを行うことを含むことができる(720)。1つの例示的な実施態様において、コントローラ110は、メモリボード104aに固定されたフラッシュメモリチップ118aのデバイス特性についてメモリモジュール120aにクエリを行うように構成されてもよい(720)。デバイス特性は、たとえば、チップがSLCチップ又はMLCチップのいずれであるか、チップがNAND又はNORチップのいずれであるか、チップセレクトの数、ブロックの数、ブロックあたりのページの数、ページあたりのバイトの数、及びチップの速度を含むことができる。メモリモジュール120aは、シリアルEEPROM(たとえば、図6のEEPROM 620a)を含むことができる。

## [0082]

もう1つの例示的な実施態様において、コントローラ110は、フラッシュメモリチップ118aに直接クエリを行うように構成されてもよい。たとえば、コントローラ110は、各フラッシュメモリチップ118aのデバイスIDページにクエリを行ってデバイス特性を決定するように構成されてもよい。

## [0083]

プロセス700は、フラッシュメモリチップの1つ以上の特性に基づいて第1のメモリボード上のフラッシュメモリチップのタイプを自動的に認識することを含むことができる(730)。たとえば、コントローラ110は、デバイス特性を使用して、メモリボード104a上のフラッシュメモリチップ118aのタイプを自動的に認識することができる。フラッシュメモリチ

10

20

30

40

20

30

40

50

ップ118aは、SLC又はMLCデバイスであってもよい。フラッシュメモリチップ118aは、NANDチップ、NORチップ、又はその他のタイプのチップであってもよい。フラッシュメモリチップ118aはまた、いくつかの異なるフラッシュメモリの製造元のうちの1つによるものであってもよい。

### [0084]

プロセス700は、インターフェイスを使用してホストからコマンドを受信すること(740)、及びフラッシュメモリチップを使用してコマンドを実行すること(750)を含むことができる。たとえば、コントローラ110は、インターフェイス108を使用してホスト106からコマンドを受信し、フラッシュメモリチップ118aを使用してコマンドを実行するように構成されてもよい。このように、コントローラ110は、任意のタイプのフラッシュメモリチップで自動的に動作するように構成されてもよい。データストレージデバイス100の電源投入時に、コントローラは、どのタイプのフラッシュメモリチップがメモリボード上にあるかを決定することができ、次いでホストから受信されたコマンドを実行するためにそれらのメモリボードで動作を開始することができる。

### [0085]

1つの例示的な実施態様において、コントローラ110は、メモリボード上に存在すると決定されるフラッシュメモリチップのタイプに基づいて1つ以上の構成アップデートを受信することができる。たとえば、コントローラ110は、メモリボードの1つで特定のタイプのフラッシュメモリチップが使用されていると決定することができ、この情報がホストに戻されてレポートされてもよい。ホスト106は、1つ以上の構成アップデートをコントローラ110に伝達することができ、コントローラ110は、図4の情報及び構成インターフェイスモジュール458においてそれらのアップデートを受信して処理することができる。

### [0086]

1つの例示的な実施態様において、コントローラ110は、同じメモリボード上の異なるタイプのフラッシュメモリチップを自動的に認識するように構成されてもよい。たとえば、メモリボード104a上のフラッシュメモリチップ118aの半数はSLC NANDフラッシュメモリチップであってもよく、メモリボード104a上のフラッシュメモリチップ118sのもう一方の半数はMLC NANDフラッシュメモリチップであってもよい。コントローラ110は、同じメモリボード上であっても両方のそれらのタイプのフラッシュメモリチップのコマンドを実行するように構成されてもよい。

### [0087]

もう1つの例示的な実施態様において、コントローラ110は、2つのメモリボードがコントローラボード102から取り外されて、異なるタイプのフラッシュメモリチップの有無にかかわらず新しいメモリボードに置き換えられる場合に認識するように構成されてもよい。このように、コントローラ110は、ホスト106の特定のアプリケーションの必要性に適合するようにデータストレージデバイス100を調整する際に高い柔軟性を実現することができる。同じメモリボード上に異なるタイプのチップ及び/又は各メモリボード上に異なるタイプのチップを含む、特定のタイプのフラッシュメモリチップは、ホスト106の特定のアプリケーションに必要とされる所望の特性に適合するために使用されてもよい。

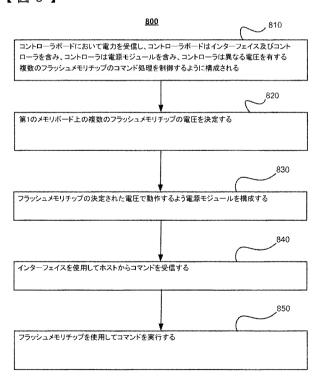

### [0088]

図8を参照すると、例示的なプロセス800は、コントローラが異なる電圧を有するフラッシュメモリチップで動作するように構成されることを示す。プロセス800は、コントローラボードにおいて電力を受信することを含むことができ、コントローラボードはインターフェイス及びコントローラを含み、コントローラは電源モジュールを含む。コントローラは、異なる電圧を有する複数のフラッシュメモリチップのコマンド処理を制御するように構成される(810)。たとえば、コントローラボード102は、ホスト106から電力(Vin)を受信するように構成されてもよく、コントローラボードは、コントローラが電源モジュール114を含むことができるかどうかにかかわらず、インターフェイス108及びコントローラ110を含むことができる。コントローラ110は、異なる電圧を有する複数のフラッシュメモリチップのコマンド処理を制御するように構成されてもよい(810)。たとえば、コントロー

20

30

40

50

ラ110は、1.2V、1.8V、3.3V、又はその他の電圧で動作するフラッシュメモリチップを制御するように構成されてもよい。

### [0089]

プロセス800は、第1のメモリボード上のフラッシュメモリチップの電圧を決定すること (810)を含む。たとえば、コントローラ110は、コントローラボード102とメモリボード104 aとの間のコネクタ上のピンの信号レベルに基づいて、フラッシュメモリチップの電圧を感知するように構成されてもよい。信号レベル(たとえば、論理ハイ及び/又は論理ローのグループ化)は、フラッシュメモリチップ118aに必要とされる電圧を指示することができる。プロセス800は、フラッシュメモリチップの決定された電圧で動作するよう電源モジュールを構成すること(830)を含む。たとえば、コントローラ110は、コントローラボード102とメモリボード104aとの間のコネクタ上のピンにおいて感知された電圧に基づいて電源モジュール114を構成するように構成されてもよい。1つの例示的な実施態様において、電源モジュール114は、1つ以上のDC-DC変換器(たとえば、図6のDC-DC変換器614)を含む。電源モジュール114は、感知された電圧で動作するように設定されてもよい。

## [0090]

プロセス800は、インターフェイスを使用してホストからコマンドを受信すること(840)、及びフラッシュメモリチップを使用してコマンドを実行すること(850)を含むことができる。たとえば、コントローラ110は、インターフェイス108を使用してホスト106からコマンドを受信し、フラッシュメモリチップ118aを使用してコマンドを実行するように構成されてもよい。このように、メモリボード104a及び104bは、同じ電圧を持つチップを含むことができ、メモリボード104a及び104bはコントローラボード102に接続される。メモリボード104a及び104bは、コントローラボード102から切断され、異なる電圧のフラッシュメモリチップを有する他のメモリボードに置き換えられてもよい。コントローラ110は、その他のメモリボード上のフラッシュメモリチップに必要とされる異なる電圧を自動的に認識して、異なる電圧レベルで動作するよう電源モジュール114を構成するように構成される。

### [0091]

本明細書において説明されるさまざまな技法の実施態様は、デジタル電子回路において、又はコンピュータハードウェア、ファームウェア、若しくはその組わち、わせで実施されてもよい。実施態様は、コンピュータプログラム製品として、すなのわちでを処理装置により実行するため、若しくはその動作を制御するための、たとえばプログラムであれて実体的に具現されるコンピュータプログラムな機が、ストレージデバイスなどの情報担体において実体的に具現されるコンピュータプログラムのよとして、実施されてもよい。上記で説明される(1つ以上の)コンピュータプログラムの形とのプログラミング言語で記述されてもよく、スタンドアロンの言語をとしてないのプログラミング環境にコンパイル済みのドアロング環境によい。日に適した他のユニットとしてなど、任意の形態で配置されてもよい。コンポーネント、サブルーチン、若しくはコンピューティング環境にコークにより相互接続された複数コンピュータ上で実行されるように配置されてもよい。

#### [0092]

方法ステップは、入力データを操作して出力を生成することにより機能を実行するようにコンピュータプログラムを実行している1つ以上のプログラム可能プロセッサによって実行されてもよい。方法ステップはまた、たとえばFPGA(フィールドプログラマブルゲートアレイ)又はASIC(特殊用途向け集積回路)などの特殊用途論理回路によって実行されてもよく、装置は特殊用途論理回路として実施されてもよい。

### [0093]

コンピュータプログラムの実行に適したプロセッサは、一例として、汎用及び特殊用途 マイクロプロセッサ、及び任意の種類のデジタルコンピュータの1つ以上のプロセッサを 含む。一般に、プロセッサは、読み取り専用メモリ又はランダムアクセスメモリ、若しくはその両方から命令及びデータを受信する。コンピュータの要素は、命令を実行するための少なくとも1つのプロセッサと、命令及びデータを格納するための1つ以上のメモリデバイスを含むことができる。一般に、コンピュータはまた、たとえば磁気、光磁気ディスク、又は光ディスクなど、データを格納するための1つ以上の大容量ストレージデバイスを含むことができるか、又は大容量ストレージデバイスとの間でデータを受信又は転送若しくはその両方を行うように機能的に結合されてもよい。コンピュータプログラム命令及びデータを具現するために適した情報担体は、一例として、たとえばEPROM、EEPROM、及びフラッシュメモリデバイスのような半導体メモリデバイス;たとえば内蔵ハードディスク又はリムーバブルディスクのような磁気ディスク;光磁気ディスク;並びにCD-ROM及びDVD-ROMディスクを含む、あらゆる形態の不揮発性メモリを含む。プロセッサ及びメモリは、特殊用途論理回路によって補完されてもよいか、又は特殊用途論理回路に組み込まれてもよい。

## [0094]

ユーザとの対話に備えるため、実施態様は、情報をユーザに表示するための、たとえばブラウン管(CRT)又は液晶ディスプレイ(LCD)モニタのような表示デバイス、並びにキーボード及び、たとえばマウス又はトラックボールのような、ユーザがコンピュータに入力を行うことができるポインティングデバイスを有するコンピュータで実施されてもよい。その他の種類のデバイスも、ユーザとの対話を行うために使用されてもよく;たとえば、ユーザに提供されるフィードバックは、たとえば視覚フィードバック、聴覚フィードバック、又は触覚フィードバックのような任意の形態の知覚的フィードバックであってもよく;ユーザからの入力は、音響、発語、又は触覚入力を含む任意の形態で受信されてもよい。【0095】

実施態様は、たとえばデータサーバのようなバックエンドコンポーネントを含むか、又はたとえばアプリケーションサーバのようなミドルウェアコンポーネントを含むか、又はたとえばユーザが実施態様と対話することができるグラフィカルユーザインターフェイス又はWebプラウザを有するクライアントコンピュータのようなフロントエンドコンポーネントを含むか、若しくはそのようなバックエンド、ミドルウェア、又はフロントエンドコンポーネントの任意の組み合わせを含むコンピューティングシステムにおいて実施されてもよい。コンポーネントは、たとえば通信ネットワークのようなデジタルデータ通信の任意の形態又は媒体によって相互接続されてもよい。通信ネットワークの例は、ローカルエリアネットワーク(LAN)、及びたとえばインターネットのようなワイドエリアネットワーク(WAN)を含む。

## [0096]

説明された実施態様の特定の特徴が本明細書において説明されるように示されたが、当業者には多数の修正、代替、変更、及び等価が考案されよう。したがって、添付の特許請求の範囲は、すべてのそのような修正及び変更を、実施態様の範囲内に含まれるものとして扱うことが意図されていることを理解されたい。

10

20

## 【図2】

【図3】

FIG. 3

# 【図4】

## 【図5】

## 【図6】

## 【図7】

## 【図8】

図8

# 【国際調査報告】

|                                                                                                                                                                                                                                                    | INTERNATIONAL SEARCH R                                                                                                                                            | EPORT                        | 1.4                                |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------|--|--|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   | International application No |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    | PCT/US2010/029677                                                                                                                                                 |                              |                                    |  |  |  |  |  |  |  |  |

| A. CLASSI                                                                                                                                                                                                                                          | FICATION OF SUBJECT MATTER<br>G06F13/40                                                                                                                           | _                            | · · · · · · · · ·                  |  |  |  |  |  |  |  |  |

| INV.                                                                                                                                                                                                                                               | GUDF 13/40                                                                                                                                                        |                              |                                    |  |  |  |  |  |  |  |  |

| ADD.                                                                                                                                                                                                                                               | G06F13/16                                                                                                                                                         |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    | hatamatianah Datasi Olassifasitas (IDD) sahah atkasilasi katendari                                                                                                |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    | o International Patent Classification (IPC) or to both national classification                                                                                    | on and IPC                   |                                    |  |  |  |  |  |  |  |  |

| B. FIELDS SEARCHED  Minimum documentation searched (classification system followed by classification symbols)                                                                                                                                      |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| G06F                                                                                                                                                                                                                                               | cumentation searched (classification system followed by classification                                                                                            | n symbooks)                  |                                    |  |  |  |  |  |  |  |  |

| """                                                                                                                                                                                                                                                |                                                                                                                                                                   | •                            |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| Documental                                                                                                                                                                                                                                         | ion searched other than minimum documentation to the extent that su                                                                                               | ch documents are in          | cluded in the fields searched      |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)                                                                                                                         |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| i variante de la companya de la comp                                                                                                                                    |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| Eru-In                                                                                                                                                                                                                                             | ternal, WPI Data                                                                                                                                                  |                              |                                    |  |  |  |  |  |  |  |  |

| ł                                                                                                                                                                                                                                                  |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| C DOCUMENT                                                                                                                                                                                                                                         | ENTS CONSIDERED TO BE RELEVANT                                                                                                                                    |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   | vani nacacasa                | Pologoni to delle Ma               |  |  |  |  |  |  |  |  |

| Category*                                                                                                                                                                                                                                          | Citation of document, with indication, where appropriate, of the rete                                                                                             | vanı passages                | Relevant to claim No.              |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| Х                                                                                                                                                                                                                                                  | US 5 844 776 A (YAMAGUCHI SYUJI [                                                                                                                                 | 1-12,                        |                                    |  |  |  |  |  |  |  |  |

| .,                                                                                                                                                                                                                                                 | AL) 1 December 1998 (1998-12-01)                                                                                                                                  | 15-35                        |                                    |  |  |  |  |  |  |  |  |

| Y                                                                                                                                                                                                                                                  | column 1, line 6 - column 4, line                                                                                                                                 | 7;                           | 13,14                              |  |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                  | figures 2A-9,12-14                                                                                                                                                | - 46                         |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    | column 5, line 45 - column 6, lin<br>column 7, line 50 - column 8, lin                                                                                            | e 40                         |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    | column 9, lines 54-64                                                                                                                                             | e 29                         |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| Υ                                                                                                                                                                                                                                                  | WO 2008/040028 A2 (VIRIDENT SYSTE                                                                                                                                 | MS INC                       | 13,14                              |  |  |  |  |  |  |  |  |

| -                                                                                                                                                                                                                                                  | [US]; OKIN KENNETH [US]; MOUSSA G                                                                                                                                 |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    | [US]; GANA) 3 April 2008 (2008-04                                                                                                                                 |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    | paragraphs [0038] - [0050], [007                                                                                                                                  |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    | [0073], [0097]                                                                                                                                                    |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| <u> </u>                                                                                                                                                                                                                                           |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| Further documents are listed in the continuation of Box C.  X See patent family annex.                                                                                                                                                             |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| * Special categories of cited documents :  *T* later document published after the international filing date                                                                                                                                        |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| "A" docume                                                                                                                                                                                                                                         | and not in conflict with the application but<br>tand the principle or theory underlying the                                                                       |                              |                                    |  |  |  |  |  |  |  |  |

| considered to be of particular relevance invention                                                                                                                                                                                                 |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| filing o                                                                                                                                                                                                                                           | ticular relevance; the claimed invention idered novel or cannot be considered to                                                                                  |                              |                                    |  |  |  |  |  |  |  |  |

| "L" document which may throw doubts on priority claim(s) or involve an inventive step when the document is taken alone which is clied to establish the publication date of another "Y" document of particular relevance; the claimed invention     |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| citation or other special reason (as specified)  cannot be considered to involve an invanitive step when it of document referring to an oral disclosure, use, exhibition or document is combined with one or more other such document is combined. |                                                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

| other                                                                                                                                                                                                                                              | mbination being obvious to a person skilled                                                                                                                       |                              |                                    |  |  |  |  |  |  |  |  |

| *P" docume                                                                                                                                                                                                                                         | *P" document published prior to the international filing date but in the art.  *ater than the priority date claimed "8" document member of the same patent family |                              |                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                    | actual completion of the international search                                                                                                                     |                              | of the international search report |  |  |  |  |  |  |  |  |

| ]                                                                                                                                                                                                                                                  | ,                                                                                                                                                                 | - 21 11 12 13                |                                    |  |  |  |  |  |  |  |  |

| 21 June 2010                                                                                                                                                                                                                                       |                                                                                                                                                                   |                              | 05/07/2010                         |  |  |  |  |  |  |  |  |

| Name and                                                                                                                                                                                                                                           | mailing address of the ISA/                                                                                                                                       | Authorized offic             | 94                                 |  |  |  |  |  |  |  |  |

| Name and mailing address of the ISA/  European Patent Office, P.B. 5818 Patentlaan 2                                                                                                                                                               |                                                                                                                                                                   |                              | <del></del>                        |  |  |  |  |  |  |  |  |

| NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,                                                                                                                                                                                                   |                                                                                                                                                                   |                              | Mant 6 a Laura                     |  |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                  | Fax: (+31-70) 340-3016                                                                                                                                            | Paris                        | Martin, Laura                      |  |  |  |  |  |  |  |  |

| FARM BCT/ISA/                                                                                                                                                                                                                                      | 210 (second sheet) (April 2005)                                                                                                                                   |                              |                                    |  |  |  |  |  |  |  |  |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No PCT/US2010/029677

| Palent document<br>cited in search report |    | Publication<br>date |          | Patent family<br>member(s) |        | Publication<br>date      |

|-------------------------------------------|----|---------------------|----------|----------------------------|--------|--------------------------|

| US 5844776                                | A  | 01-12-1998          | CN<br>JP | 1154558<br>9097124         | A<br>A | 16-07-1997<br>08-04-1997 |

| WO 2008040028                             | A2 | 03-04-2008          | US       | 2008082766                 | A1     | 03-04-2008               |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

|                                           |    |                     |          |                            |        |                          |

### フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PE,PG,PH,PL,PT,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

(72)発明者 アンドレウ ティー.スウイング

アメリカ合衆国 カリフォルニア州 95030 ロス ガトス ルククイ ロード 16370

(72)発明者 ジャソン ダブリュ.クルアウス

アメリカ合衆国 ニューヨーク州 1 1 2 1 1 ブロオクルイン アプト 3 ケー ノルトフ 4 トフ ストリート 1 6 1

F ターム(参考) 5B018 GA04 HA35 KA15 KA18 MA22 NA01 NA06 QA16 5B065 BA05 BA09 ZA04