República Federativa do Brasil

Ministério do Desenvolvimento, Indústria

e do Comércio Exterior

Instituto Nacional da Propriedade Industrial

## (21) PI 0717254-0 A2

\* B R P I 0 7 1 7 2 5 4 A 2 \*

(62) Data de Depósito do Pedido Original:

PI0109685 - 23/03/2001

(22) Data de Depósito: 31/10/2007

(43) Data da Publicação: 08/10/2013

(RPI 2231)

(51) Int.Cl.:

H03L 7/14

H03L 7/093

H03L 7/095

**(54) Título:** CIRCUITO DE CONTROLE DE FREQUÊNCIA DE OSCILAÇÃO

**(30) Prioridade Unionista:** 26/12/2006 JP 2006-349519

**(73) Titular(es):** Nihon Dempa Kogyo CO., LTD.

**(72) Inventor(es):** Naoki Onishi

**(74) Procurador(es):** Dannemann, Siemsen, Bigler & Ipanema Moreira

**(86) Pedido Internacional:** PCT JP2007071209 de 31/10/2007

**(87) Publicação Internacional:** WO 2008/078452de

03/07/2008

**(57) Resumo:** "SISTEMA E MÉTODO DE FUMO ELÉTRICO". Um sistema de fumo elétrico (21) compreendendo um cigarro (23) e um acendedor elétrico (25), no qual o cigarro (23) compreende uma superfície fosca de tabaco tubular (66) parcialmente cheia com material de tabaco (80) de modo a definir uma porção de barra de tabaco cheia (60) e uma porção de barra de tabaco vaga (90). O cigarro (23) e o acendedor (25) são mutuamente dispostos de modo que quando o cigarro (23) é recebido no acendedor (25), o elemento do aquecedor elétrico (37) do acendedor (25) pelo menos parcialmente sobrepõe pelo menos uma porção da porção da barra de tabaco cheia (60). O cigarro (23) e o acendedor (25) são também mutuamente dispostos de modo que quando o cigarro (23) é recebido no acendedor (25), a extremidade livre (15) do cigarro (23) fica fechada. O cigarro (23) inclui uma zona de perfurações (12,14) em uma localização ao longo da porção da barra de tabaco cheia (60), com o cigarro sendo isento de perfurações ao longo da porção da barra de tabaco vaga (90).

Relatório Descritivo da Patente de Invenção para "CIRCUITO DE CONTROLE DE FREQUÊNCIA DE OSCILAÇÃO".

Campo Técnico

A presente invenção refere-se a um circuito de controle de frequência de oscilação de um oscilador, e mais especificamente de um circuito de controle de frequência de oscilação suscetível de corrigir sua própria frequência em sincronismo com um sinal de saída e manter uma frequência de oscilação estável mesmo quando um sinal de referência altamente estável não é introduzido no mesmo.

10 Antecedentes da Técnica

Em uma estação base de um sistema de comunicação móvel da próxima geração, um sistema de radiodifusão digital terrestre, e similar, a precisão requerida para um sinal de referência tornou-se mais alta.

Para gerar um sinal de referência de frequência, um oscilador de referência de frequência de célio, um oscilador de referência de frequência de rubídio, um oscilador de referência de um tipo de sincronização de frequência usando um tipo de sinal GPS, e similares são usados em sistemas de radiodifusão e comunicação.

Todavia, uma vez que estes osciladores usualmente são dispendiosos, o sinal de referência dos osciladores é dividido para ser usado como uma fonte de sinal de referência de um aparelho.

O sinal de referência dividido é usado como um relógio de referência para um sistema de comunicação.

Especificamente, o sinal de referência é usado como um sinal de referência para uma comparação de fase em um circuito PLL (circuito de fase síncrona), um sinal de relógio de referência para um DSP (processador de sinal digital), um FPGA (conjunto de porta de campo programável) ou similar, e um relógio de amostragem para um conversor D/A (análogo/digital).

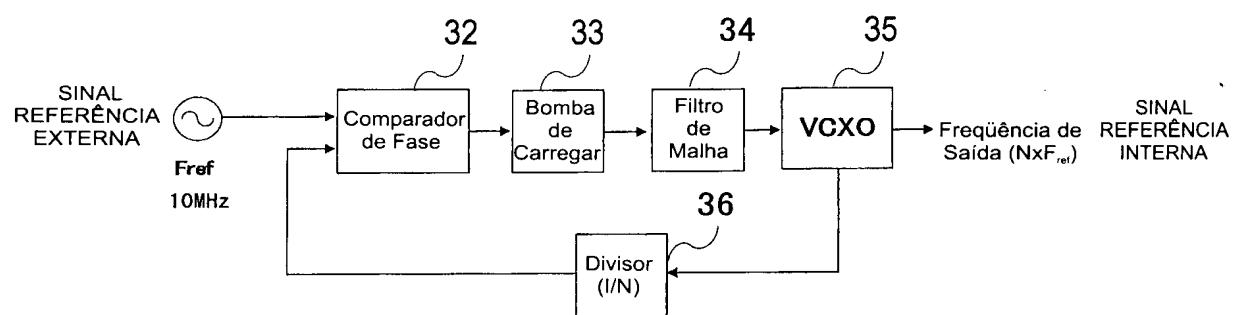

30 Circuito PLL Convencional: Figura 6

A seguir, uma descrição de um circuito PLL convencional será fornecida com referência à figura 6. A figura 6 é um diagrama em blocos de

um circuito PLL típico.

Como ilustrado na figura 6, o circuito PLL é munido de um comparador de fase 32 configurado para comparar um sinal de referência externo ( $F_{ref}$ ) com um sinal 1/N dividido para emitir um sinal de diferença de fase, 5 uma bomba de carregar 33 configurada para emitir o sinal de diferença como um sinal de duração de pulso, um filtro de malha 34 configurado para nivelar uma tensão de saída da bomba de carregar 33, um oscilador a cristal de tensão controlada (VCXO) 35 configurado para alterar uma frequência de acordo com uma tensão de controle do filtro de banda baixa 34 para oscilar 10 e emitir uma frequência desejada (sinal de referência interna: frequência de saída), e um divisor de frequência (divisor) 36 configurado para dividir a saída (sinal de referência interna) do VCXO 35 para 1/N.

O sinal de referência interna corresponde a um sinal  $N^*ref$ .

O circuito PLL é configurado para aplicar controle de realimentação ao VCXO interno 35 para que uma diferença de fase entre um sinal de referência externo e a frequência de saída do VCXO 35 para dessa formar 15 uma saída de oscilador sincronizada com o sinal de referência.

Especificamente, o comparador de fase 32 é configurado para comparar séis de um sinal de referência externo altamente estável e um sinal 20 de saída do VCXO 35 efetuando controle de frequência baseado sobre uma tensão de entrada e realizar controle PLL para que uma tensão CC obtida pelo nívelar um resultado de comparação de fase seja realimentada ao VC-XO 35 para dessa forma gerar um sinal altamente preciso.

O circuito PLL é largamente utilizado em aparelhos de comunicação 25 e radiodifusão e similares.

Um exemplo da técnica anterior de um circuito de controle de frequência no oscilador convencional é exposto no pedido de patente Japonês apresentado no 2000-083003 (Documento de Patente 1) e no pedido de patente Japonês exposto no 2003-179489 (Documento de Patente 2).

30 O documento de patente 1 apresenta um sistema de ajuste de frequência de livre funcionamento no qual um contador de frequência realiza uma operação de contagem sincronizada com um sinal de saída de um VCO

(oscilador de tensão controlada) que é introduzido dentro de um período de tempo correspondente à duração de um pulso, um circuito de bloqueio armazena no seu interior um valor de contagem correspondente a uma frequência de oscilação do VCO, e quando o valor de contagem se desvia de

- 5 uma faixa predeterminada, uma CPU altera uma tensão de aplicação ao VCO para ajustar uma frequência de livre funcionamento do VCO 10 para se enquadrar dentro de uma faixa predeterminada.

• O Documento de Patente 2 apresenta um circuito de fase síncrona tendo uma função de automaticamente ajustar uma frequência de livre funcionamento de um oscilador de tensão controlada (VCO), no qual um microcomputador conta o número de pulsos de um sinal de pulso emitido pelo VCO em um período em que uma saída de um comparador de fase está a um nível predeterminado e atualiza um dado de controle baseado sobre o valor contado, e um DAC (conversor digital analógico) converte os dados em 15 um sinal analógico para que o sinal analógico seja combinado com um sinal de LPF (filtro de malha) para ser usado como um sinal de controle de frequência do VCO.

Documento de Patente 1: Pedido de Patente Japonês nº 2000-083003.

Documento de Patente 2: Pedido de Patente Japonês nº 2003-179489.

20 Descrição da Invenção

Problemas a serem resolvidos pela Invenção

Todavia, n circuito PLL convencional, uma vez que a comparação de fase não pode ser efetuada quando um sinal de referência não é introduzido na mesma, o circuito PLL pode comutar para outro sinal de referência externo ou operar em um estado de livre funcionamento do oscilador controlado por tensão. Quando comuta para outro sinal de referência livre de 25 um sistema de reserva, uma vez que o controle PLL é efetuado mais uma vez, o desvio do sinal de referência depende do sinal de referência externo, e por conseguinte, não causa qualquer problema. Todavia, quando comuta para operar no estado de livre funcionamento, a frequência é excessivamente controlada em resposta a um resultado de comparação de fase durante a 30 comutação para aderir a uma frequência limite superior ou inferior, e assim,

existe o problema do desvio de frequência se tornar grande.

Como uma solução de curto para prazo para resolver o problema de livre funcionamento, um VC-TCXO altamente estável (oscilador a cristal de tensão controlada-temperatura compensada) pode ser usado como o oscilador de tensão controlada.

Todavia, embora uma solução desta natureza permita operação com uma estabilidade de frequência de por exemplo:  $\pm 0,5$  ppm, poderia não ser suscetível de proporcionar um desempenho satisfatório por um longo período de tempo devido ao envelhecimento.

Por exemplo, quando se presume que as características de envelhecimento são de cerca de 41 ppm por ano, um desvio de frequência pode se elevar ao máximo de 10,5 ppm no transcurso de 10 anos. Isto também pode ser explanado de que se uma frequência de saída de uma onda portadora em comunicação é de 800 MHz, um desvio de frequência pode equivaler a 8,4 kHz similar aquele da frequência de referência. Um desvio de frequência dessa natureza não é tolerável para um sistema.

Outrossim, mesmo em um sistema altamente estável usando um VCOXO (oscilador a cristal controlado de tensão controlada), uma vez que as características de envelhecimento podem causar um desvio de frequência em um longo período de tempo, torna-se necessário efetuar uma operação de correção a cada período de tempo predeterminado, e, por conseguinte, havia o problema da operação de correção ser trabalhosa.

Outrossim, o sistema ou circuito exposto no Documento de Patente 1 ou 2, conta a saída do VCO ou a saída do comparador de fase para efetuar a frequência de funcionamento livre. Todavia o sistema ou circuito não realiza o ajuste de frequência pelo diretamente detectar uma anormalidade do sinal de referência externo e é incapaz de atender suficientemente ao envelhecimento.

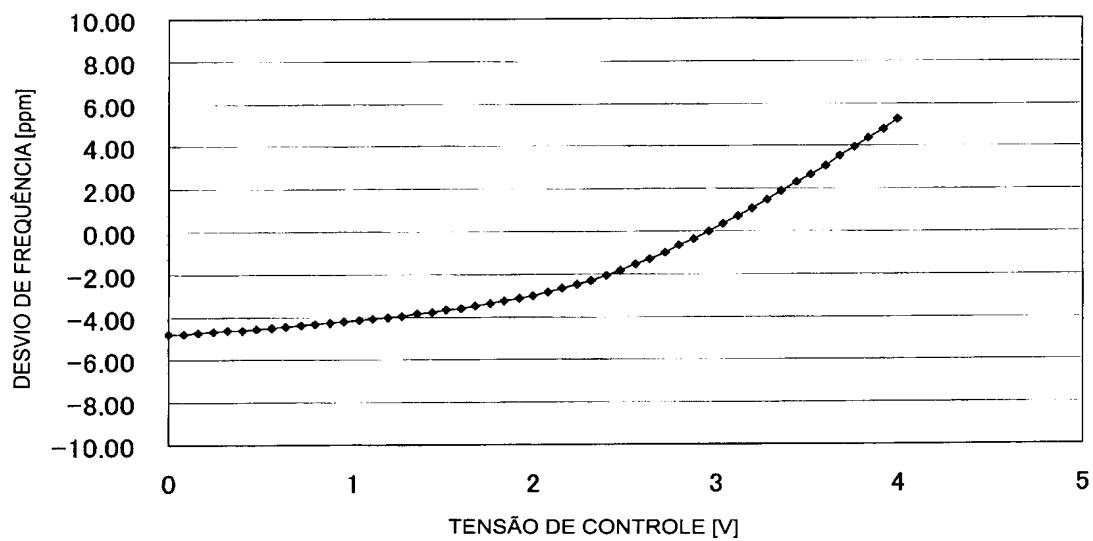

#### Características de Tensão de Controle de VCXO: Figura 7

As características de tensão de controle do VCXO são mostradas na figura 7. A figura 7 é uma vista mostrando características de tensão de controle típicas de um oscilador a cristal de tensão controlada. Na figura

7, o eixo geométrico horizontal representa uma tensão de controle, e o eixo geométrico vertical representa um desvio de frequência.

No VCXO de exemplo da figura 7, o VCX O é suscetível de operar quando a tensão de controle está na faixa de 0 a 4 V, enquanto é incapaz 5 de operar quando a tensão de controle é de 4 V ou maior.

Uma vez que o desvio de frequência se eleva com o transcurso de tempo mesmo no caso do VCXO, uma tensão de controle apropriada varia correspondentemente.

A presente invenção foi realizada em consideração da situação 10 supra mencionada, e constitui um objetivo da invenção proporcionar um circuito de controle de frequência de oscilação suscetível de corrigir sua própria frequência e manter uma frequência de oscilação estável mesmo quando um sinal de referência altamente estável não é introduzido na mesma e opera em um estado de funcionamento livre.

#### 15 Meios para Solucionar os Problemas

Para superar os problemas das técnicas convencionais, de acordo com um aspecto da presente invenção, é apresentado um circuito de controle de frequência de oscilação que compreende: um oscilador de tensão controlada; um divisor de frequência configurado para dividir uma saída 20 do oscilador de tensão controlada; um comparador de fase configurado para comparar fases de um sinal de referência externo e uma saída do divisor de frequência; um filtro de malha configurado para nivelar uma saída do comparador de fase e emitir a saída nivelada; um circuito de detecção suscetível de detectar o sinal de referência externo; um circuito de geração de pulsos 25 configurado para gerar pulsos mediante a recepção de uma informação de geração de pulso a ser emitida para o filtro de malha; uma memória suscetível de armazenar no seu interior uma informação de tensão prescrita e a informação de geração de pulsos correspondente às informações de tensão prescrita; um comutador configurado para ligar/desligar uma conexão entre o 30 comparador de fase e o filtro de malha; e uma unidade de controle configurada para ativar o comutador quando um nível do sinal de referência externo detectado pelo circuito de detecção está dentro de uma faixa apropriada en-

quanto desativando o comutador quando o nível está forma da faixa apropriada para dessa forma emitir a informação de geração de pulso armazenada na memória para o circuito de geração de pulsos.

No circuito de controle de frequência de oscilação de acordo

5 com o aspecto acima da presente invenção, as informações de tensão prescrita armazenadas na memória de uma tensão de controle central de uma tensão de saída suscetível de controlar o oscilador de tensão controlada.

- No circuito de controle de frequência de oscilação de acordo

com o aspecto acima da presente invenção, a memória armazena uma tabela

10 de características de envelhecimento, em lugar das informações de tensão prescrita e as informações de geração de pulso correspondentes às informações de tensão prescritas, a tabela armazenando uma tensão de controle apropriada para um tempo de envelhecimento e uma informação de geração de pulso correspondente à tensão de controle, e a unidade de controle

15 mede o tempo por intermédio de um timer previsto no seu interior, recupera a tensão de controle correspondente ao tempo medido a partir da tabela de características de envelhecimento da memória quando o nível do sinal de referência externa está fora da faixa apropriada, efetua a leitura-emissão das informações de geração de pulsos correspondentes à tensão

20 de controle recuperada, e emite as informações de geração de pulsos de leitura para o circuito de geração de pulsos.

No circuito de controle de frequência de oscilação de acordo com o aspecto acima da presente invenção, um circuito de detecção de nível configurado para detectar um nível de tensão de uma saída do filtro de m-

25 lha para dessa forma emitir uma informação de tensão mais recente para a unidade de controle é previsto, a memória armazena uma tabela de informações de geração de tensão/pulso em lugar das informações de tensão prescrita e das informações de geração de pulsos correspondentes às informações de tensão prescrita, a tabela armazenando as informações de tensão mais recentes, uma pluralidade de informações de tensão, e uma informação de geração de pulso correspondente às informações de tensão, e a unidade

30 de controle atualiza as informações de tensão mais recentes da memória

para as informações de tensão mais recentes recebidas do circuito de detecção de nível, efetuar a leitura-emissão das informações de geração de pulso correspondentes às informações de tensão mais recentes recebidas da tabela de informação de geração de tensão/pulso da memória quando o 5 nível do sinal de referência externo está dentro da faixa apropriada, e emite as informações de geração de pulsos de leitura para o circuito de geração de pulsos.

No circuito de controle de frequência de oscilação de acordo com o aspecto acima da presente invenção, um oscilador a cristal de tensão controlada, um oscilador a cristal de tensão controlada-temperatura controlada, um oscilador a cristal forno controlado é usado em lugar do oscilador de tensão controlada.

10

No circuito de controle de frequência de oscilação de acordo com o aspecto acima da presente invenção, o circuito de geração de pulsos 15 é um circuito de modulação de duração de pulsos, e as informações de geração de pulsos emitidas pela unidade de controle são informações sobre um ciclo de serviço de modulação de duração de pulsos.

De acordo com outro aspecto da presente invenção, é apresentado um processo de correção no circuito de controle de frequência de oscilação de acordo com o aspecto acima da presente invenção, o processo 20 compreendendo introduzir um sinal de referência em uma temporização específica em um estado onde o sinal de referência externo não é introduzido; descontinuar a introdução do sinal de referência; e controlar pela unidade de controle, um funcionamento livre de acordo com a tensão de controle central 25 para de esse modo efetuar a correção.

De acordo com outro aspecto da presente invenção, é apresentado um processo de correção no circuito de controle de frequência de oscilação de acordo com o aspecto acima da presente invenção, o processo 30 compreendendo introduzir um sinal de referência em uma temporização específica em um estado onde o sinal de referência externo não é introduzido, descontinuar a introdução do sinal de referência; e reportar-se, pela unidade de controle, à tabela de características de envelhecimento, controlar um fun-

cionamento livre de acordo com a tensão de controle correspondente ao tempo medido para desse modo efetuar a correção.

#### Vantagens da Invenção

De acordo com o aspecto acima da presente invenção, o circuito de controle de frequência de oscilação compreende um oscilador de tensão controlada; um divisor de frequência configurado para dividir uma saída do oscilador de tensão controlada; um comparador de fase configurado para comparar as fases de um sinal de referência externo e uma saída do divisor de frequência; um filtro de passo-baixo configurado para nivelar uma saída do comparador de fase e emitir a saída nivelada; um circuito de detecção suscetível de detectar o sinal de referência externo; um circuito de geração de pulsos configurado para gerar pulsos mediante a recepção de informações de geração de pulsos a ser emitida para o filtro de passo-baixo; uma memória suscetível de armazenar no seu interior uma informação de tensão prescrita e a informação de geração de pulsos correspondente às informações de tensão prescrita; um comutador configurado para ligar/desligar uma conexão entre o comparador de fase e o filtro de passo-baixo; e uma unidade de controle configurada para ativar o comutador quando um nível do sinal de referência externo detectado pelo circuito de detecção está dentro de uma faixa adequada enquanto desativando o comutador quando o nível está fora da faixa adequada para dessa maneira emitir as informações de geração de pulso armazenadas na memória para o circuito de geração de pulsos. É, por conseguinte, possível proporcionar a vantagem de uma frequência de oscilação estável poder ser mantida pelo corrigir sua própria frequência mesmo quando um sinal de referência altamente estável não é introduzido e funciona em um estado de funcionamento livre.

De acordo com o circuito de controle de frequência de oscilação do aspecto acima da presente invenção, as informações de tensão prescrita armazenadas na memória é uma tensão de controle central de uma tensão de controle suscetível de controlar o oscilador de tensão controlada. É, por conseguinte, possível proporcionar a vantagem de uma frequência de oscilação estável poder ser mantida pelo corrigir sua própria frequência.

De acordo com o circuito de controle de frequência de oscilação do aspecto acima da presente invenção, a memória armazena uma tabela de características de envelhecimento, em lugar das informações de tensão prescrita e das informações de geração de pulsos correspondentes às informações de tensão prescrita, a tabela armazenando uma tensão de controle apropriada por um tempo de envelhecimento e uma informação de geração de pulsos correspondente à tensão de controle, e a unidade de controle mede o tempo por intermédio de um contador de tempo previsto no seu interior, recupera a tensão de controle correspondente ao tempo medido da tabela de características de envelhecimento da memória quando o nível do sinal de referência externo está fora da faixa apropriada, efetua a leitura-emissão das informações de geração de pulsos correspondentes à tensão de controle recuperada, e emite as informações de geração de pulso de leitura para o circuito de geração de pulsos. Por conseguinte, é possível proporcionar a vantagem de uma correção de frequência poder enfrentar o envelhecimento.

De acordo com o circuito de controle de frequência de oscilação do aspecto acima da presente invenção, um circuito de detecção de nível configurado para detectar um nível de tensão de uma saída do filtro de passo-baixo para desse modo emitir uma informação de tensão para a unidade de controle é previsto, a memória armazena uma tabela de informações de geração de tensão/pulso em lugar das informações de tensão prescrita e as informações de geração de pulsos correspondentes às informações de tensão prescrita, a tabela armazenando as informações de tensão mais recentes, uma pluralidade de informações de tensão, e uma informação de geração de pulso correspondente às informações de tensão, e a unidade de controle atualiza as informações de tensão mais recentes da memória para as informações de tensão mais recentes do circuito de detecção de nível, efetua a leitura-emissão das informações de geração de pulsos correspondentes às informações de tensão mais recentes da tabela de informações de geração de tensão/pulsos da memória quando o nível do sinal de referência externo está dentro da faixa apropriada, e emite as informações de geração de pulsos de leitura para o circuito de geração de pulsos. Por conseguinte, é

possível proporcionar a vantagem de uma frequência de oscilação estável poder ser mantida pelo suceder ao estado de operação prévia mesmo quando o sinal de referência não é introduzido e operar em um estado de funcionamento livre.

5 De acordo com o aspecto acima da presente invenção, o processo de correção no circuito de controle de frequência de oscilação de acordo com o aspecto acima da presente invenção compreende introduzir um sinal de referência em uma temporização específica em um estado onde o sinal de referência externa não é introduzido; descontinuar a introdução do sinal de referência; e controlar, pela unidade de controle, um funcionamento livre de acordo com a tensão de controle central para assim efetuar a correção. Por conseguinte, é possível proporcionar a vantagem de a correção poder ser efetuada sem utilizar um dispositivo especial.

10 De acordo com o aspecto acima da presente invenção, o processo de correção no circuito de controle de frequência de oscilação de acordo com o aspecto acima da presente invenção compreende introduzir um sinal de referência em uma temporização específica em um estado onde o sinal de referência externo não é introduzido; descontinuar a introdução do sinal de referência; e reportando-se, pela unidade de controle, à tabela de 15 características de envelhecimento, controlar uma funcionamento livre de acordo com a tensão de controle correspondente ao tempo medido para desse modo efetuar a correção. Por conseguinte, é possível proporcionar a vantagem da correção suscetível de enfrentar o envelhecimento poder ser realizada sem utilizar um dispositivo especial.

20 **Breve Descrição dos Desenhos**

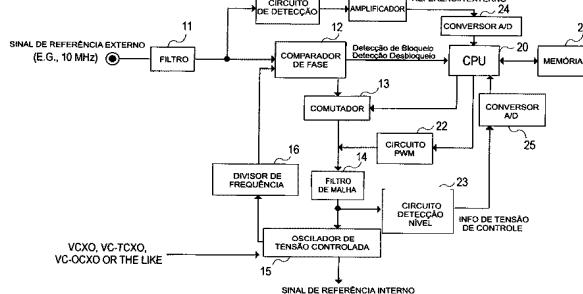

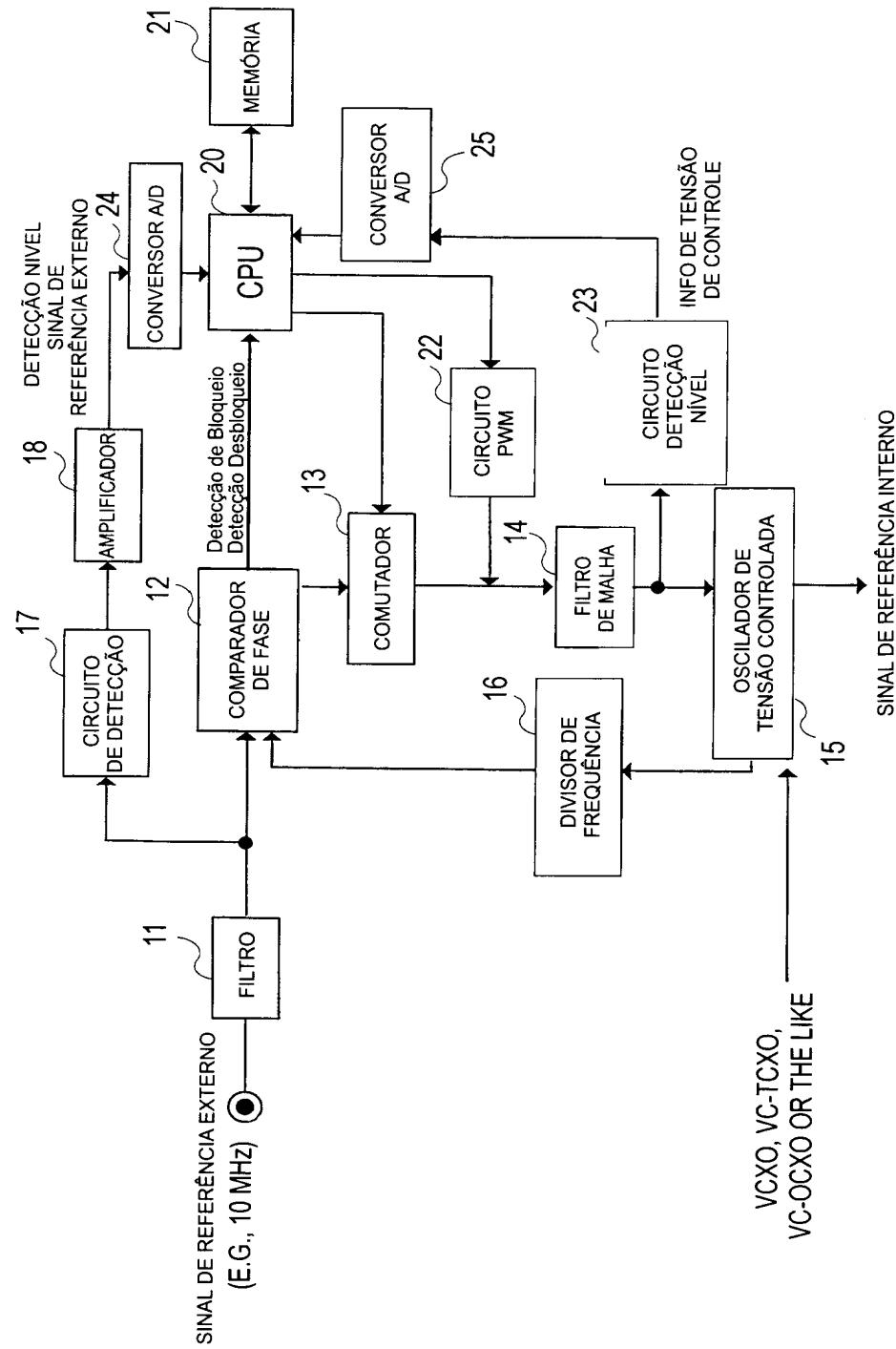

A figura 1 é um diagrama em blocos da configuração de um circuito de frequência de oscilação de acordo com uma modalidade da presente invenção;

25 A figura 2 é uma vista esquemática de uma tabela de ciclo de serviço PWM e tensão;

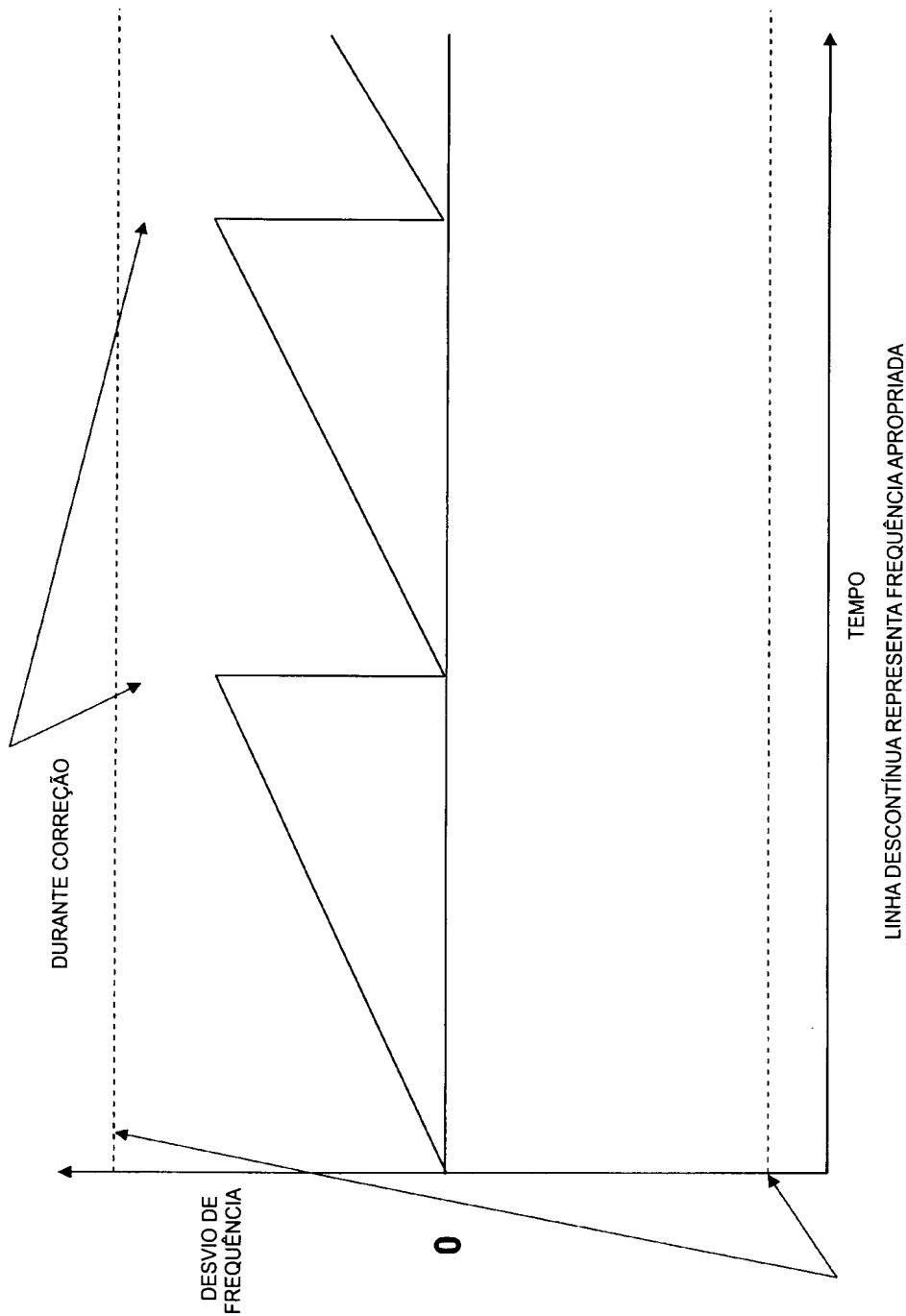

A figura 3 é uma vista mostrando características durante a correção;

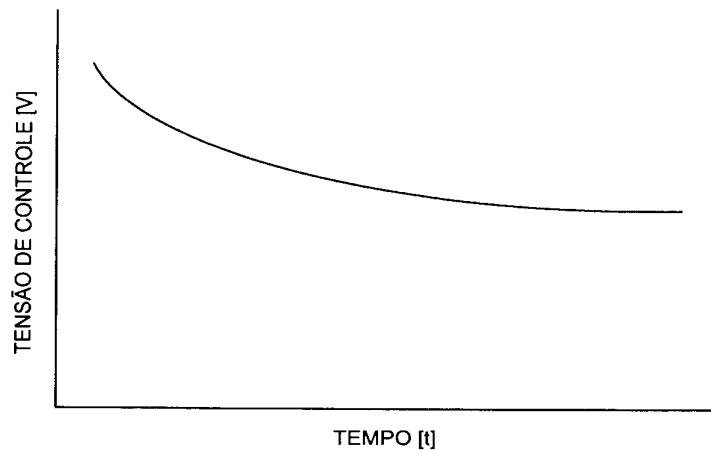

A figura 4 é uma vista mostrando as características de tensão de controle e envelhecimento;

A figura 5 é uma vista esquemática de uma tabela de características de envelhecimento;

5 A figura 6 é um diagrama em blocos da configuração de um circuito PLL típico;

A figura 7 é uma vista mostrando características de tensão de controle típicas de um oscilador a cristal de tensão controlada.

#### Listagem de Referência

- |    |                                     |

|----|-------------------------------------|

| 10 | 11 - FILTRO                         |

|    | 12 - COMPARADOR DE FASE             |

|    | 13 - COMUTADOR                      |

|    | 14 - FILTRO DE MALHA                |

|    | 15 - OSCILADOR DE TENSÃO CONTROLADA |

| 15 | 16 - DIVISOR DE FREQUÊNCIA          |

|    | 17 - CIRCUITO DE DETECÇÃO           |

|    | 18 - AMPLIFICADOR                   |

|    | 20 - CPU                            |

|    | 21 - MEMÓRIA                        |

| 20 | 12 - CIRCUITO PWM                   |

|    | 23 - CIRCUITO DE DETECÇÃO DE NÍVEL  |

|    | 24 - CONVERSOR A/D                  |

|    | 25 - CONVERSOR A/D                  |

|    | 32 - COMPARADOR DE FASE             |

| 25 | 33 - BOMBA DE CARREGAR              |

|    | 34 - FILTRO DE MALHA                |

|    | 35 - VCXO                           |

|    | 36 - DIVISOR DE FREQUÊNCIA          |

#### Melhor Modo de Realização da Invenção

30 Descrição da Modalidade

Uma modalidade da presente invenção será descrita com referência aos desenhos apensos.

Um circuito de controle de frequência de oscilação de acordo com uma modalidade de realização da presente invenção compreende um oscilador de tensão controlada; um divisor de tensão configurado para dividir uma saída do oscilador de tensão controlada; um comparador de fase configurado para comparar as fases de um circuito de referência externo e uma saída do divisor de frequência; um filtro de malha configurado para nivelar uma saída do comparador de fase e emitir a saída nivelada; um circuito de detecção suscetível de detectar o sinal de referência externo; um circuito de geração de pulsos configurado para gerar pulsos mediante a recepção de 5 informações de geração de pulsos a ser emitida para o filtro de malha; uma memória suscetível de armazenar no seu interior uma informação de tensão prescrita e a informação de geração de pulsos correspondente à informação de tensão prescrita; um comutador configurado para ativar/desativar uma conexão entre comparador de fase e o filtro de malha; e uma unidade de 10 controle configurada para ativar o comutador quando um nível do sinal de referência externo detectado pelo circuito de detecção está dentro de uma faixa adequada enquanto desativando o comutador quando o nível está fora da faixa adequada para desse modo emitir a informação de geração de pulsos armazenada na memória para o circuito de geração de pulsos. Por conseguinte, é possível manter uma frequência de oscilação estável pelo corrigir sua própria frequência mesmo quando um sinal de referência altamente estável não é introduzido e funciona em um estado de funcionamento livre.

Um circuito de controle de frequência de oscilação de acordo com uma modalidade da presente invenção é o circuito de controle de frequência de oscilação em que a memória armazena uma tabela de características de envelhecimento, no lugar das informações de tensão prescrita e 25 as informações de geração de pulsos correspondentes às informações de tensão prescrita, a tabela armazenando uma tensão de controle adequada para um tempo de envelhecimento e uma informação de geração de pulsos correspondente à tensão de controle recuperada, e emite as informações de geração de pulso de leitura para o circuito gerador de pulsos. Por conseguinte, é possível efetuar a correção de frequência de modo a enfrentar o enve-

lhecimento.

Um circuito de controle de frequência de oscilação de acordo com uma modalidade da presente invenção é o circuito de controle de frequência de oscilação no qual um circuito de detecção de nível configurado para detectar um nível de tensão de uma saída do filtro de malha para desse modo emitir uma informação de tensão mais recente para o circuito de controle é proporcionado, a memória armazena uma tabela de informações de geração de tensão/pulsos no lugar de informações de tensão prescrita e as informações de geração de pulsos correspondentes às informações de tensão prescrita, a tabela armazenando as informações de tensão mais recentes, uma pluralidade de informações de tensão, e uma informação de geração de pulsos correspondente às informações de tensão, e a unidade de controle atualiza as informações de tensão mais recentes da memória para a entrada de informações de tensão mais recentes do circuito de detecção de nível, efetua a leitura-emissão das informações de geração de pulsos correspondentes às informações de tensão mais recentes da tabela de informações de geração de tensão/pulsos da memória quando o nível do sinal de referência externa está dentro da faixa apropriada, e emite as informações de geração de pulsos de leitura para o circuito de geração de pulsos. Por conseguinte, é possível manter uma frequência de oscilação estável pelo suceder ao estado de operação prévia mesmo quando o sinal de referência não é introduzido e funciona em estado de funcionamento livre.

#### Círcuito de Controle de Frequência de Oscilação: Figura 1

Uma descrição de um circuito de controle de frequência de oscilação de acordo com uma modalidade da presente invenção será apresentada com referência à figura 1. A figura 1 é um diagrama em blocos da configuração de um circuito de controle de frequência de oscilação de acordo com uma modalidade da presente invenção.

O circuito de controle de frequência de oscilação (presente circuito) de acordo com a modalidade da presente invenção, conforme mostrado na figura 1, inclui um filtro 11, um comparador de fase 12, um comutador 13, um filtro de malha 14, um oscilador de tensão controlada 15, um divisor

de frequência 16, um circuito de detecção 17, um amplificador 18, uma CPU (unidade central de processamento) 20, uma memória 21, um circuito PWM (modulação por duração de pulsos) 22, um circuito de detecção de nível 23, um conversor A/D 24 e um conversor A/D 25.

## 5 Cada Parte do Presente Circuito

O filtro 11 é um filtro configurado para limitar uma banda de um sinal de referência externo tendo uma frequência de por exemplo 10 MHz. O filtro 11 tem a função de rejeitar um componente de alta frequência do sinal de referência externo, embora a função não seja essencial como uma configuração básica.

O comparador de fase 12 é configurado para comparar fases de um sinal de referência emitido pelo filtro 11 e um sinal do qual a frequência é dividida pelo divisor de frequência 16 para desse modo emitir um sinal de diferença de fase.

Outrossim, o comparador de fase 12 é configurado para comparar as fases do sinal de referência externo e do sinal de frequência-dividida para desse modo emitir um sinal de detecção de sincronismo para a CPU 20 quando uma sincronização (bloqueio) tiver sido detectada, enquanto emitindo um sinal de detecção de desbloqueio para a CPU 20 quando um assincronismo (desbloqueio) tiver sido detectado.

O comutador 13 é configurado para ligar/desligar uma conexão entre o comparador de fase 12 e o filtro de malha 14, de acordo com um comando de manobra da CPU 20. Ou seja, ao receber um comando de ligar (turn-on) da CPU 20, o comutador 13 fornece uma saída do comparador de fase 12 ao filtro de malha 14, enquanto interrompendo a conexão entre comparador de fase 12 e o filtro de malha 14 mediante a recepção de um comando de desligar da CPU 20.

O filtro de malha 14 é um filtro configurado para nivelar a tensão de saída do comparador de fase 12: isto é, o filtro nivela uma tensão de controle a ser alimentada ao oscilador de tensão controlada 15.

O oscilador de tensão controlada 15 é configurado para alterar uma frequência de acordo com a tensão de controle do filtro de malha 14.

para oscilar e emitir uma frequência desejada (sinal de referência interna).

Outrossim, um oscilador a cristal de tensão controlada (VCXO) ou um oscilador a cristal forno controlado, de tensão controlada (VC-OCXO) pode ser usado no lugar do oscilador de tensão controlada (VCO).

5 O divisor de frequência 16 é configurado para dividir o sinal de referência interno emitido pelo oscilador de tensão controlada 15 em 1/N.

O circuito de detecção 17 é configurado para detectar um nível do sinal de saída do filtro 11.

10 O amplificador 18 é configurado para amplificar um sinal detectado pelo circuito de detecção 17.

A CPU 20 é configurada para receber uma informação de tensão de controle do conversor A/D 25 e armazenar a informação de tensão de controle na memória 21 como uma informação de tensão de controle mais recente. Especificamente, a CPU 20 sempre recebe as informações de tensão de controle do conversor A/D 25, e quando as informações de tensão de controle recebidas não tiverem sido alteradas em relação a uma informação de tensão de controle prévia, a informação de tensão de controle armazenada na memória 21 não é atualizada, ao passo que quando as informações de tensão de controle tiverem sido alteradas em relação às informações de tensão de controle prévias, as informações de tensão de controle da memória 21 são atualizadas.

25 Outrossim, mediante a recepção do nível detectado do sinal de referência externo (REF externo) do conversor A/D 24, a CPU 20 realiza uma determinação quanto ao fato de nível detectado estar dentro de uma faixa apropriada (variando de um primeiro valor limiar para um segundo valor limiar) armazenado na memória 21 e emite um comando de ativação para o comutador 13 quando está dentro da faixa apropriada enquanto emitindo um comando de desativação para o comutador 13 quando está fora da faixa apropriada.

30 Outrossim, quando o nível de detecção da REF externa está fora da faixa apropriada, a CPU 20 reporta-se a uma tabela de tensão e ciclo de serviço PWM armazenada na memória 21 e emite uma informação de dura-

ção de pulso correspondente a um ciclo de serviço PWM baseada sobre uma informação de tensão de uma presente tensão de controle (mais recente) para o circuito PWM 22.

A memória 21 armazena no seu interior a informação de tensão de controle mais recente, os primeiro e segundo valores limiares servindo como uma base da faixa apropriada para o nível de detecção da REF externa, e a tensão e tabela de ciclo de serviço de PWM.

A informação de tensão de controle é atualizada na memória 21 quando uma alteração tiver sido detectada pelo circuito de detecção de nível 23, para que um valor mais recente possa ser mantido.

#### Tabela de Tensão e Ciclo de Serviço PWM: Figura 2

Uma descrição da Tabela de Tensão e Ciclo de Serviço PWM será apresentada abaixo com referência à figura 2. A figura 2 é uma vista esquemática da tabela de tensão e ciclo de serviço PWM.

Como mostrado na figura 2, a tabela de tensão e ciclo de serviço PWM armazena um ciclo de serviço PWM (%) para especificar uma duração de pulso para uma informação de tensão.

Aqui, a informação de tensão é usada para predeterminar um ciclo de serviço PWM de pulsos emitidos pelo circuito PWM 22 para o filtro de malha 14 de maneira a manter um valor (informação de tensão de controle) da tensão de controle do filtro de malha 14.

Por conseguinte, quando um ciclo de serviço PWM correspondente às informações de tensão de controle detectadas pelo circuito de detecção de nível 23 é lida da tabela de tensão e ciclo de serviço PWM e o circuito PWM 22 emite pulsos correspondentes ao ciclo para o filtro de malha 14, tensão de controle idêntica a precedente é emitida pelo filtro de malha 14 para o oscilador de tensão controlada 15.

O circuito PWM 22 efetua a modulação de duração de pulsos sobre dados do ciclo de serviço PWM introduzidos pela CPU 20 para desse modo emitir um sinal de pulso desejado para o filtro de malha 14. Um conversor D/A (digital/analógico) pode ser usado no lugar do circuito PWM enquanto os dados das informações de tensão puderem ser emitidos pela CPU 20.

O circuito de detecção de nível 23 é configurado para detectar uma saída de tensão CC do filtro de malha 14 para emitir a tensão detectada para o conversor A/D 25 como as informações de tensão de controle.

O conversor A/D 24 é configurado para converter um sinal analógico do nível de detecção da REF externa emitido pelo amplificador 18 um sinal digital a ser emitido para a CPU 20.

O conversor A/D 25 é também configurado para converter um sinal analógico da informação de tensão de controle do circuito de detecção de nível 23 em um sinal digital a ser emitido para a CPU 20.

No presente circuito, uma vez que a CPU 20 é suscetível de perceber um a anormalidade de entrada do sinal de referência externo do nível de detecção de REF externo do circuito de detecção emitido pelo circuito de detecção 17 e o amplificador 18, um sinal de detecção de desbloqueio do comparador de fase 12 não é usado.

#### 15 Operação do Presente Circuito

Uma descrição da operação do presente circuito será apresentada.

Em um estado de operação normal do presente circuito, o comutador 13 é ativado e o comparador de fase 12 e o filtro de malha 14 estão em uma condição ligada. Outrossim, o comparador de fase 12 emite o sinal de diferença de fase do sinal de referência externo e o sinal do divisor de frequência 16 para o oscilador de tensão controlada 15 através do filtro de malha 14 e controla uma frequência de oscilação do oscilador de tensão controlada 15. Nessa ocasião, o circuito de detecção de nível 23 detecta uma tensão de controle mais recente para emitir a tensão de controle mais recente para a CPU 20 através do conversor A/D 25, e a CPU 20 atualiza a informação de tensão de controle mais recente armazenada na memória 21 quando a informação de tensão de controle tiver sido alterada.

Outrossim, no presente circuito, o sinal de referência externo é detectado pelo circuito de detecção 17 e amplificado pelo amplificador 18 para que o nível da REF externa seja detectado e emitido para a CPU 20 através do conversor A/D 24.

Na CPU 20, uma determinação é feita quanto ao fato do nível de detecção da REF externa estar dentro da faixa apropriada. Especificamente, o valor do nível de detecção da REF externa é determinado estar dentro da faixa apropriada quando o valor está entre o primeiro valor limiar e o segundo valor limiar representando a faixa apropriada armazenada na memória 21. Por outro lado, o valor do nível de detecção da REF externa é determinado estar fora da faixa apropriada quando o valor não está entre o primeiro valor limiar e o segundo valor limiar.

Quando o resultado da determinação mostra que o nível de detecção está dentro da faixa apropriada, a CPU 20 funciona em um estado normal para manter o estado ativado do comutador 13. Quando o resultado da determinação mostra que o nível de detecção está fora da faixa apropriada, a CPU 20 funciona em um estado anormal para colocar o comutador 13 em um estado desativado para que a conexão entre o comparador de fase 12 e o filtro de malha 14 seja interrompida.

Outrossim, no estado de operação anormal, a CPU 20 efetua a leitura-emissão da informação de tensão de controle mais recente armazenada na memória 21, lê o ciclo de serviço PWM correspondente às informações de tensão da tabela de tensão e ciclo de serviço PWM, e emite informações (dados) para formar pulsos correspondentes ao ciclo de serviço PWM para o circuito PWM 22.

O circuito PWM 22 gera pulsos de acordo com a entrada de informações de geração de pulsos recebida da CPU 20 e emite a tensão de controle para o oscilador de tensão controlada 15 através do filtro de malha 14.

Desta maneira, quando uma anormalidade tiver ocorrido no sinal de referência externa, particularmente, quando o sinal de referência externo não é introduzido (o estado de funcionamento livre), ou similar, a CPU 20 imediatamente detecta a anormalidade da saída do circuito de detecção 17 no amplificador 18 e desligar a saída do comparador de fase 12, para que os mesmos pulsos da tensão de controle prévia que foram usados para controlar o oscilador de tensão controlada 15 possa ser emitidos pelo circuito PWM 22.

Isto é, pelo utilizar a saída do circuito PWM 22 em lugar da saída do comparador de fase 12, é possível controlar apropriadamente a oscilação de frequência no oscilador de tensão controlada 15 pelo suceder ao estado de operação prévio.

## 5 Outra Modalidade 1

No exemplo descrito acima, embora os pulsos emitidos pelo circuito PWM 22 terem sido gerados baseados sobre as informações de tensão de controle mais recentes detectadas pelo circuito de detecção de nível 23, uma informação de tensão padrão pode ser armazenada para que a informação de geração de pulso possa ser emitida baseada sobre o ciclo de serviço PWM correspondente às informações de tensão padrão.

Especificamente, a memória 21 armazena no seu interior um valor de tensão central dentro da faixa apropriada, da tensão de controle do oscilador de tensão controlada 15. Uma vez que o ciclo de serviço PWM correspondente ao valor de tensão central é de 50%, se a tensão de controle do oscilador de tensão controlada 14 varia de 0 a 3,3 V, a tensão de controle central é ajustada para 3,3/2 V. Outrossim, um valor de tensão arbitrário diferente do valor de tensão central pode ser armazenado para que uma tensão de controle seja estabelecida a uma tensão correspondente ao valor de tensão.

20 Quando uma informação de tensão padrão é usada, é possível omitir componentes tais como o circuito de detecção de nível 23 e o conversor A/D 25 e a tensão e tabela de ciclo de serviço PWM na memória 21.

## Correção

Uma descrição de uma operação de correção do presente circuito será apresentada com referência à figura 3. A figura 3 é uma vista mostrando características durante a correção.

No presente circuito, como mostrado na figura 3, quando o tempo transcorre em um estado onde o sinal de referência externo não é introduzido no mesmo, o desvio de frequência se eleva ou declina. No desenho 30 um caso é mostrado onde o desvio de frequência está se apresentando. Por conseguinte, um sinal de referência apropriado é introduzido em uma temporização específica, e quando a introdução do sinal de referência é desconti-

nuada, a correção é efetuada de tal maneira o desvio de frequência retorna à frequência central pelo controle de funcionamento livre. As ditas correções são repetidas duas vezes na figura 3.

Nesta correção, o controle de frequência é realizado pelo utilizar

5 um valor de tensão central dentro de uma faixa suscetível de controlar a tensão de controle do oscilador de tensão controlada 15.

De acordo com o presente circuito, é possível proporcionar a vantagem da operação de correção poder ser efetuada sem conectar um circuito especial durante a correção.

#### 10 Características de Tensão com Envelhecimento: Figura 4

A seguir, um exemplo de características de tensão de controle ideal com o envelhecimento no presente circuito é mostrado na figura 4. A figura 4 é uma vista mostrando características de envelhecimento e de tensão de controle.

15 Como mostrado na figura 4, no presente circuito, a tensão de controle ideal decresce com o transcurso de tempo (todavia, isto corresponde a um caso onde o desvio de frequência está se apresentando).

#### Outra Modalidade 2

Em ainda outra modalidade (outra modalidade 2), o presente

20 circuito é configurado para enfrentar o envelhecimento. Outra modalidade 2 será descrita com referência à figura 5. A figura 5 é uma vista esquemática de uma tabela de características de envelhecimento.

Ainda que a memória 21 armazene no seu interior a tensão e a

25 tabela de ciclo de serviço PWM, o presente circuito utiliza a tabela de características de envelhecimento mostrada na figura 5 em lugar da tensão e ciclo de serviço PWM.

A tabela de características de envelhecimento da figura 5 incorpora um fator de tempo na relação entre as informações de tensão e o ciclo de serviço PWM.

30 Especificamente, uma informação de tensão que é apropriadamente ajustada para um tempo de transcurso dado e um ciclo de serviço PWM correspondente às informações de tensão são armazenados como

uma tabela.

A CPU 20 mede um tempo de transcurso por intermédio de um temporizador previsto na mesma.

Em outra modalidade 2, quando o nível de detecção do sinal de referência externa está fora da faixa adequada, a CPU 20 desliga o comutador 13, reporta-se ao tempo medido pelo temporizador interno para recuperar o ciclo de serviço PWM da informação de tensão correspondente ao tempo, e emite uma informação de geração de pulso correspondente ao ciclo de serviço PWM para o circuito PWM 22. A seguir, o circuito PWM 22 gera pulsos desejados e emite a tensão de controle para o oscilador de tensão controlada 15 através do filtro de malha 14.

Desta maneira, em outra modalidade 2, mediante a ocorrência de uma anormalidade do sinal de referência externo, a CPU 20 corrige a frequência de oscilação usando os pulsos gerados de acordo com as informações de tensão correspondentes ao envelhecimento e o ciclo de serviço PWM correspondente às informações de tensão. Por conseguinte, é possível proporcionar uma vantagem de que o circuito de controle de frequência pode enfrentar o envelhecimento.

Outrossim, na configuração de circuito de outra modalidade 2, uma operação de correção pode ser efetuada.

Neste caso, a CPU 20 mede um tempo transcorrido, e durante a correção, efetuar o controle de frequência pelo usar um valor de tensão correspondente ao tempo transcorrido pelo reportar-se à tabela de características de envelhecimento. Por conseguinte, é possível proporcionar a vantagem da operação de correção poder enfrentar o envelhecimento do circuito de controle de frequência.

#### Aplicabilidade Industrial

A presente invenção é própria para um circuito de controle de frequência de oscilação suscetível de corrigir sua própria frequência e manter uma frequência de oscilação estável mesmo quando um sinal de referência altamente estável não é introduzido no mesmo e opera em um estado de funcionamento livre.

## REIVINDICAÇÕES

1. Circuito de controle de frequência de oscilação caracterizado pelo fato de que compreende:

- um oscilador de tensão controlada;

- 5 um divisor de frequência configurado para dividir uma saída do oscilador de tensão controlada;

- um comparador de fase configurado para comparar fases de um sinal de referência externo e uma saída do divisor de frequência;

- 10 um filtro de malha configurado para nivelar uma saída do comparador de fase e emitir uma tensão de controle para o oscilador de tensão controlada;

- um circuito de detecção suscetível de detectar o sinal de referência externo;

- 15 um circuito de geração de pulsos configurado para gerar pulsos mediante a recepção de uma informação de geração de pulsos a ser emitida para o filtro de malha;

- uma memória suscetível de armazenar no seu interior uma informação de tensão de controle e a informação de geração de pulsos correspondente às informações de tensão de controle em que um valor de tensão de controle emitido pelo oscilador de tensão de controle é usado como a informação de tensão de controle;

- 20 um comutador configurado para ativar/desativar uma conexão entre o comparador de fase e o filtro de malha; e

- uma unidade de controle configurada para ativar o comutador quando um nível do sinal de referência externo detectado pelo circuito de detecção está dentro de uma faixa apropriada enquanto desativando o comutador quando o nível está fora da faixa apropriada para desse modo emitir a informação de geração de pulsos armazenada na memória para o circuito de geração de pulsos;

- 25 30 no qual o circuito de geração de pulsos é um circuito de modulação por duração de pulsos, e a informação de geração de pulsos emitida pela unidade de controle é informação sobre um ciclo de serviço por modu-

lação de duração de pulsos.

2. Circuito de controle de frequência de oscilação de acordo com a reivindicação 1, caracterizado pelo fato da informação de tensão de controle armazenada na memória ser um valor de uma tensão de controle central de uma tensão de controle suscetível de controlar o oscilador de tensão controlada.

3. Circuito de controle de frequência de oscilação de acordo com a reivindicação 1, caracterizado pelo fato da memória armazenar uma tabela de características de envelhecimento, em lugar das informações de tensão de controle e as informações de geração de pulsos correspondente às informações de tensão de controle, a tabela armazenando uma informação de tensão de controle apropriada para um tempo de envelhecimento e uma informação de geração de pulsos correspondente à tensão de controle; e

15 no qual a umidade de controle mede o tempo por intermédio de um temporizador previsto no seu interior, recupera as informações de tensão de controle correspondentes ao tempo medido da tabela de características de envelhecimento da memória quando o nível do sinal de referência externo está fora da faixa apropriada, efetua a leitura emissão das informações de geração de pulsos correspondentes às informações de tensão de controle recuperadas, e emite as informações de geração de pulsos para o circuito de geração de pulsos.

4. Circuito de controle de frequência de oscilação de acordo com a reivindicação 1, caracterizado pelo fato de:

25 um circuito de detecção de nível configurado para detectar um nível de tensão de uma saída do filtro de malha para desse modo emitir uma informação de tensão de controle mais recente para a unidade de controle ser previsto;

30 de a memória armazenar uma tabela de informações de geração de tensão/ pulsos em lugar das informações de tensão de controle e das informações de geração de pulsos correspondentes às informações de tensão de controle, a tabela armazenando as informações de tensão de contro-

le mais recentes, uma pluralidade de informações de tensão de controle, e uma informação de geração de pulsos correspondente às informações de tensão de controle; e

- da unidade de controle atualizar as informações de tensão de controle mais recentes da memória para as informações de tensão de controle mais recentes introduzidas pelo circuito de detecção de nível, efetuar a leitura-emissão das informações de geração de pulsos correspondentes às informações de tensão de controle mais recentes da tabela de informações de geração de tensões/pulsos da memória quando o nível de referência externo está dentro da faixa apropriada, e emitir as informações de geração de pulsos de leitura para o circuito de geração de pulsos.

5. Circuito de controle de frequência de oscilação de acordo com qualquer uma das reivindicações 1 a 4, caracterizado pelo fato de um oscilador a cristal de tensão controlada, um oscilador a cristal de tensão controlada de temperatura compensada, ou um oscilador a cristal forno controlado de tensão controlada ser usado no lugar do oscilador de tensão controlada.

15. Processo de correção usando o circuito de controle de frequência de oscilação como definido na reivindicação 2, o processo caracterizado pelo fato de compreender:

introduzir um sinal de referência externo em uma temporização na qual um desvio de frequência se eleva ou declina em um estado onde o sinal de referência externo não é introduzido;

descontinuar a introdução do sinal de referência externo; e

25 controlar, pela unidade de controle, um funcionamento livre de acordo com o valor da tensão de controle central para desse modo efetuar a correção.

30. Processo de correção utilizando o circuito de controle de frequência de oscilação como definido na reivindicação 3, o processo caracterizado pelo fato de compreender;

introduzir um sinal de referência externo em uma temporização na qual um desvio de frequência se apresenta em um estado onde o sinal de

- referência externo não é introduzido;

descontinuar a introdução do sinal de referência externo; e

reportando-se, pela unidade de controle, à tabela de características de envelhecimento, controlar um funcionamento livre de acordo com o

5 valor da tensão de controle correspondente ao tempo medido para dessa maneira efetuar uma correção.

**FIG.1**

1/7

## FIG.2

| INFO DE TENSÃO | CICLO DE SERVIÇO PWM |

|----------------|----------------------|

| 0              | 0%                   |

| :              | :                    |

| 1.65           | 50%                  |

| :              | :                    |

| 3.5            | 100%                 |

FIG.3

FIG.4

**FIG.5**

| TEMPO | INFO DE TENSÃO | CICLO SERVIÇO PWM (%) |

|-------|----------------|-----------------------|

| $t_1$ | $v_1$          | DutyC <sub>1</sub>    |

| .     | .              | .                     |

| .     | .              | .                     |

| .     | .              | .                     |

| $t_n$ | $v_n$          | DutyC <sub>n</sub>    |

FIG.6

(Técnica Correlata)

7/7

FIG.7

## **RESUMO**

**Patente de Invenção: "CIRCUITO DE CONTROLE DE FREQUÊNCIA DE OSCILAÇÃO".**

A presente invenção refere-se a um circuito de controle de frequência de oscilação, que corrige sua própria frequência para que possa manter uma frequência de oscilação de maneira estável mesmo quando não tiver uma entrada de um sinal de referência altamente estável porem efetue um auto funcionamento. O circuito de controle de frequência de oscilação compreende um oscilador de tensão controlada (15), um divisor de frequência (16), um comparador de fase (12), um filtro de malha (14), um circuito de detecção (17) para detectar um sinal de referência externo, um circuito PWM (22) para gerar pulsos, quando informações geradoras de pulsos são entradas, para emitir os pulsos para o filtro de malha (14), uma memória (21) para armazenar as informações geradoras de pulsos correspondentes às informações de tensão, um comutador (13) para ativar/desativar a conexão entre o comparador de fase (12) e o filtro de malha (14). e uma CPU (20) para ativar o comutador (13) se o nível do sinal de referência externa detectado pelo circuito detector (17) está dentro de uma faixa correta porém desativar o comutador (13), se o nível está fora da faixa correta, para desse modo emitir a informação geradora de pulso armazenada na memória (21), para o circuito PWM (22).