(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5735107号

(P5735107)

(45) 発行日 平成27年6月17日(2015.6.17)

(24) 登録日 平成27年4月24日(2015.4.24)

|                          |                    |

|--------------------------|--------------------|

| (51) Int.Cl.             | F 1                |

| HO 1 L 21/8247 (2006.01) | HO 1 L 27/10 4 3 4 |

| HO 1 L 27/115 (2006.01)  | HO 1 L 29/78 3 7 1 |

| HO 1 L 21/336 (2006.01)  | HO 1 L 27/10 4 4 8 |

| HO 1 L 29/788 (2006.01)  | HO 1 L 45/00 A     |

| HO 1 L 29/792 (2006.01)  | HO 1 L 45/00 Z     |

請求項の数 15 (全 29 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-518511 (P2013-518511)  |

| (86) (22) 出願日 | 平成23年6月24日(2011.6.24)         |

| (65) 公表番号     | 特表2013-533628 (P2013-533628A) |

| (43) 公表日      | 平成25年8月22日(2013.8.22)         |

| (86) 國際出願番号   | PCT/US2011/041888             |

| (87) 國際公開番号   | W02012/009140                 |

| (87) 國際公開日    | 平成24年1月19日(2012.1.19)         |

| 審査請求日         | 平成26年6月23日(2014.6.23)         |

| (31) 優先権主張番号  | 12/825, 211                   |

| (32) 優先日      | 平成22年6月28日(2010.6.28)         |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595168543<br>マイクロン テクノロジー, インク.<br>アメリカ合衆国, アイダホ州 83716<br>-9632, ボイズ, サウス フェデ<br>ラル ウエイ 8000 |

| (74) 代理人  | 100106851<br>弁理士 野村 泰久                                                                        |

| (74) 代理人  | 100074099<br>弁理士 大菅 義之                                                                        |

| (72) 発明者  | タン, サン ディー.<br>アメリカ合衆国, アイダホ州 83709<br>, ボイズ, ウエスト ヴェルデ ドライブ<br>11587                         |

最終頁に続く

(54) 【発明の名称】 3次元メモリおよびその形成方法

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリデバイスの基板と、

前記基板の上方の、前記メモリデバイスの第1のデバイスレベル内に配置された、複数の第1のメモリセルと、

前記第1のデバイスレベルの上方であって且つ前記基板の上方の、前記メモリデバイスの第2のデバイスレベル内に配置された、複数の第2のメモリセルであって、前記第1のデバイスレベルは前記第2のデバイスレベルとは異なる高さ方向レベルにある、前記複数の第2のメモリセルと、

前記第1のメモリセルへのアクセスを制御するための、前記第1のデバイスレベル内に形成された第1の制御ゲートであって、前記第1のメモリセルのそれぞれが、前記第1の制御ゲートの前記基板と水平方向に設けられた空洞内に形成されたメモリ素子を含む、前記第1の制御ゲートと、

前記第2のメモリセルへのアクセスを制御するための、前記第2のデバイスレベル内に形成された第2の制御ゲートであって、前記第2のメモリセルのそれぞれが、前記第2の制御ゲートの前記基板と水平方向に設けられた空洞内に形成されたメモリ素子を含み、前記第1のメモリセルのそれぞれの前記メモリ素子が、誘電体材料によって、前記第2のメモリセルのそれぞれの前記メモリ素子から分離されている、前記第2の制御ゲートと、

導電材料を介して共通ソースおよび前記メモリセルに選択的に結合されるデータ線と、

を含む、装置。

10

20

**【請求項 2】**

前記複数の第1および第2のメモリセルが、第1の方向および第2の方向に配置された複数のメモリセルを含み、

前記導電材料が、前記第1および第2のメモリセルを第3の方向に貫通して延び、前記第3の方向が、前記第1および第2の方向と実質的に垂直である、請求項1に記載の装置。

**【請求項 3】**

前記共通ソースが前記第1および第2のメモリセルと前記メモリデバイスの前記基板との間にるように、前記共通ソースが前記基板の上方に形成されることにより、消去動作中に、前記第1および第2のメモリセルのうちの少なくとも一方のメモリセルの前記メモリ素子からの電子が、前記共通ソースへ移動することが可能になる、請求項2に記載の装置。

10

**【請求項 4】**

メモリデバイスの第1のデバイスレベル内に配置された複数の第1のメモリセルと、

前記メモリデバイスの第2のデバイスレベル内に配置された複数の第2のメモリセルであって、前記第1のデバイスレベルは前記第2のデバイスレベルとは異なる高さ方向レベルにある、前記複数の第2のメモリセルと、

前記第1のメモリセルへのアクセスを制御するための、前記第1のデバイスレベル内に形成された第1の制御ゲートであって、前記第1のメモリセルの各々は前記第1の制御ゲート内の空洞内に形成されたメモリ素子を含み、前記空洞は前記第1の制御ゲートを前記第1のデバイスレベルと水平方向に拡大して設けられる、前記第1の制御ゲートと、

20

前記第2のメモリセルへのアクセスを制御するための、前記第2のデバイスレベル内に形成された第2の制御ゲートであって、前記第2のメモリセルの各々は前記第2の制御ゲート内の空洞内に形成されたメモリ素子を含み、前記空洞は前記第2の制御ゲートを前記第2のデバイスレベルと水平方向に拡大して設けられ、前記第1のメモリセルの各々の前記メモリ素子は、誘電体材料によって、前記第2のメモリセルの各々の前記メモリ素子から分離されており、前記第1および第2のメモリセルは、第1の方向および第2の方向に並んだ複数のメモリセルを含む、前記第2の制御ゲートと、

共通ソースと、

前記共通ソースと前記第1および第2のメモリセルとに導電材料を介して選択的に結合されるように構成されたデータ線と、

30

を備え、

前記導電材料は、前記第1および第2のメモリセルを前記第1および第2の方向とは実質的に垂直な第3の方向に貫通して延び、前記第1および第2のメモリセルが前記共通ソースと前記メモリデバイスの基板との間にのように、前記共通ソースが前記基板の上方に形成されている、装置。

**【請求項 5】**

前記第1のメモリセルが、前記第2のメモリセルと、実質的に垂直方向に位置合わせされている、請求項1に記載の装置。

**【請求項 6】**

前記第1のメモリセルのそれぞれの前記メモリ素子が、前記第2のメモリセルのうちの1つのメモリセルの前記メモリ素子と、実質的に垂直方向に位置合わせされている、請求項1に記載の装置。

40

**【請求項 7】**

前記メモリデバイスのメモリ動作中、前記第1および第2のメモリセルに関連する前記データ線に、前記第1および第2のメモリセルを選択的に結合させるための、トランジスタを更に含み、前記トランジスタの少なくとも1つが、ダブルゲートを含む、請求項1に記載の装置。

**【請求項 8】**

前記メモリデバイスのメモリ動作中、前記第1および第2のメモリセルに関連する前記

50

データ線に、前記第1および第2のメモリセルを選択的に結合させるための、トランジスタを更に含み、前記トランジスタの少なくとも1つが、取り囲まれたゲートを含む、請求項1に記載の装置。

【請求項9】

メモリデバイスの基板と、

前記基板の上方の、前記メモリデバイスの第1のデバイスレベル内に配置された第1の導電材料であって、前記第1の導電材料は前記第1の導電材料を前記基板と水平方向に拡大して設置された第1の空洞を含み、前記第1の空洞は第1の側壁を有する、前記第1の導電材料と、

前記第1のデバイスレベルの上方であって且つ前記基板の上方の、前記メモリデバイスの第2のデバイスレベル内に配置された第2の導電材料であって、前記第2の導電材料は前記第2の導電材料を前記基板と水平方向に拡大して設置された第2の空洞を含み、前記第2の空洞は第2の側壁を有し、前記第1のデバイスレベルと前記第2のデバイスレベルとは異なる高さ方向レベルにある、前記第2の導電材料と、

前記第1の側壁および前記第2の側壁上に形成された、第1の誘電体と、

前記第1の空洞内に配置され、且つ、前記第1の誘電体の第1の部分によって前記第1の導電材料から電気的に絶縁された、第1のメモリ素子と、

前記第2の空洞内に配置され、且つ、前記第1の誘電体の第2の部分によって前記第2の導電材料から電気的に絶縁された、第2のメモリ素子であって、前記第1のメモリ素子が、前記第1の誘電体の誘電体材料によって、前記第2のメモリ素子から分離されている、前記第2のメモリ素子と、

前記第1のメモリ素子の側面上および前記第2のメモリ素子の側面上に形成された、第2の誘電体と、

前記第1のデバイスレベルから前記第2のデバイスレベルへ延び、且つ、前記第2の誘電体の少なくともそれぞれの部分によって、前記第1および第2のメモリ素子から電気的に絶縁されるように、前記第1および第2のメモリ素子に対向する、導電チャネルと、

を含む、装置。

【請求項10】

前記第1および第2のメモリ素子が、ポリシリコンを含む、請求項9に記載の装置。

【請求項11】

前記第1および第2のメモリ素子が、誘電体材料を含む、請求項9に記載の装置。

【請求項12】

前記誘電体材料が、シリコン窒化物を含む、請求項11に記載の装置。

【請求項13】

前記第1の導電材料と前記第2の導電材料との間に、誘電体材料を更に含む、請求項9に記載の装置。

【請求項14】

前記導電チャネルに選択的に結合されるように構成されたデータ線を更に含み、前記第1および第2のメモリ素子が、前記データ線と前記基板との間に配置されている、請求項9に記載の装置。

【請求項15】

メモリデバイスの第1のデバイスレベル内に配置された第1の導電材料であって、前記第1の導電材料は前記第1の導電材料を前記第1のデバイスレベルと水平方向に拡大して設置された第1の空洞を含み、前記第1の空洞は第1の側壁を有する、前記第1の導電材料と、

メモリデバイスの第2のデバイスレベル内に配置された第2の導電材料であって、前記第2の導電材料は前記第2の導電材料を前記第2のデバイスレベルの水平方向に拡大して設置された第2の空洞を含み、前記第2の空洞は第2の側壁を有し、前記第1のデバイスレベルは前記第2のデバイスレベルとは異なる高さ方向レベルにある、前記第2の導電材料と、

10

20

30

40

50

前記第1の側壁上および前記第2の側壁上に形成された第1の誘電体と、

前記第1の空洞内に配置され、且つ、前記第1の誘電体の第1の部分によって前記第1の導電材料から電気的に絶縁されている、第1のメモリ素子と、

前記第2の空洞内に配置され、且つ、前記第1の誘電体の第2の部分によって前記第2の導電材料から電気的に絶縁されている、第2のメモリ素子であって、前記第1のメモリ素子が、前記第1の誘電体の誘電体材料によって、前記第2のメモリ素子から分離されている、前記第2のメモリ素子と、

前記第1のメモリ素子の側面および前記第2のメモリ素子の側面上に形成された第2の誘電体と、

前記第1のデバイスレベルから前記第2のデバイスレベルに延び、且つ、前記第1および第2のメモリ素子に対向し、前記第2の誘電体の少なくともそれぞれの一部分によって前記第1および第2のメモリ素子から電気的に絶縁される、導電チャネルと、

基板と、

前記導電チャネルに選択的に結合されるように構成され、前記第2の導電材料と前記基板との間に配置された、データ線と、

を含む装置。

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の説明

20

本特許出願は、参照により本明細書に組み込まれる、2010年6月28日出願の米国特許出願第12/825,211号の優先権の利益を主張するものである。

【背景技術】

【0002】

フラッシュメモリデバイスなどの不揮発性メモリデバイスは、情報を格納するために、多くのコンピュータおよび電子デバイス内で使用される。フラッシュメモリデバイスは、通常は、情報（例えば、データおよび命令コード）を格納するための書き込み動作、格納された情報を引き出すための読み出し動作、およびメモリから情報を除去するための消去動作を有する。より高密度のメモリデバイスに対する需要が増大すると共に、3次元（3D）メモリデバイスが提案してきた。従来の3Dメモリデバイスの一例は、Jiyoung Kimらによる、表題「Novel 3-D Structure for Ultra High Density Flash Memory with Vertical-Array-Transistor (VRAT) and Planarized Integration on the same Plane (PIPE)」（2008 Symposium on VLSI Technology Digest of Technical Papers、22~23ページ）の論文で説明されている。3Dメモリデバイスは比較的新しいものであるため、これらのデバイスは、製造プロセス上の課題を提起し得る。

30

【図面の簡単な説明】

【0003】

40

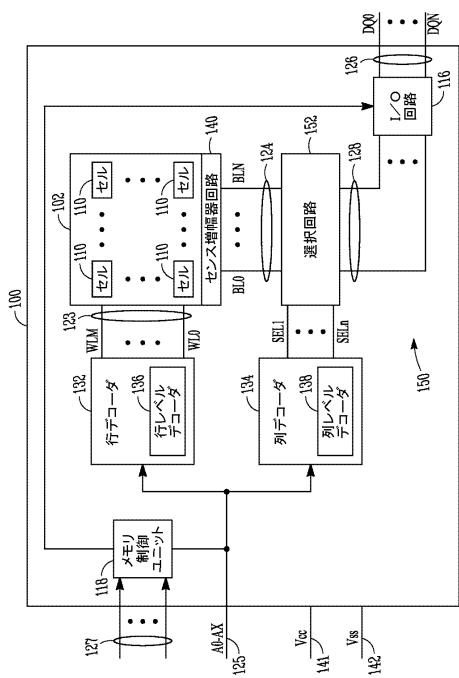

【図1】本発明の一実施形態による、メモリセルを備えるメモリアレイを有するメモリデバイスのブロック図を示す。

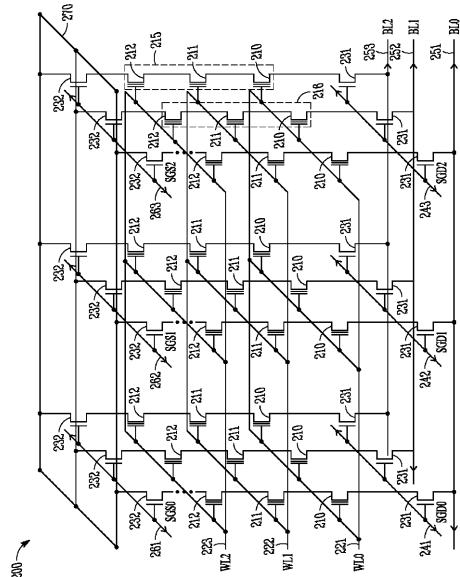

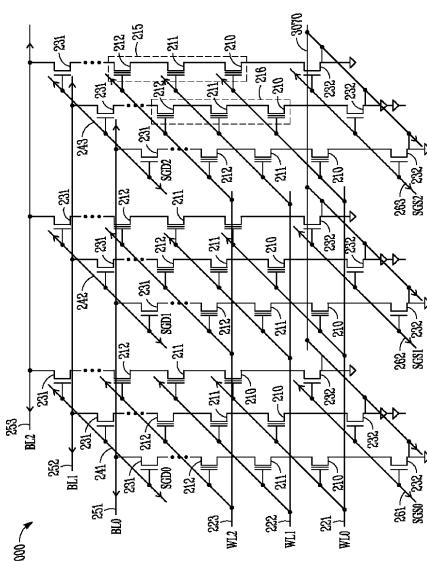

【図2】本発明の一実施形態による、メモリセルの下方にデータ線が配置されるメモリデバイスの一部分の回路図を示す。

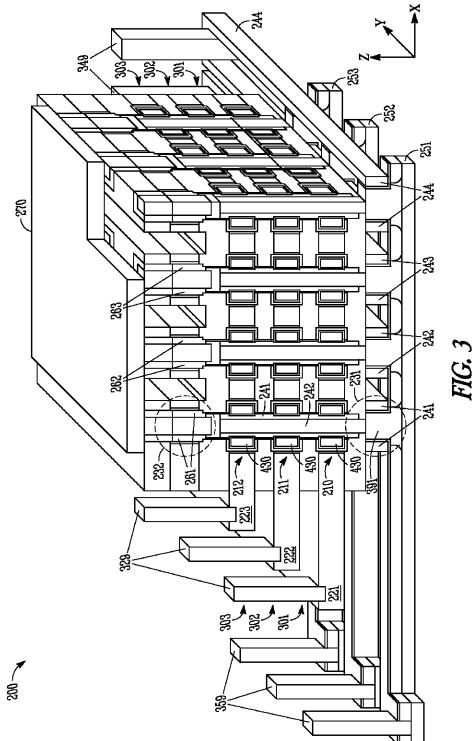

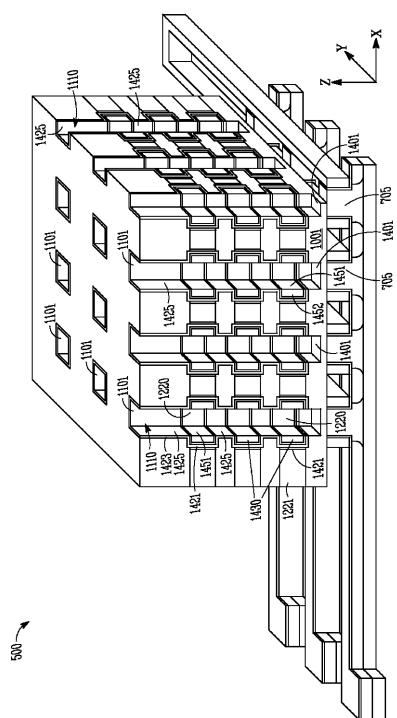

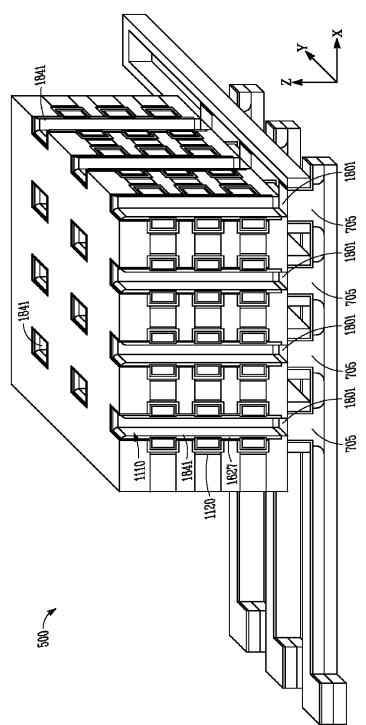

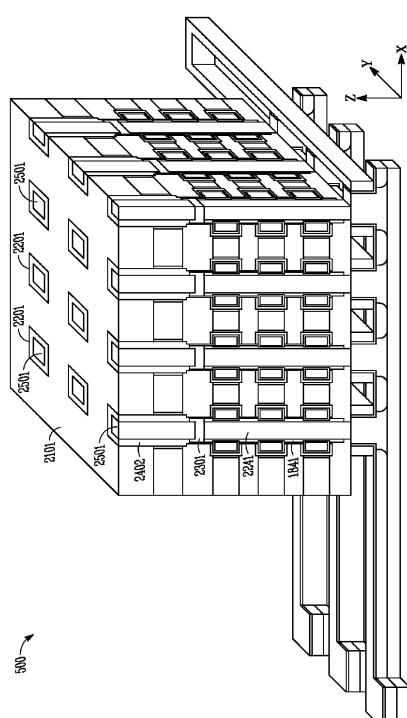

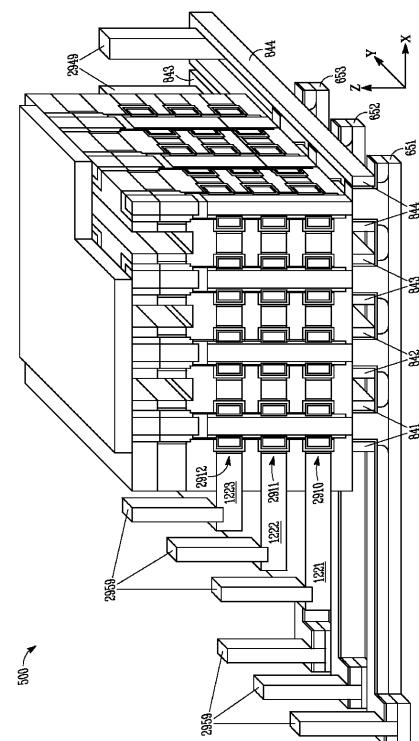

【図3】本発明の一実施形態による、図2のメモリデバイスの一部分の3次元視図を示す。

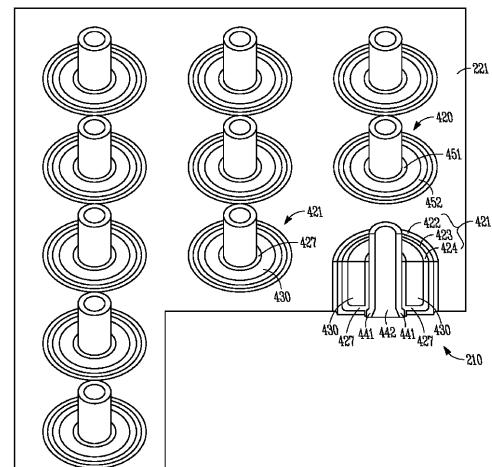

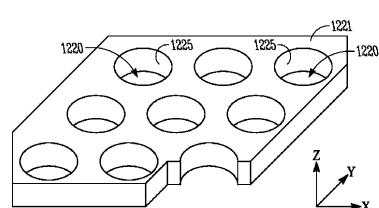

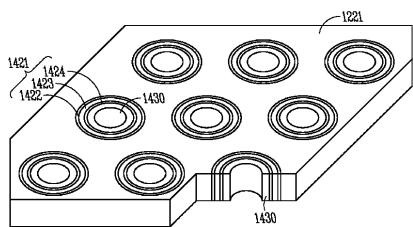

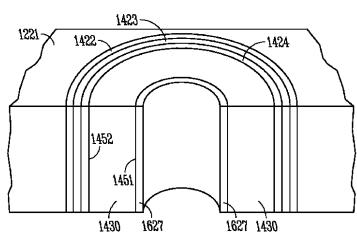

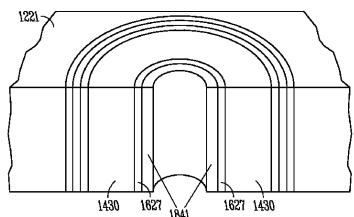

【図4】本発明の一実施形態による、図3のメモリデバイスの制御ゲートおよびメモリセルの一部分を示す。

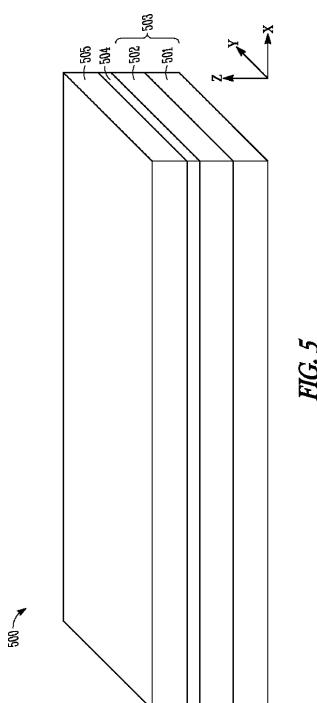

【図5】本発明の一実施形態による、メモリセルの下方にデータ線が配置されるメモリデバイスを形成する、様々なプロセスを示す。

50

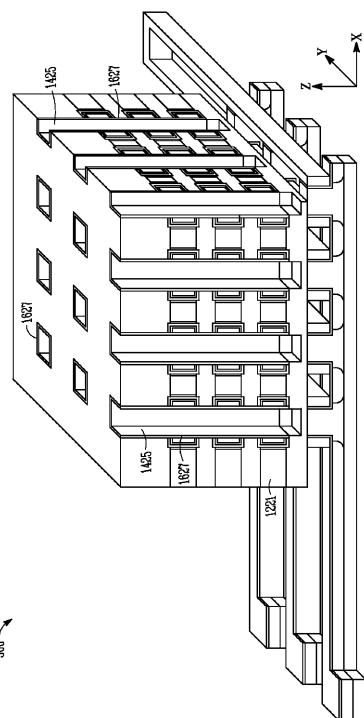

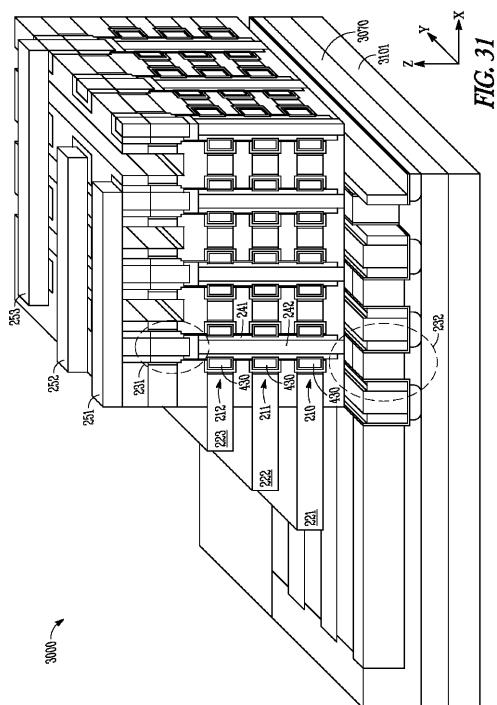

【図31】本発明の一実施形態による、図30のメモリデバイスの一部分の3次元視図を示す。

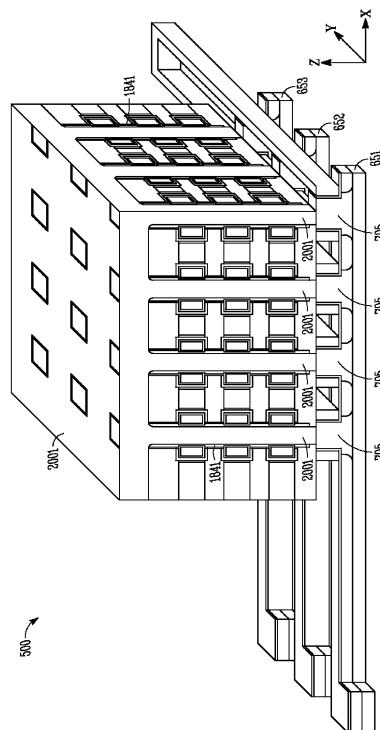

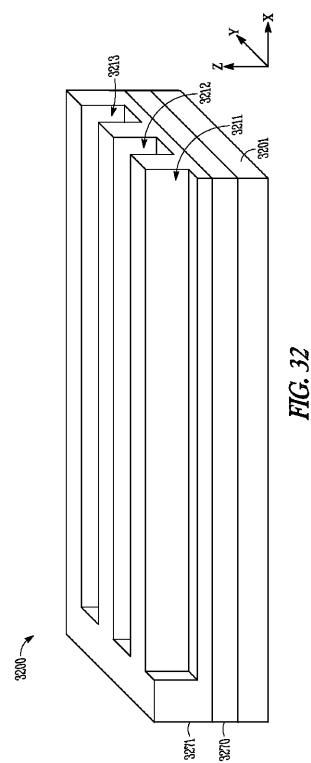

【図32】本発明の一実施形態による、メモリセルの上方にデータ線が配置されるメモリデバイスを形成する、様々なプロセスを示す。

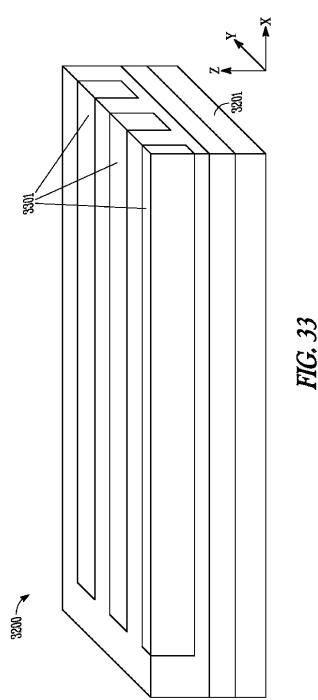

【図33】本発明の一実施形態による、メモリセルの上方にデータ線が配置されるメモリデバイスを形成する、様々なプロセスを示す。

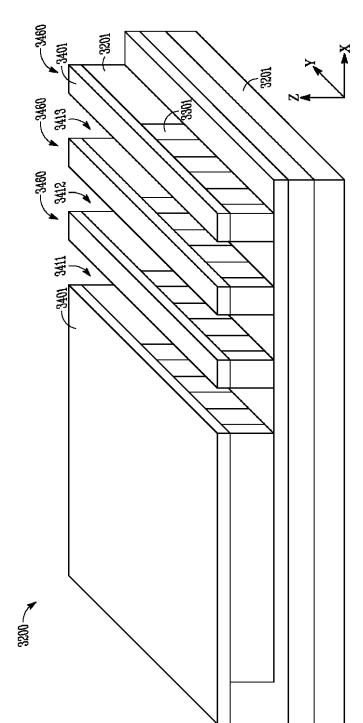

【図34】本発明の一実施形態による、メモリセルの上方にデータ線が配置されるメモリデバイスを形成する、様々なプロセスを示す。

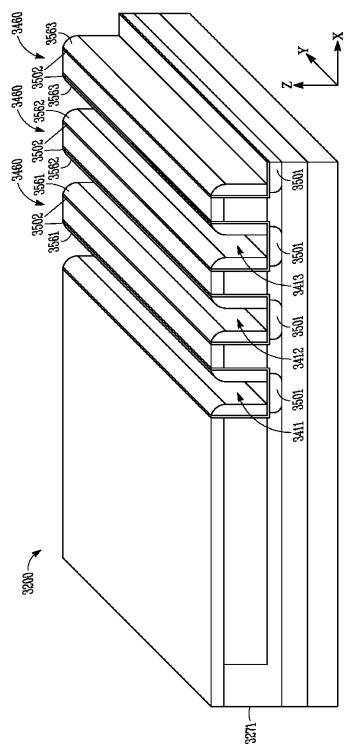

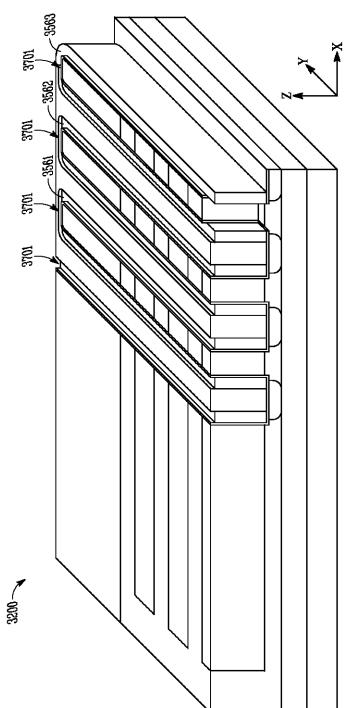

【図35】本発明の一実施形態による、メモリセルの上方にデータ線が配置されるメモリデバイスを形成する、様々なプロセスを示す。 10

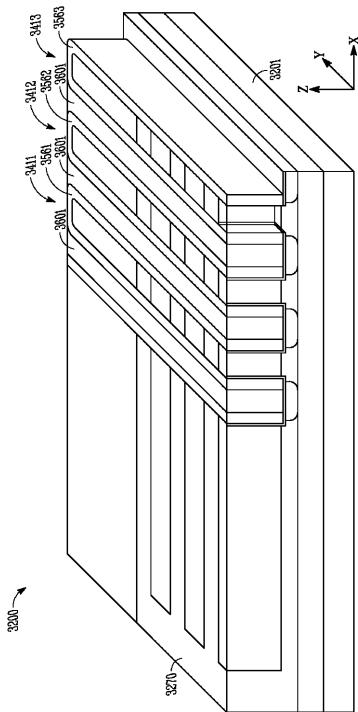

【図36】本発明の一実施形態による、メモリセルの上方にデータ線が配置されるメモリデバイスを形成する、様々なプロセスを示す。

【図37】本発明の一実施形態による、メモリセルの上方にデータ線が配置されるメモリデバイスを形成する、様々なプロセスを示す。

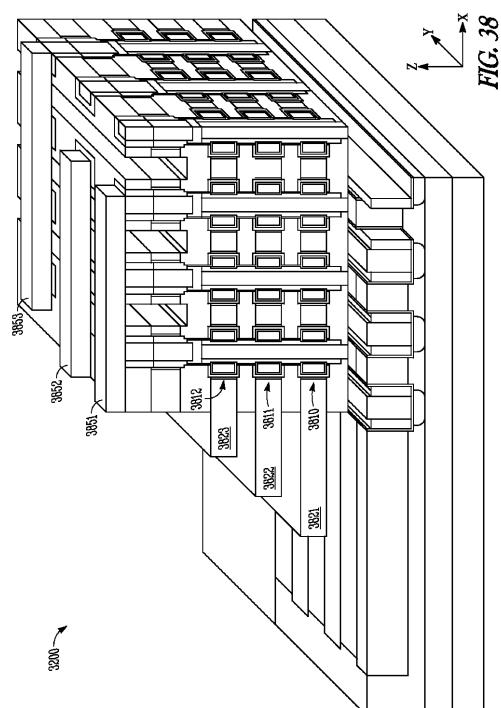

【図38】本発明の一実施形態による、メモリセルの上方にデータ線が配置されるメモリデバイスを形成する、様々なプロセスを示す。

#### 【発明を実施するための形態】

##### 【0004】

図1は、本発明の一実施形態による、メモリセル110を備えるメモリアレイ102を有するメモリデバイス100のブロック図を示す。メモリセル110は、アクセス線123（例えば、信号を有するワード線WL0～WL<sub>M</sub>）および線124（例えば、信号を有するピット線BL0～BL<sub>N</sub>）を伴って、行ならびに列の形で配置構成することができる。メモリデバイス100は、線124および線128を使用して、メモリセル110内部の情報を転送することができる。メモリセル110は、複数のデバイスレベル内に物理的に配置することができ、そのため、メモリセル110の1つのグループを、他のメモリセル110の1つ以上のグループ上に積み重ねることができる。行デコーダ132および列デコーダ134は、線125（例えば、アドレス線）上のアドレス信号A0～AXを復号して、どのメモリセル110にアクセスさせるべきかを決定する。×行及び列デコーダ132及び134の行及び列レベルデコーダ136及び138は各々、アクセスさせるべきメモリセル110が配置された、メモリデバイス100の複数のデバイスレベルのうちのどれかを決定する。 20 30

##### 【0005】

センス增幅器回路140は、メモリセル110から読み出される情報の値を判定して、その情報を、線124および線128に、信号の形態で提供するように動作する。センス增幅器回路140はまた、線124および線128上の信号を使用して、メモリセル110に書き込まれる情報の値を判定することもできる。メモリデバイス100は、メモリアレイ102と線（例えば、データ線）126との間で情報を転送するための、回路機構150を含み得る。線126上の信号DQ0～DQNは、メモリセル110から読み出されるか、またはメモリセル110内に書き込まれる情報を示し得る。線126は、メモリデバイス100内部のノード、またはメモリデバイス100が存在するパッケージ上のノード（例えば、ピンまたはハンダボール）を含み得る。メモリデバイス100の外部の他のデバイス（例えば、メモリコントローラまたはプロセッサ）は、線125、126、および線127を通じて、メモリデバイス100と通信することができる。 40

##### 【0006】

メモリデバイス100は、メモリセル110から情報を読み出すための読み出し動作、およびメモリセル110内に情報を書き込む書き込み動作（プログラミング動作と称される場合もある）などの、メモリ動作を実行する。メモリ制御ユニット118が、線127上の制御信号に基づいて、このメモリ動作を制御する。線127上の制御信号の例としては、1つ以上のクロック信号、およびメモリデバイス100が実行するいずれかの動作（例えば、書き込み動作または読み出し動作）を指示するための他の信号が挙げられる。メ 50

モリデバイス 100 の外部の他のデバイス（例えば、プロセッサまたはメモリコントローラ）は、線 127 上の制御信号の値を制御することができる。これらの線上の信号の組み合わせの、特定の値が、コマンド（例えば、書き込みコマンドまたは読み出しコマンド）を生成して、このコマンドが、メモリデバイス 100 に、対応するメモリ動作（例えば、書き込み動作または読み出し動作）を実行させることができる。

#### 【0007】

メモリセル 110 のそれぞれは、単一ビットの値、または 2 つ、3 つ、4 つ、もしくは他の数のビットなどの複数ビットの値を表す情報を、格納することができる。例えば、メモリセル 110 のそれぞれは、単一ビットのバイナリ値「0」または「1」を表す情報を格納することができる。別の実施例では、メモリセル 110 のそれぞれは、2 ビットの、4 つの可能な値「00」、「01」、「10」、および「11」のうちの 1 つ、8 つの可能な値「000」、「001」、「010」、「011」、「100」、「101」、「110」、および「111」のうちの 1 つ、あるいは他の数の複数ビットの、他の値のうちの 1 つなどの、複数ビットの値を表す情報を、格納することができる。10

#### 【0008】

メモリデバイス 100 は、線 141 上の供給電圧信号 Vcc および線 142 上の供給電圧信号 Vss を含めた、供給電圧を受け取ることができる。供給電圧信号 Vss は、接地電位（例えば、約 0 ボルトの値を有する）で動作することができる。供給電圧信号 Vcc は、バッテリーまたは交直流（AC - DC）変換回路機構などの、外部電源から、メモリデバイス 100 に供給される、外部電圧を含み得る。20

#### 【0009】

メモリデバイス 100 の回路機構 150 は、選択回路 152 および入出力（I/O）回路 116 を含み得る。選択回路 152 は、信号 SEL0 ~ SELn に応答して、メモリセル 110 から読み出されるか、またはメモリセル 110 内に書き込まれる情報を表し得る、線 124 および線 128 上の信号を選択する。列デコーダ 134 が、アドレス信号 A0 ~ AX に基づいて、SEL0 ~ SELn 信号を選択的にアクティブにする。選択回路 152 が、線 124 および線 128 上の信号を選択して、読み出し動作および書き込み動作の間の、メモリアレイ 102 と I/O 回路 116 との通信を提供する。

#### 【0010】

メモリデバイス 100 は、不揮発性メモリデバイスとすることができます、メモリセル 110 は、不揮発性メモリセルとすることができますため、メモリセル 110 は、電力（例えば、Vcc もしくは Vss、または双方）がメモリデバイス 100 から切断される際に、メモリセル 110 上に格納された情報を保持することができる。例えば、メモリデバイス 100 は、NAND フラッシュもしくは NOR フラッシュメモリデバイスなどの、フラッシュメモリデバイス、または可変抵抗メモリデバイスなど（例えば、相変化ランダムアクセスメモリ（PCRAM）、抵抗変化 RAM（RRAM（登録商標））など）の、他の種類のメモリデバイスとすることができます。30

#### 【0011】

メモリデバイス 100 は、本明細書で説明される実施形態に焦点を合わせる手助けとするために、図 1 には示されない他の機構を含み得ることが、当業者には理解されるであろう。40

#### 【0012】

メモリデバイス 100 は、図 2 ~ 図 38 を参照して以下で説明されるメモリデバイスおよびメモリセルのうちの、少なくとも 1 つを含み得る。

#### 【0013】

図 2 は、本発明の一実施形態による、メモリセル 210、211、およびメモリセル 212 の下方に、データ線 251、252、およびデータ線 253 が配置される、メモリデバイス 200 の一部分の回路図を示す。メモリセル 210、211、およびメモリセル 212 は、メモリセル 210 のグループ、メモリセル 211 のグループ、およびメモリセル 212 のグループなどのグループへと、グループ化することができる。図 2 に示すように50

、各グループ内のメモリセルは、制御ゲート 221、222、または制御ゲート 223（関連する信号 WL0、WL1、および信号 WL2 を有する）などの、同じ制御ゲートを共有する。これらのメモリセルは、ストリング 215 およびストリング 216 などのストリング内で直列に結合される。各ストリングは、異なるグループからのメモリセルのうちの 1 つを含み得、トランジスタ 231 のうちの 1 つとトランジスタ 232 のうちの 1 つの間に結合される。

#### 【0014】

図 2 に示すように、トランジスタ 231 は、選択線 241、242、および選択線 243（関連する信号 SGD0、SGD1、および信号 SGD2 を有する）に結合される、ゲートを有する。トランジスタ 231 は、データ線 251、252、およびデータ線 253（関連する信号 BL0、BL1、および信号 BL2 を有する）に結合される、ノード（例えば、ソース）を有する。データ線 251、252、およびデータ線 253 は、不揮発性メモリデバイスのビット線またはセンス線に対応する場合がある。10

#### 【0015】

トランジスタ 232 は、選択線 261、262、および選択線 263（関連する信号 SG S0、SG S1、および信号 SG S2 を有する）に結合される、ゲートを有する。トランジスタ 232 は、不揮発性メモリデバイス内のメモリセルストリングの共通ソース 270 に結合される、ノード（例えば、ドレイン）を有する。

#### 【0016】

図 2 は、関連する構成要素が結合された、メモリセルの 3 つのグループを、一実施例として示す。メモリセルのグループ、およびそれらのグループの関連する構成要素（例えば、制御ゲートおよびデータ線）の数は、変動し得る。20

#### 【0017】

メモリデバイス 200 は、メモリセル 210、211、およびメモリセル 212 内に格納された情報を検知する（例えば、読み出す）ための読み出し動作の間、ならびにメモリセル 210、211、およびメモリセル 212 内に情報を格納するための書き込み動作の間の、メモリセル 210、211、およびメモリセル 212 へのアクセスを制御するために、制御ゲート 221、222、および制御ゲート 223 を使用する。メモリデバイス 200 は、読み出し動作の間にこれらのメモリセルから読み出された情報を転送するために、データ線 251、252、およびデータ線 253 を使用する。30

#### 【0018】

トランジスタ 231 およびトランジスタ 232 は、読み出し動作または書き込み動作の間、それぞれ、信号 SGD0、SGD1、および信号 SGD2、ならびに信号 SG S0、SG S1、および信号 SG S2 に応答して、データ線 251、252、およびデータ線 253、ならびに共通ソース 270 に、メモリセルを選択的に結合する。

#### 【0019】

本明細書での説明に焦点を合わせる手助けとするために、本明細書での説明では、書き込み、読み出し、および消去動作などの、メモリデバイスの動作の詳細な説明は省略される。これらの動作は、当業者には理解されるであろう。例えば、メモリデバイス 200 の消去動作では、約 20 ボルトの電圧を、データ線 251、252、およびデータ線 253 に印加することができ、その一方で、制御ゲート 221、222、および制御ゲート 223、選択線 241、242、および線 243、ならびに選択線 261、262、および選択線 263 を、「浮遊」させる（例えば、電圧に対して非接続のままにする）ことができる。この消去動作で、メモリセル 210、211、およびメモリセル 212 のメモリ素子からの電子は、データ線 251、253、およびデータ線 253 に移動することができる。40

#### 【0020】

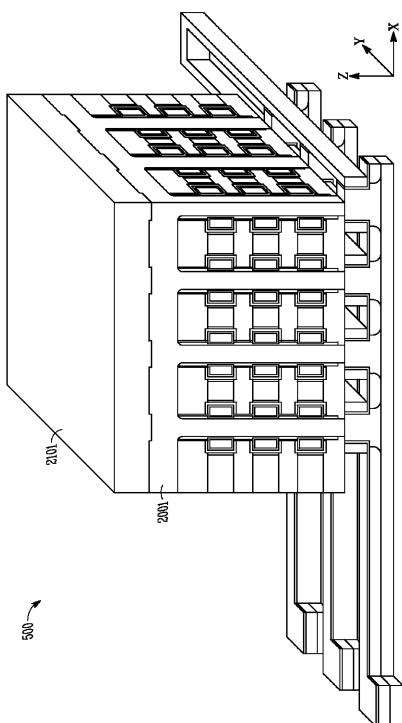

図 3 は、本発明の一実施形態による、メモリデバイス 200 の一部分の 3D 視図を示す。図 3 はまた、X 方向、Y 方向、および Z 方向も示し、デバイスレベル 301、302、およびデバイスレベル 303 が、Z 方向で配置構成される。同じグループのメモリセル 250

10は、X方向およびY方向で、行および列の形に配置構成することができる。メモリセルの各グループは、異なるデバイスレベル301、302、およびデバイスレベル303内に配置される。例えば、メモリセル210を有するグループは、デバイスレベル301内に配置される。メモリセル211を有するグループは、デバイスレベル302内に配置される。メモリセル212を有するグループは、デバイスレベル303内に配置される。

#### 【0021】

図3に示すように、各ストリング内のメモリセル210、211、およびメモリセル212（例えば、トランジスタ231とトランジスタ232との間のメモリセル）は、データ線251、252、およびデータ線253の下の基材（基板）に対して、Z方向に、実質的に垂直に位置合わせされる。この基材は、図3には示されないが、図5および図6の基材503と同様のものとすることができます。図3はまた、図2のトランジスタ231およびトランジスタ232に対応する、トランジスタ231とトランジスタ232との間の、同じストリング内のメモリセル210、211、およびメモリセル212のメモリ素子430を通って、Z方向に垂直に延びる、チャネル241ならびに導電材料部分242も示す。図3に示すように、トランジスタ231は、本体391（例えば、トランジスタチャネル）に結合されるダブルゲートを含み、トランジスタを制御する（オンまたはオフにする）ことができる。このダブルゲートの構造は、同じ選択線241の2つの区画（図3に示すような）を含み得、その2つの区画は、本体391の2つの両側上にのみ配置される。

#### 【0022】

図3のメモリデバイス200はまた、コンタクト329、349、およびコンタクト359も含み得る。コンタクト329は、制御ゲート221、222、および制御ゲート223への電気的接続を提供する。コンタクト349は、選択線241、242、243、および選択線244への電気的接続を提供する。コンタクト359は、データ線251、252、およびデータ線253との間の電気的接続を提供する。選択線244、および選択線244とZ方向で関連するメモリセルは、図2には示されない。

#### 【0023】

図4は、図3のメモリデバイス200の制御ゲート221およびメモリセル210の一部分を示す。図2の制御ゲート222および制御ゲート223、ならびにメモリセル211およびメモリセル212は、それぞれ、制御ゲート221およびメモリセル210と同様の構造を有する。図4に示すように、制御ゲート221は、空洞420を有する均質材料を含み、各空洞は、この均質材料とは異なる材料を含めた、様々な構成要素で充填することができる。その様々な構成要素としては、メモリ素子430、チャネル441、導電材料部分442、ならびに誘電体421および誘電体427が挙げられる。誘電体421は、異なる層として配置構成される、複数の材料422、423、および材料424を含み得る。図4に示すように、各メモリセル210のメモリ素子430は、内側面451および外側面452を有する、リング形状（例えば、ドーナツ形状）を有する。図3に示す他のメモリセル211およびメモリセル212のそれともまた、リング形状を有する。図3に示すように、同じストリング内（例えば、トランジスタ231とトランジスタ232との間）のメモリセル210、211、およびメモリセル212の内部では、各メモリセルのリング形状メモリ素子430の全体が、同じストリング内の他のメモリセルのそれとも、リング形状メモリ素子の全体と、実質的に垂直に（Z方向で）位置合わせされる。

#### 【0024】

各メモリ素子430は、その中の電荷の量（例えば、電子の数）に基づくような、情報を格納することができる。そのような各メモリ素子430では、電荷の量は、そのメモリ素子が格納する情報の値に対応する。この電荷の量は、書き込み動作で、または消去動作で、制御することができる。例えば、チャネル441もしくは導電材料部分442、または双方からの電子は、当業者には既知のトンネル効果により、書き込み動作の間に、メモリ素子430に移動することができる。消去動作では、メモリ素子430からの電子は、

10

20

30

40

50

チャネル 441 もしくは導電材料部分 442、または双方へ戻り、データ線 251、253、およびデータ線 253（図 2 および図 3）に移動することができる。代替的実施形態は、例えば、素子 430 の抵抗に基づくような、情報を格納することができる、メモリ素子 430 を使用することも可能である。

#### 【0025】

図 3 のメモリデバイス 200 は、図 5～図 29 を参照して以下で説明されるものと同様のプロセス、または同一のプロセスを使用して、形成することができる。

#### 【0026】

図 5～図 29 は、本発明の一実施形態による、メモリセルの下方にデータ線が配置されるメモリデバイス 500 を形成する、様々なプロセスを示す。メモリデバイス 500（図 29 に、より詳細に示す）は、図 3 のメモリデバイス 300 に対応し得る。

10

#### 【0027】

図 5 は、基材（基板）503 を有するメモリデバイス 500 を示し、この基材 503 は、層として配置構成される材料 501 および材料 502 を含み得る。材料 501 は、バルクシリコンを含み得、または別の半導体材料とすることも可能である。材料 502 は、誘電材料（誘電体材料）、例えば、シリコン酸化物とすることができます。図 5 はまた、基材 503 の上に形成される、材料 504 および材料 505 も示す。材料 504 および材料 505 の形成は、基材 503 の上に導電材料を付着（堆積）させ、次に材料 504 の上に別の導電材料を付着させる工程を含み得る。材料 504 は、金属、または他の導電材料を含み得る。材料 505 は、非ドープのポリシリコン、もしくは p 型シリコンなどのドープポリシリコン、または別の導電材料を含み得る。

20

#### 【0028】

図 5 はまた、X 方向、X 方向に対して垂直な Y 方向、ならびに X 方向および Y 方向の双方に対して垂直な Z 方向も示す。図 5 に示すように、材料 504 および材料 505 は、1 つの層が、Z 方向で 1 つ以上の他の層の上方に（例えば、層上に）ある、異なる層として形成することができる。

#### 【0029】

本明細書で使用するとき、一方が他方「上に」ある、2 つ以上の材料に関して使用される用語「～上に」とは、それらの材料の間の少なくとも一部の接触を意味し、一方で、「の上方に」または「上有る」は、材料が別の材料「上に」あることか、またはそれらの材料の間に、1 つ以上の追加的な介在材料が存在する場合を指すことができる（例えば、接触は必ずしも必要とされない）。これらの用語「～上に」、「の上方に」、または「上有る」は、本明細書で使用するとき、特にそのような明示的記述がない限り、いずれの方向性も示すものではない。

30

#### 【0030】

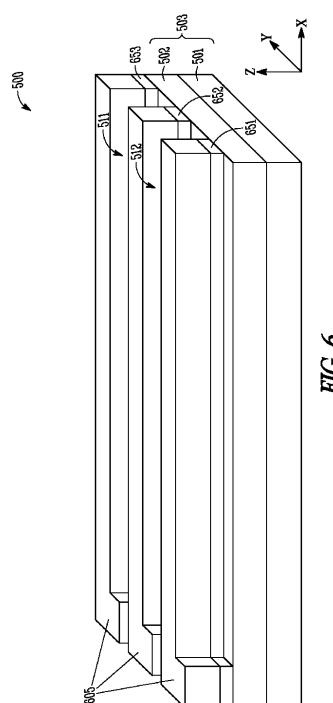

図 6 は、データ線 651、652、およびデータ線 653、ならびにデバイス構造体 605 が形成された後の、メモリデバイス 500 を示す。エッチング（例えば、乾式エッチング）などのプロセスを使用して、材料 504 および材料 505（図 5）の諸部分を除去し、トレーナー 511 およびトレーナー 512 を形成することができ、このトレーナー 511 およびトレーナー 512 は、材料 502 で、トレーナーの底部を有する。データ線 651、652、およびデータ線 653 のそれぞれ、ならびにデバイス構造体 605 のそれぞれは、X 方向に延びる、より大きい寸法（例えば、長さ）を有する。X 方向に延びる個別の開口部を有するマスク（図 6 には示さず）を使用して、トレーナー 511 およびトレーナー 512 を形成することができる。図 6 に示すように、トレーナー 511 およびトレーナー 512 は、材料 504（図 5）を、図 2 のデータ線 251、252、およびデータ線 253 に対応し得る、個別のデータ線 651、652、およびデータ線 653 へと分割する。

40

#### 【0031】

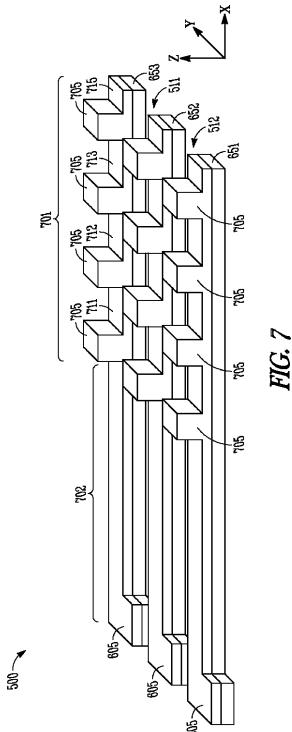

図 7 は、ピラー 705 が、メモリデバイス 500 の区域 701 内に形成された後の、メモリデバイス 500 を示す。ピラー 705 は、メモリデバイス 500 の区域 702 内には形成されない。簡略化のために、図 7～図 29 には、図 6 の基材 503 は示されない。図

50

7では、エッティング(例えば、乾式エッティング)などのプロセスを使用して、デバイス構造体605の諸部分を除去し、トレンチ511およびトレンチ512と垂直なY方向で、トレンチ711、712、およびトレンチ713を形成することができ、それによりピラー705を、図7に示すように形成することができる。Y方向に延びる個別の開口部を有するマスク(図7には示さず)を使用して、トレンチ711、712、およびトレンチ713を形成することができる。各ピラー705は、約20~50ナノメートルの、Z方向での高さを含み得る。図7に示すように、ピラー705は、X方向およびY方向で、行および列の形に(例えば、マトリックスの形に)配置構成される。簡略化のために、図7には、トレンチ511およびトレンチ512内に充填される誘電材料は示されない。しかしながら、図7のメモリデバイス500の形成はまた、デバイス構造体605の頂部表面715まで、トレンチ511およびトレンチ512を充填するように、誘電材料(例えば、シリコン酸化物)を形成する工程も含み得る。

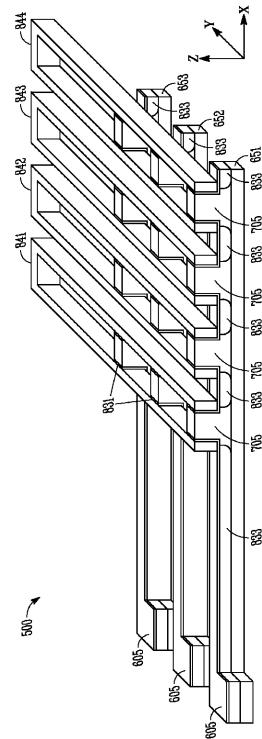

#### 【0032】

図8は、誘電体831、ならびに選択線841、842、843、および選択線844が形成された後、メモリデバイス500を示す。選択線841、842、843、および選択線844は、それぞれ、図3の選択線241、242、243、および選択線244に対応し得る。図8では、誘電体831は、選択線841、842、843、および選択線844を、ピラー705から電気的に絶縁するように形成される。誘電体831は、例えば、各ピラー705の少なくとも2つの面上に、誘電材料(例えば、シリコン酸化物)を付着させることによって、またはピラー705を酸化させることによって、形成することができる。誘電体831が形成された後、例えば、ピラー705、ならびにトレンチ711、712、およびトレンチ713(図7)の上に、導電材料を付着させ、次にその導電材料の一部分を除去(例えば、エッティング)することによって、選択線841、842、843、および選択線844を形成し、図8に示す構造を有する、選択線841、842、843、および選択線844を形成することができる。選択線841、842、843、および選択線844のための導電材料の例としては、ポリシリコン、金属、あるいは、TiNおよびTaNなどの、他の導電材料が挙げられる。

#### 【0033】

図8はまた、デバイス構造体605の選択部分内にn型不純物を挿入する(例えば、注入する)ことによって形成することができる、ドープ領域833も示す。n型不純物の例としては、リン(P)またはヒ素(A s)などの元素が挙げられる。n型不純物が挿入されていない、デバイス構造体605の残余部分は、図5を参照して上記で説明されたような、p型シリコンなどの、その本来の材料を維持し得る。

#### 【0034】

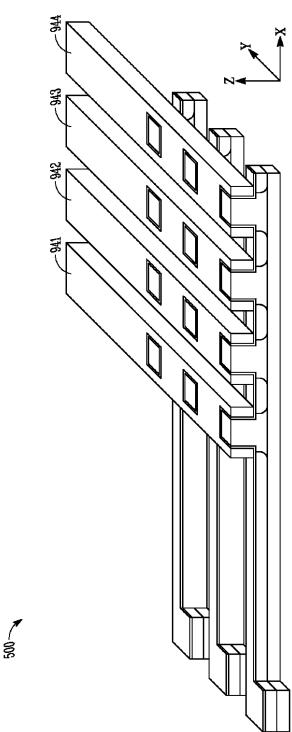

図9は、図8の選択線841、842、843、および選択線844の代替的構造体である、選択線941、942、943、および選択線944を有する、メモリデバイス500を示す。図8では、各ピラー705の相対する側面は、同じ選択線841、842、843、または選択線844の、2つの異なる区画と関連する。図9では、ピラー705の頂部表面を除いて、選択線941、942、943、または選択線944のうちの1つの材料によって、各ピラー705を完全に取り囲むことができる(例えば、各ピラー705の4つの側面が、同じ選択線の4つの異なる区画と関連する)。選択線841、842、843、および選択線844と比較して、より高効率のメモリデバイスを、選択線941、942、943、および選択線944を使用して達成することができる。選択線941、942、943、および選択線944はまた、それぞれ、図3の選択線241、242、243、および選択線244の代替的構造体とすることもできる。それゆえ、図2および図3の各トランジスタ231は、図9に示す構造を有する、取り囲まれたゲート(サラウンドゲート)を含み得る。それゆえ、図3に示すダブルゲートの代わりに、図3の各トランジスタ231は、代替的には、本体391(図3)を取り囲む、同じ選択線(選択線941など)の4つの異なる区画を有する、取り囲まれたゲートを含み得る。

#### 【0035】

10

20

30

40

50

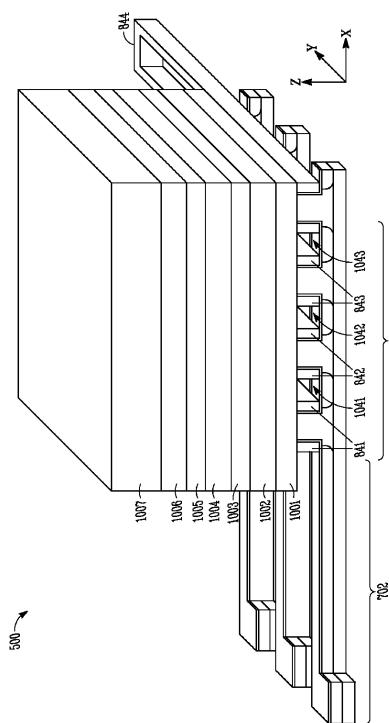

図10は、材料1001～1007が、ピラー705、ならびに選択線841、842、843、および選択線844の上に形成された後の、メモリデバイス500を示す。材料1001～1007は、メモリデバイス500の区域701内および区域702内の双方に形成することができる。しかしながら、本明細書での説明に焦点を合わせるために、図10には、区域702内の、材料1001～1007の一部の部分は示されない。図28および図29を参照する下記の説明で、メモリデバイス500の区域702内の追加的構成要素（例えば、図3のコンタクト329と同様の構成要素）の形成が説明される。

#### 【0036】

図10～図29では、簡略化のために、メモリデバイス500の一部の構成要素に関する一部の番号指定は、1つ1つの図ごとに繰り返さない場合がある。図10では、材料1001～1007を形成する前に、シリコン酸化物などの誘電材料（図10には示さず）を、間隙1041、1042、および間隙1043を充填するように形成することができる。材料1001～1007の形成は、誘電材料と導電材料とを、交互配置方式で交互に付着させる工程を含み得ることにより、これらの材料は、図10に示すように、Z方向で互いの上に交互に積み重ねられる。材料1001、1003、1005、および材料1007は、シリコン酸化物などの誘電材料を含み得る。材料1002、1004、および材料1006は、金属またはポリシリコン（例えば、p型シリコンに対するn型シリコン）などの導電材料を含み得る。図10に示すように、材料1001～1007は、材料1002、1004、および材料1006が、材料1001、1003、1005、および材料1007によって互いに電気的に絶縁されるように、形成される。

#### 【0037】

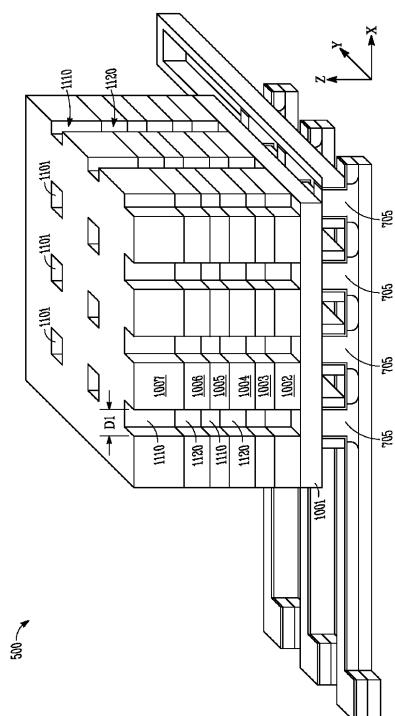

図11は、開口部（例えば、穴）1101が、材料1002～1107内に形成された後の、メモリデバイス500を示す。穴1101は、図11に示すように、各穴1101を、対応するピラー705の実質的に直接上に、位置合わせすることができるよう形成される。穴1101の形成は、材料1002～1007のそれぞれの一部分を除去（例えば、エッティング）して、材料1001で停止させる工程を含み得ることにより、材料1001の少なくとも一部分、または材料1001の全体が、穴1101をピラー705から隔てるよう残存する。穴1101の形成は、材料1003、1005、および材料1007内のそれぞれの空洞1110、ならびに材料1002、1004、および材料1006内のそれぞれの空洞1120の形成をもたらす。図11に示すように、材料1003、1005、および材料1007内の空洞1110は、他の材料1002、1004、および材料1006内の空洞1120の実質的に直接上に、位置合わせされる。各空洞1110および各空洞1120は、実質的に同じ直径D1を有し得る。直径D1はまた、各空洞1110および各空洞1120の場所での、各穴1101の直径と見なすことができる。

#### 【0038】

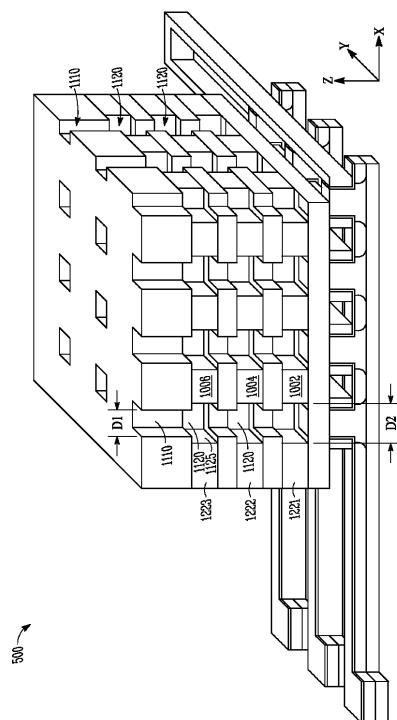

図12は、空洞1220が、材料1002、1004、および材料1006（制御ゲート1221、1222、および制御ゲート1223を形成するために使用される）内に形成された後の、メモリデバイス500を示す。空洞1220の形成は、空洞1120（図11）のサイズを拡大し、その一方で、空洞1110のサイズを実質的に変化させずに保つ（例えば、実質的に直径D1で維持する）工程を含み得る。例えば、空洞1120（図11）のサイズの拡大は、各空洞1120（図11）で、材料1002、1004、および材料1006のそれぞれの一部分を選択的に除去（例えば、選択的な、湿式または乾式エッティング）する工程を含み得ることにより、各空洞1220の直径が、実質的に直径D2へと増大し、その一方で、各空洞1110での直径D1は、実質的に変化せずに維持される。直径D2は、直径D1よりも大きい。材料1002、1004、および材料1006内の空洞1120の形成はまた、図2の制御ゲート221、222、および制御ゲート223に対応し得る、制御ゲート1221、1222、および制御ゲート1223も形成する。

#### 【0039】

図13は、図12の制御ゲート1221の、更なる詳細を示す。図12の制御ゲート1

10

20

30

40

50

222および制御ゲート1223は、制御ゲート1221と同様の構造を有する。図13に示すように、制御ゲート1221は、図11の空洞1220が、X方向およびY方向で、行および列の形に配置構成される、均質材料を含み得る。各空洞1220は、側壁1225を含み得る。

#### 【0040】

図14および図15は、誘電体1421およびメモリ素子1430が、空洞1220内に形成された後の、メモリデバイス500を示す。簡略化のために、図15には、全ての空洞1220内の、誘電体1421およびメモリ素子1430は示されない。各誘電体1421は、制御ゲート1221の材料とメモリ素子1430との間に各誘電体1421を配置することができるよう、側壁1225上に形成することができ、それにより、メモリ素子1430を、誘電体1421の少なくとも一部分によって、制御ゲート1221の材料から電気的に絶縁することができる。誘電体1421の形成は、複数の材料1422、1423、および材料1424(図15)を、異なる時点で、次々と形成する工程を含み得る。材料1422の形成は、側壁1225の一部分(例えば、表面)を酸化させて、側壁1225上に誘電材料(例えば、シリコン酸化物)を形成する工程を含み得る。あるいは、材料1422の形成は、側壁1225上に誘電材料(例えば、シリコン酸化物)を付着させる工程を含み得る。材料1423の形成は、材料1422上に誘電材料(例えば、シリコン窒化物)を付着させる工程を含み得、その誘電材料の一部分はまた、各空洞1110の側壁1425上にも形成される。材料1424の形成は、材料1423上に誘電材料(例えば、シリコン酸化物)を付着させる工程を含み得る。

10

20

#### 【0041】

メモリ素子1430は、誘電体1421が形成された後に、形成することができる。図15に示すように、各メモリ素子1430は、図14の内側面1451および外側面1452を有する、リング形状(例えば、ドーナツ形状)を有する。メモリ素子1430の形成は、穴1101内に材料を付着させる工程を含み得る。図14の空洞1220は、空洞1110と実質的に位置合わせされているため、この材料(メモリ素子1430を形成する)は、空洞1110および空洞1120の双方に充填することができる。次に、メモリ素子1430を形成する材料の一部分(例えば、各穴の中心部分)を除去する(例えば、同じ单一のエッティング工程での、エッティングによって)ことができ、それにより、空洞1110内の材料を除去(例えば、完全に除去)することができ、空洞1220内の材料は、完全に除去されることなく、部分的に除去される。図14に示すように、メモリ素子1430を形成する材料が、空洞1110から除去された後、誘電材料1423(例えば、材料1422上に形成された、シリコン窒化物)の一部分を、露出させることができる。図14に示すように、メモリ素子1430を形成する材料が、空洞1220から部分的に除去された後、同じ穴1101に関連するメモリ素子1430(空洞1220内の残留材料によって形成される)は、空洞1110の側壁1425(または、空洞1110の、材料1422および材料1423の諸部分を有する側壁1425)と実質的に位置合わせされる、その内側面1451を有し得る。

30

#### 【0042】

メモリ素子1430の材料としては、例えば、半導体材料(例えば、ポリシリコン)、シリコン窒化物もしくは他の誘電電荷トラッピング材料などの誘電電荷トラッピング材料、または相変化材料(例えば、GST)などの可変抵抗材料を挙げることができる。メモリ素子1430を形成する材料の一部分を除去(例えば、エッティング)する間、ピラー705の上に配置された、材料1001の部分1401もまた除去して、部分1401の厚さを低減することができる。

40

#### 【0043】

図16および図17は、誘電体1627が、メモリ素子1430の内側面1451上、および空洞1110内に形成された後の、メモリデバイス500を示す。誘電体1627の形成は、内側面1451上に誘電材料(例えば、シリコン酸化物)を付着させる工程を含み得る。あるいは、誘電体1627の形成は、メモリ素子1430の一部分(例えば、

50

内側面 1451) を酸化させる工程を含み得る。誘電体 1627 の形成(例えば、酸化による)はまた、空洞 1110 の側壁 1425 上に形成された材料 1422 上に形成される、材料 1423(図 14)もまた、消耗させることができる。それゆえ、誘電体 1627 はまた、材料 1422 の上で、空洞内に形成することもできる。

#### 【0044】

図 18 および図 19 は、チャネル 1841 が、空洞 1110 内および空洞 1220 内の双方の、誘電体 1627 上に形成された後の、メモリデバイス 500 を示す。チャネル 1841 の形成は、誘電体 1627 上に導電材料を付着させる工程を含み得る。エッティングプロセスを使用して、その付着の後に、導電材料の厚さを低減することができる。チャネル 1841 の導電材料は、ピラー 705 と同じ材料のタイプ(例えば、p 型)を有し得る、ドープポリシリコンを含み得る。図 18 はまた、開口部 1801 の形成も示し、この開口部 1801 は、ピラー 705 の上に配置された部分 1401(図 14)を除去することによって、(例えば、エッティングによって)形成することができる。図 19 に示すように、チャネル 1841 は、メモリ素子 1430 と対向しており、誘電体 1627 の少なくとも一部分によって、メモリ素子 1430 から電気的に絶縁される。

#### 【0045】

図 20 は、例えば非ドープまたは低ドープのポリシリコンを付着させることによって、導電材料 2001 が形成され、チャネル 1841 とピラー 705 とが電気的に連通された後の、メモリデバイス 500 を示す。図 20 に示すように、導電材料 2001 は、ピラー 705 を通じて、チャネル 1841 とデータ線 651、652、およびデータ線 653 との間に、連続的な導電経路を形成する。

#### 【0046】

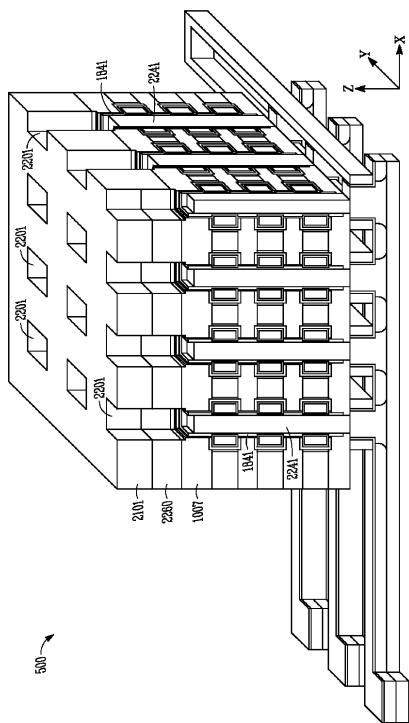

図 21 は、誘電材料 2101(例えば、シリコン酸化物)が、導電材料 2001 の上に形成された後の、メモリデバイス 500 を示す。

#### 【0047】

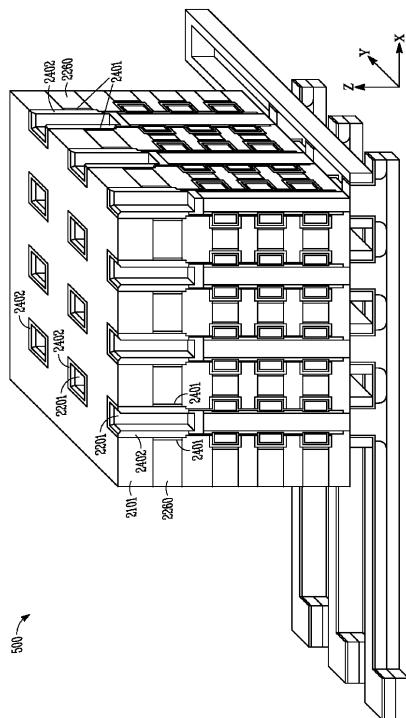

図 22 は、開口部(例えば、穴 2201)、導電材料部分 2260、および導電材料部分 2241 の形成後の、メモリデバイス 500 を示す。穴 2201 は、図 22 に示すように、各穴 2201 を、チャネル 1841 の実質的に直接上に、位置合わせすることができるよう形成される。穴 2201 の形成は、誘電材料 2101 の一部分、および導電材料 2001(図 21)の一部分を除去(例えば、エッティング)して、材料 1007 内の場所で停止させる工程を含み得る。穴 2201 が形成されることにより、導電材料 2001 の一部分が、穴 2201 の形成の間に除去された後、導電材料 2001 は、図 22 に示すように、導電材料部分 2260 と導電材料部分 2241 とに分離することができる。

#### 【0048】

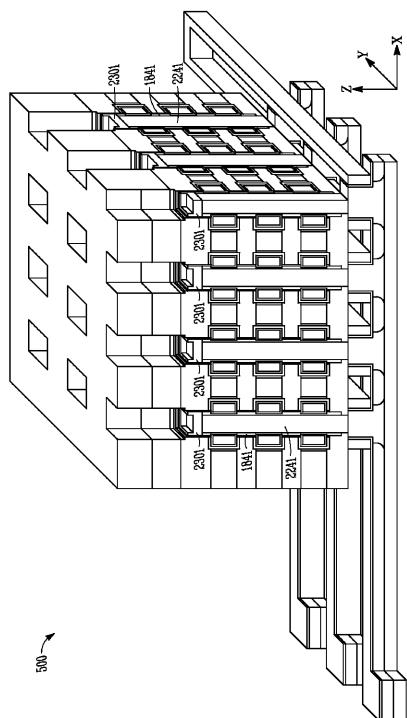

図 23 は、ドープ領域 2301 が形成された後の、メモリデバイス 500 を示す。ドープ領域 2301 の形成は、導電材料部分 2241 の頂部部分内に、n 型不純物を挿入する(例えば、注入する)工程を含み得る。ドープ領域 2301 は、チャネル 1841 とメモリデバイス 500 の他の構成要素との間に、比較的低い抵抗の接続を提供することができる。

#### 【0049】

図 24 は、誘電体 2401 およびチャネル 2402 が形成された後の、メモリデバイス 500 を示す。誘電体 2401(例えば、シリコン酸化物)は、穴 2201 の場所で、導電材料部分 2260 の側壁上に形成される。チャネル 2402 は、誘電材料 2101 の側壁上、および誘電体 2401 上に形成される。

#### 【0050】

図 25 は、導電材料 2501 が、各穴 2201 内に形成された後の、メモリデバイス 500 を示し、このことにより、チャネル 2402 は、導電材料 2501、ドープ領域 2301、および導電材料部分 2241 を通じて、チャネル 1841 と電気的に結合することができる。各穴 2201 内の導電材料 2501 の形成は、材料の上に導電材料(例えば、ポリシリコン)を付着させることにより、その導電材料が穴 2201 を充填する工程を含

み得る。次に、例えば導電材料をエッチ(etching)バックすることによって、または化学機械研磨(CMP)によって、その導電材料の頂部部分を除去することができる。

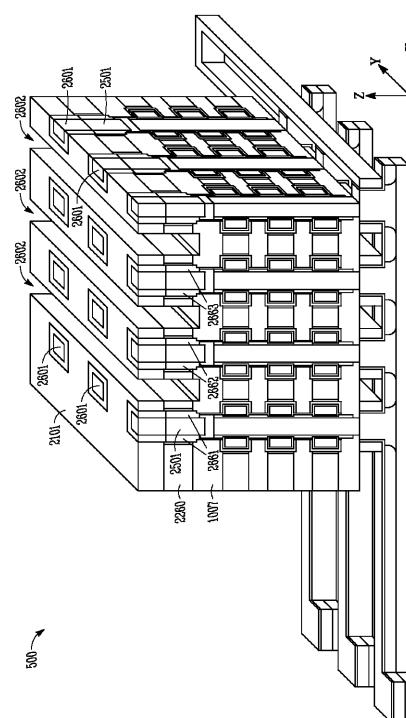

#### 【0051】

図26は、ドープ領域2601、ならびに選択線2661、2662、および選択線2663が形成された後の、メモリデバイス500を示す。ドープ領域2601の形成は、導電材料部分2501の頂部部分内に、n型不純物を挿入する(例えば注入する)工程を含み得る。選択線2661、2662、および選択線2663の形成は、誘電材料2101および導電材料部分2260の諸部分を除去して、トレンチ2602を形成する工程を含み得、このトレンチ2602は、材料1007内に部分的に延びる、トレンチの底部を有する。図26に示すように、トレンチ2602は、導電材料部分2260を、図2の選択線261、262、および選択線263に対応し得る、選択線2661、2662、および選択線2663へと分離する。

10

#### 【0052】

図27は、材料2701および共通ソース2770が形成された後の、メモリデバイス500を示す。材料2701の形成は、材料2101の上に誘電材料(例えば、シリコン酸化物)を付着させることにより、その誘電材料がトレンチ2602を充填する工程を含み得る。次に、例えば誘電材料をエッチバックすることによって、またはCMPによって、その誘電材料の頂部部分を除去することができる。共通ソース2770の形成は、材料2701および材料2101の上に導電材料(例えば、金属)を付着させる工程を含み得る。

20

#### 【0053】

図28は、区域702(図10)内の材料1001～1007が、階段状パターンを形成するように処理(例えば、パターニングによって)された後の、メモリデバイス500を示し、階段の間の材料は、図28には示されない。図10の説明で上述されたように、材料1001～1007の一部の部分は、簡略化のために、図10～図27の区域702からは省略されている。図28は、階段状パターンを形成するように処理された後の、区域702内の材料1001～1007を示す。図28に示すように、制御ゲート1221、1222、および制御ゲート1223が、それぞれ、階段状パターンに形成される材料1002、1004、および材料1006から形成される。

30

#### 【0054】

図29は、コンタクト2929、2949、およびコンタクト2959が形成された後の、メモリデバイス500を示す。コンタクト2929は、制御ゲート1221、1222、および制御ゲート1223への電気的接続を提供する。コンタクト2949は、選択線841、842、843、および選択線844への電気的接続を提供する。コンタクト2959は、データ線651、652、およびデータ線653との間の電気的接続を提供する。

#### 【0055】

図29に示すように、メモリデバイス500は、図2および図3を参照して上記で説明された、メモリデバイス300の構成要素ならびにメモリセル210、211、およびメモリセル212と同様、もしくは同一の、構成要素ならびにメモリセル2910、2911、およびメモリセル2912を含み得る。

40

#### 【0056】

追加的なプロセスを実行して、上述のメモリデバイス500などのメモリデバイスの、追加的な機構を形成することができる点が、当業者には容易に理解されるであろう。それゆえ、本明細書で説明される実施形態に焦点を合わせる手助けとするために、上述の図5～図29、および以下で説明される図30～図38には、メモリデバイス500などのメモリデバイスの、機構の一部のみが示される。

#### 【0057】

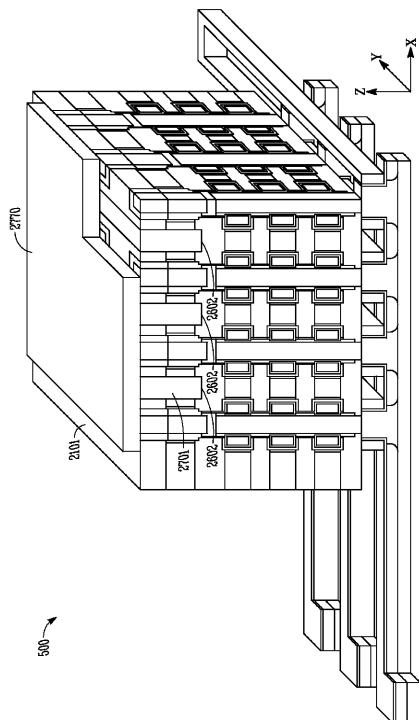

図30は、本発明の一実施形態による、メモリセル210、211、およびメモリセル212の上方に、データ線251、252、およびデータ線253が配置される、メモリ

50

デバイス 300 の一部分の回路図を示す。メモリデバイス 300 は、図 3 のメモリデバイス 200 のものと同様の構成要素を含み得る。それゆえ、簡略化のために、メモリデバイス 200 とメモリデバイス 300 との間で同様の構成要素、または同じ構成要素には、同じ番号指定が与えられる。これらの同様の構成要素の詳細な説明は、図 30 では繰り返されない。メモリデバイス 300 とメモリデバイス 200 との主要な相違としては、大域消去動作を可能にするための、メモリデバイス 300 の、データ線 251、252、およびデータ線 253、ならびに共通ソース 3070 の場所が挙げられる。図 30 に示すように、データ線 251、252、およびデータ線 253 は、メモリセル 210、211、およびメモリセル 212 の上方に配置される。共通ソース 3070 は、メモリセル 210、211、およびメモリセル 212 の下方に配置され、メモリデバイス 300 の基材 (例えは、図 31 の基材 3101) の少なくとも一部分に、直接結合することができる。この主要な相違により、メモリデバイス 200 の消去動作 (例えは、局所消去動作) と比較して、消去動作の間、メモリデバイス 300 の様々な構成要素に、異なる方法で電圧を印加することが可能になり、メモリデバイス 300 は、異なる方式で機能する (例えは、大域消去動作の間) ことが可能になる。例えは、メモリデバイス 300 の消去動作では、約 20 ボルトの電圧を、共通ソース 3070 に印加することができ、その一方で、制御ゲート 221、222、および制御ゲート 223、データ線 251、252、およびデータ線 253、選択線 241、242、および線 243、ならびに選択線 261、262、および選択線 26 を「浮遊」させることができる。この消去動作では、メモリセル 210、211、およびメモリセル 212 のメモリ素子からの電子は、共通ソース 3070 に移動する (例えは、トンネル現象によって) ことができる (例えは、大域消去)。メモリ 200 では、図 2、図 3、および図 4 を参照して上記で説明されたように、消去動作の間、メモリセル 210、211、およびメモリセル 212 のメモリ素子からの電子は、データ線 251、253、およびデータ線 253 へと移動することができる (例えは、局所消去)。

図 31 は、本発明の一実施形態による、図 30 のメモリデバイス 300 の一部分の 3D 視図を示す。図 31 に示すように、データ線 251、252、およびデータ線 253 は、メモリセル 210、211、およびメモリセル 212 の上方に配置され、共通ソース 3070 は、メモリセル 210、211、およびメモリセル 212 の下方に配置されて、基材 3101 に結合される。基材 3101 は、p 型シリコンなどの、半導体材料を含み得る。

#### 【0058】

図 31 に示すように、各ストリング内のメモリセル 210、211、およびメモリセル 212 (例えは、トランジスタ 231 とトランジスタ 232 との間のメモリセル) は、基材 3101 に対して、Z 方向で実質的に垂直に位置合わせされる。トランジスタ 232 は、図 3 のトランジスタ 231 の、ダブルゲート (図 3) または取り囲まれたゲート (図 9) と同様の、ダブルゲートまたは取り囲まれたゲートを含み得る。図 31 はまた、Z 方向で垂直に延び、図 30 のトランジスタ 231 およびトランジスタ 232 に対応する、トランジスタ 231 とトランジスタ 232 との間の、同じストリング内のメモリセル 210、211、およびメモリセル 212 の、メモリ素子 430 を貫通する、チャネル 441 ならびに導電材料部分 442 も示す。

#### 【0059】

各メモリセル 210、211、およびメモリセル 212 内の、メモリ素子 430 は、リング形状を有する。図 31 に示すように、同じストリング内のメモリセル 210、211、およびメモリセル 212 の内部では、各メモリセルのリング形状メモリ素子 430 の全体が、同じストリング内の他のメモリセルのそれぞれの、リング形状メモリ素子の全体と、実質的に垂直に (Z 方向で) 位置合わせされる。

#### 【0060】

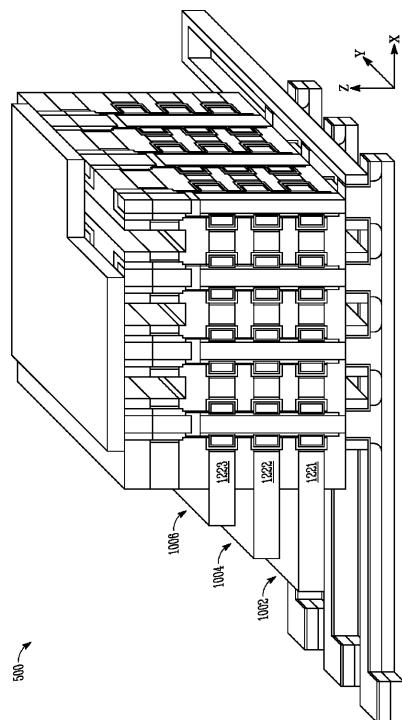

図 32 ~ 図 38 は、本発明の一実施形態による、メモリセルの上方にデータ線が配置されるメモリデバイス 3200 を形成する、様々なプロセスを示す。メモリデバイス 320

10

20

30

40

50

0(図38に、より詳細に示す)は、図31のメモリデバイス3000に対応し得る。

#### 【0061】

図32は、基材3201、ならびにトレンチ3211、3212、およびトレンチ3213を有する、メモリデバイス3200を示し、基材部分3270および基材部分3271が、基材3201の頂部部分上に形成される。基材3201は、バルクシリコンなどの、半導体材料を含み得る。頂部の基材部分3270および基材部分3271は、基材3201の頂部部分内にp型不純物を挿入する(例えば、注入する)ことによって形成することができる。それゆえ、基材部分3270および基材部分3271は、p型シリコンを含み得る。トレンチ3211、3212、およびトレンチ3213、ならびに基材部分3270の形成は、基材部分3271の一部分を除去(例えば、エッティング)する工程を含み得る。メモリデバイス3200の書き込み動作または読み出し動作の間、基材部分3270は、接地などの電位に結合することができる。メモリデバイス3200の消去動作の間、基材部分3270は、例えば約20ボルトの電圧に結合することができる。10

#### 【0062】

図33は、材料3301が、トレンチ3211、3212、およびトレンチ3213(図32)内に形成された後の、メモリデバイス3200を示す。材料3301の形成は、基材3201の上に誘電材料(例えば、シリコン酸化物)を付着させ、トレンチ3211、3212、およびトレンチ3213を充填する工程を含み得る。次に、その誘電材料の頂部部分を、例えばCMPによって、除去することができる。20

#### 【0063】

図34は、材料3401、ならびにトレンチ3411、3412、およびトレンチ3413、ならびにデバイス構造体3460が形成された後の、メモリデバイス3200を示す。材料3401の形成は、基材3201および材料3301の上に誘電材料(例えば、シリコン酸化物またはシリコン窒化物)を付着させる工程を含み得る。トレンチ3411、3412、およびトレンチ3413の形成は、基材3201、材料3301、および材料3401の諸部分を除去(例えば、エッティング)する工程を含み得る。デバイス構造体3460は、トレンチ3411、3412、およびトレンチ3413の形成の結果として形成される。30

#### 【0064】

図35は、ドープ領域3501、材料3502、ならびに選択線3561、3562、および選択線3563の形成後の、メモリデバイス3200を示す。ドープ領域3501の形成は、基材部分3271の選択部分内にn型不純物を挿入する(例えば、注入する)工程を含み得る。材料3502(例えば、シリコン酸化物)を、各デバイス構造体3460の両側面上に形成して、選択線3561、3562、および選択線3563を、デバイス構造体3460から電気的に絶縁することができる。選択線3561、3562、および選択線3563の材料としては、1種以上の金属、合金、他の導電材料、またはそれらの組み合わせなどの、1種以上の導電材料を挙げることができる。選択線3561、3562、および選択線3563は、図30のメモリデバイス3000の、選択線261、262、および選択線263に対応し得る。40

#### 【0065】

図36は、材料3601が、トレンチ3411、3412、およびトレンチ3413内に形成された後の、メモリデバイス3200を示す。材料3601の形成は、誘電材料(例えば、シリコン酸化物)を付着させ、トレンチ3411、3412、およびトレンチ3413を充填する工程を含み得る。次に、例えば導電材料をエッチバックすることによって、またはCMPによって、その誘電材料の頂部部分を除去し、基材部分3270で停止させることができる。50

#### 【0066】

図37は、選択線3561、3562、および選択線3563を形成するために使用される材料の頂部部分を除去することによって(例えば、湿式エッティングによって)、溝3701が形成された後の、メモリデバイス3200を示す。あるいは、溝3701の形成

は、省略することができる。

#### 【0067】

図38は、他の構成要素が形成された後の、メモリデバイス3200を示す。図38のメモリデバイス3200の構成要素を形成するためのプロセスは、図10～図29を参照して上記で説明された、メモリデバイス500の構成要素を形成するための、同様のプロセス、または同一のプロセスを含み得る。例えば、図38の制御ゲート3821、3822、および制御ゲート3823は、図5～図29を参照して上記で説明された、メモリデバイス500の制御ゲート1221、1222、および制御ゲート1223を形成するものと同様のプロセス、もしくは同一のプロセスを使用して、形成することができる。図38のデータ線3851、3852、およびデータ線3853は、図30および図31のデータ線251、252、およびデータ線253に対応し得る。図38に示すように、メモリデバイス3200は、図5～図29を参照して上記で説明された、メモリデバイス500のメモリセル2910、2911、およびメモリセル2912を形成するものと同様のプロセス、もしくは同一のプロセスを使用して形成することができる、メモリセル3810、3811、およびメモリセル3812を含み得る。

10

#### 【0068】

本明細書で説明される1つ以上の実施形態は、メモリデバイス、およびそのメモリデバイスの形成方法を含む。1つのそのようなメモリデバイスは、メモリセルの第1のグループを含み得、この第1のグループの各セルは、そのメモリデバイスの1つのデバイスレベル内に配置される第1の制御ゲートの、対応する空洞内に形成される。このメモリデバイスはまた、メモリセルの第2のグループも含み得、この第2のグループの各セルは、そのメモリデバイスの別のデバイスレベル内に配置される第2の制御ゲート内の、空洞内に形成される。追加的な装置および方法が説明される。追加的な装置および方法を含めた、他の実施形態は、図1～図38を参照して上記で説明される。

20

#### 【0069】

メモリデバイス100、200、500、3000、およびメモリデバイス3200、ならびにメモリセル210、211、212、2910、2911、2912、3010、3811、およびメモリセル3812などの装置の説明は、様々な実施形態の構造の、全般的な理解を提供することを意図するものであり、本明細書で説明される構造を利用することができる装置の、全ての要素および機構の、完全な説明を提供することを意図するものではない。

30

#### 【0070】

その様々な実施形態の装置は、高速コンピュータ内で使用される電子回路機構、通信および信号処理回路機構、メモリモジュール、携帯用メモリ記憶装置（例えば、サムドライブ）、单一またはマルチプロセッサモジュール、单一または多重埋め込みプロセッサ、マルチコアプロセッサ、データスイッチ、ならびにマルチレイヤー、マルチチップモジュールを含む、特定用途向けモジュールを含み得るか、もしくはこれらに含めることができる。そのような装置は、テレビジョン、携帯電話、パーソナルコンピュータ（例えば、ラップトップコンピュータ、デスクトップコンピュータ、ハンドヘルドコンピュータ、タブレットコンピュータなど）、ワークステーション、ラジオ、ビデオプレーヤー、オーディオプレーヤー、（例えば、M P 3 (Motion Picture Experts Group, Audio Layer 3) プレーヤー）、車両、医療装置（例えば、ハートモニター、血圧モニターなど）、セットトップボックスなどのよう、様々な電子システム内部のサブコンポーネントとして、更に含めることができる。

40

#### 【0071】

上記の説明および図面は、本発明の一部の実施形態を説明することにより、当業者が、本発明の実施形態を実践することを可能にする。他の実施形態は、構造的変更、論理的変更、電気的変更、プロセスの変更、および他の変更を、組み込むことができる。実施例は、単に可能な変型を代表するものである。一部の実施形態の諸部分および諸機構は、他の諸部分および諸機構内に含めるか、またはそれらに置き換えることができる。上記の説明

50

を研究し、理解することで、当業者には、多くの多の実施形態が明らかとなるであろう。

【 0 0 7 2 】

要約は、本技術的開示の本質および要旨を、読者が手早く確認することを可能にする要約を要求する、37 C . F . R . Section 1 . 72 ( b ) に従って、提供されるものである。本開示の要約は、特許請求の範囲の範囲または意味を、解釈もしくは限定するために使用されることがないという理解のもとに提示される。

【 义 1 】

【 义 2 】

FIG. 2

【図3】

【図4】

【図5】

【図6】

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図11】

FIG. 11

【図12】

FIG. 12

【図13】

*FIG. 13*

【図14】

FIG. 14

【図15】

FIG. 15

【図16】

FIG. 16

【図17】

FIG. 17

【図18】

FIG. 18

【図19】

FIG. 19

【図20】

FIG. 20

【図21】

FIG. 21

【図22】

FIG. 22

【図23】

【図24】

【図25】

【図26】

【図27】

FIG. 27

【図28】

FIG. 28

【図29】

FIG. 29

【図30】

FIG. 30

【図31】

【図32】

【図33】

【図34】

【図35】

FIG. 35

【図36】

FIG. 36

【図37】

FIG. 37

【図38】

FIG. 38

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 27/105 (2006.01) H 01 L 49/00 Z

H 01 L 45/00 (2006.01)

H 01 L 49/00 (2006.01)

(72)発明者 ザフラク , ジョン ケー .

アメリカ合衆国 , アイダホ州 83616 , イーグル , ウエスト シュガーベリー ドライブ 2

633

審査官 小山 満

(56)参考文献 特開2009-266945 (JP, A)

特開2009-117843 (JP, A)

特開2008-160004 (JP, A)

特開2010-102755 (JP, A)

特開2010-130016 (JP, A)

特開2010-010688 (JP, A)

特開2007-318083 (JP, A)

国際公開第2009/114675 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/8247

H 01 L 21/336

H 01 L 27/105

H 01 L 27/115

H 01 L 29/788

H 01 L 29/792

H 01 L 45/00

H 01 L 49/00