(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5702725号

(P5702725)

(45) 発行日 平成27年4月15日(2015.4.15)

(24) 登録日 平成27年2月27日(2015.2.27)

|                         |                    |

|-------------------------|--------------------|

| (51) Int.Cl.            | F 1                |

| HO 1 L 27/105 (2006.01) | HO 1 L 27/10 4 4 8 |

| HO 1 L 27/10 (2006.01)  | HO 1 L 27/10 4 8 1 |

| HO 1 L 45/00 (2006.01)  | HO 1 L 45/00 Z     |

| HO 1 L 49/00 (2006.01)  | HO 1 L 49/00 Z     |

| G 11 C 13/00 (2006.01)  | G 11 C 13/00 2 3 0 |

請求項の数 30 (全 20 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2011-531175 (P2011-531175)  |

| (86) (22) 出願日 | 平成21年10月8日 (2009.10.8)        |

| (65) 公表番号     | 特表2012-505551 (P2012-505551A) |

| (43) 公表日      | 平成24年3月1日 (2012.3.1)          |

| (86) 國際出願番号   | PCT/US2009/060023             |

| (87) 國際公開番号   | W02010/042732                 |

| (87) 國際公開日    | 平成22年4月15日 (2010.4.15)        |

| 審査請求日         | 平成24年9月27日 (2012.9.27)        |

| (31) 優先権主張番号  | 61/103,928                    |

| (32) 優先日      | 平成20年10月8日 (2008.10.8)        |

| (33) 優先権主張国   | 米国 (US)                       |

|           |                                                                                                                                                                                    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 511000957<br>ザ・リージェンツ・オブ・ザ・ユニバーシティ・オブ・ミシigan<br>THE REGENTS OF THE UNIVERSITY OF MICHIGAN<br>アメリカ合衆国、48109-2590<br>ミシigan州、安娜ーバー、ヒューロン・パークウェイ、1600、オフィス・オブ・テクノロジー・トラン스ファー、セカンド・フロア |

| (74) 代理人  | 110001195<br>特許業務法人深見特許事務所                                                                                                                                                         |

最終頁に続く

(54) 【発明の名称】調整可能な抵抗を備えたシリコン系ナノスケール抵抗素子

## (57) 【特許請求の範囲】

## 【請求項 1】

不揮発固体抵抗素子であって、

第1電極と、

p型シリコン第2電極と、

前記第1電極と前記p型シリコン第2電極との間に電気的に接続された非結晶質シリコンナノ構造とを備え、前記非結晶質シリコンナノ構造は、ナノスケール範囲にある少なくとも2つの次元を有し、

前記第1電極は、前記第1電極と前記p型シリコン第2電極との間に印加される電圧の存在下において、前記非結晶質シリコンナノ構造内にフィラメントを形成する金属イオンを供給する金属電極であり、

前記非結晶質シリコンナノ構造は前記第1電極と前記p型シリコン第2電極とを介して前記非結晶質シリコンナノ構造に印加される電圧に応答して調整可能な抵抗を有し、さらに、

3つ以上の抵抗値間で前記非結晶質シリコンナノ構造の前記抵抗を調整するように動作し得る制御回路を備える、

抵抗素子。

## 【請求項 2】

前記非結晶質シリコンナノ構造は非晶質シリコン含有材料を含む、請求項1に記載の抵抗素子。

**【請求項 3】**

前記 p 型シリコン第 2 電極は p 型ドープポリシリコン材料を含む、請求項 1 または請求項 2 に記載の抵抗素子。

**【請求項 4】**

前記非結晶質シリコンナノ構造は対向する端面を有するピラーを含み、各電極は前記端面の異なる 1 つに接している、請求項 1 から請求項 3 のいずれか 1 項に記載の抵抗素子。

**【請求項 5】**

前記非結晶質シリコンナノ構造は空間 3 次元の全てにおいてナノスケールである、請求項 1 から請求項 4 のいずれか 1 項に記載の抵抗素子。

**【請求項 6】**

前記 空間 3 次元の各々が 100 nm 未満である、請求項 5 に記載の抵抗素子。

**【請求項 7】**

前記制御回路は、前記非結晶質シリコンナノ構造へ電気的に直列接続される 1 以上の抵抗要素を含む、請求項 1 から請求項 6 のいずれか 1 項に記載の抵抗素子。

**【請求項 8】**

前記抵抗要素は制御抵抗を含む、請求項 7 に記載の抵抗素子。

**【請求項 9】**

前記制御回路は、前記非結晶質シリコンナノ構造へ接続される抵抗の総量を選択的に変えるように動作し得る回路とともに前記 1 以上の抵抗要素を含む、請求項 7 または請求項 8 に記載の抵抗素子。

**【請求項 10】**

前記制御回路は前記非結晶質シリコンナノ構造に直列接続される制御抵抗を与え、前記制御回路はその制御抵抗を関連する抵抗値に設定することによって前記非結晶質シリコンナノ構造の抵抗を任意の抵抗値に調整するように動作可能である、請求項 1 から請求項 9 のいずれか 1 項に記載の抵抗素子。

**【請求項 11】**

前記抵抗素子が前記非結晶質シリコンナノ構造に直列のダイオードを含むように、前記 p 型シリコン第 2 電極に接する n 型ドープシリコン層をさらに含む、請求項 1 から請求項 10 のいずれか 1 項に記載の抵抗素子。

**【請求項 12】**

前記第 1 電極は、銀、金、アルミニウムからなる群から選択される、請求項 1 から請求項 11 のいずれか 1 項に記載の抵抗素子。

**【請求項 13】**

前記非結晶質シリコンナノ構造近くの位置において前記 p 型シリコン第 2 電極と接している第 2 金属電極をさらに含む、請求項 1 から請求項 12 のいずれか 1 項に記載の抵抗素子。

**【請求項 14】**

前記第 2 金属電極は前記非結晶質シリコンナノ構造から 100 nm 以下だけ隔てられている、請求項 13 に記載の抵抗素子。

**【請求項 15】**

前記非結晶質シリコンナノ構造は、約 30 nm から約 60 nm の範囲から選択された直径を有する、請求項 1 から請求項 14 のいずれか 1 項に記載の抵抗素子。

**【請求項 16】**

絶縁層をさらに備え、前記非結晶質シリコンナノ構造は前記絶縁層に埋め込まれている、請求項 1 から請求項 15 のいずれか 1 項に記載の抵抗素子。

**【請求項 17】**

不揮発固体抵抗素子を有する少なくとも一つのメモリセルを含むメモリ装置であって、前記不揮発固体抵抗素子は、

第 1 電極と、

p 型シリコン第 2 電極と、

10

20

30

40

50

前記第1電極と前記p型シリコン第2電極との間に電気的に接続された非結晶質シリコンナノ構造とを備え、前記非結晶質シリコンナノ構造は、ナノスケール範囲にある少なくとも2つの次元を有し、

前記第1電極は、前記第1電極と前記p型シリコン第2電極との間に印加される電圧の存在下において、前記非結晶質シリコンナノ構造内にフィラメントを形成する金属イオンを供給する金属電極であり、

前記非結晶質シリコンナノ構造は、前記第1電極と前記p型シリコン第2電極とを介して前記非結晶質シリコンナノ構造に印加される電圧に応答して調整可能な抵抗を有し、

前記不揮発固体抵抗素子の前記非結晶質シリコンナノ構造は前記メモリセル内において調整可能な抵抗を有し、

前記調整可能な抵抗は異なる記憶数に対応する3以上の抵抗のいずれかに設定可能であって、それによって前記メモリセルがマルチレベル数の記憶が可能である、メモリ装置。

#### 【請求項18】

前記メモリセル内にストアされるべき数に基づいて調整可能な抵抗値を設定するための制御回路をさらに含む、請求項17に記載のメモリ装置。

#### 【請求項19】

前記制御回路は前記非結晶質シリコンナノ構造に直列の制御抵抗を含む、請求項18に記載のメモリ装置。

#### 【請求項20】

前記p型シリコン第2電極はp型ポリシリコンを含む、請求項17から請求項19のいずれか1項に記載のメモリ装置。

#### 【請求項21】

前記第1電極は、銀、金、アルミニウムからなる群から選択される、請求項17から請求項20のいずれか1項に記載のメモリ装置。

#### 【請求項22】

前記第1電極と結合された複数のCMOSデバイスをさらに備える、請求項17から請求項21のいずれか1項に記載のメモリ装置。

#### 【請求項23】

前記非結晶質シリコンナノ構造は、非晶質シリコン含有材料を含む、請求項17から請求項22のいずれか1項に記載のメモリ装置。

#### 【請求項24】

不揮発固体抵抗素子であって、

第1金属電極と、

p型ポリシリコン電極と、

前記第1金属電極と前記p型ポリシリコン電極との間で少なくとも部分的に配置された絶縁層と、

対向する端面を有しあつ前記絶縁層内に埋め込まれた非結晶質シリコンナノ構造とを備え、前記対向する各端面は前記第1金属電極および前記p型ポリシリコン電極の異なる1つに接続され、前記非結晶質シリコンナノ構造は、ナノスケール範囲にある少なくとも2つの次元を有し、さらに、

前記p型ポリシリコン電極と接触し、かつ、前記p型ポリシリコン電極を介して前記非結晶質シリコンナノ構造と電気的に接続される第2金属電極を備え、

前記第1金属電極は、前記第1金属電極と前記p型ポリシリコン電極との間に印加される電圧の存在下において、前記非結晶質シリコンナノ構造内にフィラメントを形成する金属イオンを供給する金属を含み、それによって前記非結晶質シリコンナノ構造は前記印加電圧に基づいて調整され得る抵抗を示し、

前記第2金属電極は、前記非結晶質シリコンナノ構造から100nm以下だけ隔てられている、抵抗素子。

#### 【請求項25】

前記絶縁層はスピンドルオングラス層を含む、請求項24に記載の抵抗素子。

10

20

30

40

50

**【請求項 2 6】**

前記第1金属電極は、銀、金、アルミニウムからなる群から選択される、請求項2 4または請求項2 5に記載の抵抗素子。

**【請求項 2 7】**

前記第1金属電極と結合された複数のCMOSデバイスをさらに備える、請求項2 4から請求項2 6のいずれか1項に記載の抵抗素子。

**【請求項 2 8】**

前記非結晶質シリコンナノ構造は、非晶質シリコン含有材料を含む、請求項2 4から請求項2 7のいずれか1項に記載の抵抗素子。

**【請求項 2 9】**

請求項1から請求項1 6、請求項2 4から請求項2 8のいずれか1項に記載の抵抗素子を含む少なくとも1つのメモリセルを有するデジタル不揮発メモリ装置。 10

**【請求項 3 0】**

請求項1から請求項1 6、請求項2 4から請求項2 8のいずれか1項に記載の抵抗素子を含む電気的相互接続を有する、電子回路。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は調整可能な抵抗を有する不揮発性で固体状の2端子抵抗素子に関し、これは記憶貯蔵や制御可能な回路接続に使用し得るものである。 20

**【背景技術】****【0 0 0 2】**

最近では、抵抗ランダムアクセスメモリ( R R A M s )が、超高密度の不揮発情報記憶のための潜在的候補として顕著な興味を引起している。典型的なR R A M 装置は、一対の電極間に挟まれた絶縁層からなっており、電気的パルス誘起によるヒステリシス抵抗スイッチング効果を示す。抵抗スイッチングは、ジュール加熱と、二元酸化物( 例えは、N i O や T i O<sub>2</sub> )中の電気化学プロセスまたは酸化物、カルコゲニドおよびポリマを含むイオン性導体に関する酸化還元プロセスとによる絶縁体内の導電性フィラメントの形成によって説明してきた。抵抗スイッチングは、T i O<sub>2</sub>膜および非晶質シリコン( a - S i )膜中のイオンの電界アシスト拡散によっても説明してきた。 30

**【0 0 0 3】**

a - S i 構造の場合、シリコン内への金属イオンの電圧誘起拡散は、a - S i 構造の抵抗を減ずる導電性フィラメントを形成させる。これらのフィラメントはバイアス電圧の除去後にも残って素子の不揮発性を与え、それらは逆極性の印加電圧の駆動力下において金属電極へのイオンの逆拡散によって除去され得る。

**【発明の概要】****【発明が解決しようとする課題】****【0 0 0 4】**

2つの金属電極間に挟まれたa - S i 構造によって形成された抵抗素子は、その制御可能な抵抗特性を示すとして知られてきた。しかし、そのような素子は典型的にはミクロンサイズのフィラメントを有し、サブ100ナノメータ範囲へスケールダウンされることが阻害されている。また、そのような素子は高い形成電圧を必要とし、これは素子のダメージを生じて製造歩留まりを限定させる。 40

**【課題を解決するための手段】****【0 0 0 5】**

本発明の1つの態様によれば、不揮発性の固体抵抗素子が提供され、それは第1電極、p型シリコン第2電極、およびそれらの電極間に電気的接続された非結晶質シリコンナノ構造を含んでいる。このナノ構造は、電極を介してナノ構造に印加される電圧に応答して調整可能な抵抗を有する。その非結晶質シリコンナノ構造は、例えは非晶質シリコンナノ構造または非晶質ポリシリコンナノ構造であり得る。 50

## 【0006】

本発明のもう1つの態様では、その抵抗素子が、デジタル記憶装置中のメモリセルとして使用される。その記憶装置は抵抗素子のアレイを含むことができ、一例では各抵抗素子に関して単一ビットの記憶を提供し、もう1つの例では各メモリセルが1ビットより多いデータをストアし得るように各抵抗素子に関してマルチレベル数の記憶を提供する。

## 【0007】

本発明にさらにもう1つの態様では、抵抗素子が、電気回路中の電気的相互接続として使用される。この相互接続は、少なくとも実質的に導電性と実質的に非導電性の状態の間でスイッチされ得る。

## 【0008】

本発明にさらにもう1つの態様では、不揮発固体抵抗素子が提供され、それは第1電極、p型ポリシリコン電極、これらの電極間で少なくとも部分的に配置された絶縁層、その絶縁層に埋め込まれた非晶質シリコン構造、および第2金属電極を含んでいる。その非晶質シリコン構造は対向する端面を有し、これらの各々は異なる電極の1つに接続されている。第1電極は金属を含み、複数の電極を横切る印加電圧の存在において、シリコン構造内にフィラメントを形成する金属イオンを供給する。その結果、シリコン構造は、印加電圧に基づいて調整され得る抵抗を示す。第2金属電極は、シリコン構造から100nm以下の位置においてポリシリコン電極に接している。

## 【0009】

本発明にさらにもう1つの態様では、不揮発固体スイッチング素子をオフ状態からオン状態へ調整する方法が提供され、非結晶質シリコンナノ構造を横切る電圧を印加するステップを含み、印加される電圧は、シリコンナノ構造がオフ状態からオン状態へ切替る所定の確率を達成するように選択された大きさと持続時間を有する。

## 【図面の簡単な説明】

## 【0010】

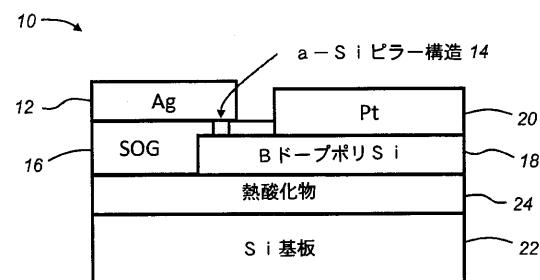

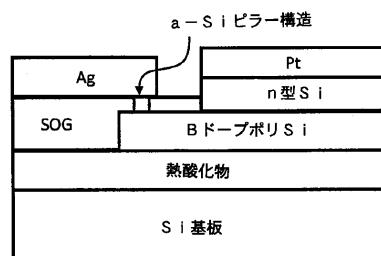

【図1a】本発明によって構成された单一セルa-Si抵抗素子の一実施例の模式図である。

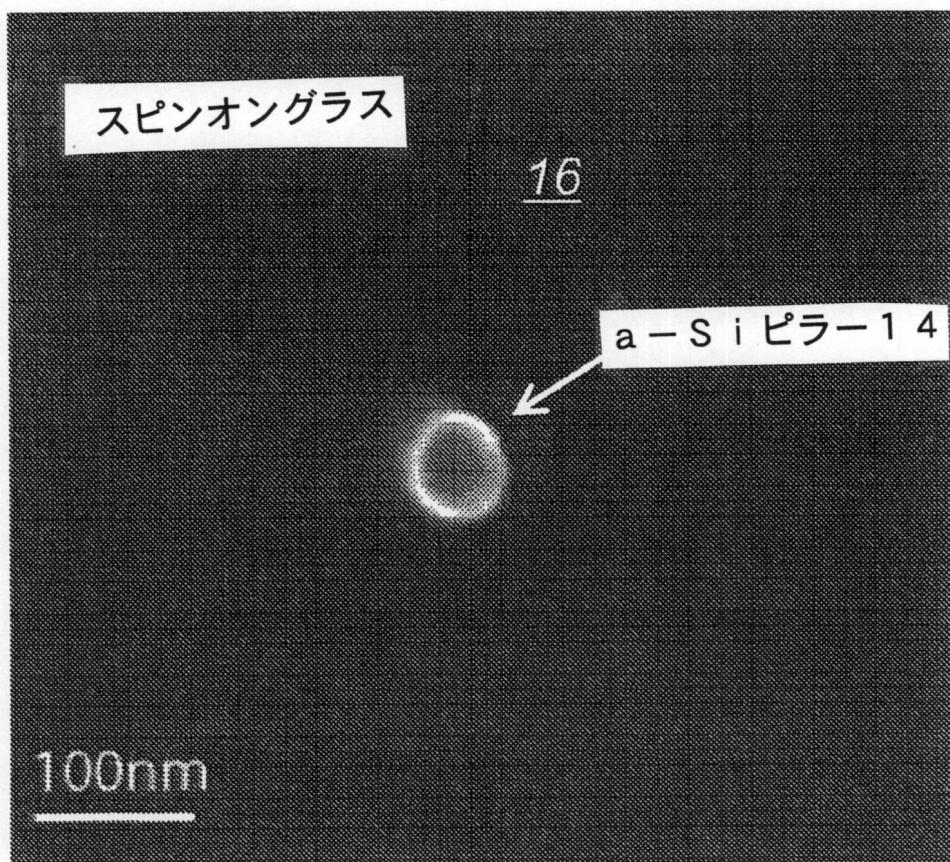

【図1b】図1(a)に示されているような素子の部分的に構築されたa-Si構造の上面のSEM像である。

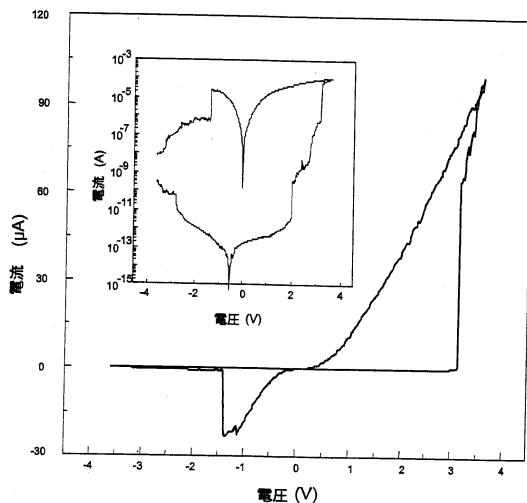

【図1c】図1(a)に示されているような典型的なa-Si構造の抵抗スイッチング特性を示すグラフである。

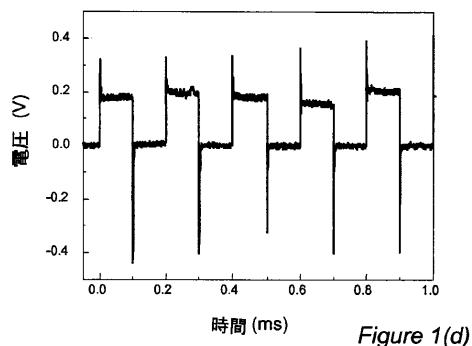

【図1d】図1(a)に示されているようなa-Si素子に関するプログラミング応答を示す波形である。

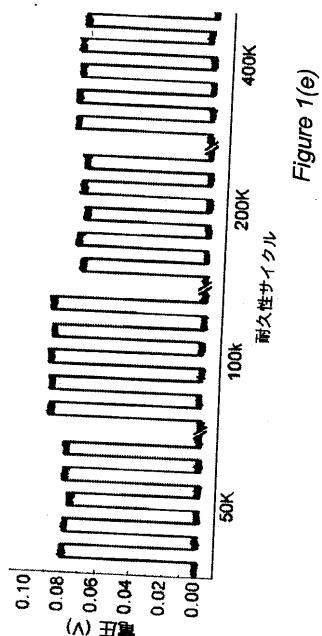

【図1e】図1(a)に示されているようなa-Si素子の耐久性試験の結果を示す波形である。

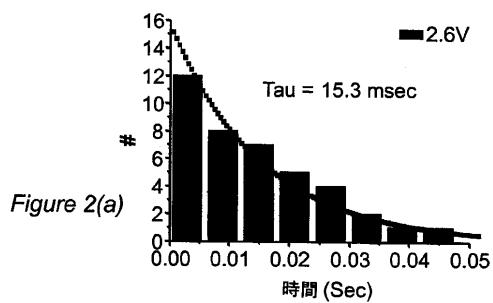

【図2a】或るバイアス電圧に関する典型的なa-Si素子のスイッチング応答の棒グラフである。

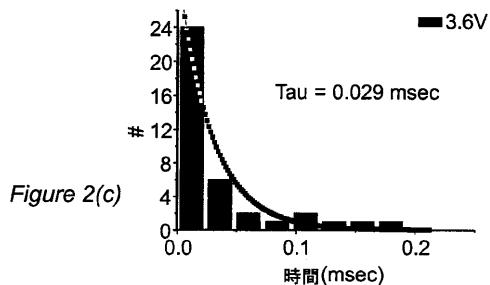

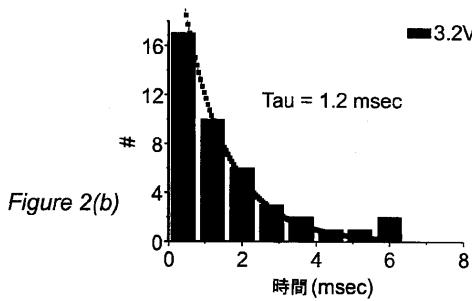

【図2b】異なるバイアス電圧に関する典型的なa-Si素子のスイッチング応答の棒グラフである。

【図2c】異なるバイアス電圧に関する典型的なa-Si素子のスイッチング応答の棒グラフである。

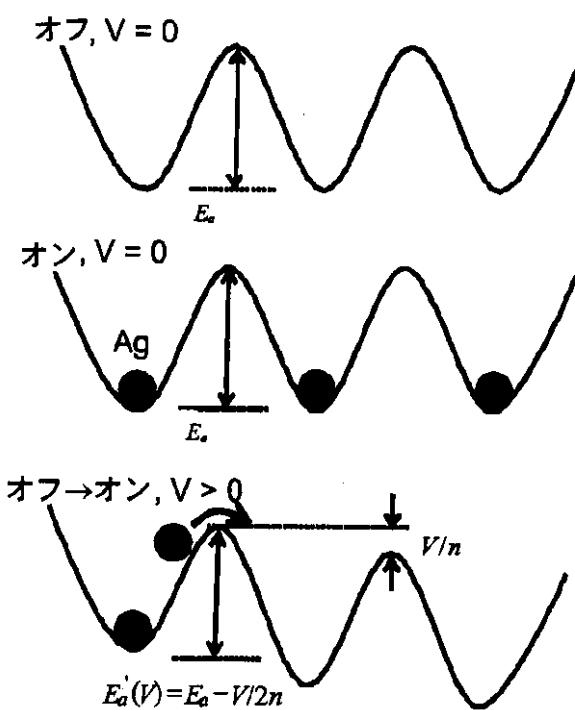

【図2d】図1(a)に示されているようなa-Si素子の異なる導電性状態における金属イオンの拡散を示す3部模式図である。

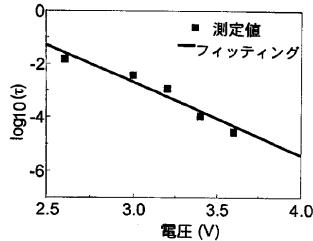

【図2e】図1(a)に示されているようなa-Si素子に関するスイッチング時間とバイアス電圧との関係を示すグラフである。

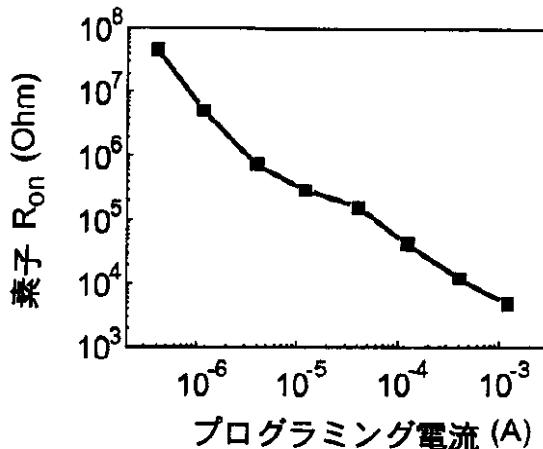

【図3a】直列接続される異なる制御抵抗または他の手段によって制御される異なるプログラミング電流レベルを用いて典型的なa-Si素子をプログラミングした結果を示すグラフである。

【図3b】プログラムされたa-Si素子の最終的抵抗とその素子をプログラムするために選択されて使用された制御抵抗との相関関係を示すグラフである。

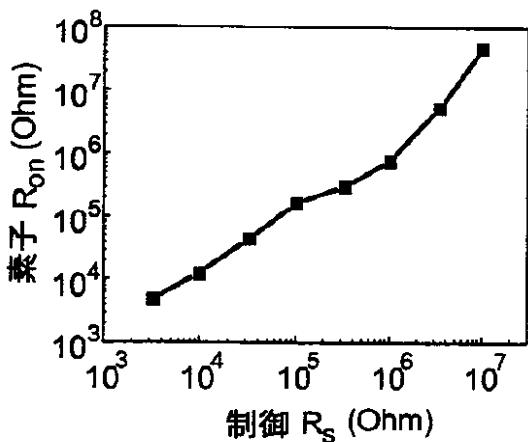

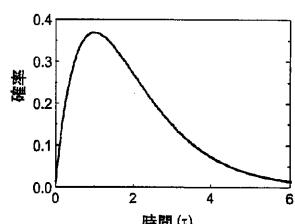

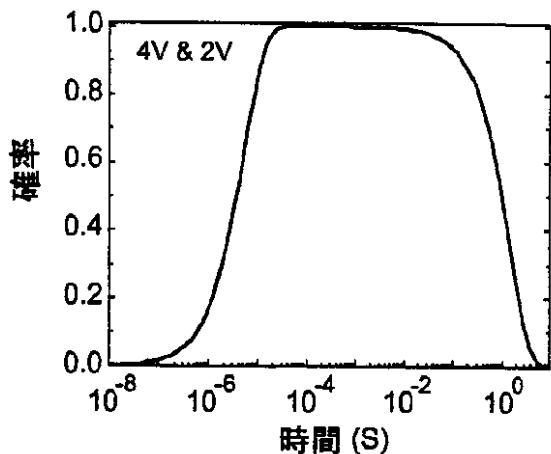

【図3c】直列接続される制御抵抗なしに所定のバイアス電圧を典型的なa-Si素子に印加する場合に、個別単一の抵抗スイッチング事象の確率を時間に対して示すグラフである。

【図3d】直列接続される制御抵抗なしに所定のバイアス電圧を典型的なa-Si素子に印加する場合に、少なくとも1つの抵抗スイッチング事象を有する確率を時間に対して示すグラフである。

【図3e】直列接続される制御抵抗を用いる場合に、典型的なa-Si素子に関して、個別単一の抵抗スイッチング事象の確率を時間に対して示すグラフである。

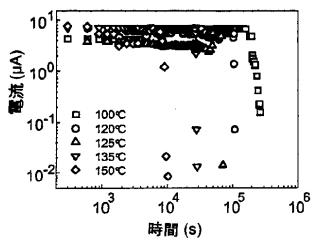

【図4a】図1(a)に示されているようなa-Si素子へバイアス電圧が印加されない場合に、オンからオフへの抵抗遷移に関する待ち時間のプロットである。 10

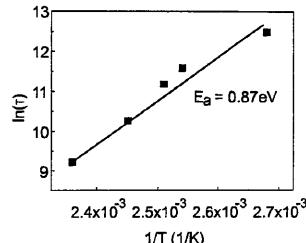

【図4b】温度に対する待ち時間のグラフである。

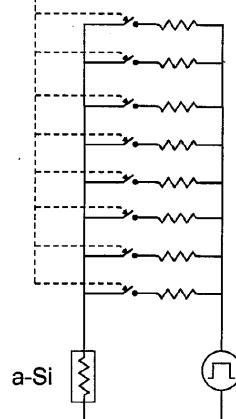

【図5】単一のa-Si素子においてマルチレベル数記憶のために複数の制御抵抗を使用する制御回路を示す図である。

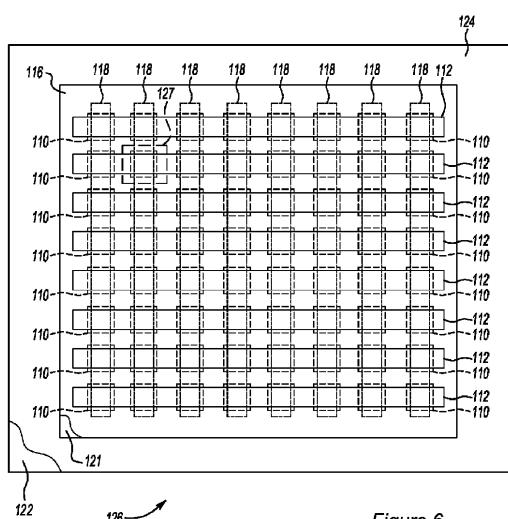

【図6】図1に示されているようなa-Si構造の複数を用いたメモリ装置の部分破断平面図である。

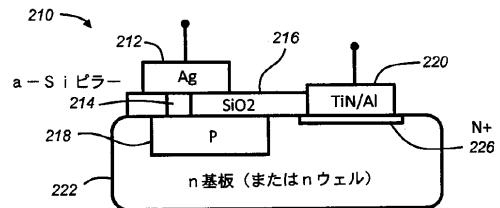

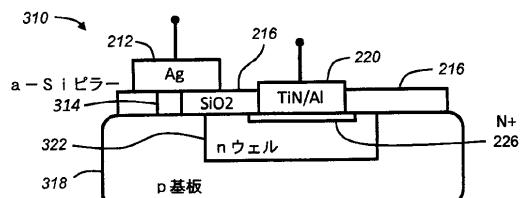

【図7】組込みダイオードを有する単一セルa-Si抵抗素子の異なる実施例の模式図である。

【図8】組込みダイオードを有する単一セルa-Si抵抗素子の異なる実施例の模式図である。

【図9】組込みダイオードを有する単一セルa-Si抵抗素子の異なる実施例の模式図である。 20

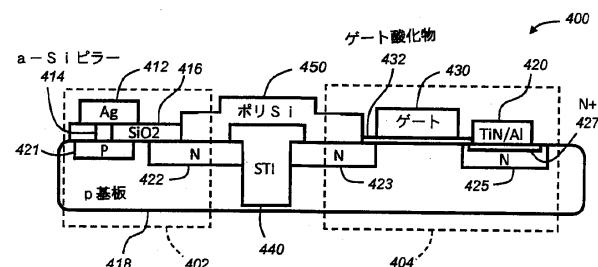

【図10】組込みダイオードを備えたa-Si抵抗素子とそのa-Si素子のマルチレベルプログラミングのためにゲート制御された可変抵抗器として動作する電界効果トランジスタ(FET)の実施例の模式図である。

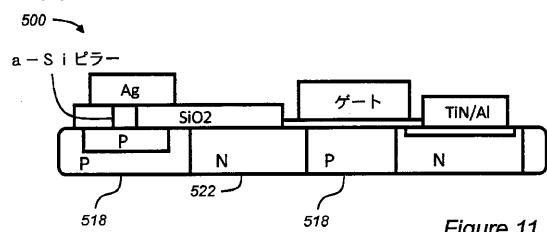

【図11】組込みダイオードを備えたa-Si抵抗素子とそのa-Si素子のマルチレベルプログラミングのためにゲート制御された可変抵抗器として動作する電界効果トランジスタ(FET)の異なる実施例の模式図である。

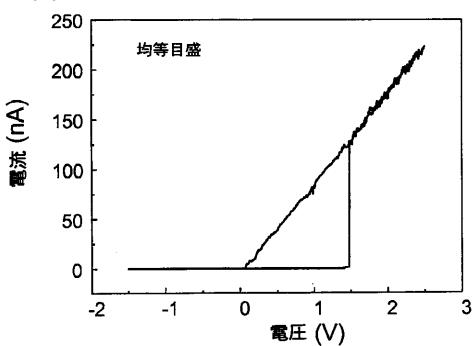

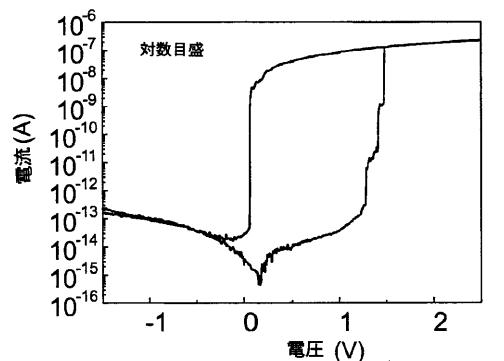

【図12】ここに開示された基本的a-Si抵抗素子に関する例示的な内在ダイオード特性のグラフである。

【図13】ここに開示された基本的a-Si抵抗素子に関する例示的な内在ダイオード特性のグラフである。 30

#### 【発明を実施するための形態】

##### 【0011】

図1(a)は、不揮発固体抵抗素子10を描いており、それは適切な制御回路を用いて種々の値に選択的に設定されかつリセットされ得る抵抗を示すナノスケールa-Si構造を含んでいる。一度設定されれば、その抵抗値は、それを変化させることなくその抵抗を判定するに十分な大きさの小さな電圧を用いて読まれ得る。図解されている実施例は抵抗要素としてa-Siを用いているが、非晶質ポリシリコンのような他の非結晶質シリコン(nc-Si)構造も使用され得ることが理解されよう。すなわち、ここで用いられかつ特許請求の範囲で用いられているように、非結晶質シリコン(nc-Si)は、制御可能な抵抗を示す非晶質シリコン(a-Si)、非晶質ポリシリコン(ポリSi)、またはそれら2つの組合せを意味する。また、ここにおける議論の多くはミクロン範囲の1以上の次元を有するより大きなスケールのa-Si構造にも当てはまるが、図示された実施例は、小さなスケールに特有の或る特性を示すa-Siナノ構造である。ここで用いられているようなナノ構造の用語は、ナノスケール範囲にある少なくとも2つの次元を有する構造を言及しており、例えば、0.1から100ナノメータの一般的範囲内における直径または複数の断面次元を有する構造である。これは、全ての空間三次元がナノスケールにある構造を含み、例えば、ナノスケール直径と同程度の長さを有する円柱状のナノコラムまたはナノピラーである。ナノ構造は当業者に知られている種々のナノスケール構造を含み得て、例えば、ナノチューブ、ナノワイヤ、ナノロッド、ナノコラム、ナノピラー、 40

ナノ粒子、およびナノファイバーである。1つのそのような構造が図1(a)と1(b)に描かれた実施例であり、それは100nm未満(例えば、図示されている特定の例では60nm)の直径の円形断面であり得るプラグまたはピラー構造である。そのピラー高さまたは長さは配置に依存し、ナノスケール(例えば、図示されている例では30nm)またはそれ以上であり得る。

#### 【0012】

図1(a)と1(b)のa-Si構造14は、絶縁誘電体16に埋め込まれている。この絶縁誘電体は種々の材料で造られかつ異なる方法で構築され得るが、図示ではスピンドルガラス(SOG)であって、これは最初にa-Si構造14の周りに流されてから固化される。全ての絶縁誘電体が、公知のプロセスによって構築され得る。全体的抵抗素子10は、熱酸化物層24で覆われたシリコン基板層22を用いて構築されている。a-Siピラー14の下にあるのはボロンドープされたまたは他のp型のポリシリコン電極18であり、これはa-Siピラー14の下端面に接するとともに被さる金属電極20を受けるようにピラーから横方向に伸びている。この電極は任意の適切な金属で造られ得て、例えばパラジウムまたは白金のような白金族金属を含み得る。ポリシリコン(p-Si)電極18に対向してa-Siピラー14の上面上にあるのは銀(Ag)金属電極12であり、これはフィラメント形成イオン源として働く。図示されている実施例では銀が用いられるが、この電極12(他の金属電極20も)は種々の他の適切な金属、例えば金(Au)、ニッケル(Ni)、アルミニウム(Al)、クロム(Cr)、鉄(Fe)、マンガン(Mn)、タンゲステン(W)、バナジウム(V)、コバルト(Co)などから形成され得ることが理解されよう。フィラメント形成イオンを供給し得る他の適切な金属も使用され得る。

#### 【0013】

図1(a)のa-Si素子10を作製するために、200nm厚さの熱酸化物層を備えた最高級シリコン基板上に、Bドープp-Si底部電極18がLPCVD(低圧化学気相堆積)によって堆積され得る。非晶質シリコン層はBドープp-Si上に堆積された30nm厚さの層であり得て、その後の2つのRIE(反応性イオンエッチング)ステップによってa-Siピラー14とp-Si底部電極18の構造が規定される。その後、スピンドルガラス(SOG)が、3000RPMの速度でサンプル上にスピンドルコートされて、320において1時間で硬化され得る。この絶縁性SOG層16は、2つの電極12、18の電気的分離を提供するとともに、a-Siピラー14のための機械的サポートをも提供する。このように形成された後に、SOG層16は、平坦な平面を生じてa-Siピラー14の端面を露出するように、部分的にエッチングされ得る。その後、a-Siピラー14の露出された端面上に、Ag電極12がリフトオフ法を用いるパターニングによって形成され得る。その後、底部p-Si層18にオーミックコンタクトを与えるように、第2金属(白金)電極20が付与される。白金電極20はp-Si電極18を介する抵抗の最小化を助けるようにa-Siピラー14の近くに配置され、この距離は好ましくは100nm以下である。パターン設計は、SOG16を介する直接的漏れ電流を小さく維持するために、頂部と底部の電極間の重なりを最小化するように選択され得る。この製造手続きに対する種々の変更がなされ得て、図1(a)の構造またはその素子の抵抗調整性を許容する他の適切なn-c-Si構造の達成のために他の製造アプローチも用いられ得ることが当業者に理解されよう。米国特許出願公開第2009/0014707A1号は、図1(a)および1(b)に示されたa-Si素子のような不揮発固体抵抗スイッチング素子の特性、使用、および動作に関する付加的な情報を与えている。それはa-Si素子の代替的実施例の構成に関する情報をも提供しており、それらの少なくとも或るものは図1(a)および1(b)に示されたa-Si素子の構築に適用可能である。不揮発固体抵抗スイッチング素子の製造、構成、および使用に関して米国特許出願公開第2009/0014707A1号に開示されて含まれている情報は、その参照によってここに導入される。

#### 【0014】

図1(a)に示されているような単一のa-Si素子は、独立に制御される頂部と底部の電極ペアとともに独立型の設定可能な相互接続またはメモリビットとして使用され得る

10

20

30

40

50

。底部コンタクトとして化学気相堆積（CVD）で堆積されたポリシリコンの使用は、種々の基板上の素子作製を可能にし、多層化された3次元構造の集積の潜在性を含んでいる。連続的なa-Si膜に比べて、図示されているa-Siプラグ構造14は、活性a-Si領域とフィラメント領域が物理的に明瞭に規定されることを確実にする助けとなる。また、この素子の構成はCMOS技術に完全に適合可能であり、神経形態学的ネットワークのような論理回路中の高密度不揮発メモリまたは設定可能な相互接続として現存のシステム中に容易に組入れられ得る。

## 【0015】

図1(c)は図1(a)に示されているような典型的なa-Siピラーの抵抗スイッチング特性を示しており、例として、約60nmの直径と30nmの厚さを有する素子に関するものである。それは対数目盛によるこのスイッチング特性の挿入グラフを含んでおり、これはターンオン過程中にステップ状遷移を示している。これらのナノスケールa-Siスイッチのために高電圧の生成は必要ではなく、作製後の素子は正の書き込みと負の消去の電圧パルスを印加することによって低抵抗のオン状態と高抵抗のオフ状態の間で繰返して切替えられ得る。小さなバイアスで測定されたオン/オフ抵抗比は、図1(c)に示されているように、 $10^7$ ほどに高くなり得る。前述のようにして作製されたa-Si素子の試験は、メモリ素子として、そのa-Siスイッチが歩留まり(例えば、60nm径のa-Siピラーの素子に関して>90%)、速度、耐久性、および記憶保持力において優れた性能基準を示している。図1(d)は、典型的な素子における50nsの書き込み/消去のパルス幅での書き込み-読み出し-消去-読み出しの繰り返しパルスシーケンスと出力応答を示している。素子の耐久性試験の結果は図1(e)に示されている。オン電流<20μAでの典型的な素子は、 $10^5$ より大きなプログラミングサイクルに対して劣化なしに耐えることが予想される。この限界を超えるとオフ状態の導電性が増大し始め、それによって減少されたオン/オフ抵抗比の結果となる。

## 【0016】

a-Si構造におけるスイッチングは、プログラミング電圧の印加によるナノスケールAgフィラメントの生成と回復によって説明することができ、図2(d)において模式的に示されている。マイクロスケールの金属/a-Si/金属構造についての以前の実験的および理論的検討では、フィラメントはa-Si層内の欠陥位置にトラップされた正に帯電した一連のAg<sup>+</sup>粒子の形にあると示唆されていた。オン状態における導電機構はAg<sup>+</sup>チェインを介する電子トンネリングであり、そして素子抵抗は最後のAg<sup>+</sup>粒子と底部電極との間のトンネリング抵抗によって支配される。図1(c)に示されているように、この挙動はオフ-オン遷移中の対数目盛による電流のステップ状の増大と整合している。なぜならば、Agフィラメントは、付加的なAg<sup>+</sup>粒子が新たなトラップ位置に飛び移るときに、ステップバイステップ様式で成長するからである。

## 【0017】

CMOS適合作製プロセスによって提供される微細制御に伴うa-Siピラー構造中の明瞭に規定された活性スイッチング領域は、その抵抗スイッチング素子によって提供される特有の特性を調査する詳細な検討を可能にする。フィラメント形成モデルの1つの直接的結論は、スイッチング速度がバイアス依存であろうということである。なぜならば、電子トンネリングと異なって、Ag<sup>+</sup>粒子の飛び移りは熱活性プロセスであり、その速度はバイアス依存活性エネルギーEa'(V)によって決定されるからであり、

## 【0018】

## 【数1】

$$\Gamma = 1/\tau = \nu e^{-E_a(V)/k_B T}, \quad (1)$$

## 【0019】

ここでk<sub>B</sub>はボルツマン係数、Tは絶対温度、 $\nu$ は特性滞留時間、そして $\Gamma$ は試行頻度である。図2(d)に示されているように、活性エネルギーはバイアス電圧の印加によって下がることができ、バイアス依存の待ち時間とスイッチング速度の結果となる。

10

20

30

40

50

## 【0020】

この効果は、バイアス電圧の関数としての第1遷移（すなわち、図1(c)中の第1電流ステップ）に関する待ち時間の検討を通して立証された。その待ち時間は、オフ状態の素子に所定の大きさの正方形パルスを印加して、電流における最初のシャープな増大までの経過時間  $t$  を測定することによって測定された。その後に素子が負の電圧パルスで消去されて、測定が繰り返された。図2(a)から(c)は、同じ素子において2.6V、3.2Vおよび3.6Vのバイアス電圧での第1遷移に関する待ち時間の棒グラフを示している。スイッチング過程の統計的性質のために、待ち時間はポアソン分布にしたがうはずであり、スイッチングが時間  $t$  の  $t$  内に起る確率は次式で与えられる。

## 【0021】

10

## 【数2】

$$P(t) = \frac{\Delta t}{\tau} e^{-t/\tau}. \quad (2)$$

## 【0022】

図2(a)から(c)における棒グラフは唯一のフィッティングパラメータとして ( $T_{au}$ と表示) を用いて式2にフィットされ得て、それによって 15.3 ms、1.2 ms および 0.029 ms の 値をそれぞれ生じる。これらのグラフは、 $\tau$  が  $V$  の強い関数であって  $V$  がわずか 1 V だけ増大するときにほとんど  $10^3$  だけ減少することを示している。図2(e)は 5 つの異なるバイアス電圧で測定された  $\tau$  の分布を指数関数的減衰を仮定するフィッティングとともに示しており、フィッティングパラメータとして  $\tau_0$  と  $V_0$  を扱って、

20

## 【0023】

## 【数3】

$$\tau(V) = \tau_0 e^{-V/V_0}, \quad (3)$$

## 【0024】

式3における  $V_0$  の物理的意味に注目することは興味あることである。図2(d)から、まず  $E_a' = E_a - Ed$  であり、ここで  $E_a$  はゼロバイアスにおける活性化エネルギー、  $E$  は電界、そして  $d$  は  $Ag^+$  トラップ位置間の距離である。 $Ag^+$  チェインを横切って電圧のほとんどが落ちると仮定すれば、 $Ag^+$  粒子はチェイン内で均等に分布し、  $E_a'$  ( $V$ ) =  $E_a - V / 2n$  となり、ここで  $n$  は  $Ag^+$  位置の番号である。そして、式3は式1から直接的に導出され得て、

30

## 【0025】

## 【数4】

$$\tau_0 = 1/v e^{E_a/k_B T} \text{ および } V_0 = 2n k_B T.$$

## 【0026】

40

重要なことは、図2(e)中のフィッティングから推論された 0.155 V の  $V_0$  値が、図1(c)中の片対数  $I$ - $V$  プロット中の主要電流ステップの数で示唆されているように、フィラメント中に 3 つの  $Ag^+$  位置が存在する ( $n = 3$ ) と仮定した場合に、この単純なモデルで予想される  $V_0 = 2n k_B T = 0.156$  V に非常に近いことである。明らかに式3は、待ち時間が強くバイアス依存性であることを示唆しており、それが印加バイアスの増大によって指数関数的に低減されることを示唆している。

## 【0027】

バイアス依存のスイッチング特性は、素子動作に対して重要な関係を有している。第1に、そのスイッチングが非常にシャープであるとしても(図1(c)参照)、そのスイッチングは基本的に“堅固な”閾値電圧を有していない。なぜならば、比較的低いバイアス

50

電圧においてもスイッチングが起る限定された確率が常に存在するからである。他方、閾値電圧は、或るプログラミングパルス幅に関して規定され得る。例えば、95%の成功率が達成される電圧以上として閾値が定義されれば、その閾値電圧は1msパルス幅に関して3.3Vであって、10nsパルス幅に関して5.1Vである。第2に、これらの素子において、外部回路抵抗を調整することによって、マルチレベルビット記憶が達成され得る。素子に直列抵抗が取り付けられれば、それを横切る電圧が最初のスイッチングの後に低下し、引き続くスイッチング事象の待ち時間が顕著に増大する。その結果、続くスイッチング事象が起る前にプログラミングパルスが除去されれば、部分的に形成されたフィラメントが生成され得て、オン状態とオフ状態の間の中間的抵抗値の結果となる。図3(a)は、同じプログラミングパルスであるが異なる直列抵抗値を用いて同一素子において得られた最終素子抵抗を示している。その素子において得られた $8 = 2^3$ の異なる抵抗レベルは、メモリ要素としての各素子が3ビットの情報を記憶し得ることを示唆している。図3(b)に示されているように、素子抵抗Rは直列抵抗の抵抗 $R_s$ とも相関している。なぜならば、待ち時間の延長を生じさせる電圧分割器効果は、素子抵抗が $R_s$ と同程度のときに最も顕著になるからである。

#### 【0028】

a - Si素子内へのマルチレベル数の選択的プログラミングを実行するために、種々のアプローチが用いられ得る。ここで用いられるように、マルチレベル数は、2(バイナリ)より多いレベルまたは値を有する数であり、例えば基数3ディジットまたは数、基数4数などである。マルチレベル数記憶装置はバイナリ情報のマルチビットをストアするために使用することができ、例えば、4レベルa - Si記憶セルは単一のa - Siセル内にバイナリデータの2ビットをストアすることができ、8レベルセルはバイナリデータの3ビットをストアすることができる。デジタル回路装置内で使用される場合、メモリセルは、a - Si素子内へバイナリまたは他の数をプログラムするために適当な制御回路を含むことができる。そのような回路は当業者のレベルの範囲内であり、そのような制御回路の例示的模式図が図5に示されている。図示されている制御回路は、a - Si構造と直列の回路内への付加的な抵抗の挿入または除去によって、8抵抗レベルの任意の1つでa - Si構造をセットするように使用され得る。この目的のために、回路内への制御抵抗の挿入と除去を切替えるために使用される制御信号へ3ビットのバイナリ入力データを変換するために、デコード回路が用いられ得る。この方法において、デコード回路は、a - Si構造に直列接続の合計制御抵抗を関連する抵抗値に設定することによって、a - Si構造の抵抗を所望の複数抵抗値の任意値に設定するように使用され得る。理解されるであろうように、図5の制御回路は模式的なものに過ぎず、a - Si構造の抵抗値の書き込み、消去、および読み出しのための具体的な回路構成は当業者に知られ得るであろう。

#### 【0029】

図5に示されているような制御回路は、a - Si構造の抵抗を調整するために、上記で議論された種々のステップを実行するように使用され得る。これらのステップは、全体として、a - Si構造の抵抗を初期抵抗値と最終抵抗値との間で調整するために用いられ得る方法を含む。一般に、その方法は、a - Si構造(第1抵抗素子)を第2抵抗素子へ電気的に直列接続し、直列接続されたそれらの抵抗素子を横切って電圧を印加するステップを含む。上記で議論されたように、第2抵抗素子は制御抵抗であって、2以上の制御抵抗の1つまたは組合せを含んでいる。制御抵抗は、a - Si構造に関する所望の最終抵抗値に基づいて(例えば、デコード回路によって)選択される。また、ここで議論されたように、a - Si構造構造の最終抵抗値は、印加電圧の大きさ、印加電圧の持続時間、またはそれらの両方に基づいて、少なくとも部分的に設定され得る。すなわち、印加ステップは、直列接続の抵抗素子を横切って選択された大きさと持続時間の電圧を印加することによって、最終抵抗値を設定することを含んでいる。また、上記で認識されるように、a - Si構造を用いてマルチレベル数記憶を行なうことができ、最終抵抗値は複数の選択可能な抵抗値の1つにされる。このために、a - Si構造を制御抵抗へ直列に電気的接続するステップは、選択可能な抵抗値の選択された1つに基づいて、a - Si構造に対して選択的

に 1 以上の制御抵抗を直列に挿入または短絡させることによって電気的に制御抵抗を形成することを含む。これも、図 5 のデコード回路または当業者に明らかであろう他の適切な回路を用いて行なわれ得る。a - S i 素子を初期の抵抗値にリセットするためには、逆極性のリセット電圧が a - S i 構造へ印加される。

#### 【 0 0 3 0 】

a - S i 構造はデジタル不揮発メモリ装置のメモリセルとして使用され得て、それはアレイまたは他の適当な構造に配置された多くの a - S i メモリセルを有している。図 6 は、超高密度メモリ装置を形成するために用いられるような例示的実施例を描いている。図示されたメモリ装置 126 は、S i O<sub>2</sub> 上層 124 を有するシリコン基板 122 と、一組の平行な p - S i 電極 118 に直交して重なる一組の平行な金属電極 112 から形成される交差バー構造とを含んでいる。a - S i 抵抗素子（全体として 110 で示されている）は、2 つのタイプの電極の各交差位置に配置されている。図 1 (a) の番号付けされた要素に比べて図 6 において 100 だけ異なって番号付けされた要素は、図 1 (a) の番号付けされた要素と必ずしも同一ではないが類似の構造と機能を有し得る。複数の抵抗素子 110 は、メモリ装置 126 の個別にアドレス可能な複数のメモリセルを含む。上側の組の電極 112 と下側の組の電極 118 との間に配置されているのは、SOG または他の絶縁層 116 であって、各メモリセル 110 における a - S i 構造を含んでいる。絶縁層 116 は基板の上層 124 まで延在し得て、それによって隣合う電極 118 を互いに分離し、または層 116 下の別の絶縁層 121 がこの目的のために用いられ得る。また、コラム内で隣接するセル間に p - S i 電極 118 を延在させる代わりに、それらは各セル位置に限定され得て、P t または他の適当な金属電極が各コラム内の p - S i 電極を相互接続するように用いられ得る。他の変更例も、当業者に明らかであろう。素子 110 のためのセルサイズ 127 は約 0.003 μm<sup>2</sup> である。他の例では、セルサイズ 127 は 0.003 μm<sup>2</sup> 未満または 0.01 μm<sup>2</sup> 以下であり得る。

#### 【 0 0 3 1 】

各メモリセル 110 は単一の a - S i 構造を含み得て、上記で議論されたように、a - S i 構造は単一ビットのデジタル記憶を行なうために使用される調整可能な抵抗を有し得て、または異なるストア数に対応する 3 以上の任意の抵抗に設定される調整可能な抵抗を有し得る。こうして、各メモリセルはマルチレベル数記憶が可能である。この目的のために、メモリ装置 126 は、任意の選択されたメモリセル 110 にマルチレベルデータを書き込むことを可能にするために、図 5 におけるような制御回路を含み得る。

#### 【 0 0 3 2 】

ビットまたはマルチレベル数記憶のために使用される代わりに、a - S i 構造は、上記で議論されたように、オン状態とオフ状態間でそれを切替える方法によって動作させられ得る。これは a - S i 構造を横切って電圧を印加することによって行なうことができ、その印加電圧は、オフ状態からオン状態へ切替える a - S i 素子の所定の確率を達成するようを選択された大きさと持続時間を持つている。成功裏のスイッチングの所定確率は、例えば 95 % または a - S i 素子の特定の応用に望まれるもしくは必要とされる他の任意のパーセンテージであり得る。

#### 【 0 0 3 3 】

上記のように、a - S i 素子の成功裏の動作は、バイアスの大きさに依存するのみならず持続時間にも依存する。また、スイッチング制御要件は、デジタルスイッチング（例えば、単一ビットメモリ）またはアナログ動作（例えば、相互接続）が望まれているかに依存する。上記で議論されたポアソン過程に関して、図 3 (c) は時間 t の間に確実に 1 つのスイッチング事象が起る確率をプロットしているのに対して、図 (d) は時間 t の間に少なくとも 1 つのスイッチング事象が起る確率をプロットしている。それらは外部直列抵抗が存在しない場合に対応しており、単一のスイッチング率 1 /  $t_{pulse}$  はステップ状のフィラメント形成プロセスに当たる。そして、十分長いプログラミングパルスに関して優れたデジタルスイッチとして働くことが明らかである（例えば、 $t_{pulse} > 3$  について 95 % の成功率が達成される）。他方、マルチレベル数記憶またはスイッチのアナログ

10

20

30

40

50

動作に関しては、パルス幅が最適化されなければならない。例えば、最初のスイッチングのみが起る最も高い確率に関して、 $t_{p u l s e}$ はに集中される必要がある。そうとしても、図3(c)に示されているように、最大の成功率はわずかに38%程度である。しかし、マルチビット動作に関する成功率は外部直列抵抗の付加によって顕著に改善され得て、引続くスイッチング率を劇的に減少させる。図3(e)は単純化された2ステップフィラメント形成プロセスにおいて最初のスイッチング事象のみが起る確率をプロットしており、そこでは2つの異なる速度が用いられ：

【0034】

【数5】

$$P(t) = \frac{\tau_2}{\tau_1 - \tau_2} \left( e^{-t/\tau_1} - e^{-t/\tau_2} \right), \quad (4)$$

10

【0035】

ここで、素子を横切る電圧が4V(最初のスイッチング事象の前で $R >> R_s$ )から2V(最初のスイッチング事象の後で $R = R_s$ )へ変化するときのスイッチング速度に対応してそれぞれ $\tau_1 = 3.36 \mu s$ および $\tau_2 = 1.30 s$ であり、これは最初のスイッチング事象後の電圧分割器効果の結果である。遙かに高い99%より大きな成功率は、スイッチングを最初の事象のみに限定するように、 $5 \tau_1 < t_{p u l s e} < 0.01 \tau_2$ (4Vにおける約13msの時間余裕)に関して達成され得る。付加的に、類似して示された特性は、他の抵抗スイッチング素子から予想されるものである。なぜならば、それらの多くは例えればイオンの拡散や酸化還元プロセスのような或る種の活性化工エネルギープロセスを伴うからである。

20

【0036】

バリアの活性化工エネルギーは、式1において待ち時間の温度依存性から推論することができる。図4(a)は、当初にオン状態にプログラムされた素子に関して、100から150の温度でゼロバイアスにおける時間依存の抵抗変化を示している。図1(c)を再度参照して、オフ状態への突然の遷移は、底部電極に最も近いトラップ位置から頂部電極へ向けてのAg<sup>+</sup>粒子の熱活性化飛び移りによるAgフィラメントの回復に対応しており、これは図4(b)に示された $1/k_B T$ に対する待ち時間 $t$ のアレニウス型プロットにおける良好なフィッティングによって立証されている。オン/オフ遷移に関する活性化工エネルギーはアレニウスプロットの傾斜からこの素子に関して0.87eVであると推論され、室温における保持時間は外挿からして6年であると見積ることができる。

30

【0037】

図6に示されているようなメモリアレイ内に組入れられるときまたは特定の応用のために必要もしくは望まれるとき、a-Si素子はp-n接合の形の内在ダイオードを伴って構築され得る。これは、製造中にp型ポリSi電極と第2金属(例えば、白金)電極との間にn型層を含めることによって導入され得る。この一例が図7に示されており、Pt電極下の付加的なn型層以外は、図1のa-Si抵抗素子10と同じであり得る。交差バー型のメモリアレイ内で用いられるとき、この構成は隣接する素子間のクロストークを防止するために使用することができる。なぜならば、1つのセルからそのダイオードを通って流出する順方向導電流は隣接するセルの(そのとき逆バイアスされている)ダイオードによって阻止されるであろうからである。

40

【0038】

図8は、従来のCMOS製造技術を用いて形成され得る組込みダイオードを含む单一セルa-Si抵抗素子210の実施例を描いている。図1の番号付けられた要素に比べて200だけ異なる図8の番号付けされた要素は、図1の番号付けされた要素に比べて必ずしも同一ではないが類似の構成と機能を有し得る。素子210は、n型結晶質シリコン基板222を用いて構築され得る。p型シリコン領域218は、イオン注入または拡散法のような従来のCMOSプロセスによって形成されるポリSi層であり得る。p型領域218とAg端子212とは、上述のように印加バイアスに依存して抵抗を変化させ得るa-Si

50

i ピラー 214 とコンタクトを形成する。絶縁層 216 は、SOG (スピンオングラス) または CVD (化学気相堆積) 法によって形成され得る。第 2 金属電極 220 は基板層 222 に接しており、例えば、良好な電気的コンタクトを有する TiN / Al 金属積層であり得る。イオン注入によって形成され得て高度にドープされた n 型領域 226 は n - 基板 222 と電極 220 との間の良好な電気的コンタクトをさらに確実にする。p 型層 218 は n 型シリコン基板 222 上に形成されるので、それらは一緒にダイオードを形成する。したがって、電極 212 と 220 が外部コンタクトのために使用されれば、全体的構造は直列接続された p-n ダイオードを有する a-Si 抵抗素子を含む。図 9 は図 8 と同様な構造 310 を描いており、主要な相違は基板のタイプであって、それは p 型基板 318 であり得る。この場合、基板 318 上に n 型領域 322 が形成され、これも直列接続された p-n ダイオードを a-Si 抵抗素子に与える。

10

#### 【0039】

図 10 は a-Si 抵抗素子 400 の 1 つの例示的実施を描いており、これは多くの異なる抵抗の任意のものに a-Si 構造をプログラムするように使用される或る制御回路を含んでおり、それによって素子内のマルチビットまたはマルチレベル数の記憶を可能にする。この構造 400 は、従来の CMOS 製造プロセスで構築され得る。この構造は、a-Si 抵抗素子 402 (p-n ダイオードを備える) と、ゲートバイアス制御抵抗器として働き得る FET 404 とを組合せる。a-Si 素子 402 は、銀または他の適当な金属であり得る頂部電極の下の絶縁層 416 内に埋め込まれた a-Si ナノピラー 414 を含んでいる。FET 404 は、ゲート酸化物層 432 上に形成されたゲート 430 を含んでいる。ゲート 430 における印加バイアスに依存して、2 つの n 型領域 423、425 の間の抵抗が制御され得て、それによって可変抵抗器が生成される。n 型領域 425 は、高ドープ n 型領域 427 を介して第 2 金属電極 420 に接続される。構造 400 は、p 型シリコン基板 418 上に形成され得る。もう 1 つの p 型領域 421 は、素子性能を制御するために、p 型基板 418 と異なる抵抗値を有している。ポリ Si 相互接続 450 は、2 つの n 型領域 422、423 を接続することによって、a-Si 抵抗素子 402 と n 型 FET 404 とをつなげる。STI (浅いトレンチ分離) 440 は、p 型基板を介する直接的リーケ電流を抑制し得る標準的な CMOS 製造技術である。活性基板 (本体) の厚さが薄い (< 1 μm) 場合、素子 400 の構造は図 11 に示されているように簡略化され得る。これは、基本的に図 10 の素子 400 からの要素 440、450、および 423 の除去を伴う。

20

基板 518 は、p 型シリコンであり得る。n 領域 522 は p-n ダイオードの n 部分として働くとともに FET の一部としても働き、コンパクトな素子サイズとなる。

30

#### 【0040】

上述のように組込みダイオードを形成するための付加された n 型層の使用から離れて、ここに開示されている基本的な a-Si 抵抗素子は、それ自体が内在的なダイオード特性を示し得る。図 12 と 13 は、このダイオード特性の例を描いている。これらの図に示されているように、メモリ装置がそのオン状態にあるとき、電流は負バイアスではなくて正バイアスのときのみに素子を通って流れ得る。この内在的ダイオード特性は電流を制御するためにも用いられ得て、交差バーレイ中のクロストークを防止することができる。その内在的ダイオード特性は、a-Si 堆積条件を制御しあるよび / またはプログラミング電流を制御することによって得ることができる。何らかの動作理論に限定されることなく、この内在的特性のありそうな原因是、界面の内蔵電界および / または PECVD の a-Si / ポリ Si 間の浅いトラップポテンシャルであると信じられる。自然に後退させられた Ag 可動イオンは通常のプログラミングバイアスより遙かに小さなバイアスで近くの界面へ再び注入され得て、したがって小さな正の読み出し電圧で素子の状態を読み出すときに、オン状態が依然として得られる。このプロセスは、Ag 可動イオンが十分なバリアエネルギーで他の安定な位置へ後退させられる消去プロセスとは異なる。

40

#### 【0041】

上述のことは、本発明の 1 以上の例示的実施例の説明であると理解されるべきである。本発明はここで説明された特定の実施例に限定されず、特許請求の範囲のみによって規定

50

されるものである。また、上記明細書に含まれる陳述は特定の実施例に関係しており、上記で明言でもって定義された用語または語句を除けば、本発明の範囲または特許請求の範囲で用いられた用語の定義に対する限定として解釈されるべきではない。種々の他の実施例および開示された種々の変更および修正が当業者にとって明らかであろう。そのような他の全ての実施例、変更、および修正は、本願特許請求の範囲の範囲内に含まれることが意図されている。

## 【0042】

この明細書および特許請求の範囲において用いられている用語「例えば」、「実例として」、「そのような」、「など」、および動詞「含む」、「有する」、「含有する」、その他の動詞は、1以上の要素または他の項目の列挙に関して使用されるとき、それぞれ開かれたものとして解釈され、その列挙は他の付加的な要素または項目を排除するものとして解釈されるべきでないことを意味している。他の用語は、それらが異なる解釈を必要とする文脈で用いられない限り、それらの最も広い合理的な意味を用いて解釈されるべきである。

10

【図1a】

Figure 1(a)

【図1c】

Figure 1(c)

【図 1 d】

【図 1 e】

【図 2 a】

【図 2 c】

【図 2 b】

【図 2 d】

Figure 2(d)

【図 2 e】

Figure 2(e)

【図 3 a】

Figure 3(a)

【図 3 b】

Figure 3(b)

【図 3 d】

Figure 3(d)

【図 3 c】

Figure 3(c)

【図3e】

Figure 3(e)

【図4b】

Figure 4(b)

【図5】

デコード回路

Figure 5

【図4a】

Figure 4(a)

【図6】

Figure 6

【図8】

Figure 8

【図9】

Figure 9

【図7】

Figure 7

【図10】

Figure 10

【図 1 1】

【図 1 3】

Figure 11

Figure 13

【図 1 2】

Figure 12

【図 1 b】

Figure 1(b)

---

フロントページの続き

(72)発明者 ルー , ウェイ

アメリカ合衆国、48103 ミシガン州、アナーバー、セッジウッド・レーン、344

(72)発明者 ジョ , ソン・ヒョン

アメリカ合衆国、48105 ミシガン州、アナーバー、グリーンブライア・ブルバード、37

45、アパートメント・214ビィ

(72)発明者 キム , クク・ファン

アメリカ合衆国、48105 ミシガン州、アナーバー、グリーンブライア・ブルバード、35

54、アパートメント・432ビィ

審査官 小山 満

(56)参考文献 米国特許出願公開第2004/0026682(US, A1)

特表2005-506703(JP, A)

特開2007-281208(JP, A)

特開2006-032951(JP, A)

特開昭58-090790(JP, A)

特開2007-328857(JP, A)

特開2007-067408(JP, A)

特開2004-006777(JP, A)

国際公開第2008/060543(WO, A1)

国際公開第2008/058264(WO, A2)

(58)調査した分野(Int.Cl., DB名)

H01L 27/105

G11C 13/00

H01L 27/10

H01L 45/00

H01L 49/00