(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4717780号

(P4717780)

(45) 発行日 平成23年7月6日(2011.7.6)

(24) 登録日 平成23年4月8日(2011.4.8)

(51) Int.Cl.

H03M 7/40 (2006.01)

H04N 7/30 (2006.01)

F 1

H03M 7/40

H04N 7/133

Z

請求項の数 5 (全 18 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2006-298214 (P2006-298214)  |

| (22) 出願日  | 平成18年11月1日 (2006.11.1)        |

| (65) 公開番号 | 特開2008-118307 (P2008-118307A) |

| (43) 公開日  | 平成20年5月22日 (2008.5.22)        |

| 審査請求日     | 平成21年10月28日 (2009.10.28)      |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (72) 発明者  | 野澤 慎吾<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

最終頁に続く

(54) 【発明の名称】 符号化装置及びその制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

符号化対象の2値シンボルを順に入力し、0以上1未満の小数点以下の値を示す2進データを符号化データとして生成し、生成した符号化データを出力する算術符号化を用いた符号化装置であって、

2値シンボルを入力する度に、有限精度で表現される数直線上の区間を、優勢シンボルと劣勢シンボルの発生確率の比に従って2分割すると共に、入力した2値シンボルの値に従って、分割した一方の区間を選択することを繰り返す区間分割/選択手段と、

該区間分割/選択手段で選択された選択区間の長さが、予め設定された区間長を下回る場合に、前記選択区間の長さを拡大するための正規化を行なう正規化手段と、

該正規化手段の正規化対象の前記選択区間の上端と下端の値を判定する上下端判定手段と、

前記正規化手段による前記選択区間の正規化を行なう際に、前記上下端判定手段で判定された上端と下端の値に応じて、符号化データのビットの値の決定と出力、又は、出力すべきビットの保留個数の増加を行なう処理手段とを備え、

前記処理手段は、

前記正規化対象となる前記選択区間に、注目する小数の桁を決定するための閾値が存在するか否かを判定する判定手段と、

該判定手段で、前記選択区間に前記閾値が存在すると判定した場合、保留ビット数を1つ増加させる保留ビット増加手段と、

前記判定手段で、前記選択区間外に前記閾値が存在すると判定した場合、前記選択区間と前記閾値との相対位置に基づいて決定される1ビットのデータを出力し、保留ビット数の数分のビットのデータを決定し、出力すると共に、保留ビット数をゼロクリアする符号ビット出力手段とを含む

ことを特徴とする符号化装置。

#### 【請求項2】

更に、画像データを入力する画像データ入力手段と、

入力した画像データを周波数変換する周波数変換手段と、

周波数変換して得られた係数データを量子化する量子化手段と、

該量子化手段による量子化後の係数データを2値化し、前記2値シンボルとして出力する2値化手段と

を備えることを特徴とする請求項1に記載の符号化装置。

#### 【請求項3】

符号化対象の2値シンボルを順に入力し、0以上1未満の小数点以下の値を示す2進データを符号化データとして生成し、生成した符号化データを出力する算術符号化を用いた符号化装置の制御方法であって、

2値シンボルを入力する度に、有限精度で表現される数直線上の区間を、優勢シンボルと劣勢シンボルの発生確率の比に従って2分割すると共に、入力した2値シンボルの値に従って、分割した一方の区間を選択することを繰り返す区間分割／選択工程と、

該区間分割／選択工程で選択された選択区間の長さが、予め設定された区間長を下回る場合に、前記選択区間の長さを拡大するための正規化を行なう正規化工程と、

該正規化工程による正規化対象の前記選択区間の上端と下端の値を判定する上下端判定工程と、

前記正規化工程による前記選択区間の正規化を行なう際に、前記上下端判定工程で判定された上端と下端の値に応じて、符号化データのビットの値の決定と出力、又は、出力すべきビットの保留個数の増加を行なう処理工程とを備え、

前記処理工程は、

前記正規化対象となる前記選択区間に内に、注目する小数の桁を決定するための閾値が存在するか否かを判定する判定工程と、

該判定工程で、前記選択区間に内に前記閾値が存在すると判定した場合、保留ビット数を1つ増加させる保留ビット増加工程と、

前記判定工程で、前記選択区間に外に前記閾値が存在すると判定した場合、前記選択区間と前記閾値との相対位置に基づいて決定される1ビットのデータを出力し、保留ビット数の数分のビットのデータを決定し、出力すると共に、保留ビット数をゼロクリアする符号ビット出力工程とを含む

ことを特徴とする符号化装置の制御方法。

#### 【請求項4】

コンピュータが読み実行することで、前記コンピュータを、請求項1又は2に記載の各手段として機能させることを特徴とするコンピュータプログラム。

#### 【請求項5】

請求項4に記載のコンピュータプログラムを格納したことを特徴とするコンピュータ可読記憶媒体。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、画像データ等のデジタル情報から生成された2値シンボル列を算術符号化する技術に関するものである。

#### 【背景技術】

#### 【0002】

近年、デジタル信号処理技術の進歩により、動画像や静止画像、音声等、大量のデジタ

10

20

30

40

50

ル情報を高能率符号化し、小型記録媒体への記録や通信媒体による伝送を行うことが可能になっている。このような技術を応用し、テレビ放送やビデオカメラの映像をストリームに変換できる映像符号化装置の開発が行われている。動画像の映像符号化方法の中では、とりわけ I T U - T が策定した規格 H . 2 6 4 (別名 M P E G 4 P a r t 1 0 / A V C ) が注目されている。昨今における高能率符号化の圧縮効果は、エントロピー符号化によるものが大きく、特に効率の高いエントロピー符号化方法として算術符号化が挙げられ、上記の H . 2 6 4 においても採用されている。

#### 【 0 0 0 3 】

H . 2 6 4 では Context - based Adaptive Binary Arithmetic Coding と呼ばれる算術符号化 (以下、 C A B A C と称す) と、 Context - based Adaptive Variable length Coding と呼ばれる可変長符号化 (以下、 C A V L C と称す) とが採用されている。10

#### 【 0 0 0 4 】

前記 C A B A C 及び C A V L C に着目した先行例として、特許文献 1 が提案されている。この特許文献 1 の「画像情報符号化方法及び画像情報復号方法」には、 C A B A C への入出力データ量を制限し、復号化器の処理時間を保証することを目的とした発明が開示されている。

#### 【特許文献 1】特開 2 0 0 4 1 3 5 2 5 1 号公報

##### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【 0 0 0 5 】

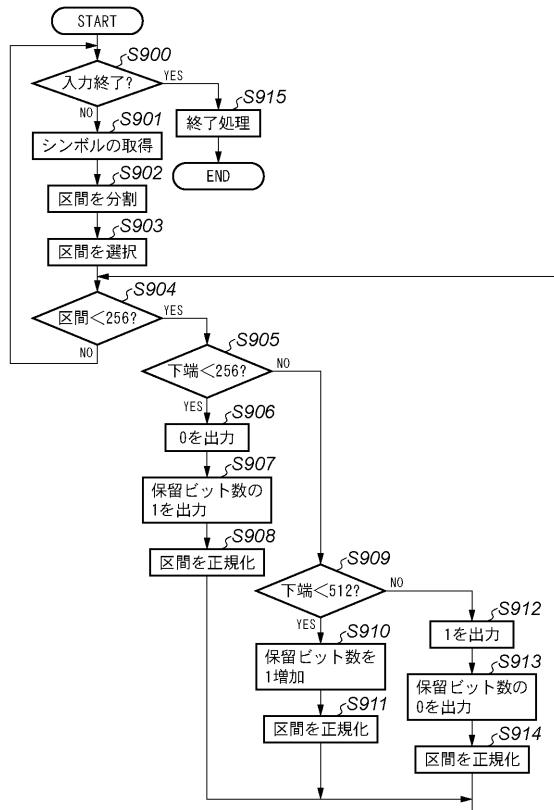

図 5 は従来の算術符号化方法の処理手順を示すフローチャートである。なお、この処理手順は I T U - T H . 2 6 4 規格書により定められており、公知のものである。 H . 2 6 4 における算術符号化、すなわち C A B A C は、 2 値シンボルの入力に対応している。20

#### 【 0 0 0 6 】

図 5 においてステップ S 9 0 0 でシンボルの入力が終了したか否かを判定し、未完であると判断した場合にはステップ S 9 0 1 にてシンボルを入力する。ここで入力されるシンボルとは 0 または 1 の 2 値シンボルである。次にステップ S 9 0 2 は区間を分割する。区間とは、 0 から 1 0 2 3 までの整数領域内で下端と長さによって表現される。区間の分割とは、 2 値シンボルの発生確率の比により、区間を二つに分けることである。例えば、シンボル “ 0 ” の発生確率が 7 5 % で、シンボル “ 1 ” の発生確率が 2 5 % の場合、区間は 7 5 : 2 5 の比で分割する (この場合、シンボル “ 0 ” を優勢シンボル、シンボル “ 1 ” を劣勢シンボルと呼ぶ)。続くステップ S 9 0 3 は、前記入力シンボルに従って、この分割された区間のいずれか一方を選択する。30

#### 【 0 0 0 7 】

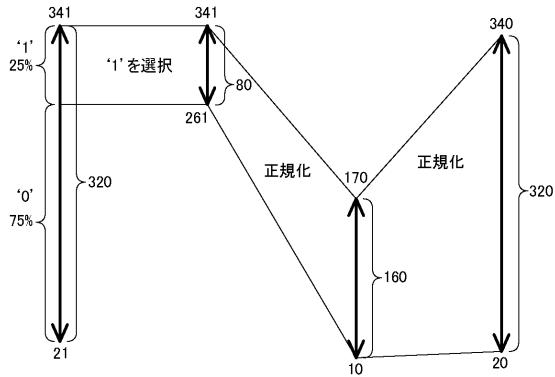

例えば、図 6 のように、現在の区間が下端の値が 2 1 、長さ 3 2 0 で表されているとする。 0 と 1 の発生確率が 7 5 % と 2 5 % の場合とする。今、入力したシンボルが “ 1 ” であるとき、“ 1 ” の区間が選択される。この結果、新たな下端は 2 6 1 、長さは 8 0 となる。

#### 【 0 0 0 8 】

次にステップ S 9 0 4 では、新たな区間の長さが 2 5 6 未満であるか否かを判定する。40 区間の長さが 2 5 6 以上の場合には、ステップ S 9 0 0 へと戻る。また、図 6 で説明した例のように区間の長さ 8 0 となり、 2 5 6 を下回る場合は、ここでステップ S 9 0 5 へ分岐する。

#### 【 0 0 0 9 】

ステップ S 9 0 5 では、区間の下端の値が 2 5 6 未満であるか否かを判定する。区間の下端が 2 5 6 未満の場合はステップ S 9 0 6 へ分岐し、符号列として “ 0 ” を出力し、ステップ S 9 0 7 は後述する保留ビット数に相当する個数の “ 1 ” を符号列として出力する。また、保留ビット数はここでゼロにリセットされる。ステップ S 9 0 8 は、区間の正規化を行う。正規化とは、 2 5 6 未満になった区間の長さを拡大し、以降の処理の精度を確保する処理である。このステップ S 9 0 8 では、下端の値と区間の長さをそれぞれ 2 倍に50

する。

#### 【0010】

ステップS905において、下端が256以上であると判定した場合、処理はステップS909に分岐し、区間の下端が512未満か否かを判定する。区間の下端が512未満の場合にはステップS910へ、512以上の場合にはステップS912へ分岐する。

#### 【0011】

ステップS912では、符号列として“1”を出力し、ステップS913では後述する保留ビット数に相当する個数の“0”を続く符号列として出力する。保留ビット数はここでもゼロにリセットされる。ステップS914では、区間の正規化を行う。このステップによる正規化では、下端から512を引いて2倍した値を新たな下端とし、また、区間の長さを2倍する。10

#### 【0012】

また、ステップS909において、下端が512を下回る場合はステップS910へ分岐し、保留ビット数を1つ増加させる。続いてステップS911では、区間の正規化を行う。このステップS911による正規化は、下端から256を引き2倍、区間も2倍する。例えば図6の例では、下端が10になり( $= (261 - 256) \times 2$ )、区間の長さは160( $= 80 \times 2$ )。また、保留ビットも“1”に増加する。これら正規化処理の各ステップの後、再度ステップS904へ戻って、区間の長さが256以上になるまで、同様に正規化処理を繰り返す。

#### 【0013】

例えば図6の例では、正規化後の区間の長さは160なので、再度ステップS904からステップS905へ進む。下端が10なので、ステップS906へと進み、“0”を出力、先ほど保留ビット数を1に増加しているので、1個の“1”を出力する(ステップS907)。すなわち符号列“01”が出力される。さらに正規化のステップS908により、下端を2倍の20、区間の長さも2倍の320とする。ここで区間の長さは256以上となるので、ステップS904からS900へと戻る。このステップS900により入力シンボルの終了を検知し、ステップS915の終了処理ステップへ分岐するまで上記処理を繰り返す。20

#### 【0014】

本発明者は、以上の従来の算術符号化方法には、2つの問題点があると考えた。第1には、ステップS904からS914までのループにより、ひとつの入力シンボルを処理するためのステップ数が非常に多いことである。これは、ソフトウェアによる処理時間の増大や、ハードウェアによる回路規模を増大の要因となる。第2には、ステップS910における、保留ビット数の増加が繰り返されると、その値の保持に必要なメモリが多くなり、更に保留ビットの解消処理であるステップS907、S913の処理回数も増大する点である。30

#### 【0015】

本発明はかかる問題に鑑みなされたものであり、算術符号化をハードウェアに適用するのであれば、回路を簡略化できて消費電力を少なくすることを可能にし、ソフトウェアに適用するのであれば、処理の簡略化に伴うメモリ消費量の削減と高速処理を可能ならしめる技術を提供することにある。40

#### 【課題を解決するための手段】

#### 【0016】

かかる課題を解決するため、例えば第1の発明の符号化装置は以下の構成を備える。すなわち、

符号化対象の2値シンボルを順に入力し、0以上1未満の小数点以下の値を示す2進データを符号化データとして生成し、生成した符号化データを出力する算術符号化を用いた符号化装置であって、

2値シンボルを入力する度に、有限精度で表現される数直線上の区間を、優勢シンボルと劣勢シンボルの発生確率の比に従って2分割すると共に、入力した2値シンボルの値に50

従って、分割した一方の区間を選択することを繰り返す区間分割／選択手段と、

該区間分割／選択手段で選択された選択区間の長さが、予め設定された区間長を下回る場合に、前記選択区間の長さを拡大するための正規化を行なう正規化手段と、

該正規化手段の正規化対象の前記選択区間の上端と下端の値を判定する上下端判定手段と、

前記正規化手段による前記選択区間の正規化を行なう際に、前記上下端判定手段で判定された上端と下端の値に応じて、符号化データのビットの値の決定と出力、又は、出力すべきビットの保留個数の増加を行なう処理手段とを備え、

前記処理手段は、

前記正規化対象となる前記選択区間に内に、注目する小数の桁を決定するための閾値が存在するか否かを判定する判定手段と、

該判定手段で、前記選択区間に内に前記閾値が存在すると判定した場合、保留ビット数を1つ増加させる保留ビット増加手段と、

前記判定手段で、前記選択区間に外に前記閾値が存在すると判定した場合、前記選択区間と前記閾値との相対位置に基づいて決定される1ビットのデータを出力し、保留ビット数の数分のビットのデータを決定し、出力すると共に、保留ビット数をゼロクリアする符号ビット出力手段とを含むことを特徴とする。

#### 【発明の効果】

#### 【0018】

第1の発明によれば、保留ビット数を増加する処理の回数がこれまでの技術よりも少なくてできるので、ハードウェアに適用するのであれば、回路を簡略化できて消費電力を少なくすることを可能になる。また、ソフトウェアに適用するのであれば、処理の簡略化に伴うメモリ消費量の削減と処理を更に高速なものとすることが可能になる。

#### 【発明を実施するための最良の形態】

#### 【0020】

以下、添付図面に従って本発明に係る実施形態を詳細に説明する。

#### 【0021】

##### <第1の実施形態>

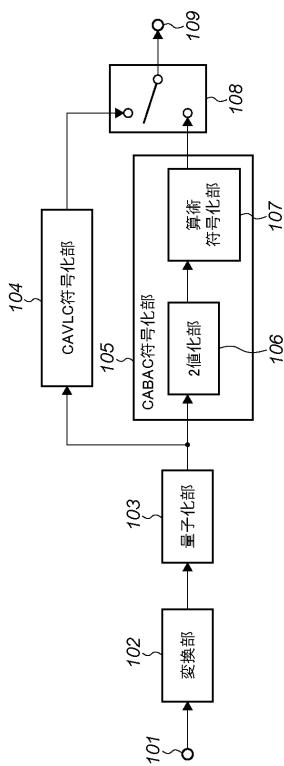

図7は、本実施形態による装置の構成例を示すブロック図である。101は映像入力部、102は変換部、103は量子化部、104はCAVL C符号化部、105はCABA C符号化部、106は2値化部、107は算術符号化部、108は選択部、109はストリーム出力部である。本実施形態における符号化装置は、H.264規格に基づき、以下の手順で高能率符号化処理を行う。なお、本符号化装置は撮像装置（ビデオカメラ）や映像記録再生装置に適用可能な構成である。

#### 【0022】

映像入力部101から入力されるデジタル映像信号は、変換部102に供給される。変換部102は、入力したデジタル映像信号で表わされる画像データを、例えば $16 \times 16$ 画素で構成されるブロックに分割し、各ブロック毎に係数列へ変換する。この変換部102は、動き予測処理、動き補償処理及び直交変換処理（周波数変換）などにより、ブロックにおける情報量の視覚的な冗長性を削減する。

#### 【0023】

変換部102の変換処理で得られた係数列は、量子化部103へ供給される。量子化部103は、入力した係数列を、予め設定された量子化パラメータに従って量子化する。

#### 【0024】

この量子化部103における量子化パラメータの大小に応じて、係数列の情報量は削減される。量子化された係数列は、CAVL C符号化部104とCABA C符号化部105に供給される。CAVL C符号化部104については、本発明に直接関係が無いので詳細な説明は省略し、CABA C符号化部105について説明する。

#### 【0025】

CABA C符号化部105内の2値化部106は、入力した係数列を0、1の2値シン

10

20

30

40

50

ボル列へ変換する。

**【0026】**

算術符号化部107は、2値化部106で2値化された2値シンボル列の順次を入力し、後述する手順に従った処理を行なうことで、圧縮した算術符号化データ列を生成し出力する。この時、2値化部106はテーブルによって各係数を2値シンボル列へ1対1に変換できるので、処理は1係数単位に実行することができる。一方、算術符号化部107は、2値シンボル1つずつ処理を行う必要がある。

**【0027】**

C A V L C 符号化部104によって発生した符号列と、算術符号化が行われたC A B A C 符号化部105によって発生した符号列は、それぞれ選択部108に供給され、選択部 108 によっていずれか一方の符号列（ストリーム）が出力として選択される。その後、選択されたストリームがストリーム出力部109より出力される。

**【0028】**

本実施形態における特徴は、図7における算術符号化部107にある。そこで、この算術符号化部107を更に詳しく説明する。

**【0029】**

算術符号化は、既に説明したように、入力されるシンボルの値に応じて区間の分割、選択を繰り返し、0以上の1未満の小数点の値を符号化結果とするものである。0以上の1未満の小数点の値は、「0 . x x x ... (xは0または1)」の形式となるので、整数部分と小数点を除いた「x x x ...」が符号化データとなる。小数点第1位のビットは、十進数の“0 . 5”を示し、小数点第2位のビットは“0 . 25”を示す。つまり、小数点第i桁のビットで表わされる値は、小数点第i-1桁のビットで表わされる値の半分と言える。例えば、十進数の“0 . 75”は2進数では“0 . 11”と表現できる。

**【0030】**

また、電子回路、又は、コンピュータプログラムで処理するわけであるから、区間の下端、上端、区間長さは限られたビット数のレジスタで表現しなければならない。ところが、各小数点以下の桁のビットを求めていくと、それに応じて区間の長さは次第に狭くなっていく。つまり、区間の下端と上端を定義するレジスタの値の差は次第に小さくなっている、シンボルの発生確率の比で区間を分割する際の精度が低くなっていく。それゆえ、使用するビット数を有効に機能するようにするために、区間の長さある閾値未満となったとき、その区間の長さを拡大する処理が必要になる。この区間の長さの拡大処理を正規化と言う。

**【0031】**

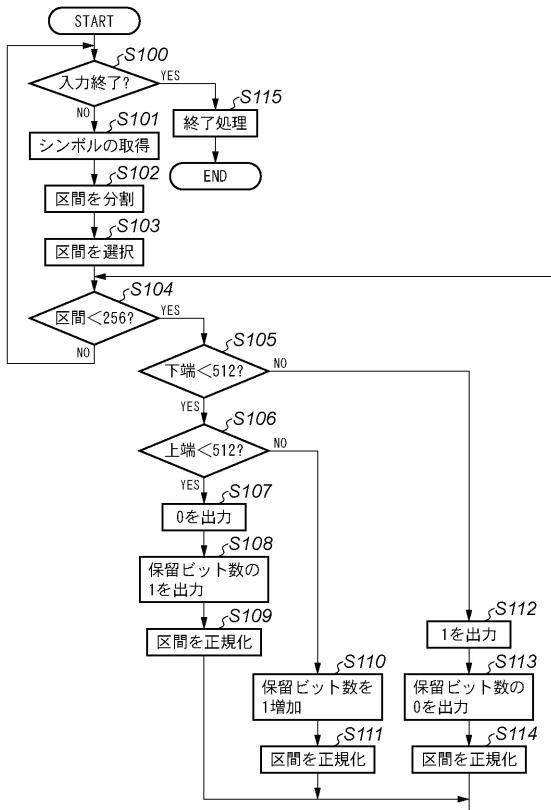

図1は、本実施形態における算術符号化部107における算術符号化処理手順を示すフローチャートである。以下、このフローチャートに従って算術符号化部107の処理内容を説明する。

**【0032】**

先ず、ステップS100では、符号化すべきシンボルの入力が終了したか否かを判断する。この判断は、入力したシンボルの個数を計数し、その個数が予め定められた符号化単位であるシンボル数になったか否かで判断すればよい。

**【0033】**

符号化処理が未完であると判断した場合には、ステップS101に処理を進め、シンボルを1つ入力する。本実施形態での符号化対象のシンボルは、2値化部106から出力される0または1の2値シンボルである。

**【0034】**

次にステップS102では、区間を分割する。符号化の開始時の区間は0乃至1023の範囲である。すなわち、下端が0、区間の長さが1024であり、下端を0、上端の1023を整数の“1”と見立て、その間が小数点以下を表わすものとして定義する。この場合、下端と上端はそれぞれ10ビットのレジスタで記憶保持すれば良いことになる。

**【0035】**

10

20

30

40

50

ステップS102の区間の分割処理とは、入力した2値シンボルの発生確率の比により、区間を2つに分けることである。例えば、0の発生確率が75%で、1の発生確率が25%の場合、区間は75：25の比で分割される。

#### 【0036】

続くステップS103では、入力シンボルに従って、この分割された区間のいずれか一方を選択する。例えば、図6のように、現在の区間の下端が“21”、その区間の長さが“320”であり、シンボル0と1の発生確率が75%、25%であるとする。今、入力したシンボルが“1”であった場合、1の区間が選択され、新たな下端は“261”、その区間の長さは“80”となる。

#### 【0037】

次にステップS104は、新たな区間の長さを閾値“256”と比較する。区間の長さが“256”以上の場合は、ステップS100へ戻る。

#### 【0038】

また、図6に示すように、区間の長さが“80”となって、“256”を下回る場合、処理はステップS105に分岐する。

#### 【0039】

ステップS105では、区間の下端の値を判定する。下端の値が“512”に満たない場合、処理はステップS106に分岐する。このステップS106では、区間の上端の値が“512”未満であるか否かを判定する。

#### 【0040】

ステップS106にて、上端の値が“512”未満であると判定した場合、ステップS107に処理を進める。

#### 【0041】

ステップS107に処理を進むのは、選択した区間の上下端の値が共に“512”以下の場合である。従って、ステップS107では、“0”を符号化後のビットとして出力する。そして、続くステップS108では、その時点での保留ビット数で示される数だけ“1”を出力した後、保留ビット数を“0”にリセットする。なお、ステップS108に処理が進んだ直後の保留ビット数が“0”的場合には、何もしない。そして、ステップS109にて、区間の正規化を行う。このステップS109での正規化処理とは、“256”未満となった区間を拡大し、以降の符号化処理の精度を確保する処理である。このステップS109では、下端の値を2倍にした値を更新後の区間の下端の値とする。また、区間の長さを2倍にし、その結果を更新後の区間の長さとする。そして、ステップS104に戻る。

#### 【0042】

一方、ステップS105にて、選択区間の下端の値が“512”以上であると判定した場合、処理はステップS112に分岐する。すなわち、現在の区間の上端及び下端の値が共に、“512”以上である場合である。ステップS112では、注目桁の値として“1”を符号化後のビットとして出力する。続くステップS113では、保留ビット数で示される数の“0”を出力した後、保留ビット数を“0”にリセットする。そして、ステップS114にて、区間の正規化を行う。このステップS114での正規化処理とは、“256”未満となった区間を拡大し、以降の符号化処理の精度を確保する処理である。このステップS114では、下端の値から512を減じ、その減算結果を2倍にした値を更新後の下端の値にする。また、区間の長さを2倍した結果を、更新後の区間の長さとする。この後、処理はステップS104に戻る。

#### 【0043】

また、ステップS106にて、区間の上端の値が“512”以上であると判断した場合、処理はステップS110に進む。ステップS110に進むのは、区間の下端の値が“512”未満であり、区間の上端の値が“512”以上の場合である。つまり、注目桁のビットが“0”か、“1”かは、現時点では未定であることを示している。それ故、ステップS110にて、保留ビット数を1つ増加させる。続いて、ステップS111にて、区間

10

20

30

40

50

の正規化を行う。このステップ S 111 における正規化は、区間の下端の値から“256”を減じ、その減算結果を2倍にした値を更新後の下端の値とする。また、区間の長さを2倍にした結果を更新後の区間の長さとする処理を行なう。この後、処理はステップ S 104 に戻る。

#### 【0044】

こうして、符号化すべき全シンボルについてステップ S 100 乃至 S 114 の処理を終えると、ステップ S 115 の終了処理を行なう。この終了処理では、直前までの処理で決定された区間の上端、下端の間にあって、二進表記で都合の良い値を1つ決定し、その決定した値に従って、未出力の桁のビットを出力する処理を行なう。例えば、区間の上端の値が、区間の下端の値と等しくなったものとし（区間の長さが0になったものとし）、その際の符号化ビット及び保留ビットを出力する。

#### 【0045】

以上、本実施形態の算術符号化部 107 の処理内容を説明した。本実施形態の処理は、先に説明した図 5 の前述した従来方法よりも、保留ビット数を増加させるステップの実行回数を半減させることができになる。

#### 【0046】

例えば、図 6 の例では、区間選択により得られた新しい区間の下端の値が“261”である。従来方法では、ステップ S 905、S 909 による分岐で、保留ビット数を増加させるステップ S 910 へと進む。

#### 【0047】

これに対し、本実施形態によれば、区間の下端の値が“261”で、尚且つ、区間の上端の値が“341”（= 261 + 80）であるから、ステップ S 105、106 の分岐処理で、ステップ S 107 以降の処理を行なう。すなわち、上記の場合、本実施形態によれば、保留ビットを増加する処理は行なわない。

#### 【0048】

また、ステップ S 107 では、符号化データとしてビット“0”を出力する。この後、処理はステップ S 108 に進むが、図 6 の場合、保留ビット数がゼロのままである。従つて、このステップ S 108 は無処理となる。そして、ステップ S 109 の正規化では、現在の区間の下端の値と区間の長さをそれぞれ2倍にする。すなわち、区間の下端の値は“522”、区間の長さが“160”になる。この後、ステップ S 104 に戻るが、区間の長さ“160”は、閾値“256”未満であるので、ステップ S 104、S 105 による分岐処理を経たのち、ステップ S 112 に処理が進む。ステップ S 112 では、“1”を出力し、ステップ S 113 は無処理となる。そして、ステップ S 114 の正規化処理の結果、区間の下端の値は“20”（= (522 - 512) × 2）、区間の長さは“320”（= 160 × 2）となる。

#### 【0049】

以上により、出力される符号化データは“01”となり、区間の下端の値は“20”、区間の長さは“320”となる。ここで注目すべき点は、本実施形態の場合、保留ビットの増加処理を行なっていないにもかかわらず、図 5 に示した従来方法と同じ出力、同じ区間状態になっていることである。

#### 【0050】

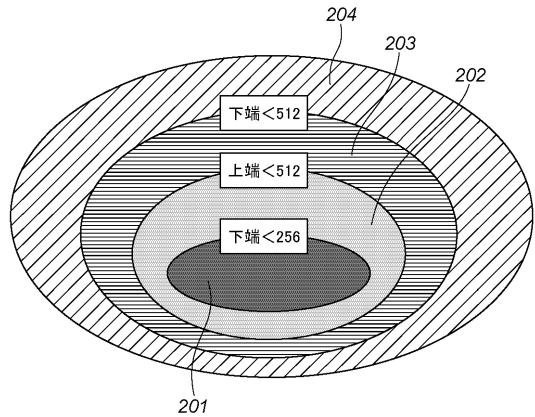

ここで、従来技術と本実施形態の処理の違いを図 2 を用いて説明する。図 2 は正規化前の区間を上端と下端の範囲で分類したベン図である。

#### 【0051】

従来方法では、区間の長さが“256”未満となり、符号化データとしてビット“0”を出力するのは、その区間が下端の値が“256”未満の領域 201 のみである。すなわち、残る領域 202、203 では保留ビットを増加させる処理を行なわざるをえない。

#### 【0052】

一方、本実施形態による方法では、区間の長さが“256”未満であるとき、区間が領域 201、202 の条件を満たすとき、符号化データとしてビット“0”を出力する。そ

10

20

30

40

50

して、保留ビットを増加させるのは、領域 203、すなわち、区間の上端の値が“512”以上であり、区間の下端の値が“512”未満の場合のみである。

#### 【0053】

このように本実施形態の如く、分類に上端を取り入れて詳細化することで、区間が本来保留する必要の無い領域 202 にあるときに、“0”を符号化データとして出力することで、保留ビット増加の処理の回数は、従来技術の半分まで減らすことが可能になる。因に、区間の下端の値が“512”以上を示す領域 204 では、符号化データのビットとして“1”を出力する。従って、区間の下端の値が“512”以上を示す領域 204 における、本実施形態の処理は、従来技術と方法と一致する。

#### 【0054】

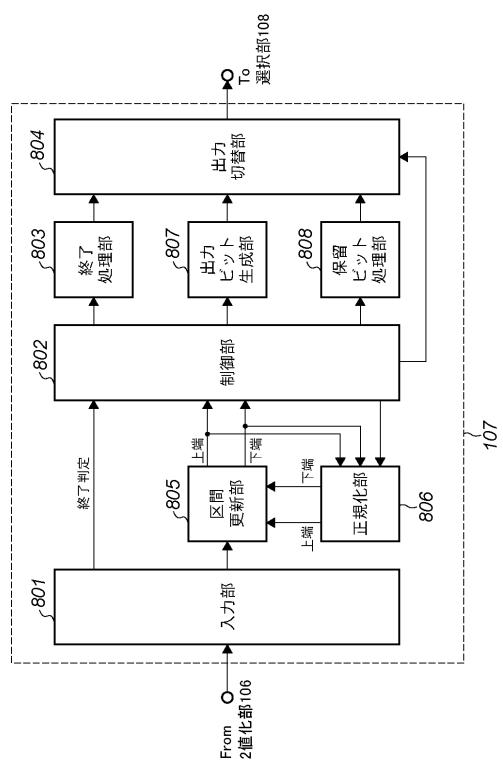

図 8 は、実施形態における算術符号化部 107 の具体的な内部のブロック構成図である。

#### 【0055】

本実施形態の算術符号化部 107 は、図示の如く、入力部 801、制御部 802、終了処理部 803、出力切替部 804、区間更新部 805、正規化部 806、出力ビット生成部 807、保留ビット処理部 808 で構成される。この構成における動作を、再び、図 1 のフローチャートと対応づけて説明する。

#### 【0056】

入力部 801 は、ステップ S101 にて、2 値化部 106 から 2 値シンボルを順次入力する。また、入力部 801 は、入力したシンボル数が符号化単位の予め設定された個数になつたことを検知すると、終了判定信号を制御部 802 に出力する。

#### 【0057】

区間更新部 805 はステップ S102 による区間の分割とステップ S103 における区間の選択を行い、選択された区間の上端と下端の値を示す信号を制御部 802 と正規化部 806 へ供給する。

#### 【0058】

制御部 802 は各ブロックから供給される信号に基づき、制御信号を各ブロックへ供給する。

#### 【0059】

終了処理部 803 は、制御部からのトリガー信号により、ステップ S115 における終了処理を行い、終了ビット列を出力切替部 804 に供給する。

#### 【0060】

出力ビット生成部 807 は制御部 802 からの制御信号に従い、“0”もしくは“1”を出力切替部 804 へ供給する。この処理は、図 1 におけるステップ S107 もしくはステップ S112 に相当する。

#### 【0061】

保留ビット処理部 808 は制御部 802 からの制御信号に従い、ステップ S108、ステップ S110、ステップ S113 における保留ビット列を出力切替部 804 へ供給する。

#### 【0062】

出力切替部 804 は制御部 802 からの制御信号に従い、終了処理部 803、出力ビット生成部 807、保留ビット処理部 808 から供給されるビット列のいずれかを選択し出力する。

#### 【0063】

正規化部 806 は制御部 802 からの制御信号と、区間更新部からの上端と下端の値を表す信号を受け取り、区間を正規化して新たな区間の上端と下端を区間更新部 805 へ供給する。この処理は、図 1 のステップ S109、S111、S114 に相当するものであるが、いずれの処理を行なうかは、制御部 802 からの制御信号によって決定される。正規化により変更された上端と下端の値は、区間更新部 805 を経由して、制御部 802 へ供給される。

10

20

30

40

50

**【0064】**

制御部802は、図1のフローチャートの分岐処理であるステップS100、S104、S105、S106の判断に依存し、これら各ブロックを制御するための信号を生成することになる。

**【0065】**

以上説明したように本実施形態によれば、2値シンボル列を符号化する際に、保留ビット数を増加する処理回数を、これまでの半分に減らすことが可能になり、尚且つ、生成される符号化データのコンパチビリティも保証することが可能になる。従って、ハードウェアによる回路規模の増大を防ぐ事が可能になる。

**【0066】**

また、符号化対象の画像データを入力する入力装置（ビデオカメラ、イメージスキャナ、或いは、非圧縮の画像データを蓄積する蓄積装置）を有し、それ以外の図7に示す各構成要素をマイクロコンピュータ等の高度な制御部と、その制御部が実行するプログラムを記憶したRAMによって構成することも勿論可能である。また、図7における算術符号化部107のみ、マイクロコンピュータとそれが実行するソフトウェアによって実現させても構わない。

**【0067】**

## &lt;第2の実施形態&gt;

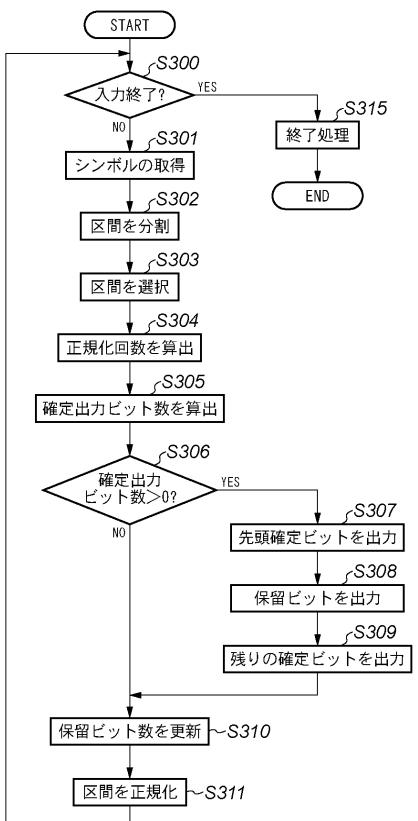

本発明に係る第2の実施形態を説明する。図3は、本第2の実施形態における算術符号化部107の処理手順を示すフローチャートである。算術符号化部107以外は、第1の実施形態と同じとし、その説明は省略する。

**【0068】**

以下、図3のフローチャートに従って、算術符号化部107の処理手順を説明する。

**【0069】**

先ず、ステップS300では、符号化すべきシンボルの入力が終了したか否かを判断する。この判断は、入力したシンボルの個数を計数し、その個数が予め定められた符号化単位であるシンボル数になったか否かで判断すればよい。

**【0070】**

符号化処理が未完であると判断した場合には、ステップS301に処理を進め、シンボルを1つ入力する。本実施形態での符号化対象のシンボルは、2値化部106から出力される0または1の2値シンボルである。

**【0071】**

次にステップS302では、区間を分割する。符号化の開始時には、区間の下端が0、区間の長さが1024である。

**【0072】**

ステップS302の区間の分割処理とは、入力した2値シンボルの発生確率の比により、区間を2つに分けることである。例えば、0の発生確率が75%で、1の発生確率が25%の場合、区間は75:25の比で分割される。続く、ステップS303では、入力シンボルに従って、この分割された区間のいずれか一方を選択する。例えば、図6のように、区間が下端21と長さ320で表されていて、シンボル“0”と“1”的発生確率が75%と25%の場合とする。この場合、入力シンボルが“1”であった場合には、1の区間が選択され、新たな区間の下端は“261”、長さは“80”となる。

**【0073】**

次にステップS304では、ステップS303で選択した新たな区間の長さによって、正規化回数を算出する。既に述べたように、正規化処理は、区間の長さが256未満の時に発生し、区間の長さを2倍にする処理である。そして、正規化処理は、区間の長さが256以上となるまで繰り返される。

**【0074】**

即ち、区間の長さと正規化回数との関係は次の通りとなる。

- ・区間の長さ128以上、256未満の場合は正規化回数は1回、

10

20

30

40

50

- ・区間の長さが 64 以上、128 未満の場合には正規化回数は 2 回、

- ・区間の長さが 32 以上、64 未満の場合には正規化回数は 3 回、

- ・区間の長さが 16 以上、32 未満の場合には正規化回数は 4 回、

- ・区間の長さが 8 以上、16 未満の場合には正規化回数は 5 回、

- ・区間の長さが 4 以上、8 未満の場合には正規化回数は 6 回。

#### 【0075】

上記を考察すると、区間の長さを 9 ビットで 2 進表現した場合、正規化回数は、最上位ビット (MSB) から最下位ビット (LSB) に向かうゼロの連続数と一致する。従って、ステップ S304 では、MSB からゼロの連続数をカウントし、そのカウントした値を正規化回数として求める。なお、正規化回数を求める方法は上記に限らない。例えば、2 を低とする区間の長さの対数を求め、その対数の小数点以下を切り捨てる。そして、切り捨てた対数を、8 から減じた値を、正規化回数としても構わない。ただし、前者の方が、単純な処理、又は、単純な回路構成で実現できる。10

#### 【0076】

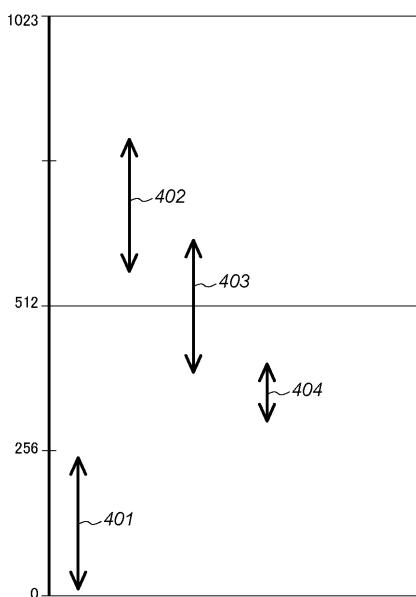

続いてステップ S305 では、確定して出力する符号ビット数を算出する。保留ビットの増加の処理が無ければ、正規化回数と確定出力ビット数は一致する。

#### 【0077】

例えば、図 4 の区間 401、402、403 はいずれも、その区間の長さが “128” 以上、“256” 未満であることを示している。従って、区間 401、402、403 に対する正規化回数は 1 回である。区間 401 は、その上端が “512” 未満であるため、“0” を符号化データのビットとして出力する。区間 402 は、その下端が “512” 以上であるため、“1” を出力する。20

#### 【0078】

一方、区間 403 は、その下端が “512” 未満であり、上端が “512” 以上であるため、保留ビットを 1 増加させるだけで、この時点での符号化データのビットの出力は行なわない。すなわち、或る区間の上端と下端の間に閾値 “512” が存在する場合には、保留ビットを “1” だけ増加させ、符号化データの出力は行なわない。

#### 【0079】

上記を更に詳しく検討すると、次のようになる。

#### 【0080】

区間の上端、下端を 10 ビットで表わすとする。或る区間の上端と下端が共に “512” 未満であるとき、上端及び下端の最上位ビット (MSB) は共に “0” となる。また、或る区間の上端と下端が共に “512” 以上であるとき、上端及び下端の MSB は共に “1” となる。そして、区間が “512” を跨ぐ、すなわち、下端 < 512 上端の場合、上端と下端の MSB は一致しない。

#### 【0081】

従って、上端と下端の MSB が一致するとき、出力ビットの 1 個が確定する。そして、上端と下端の MSB が不一致の場合、保留ビットを “1” だけ増加させれば良いことになる。複数回の正規化回数の場合も同様に考えることが出来る。

#### 【0082】

再び、図 4 に着目する。図 4 における区間 404 は、その下端が “270”、上端が “389”、区間の長さが “119” (= 389 - 270) であることを示している。

先に説明した第 1 の実施形態の手順によると、2 回の正規化回数の結果、2 ビットの符号 “01” が出力される。出力ビット数が “2” となるのは、1 回目の正規化後の区間の上端と下端が “512” を跨がず、さらに上端と下端が 2 倍された後の 2 回目の正規化後の区間も “512” を跨がないからである。別な言い方をすれば、1 回目の正規化後の区間が “256” を跨いでいなければ、2 倍される 2 回目の正規化後の区間は “512” を跨がない、と言える。すなわち、区間の上端と下端が “512” を跨がなければ出力ビット数は 1、さらに、その区間が “256” も跨がなければ出力ビット数は 2、さらに “128” も跨がなければ出力ビット数は 3 というように判定する。結局のところ、区間の上4050

端と下端を 10 ビットで二進表現したとき、両者の最上位ビットからの一致ビット数が出力ビット数に等しいことになる。ただし、出力ビット数は、許容正規化回数を超えることは無いので、許容正規化回数を上限として出力ビット数をクリップする。

#### 【 0 0 8 3 】

図 3 の説明に戻る。以上のように算出した出力ビット数が決定されるが、ステップ S 3 0 6 では、出力ビット数が “ 1 ” 以上であるか否かを判定する。出力ビット数が “ 1 ” 以上であると判定した場合には、ステップ S 3 0 7 乃至ステップ S 3 0 9 の処理を実行する。

#### 【 0 0 8 4 】

このステップ S 3 0 7 乃至 S 3 0 9 では、ビット列を符号として出力する。この時、出力されるビット列は、区間の上記の上端と下端の一致ビット列そのものである。10

#### 【 0 0 8 5 】

例えば、図 4 の区間 4 0 4 の場合、その上端は “ 389 ” であり、下端は “ 270 ” である。これを二進数で表現すると、上端は “ 0110000101 ” 、下端は “ 0100001110 ” である。従って、両者は最上位ビットから 2 ビット “ 01 ” が一致するので、一致ビット列 “ 01 ” を出力する。

#### 【 0 0 8 6 】

次にステップ S 3 1 0 では、保留ビット数の更新を行う。前記正規化回数から出力ビット数を減じた値を保留ビット数に加える。この後、ステップ S 3 1 1 において、区間の正規化を行う。下端から前記出力ビット列を除去（ゼロにする）し、前記正規化回数分だけ 2 倍にする処理を繰り返す。また、区間の長さも同様に前記正規化回数分だけ 2 倍を繰り返す。ここで 2 倍を N 回繰り返すことは、N ビットの左シフト算に置き換える同じである。20

#### 【 0 0 8 7 】

上記ステップ S 3 0 7 乃至 S 3 0 9 のビット列を出力する工程で、もし保留ビット数が 1 以上の場合には、まずステップ S 3 0 7 では出力ビット列の先頭ビットのみを出力する。そして、ステップ S 3 0 8 で該先頭ビットの反転ビットを保留ビット数分だけ出力する。そしてステップ S 3 0 9 では、残りの出力ビット列を出力する。

#### 【 0 0 8 8 】

例えば、図 4 の区間 4 0 4 となったときに、保留ビット数が仮に “ 3 ” であったとする。この場合、出力ビット列 “ 01 ” の先頭ビット “ 0 ” をまず出力し、続いて “ 0 ” を反転した “ 1 ” を保留ビット数分の 3 個、すなわち “ 111 ” を出力する。そして、残りのビット列 “ 1 ” (“ 01 ” の 2 ビット目) をステップ S 3 0 9 で出力する。よって、このステップで出力される符号化データは “ 01111 ” となる。なお、保留ビット数はここでゼロにリセットされる。30

#### 【 0 0 8 9 】

以下、ステップ S 3 0 0 に戻り、入力シンボルの終了を判定するまで、ステップ S 3 0 1 乃至 S 3 1 1 の処理を繰り返し、入力シンボルの終了を判定した場合にはステップ S 3 1 5 の終了処理を行なう。

#### 【 0 0 9 0 】

図 3 のフローチャートからもわかるように、正規化回数や出力ビットの数を算出して、一括して処理しているため、従来の方法に比べ、ループ構造が格段に少なくなっていることがわかる。また、1 入力シンボルに対して 1 回のループで処理できることもわかる。

#### 【 0 0 9 1 】

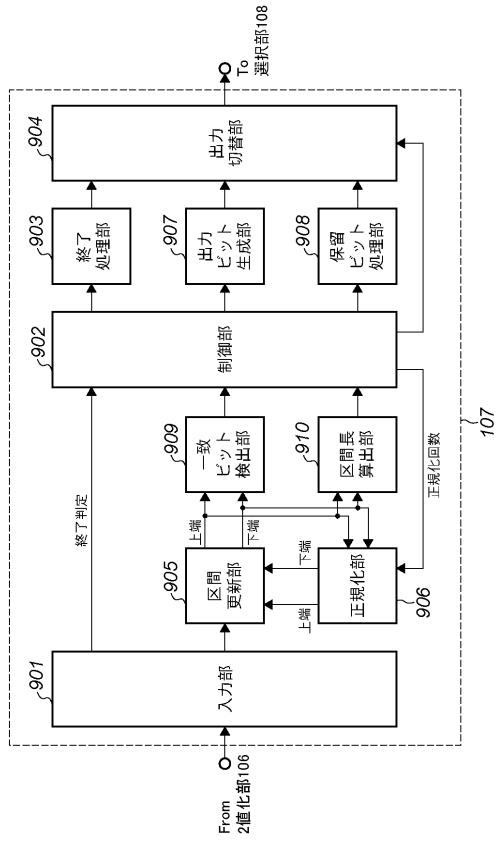

図 9 は、上述した処理を行なうための、本第 2 の実施形態における算術符号化部 1 0 7 の内部ブロック構成図である。本第 2 の実施形態の算術符号化部 1 0 7 は入力部 9 0 1 、制御部 9 0 2 、終了処理部 9 0 3 、出力切替部 9 0 4 、区間更新部 9 0 5 、正規化部 9 0 6 、出力ビット生成部 9 0 7 、保留ビット処理部 9 0 8 、一致ビット検出部 9 0 9 、区間長算出部 9 1 0 を備える。以下、各処理部の動作を、図 3 のフローチャートに対応付けて説明する。50

**【0092】**

入力部901はステップS301にて、2値化部106からの2値シンボルを順次入力する。また、入力部801は、入力したシンボル数が、符号化単位である予め設定された個数になったことを検出すると、終了判定信号を制御部902に出力する。

**【0093】**

区間更新部905は、ステップS302の区間の分割処理と、ステップS303の区間の選択処理を行なう。そして、区間更新部905は、選択された区間の上端と下端の値を示す信号を一致ビット検出部909、区間長算出部910、正規化部906へ供給する。

**【0094】**

一致ビット検出部909は、区間更新部905から供給される上端と下端の値を比較し、2進表現における最上位ビットから連続して一致するビット数をカウントする。この処理は、ステップS305に相当し、一致したビットの数を制御部902へ供給する。10

**【0095】**

区間長算出部910は、区間更新部905から供給される上端の値から下端の値を減じて区間の長さを算出する処理（ステップS304に相当）を行ない、その区間の長さを示す信号を制御部902に供給する。

**【0096】**

制御部902は、区間長算出部910より入力した区間の長さから必要な正規化の回数を算出し、正規化回数を正規化部906へ供給する。

**【0097】**

正規化部906は制御部902から供給される正規化回数に従い、区間更新部から供給された上端と下端の値を正規化して新たな区間の上端と下端を区間更新部905へ供給する。この処理はステップS311に相当し、ループ処理することなく单一のステップで、前記回数分の正規化を処理する。20

**【0098】**

また、制御部902は各ブロックから供給される信号に基づき、制御信号を各ブロックへ供給する。

**【0099】**

制御部902は、入力部901からの終了判定信号を受信した場合に、終了処理部903にトリガ信号を出力する。終了処理部903は、制御部902からのトリガ信号により、ステップS315に相当する終了処理を行ない、終了ビット列を出力切替部904に出力する。30

**【0100】**

出力ビット生成部907は制御部902からの制御信号に従い、“0”もしくは“1”を出力切替部904へ供給する。この処理は、図3のフローチャートにおけるステップS307およびステップS309に相当し、一致ビット検出部909が検出した一致ビット数に相当する個数の出力ビットを生成する。

**【0101】**

保留ビット処理部908は制御部902からの制御信号に従い、ステップS308、ステップS310における保留ビット列を出力切替部904へ供給する。40

**【0102】**

出力切替部904は制御部902からの制御信号に従い、終了処理部903、出力ビット生成部907、保留ビット処理部908から供給されるビット列のいずれかを選択し出力する。

**【0103】**

なお、制御部902は、図3のフローチャートのステップS300及びS306に相当する分岐判定処理に相当する処理を行ない、各ブロックの制御信号を発行することになる。

**【0104】**

以上説明したように本第2の実施形態によれば、従来と比べ、算術符号化の処理のルー50

フ処理を削減し、また、保留ビット数の増加を抑制することが可能になる。その結果、より少ない回路規模や消費電力で処理可能な算術符号化装置を提供できる。

#### 【0105】

また、符号化対象の画像データを入力する入力装置（ビデオカメラ、イメージスキャナやビデオカメラ等の撮像装置、或いは、非圧縮の画像データを蓄積する蓄積装置）を有し、それ以外の図7に示す各構成要素をマイクロコンピュータ等の高度な制御部と、その制御部が実行するプログラムを記憶したRAMによって構成することも勿論可能である。また、図7における算術符号化部107のみを、マイクロコンピュータとそれが実行するソフトウェアを格納するメモリによって実現させても構わない。

#### 【0106】

また、第1、第2の実施形態では、撮像装置（ビデオカメラ）や映像記録再生装置に適用した例を説明したが、符号化対象情報として2値シンボルを生成する構成を備える装置であれば適用できるので、上記実施形態によって本発明が限定されるものではない。

#### 【0107】

また、通常、ソフトウェア、すなわち、コンピュータプログラムは、CD-ROM等のコンピュータ可読記憶媒体に格納されている。そして、そのコンピュータ可読記憶媒体を、コンピュータの読み取り装置（例えばCD-ROMドライブ）にセットし、システムにコピーもしくはインストールすることで、そのコンピュータが該当するコンピュータプログラムを実行可能にことができる。従って、かかるコンピュータ可読記憶媒体も本発明の範疇に入るるのは明らかである。

#### 【図面の簡単な説明】

#### 【0108】

【図1】第1の実施形態における算術符号化部の処理手順を示すフローチャートである。

【図2】本第1の実施形態における算術符号化処理中の区間の分類を示すベン図である。

【図3】第2の実施形態における算術符号化部の処理手順を示すフローチャートである。

【図4】第2の実施形態における算術符号化における区間の例を示す図である。

【図5】従来の算術符号化処理手順を示すフローチャートである。

【図6】正規化処理を説明するための図である。

【図7】実施形態が適用する装置における符号化部のブロック構成図である。

【図8】第1の実施形態における算術符号化部の具体的なブロック構成図である。

【図9】第2の実施形態における算術符号化部の具体的なブロック構成図である。

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

審査官 北村 智彦

(56)参考文献 特開2004-135251(JP,A)

特開2005-252374(JP,A)

特表2005-525018(JP,A)

国際公開第2008/001012(WO,A1)

特開平10-032496(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M3/00-11/00

H04N 7/30