(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2010-532578

(P2010-532578A)

(43) 公表日 平成22年10月7日(2010.10.7)

| (51) Int.Cl.           | F 1             | テーマコード (参考) |

|------------------------|-----------------|-------------|

| HO1L 21/8238 (2006.01) | HO1L 27/08 321D | 4M104       |

| HO1L 27/092 (2006.01)  | HO1L 27/08 331E | 5FO48       |

| HO1L 27/08 (2006.01)   | HO1L 29/78 613A | 5F110       |

| HO1L 29/786 (2006.01)  | HO1L 29/78 618B |             |

| HO1L 21/28 (2006.01)   | HO1L 21/28 301R |             |

審査請求 未請求 予備審査請求 未請求 (全 17 頁) 最終頁に続く

|               |                              |          |                                                                                                     |

|---------------|------------------------------|----------|-----------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2010-514909 (P2010-514909) | (71) 出願人 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 78729 テキサス州<br>オースチン ウエスト パーマー レー<br>ン 7700 |

| (86) (22) 出願日 | 平成20年5月20日 (2008.5.20)       | (74) 代理人 | 100142907                                                                                           |

| (85) 翻訳文提出日   | 平成21年11月30日 (2009.11.30)     | (74) 代理人 | 弁理士 本田 淳                                                                                            |

| (86) 國際出願番号   | PCT/US2008/064192            | (74) 代理人 | 100149641<br>弁理士 池上 美穂                                                                              |

| (87) 國際公開番号   | W02009/005903                | (72) 発明者 | カーブ、ガウリ ブイ.<br>アメリカ合衆国 12524 ニューヨー<br>ク州 フィッシュキル ストーニー ブル<br>ック ロード 117                             |

| (87) 國際公開日    | 平成21年1月8日 (2009.1.8)         |          |                                                                                                     |

| (31) 優先権主張番号  | 11/771,721                   |          |                                                                                                     |

| (32) 優先日      | 平成19年6月29日 (2007.6.29)       |          |                                                                                                     |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                     |

最終頁に続く

(54) 【発明の名称】デュアルメタルゲート構造の形成方法

## (57) 【要約】

半導体構造(10)の形成方法は、第1および第2ウェル領域(16、18)を含む半導体層上にチャネル領域層(40)を形成すること、チャネル領域層上に保護層(80)を形成すること、第1ウェル領域上に第1ゲート誘電体層(26)を形成すること、第1ゲート誘電体上に第1メタルゲート電極層(28)を形成すること、保護層を除去すること、チャネル領域層上に第2ゲート誘電体層(42)を形成すること、第2ゲート誘電体層上に第2メタルゲート電極層を形成すること、第1ウェル領域上に、第1ゲート誘電体層と第1メタルゲート電極層の各々の一部を含む第1ゲートスタック(58)を形成し、チャネル領域層上に、第2ゲート誘電体層と第2メタルゲート電極層の各々の一部を含む第2ゲートスタック(66)を形成することを含む。

## 【特許請求の範囲】

## 【請求項 1】

半導体構造の形成方法であって、

半導体層上にチャネル領域層を形成することであって、前記半導体層は第1ウェル領域と第2ウェル領域を備え、前記チャネル領域は前記第2ウェル領域上に形成される、前記チャネル領域を形成すること、

前記チャネル領域層上に保護層を形成すること、

前記第1ウェル領域上に第1ゲート誘電体層を形成すること、

前記第1ゲート誘電体上に第1メタルゲート電極層を形成すること、

前記第1メタルゲート電極層の形成後に前記保護層を除去すること、

前記チャネル領域層上に第2ゲート誘電体層を形成すること、

前記第2ゲート誘電体層上に第2メタルゲート電極層を形成することであって、前記第2メタルゲート電極層は前記第1メタルゲート電極層とは異なる金属である、前記第2メタルゲート電極層を形成すること、

前記第1ゲート誘電体層と前記第1メタルゲート電極層のそれぞれの一部を備えた第1ゲートスタックを前記第1ウェル領域上に形成し、前記第2ゲート誘電体層と前記第2メタルゲート電極層それぞれの一部を備えた第2ゲートスタックを前記チャネル領域層上および前記第2ウェル領域上に形成することを備える方法。

## 【請求項 2】

前記第1ゲートスタックを用いて第1導電性を有する第1デバイスを形成し、前記第2ゲートスタックを用いて、前記第1導電性とは異なる第2導電性を有する第2デバイスを形成することを更に備え、前記第2デバイスのチャネル領域は前記チャネル領域層内に存在する、請求項1に記載の方法。

## 【請求項 3】

前記第1ゲートスタックと前記第2ゲートスタックの形成前に、前記第1メタルゲート電極層と前記第2メタルゲート電極層の各々の上に導電ゲート厚み付け層を形成することを更に備える、請求項1に記載の方法。

## 【請求項 4】

前記チャネル領域層を形成することは、前記半導体層の半導体材料とは異なる半導体金属材料を成長させることを含む、請求項1に記載の方法。

## 【請求項 5】

前記チャネル領域層を形成することは、前記第2ウェル領域の上にケイ素ゲルマニウムをエピタキシャル成長させることを含む、請求項4に記載の方法。

## 【請求項 6】

前記保護層を形成することは、酸化物と窒化物から成る群より選択された材料を堆積させることを含む、請求項1に記載の方法。

## 【請求項 7】

前記第1ゲート誘電体層を形成することは、第1高k誘電体層を形成することを含み、前記第2ゲート誘電体層を形成することは、前記第1高k誘電体層とは異なる高k誘電体を含む第2高k誘電体層を形成することを含む、請求項1に記載の方法。

## 【請求項 8】

半導体構造の形成方法であって、

半導体層上にチャネル領域層を形成することであって、前記半導体層は第1ウェル領域と第2ウェル領域を備え、前記チャネル領域は、前記第1ウェル領域ではなく前記第2ウェル領域の上に形成される、前記チャネル領域層を形成すること、

前記チャネル領域層上に保護層を形成すること、

前記半導体層と前記保護層の上にゲート誘電体層を形成すること、

前記第1ゲート誘電体層上に第1メタルゲート電極層を形成すること、

前記保護層の上にある前記第1ゲート誘電体層と前記第1メタルゲート電極層の各一部を除去すること、

10

20

30

40

50

前記保護層を除去すること、

前記第1ゲート電極層と前記チャネル領域層の上に第2ゲート誘電体層を形成すること、

前記第2ゲート誘電体層上に第2メタルゲート電極層を形成することであって、前記第2メタルゲート電極層は前記第1メタルゲート電極層とは異なる金属である、前記第2メタルゲート電極層を形成すること、

前記第1ゲート電極層の上にある前記第2メタルゲート電極層と前記第2ゲート誘電体層の各一部を除去すること、

前記第1ウェル領域上に、前記第1ゲート誘電体層と前記第1メタルゲート電極層の各々の一部を備えた第1ゲートスタックを形成し、前記チャネル領域層上および前記第2ウェル領域上に、前記第2ゲート誘電体層と前記第2メタルゲート電極層の各々の一部を備えた第2ゲートスタックを形成することを備える方法。

10

【請求項9】

前記保護層を形成することは、酸化物と窒化物から成る群より選択された材料を堆積させることを含む、請求項8に記載の方法。

【請求項10】

前記第1ゲートスタックを用いて第1導電性を有する第1デバイスを形成し、前記第2ゲートスタックを用いて、前記第1導電性とは異なる第2導電性を有する第2デバイスを形成することを更に備え、

前記第2デバイスのチャネル領域は前記チャネル領域層内に存在する、請求項8に記載の方法。

20

【請求項11】

前記チャネル領域層を形成することは、前記半導体層の半導体材料とは異なる半導体材料を成長させることを含む、請求項8に記載の方法。

【請求項12】

前記チャネル領域層を形成することは、前記第2ウェル領域上にケイ素ゲルマニウムをエピタキシャル成長させることを含む、請求項8に記載の方法。

【請求項13】

前記第1ゲート誘電体層を形成することは、第1高k誘電体層を形成することを含み、前記第2ゲート誘電体層を形成することは、前記第1高k誘電体層とは異なる高k誘電体を含む第2高k誘電体層を形成することを含む、請求項8に記載の方法。

30

【請求項14】

前記第1ゲート電極層の上に導電層を形成することを更に備え、

前記第1ゲート電極層と前記チャネル領域層の上に第2ゲート誘電体層を形成することは、前記導電層と前記チャネル領域層の上に前記第2ゲート誘電体層を形成することを含む、請求項8に記載の方法。

【請求項15】

前記第1ゲート電極層上にある前記第2メタルゲート電極層と前記第2ゲート誘電体層との各一部を除去することは、前記導電層をエッチング停止層として使用することを含む、請求項14に記載の方法。

40

【請求項16】

前記第2メタルゲート電極層上に導電層を形成することを更に備える、請求項8に記載の方法。

【請求項17】

半導体構造の形成方法であって、

半導体層上にチャネル領域層を形成することであって、前記半導体層は第1ウェル領域と第2ウェル領域を備え、前記チャネル領域層は前記第2ウェル領域上に形成されている、前記チャネル領域層を形成すること、

前記チャネル領域層上に保護層を形成すること、

前記第1ウェル領域上に第1高kゲート誘電体層を形成すること、

50

前記第1高kゲート誘電体の上に第1メタルゲート電極層を形成すること、

前記第1メタルゲート電極層の形成後に前記保護層を除去すること、

前記チャネル領域層上に第2高kゲート誘電体層を形成することであって、前記第2高kゲート誘電体層は、前記第1高kゲート誘電体層とは異なる高k誘電体を有する、前記第2高kゲート誘電体層を形成すること、

前記第2高kゲート誘電体層上に第2メタルゲート電極層を形成することであって、前記第2メタルゲート電極層は前記第1メタルゲート電極層とは異なる金属である、前記第2メタルゲート電極層を形成すること、

前記第1ウェル領域上に、前記第1高kゲート誘電体層と前記第1メタルゲート電極層の各々の一部を備えた第1ゲートスタックを形成し、前記チャネル領域層上および前記第2ウェル領域上に、前記第2高kゲート誘電体層と前記第2メタルゲート電極層の各々の一部を備えた第2ゲートスタックを形成すること、

前記第1ゲートスタックを用いて第1導電性を有する第1デバイスを形成し、また、前記第2ゲートスタックを用いて、前記第1導電性とは異なる第2導電性を有する第2デバイスを形成することを含み、前記第2デバイスのチャネル領域は前記チャネル領域層内に存在する、方法。

#### 【請求項18】

前記第1ゲートスタックと前記第2ゲートスタックの形成前に、前記第1メタルゲート電極層と前記第2メタルゲート電極層の各々の上に導電ゲート厚み付け層を形成することを更に備える、請求項17に記載の方法。

#### 【請求項19】

前記チャネル領域層を形成することは、前記半導体層の半導体材料とは異なる半導体材料を成長させることを含む、請求項17に記載の方法。

#### 【請求項20】

前記保護層を形成することは、酸化物と窒化物から成る群より選択される材料を堆積させることを含む、請求項17に記載の方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本開示は概して半導体処理に関し、より詳細にはデュアルメタルゲート構造の形成方法に関する。

#### 【背景技術】

#### 【0002】

半導体処理の分野では、ゲート誘電体が徐々に薄くなるに従い、ポリシリコンゲートゲート構造の使用がますます困難になっている。半導体プロセスで、誘電率の高いゲート誘電体（高k（high k）誘電体とも呼ばれる）を重視したことで、ゲート誘電体に二酸化ケイ素を使用しなくなるにつれて、ポリシリコンゲートが原因の問題が以前よりも多く生じるようになった。ポリシリコンゲートが原因で生じる問題を克服する1つの解決法として、メタルゲートの使用がある。デュアルメタルゲートプロセスでは、第1金属をPMOS（pチャネル金属酸化物半導体）デバイス用ゲートの形成に使用し、これとは別の第2金属をNMOS（nチャネル金属酸化物半導体）デバイスに使用する。異なる金属を使用することで、両タイプのデバイスについて仕事関数を最適化できる。しかし、従来のデュアルメタルゲート集積化では、金属エッチングやハードマスク除去のような処理工程で、デュアルメタルゲート構造の高kゲート誘電体が損傷され、デバイス性能が低下してしまう可能性があった。

#### 【図面の簡単な説明】

#### 【0003】

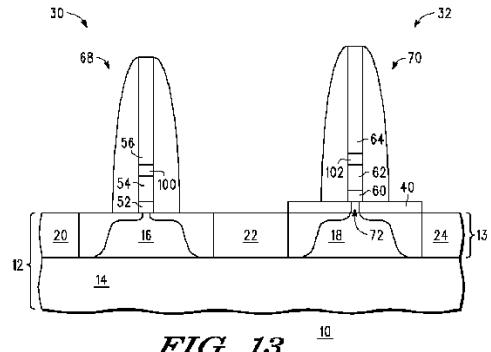

【図1】一実施形態に従い、半導体層上にチャネル領域層を設けた半導体構造の断面図を示す。

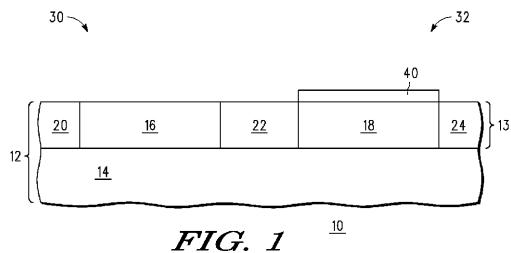

【図2】一実施形態に従い、半導体層上およびチャネル領域層上に保護層を形成し、保護

層上にパターン化されたマスキング層を形成した状態の、図1の半導体構造の断面図を示す。

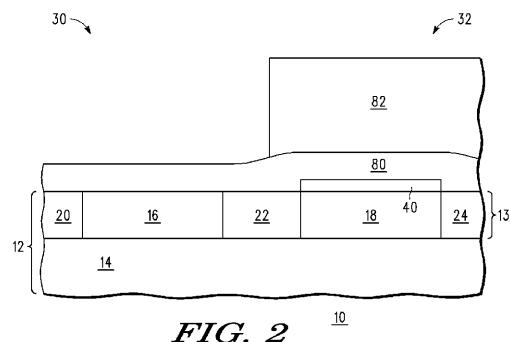

【図3】一実施形態に従い、保護層の露出部分を除去した状態にある、図2の半導体構造の断面図を示す。

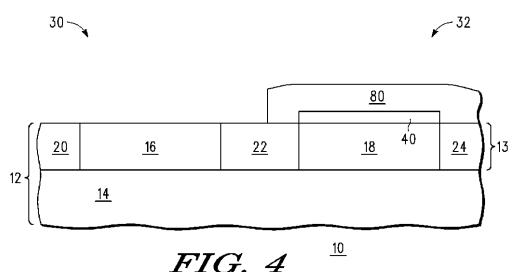

【図4】一実施形態に従い、図2で形成したパターン化されたマスキング層を除去した状態にある、図3の半導体構造の断面図を示す。

【図5】一実施形態に従い、半導体層と保護層上にゲート誘電体層を形成し、誘電体層上にゲート電極層を形成し、ゲート電極層上に導電層を形成し、導電層上にパターン化されたマスキング層を形成した状態にある、図4の半導体構造の断面図を示す。

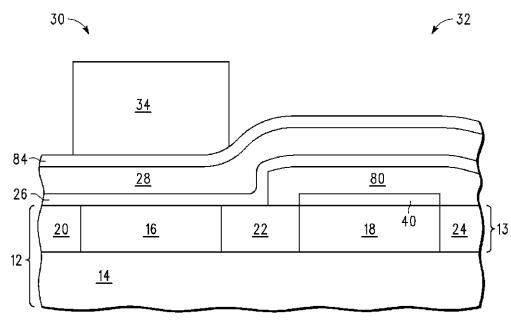

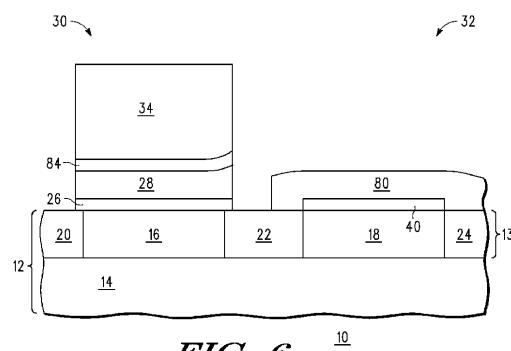

【図6】一実施形態に従い、図5で形成したパターン化されたマスキング層を用いて図5で形成したゲート誘電体層、ゲート電極層、および導電層をパターン化した状態にある、図5の半導体構造の断面図を示す。

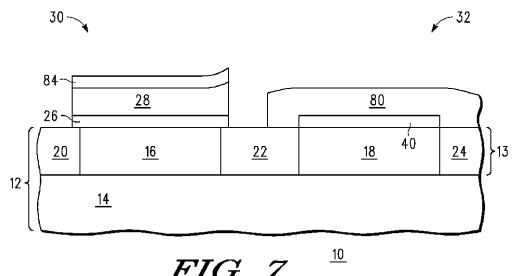

【図7】一実施形態に従い、図5で形成したパターン化されたマスキング層を除去した状態にある、図6の半導体構造の断面図を示す。

【図8】一実施形態に従い保護層を除去した状態にある、図7の半導体構造の断面図を示す。

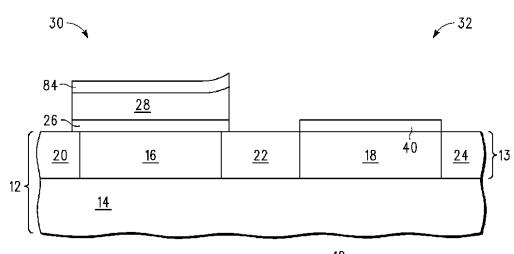

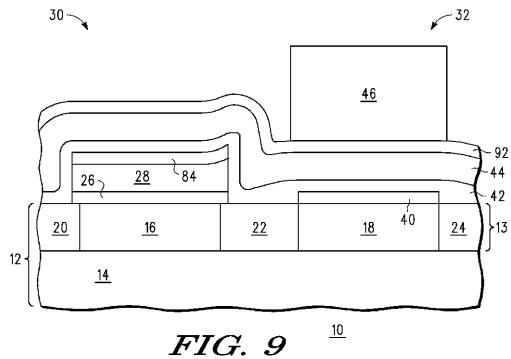

【図9】一実施形態に従い、導電層とチャネル領域層上にゲート誘電体層を形成し、ゲート誘電体層上にゲート電極層を形成し、ゲート電極層上に導電層を形成し、ゲート電極層上にパターン化されたマスキング層を形成した状態にある、図8の半導体構造の断面図を示す。

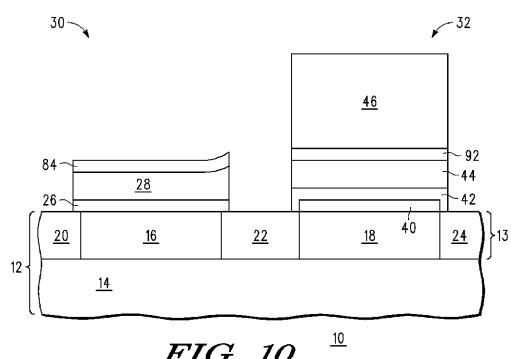

【図10】一実施形態に従い、図9で形成した導電層、ゲート電極層、およびゲート誘電体層の各一部を除去した状態にある、図9の半導体構造の断面図を示す。

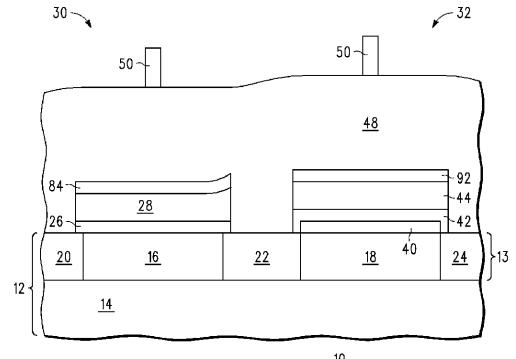

【図11】一実施形態に従い、図9で形成したパターン化されたマスキング層を除去し、更に、導電層上にゲート厚み付け層を形成し、ゲート厚み付け層上にパターン化されたマスキング層を形成した状態にある、図10の半導体構造の断面図を示す。

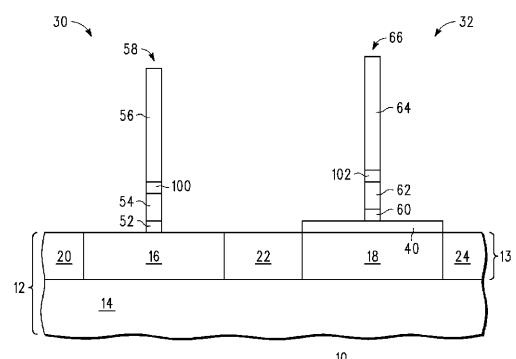

【図12】一実施形態に従い、2つのゲートスタックを形成した状態にある、図11の半導体構造の断面図を示す。

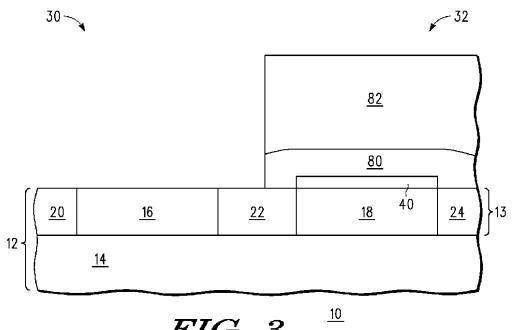

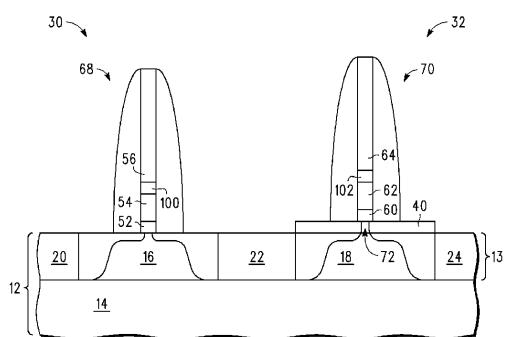

【図13】一実施形態に従い、この後完了する、図12のゲートスタックを設けた半導体デバイスを形成した状態にある、図12の半導体構造の断面図を示す。

#### 【発明を実施するための形態】

##### 【0004】

本発明は例として図示され、添付の図面によって制限されることはなく、かつ、類似した要素は同様の参照符号で表される。図面中の要素は単純かつ明瞭に図示されているが、必ずしも一定の比率の縮尺で描かれてはいない。

##### 【0005】

第1金属をN M O Sデバイスとして使用し、これと別の第2メタルゲートをP M O Sデバイスとして使用するデュアルメタルゲート集積を、ポリシリコンゲートに伴う問題を検討するため、また、それぞれのタイプのデバイスについて仕事関数を最適化するために使用することができる。また、デバイスの各チャネル領域に異なる材料を使用すれば、P M O SデバイスおよびN M O Sデバイスの性能を更に改善できる。例えば、N M O Sデバイスは、チャネル領域が1つの半導体材料（例えばシリコン）で形成されている場合に良好に機能でき、P M O Sデバイスは、チャネル領域を別の半導体材料（例えばシリコンゲルマニウム）で形成することにより良好に機能できる。したがって、以下に示す一実施形態は、異なるタイプのチャネル領域をN M O SデバイスとP M O Sデバイスに使用することが可能なデュアル金属集積を含む。

##### 【0006】

図1は、半導体基板12を設けた半導体構造10を図示している。半導体基板12は、埋め込み酸化物層14とその上の半導体層13を含む。半導体層13はN M O Sデバイスの形成に使用されるN M O Sウェル領域16と、P M O Sデバイスの形成に使用されるP M O Sウェル領域18とを含む。半導体層13は、異なるウェル領域同士を分離するため

10

20

30

40

50

の分離領域 20、22、24を含む。それぞれのウェル領域、例えばウェル領域 16、18の各々を使用して、任意数のデバイスを形成できる点に留意されたい。この図示の実施形態では、半導体基板は、埋め込み酸化物層 14の上に半導体層 13を積層したセミコンダクタ・オン・インシュレータ (S O I) 基板として図示されている。しかし、別の実施形態では、基板 12は、埋め込み酸化物層 14が表面に現れないバルク半導体基板であつてよい。半導体層 13はあらゆる半導体材料を含むことができる。一実施形態では、半導体層 13はシリコン層である。

#### 【 0 0 0 7 】

半導体層 13は、内部に1つまたは複数のN M O S デバイスが形成されるN M O S デバイス領域 30と、内部に1つまたは複数のP M O S デバイスが形成されるP M O S デバイス領域 32とを含んでいる。N M O S デバイス領域 30は、N M O S ウェル領域 16のようなN M O S ウェル領域を任意数含んでいてよく、P M O S デバイス領域 32は、P M O S ウェル領域 18のようなP M O S ウェル領域を任意数含んでいてよい点に留意されたい。

#### 【 0 0 0 8 】

図 1 はまた、P M O S デバイス領域 32内のP M O S ウェル領域 18の上に形成したチャネル領域層 40を図示している。チャネル領域層 40は、後にP M O S デバイスのチャネル領域を収容する層である。したがって、チャネル領域層 40は、半導体層 13の（あるいはN M O S ウェル領域 16の）半導体材料とは別の半導体材料を含んだ、P M O S デバイスに一段と適した層である。これは例えば、引張、バンドギャップ、移動性などに対して、あるいはこれらの任意の組合せに対して影響を与える材料であつてよい。例えば一実施形態では、チャネル領域層 40はケイ素ゲルマニウム層であり、この層は、ケイ素使用時よりも改善されたP M O S デバイスを作成できる。そのため一実施形態では、半導体層 13のウェル領域 16、18はケイ素であつてよく、チャネル領域層 40はケイ素ゲルマニウムであつてもよい。一実施形態では、ケイ素ゲルマニウムを約 550～700 の温度で、厚さ約 2～15 ナノメートルにまでエピタキシャル成長させており、そのゲルマニウム濃度は約 10～50 % である。

#### 【 0 0 0 9 】

図 2 は、半導体層 13とチャネル領域層 40との上に保護層 80を形成した状態の半導体構造 10を図示している。一実施形態では、保護層 80は、酸化物を約 5～20 ナノメートルの厚さにプランケット堆積させて形成されている。別の実施形態では、保護層 80はプラズマ増強窒化物を含んでいてよい。図 2 はまた、P M O S デバイス領域 32内の保護層 80の上に形成したパターン化されたマスキング層 82を図示している。一実施形態では、パターン化されたマスキング層 82はフォトレジストを含む。一実施形態では、従来の処理を用いて、パターン化されたマスキング層 82を形成することができる。

#### 【 0 0 1 0 】

図 3 は、パターン化したマスキング層 82を用いて保護層 80の露出部分を除去した半導体構造 10を図示している。したがって、パターン化されたマスキング層 82を使用すれば、N M O S デバイス領域 30内の保護層 80の一部を除去し、半導体層 13のN M O S ウェル領域 16を露出させることができる。一実施形態では、従来のエッチングプロセスと化学薬品を用いて、保護層 80の露出部分を除去することができる。

#### 【 0 0 1 1 】

図 4 は、パターン化されたマスキング層 82除去後の半導体構造 10を図示している。一実施形態では、従来の処理を用い、パターン化されたマスキング層 82を除去する。

図 5 は、半導体層 13と保護層 80の上にゲート誘電体層 26を、誘電体層 26の上にゲート電極層 28を、ゲート電極層 28の上に導電層 84を、更にN M O S 領域 30内の導電層 84の上にパターン化されたマスキング層 34を形成した状態にある半導体構造 10を図示している。一実施形態では、ゲート誘電体層 26は半導体層 13と保護層 80の上にプランケット堆積され、ゲート電極層 28はゲート誘電体層 26の上にプランケット堆積されている。一実施形態では、ゲート誘電体層 26は、例えば酸化ハフニウムまたは

酸化ハフニウムジルコニウムを含む高 k ゲート誘電体である。（ここで使用している高 k 誘電体は、二酸化物ケイ素のものよりも高い誘電率 k を有する誘電体である点に留意されたい。）更に、ゲート誘電体層 26 は、酸化物で覆った高 k 誘電体層のような層を 2 層以上含んでいてよい。一実施形態では、ゲート誘電体層 26 の厚さは約 1 ~ 5 ナノメートルであってよい。一実施形態では、ゲート電極層 28 は、例えば炭化タンタル、窒化タンタル、窒化チタンなどの金属を含む。一実施形態では、ゲート電極層 28 の厚さは約 2 ~ 10 ナノメートルである。この図示の実施形態では、ゲート誘電体層 26 とゲート電極層 28 はそれぞれ、N M O S デバイス領域 30 内に N M O S デバイスを形成するために使用されるゲート誘電体層とゲート電極層である点に留意されたい。

## 【0012】

10

更に図 5 を参照すると、一実施形態では、導電層 84 は原位置 (in-situ) ドープした多結晶シリコン層である。一実施形態では、導電層 84 は厚さ約 2 ~ 20 ナノメートルである。別の実施形態では、導電層 84 を設けていない。また、一実施形態では、パターン化されたマスキング層 34 はフォトレジストを含んでおり、従来の処理を用いて形成することができる。

## 【0013】

図 6 は、パターン化されたマスキング層 34 を用いて、ゲート誘電体層 26、ゲート電極層 28、および導電層 84 のそれぞれの露出部分を除去した状態の半導体構造 10 を図示している。したがって、パターン化されたマスキング層 34 を使用することで、P M O S デバイス領域 32 内のゲート誘電体層 26、ゲート電極層 28、および導電層 84 の各一部分を除去できる点に留意されたい。一実施形態では、乾式エッチングを用いて少なくとも導電層 84 を貫通エッチングする一方で、湿式または乾式エッチングを用いてゲート電極層 28 とゲート誘電体層 26 を貫通エッチングすることができる。図示の実施形態において、保護層 80 は、P M O S デバイス領域 32 内のゲート誘電体層 26、ゲート電極層 28、および導電層 84 のエッチング中にチャネル領域 40 を保護する点に留意されたい。

20

## 【0014】

図 7 は、パターン化したマスキング層 34 を除去した半導体構造 10 を図示する。一実施形態では、パターン化されたマスキング層 34 の除去に従来の処理を使用することができる。

30

## 【0015】

図 8 は保護層 80 を除去した状態の半導体構造 10 を図示している。一実施形態では、フッ化水素酸 (H F) を使用して P M O S デバイス領域 32 内の保護層 80 を除去する。

図 9 は、N M O S デバイス領域 30 内の導電層 84 の上と、P M O S デバイス領域 32 内のチャネル領域 40 の上にゲート誘電体層 42 を形成し、ゲート誘電体層 42 の上にゲート電極層 44 を形成し、ゲート電極層 44 の上に導電層 92 を形成し、P M O S デバイス領域 32 内の導電層 92 の上にパターン化されたマスキング層 46 を形成した状態の半導体構造 10 を図示している。一実施形態では、導電層 84、半導体層 13、およびチャネル領域 40 の上にゲート誘電体層 42 をプランケット堆積させ、ゲート誘電体層 42 の上にゲート電極層 44 をプランケット堆積させている。一実施形態では、ゲート誘電体層 42 は、例えば酸化ハフニウムや酸化ハフニウムジルコニウムを含む高 k ゲート誘電体である。（一実施形態では、ゲート誘電体層 42 はゲート誘電体 26 の場合と別の高 k 誘電体を使用して形成されていることに留意されたい。）更に、ゲート誘電体層 42 は、例えば酸化物で覆った高 k 誘電体層のような層を 2 層以上含むことができる。一実施形態では、ゲート誘電体層 42 の厚さは約 1 ~ 5 ナノメートルであってよい。一実施形態では、ゲート電極層 44 は、例えば窒化モリブデン、ルテニウムなどの金属を含んでいる。更に一実施形態では、ゲート電極層 44 はゲート電極層 28 のものとは別の金属で形成されている。一実施形態では、ゲート電極層 44 の厚さは約 2 ~ 10 ナノメートルである。図示の実施形態では、ゲート誘電体層 42 とゲート電極層 44 はそれぞれ、P M O S デバイス領域 32 内に P M O S デバイスを形成するために使用されるゲート誘電体層とゲート電

40

50

極層である点に留意されたい。

【0016】

更に図9を参照すると、一実施形態では、導電層92は原位置(in-situ)ドープした多結晶シリコン層である。一実施形態では、導電層92の厚さは約3～15ナノメートルである。別の実施形態では、導電層92を設けていない。また、一実施形態では、パターン化されたマスキング層46はフォトレジストを含んでおり、従来の処理を用いて形成できる。

【0017】

NMOSデバイス領域30は第1デバイス領域と呼ばれ、同様にNMOSウェル領域16は第1ウェル領域と呼ばれ、PMOSデバイス領域32は第2デバイス領域と呼ばれ、同様にPMOSウェル領域18は第2ウェル領域と呼ばれる点に留意されたい。更に、極性を反転させて、第1デバイス領域をPMOSデバイス領域に対応させ、第2デバイス領域をNMOSデバイス領域に対応させることができる点にも留意されたい。同様に、この実施形態では第1ウェル領域がPMOSウェル領域に対応し、第2ウェル領域がNMOSウェル領域に対応している。更にこの場合、ゲート誘電体層26とゲート電極層28のそれぞれが、PMOSデバイスの形成に使用されるゲート誘電体層とゲート電極層に対応し、ゲート誘電体層42とゲート電極層44のそれぞれが、NMOSデバイスの形成に使用されるゲート誘電体層とゲート電極層に対応している。

10

【0018】

図10は、パターン化されたマスキング層46を用いて、NMOSデバイス領域30内の導電層92、ゲート電極層44、およびゲート誘電体層42の露出部分を除去した状態の半導体構造10を図示している。そのため、パターン化されたマスキング層46を使用することで、NMOSデバイス領域30内の導電層92、ゲート電極層44、およびゲート誘電体層42の上記一部をエッチングすることができる点に留意されたい。この場合、一実施形態では、導電層86がエッチング停止層として働き、エッチング中にその下のゲート電極層28を保護するべく働く。別の実施形態では、導電層84を設けていない。この別の実施形態では、導電層92、ゲート電極層44、およびゲート誘電体層42のエッチング中に除去されるゲート電極層28の頂部を厚く設けることもできる。こうすることで、ゲート電極層44は、頂部が除去された後にもゲート電極として適切に機能できる十分な厚さを維持できる。一実施形態では、導電層92、ゲート電極層44、およびゲート誘電体層42の上記一部の除去に従来の処理を用いてもよい。

20

【0019】

図11は、パターン化されたマスキング層46除去後の半導体構造を図示する。導電層92は、パターン化されたマスキング層46の除去中に、下に存在するゲート電極層44を保護するように機能することに留意されたい。一実施形態では、アッシュ(ash)または「ピラニア(Piranha)」洗浄を用いてパターン化されたマスキング層46を除去できる。この場合、導電保護層92を設けていないと、アッシュまたは「ピラニア」によってゲート電極層44が損傷する可能性がある。別の実施形態では、導電層92は設けなくてもよい。例えば、一実施形態では、パターン化されたマスキング層46を、その下の層、例えばゲート電極層44を損傷することのない溶剤によって除去することができる。

30

【0020】

図11はまた、導電層84、92の上にゲート厚み付け層48を形成し、ゲート厚み付け層48の上にパターン化されたマスキング層50を形成した状態の半導体構造10を図示する。導電層84を設けていない場合には、ゲート電極28の上にゲート厚み付け層48が直接形成され、導電層92を設けていない場合には、ゲート厚み付け層48がゲート電極44の上に直接形成される点に留意されたい。一実施形態では、ゲート厚み付け層48は例えば多結晶シリコンのような導電性材料を含んでいるため、導電ゲート厚み付け層とも呼ばれる。また、ゲート厚み付け層48は1つまたは複数層の導電性材料を含んでいてよい。一実施形態では、ゲート厚み付け層48は形成中のデバイスのゲートスタックを

40

50

厚くするよう働くことで、ソース／ドレイン注入時にゲートスタックが、チャネル領域への注入を阻止できるのに十分な程度に厚くなる。別の実施形態では、ゲート厚み付け層は形成しなくてもよい。パターン化されたマスキング層50は、形成中のデバイスのゲートスタックに対応する位置を規定する。この実施形態では、パターン化されたマスキング層50は、NMOSデバイス領域30内におけるゲートスタックの位置と、PMOSデバイス領域32内におけるゲートスタックの位置とを規定する。一実施形態では、パターン化されたマスキング層50はフォトレジストを含む。一実施形態では、従来の処理を用いて、ゲート厚み付け層48とパターン化されたマスキング層50を形成することができる。

#### 【0021】

図12は、パターン化されたマスキング層50を用いてゲートスタック58、66を形成し、次に、パターン化されたマスキング層50を除去した状態の半導体構造10を図示する。しがたって、パターン化されたマスキング層50を使用して、ゲート厚み付け層48の露出部分をデバイス領域30、32から除去し、導電層84、ゲート電極層28、およびゲート誘電体層26の該当部分をNMOSデバイス領域30から除去し、導電層92、ゲート電極層44、およびゲート誘電体層42の該当部分をPMOSデバイス領域32から除去することで、NMOSデバイス領域30内にゲートスタック58が、PMOSデバイス領域32内にゲートスタック66が出来上がる。図13に示す実施形態のエッチング中に、両方のメタルゲート電極層（ゲート電極層28、44）が同時にエッチングされる点に留意されたい。一実施形態では、ゲート電極層28、44の厚さは、両方の層を同じ合計時間でエッチングするために、その相対エッチング速度に応じて調整できるようになっている。一実施形態では、従来の処理を用い、ゲートスタック58、66と、パターン化されたマスキング層50とを形成することができる。

#### 【0022】

図13に図示するように、ゲートスタック58は、NMOSウェル領域16上のゲート誘電体52（ゲート誘電体層26で形成されている）と、ゲート誘電体52上のゲート電極54（ゲート電極層28で形成されている）と、ゲート電極54上の導電層100（導電層84で形成されている）と、ゲート電極54上のゲート厚み付け部56（ゲート厚み付け層48で形成されている）とを含む。ゲートスタック66は、チャネル領域層40上のゲート誘電体60（ゲート誘電体層42で形成されている）と、ゲート誘電体60上のゲート電極62（ゲート電極層44で形成されている）と、ゲート電極62上の導電層102（導電層92で形成されている）と、ゲート電極62上のゲート厚み付け部64（ゲート厚み付け層48で形成されている）とを含む。

#### 【0023】

図14は、次の段階で完了するNMOSデバイス68、およびPMOSデバイス70が形成された状態にある半導体構造10を図示する。NMOSデバイス68は、NMOSデバイス領域30内のゲートスタック58を用いて形成され、PMOSデバイスはPMOSデバイス領域32内のゲートスタック66を用いて形成される。各デバイスについて、従来の処理を使用してスペーサ、およびソース／ドレイン領域を形成することが可能である。チャネル領域は、半導体層13のNMOSウェル領域16内のゲート誘電体52の下にあたる、NMOSデバイス68のソース／ドレイン領域間に形成される点に留意されたい。しかし、PMOSデバイス70のチャネル領域は、半導体層13内ではなく、チャネル領域層40内のゲート誘電体60の下にあたる、PMOSデバイス70のソース／ドレイン領域間に位置している。こうすることで、NMOSデバイス68とPMOSデバイス70が、異なるメタルゲート電極を持ち、更に、チャネル領域に異なる半導体材料を有して形成されることが可能となる。そのため、異なるメタルゲート電極と異なるチャネル領域材料とを選択することにより、NMOSデバイスとPMOSデバイスを別個に最適化することが可能となる。

#### 【0024】

したがって、保護層80を使用することで、ゲート電極層28とゲート誘電体層26（更に、使用されていれば導電層84）を、先に形成されたチャネル領域層40を損傷する

10

20

30

40

50

ことなくデバイス領域32からエッチングできるようになることが理解される。更に、導電層84、92を使用することで、その下の層、例えばゲート電極層28、44のそれぞれを、デュアルメタルゲート構造の形成に必要な後続の処理中（例えば、上の層の除去中）に保護することができる。こうすることで、デバイス領域32内に形成中の特定タイプのデバイスに一層適したチャネル領域層を形成できるようになる。

#### 【0025】

別の実施形態では、チャネル領域層、例えばチャネル領域層40を、PMOSデバイスではなくNMOSデバイスの形成に使用してもよい。更に別の実施形態では、チャネル領域層、例えばチャネル領域層40をNMOSデバイスとPMOSデバイスの両方を形成するために使用できる。例えば、ゲート誘電体層26を形成する前に、チャネル領域層をウェル領域16の上に形成することも可能である。

10

#### 【0026】

一実施形態は半導体構造の形成方法に関するものであり、この形成方法は、半導体層上にチャネル領域層を形成することであって、半導体層は第1ウェル領域と第2ウェル領域を含み、チャネル領域は第2ウェル領域上に形成されている、チャネル領域層を形成すること、チャネル領域層上に保護層を形成すること、第1ウェル領域上に第1ゲート誘電体層を形成すること、第1ゲート誘電体上に第1メタルゲート電極層を形成すること、第1メタルゲート電極層の形成後に保護層を除去すること、チャネル領域層上に第2ゲート誘電体層を形成すること、第2ゲート誘電体層上に第2メタルゲート電極層を形成することであって、第2メタルゲート電極層は第1メタルゲート電極層とは異なる金属である、第2メタルゲート電極層を形成すること、第1誘電体層と第1メタルゲート電極層の各一部を含む第1ゲートスタックを第1ウェル領域上に形成し、第2ゲート誘電体層と第2メタルゲート電極層の各一部を含む第2ゲートスタックをチャネル領域層上および第2ウェル領域上に形成することを含む。

20

#### 【0027】

別の実施形態では、この方法は、第1ゲートスタックを用いて第1導電性を有する第1デバイスを形成すること、第2ゲートスタックを用いて、第1導電性とは異なる第2導電性を有する第2デバイスを形成することを更に含み、第2デバイスのチャネル領域はチャネル領域層内に存在する。

30

#### 【0028】

更に別の実施形態では、この方法は、第1ゲートスタックと第2ゲートスタック形成前に、第1メタルゲート電極層と第2メタルゲート電極層のそれぞれの上に導電ゲート厚み付け層を形成することを更に含む。

#### 【0029】

又別の実施形態では、チャネル領域層を形成することは、半導体層の半導体材料とは異なる半導体材料を成長させることを含む。更に別の実施形態では、チャネル領域層を形成することは、第2ウェル領域の上にケイ素ゲルマニウムをエピタキシャル成長させることを含む。

#### 【0030】

又別の実施形態では、保護層を形成することは、酸化物と窒化物から成る群より選択される材料を堆積させることを含む。

40

更に別の実施形態では、第1ゲート誘電体層を形成することは、第1高k誘電体層を形成することを含み、第2ゲート誘電体層を形成することは、第1高k誘電体層とは異なる高k誘電体を含む第2高k誘電体層を形成することを含む。

#### 【0031】

別の実施形態では、半導体構造の形成方法は、半導体層上にチャネル領域層を形成することであって、半導体層は第1ウェル領域と第2ウェル領域を含み、チャネル領域は、第1ウェル領域ではなく第2ウェル領域の上に形成される、チャネル領域層を形成すること、チャネル領域層上に保護層を形成すること、半導体層と保護層の上にゲート誘電体層を形成すること、第1ゲート誘電体層上に第1メタルゲート電極層を形成すること、保護層

50

の上にある第1ゲート誘電体層と第1メタルゲート電極層の各一部を除去すること、保護層を除去すること、第1ゲート電極層とチャネル領域層の上に第2ゲート誘電体層を形成すること、第2ゲート誘電体層上に第2メタルゲート電極層を形成することであって、第2メタルゲート電極層は第1メタルゲート電極層とは異なる金属である、第2メタルゲート電極層を形成すること、第1ゲート電極層の上にある第2メタルゲート層と第2ゲート誘電体層の各一部を除去すること、第1ウェル領域上に、第1ゲート誘電体層と第1メタルゲート電極層の各々の一部を含む第1ゲートスタックを形成し、チャネル領域層上および第2ウェル領域上に、第2ゲート誘電体層と第2メタルゲート電極層の各々の一部を含む第2ゲートスタックを形成することを含む。

【0032】

上記別の実施形態の更なる実施形態では、保護層を形成することは、酸化物と窒化物から成る群より選択される材料を堆積させることを含む。

上記別の実施形態の更に別の実施形態では、第1ゲートスタックを用いて、第1導電性を有する第1デバイスを形成すること、第2ゲートスタックを用いて、第1導電性とは異なる第2導電性を有する第2デバイスを形成することであり、この場合、第2デバイスのチャネル領域はチャネル領域層内に存在する。

【0033】

上記別の実施形態の更に別の実施形態では、チャネル領域層を形成することは、半導体層の半導体材料とは異なる半導体材料を成長させることを含む。更に別の実施形態では、チャネル領域層を形成することは、第2ウェル領域の上にケイ素ゲルマニウムをエピタキシャル成長させることを含む。

【0034】

上記別の実施形態の更に別の実施形態では、第1ゲート誘電体層を形成することは第1高k誘電体層を形成することを含み、第2ゲート誘電体層を形成することは、第1高k誘電体層とは異なる高k誘電体を含む第2高k誘電体層を形成することを含む。

【0035】

上記別の実施形態の更に別の実施形態では、この方法は更に、第1ゲート電極層上に導電層を形成することを含み、この場合、第1ゲート電極層とチャネル領域層上に第2ゲート誘電体層を形成することは、導電層とチャネル領域層上に第2ゲート誘電体層を形成することを含む。更に別の実施形態では、第1ゲート電極層上にある第2メタルゲート電極層と第2ゲート誘電体層の各一部を除去することは、導電層をエッティング停止層として使用することを含む。

【0036】

上記別の実施形態の更に別の実施形態では、この方法は更に、第2メタルゲート電極層の上に導電層を形成することを含む。

更に別の実施形態では、半導体構造の形成方法は、半導体層上にチャネル領域層を形成することであって、半導体層は第1ウェル領域と第2ウェル領域を含み、チャネル領域層は第2ウェル領域上に形成されている、チャネル領域層を形成すること、チャネル領域層上に保護層を形成すること、第1ウェル領域上に第1高kゲート誘電体層を形成すること、第1高kゲート誘電体の上に第1メタルゲート電極層を形成すること、第1メタルゲート電極層の形成後に保護層を除去すること、チャネル領域層上に第2高kゲート誘電体層を形成することであって、第2高kゲート誘電体層は、第1高kゲート誘電体層とは異なる高k誘電体を有する、第2高kゲート誘電体層を形成すること、第2高kゲート誘電体層上に第2メタルゲート電極層を形成することであって、第2メタルゲート電極層は第1メタルゲート電極層とは異なる金属である、第2メタルゲート電極層を形成すること、第1ウェル領域上に、第1高kゲート誘電体層と第1メタルゲート電極層の各々の一部を含む第1ゲートスタックを形成し、チャネル領域層上および第2ウェル領域上に、第2高kゲート誘電体層と第2メタルゲート電極層の各々の一部を含む第2ゲートスタックを形成すること、第1ゲートスタックを用いて第1導電性を有する第1デバイスを形成し、第2ゲートスタックを用いて、第1導電性とは異なる第2導電性を有する第2デバイスを形成

10

20

30

40

50

することを含み、第2デバイスのチャネル領域はチャネル領域層内に存在する。

【0037】

上記更に別の実施形態の更なる実施形態では、この方法は、第1ゲートスタックと第2ゲートスタックの形成前に、第1メタルゲート電極層と第2メタルゲート電極層のそれぞれの上に導電ゲート厚み付け層を形成することを更に含む。

【0038】

上記の更に別の実施形態の又別の実施形態では、チャネル領域層を形成することは、半導体層の半導体材料とは異なる半導体材料を成長させることを含む。

上記又別の実施形態の更に別の実施形態では、保護層を形成することは、酸化物と窒化物の群より選択される材料を堆積させることを含む。

10

【0039】

本発明を特定の導電性または電位の極性に関連して説明したが、当業者は導電性と電位の極性とを反転することができることを理解するであろう。

更に、発明の説明と請求項に記載された用語「前」、「後」、「頂部」、「底部」、「上」、「下」などは、これらが使用されている場合、それは説明目的のみで使用されたものであり、必ずしも永久的な相対位置を述べるものではなく、また、このように使用されたこれらの用語は適切な状況下において相互交換が可能であることが理解される。この例として、本明細書で述べた本発明の実施形態が、本明細書で図示または説明している方位とは別の方位へ動作できることなどを挙げる。

20

【0040】

本明細書では本発明を特定の実施形態を参照して説明したが、特許請求の範囲で述べている本発明の範囲から逸脱しない限り、様々な改良および変更が可能である。したがって、本願明細書および図面は、限定的なものとしてよりも例証的なものとして捉えられるべきであり、こうした改良は全て本発明の範囲に包含されるものとする。本明細書で特定の実施形態に関連して述べたあらゆる恩典、利点、問題解決方法は、いずれかまたは全ての請求項の重大な、必要な、または必須な特徴・要素と解釈されることを意図したものではない。

【0041】

特に記載がある場合以外は、「第1」、「第2」という用語は、こうした用語によって説明される要素を任意に区別するために使用されている。したがって、これらの用語がこうした要素の一時的あるいはその他の優先順位を必ずしも意味するとは限らない。

30

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図 9】

FIG. 9 10

【図 10】

FIG. 10 10

【図 11】

FIG. 11 10

【図 12】

FIG. 12 10

【図 13】

FIG. 13 10

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                      | International application No.<br><b>PCT/US2008/064192</b>                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                      |                                                                                                                                                             |

| <b>H01L 21/336(2006.01)i, H01L 29/78(2006.01)i</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                      |                                                                                                                                                             |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                      |                                                                                                                                                             |

| <b>B. FIELDS SEARCHED</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                      |                                                                                                                                                             |

| Minimum documentation searched (classification system followed by classification symbols)<br>IPC 8 : as above                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                      |                                                                                                                                                             |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched<br>Korean Utility Models and application for Utility Models since 1975<br>Japanese Utility models and applications for Utility Models since 1975                                                                                                                                                                                                                                                                                                                                 |                                                                                                      |                                                                                                                                                             |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>eKIPASS(KIPO internal) "dual", "gate"                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                      |                                                                                                                                                             |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                      |                                                                                                                                                             |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Citation of document, with indication, where appropriate, of the relevant passages                   | Relevant to claim No.                                                                                                                                       |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | WO 2004095527 A2(FREESCALE SEMICONDUCTOR INC.) 04 NOVEMBER 2004<br>See claims and figs 3-7           | 1-20                                                                                                                                                        |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | US 20060157796 A1(KIM, MIN-JOO et al.) 20 JULY 2006<br>See claims and figs 1-6                       | 1-20                                                                                                                                                        |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | US 20070111453 A1(LEE, HYE-LAN et al.) 17 MAY 2007<br>See claims and figs 2-5                        | 1-20                                                                                                                                                        |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | US 6794252 B2(ANTONIO L.P.ROTONDARO; MARK R. VISOKAY) 21 SEPTEMBER 2004<br>See claims and figs 1A-1D | 1-20                                                                                                                                                        |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input checked="" type="checkbox"/> See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                      |                                                                                                                                                             |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"B" earlier application or patent but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                                      |                                                                                                                                                             |

| Date of the actual completion of the international search<br><b>26 NOVEMBER 2008 (26.11.2008)</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                      | Date of mailing of the international search report<br><b>26 NOVEMBER 2008 (26.11.2008)</b>                                                                  |

| Name and mailing address of the ISA/KR<br> Korean Intellectual Property Office<br>Government Complex-Daejeon, 139 Seonsa-ro, Seo-gu, Daejeon 302-701, Republic of Korea<br>Facsimile No. 82-42-472-7140                                                                                                                                                                                                                                                                                                                     |                                                                                                      | Authorized officer<br>KIM Jung Min<br>Telephone No. 82-42-481-8358<br> |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No.

**PCT/US2008/064192**

| Patent document cited in search report | Publication date | Patent family member(s)                                                                                                                                 | Publication date                                                                                             |

|----------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| WO 2004-095527 A2                      | 04.11.2004       | CN 101027771 A<br>EP 1611612 A2<br>EP 1611612 A4<br>JP 2007-524992 T<br>KR 10-2005-0112114 A<br>US 2004-191974 A1<br>US 6972224 B2<br>WO 2004-095527 A3 | 29.08.2007<br>04.01.2006<br>05.12.2007<br>30.08.2007<br>29.11.2005<br>30.09.2004<br>06.12.2005<br>29.03.2007 |

| US 2006-0157796 A1                     | 20.07.2006       | None                                                                                                                                                    |                                                                                                              |

| US 2007-0111453 A1                     | 17.05.2007       | None                                                                                                                                                    |                                                                                                              |

| US 6794252 B2                          | 21.09.2004       | US 7432566<br>US 2003-062577 A1                                                                                                                         | 07.10.2008<br>03.04.2003                                                                                     |

## フロントページの続き

|                         |              |            |

|-------------------------|--------------|------------|

| (51) Int.Cl.            | F I          | テーマコード(参考) |

| H 01 L 29/423 (2006.01) | H 01 L 21/28 | 3 0 1 B    |

| H 01 L 29/49 (2006.01)  | H 01 L 29/58 | G          |

|                         | H 01 L 27/08 | 3 2 1 C    |

(81) 指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MT,NL,NO,PL,PT,RO,SE,SI,SK,T

R),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BR,BW,BY,

BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,D0,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IS,JP,KE,K

G,KM,KN,KP,KR,KZ,LA,LC,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL,PT

,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,SV,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

(72) 発明者 カパッソ、クリスチアーノ

アメリカ合衆国 7 8 7 2 7 テキサス州 オースティン シンクリング レーン 1 2 6 0 1

(72) 発明者 サマベダム、スリカンス ビー。

アメリカ合衆国 1 2 5 2 4 ニューヨーク州 フィッシュキル ストーニー ブルック ロード

1 1 7

(72) 発明者 シェーファー、ジェームズ ケイ。

アメリカ合衆国 1 2 5 9 0 ニューヨーク州 ワピンジャーズ フォールズ アッシュ ロード

1 4

(72) 発明者 テイラー、ウィリアム ジェイ. ジュニア

アメリカ合衆国 7 8 6 8 1 テキサス州 ラウンド ロック シーダー ベンド ドライブ 1

9 0 5

F ターム(参考) 4M104 AA01 AA03 AA09 BB04 BB30 BB31 BB32 BB34 CC05 DD62

DD64 DD65 DD72 DD95 EE03 EE12 EE16 FF13 GG09 GG10

GG14

5F048 AC01 AC03 AC04 BA01 BA14 BA16 BB05 BB09 BB10 BB11

BB12 BB17 BC06 BD09 BE03 BG07 BG11 DA23

5F110 AA26 BB04 CC02 DD05 DD13 EE01 EE02 EE09 EE14 FF01

GG01 GG02 GG12 GG19 GG25 GG42