(12) 发明专利申请

(10) 申请公布号 CN 115831990 A

(43) 申请公布日 2023.03.21

(21) 申请号 202211121673.3

(22) 申请日 2022.09.15

(30) 优先权数据

10-2021-0125031 2021.09.17 KR

(71) 申请人 三星电子株式会社

地址 韩国京畿道

(72) 发明人 朴海龙 崔性洙 朴钟银

(74) 专利代理机构 北京市柳沈律师事务所

11105

专利代理人 翟然

(51) Int.Cl.

H01L 27/146 (2006.01)

权利要求书3页 说明书11页 附图34页

(54) 发明名称

图像传感器

(57) 摘要

一种图像传感器包括：具有彼此相反的第一表面和第二表面的基板，该基板包括彼此相邻的第一和第二像素；在基板中将第一和第二像素彼此隔离的器件隔离部分；在第一和第二像素的第一表面上的传输栅极；在第一和第二像素之一中的接地区域；以及堆叠在第二表面上的第一滤色器和微透镜阵列层。深器件隔离部分包括垂直重叠并间隔开的第一和第二隔离部分。第一隔离部分包括从第一表面朝向第二表面延伸的第一导电图案、在第一导电图案上的高浓度掺杂图案以及在第一导电图案和高浓度掺杂图案之间的绝缘图案。接地区域和高浓度掺杂图案包括具有相同导电类型的掺杂剂。

1. 一种图像传感器，包括：

具有第一表面和与所述第一表面相反的第二表面的基板，所述基板包括第一像素和与所述第一像素相邻的第二像素；

深器件隔离部分，在所述基板中并且将所述第一像素和所述第二像素彼此隔离；

传输栅极，在所述第一像素和所述第二像素中的每个中在所述第一表面上；

接地区域，选择性地位于所述第一像素和所述第二像素之一中；以及

第一滤色器和微透镜阵列层，依次堆叠在所述第二表面上，

所述深器件隔离部分包括垂直地彼此重叠并且彼此间隔开的第一隔离部分和第二隔离部分，

所述第一隔离部分包括

从所述第一表面朝向所述第二表面延伸的第一导电图案；

在所述基板中在所述第一导电图案上的高浓度掺杂图案；以及

在所述第一导电图案和所述高浓度掺杂图案之间的绝缘图案，所述接地区域和所述高浓度掺杂图案掺有具有相同导电类型的掺杂剂。

2. 根据权利要求1所述的图像传感器，其中，所述第一像素和所述第二像素共享具有相同颜色的所述第一滤色器。

3. 根据权利要求1所述的图像传感器，其中

所述第二隔离部分从所述第二表面朝向所述第一表面延伸，以及

所述第二隔离部分和所述第一隔离部分之间的距离在从100nm到300nm的范围内。

4. 根据权利要求1所述的图像传感器，其中

所述接地区域在所述第一像素中，以及

所述接地区域不提供在所述第二像素中。

5. 根据权利要求1所述的图像传感器，进一步包括：

在所述基板中的第三像素，所述第三像素在第一方向上与所述第一像素间隔开且所述第二像素在其间；以及

在所述第三像素上的第二滤色器，

其中

所述深器件隔离部分进一步包括第三隔离部分和第四隔离部分，所述第三隔离部分和所述第四隔离部分在所述基板中、将所述第二像素和所述第三像素彼此隔离、并且彼此垂直重叠，以及

所述第一滤色器和所述第二滤色器具有不同的颜色。

6. 根据权利要求5所述的图像传感器，其中，所述第三隔离部分和所述第四隔离部分彼此间隔开。

7. 根据权利要求5所述的图像传感器，其中，所述第三隔离部分和所述第四隔离部分彼此接触。

8. 根据权利要求1所述的图像传感器，其中当在平面图中观察时，所述传输栅极的面积是所述第一像素和所述第二像素中的每个的面积的10%或更多。

9. 根据权利要求1所述的图像传感器，其中所述高浓度掺杂图案的所述掺杂剂的浓度在从 $1 \times 10^{17}/\text{cm}^3$ 到 $1 \times 10^{19}/\text{cm}^3$ 的范围内。

10. 一种图像传感器，包括：

具有第一表面和与所述第一表面相反的第二表面的基板，所述基板包括在第一方向和第二方向上二维排列的第一像素组、第二像素组和一对第三像素组，所述第一方向平行于所述第一表面，所述第二方向平行于所述第一表面并与所述第一方向交叉；

在所述第一像素组上的第一滤色器；

在所述第二像素组上的第二滤色器；以及

在所述一对第三像素组中的每个上的第三滤色器，

所述第一像素组、所述第二像素组和所述第三像素组中的每个包括沿着所述第一方向和所述第二方向以 $N \times N$ 矩阵形式排列的 $N^2$ 个像素，其中‘N’是2或更大的自然数，

在所述 $N^2$ 个像素之间和在所述第一像素组至所述第三像素组之间在所述基板中的深器件隔离部分，所述深器件隔离部分包括从所述第一表面朝向所述第二表面延伸的第一隔离部分和从所述第二表面朝向所述第一表面延伸的第二隔离部分，所述第一隔离部分包括提供在所述 $N^2$ 个像素之间的第一隔离图案和提供在所述第一像素组至所述第三像素组之间的第二隔离图案，所述第二隔离部分包括提供在所述 $N^2$ 个像素之间的第三隔离图案和在所述第一像素组至所述第三像素组之间的第四隔离图案，所述 $N^2$ 个像素之一选择性地包括接地区域，

所述第一隔离图案和所述第三隔离图案彼此垂直对准并且彼此间隔开，

所述第二隔离图案和所述第四隔离图案彼此垂直对准，

所述第一隔离部分包括

从所述第一表面朝向所述第二表面延伸的第一导电图案；

在所述第一导电图案上的高浓度掺杂图案；以及

在所述第一导电图案和所述高浓度掺杂图案之间的绝缘图案。

11. 根据权利要求10所述的图像传感器，其中

所述第一隔离图案在所述第一方向上具有第一宽度，

所述第二隔离图案在所述第一方向上具有第二宽度，以及

所述第一宽度小于所述第二宽度。

12. 根据权利要求10所述的图像传感器，其中，所述第一隔离图案的长度小于所述第二隔离图案的长度。

13. 根据权利要求10所述的图像传感器，其中，所述第一隔离图案在所述第一方向上的宽度等于所述第二隔离图案在所述第一方向上的宽度。

14. 根据权利要求10所述的图像传感器，其中，所述第二隔离图案和所述第四隔离图案彼此接触。

15. 根据权利要求14所述的图像传感器，其中

所述第二隔离部分包括具有负固定电荷的固定电荷层，以及

所述第四隔离图案的最下部分的水平低于所述第二隔离图案的最上部分的水平。

16. 根据权利要求10所述的图像传感器，其中，所述第二隔离图案和所述第四隔离图案彼此间隔开。

17. 根据权利要求10所述的图像传感器，其中，在两个邻近像素之间从所述第二表面到所述第一隔离图案的顶表面的距离大于在所述像素组中四个邻近像素彼此相邻的地方从

所述第二表面到所述第一隔离图案的顶表面的距离。

18. 根据权利要求17所述的图像传感器，其中，在所述四个邻近像素彼此相邻的所述地方，所述第二表面的最低部分的水平高于所述第二隔离图案的顶表面的水平。

19. 根据权利要求10所述的图像传感器，其中，所述第一隔离图案的长度大于所述第三隔离图案的长度。

20. 一种图像传感器，包括：

具有第一表面和与所述第一表面相反的第二表面的基板，所述基板包括第一像素和与所述第一像素相邻的第二像素；

深器件隔离部分，在所述基板中并且将所述第一像素和所述第二像素彼此隔离；

传输栅极，在所述第一像素和所述第二像素的每个中在所述第一表面上；

接地区域，选择性地位于所述第一像素和所述第二像素之一中；以及

依次堆叠在所述第二表面上的滤色器和微透镜阵列层，

所述深器件隔离部分包括彼此垂直重叠并且彼此间隔开的第一隔离部分和第二隔离部分，

所述第一隔离部分包括

从所述第一表面朝向所述第二表面延伸的第一导电图案；

在所述第一导电图案上的高浓度掺杂图案；以及

在所述第一导电图案和所述高浓度掺杂图案之间的绝缘图案，

所述高浓度掺杂图案在所述第一像素和所述第二像素之间是连续的。

## 图像传感器

### 技术领域

[0001] 本公开涉及具有选择性接地区域的图像传感器。

### 背景技术

[0002] 图像传感器是用于将光学图像转换为电信号的半导体器件。随着计算机和通信产业发展，在诸如数码相机、便携式摄像机、个人通信系统(PCS)、游戏控制台、安全摄像机和医用微型摄像机的各种领域中，高性能图像传感器被越来越多地需求。图像传感器可以被分类为电荷耦合器件(CCD)图像传感器和互补金属氧化物半导体(CMOS)图像传感器中的任何一种。CIS是CMOS图像传感器的缩写。CIS可以包括二维排列的多个像素。每个像素可以包括光电二极管(PD)。光电二极管可以将入射光转换成电信号。多个像素可以由设置在其间的深器件隔离图案限定。

### 发明内容

[0003] 发明构思的示例实施方式可以提供能够增加栅电极的尺寸并最小化像素之间的串扰的图像传感器及其制造方法。

[0004] 发明构思的示例实施方式还可以提供能够容易地提高集成度的图像传感器及其制造方法。

[0005] 在一些示例实施方式的一个方面中，一种图像传感器可以包括：具有彼此相反的第一表面和第二表面的基板，基板包括第一像素和与第一像素相邻的第二像素；深器件隔离部分，在基板中并且将第一像素和第二像素彼此隔离；传输栅极，在第一像素和第二像素中的每个中的第一表面上；接地区域，选择性地位于第一像素和第二像素之一中；以及依次堆叠在第二表面上的第一滤色器和微透镜阵列层。深器件隔离部分可以包括垂直地彼此重叠并且彼此间隔开的第一隔离部分和第二隔离部分。第一隔离部分可以包括：从第一表面朝向第二表面延伸的第一导电图案；在基板中在第一导电图案上的高浓度掺杂图案；以及在第一导电图案和高浓度掺杂图案之间的绝缘图案。接地区域和高浓度掺杂图案可以掺有具有相同导电类型的掺杂剂。

[0006] 在一些示例实施方式的一个方面中，一种图像传感器可以包括：具有彼此相反的第一表面和第二表面的基板，基板包括在第一方向和第二方向上二维排列的第一像素组、第二像素组和一对第三像素组，第一方向平行于第一表面，第二方向平行于第一表面并与第一方向交叉；在第一像素组上的第一滤色器；在第二像素组上的第二滤色器；以及在该对第三像素组中的每个上的第三滤色器。第一、第二和第三像素组中的每个可以包括沿着第一方向和第二方向以 $N \times N$ 矩阵形式排列的 $N^2$ 个像素，其中‘N’是2或更大的自然数。深器件隔离部分可以在基板中在 $N^2$ 个像素之间和第一至第三像素组之间。深器件隔离部分可以包括从第一表面朝向第二表面延伸的第一隔离部分和从第二表面朝向第一表面延伸的第二隔离部分。第一隔离部分可以包括在 $N^2$ 个像素之间的第一隔离图案和在第一至第三像素组之间的第二隔离图案。第二隔离部分可以包括在 $N^2$ 个像素之间的第三隔离图案和在第一至

第三像素组之间的第四隔离图案。第一隔离图案和第三隔离图案可以彼此垂直对准并且可以彼此间隔开。第二隔离图案和第四隔离图案可以彼此垂直对准。 $N^2$ 个像素之一可以选择性地包括接地区域。第一隔离部分可以包括：从第一表面朝向第二表面延伸的第一导电图案；在第一导电图案上的高浓度掺杂图案；以及在第一导电图案和高浓度掺杂图案之间的绝缘图案。

[0007] 在一些示例实施方式的一个方面中，一种图像传感器可以包括：具有第一表面和与第一表面相反的第二表面的基板，基板包括第一像素和与第一像素相邻的第二像素；深器件隔离部分，在基板中并且将第一像素和第二像素彼此隔离；传输栅极，在第一像素和第二像素的每个中的第一表面上；接地区域，选择性地位于第一像素和第二像素之一中；以及依次堆叠在第二表面上的滤色器和微透镜阵列层。深器件隔离部分可以包括彼此垂直重叠并且彼此间隔开的第一隔离部分和第二隔离部分。第一隔离部分可以包括：从第一表面朝向第二表面延伸的第一导电图案；在第一导电图案上的高浓度掺杂图案；以及在第一导电图案和高浓度掺杂图案之间的绝缘图案。高浓度掺杂图案在第一像素和第二像素之间可以是连续的。

## 附图说明

[0008] 通过以下结合附图进行的简要描述，示例实施方式将被更清楚地理解。附图描绘了如在这里描述的非限制性的示例实施方式。

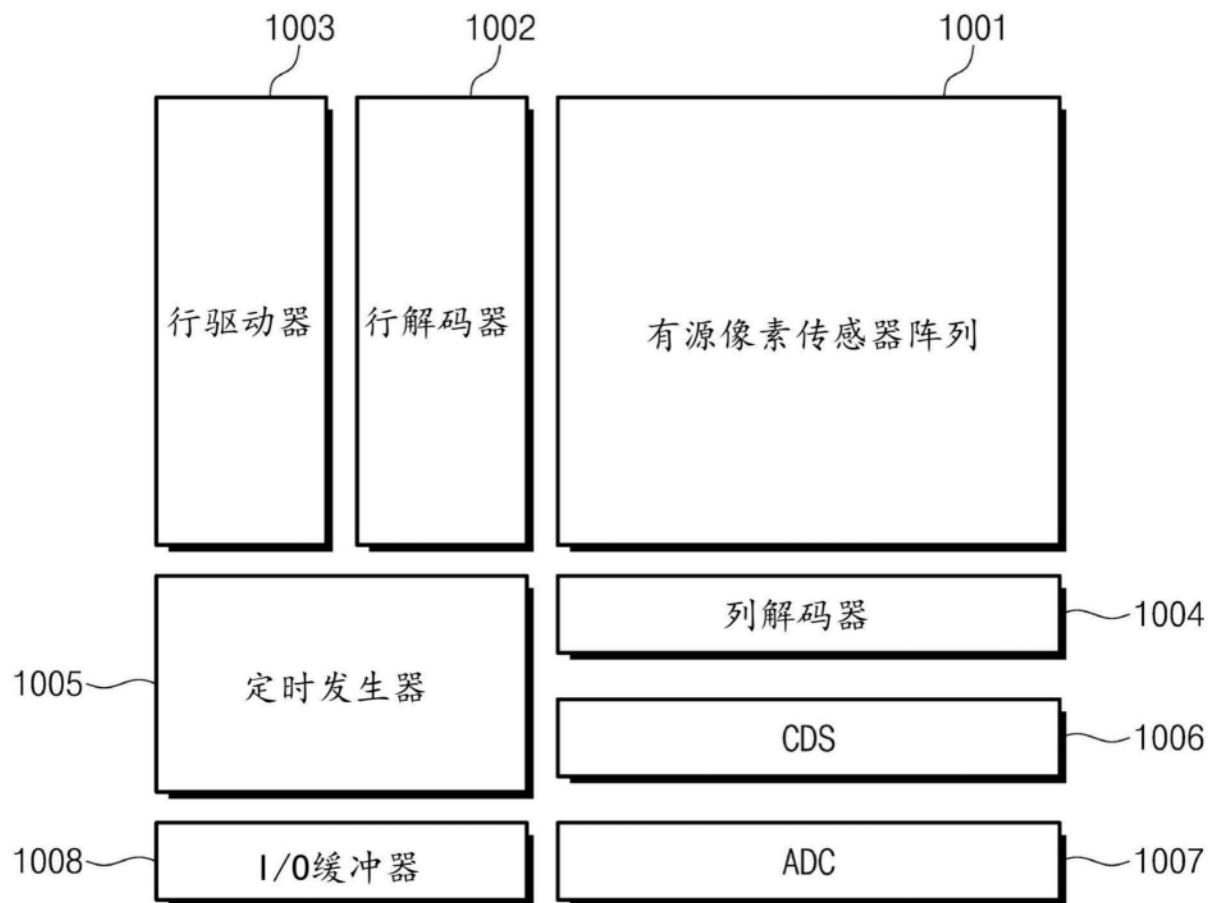

[0009] 图1是根据发明构思的一些示例实施方式的图像传感器的框图。

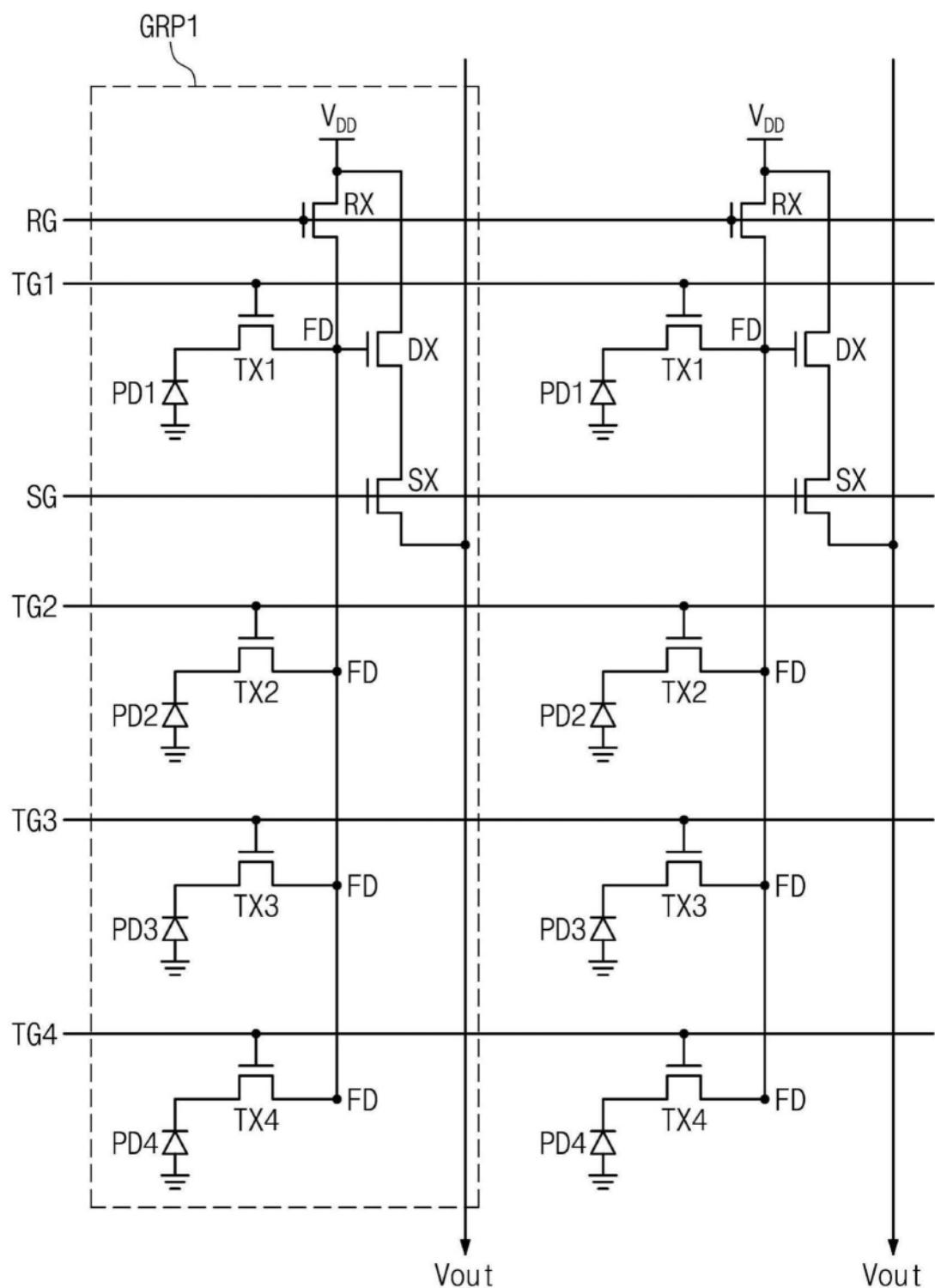

[0010] 图2是根据发明构思的一些示例实施方式的图像传感器的有源像素传感器阵列的电路图。

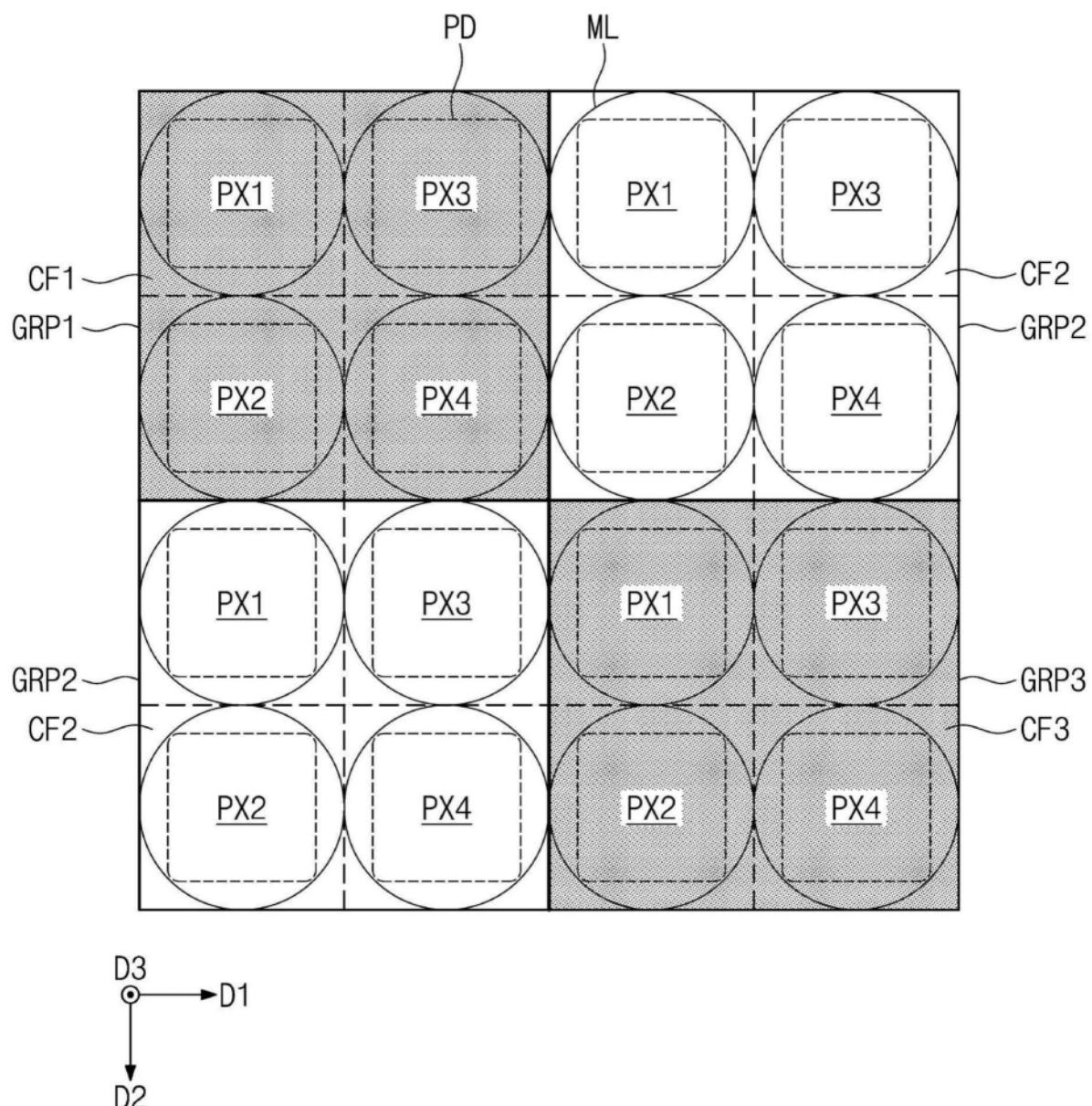

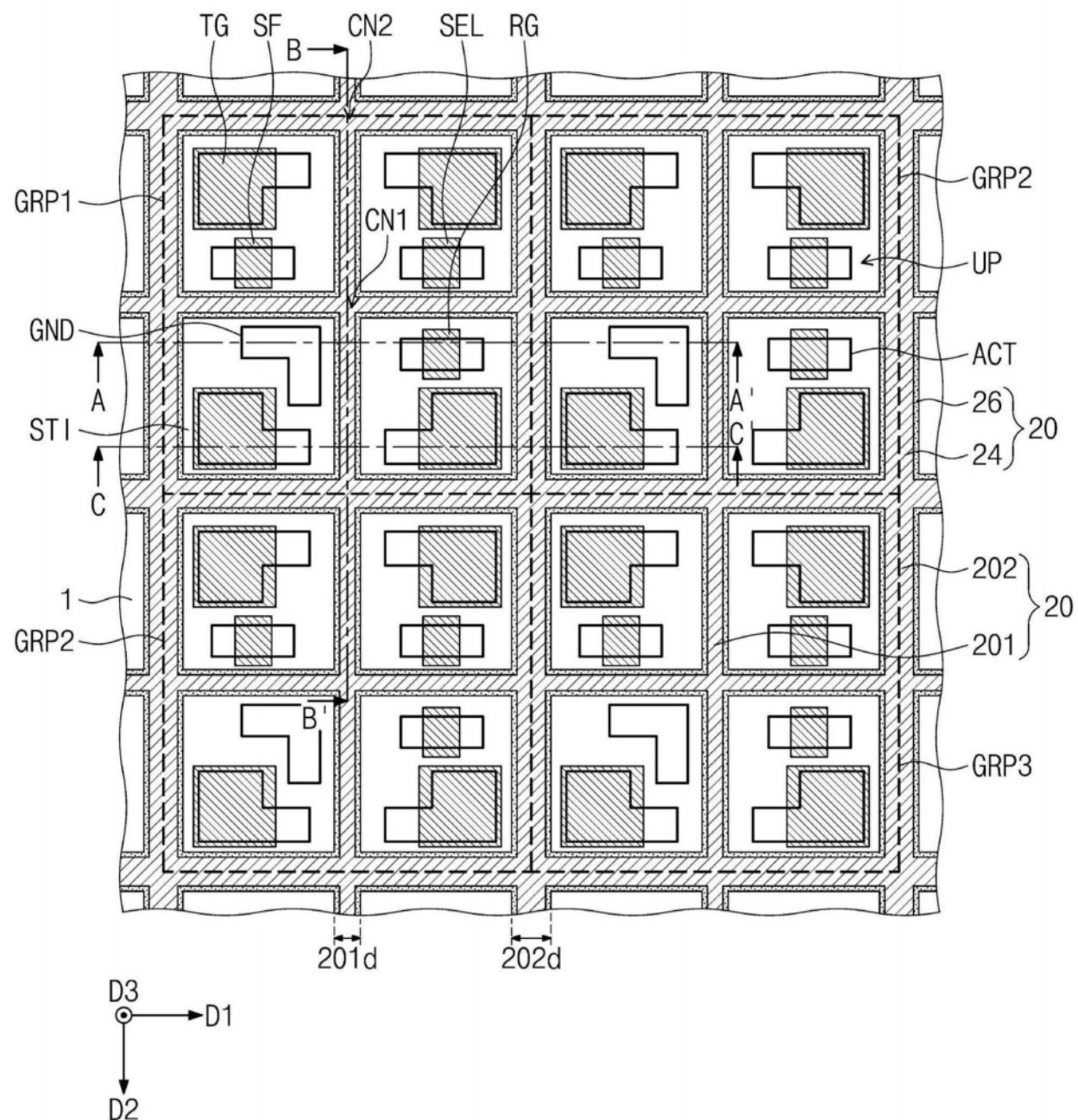

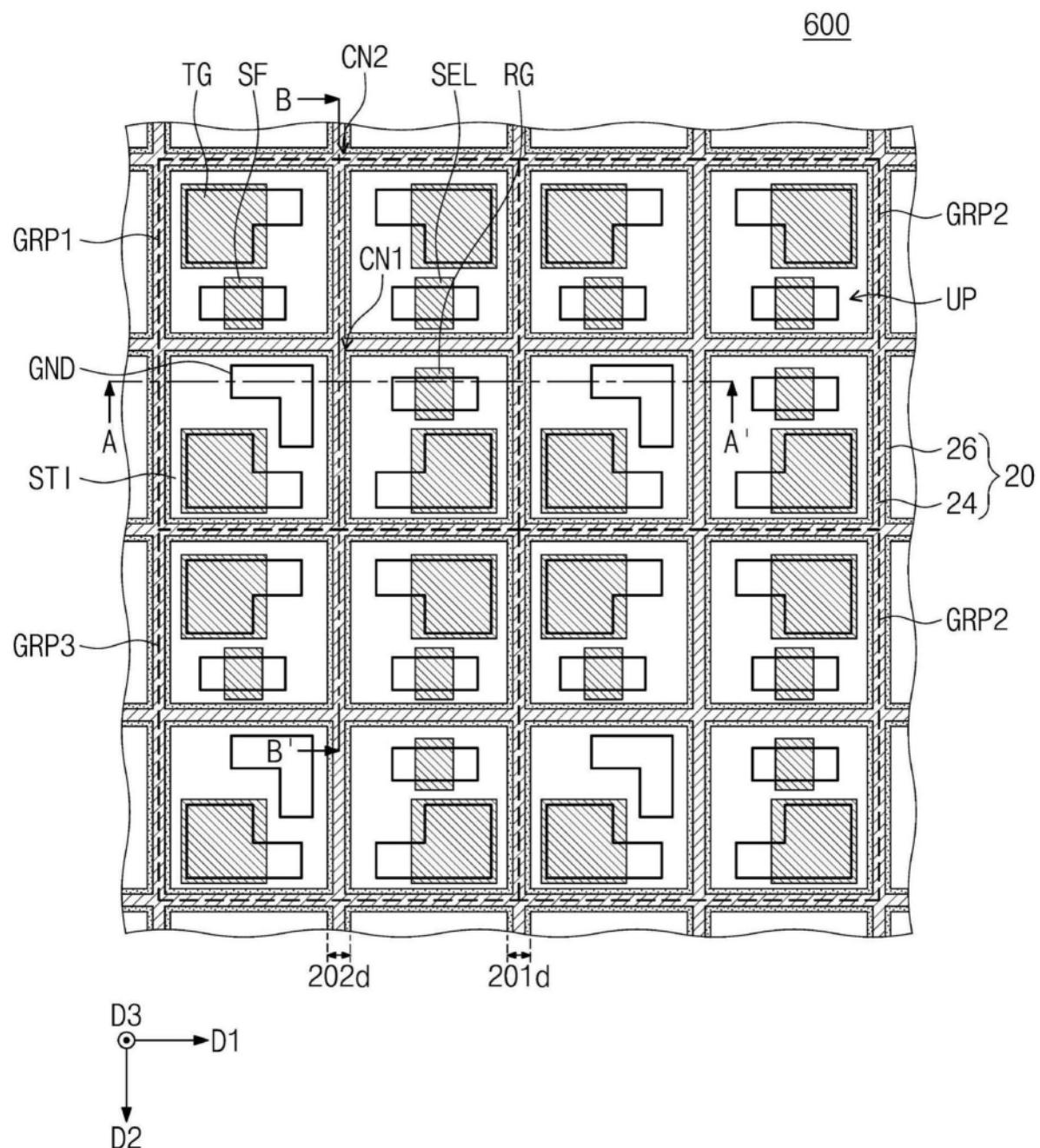

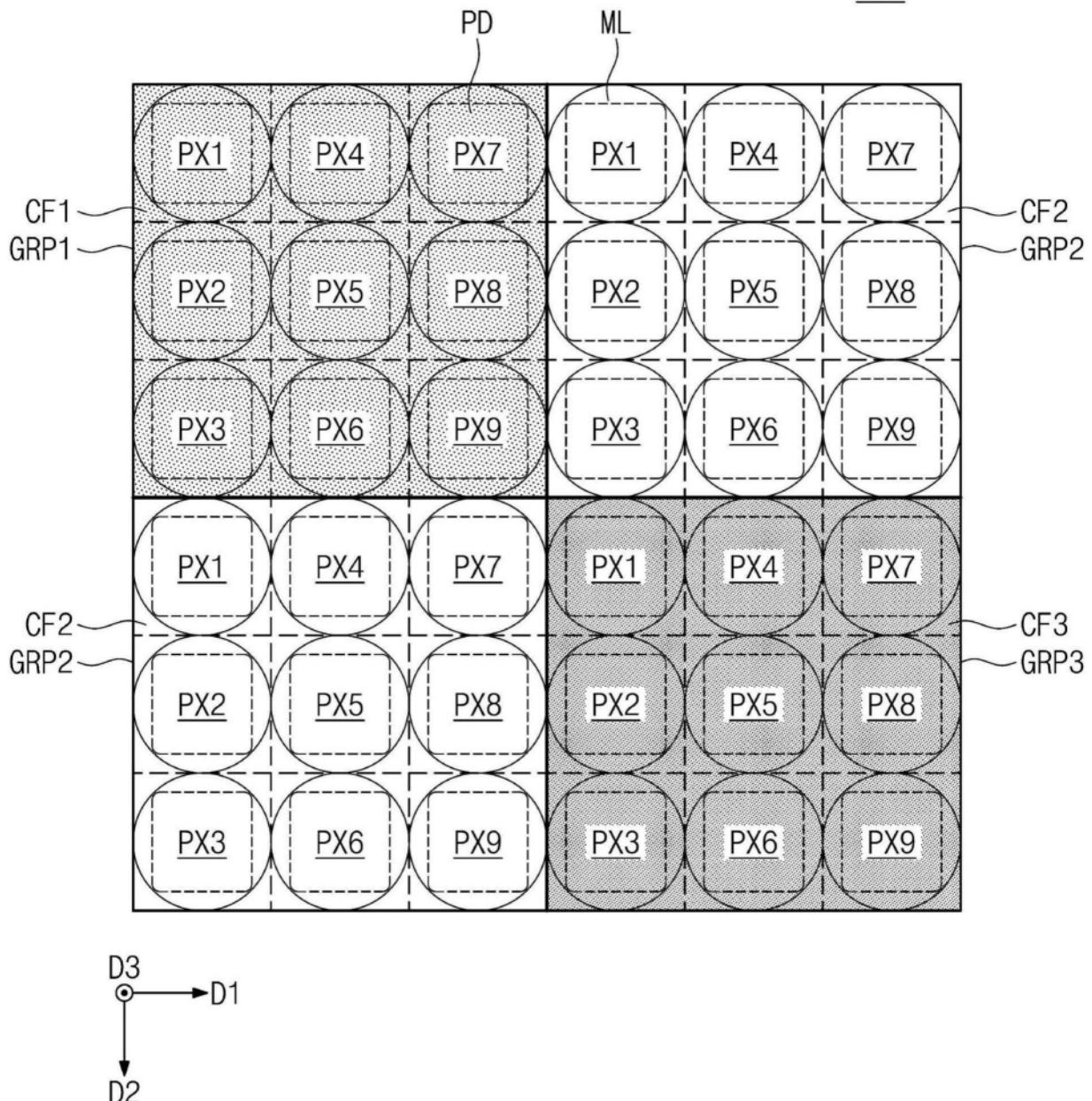

[0011] 图3是根据发明构思的一些示例实施方式的图像传感器的平面图。

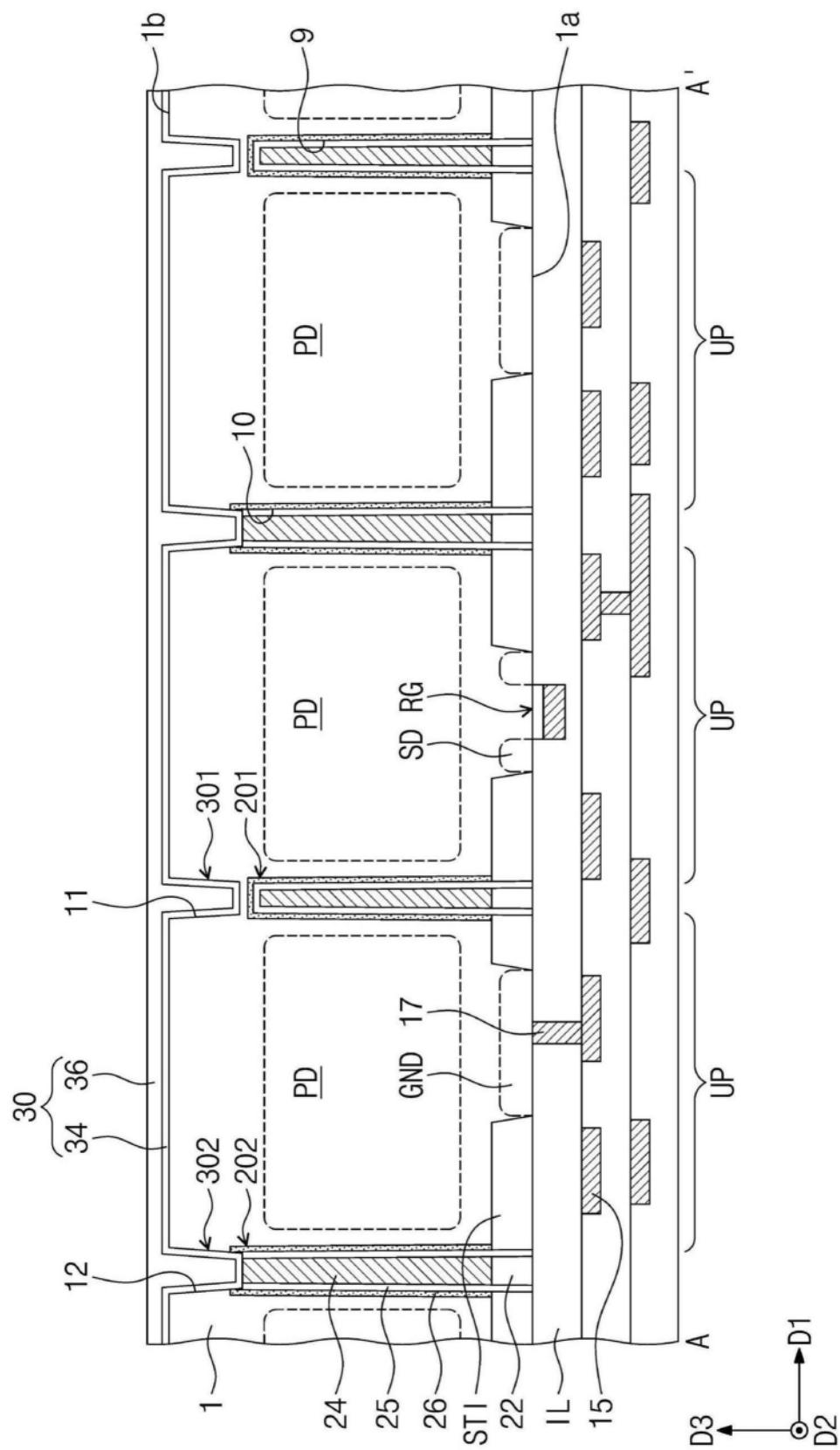

[0012] 图4是对应于图3的图像传感器的平面图。

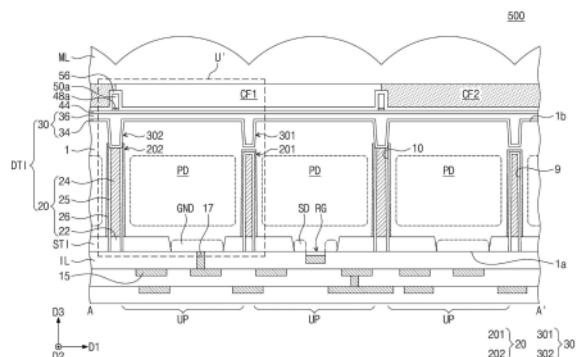

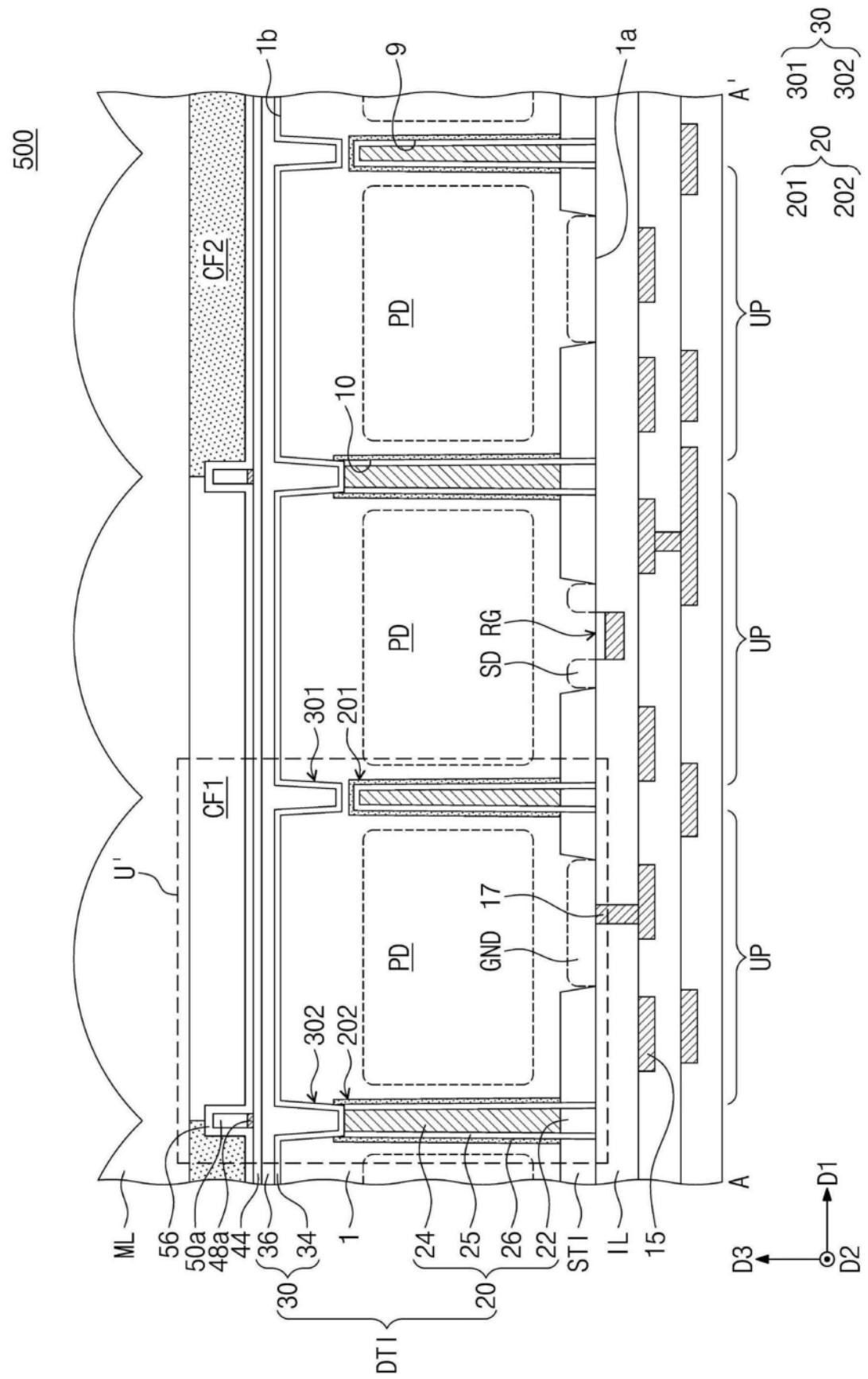

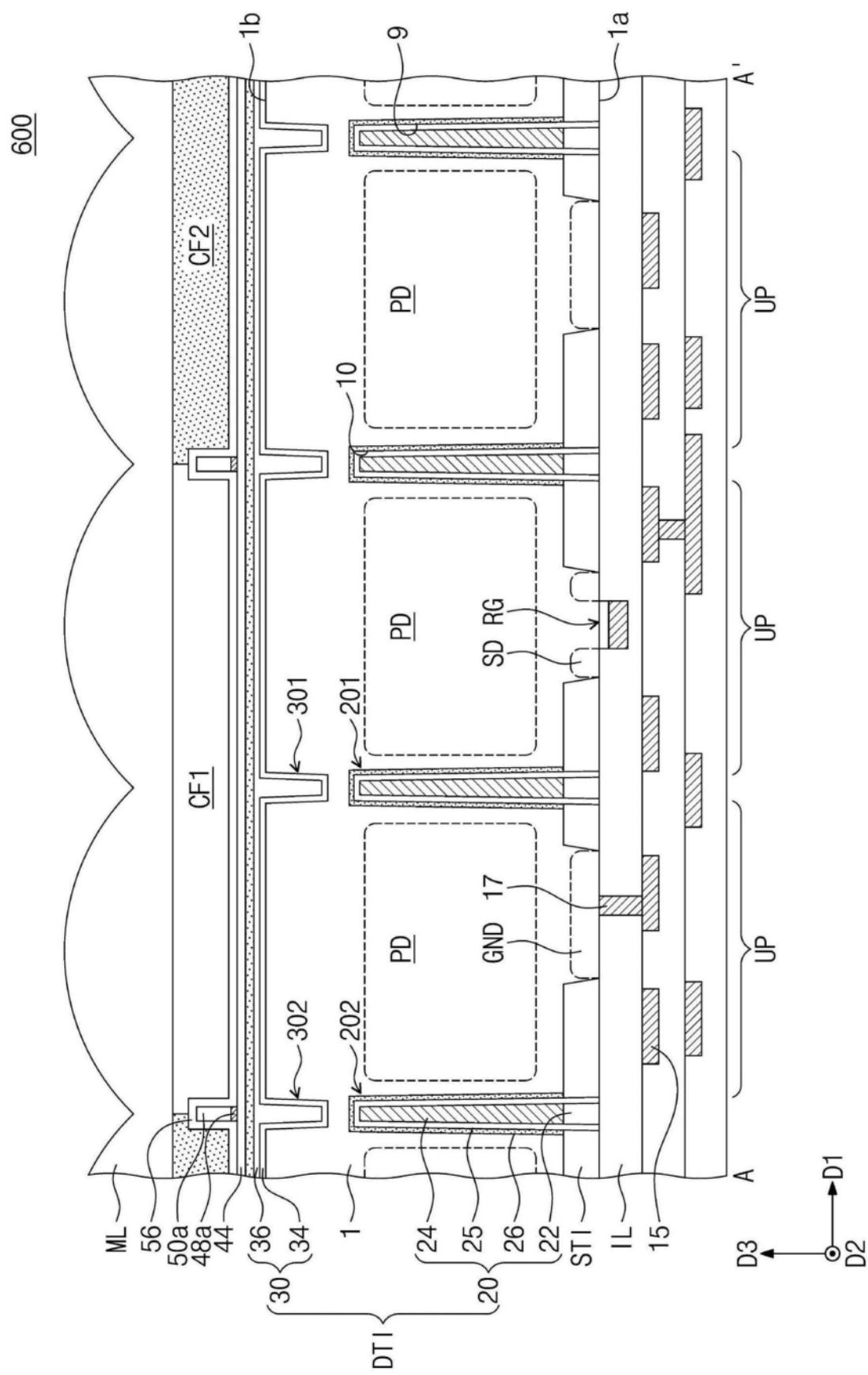

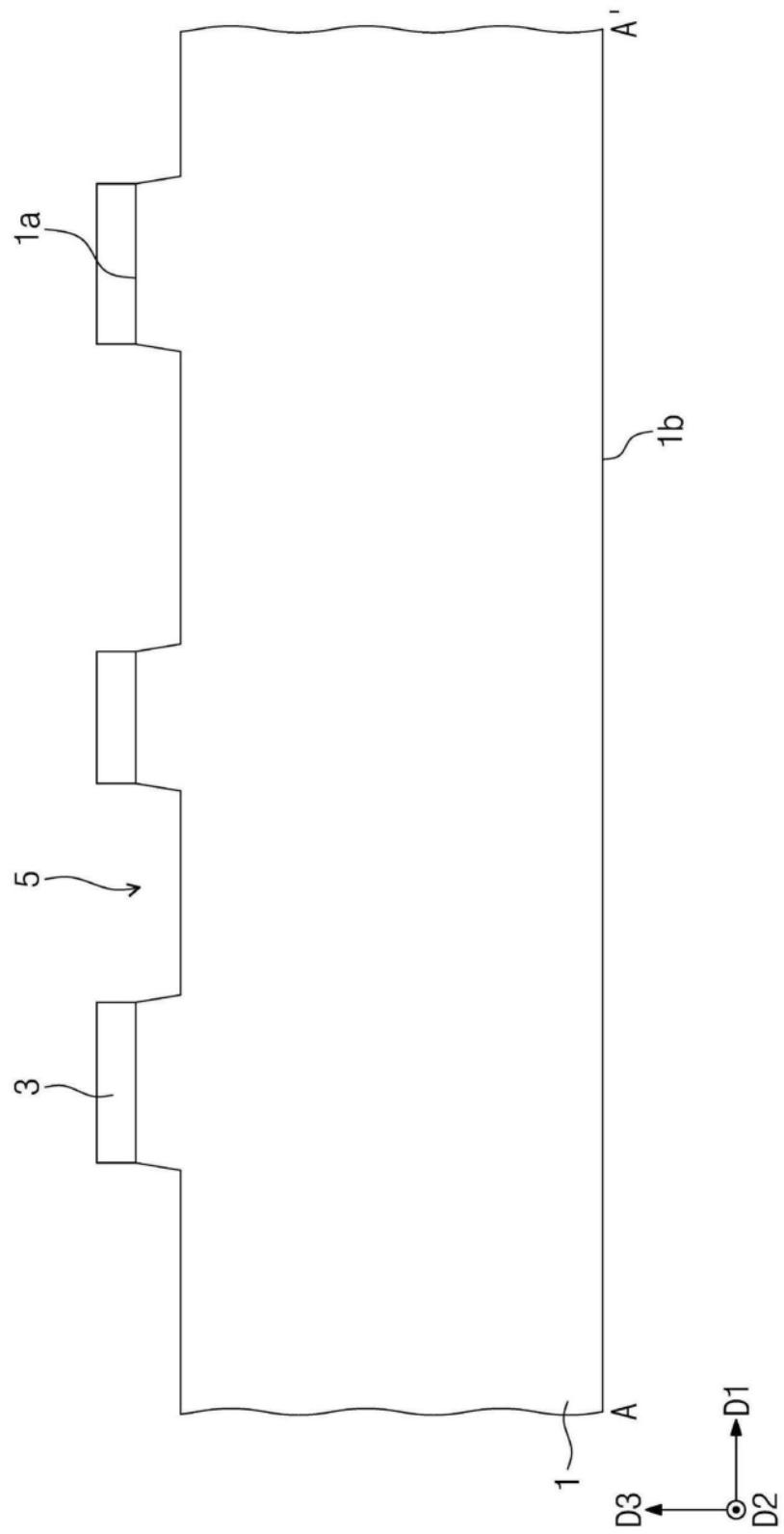

[0013] 图5A是根据发明构思的一些示例实施方式的沿图4的线A-A'截取的截面图。

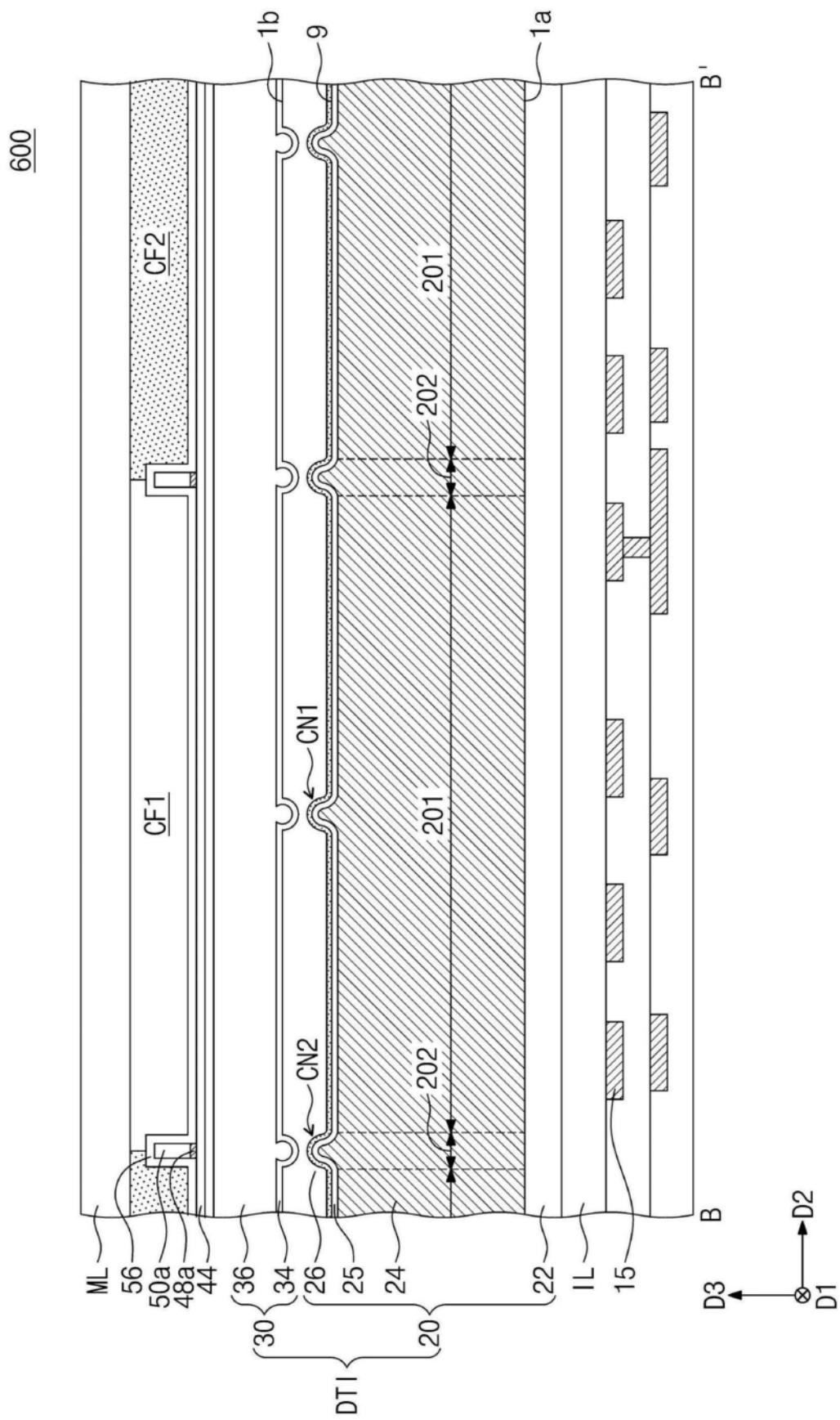

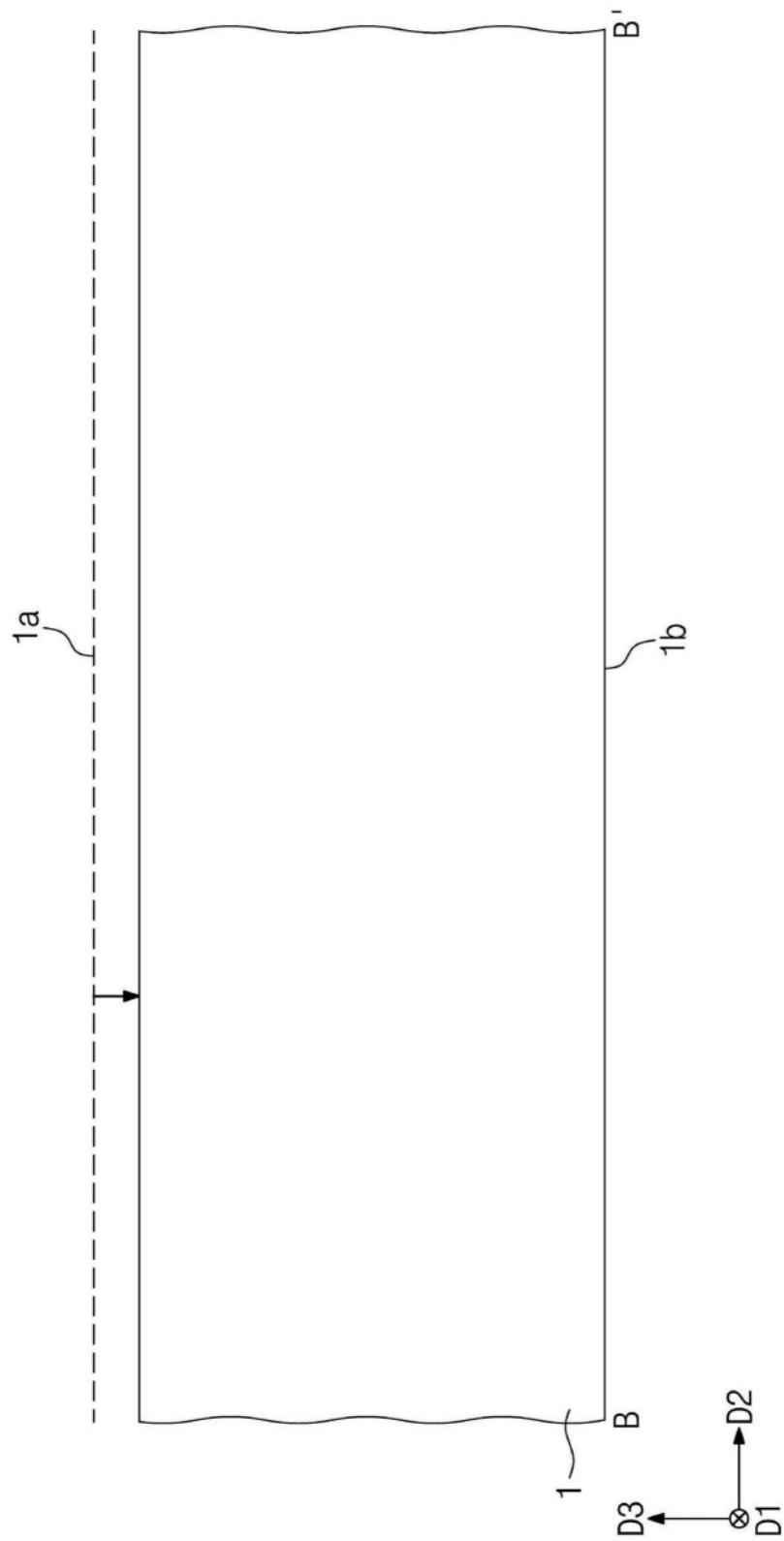

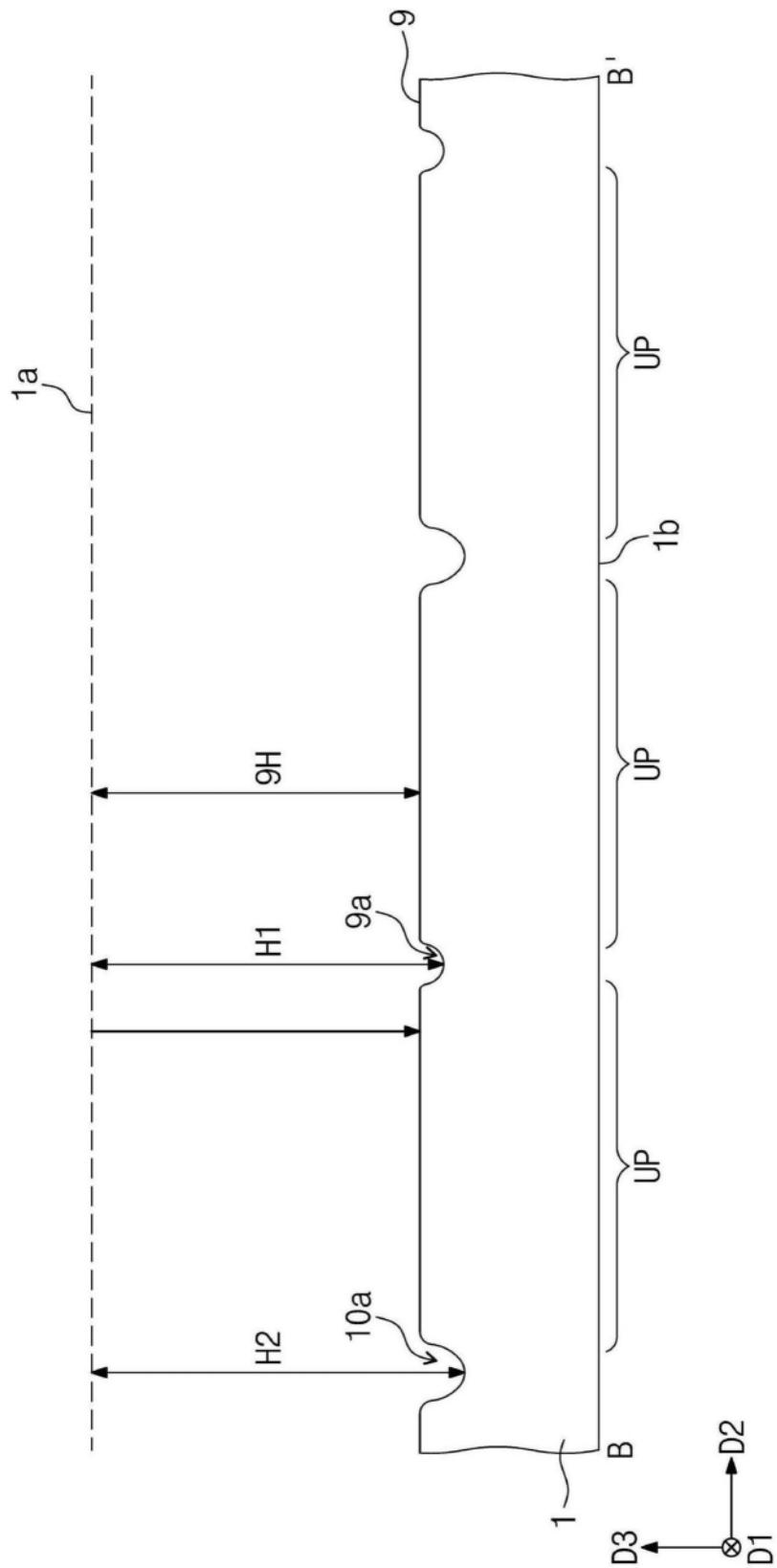

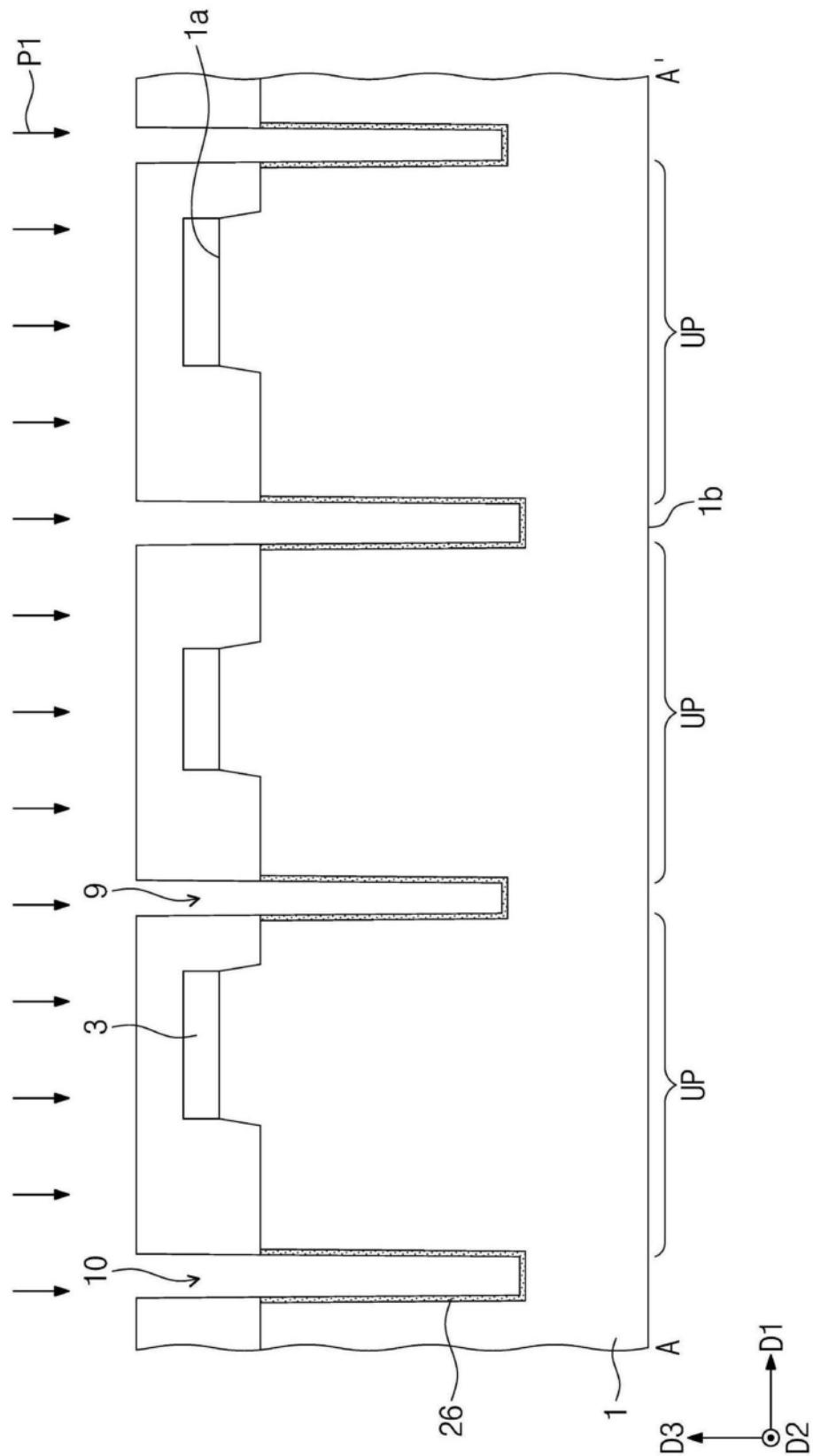

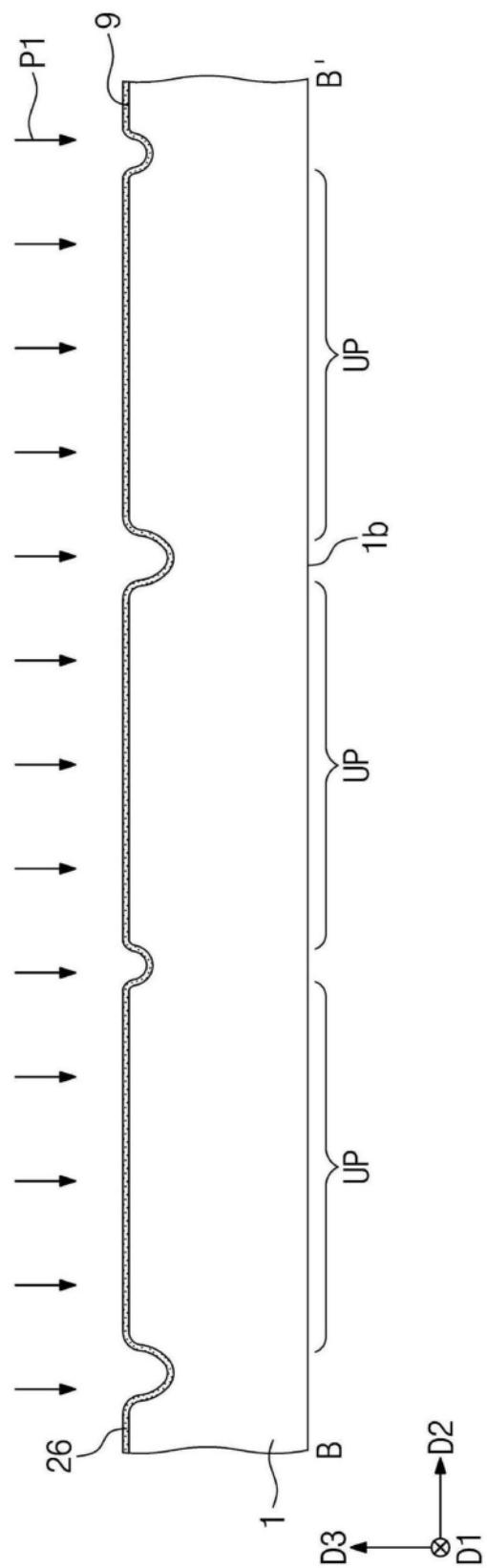

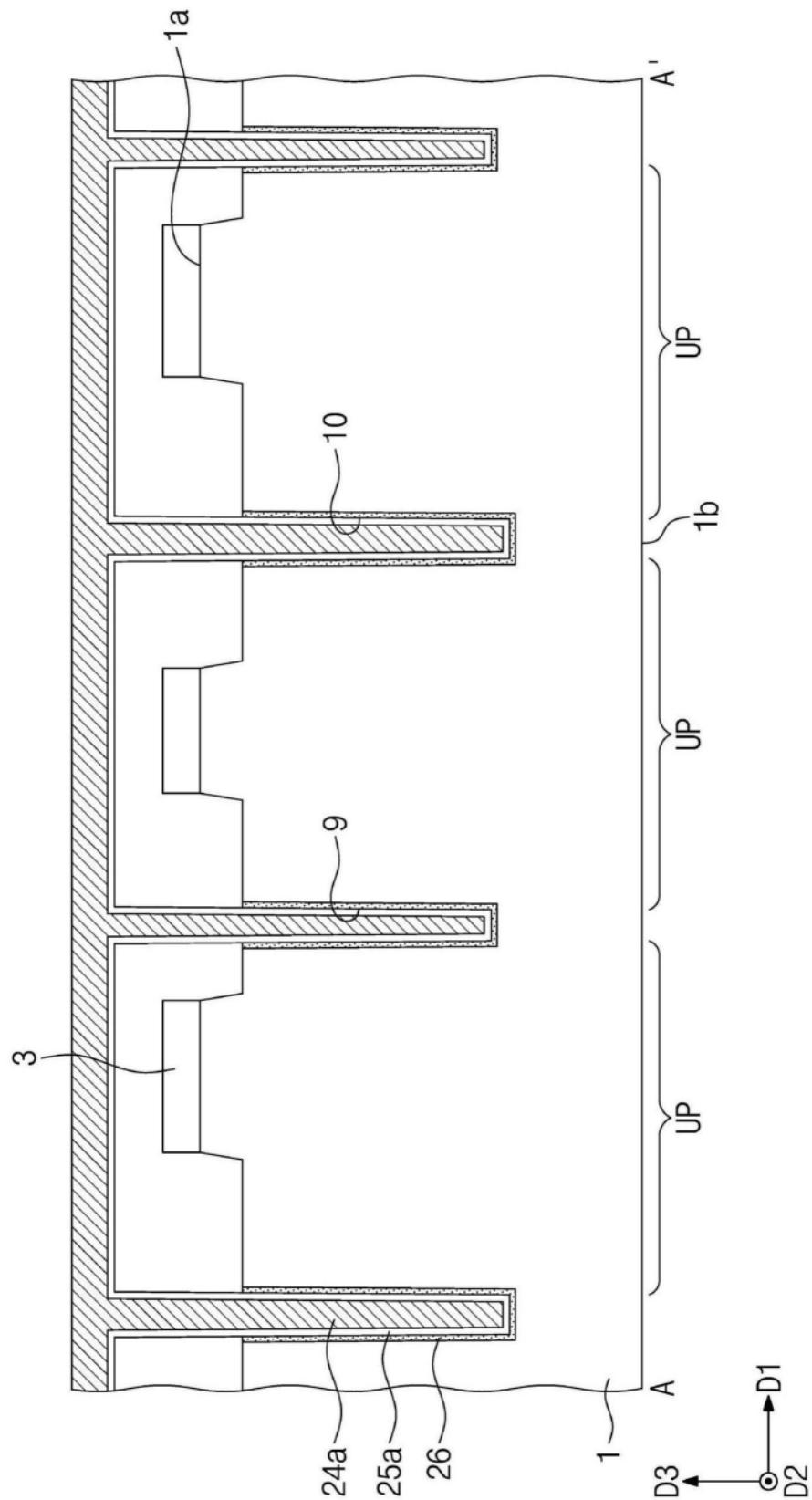

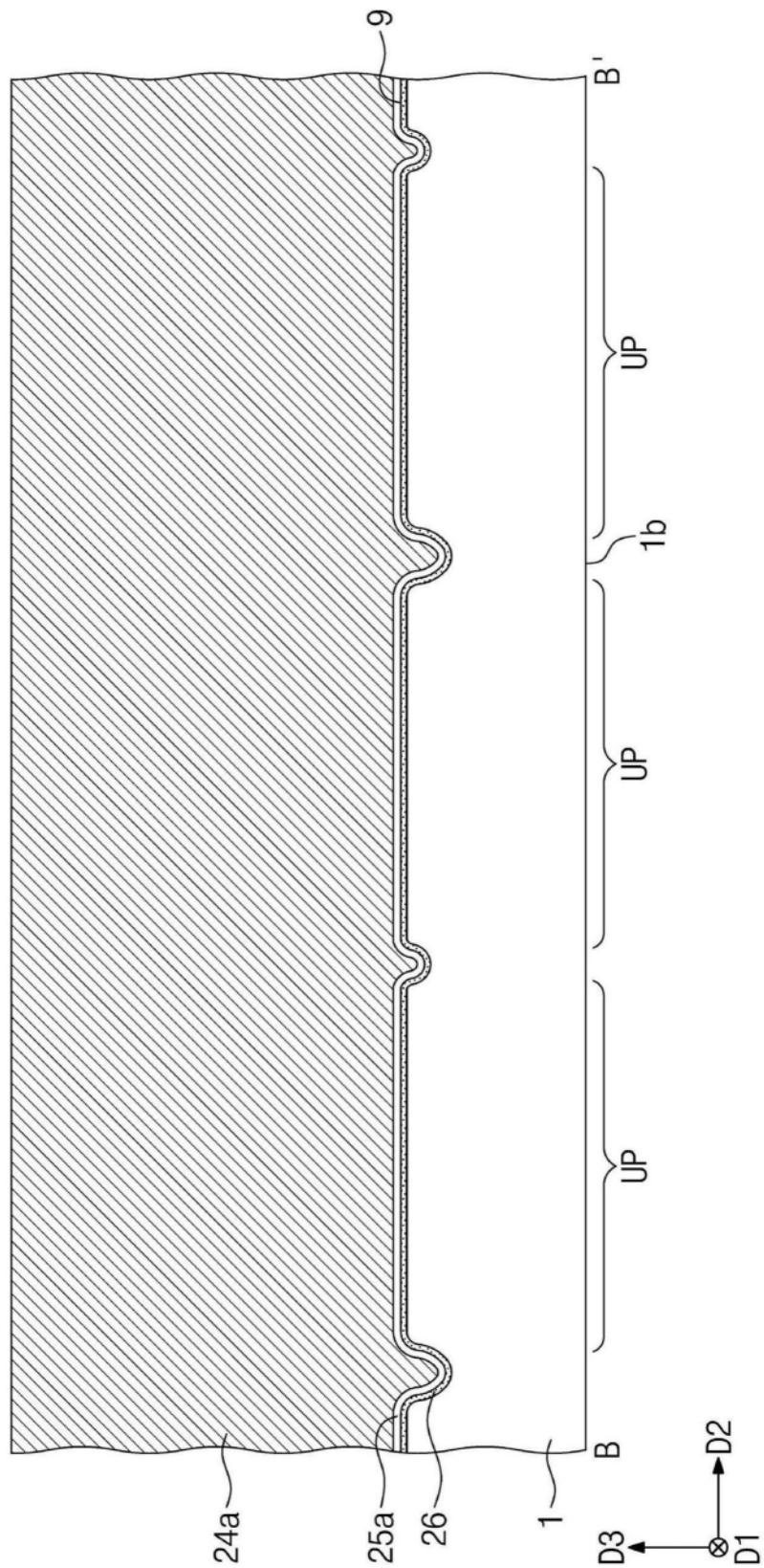

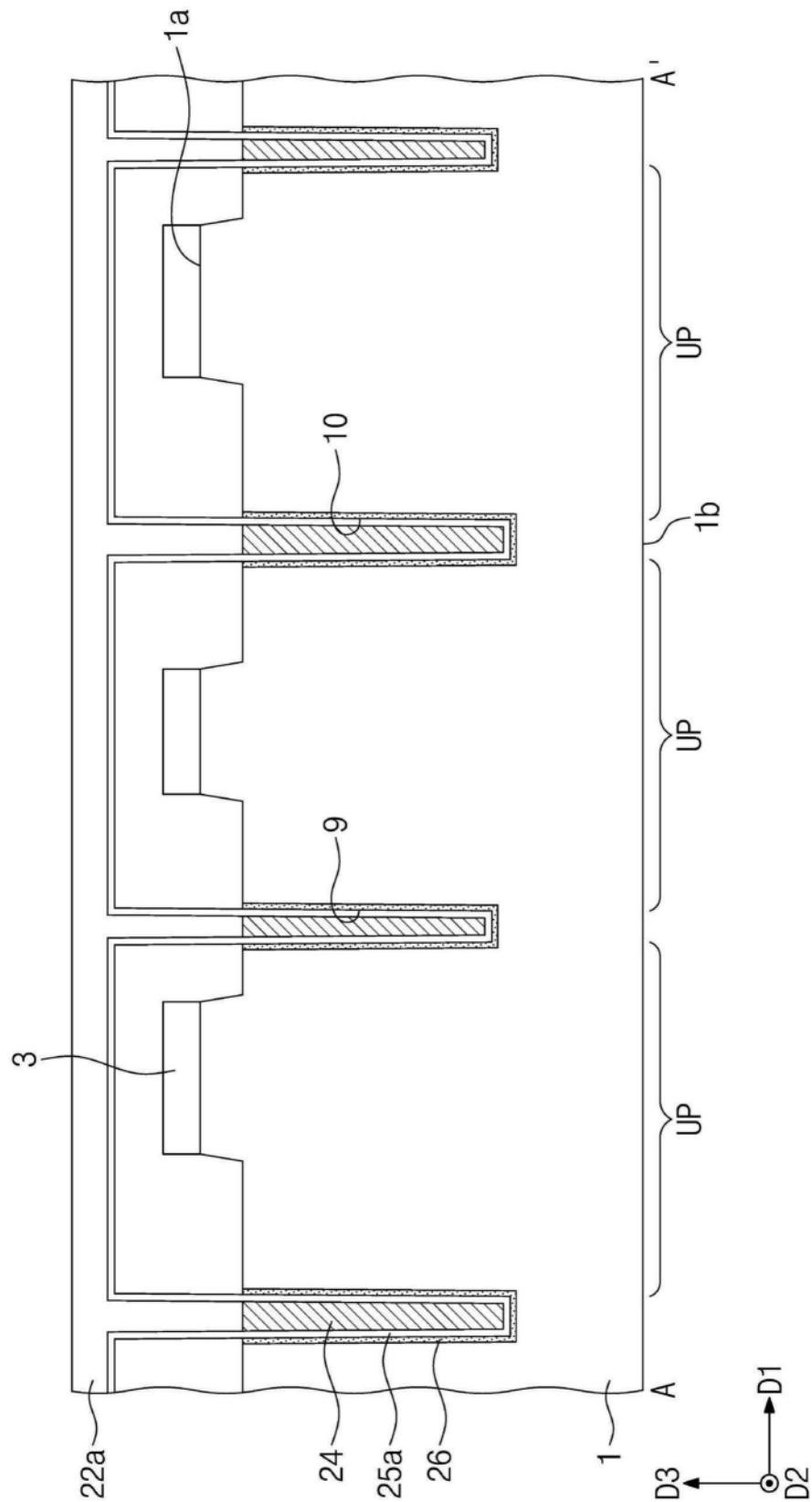

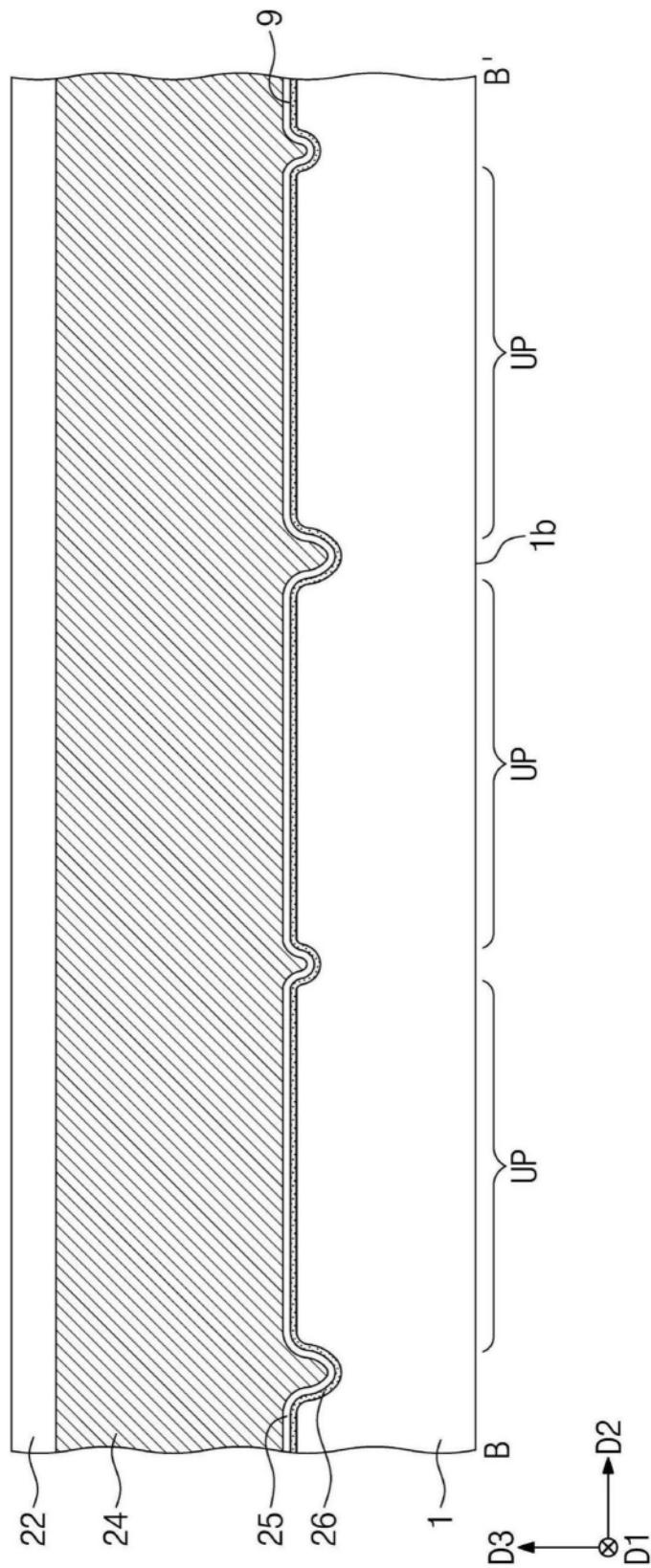

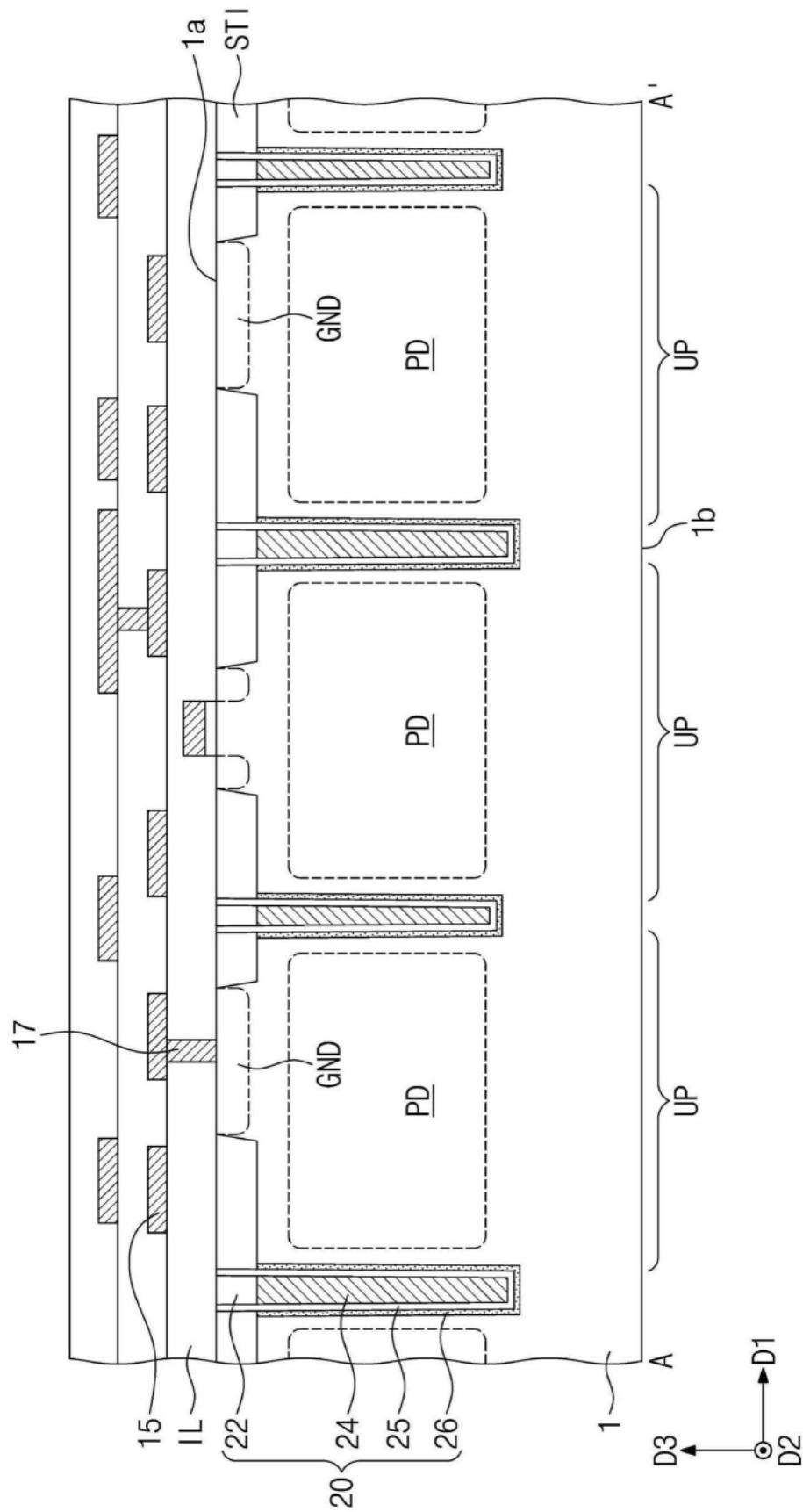

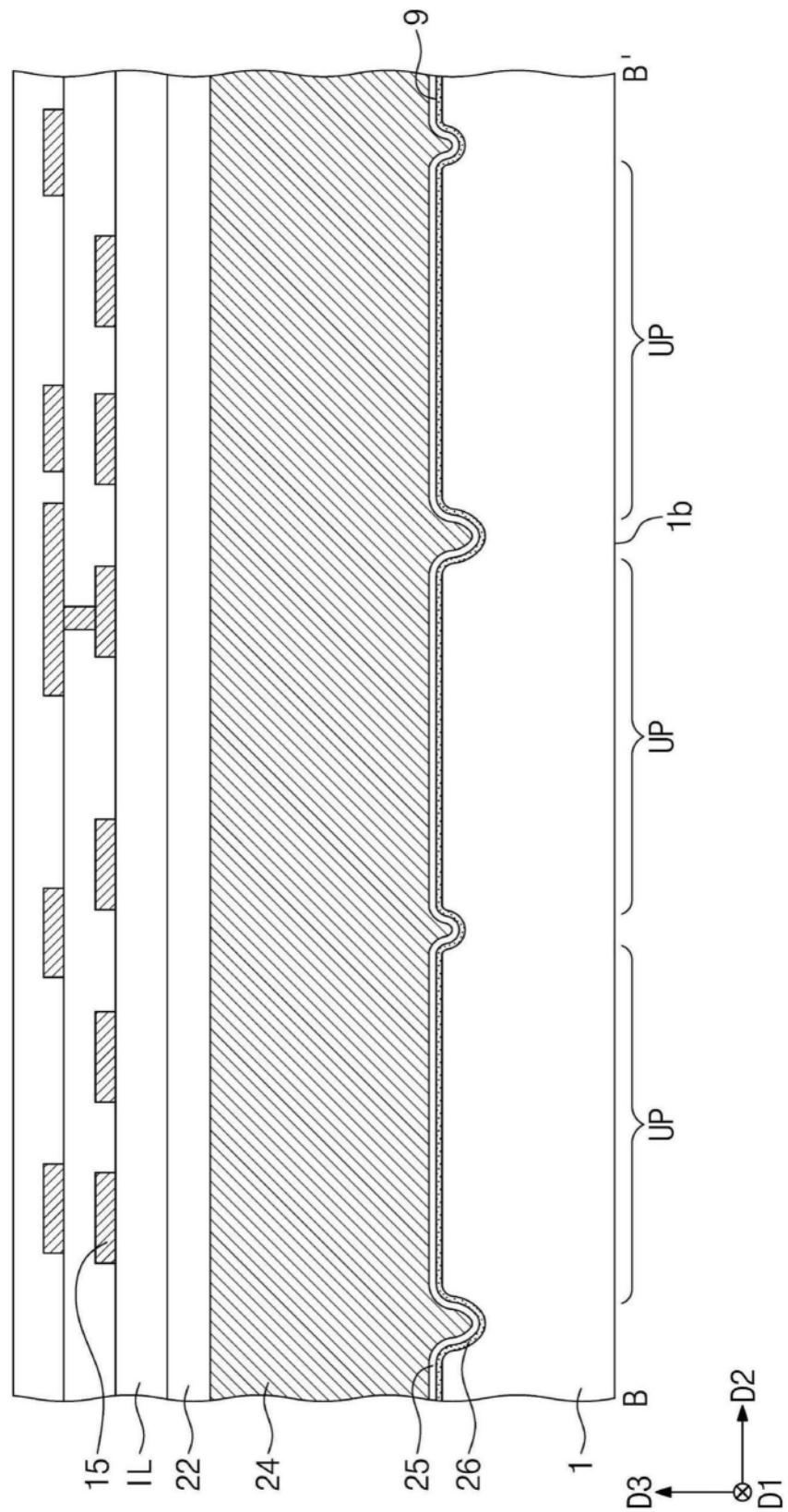

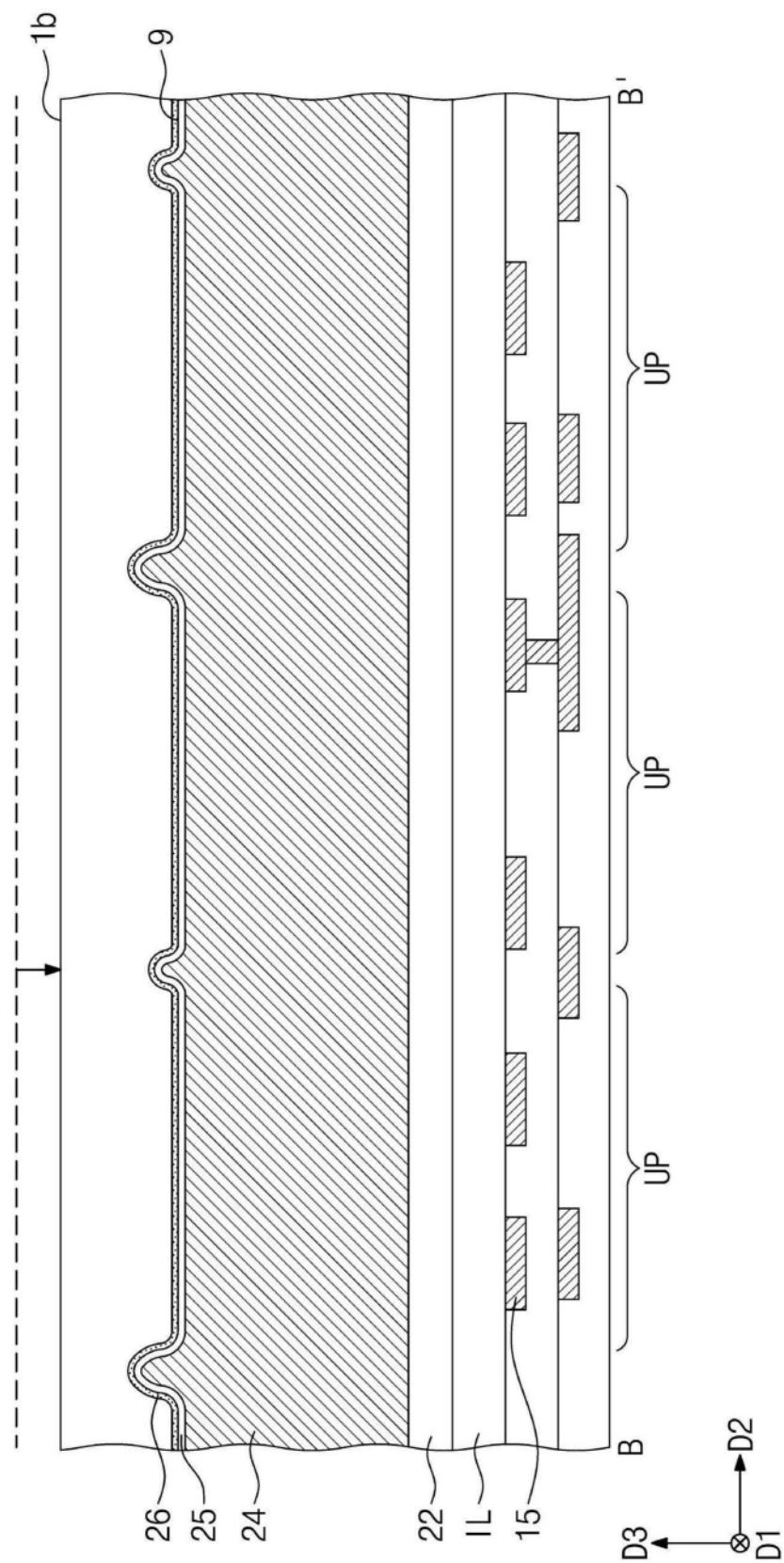

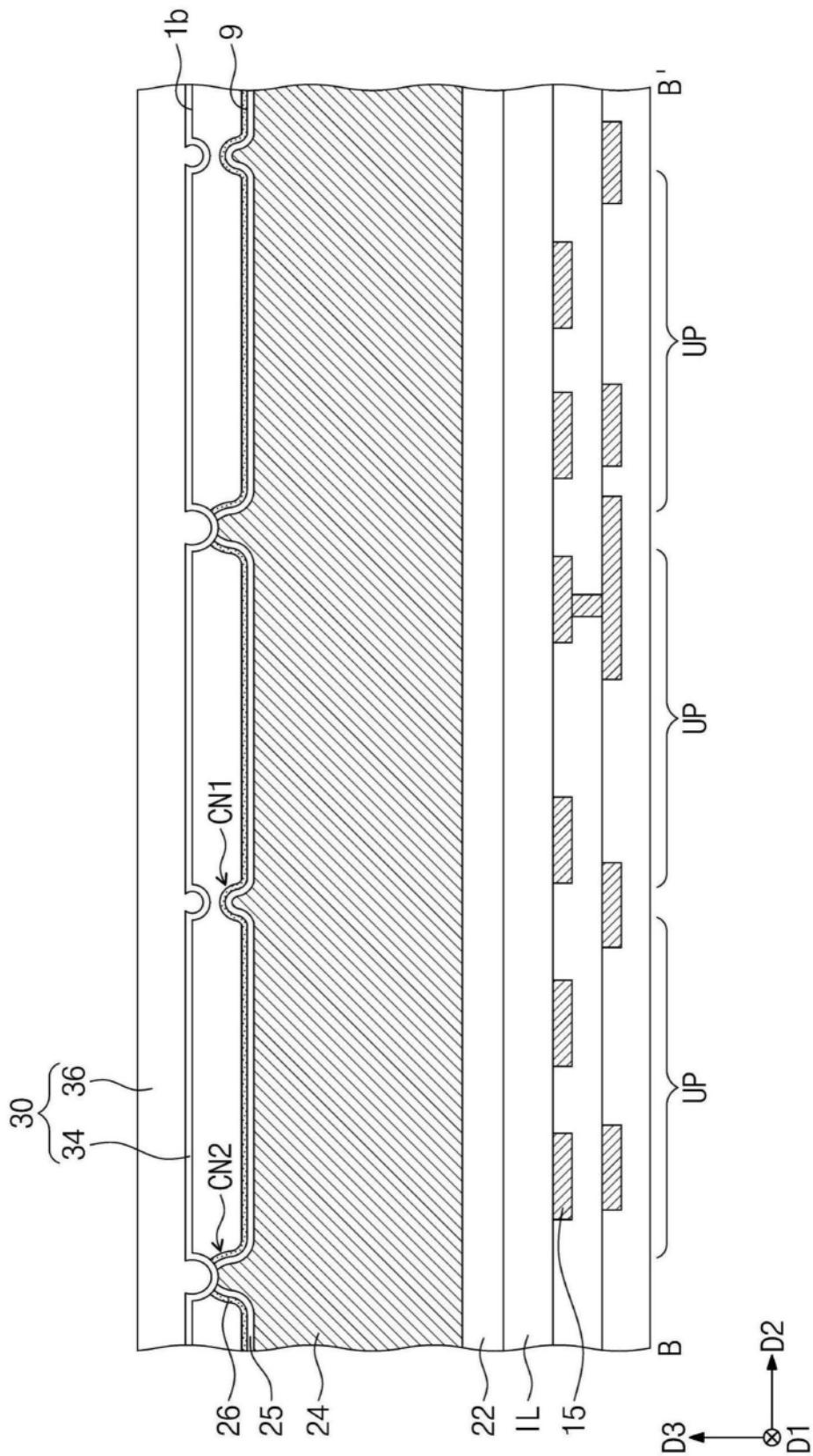

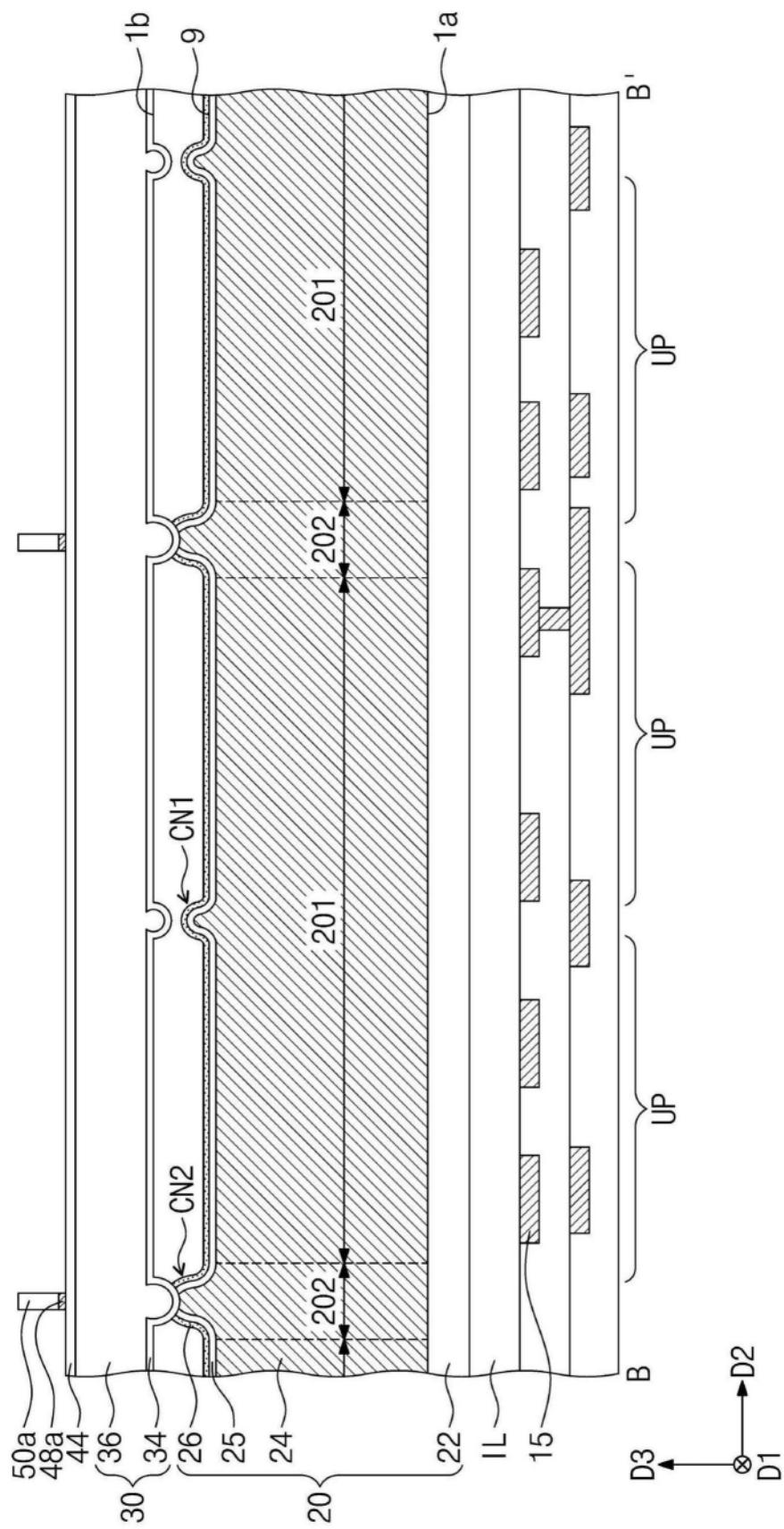

[0014] 图5B是根据发明构思的一些示例实施方式的沿图4的线B-B'截取的截面图。

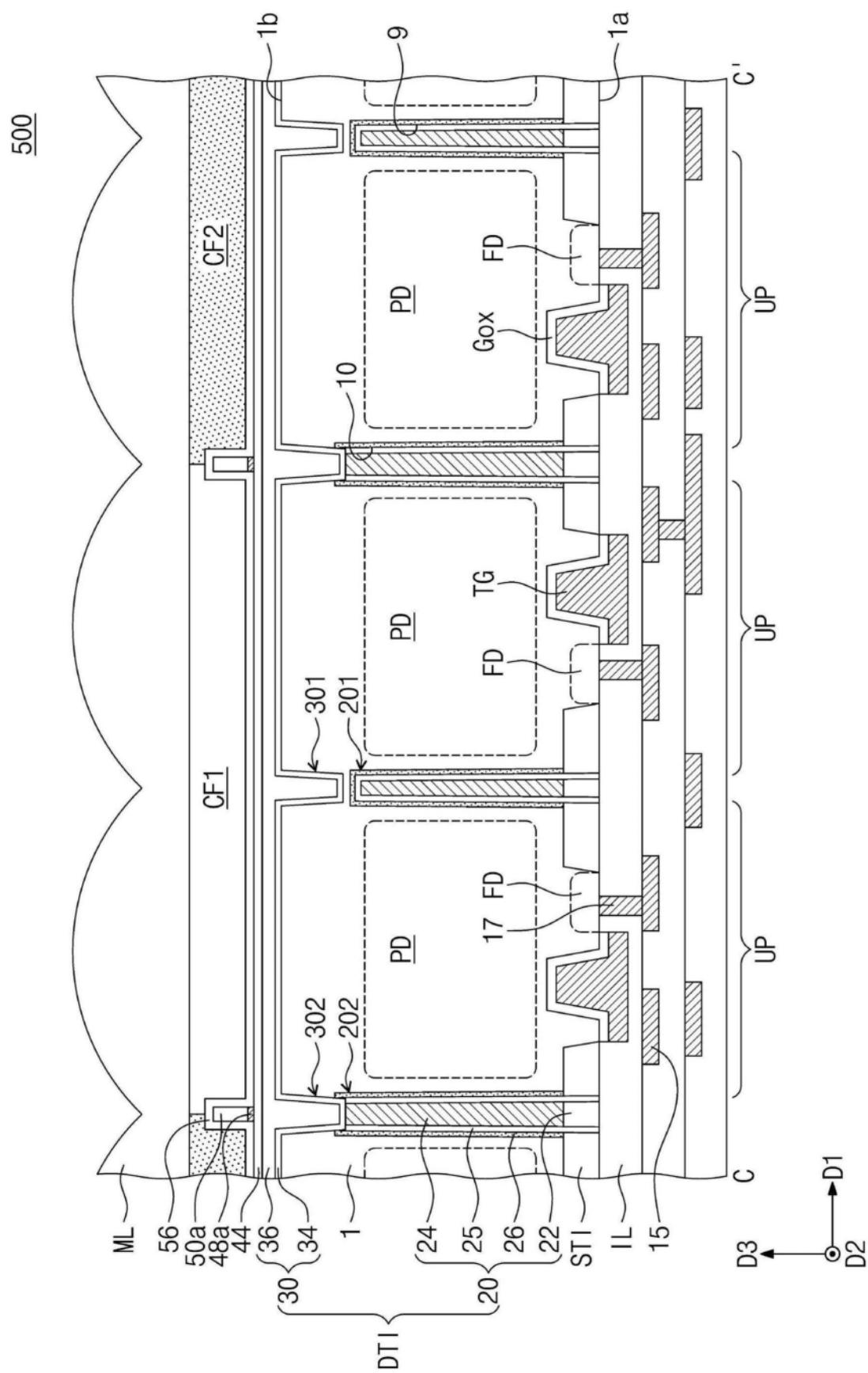

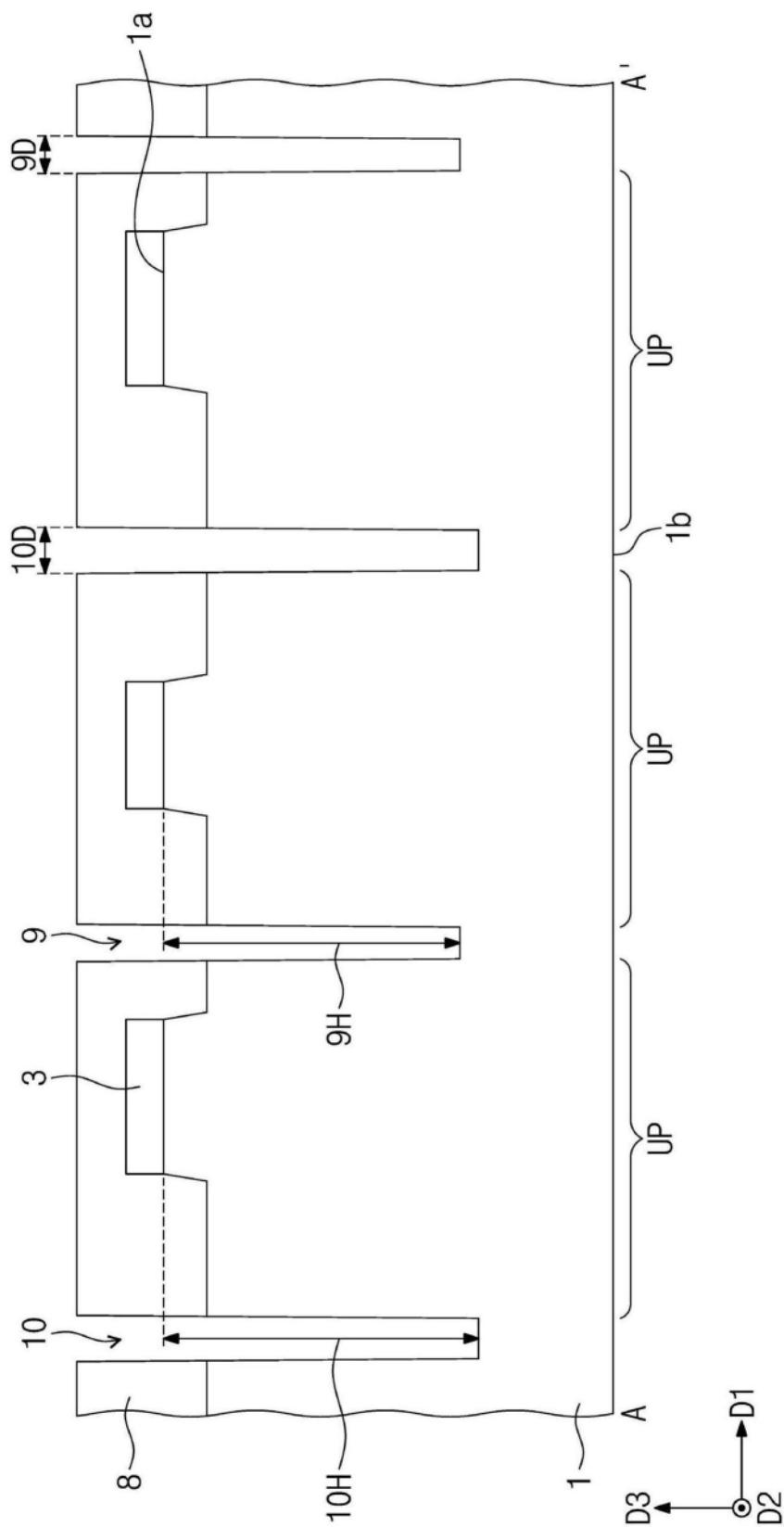

[0015] 图5C是根据发明构思的一些示例实施方式的沿图4的线C-C'截取的截面图。

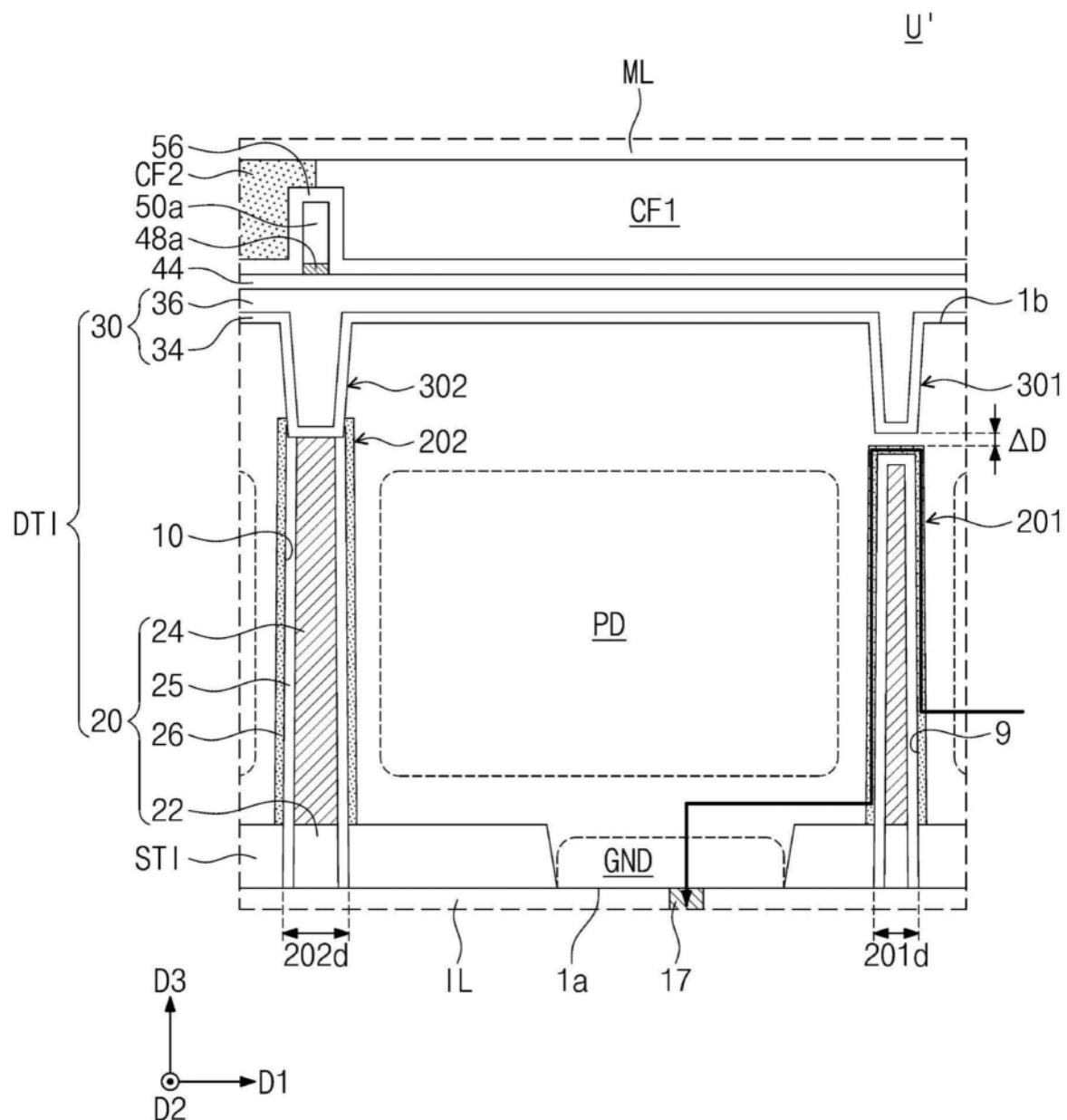

[0016] 图6是图5A的部分U'的放大图。

[0017] 图7是示出根据发明构思的一些示例实施方式的图像传感器的平面图。

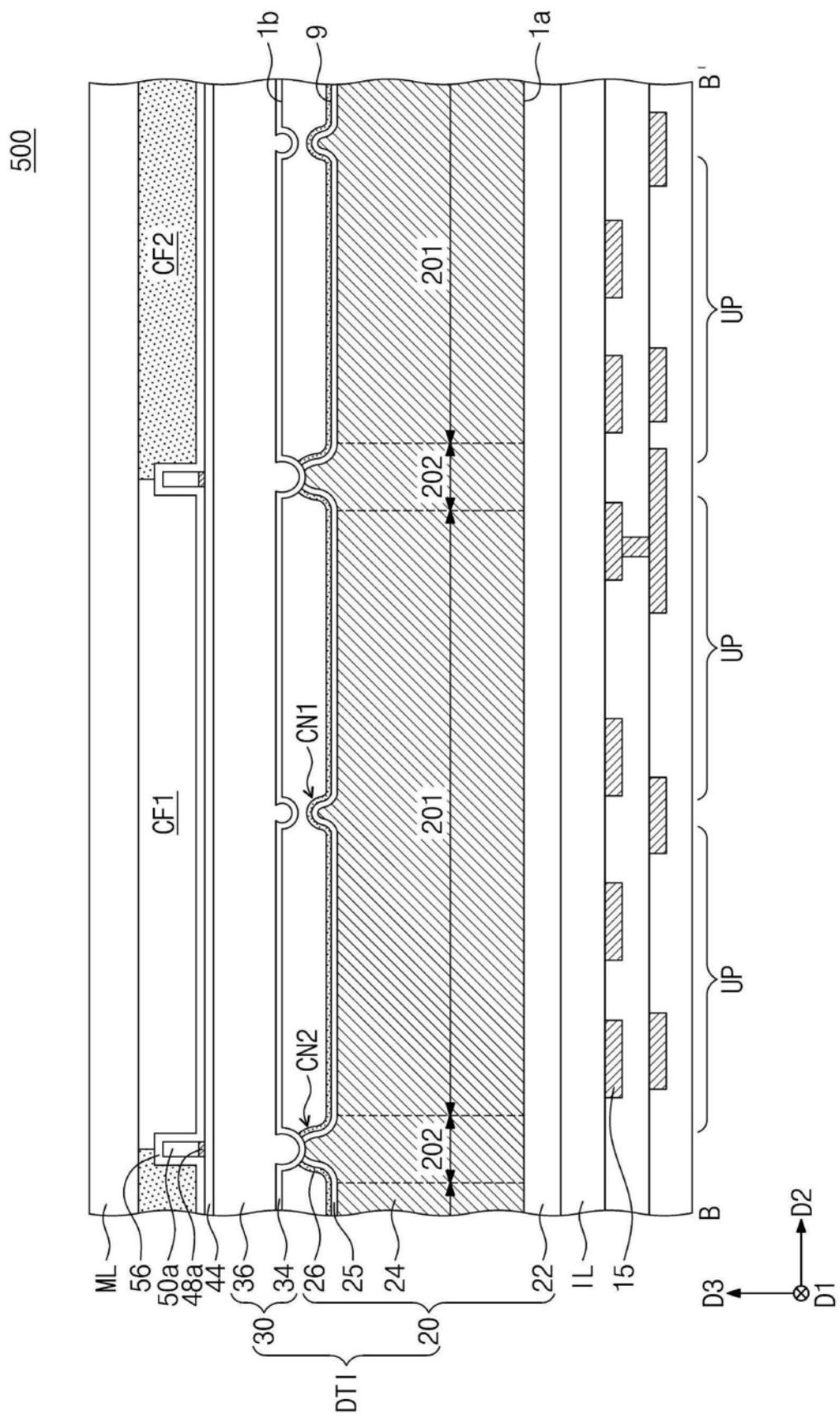

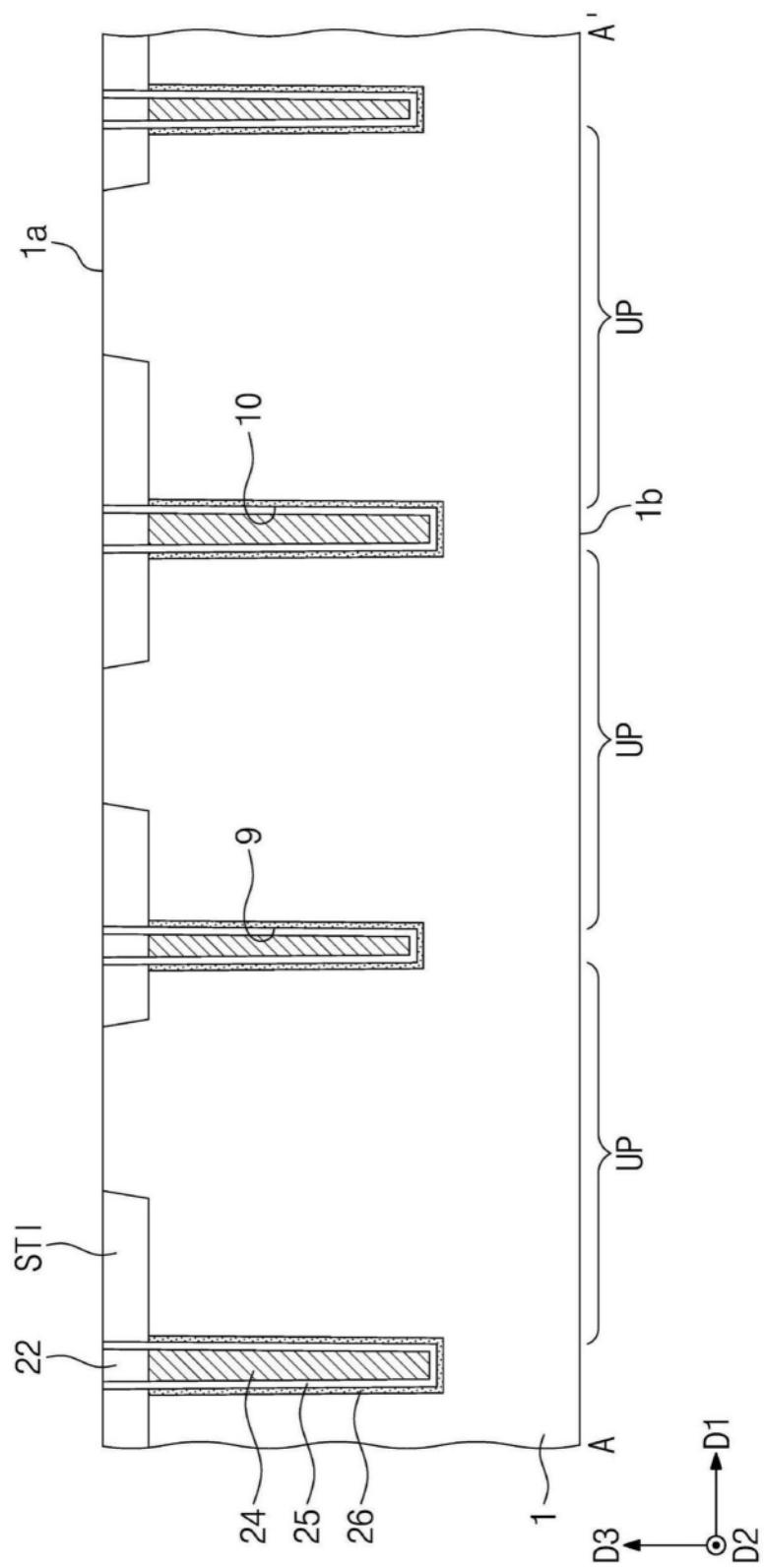

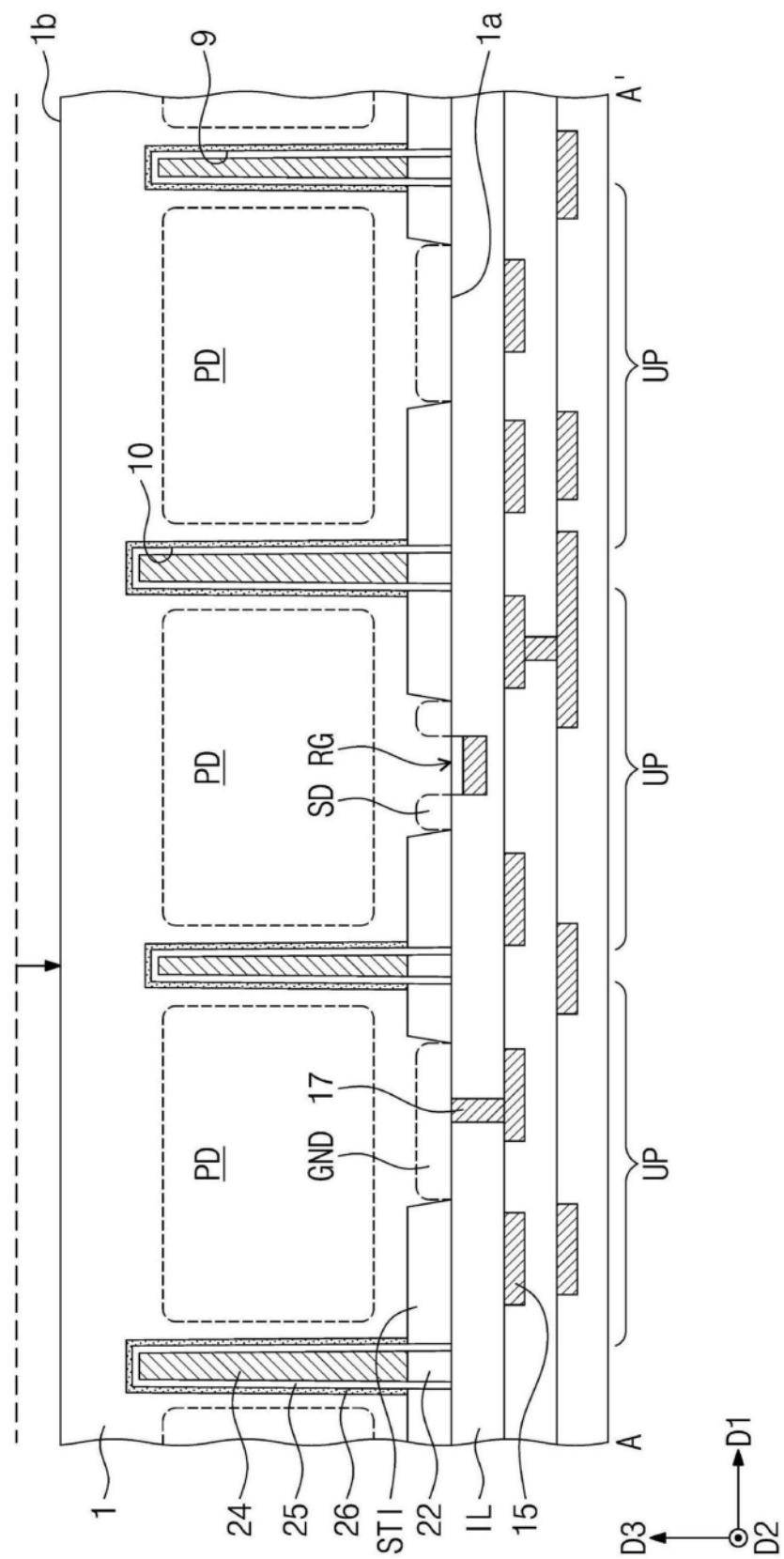

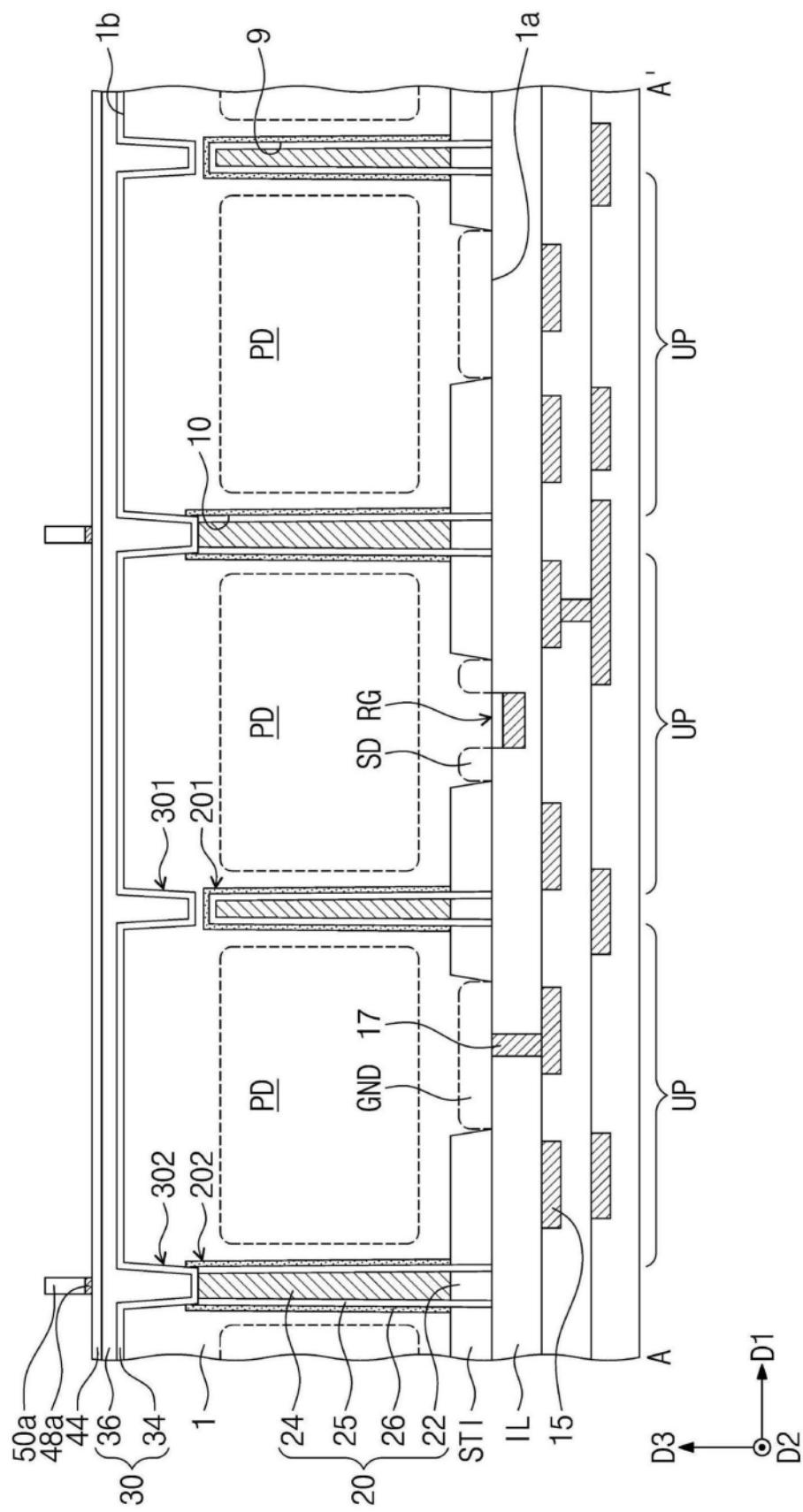

[0018] 图8A是根据发明构思的一些示例实施方式的沿图7的线A-A'截取的截面图。

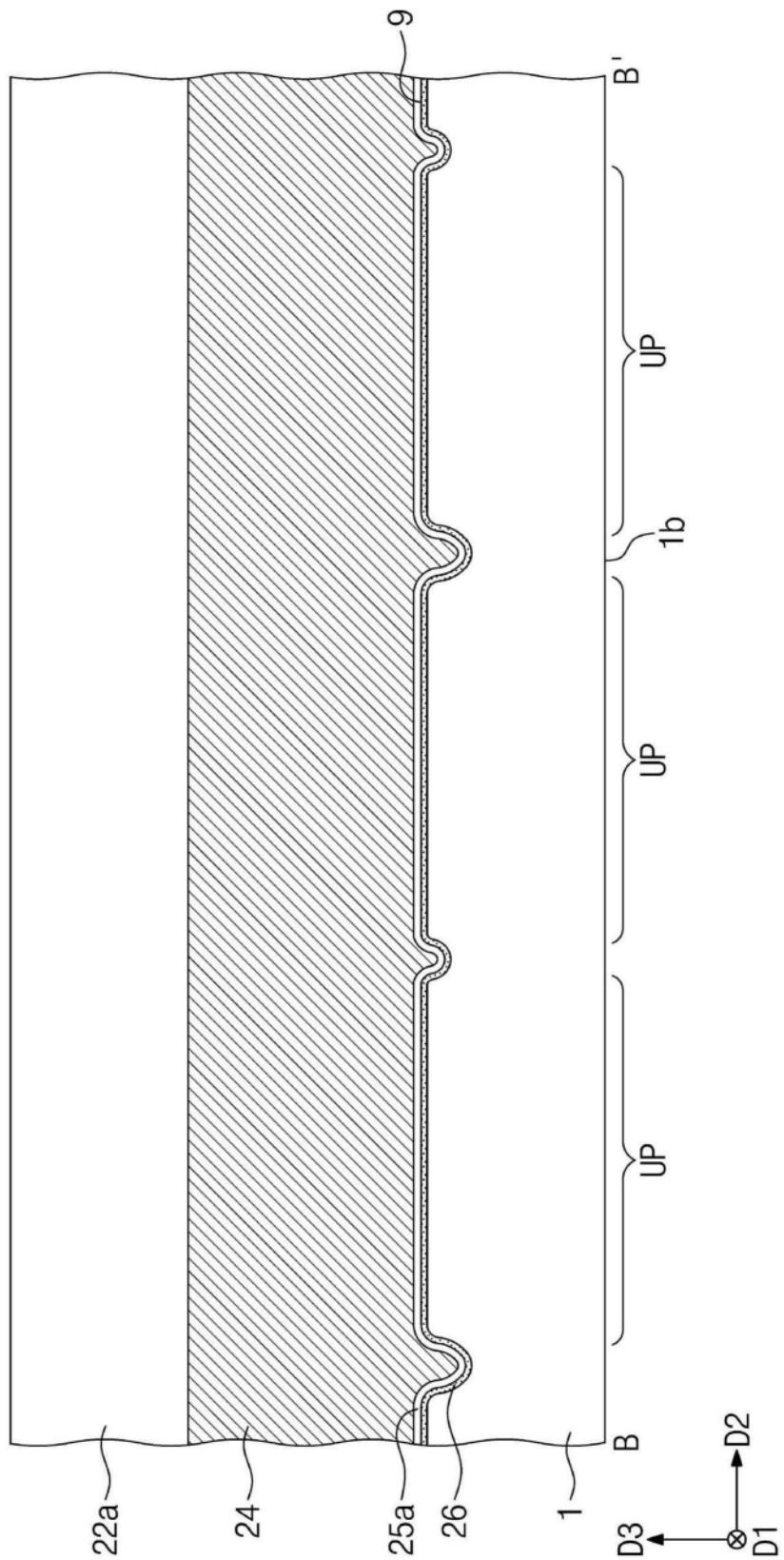

[0019] 图8B是根据发明构思的一些示例实施方式的沿图7的线B-B'截取的截面图。

[0020] 图9是根据发明构思的一些示例实施方式的图像传感器的平面图。

[0021] 图10A至图19A是制造图5A的图像传感器的方法的截面图。

[0022] 图10B至图19B是制造图5B的图像传感器的方法的截面图。

[0023] 图20是示出根据发明构思的一些示例实施方式的图像传感器的平面图。

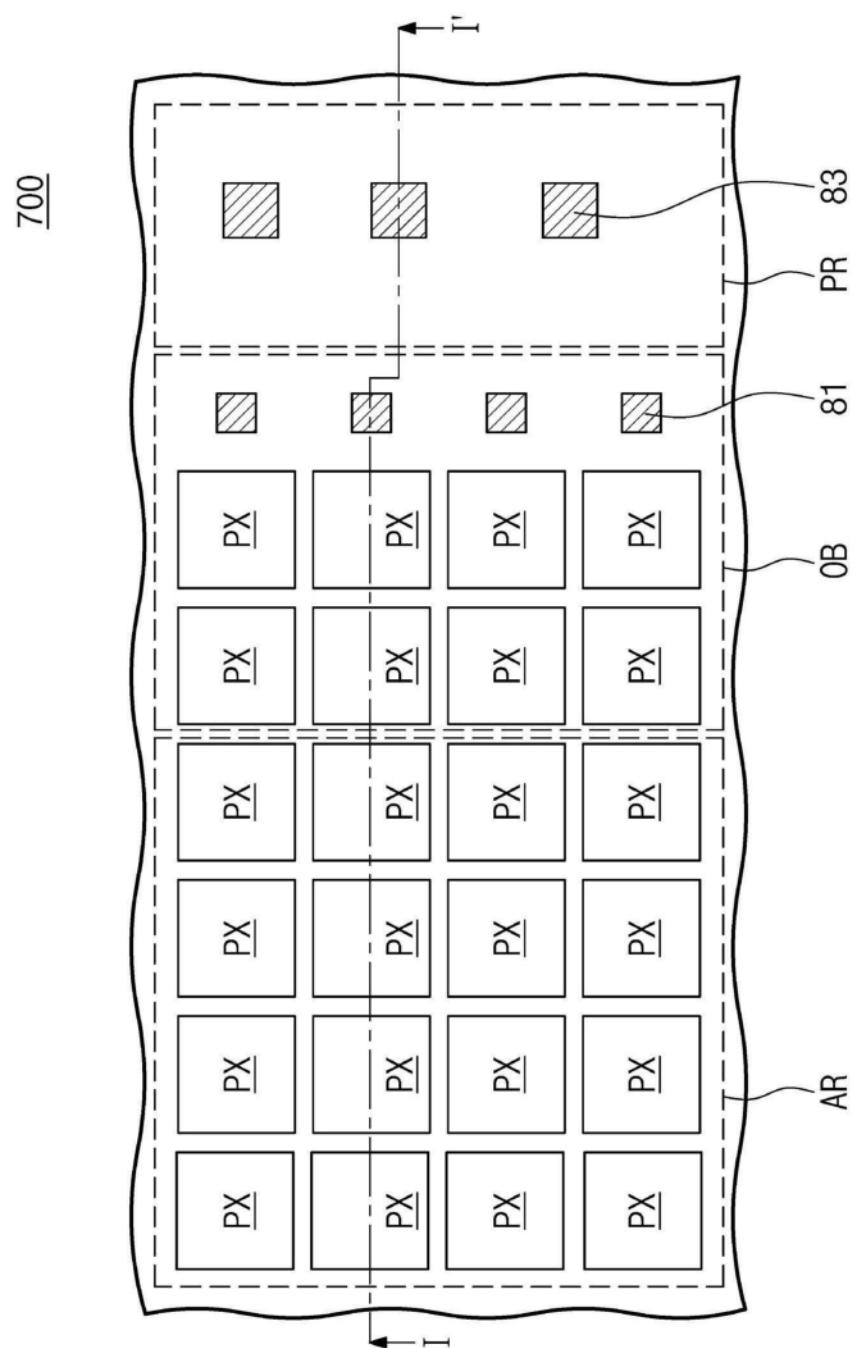

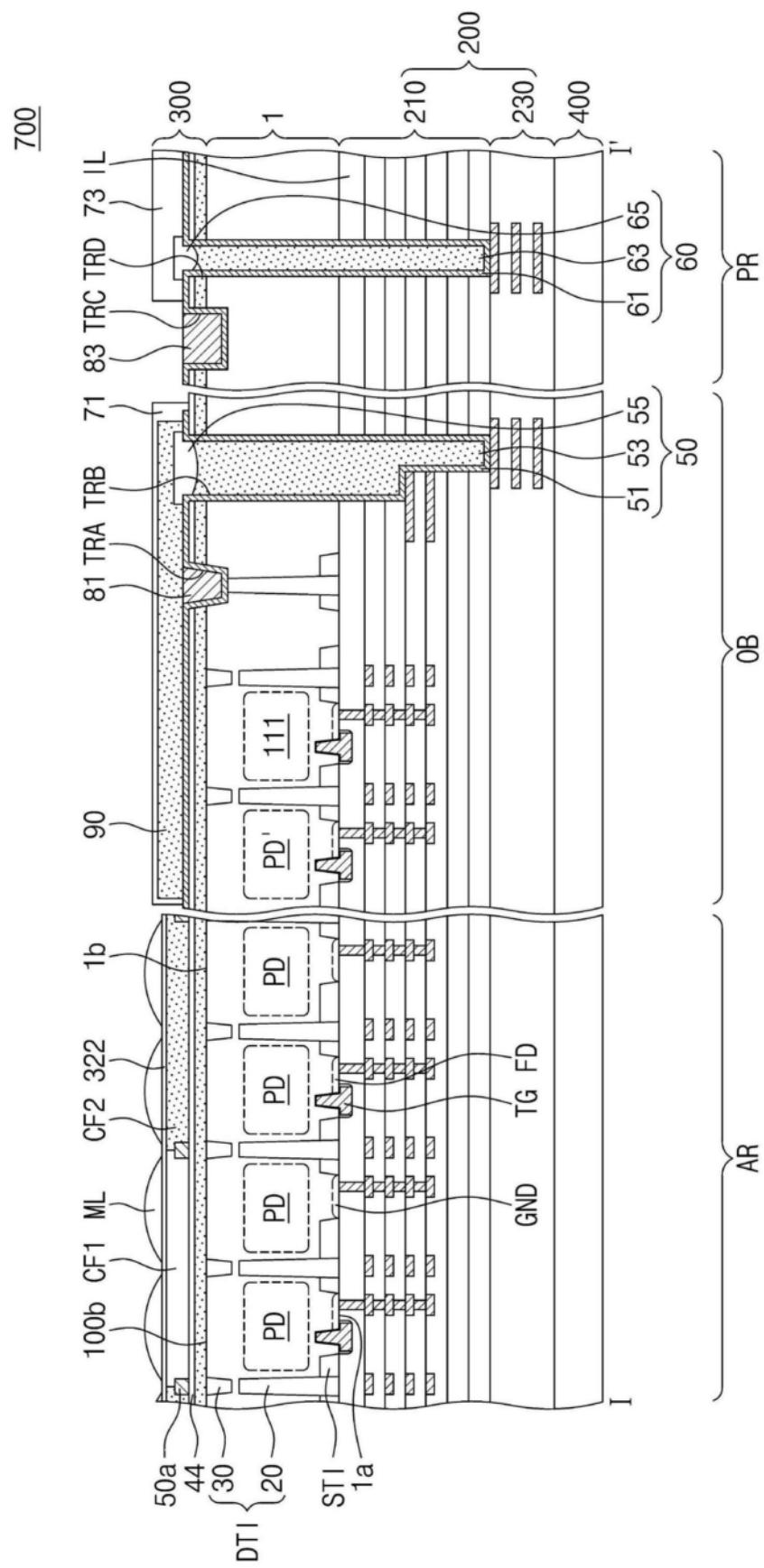

[0024] 图21是沿图20中的线I-I'截取的截面图。

## 具体实施方式

[0025] 现在将参照附图更全面地描述发明构思的示例实施方式。

[0026] 图1是根据发明构思的一些示例实施方式的图像传感器的框图。

[0027] 参照图1,图像传感器可以包括有源像素传感器阵列1001、行解码器1002、行驱动器1003、列解码器1004、定时发生器1005、相关双采样器(CDS)1006、模数转换器(ADC)1007和输入/输出(I/O)缓冲器1008。

[0028] 有源像素传感器阵列1001可以包括多个二维排列的单位像素,并且可以将光信号转换为电信号。有源像素传感器阵列1001可以由从行驱动器1003提供的多个驱动信号(例如像素选择信号、复位信号和电荷转移信号)驱动。此外,转换后的电信号可以被提供给相关双采样器1006。

[0029] 响应于在行解码器1002中解码的信号,行驱动器1003可以向有源像素传感器阵列1001提供用于驱动多个单位像素的多个驱动信号。当单位像素以矩阵形式排列时,可以以矩阵形式的行为单位提供驱动信号。

[0030] 定时发生器1005可以向行解码器1002和列解码器1004提供定时信号和控制信号。

[0031] 相关双采样器1006可以接收从有源像素传感器阵列1001产生的电信号,并且可以保持和采样所接收的电信号。相关双采样器1006可以对电信号的特定噪声电平和信号电平进行双采样,以输出与噪声电平和信号电平之差相对应的差电平。

[0032] 模数转换器1007可以将对应于相关双采样器1006输出的差值电平的模拟信号转换为数字信号,并且可以输出该数字信号。

[0033] I/O缓冲器1008可以锁存数字信号,并且可以响应于在列解码器1004中解码的信号,将锁存的数字信号顺序输出至图像信号处理单元(未显示)。

[0034] 图2是根据发明构思的一些示例实施方式的图像传感器的有源像素传感器阵列的电路图。特别地,图2是图1的有源像素传感器阵列1001的电路图。参照图2,多个像素组(例如第一像素组GRP1)中的每个可以包括第一至第四光电转换部分PD1、PD2、PD3和PD4,第一至第四传输晶体管TX1、TX2、TX3和TX4,以及逻辑晶体管RX、SX和DX。这里,逻辑晶体管可以包括复位晶体管RX、选择晶体管SX和驱动晶体管DX。第一至第四传输晶体管TX1、TX2、TX3和TX4、复位晶体管RX和选择晶体管SX的栅电极可以分别连接到驱动信号线TG1、TG2、TG3、TG4、RG和SG。

[0035] 第一至第四传输晶体管TX1、TX2、TX3和TX4可以分别包括第一至第四传输栅电极TG1、TG2、TG3和TG4以及第一至第四光电转换部分PD1、PD2、PD3和PD4。在一些示例实施方式中,第一至第四传输晶体管TX1、TX2、TX3和TX4可以分别连接到浮置扩散区FD。

[0036] 分别连接至传输晶体管TX1、TX2、TX3和TX4的多个浮置扩散区FD可以提供在像素组(例如GRP1)中。在一些示例实施方式中,可以在每个像素组(例如GRP1)中形成单个浮置扩散区FD。每个像素组(例如GRP1)中的传输晶体管TX1、TX2、TX3和TX4可以共享单个浮置扩散区FD。

[0037] 第一至第四(第一、第二、第三和第四)光电转换部分PD1、PD2、PD3和PD4可以产生并积累与从外部入射的光的量成比例的光电荷(或电荷)。第一至第四光电转换部分PD1、PD2、PD3和PD4中的每个可以包括光电二极管、光电晶体管、光电门、被钉扎光电二极管(PPD)或其任意组合。

[0038] 浮置扩散区FD可以接收在第一至第四光电转换部分PD1、PD2、PD3和PD4中产生的光电荷,并且可以累积地存储所接收的光电荷。可以根据浮置扩散区FD中累积的光电荷的量来控制驱动晶体管DX。

[0039] 复位晶体管RX可以定期地复位在浮置扩散区FD中累积的电荷。详细地，复位晶体管RX的漏电极可以连接到浮置扩散区FD，复位晶体管RX的源电极可以连接到电源电压 $V_{DD}$ 。当复位晶体管RX导通时，连接到复位晶体管RX的源电极的电源电压 $V_{DD}$ 可以传输到浮置扩散区FD。因此，当复位晶体管RX导通时，累积在浮置扩散区FD中的电荷可以被放电以复位浮置扩散区FD。

[0040] 驱动晶体管DX可以放大浮置扩散区FD中的电位变化，并且可以通过选择晶体管SX将放大的信号或像素信号输出至输出线Vout。驱动晶体管DX可以是源极跟随器缓冲放大器，其产生与输入到其栅电极的光电信号的量成比例的源极-漏极电流。驱动晶体管DX的栅电极可以连接到浮置扩散区FD，驱动晶体管DX的漏电极可以连接到电源电压 $V_{DD}$ ，驱动晶体管DX的源电极可以连接到选择晶体管SX的漏电极。

[0041] 选择晶体管SX可以选择将以行为单位被读取的像素。当选择晶体管SX导通时，连接到驱动晶体管DX的漏电极的电源电压 $V_{DD}$ 可以传输到选择晶体管SX的源电极。

[0042] 图3是根据发明构思的一些示例实施方式的图像传感器的平面图。

[0043] 参照图3，根据一些示例实施方式的图像传感器500可以包括沿第一方向D1和第二方向D2二维排列的第一至第三像素组GRP1、GRP2和GRP3。第一滤色器CF1可以设置在第一像素组GRP1上。第二滤色器CF2可以设置在第二像素组GRP2上。第三滤色器CF3可以设置在第三像素组GRP3上。第一至第三滤色器CF1至CF3可以具有不同的颜色。例如，第二滤色器CF2可以是绿色滤色器。第一滤色器CF1和第三滤色器CF3中的一个可以是红色滤色器，另一个可以是蓝色滤色器。图3的第一至第三像素组GRP1、GRP2和GRP3可以构成组单元，组单元可以提供为多个，并且所述多个组单元可以在第一方向D1和第二方向D2上二维排列。

[0044] 第一至第三像素组GRP1、GRP2和GRP3中的每个可以包括以 $N \times N$ 矩阵形式排列的 $N^2$ 个像素，该 $N \times N$ 矩阵形式由沿第二方向D2排列的N行和沿第一方向D1排列的N列组成。这里，‘N’可以是2或更大的自然数。

[0045] 例如，与图3类似，第一至第三像素组GRP1、GRP2和GRP3中的每个可以包括以 $2 \times 2$ 矩阵形式排列的第一至第四像素PX1至PX4，该 $2 \times 2$ 矩阵形式由沿第二方向D2排列的2行和沿第一方向D1排列的2列组成。在第一至第三像素组GRP1、GRP2和GRP3的每个中，第一和第二像素PX1和PX2可以沿第二方向D2依次排列，并且可以构成第一列。第三和第四像素PX3和PX4可以在第二方向D2上依次排列，并且可以构成第二列。第一和第三像素PX1和PX3可以沿第一方向D1依次排列，并且可以构成第一行。第二和第四像素PX2和PX4可以沿第一方向D1依次排列，并且可以构成第二行。光电转换部分PD可以分别设置在第一至第四像素PX1至PX4中。第一至第四像素PX1至PX4的光电转换部分PD可以对应于图5A至图5C的光电转换部分PD。

[0046] 微透镜阵列层ML可以设置在第一至第四像素PX1至PX4上。深器件隔离部分DTI可以在第一至第四像素PX1至PX4之间以及第一至第三像素组GRP1、GRP2和GRP3之间设置在基板1中。

[0047] 图4是对应于图3的图像传感器的平面图。图5A是根据发明构思的一些示例实施方式的沿着图4的线A-A'截取的截面图。图5B是根据发明构思的一些示例实施方式的沿着图4的线B-B'截取的截面图。图5C是根据发明构思的一些示例实施方式的沿着图4的线C-C'截取的截面图。图6是图5A的部分U'的放大图。

[0048] 参照图4、图5A、图5B和图5C，根据发明构思的一些示例实施方式的图像传感器500可以包括基板1。例如，基板1可以是单晶硅晶片、硅外延层或绝缘体上硅(SOI)基板。基板1可以掺有例如具有第一导电类型的掺杂剂。例如，第一导电类型可以是P型。基板1可以包括彼此相反的第一表面1a和第二表面1b。基板1可以包括图1的有源像素传感器阵列1001，并且图3的第一至第四像素PX1至PX4可以分别对应于单位像素UP。

[0049] 深器件隔离部分DTI可以设置在基板1中，以隔离/限定单位像素UP。当在平面图中观察时，深器件隔离部分DTI可以具有网格形状。

[0050] 光电转换部分PD可以分别设置在单位像素UP的基板1中。光电转换部分PD可以掺杂有具有与第一导电类型相反的第二导电类型的掺杂剂。例如，第二导电类型可以是N型。光电转换部分PD的N型掺杂剂可以在光电转换部分PD周围与基板1的P型掺杂剂形成PN结，以提供光电二极管。

[0051] 邻近第一表面1a的浅器件隔离部分STI可以设置在基板1中。深器件隔离部分DTI可以穿透浅器件隔离部分STI。浅器件隔离部分STI可以在每个单位像素UP中限定与第一表面1a相邻的有源区ACT。可以针对图2的晶体管TX、RX、DX和SX提供有源区ACT。

[0052] 在每个单位像素UP中，传输栅极TG可以设置在基板1的第一表面1a上。传输栅极TG的一部分可以延伸到基板1中。传输栅极TG可以是垂直型栅极。或者，传输栅极TG可以是不延伸到基板1中但具有平坦形状的平面型栅极。栅极绝缘层Gox可以设置在传输栅极TG和基板1之间。浮置扩散区FD可以设置在传输栅极TG一侧的基板1中。例如，浮置扩散区FD可以掺有具有第二导电类型(例如N型)的掺杂剂。

[0053] 图像传感器500可以是背侧照明图像传感器。光可以通过基板1的第二表面1b入射到基板1中。入射光可以在PN结的耗尽区中产生电子-空穴对。所产生的电子可以移动到光电转换部分PD中。当电压被施加到传输栅极TG时，电子可以移动到浮置扩散区FD中。

[0054] 在单位像素(第一单位像素)UP中，接地区域GND可以提供在基板1中，并且可以与第一表面1a和传输栅极TG相邻。接地区域GND可以具有与基板1相同的导电类型。接地区域GND可以是掺有具有第一导电类型的掺杂剂的区域。在另一单位像素(第二单位像素)UP中，复位栅极RG可以设置在第一表面1a上与传输栅极TG相邻。在又一个单位像素(第三单位像素)UP中，源极跟随器栅极SF可以设置在第一表面1a上与传输栅极TG相邻。在又一个单位像素(第四单位像素)UP中，选择栅极SEL可以设置在第一表面1a上与传输栅极TG相邻。栅极TG、RG、SF和SEL可以分别对应于图2的晶体管TX、RX、DX和SX的栅电极。源极/漏极区SD可以提供在复位栅极RG、源极跟随器栅极SF和选择栅极SEL中的每个的两侧。接地区域GND和栅极TG、RG、SF和SEL可以与有源区ACT重叠。第一至第四单位像素UP可以构成像素组(例如GRP1、GRP2或GRP3)。

[0055] 第一表面1a可以由第一层间绝缘层IL覆盖。每个第一层间绝缘层IL可以由硅氧化物层、硅氮化物层、硅氮氧化物层和多孔低k电介质层中的至少一种形成。互连线15可以设置在第一层间绝缘层IL之间或之中。接地区域GND可以电连接到接触插塞17中的相应接触插塞17和互连线15中的相应互连线15。接触插塞17可以穿透第一层间绝缘层IL中的最靠近第一表面1a的第一层间绝缘层IL。接地电压可以通过相应的互连线15和接地区域GND施加到基板1。接地区域GND可以邻近深器件隔离部分DTI设置。接地区域GND的布局形状可以各种各样地修改，接地区域GND可以具有诸如L形或倒L形的形状。浮置扩散区FD可以电连接到

接触插塞17中的相应接触插塞17和互连线15中的相应互连线15。

[0056] 深器件隔离部分DTI可以包括第一隔离部分20和第二隔离部分30。第一隔离部分20可以包括第一隔离图案201和第二隔离图案202。第二隔离部分30可以包括第三隔离图案301和第四隔离图案302。第一隔离部分20可以从第一表面1a向第二表面1b延伸。第二隔离部分30可以从第二表面1b向第一表面1a延伸。

[0057] 第一隔离部分20可以包括第一隔离图案201和第二隔离图案202。第一隔离图案201可以提供在每个像素组GRP1、GRP2和GRP3中的两个相邻单位像素UP之间。第二隔离图案202可以提供在像素组GRP1、GRP2和GRP3之间。

[0058] 第一隔离图案201在第一方向D1上的宽度201d可以小于第二隔离图案202在第一方向D1上的宽度202d。第一隔离图案201可以比第二隔离图案202从第一表面1a向第二表面1b延伸得少。换言之，第一隔离图案201的长度可以小于第二隔离图案202的长度。第一隔离图案201和第二隔离图案202的长度可以意指在垂直于第一表面1a的第三方向D3上从基板1的第一表面1a起的长度。

[0059] 第二隔离部分30可以包括第三隔离图案301和第四隔离图案302。第三隔离图案301可以提供在每个像素组GRP1、GRP2和GRP3中的两个相邻单位像素UP之间。第四隔离图案302可以提供在像素组GRP1、GRP2和GRP3之间。

[0060] 第一隔离图案201和第三隔离图案301可以彼此垂直重叠(或对准)，并且可以彼此间隔开。第一隔离图案201和第三隔离图案301之间的距离 $\triangle D$ 可以在从100nm至300nm的范围内(见图6)。第二隔离图案202和第四隔离图案302可以彼此垂直重叠(或对准)，并且可以彼此接触。

[0061] 第一隔离部分20可以包括填充绝缘图案22、导电图案24、衬垫绝缘图案25和高浓度掺杂图案26。填充绝缘图案22可以设置在层间绝缘层IL上。导电图案24可以提供在填充绝缘图案22上，并且可以与层间绝缘层IL间隔开，且填充绝缘图案22插置在其间。衬垫绝缘图案25可以设置在导电图案24和基板1之间以及在填充绝缘图案22和浅器件隔离部分STI之间。

[0062] 填充绝缘图案22和/或衬垫绝缘图案25可以包括例如硅氧化物。导电图案24可以与基板1间隔开。导电图案24可以包括掺有掺杂剂的多晶硅层或硅锗层。例如，掺在多晶硅层或硅锗层中的掺杂剂可以包括硼、磷或砷。

[0063] 填充绝缘图案22、导电图案24和衬垫绝缘图案25可以填充第一深沟槽9和第二深沟槽10。高浓度掺杂图案26可以形成在第一深沟槽9和第二深沟槽10的内表面区域中。高浓度掺杂图案26可以是基板1的用具有第一导电类型的掺杂剂掺杂的区域。高浓度掺杂图案26可以具有比基板1的掺杂浓度高的掺杂浓度，并且可以具有例如 $1 \times 10^{17}/\text{cm}^3$ 至 $1 \times 10^{19}/\text{cm}^3$ 的掺杂浓度。

[0064] 第二隔离部分30可以包括第一固定电荷层34和绝缘图案36。第一固定电荷层34可以由单层或多层形成，包括包含就化学计量比而言不足的氧的金属氧化物层和就化学计量比而言不足的氟的金属氟化物层中的至少一种。因此，第一固定电荷层34可以具有负的固定电荷。第一固定电荷层34可以由金属氧化物或金属氟化物的单层或多层形成，该金属氧化物或金属氟化物包括从由铪(Hf)、锆(Zr)、铝(Al)、钽(Ta)、钛(Ti)、钇(Y)和镧系元素组成的组中选择的至少一种金属。例如，第一固定电荷层34可以包括铪氧化物和/或铝氧化

物。暗电流和白点可以通过第一固定电荷层34减少。绝缘图案36可以提供在第一固定电荷层34上。例如，绝缘图案36可以包括硅氧化物。

[0065] 第一固定电荷层34可以与基板1的表面接触。第一固定电荷层34可以覆盖在基板1的第二表面1b中形成的沟槽。第一固定电荷层34可以与第二隔离图案202的衬垫绝缘图案25和/或导电图案24接触。第二隔离图案202的高浓度掺杂图案26可以不被第一固定电荷层34连接。相反，第一隔离图案201的高浓度掺杂图案26在相邻的单位像素UP之间可以是连续的。

[0066] 与图5B类似，在像素组（例如GRP1、GRP2或GRP3）中的四个相邻单元像素UP彼此相邻的位置CN1处，像素组（例如GRP1）中的两个邻近单元像素UP之间从第二表面1b到第一隔离图案201的顶表面的第一距离可以大于在像素组（例如，GRP1、GRP2或GRP3）中的四个相邻单位像素UP彼此相邻的位置CN1处从第二表面1b到第一隔离图案201的顶表面的第二距离。此外，在相邻像素组（例如GRP1和GRP2）之间的四个邻近单位像素UP彼此相邻的位置CN2处，第二表面1b的最低水平可以低于第二隔离图案202的顶表面的水平。

[0067] 根据发明构思的一些示例实施方式，每个像素组（例如GRP1、GRP2和GRP3）中包含的像素可以共享接地区域GND。例如，在其中四个像素构成像图3和图4那样的单个像素组的情况下，可以在这四个像素中的一个（例如PX2）中选择性地提供接地区域GND。由于第一隔离图案201和第三隔离图案301彼此不接触，所以其中没有提供接地区域GND的像素（例如PX1、PX3和PX4）的正电荷可以通过第一隔离图案201的连续高浓度掺杂图案26（见图6）移动到具有接地区域GND的像素（例如PX2）中。结果，即使所述三个像素不具有接地区域GND，所述三个像素的正电荷也可以通过第一隔离图案201释放到接地区域GND中。此外，由于所述三个像素不需要接地区域GND，所以栅极TG、RG、SEL和SF的面积可以增加。例如，传输栅极TG的平面面积可以是单位像素面积的10%或更多。

[0068] 根据发明构思的一些示例实施方式，由于第二隔离图案202和第四隔离图案302在像素组之间彼此接触，所以所接收的光不会移动到其它像素组中（见图6）。因此，可以防止或减少具有颜色彼此不同的滤色器的相邻像素之间的串扰。

[0069] 第一保护层44可以提供在第二表面1b上。在一些示例实施方式中，第二固定电荷层可以设置在第一保护层44和绝缘图案36之间。第二固定电荷层可以包括单层或多层的金属氧化物或金属氟化物。例如，第二固定电荷层可以包括铪氧化物和/或铝氧化物。第二固定电荷层可以增强第一固定电荷层34和/或可以用作粘合层。第一保护层44可以包括PETEOS、SiOC、 $\text{SiO}_2$ 和SiN中的至少一种。第一保护层44可以用作抗反射层和/或平坦化层。

[0070] 光阻挡图案48a和低折射率图案50a可以依次堆叠在第一保护层44上。光阻挡图案48a和低折射率图案50a在平面图中可以具有网格形状，并且可以与深器件隔离部分DTI重叠。光阻挡图案48a可以包括例如钛。低折射率图案50a可以包括有机材料。低折射率图案50a可以具有比滤色器CF1、CF2和CF3的折射率小的折射率。例如，低折射率图案50a可以具有约1.3或更小的折射率。低折射率图案50a的侧表面可以与光阻挡图案48a的侧表面对准。光阻挡图案48a和低折射率图案50a可以防止或减少相邻像素之间的串扰。

[0071] 第二保护层56可以堆叠在第一保护层44上。第二保护层56可以共形地覆盖低折射率图案50a和光阻挡图案48a。滤色器CF1、CF2和CF3可以设置在具有网格形状的低折射率图案50a的开口中。微透镜阵列层ML可以设置在滤色器CF1、CF2和CF3上。微透镜阵列层ML可以

包括分别与单位像素UP重叠的凸透镜部分。

[0072] 图7是根据发明构思的一些示例实施方式的图像传感器的平面图。图8A是根据发明构思的一些示例实施方式的沿着图7的线A-A'截取的截面图。图8B是根据发明构思的一些示例实施方式的沿着图7的线B-B'截取的截面图。在下文,为了说明的容易和方便,将省略对与图4至图6的示例实施方式中相同的特征的描述,并且将主要描述图7至图8B的示例实施方式和图4至图6的示例实施方式之间的差异。

[0073] 参照图7、图8A和图8B,第二隔离图案202在第一方向D1上的宽度202d可以基本等于第一隔离图案201在第一方向D1上的宽度201d。第二隔离图案202从第一表面1a朝向第二表面1b的延伸深度可以基本上等于第一隔离图案201从第一表面1a朝向第二表面1b的延伸深度。换言之,第二隔离图案202的长度可以基本上等于第一隔离图案201的长度。

[0074] 第一隔离图案201和第三隔离图案301可以彼此垂直重叠(或对准),并且可以彼此间隔开。第二隔离图案202和第四隔离图案302可以彼此垂直重叠(或对准),并且可以彼此间隔开。

[0075] 如图8B所示,相邻像素组(例如GRP1和GRP2)之间的四个邻近单位像素UP彼此相邻的位置CN2中的第二表面1b的最低水平可以高于第二隔离图案202的顶表面的水平。因此,第一隔离图案201的高浓度掺杂图案26可以连接到第二隔离图案202的高浓度掺杂图案26。

[0076] 换言之,根据发明构思,第一像素组GRP1中不具有接地区域GND的像素的正电荷可以通过第一隔离图案201的连续高浓度掺杂图案26和第二隔离图案202的连续高浓度掺杂图案26移动到第二像素组GRP2的接地区域GND中。由于共享接地区域GND的像素的数量如上所述地增加,所以共享像素的栅极TG、RG、SEL和SF的面积可以增加。

[0077] 图9是示出根据发明构思的一些示例实施方式的图像传感器的平面图。

[0078] 参照图9,第一至第三像素组GRP1、GRP2和GRP3中的每个可以包括以 $3 \times 3$ 矩阵形式排列的第一至第九像素PX1至PX9,所述 $3 \times 3$ 矩阵形式由沿第二方向D2排列的三行和沿第一方向D1排列的三列构成。

[0079] 根据一些示例实施方式的图像传感器510还可以具有在同一像素组中共享接地区域GND的像素和参照图3至图8描述的深器件隔离部分DTI的结构特征。

[0080] 在一些示例实施方式中,第一至第三像素组GRP1、GRP2和GRP3中的每个可以包括以 $4 \times 4$ 矩阵形式排列的第一至第十六像素,该 $4 \times 4$ 矩阵形式由沿第二方向D2排列的四行和沿第一方向D1排列的四列构成。

[0081] 图10A至图19A是对应于图4的线A-A'的截面图,以示出制造图5A的图像传感器的方法。图10B至图19B是对应于图4的线B-B'的截面图,以示出制造图5B的图像传感器的方法。

[0082] 参照图10A和图10B,可以制备基板1。可以通过使用第一蚀刻掩模图案3对基板1执行蚀刻工艺,从而形成第一沟槽5。

[0083] 参照图11A和图11B,可以形成第一绝缘层8以覆盖基板1的第一表面1a。第一绝缘层8可以填充第一沟槽5。例如,第一绝缘层8可以包括硅氧化物层。接下来,可以形成第一深沟槽9和第二深沟槽10以穿透第一沟槽5。第一深沟槽9和第二深沟槽10的形成可以包括形成第二蚀刻掩模图案的工艺以及通过使用第二蚀刻掩模图案蚀刻第一绝缘层8和基板1的工艺。第一深沟槽9和第二深沟槽10可以形成为具有其中沟槽彼此交叉的网格形状。第一深

沟槽9在第一方向D1上的宽度9D可以小于第二深沟槽10在第一方向D1上的宽度10D。第一深沟槽9的深度9H可以小于第二深沟槽10的深度10H(负载效应)。

[0084] 此时,四个邻近像素UP之间的基板1的蚀刻量可以大于两个邻近像素UP之间的基板1的蚀刻量。换言之,基板1的蚀刻量在其中一对第一深沟槽9彼此交叉的位置9a和其中第二深沟槽10与第一深沟槽9或第二深沟槽10交叉的位置10a中可能更多。其中第二深沟槽10与第一深沟槽9或第二深沟槽10交叉的位置10a中的基板1的蚀刻量H2可以大于其中一对第一深沟槽9彼此交叉的位置9a中的基板1的蚀刻量H1(负载效应)。

[0085] 参照图12A和12B,通过从基板1的第一表面1a向第二表面1b执行的等离子体掺杂(PLAD)工艺P1,可以将具有第一导电类型(例如P型)的掺杂剂注入到基板1的一部分中。例如,具有第一导电类型的掺杂剂可以包括硼。通过等离子体掺杂工艺P1,可以在第一和第二深沟槽9和10的每个的内表面中形成高浓度掺杂图案26。

[0086] 参照图13A和图13B,可以形成衬垫绝缘层25a和导电层24a以填充第一深沟槽9和第二深沟槽10。例如,衬垫绝缘层25a可以包括硅氧化物层,导电层24a可以包括掺有具有第一导电类型(例如P型)的掺杂剂的多晶硅。

[0087] 参照图14A和图14B,可以去除导电层24a的一部分。导电层24a的去除工艺可以包括回蚀工艺。可以通过回蚀工艺形成导电图案24。此后,可以在衬垫绝缘层25a上形成第二绝缘层22a。第二绝缘层22a可以包括硅氧化物层。

[0088] 参照图15A和图15B,可以对基板1的第二表面1b执行平坦化工艺。可以去除第一和第二绝缘层8和22a的部分,以形成浅器件隔离部分STI和填充绝缘图案22。此外,可以去除衬垫绝缘层25a的一部分以形成衬垫绝缘图案25。有源区可以由浅器件隔离部分STI限定。

[0089] 参照图16A和图16B,可以对基板1执行离子注入工艺,以形成光电转换部分PD。因此,单位像素UP可以彼此隔离。此外,可以执行一般工艺以在基板1的第一表面1a上形成栅极绝缘层Gox、传输栅极TG、浮置扩散区FD、接触插塞17、互连线15和层间绝缘层IL。

[0090] 参照图17A和图17B,可以以第二表面1b面朝上的方式翻转基板1。可以执行研磨工艺或化学机械抛光(CMP)工艺以减小基板1的厚度。可以以不暴露高浓度掺杂图案26的方式执行研磨工艺或CMP工艺。在一些示例实施方式中,可以省略该工艺。

[0091] 参照图18A和图18B,可以在基板1的第二表面1b上形成第三蚀刻掩模图案。第三蚀刻掩模图案可以形成为具有与第一隔离图案201和第二隔离图案202重叠的开口。可以使用第三蚀刻掩模图案作为蚀刻掩模来蚀刻基板1,以形成第三沟槽11和第四沟槽12。第三沟槽11可以以第三沟槽11的底表面与第一隔离图案201的最上部间隔开这样的方式形成。第四沟槽12可以以第四沟槽12的底表面暴露第二隔离图案202的最上部分这样的方式形成。第四沟槽12的底表面的水平可以低于第三沟槽11的底表面的水平。在一些示例实施方式中,第四沟槽12的底表面可以不暴露第二隔离图案202的最上部分(见图8A)。

[0092] 此时,四个邻近像素UP之间的基板1的蚀刻量可以大于两个邻近像素UP之间的基板1的蚀刻量。换言之,基板1的蚀刻量在其中一对第三沟槽11彼此交叉的位置和其中第四沟槽12与第三沟槽11或第四沟槽12交叉的位置中可能更多。

[0093] 接下来,可以去除第三蚀刻掩模图案。此后,可以在第二表面1b上共形地形成第一固定电荷层34。第一固定电荷层34可以共形地覆盖第三沟槽11的内侧表面和底表面以及第四沟槽12的内侧表面和底表面。可以在第一固定电荷层34上形成绝缘图案36,以填充第三

沟槽11和第四沟槽12。

[0094] 参照图19A和图19B,可以依次形成第二固定电荷层(未显示)和第一保护层44。可以在第一保护层44上依次形成扩散阻挡层和第一金属层。第一金属层可以被蚀刻以形成低折射率图案50a。扩散阻挡层可以被蚀刻以形成光阻挡图案48a。

[0095] 再次参照图5A和图5B,可以在第一保护层44上共形地形成第二保护层56。可以在第二保护层56上在低折射率图案50a的开口中形成滤色器CF1、CF2和CF3。可以在滤色器CF1、CF2和CF3上形成微透镜阵列层ML。因此,可以制造图5A和图5B的图像传感器500。

[0096] 图20是根据发明构思的一些示例实施方式的图像传感器的平面图,图21是沿图20的线I-I'截取的截面图。

[0097] 参照图20和图21,图像传感器700可以包括包含像素阵列区AR、光学黑区OB和焊盘区PR的基板1,在基板1的第一表面1a上的互连层200,在互连层200上的基底基板400和在基板1的第二表面1b上的光透射层300。互连层200可以设置在基板1的第一表面1a和基底基板400之间。互连层200可以包括与基板1的第一表面1a相邻的上互连层210以及在上互连层210和基底基板400之间的下互连层230。像素阵列区AR可以包括多个像素PX和设置在其间的深器件隔离部分DTI。深器件隔离部分DTI可以与上述图像传感器500或600的深器件隔离部分DTI基本相同。

[0098] 第一连接结构50、第一接触81和体滤色器90可以设置在基板1的光学黑区OB上。第一连接结构50可以包括第一光阻挡图案51、第一低折射率残留层53和第一覆盖图案55。第一光阻挡图案51可以设置在基板1的第二表面1b上。第一光阻挡图案51可以覆盖第一保护层44,并且可以共形地覆盖第一沟槽TRA和第二沟槽TRB中的每个的内表面。第一光阻挡图案51可以穿透基板1和上互连层210。第一光阻挡图案51可以连接到基板1的深器件隔离部分DTI的第一隔离部分20,并且可以连接到上互连层210和下互连层230中的互连线。因此,第一连接结构50可以电连接基板1和互连层200。第一光阻挡图案51可以包括金属材料(例如钨)。第一光阻挡图案51可以阻挡朝向光学黑区OB入射的光。

[0099] 第一接触81可以填充第一沟槽TRA的剩余部分。第一接触81可以包括金属材料(例如铝)。第一接触81可以连接到深器件隔离部分DTI的第一隔离部分20。可以通过第一接触81向第一隔离部分20施加偏压。第一低折射率残留层53可以填充第二沟槽TRB的剩余部分。第一低折射率残留层53可以穿透基板1,并且可以穿透互连层200的一部分。第一低折射率残留层53可以包括绝缘材料。第一覆盖图案55可以设置在第一低折射率残留层53上。第一覆盖图案55可以包括与深器件隔离部分DTI的填充绝缘图案22相同的材料。

[0100] 体滤色器90可以设置在第一连接结构50和第一接触81上。体滤色器90可以覆盖第一连接结构50和第一接触81。第三保护层71可以设置在体滤色器90上,以密封或封装体滤色器90。

[0101] 附加光电转换部分PD'和虚设区111可以提供在光学黑区OB的相应像素PX中。附加光电转换部分PD'可以是掺有具有不同于基板1的第一导电类型的第二导电类型(例如N型)的掺杂剂的区域。附加光电转换部分PD'可以具有与像素阵列区AR的多个像素PX中的光电转换部分PD的结构类似的结构,但是可以不执行与光电转换部分PD相同的操作(例如,将所接收的光转换成电信号的操作)。虚设区111可以不掺有掺杂剂。

[0102] 第二连接结构60、第二接触83和第四保护层73可以设置在基板1的焊盘区PR上。第

二连接结构60可以包括第二光阻挡图案61、第二低折射率残留层63和第二覆盖图案65。

[0103] 第二光阻挡图案61可以设置在基板1的第二表面1b上。第二光阻挡图案61可以覆盖第一保护层44，并且可以共形地覆盖第三沟槽TRC和第四沟槽TRD中的每个的内表面。第二光阻挡图案61可以穿透基板1和上互连层210。第二光阻挡图案61可以连接到下互连层230中的互连线。因此，第二连接结构60可以电连接基板1和互连层200。第二光阻挡图案61可以包括金属材料(例如钨)。第二光阻挡图案61可以阻挡朝向焊盘区PR入射的光。

[0104] 第二接触83可以填充第三沟槽TRC的剩余部分。第二接触83可以包括金属材料(例如铝)。第二接触83可以用作图像传感器700和外部器件之间的电连接路径。第二低折射率残留层63可以填充第四沟槽TRD的剩余部分。第二低折射率残留层63可以穿透基板1，并且可以穿透互连层200的一部分。第二低折射率残留层63可以包括绝缘材料。第二覆盖图案65可以设置在第二低折射率残留层63上。第二覆盖图案65可以包括与深器件隔离部分DTI的填充绝缘图案22相同的材料。第四保护层73可以覆盖第二连接结构60。

[0105] 通过第二接触83施加的电流可以通过第二光阻挡图案61、在互连层200中的互连线、和第一光阻挡图案51流入深器件隔离部分DTI的第一隔离部分20。从像素阵列区AR的多个像素PX中的光电转换部分PD产生的电信号可以通过互连层200中的互连线、第二光阻挡图案61和第二接触83传输到外部。

[0106] 根据发明构思的一些示例实施方式，每个像素组中包括的像素可以共享接地区域。当四个像素构成单个像素组时，接地区域可以选择性地提供在所述四个像素之一中。隔离像素的深器件隔离部分可以包括彼此垂直重叠并且彼此间隔开的第一和第二隔离图案。不具有接地区域的像素的正电荷可以通过第一隔离图案的高浓度掺杂图案移动到接地区域。结果，不具有接地区域的三个像素的正电荷可以通过第一隔离图案释放到接地区域。此外，由于所述三个像素不需要接地区域，所以可以增加图像传感器的栅电极的面积。

[0107] 当术语“约”或“基本上”在本说明书中与数值结合使用时，其意图是相关联数值包括以所述及的数值为中心的制造或操作公差(例如 $\pm 10\%$ )。此外，当词语“通常”和“基本上”与几何形状结合使用时，其意图是不需要几何形状的精度，但是该形状的范围在本公开的范围内。此外，不管数值或形状是否被修饰为“约”或“基本上”，但是将理解的是，这些数值和形状应被解释为包括以所述及数值或形状为中心的制造或操作公差(例如 $\pm 10\%$ )。

[0108] 虽然已经对发明构思的示例实施方式进行了具体显示和描述，但本领域普通技术人员将理解，在不脱离所附权利要求的精神和范围的情况下，可以在其中进行形式和细节上的变更。

[0109] 该专利申请要求于2021年9月17日在韩国知识产权局提交的第10-2021-0125031号韩国专利申请的优先权，其全部内容通过引用合并于此。

图1

1001

图2

500

图3

500

图4

图5A

图5B

图5C

图6

图7

图8A

图8B

510

图9

图10A

图10B

图11A

图11B

图12A

图12B

图13A

图13B

图14A

图14B

图15A

图15B

图16A

图16B

图17A

图17B

图18A

图18B

图19A

图19B

图20

图21