(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7513385号**

**(P7513385)**

(45)発行日 令和6年7月9日(2024.7.9)

(24)登録日 令和6年7月1日(2024.7.1)

(51)国際特許分類

|         |                  |     |         |             |

|---------|------------------|-----|---------|-------------|

| H 1 0 B | 43/27 (2023.01)  | F I | H 1 0 B | 43/27       |

| H 1 0 B | 41/27 (2023.01)  |     | H 1 0 B | 41/27       |

| H 0 1 L | 21/336 (2006.01) |     | H 0 1 L | 29/78 3 7 1 |

| H 0 1 L | 29/788 (2006.01) |     | H 1 0 B | 41/40       |

| H 0 1 L | 29/792 (2006.01) |     | H 1 0 B | 43/40       |

請求項の数 19 (全35頁) 最終頁に続く

(21)出願番号 特願2019-218961(P2019-218961)

(22)出願日 令和1年12月3日(2019.12.3)

(65)公開番号 特開2020-102613(P2020-102613

A)

(43)公開日 令和2年7月2日(2020.7.2)

審査請求日 令和4年11月29日(2022.11.29)

(31)優先権主張番号 10-2018-0167170

(32)優先日 平成30年12月21日(2018.12.21)

(33)優先権主張国・地域又は機関

韓国(KR)

(73)特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 1 2

9

1 2 9 , Samsung - ro , Yeo

n g t o n g - g u , Suw o n - s i

, Gyeonggi - do , Repub

lic of Korea

(74)代理人 110000051

弁理士法人共生国際特許事務所

金森 宏治

大韓民国 京畿道 水原市 灵通区 三星路

1 2 9

最終頁に続く

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項 1】**

基板と、前記基板上に配置される複数の回路素子と、前記回路素子上に各々配置される複数の第1接合パッドと、を含む第1半導体構造物と、

前記第1半導体構造物上で前記第1半導体構造物と接続される第2半導体構造物と、を有し、

前記第2半導体構造物は、

前記第1半導体構造物に向かう第1面と前記第1面と対向する第2面とを有するベース層と、

前記ベース層の第1面上で前記第1面に垂直な方向に沿って互いに離隔して積層される第1ゲート電極と、前記第1ゲート電極の少なくとも一部を貫通して延長される第1チャネルと、を含む第1メモリセル構造物と、

前記第1ゲート電極の下部で前記第1面に垂直な方向に沿って互いに離隔して積層される第2ゲート電極と、前記第2ゲート電極の少なくとも一部を貫通して延長される第2チャネルと、を含む第2メモリセル構造物と、

前記第1メモリセル構造物と前記第2メモリセル構造物との間に配置され、前記第1及び第2チャネルに共通に電気的に接続されるピットラインと、

前記ベース層の第2面上で互いに離隔して配置される第1及び第2導電層と、

前記第1及び第2導電層上に配置され、前記第2導電層の一部を露出させる開口部を有するパッド絶縁層と、

10

20

前記第2導電層の下で前記第1面に垂直な方向に沿って延長され、前記第2導電層と電気的に接続される第1コンタクトプラグと、

前記第2メモリセル構造物の下部で前記第1接合パッドと対応するように配置される複数の第2接合パッドと、を含み、

前記第1半導体構造物に含まれる前記複数の回路素子は、周辺回路領域の入出力回路を含み、

前記第2導電層は、前記周辺回路領域の入出力回路と電気的に接続され、

前記第2半導体構造物は、前記ビットラインと並行して配置され、前記第2導電層と電気的に接続される接続パッドをさらに含むことを特徴とする半導体装置。

#### 【請求項2】

10

前記第1コンタクトプラグは、前記第2導電層と前記接続パッドとの間に配置され、前記第2導電層及び前記接続パッドを電気的に接続することを特徴とする請求項1に記載の半導体装置。

#### 【請求項3】

前記第1コンタクトプラグは、複数個からなり、1つの前記第2導電層に前記第1コンタクトプラグの複数個が接続されることを特徴とする請求項2に記載の半導体装置。

#### 【請求項4】

前記第1コンタクトプラグは、前記ベース層を貫通して前記第2導電層と直接接続されることを特徴とする請求項2に記載の半導体装置。

#### 【請求項5】

20

前記接続パッドと前記第2接合パッドとの間に配置され、前記第2接合パッドの少なくとも1つと前記接続パッドとを電気的に接続する第2コンタクトプラグをさらに有することを特徴とする請求項1に記載の半導体装置。

#### 【請求項6】

前記接続パッドは、前記ビットラインと実質的に同一の厚さを有することを特徴とする請求項1に記載の半導体装置。

#### 【請求項7】

前記第1導電層は、前記第1及び第2ゲート電極と重畳するよう配置され、前記第2導電層は、前記第1及び第2ゲート電極と重畳しないように前記第1及び第2ゲート電極から水平方向に離隔して配置されることを特徴とする請求項1に記載の半導体装置。

30

#### 【請求項8】

前記第1導電層は、前記第1チャネルに電気的信号を印加するソースラインを構成し、前記第2導電層は、前記第1導電層と電気的に分離されることを特徴とする請求項1に記載の半導体装置。

#### 【請求項9】

前記第1及び第2導電層は、実質的に同一の高さレベルに位置し、実質的に同一の厚さを有することを特徴とする請求項1に記載の半導体装置。

#### 【請求項10】

前記開口部を定義する前記パッド絶縁層の側面及び前記開口部によって露出した前記第2導電層の上面は、前記半導体装置の外側に露出することを特徴とする請求項1に記載の半導体装置。

40

#### 【請求項11】

前記第1及び第2チャネルは、前記ベース層に向かって幅が狭くなるように傾斜した側面を有することを特徴とする請求項1に記載の半導体装置。

#### 【請求項12】

前記第2メモリセル構造物の下部に配置され、前記第2チャネルに電気的信号を印加するソースラインを構成する第3導電層をさらに有することを特徴とする請求項1に記載の半導体装置。

#### 【請求項13】

基板と、前記基板上に配置される複数の回路素子と、前記回路素子上に各々配置される

50

複数の第1接合パッドとを含む第1半導体構造物と、

前記第1半導体構造物上で前記第1半導体構造物と接続され、ベース層と、前記ベース層の下面上で、前記下面に垂直な方向に沿って積層される複数のメモリセル構造物と、前記メモリセル構造物の間に配置され、上下の前記メモリセル構造物の間で共有される少なくとも1つの配線ラインと、前記ベース層の上面上で互いに離隔して配置される第1及び第2導電層と、前記第1及び第2導電層上に配置され、前記第2導電層の一部を露出させる開口部を有するパッド絶縁層と、前記第2導電層の下部で前記配線ラインと並行して配置され、前記第2導電層と電気的に接続される接続パッドと、前記メモリセル構造物の下部で前記第1接合パッドと対応するように配置される複数の第2接合パッドと、を含む第2半導体構造物と、を有し、

前記第1半導体構造物に含まれる前記複数の回路素子は、周辺回路領域の入出力回路を含み、

前記第2導電層は、前記周辺回路領域の入出力回路と電気的に接続されることを特徴とする半導体装置。

**【請求項14】**

前記接続パッドの上面及び下面にそれぞれ配置される複数のコンタクトプラグをさらに有することを特徴とする請求項13に記載の半導体装置。

**【請求項15】**

前記第2導電層は、前記接続パッド及び前記コンタクトプラグを介して前記第2接合パッドの少なくとも1つと電気的に接続されることを特徴とする請求項14に記載の半導体装置。

**【請求項16】**

それぞれの前記メモリセル構造物は、前記ベース層の下面に垂直な方向に沿って互いに離隔して積層されるゲート電極及び前記ゲート電極を貫通して延長されるチャネルを含み、

前記少なくとも1つの配線ラインは、隣接する前記メモリセル構造物の前記チャネルに共通に電気的に接続されるビットラインを含むことを特徴とする請求項13に記載の半導体装置。

**【請求項17】**

前記少なくとも1つの配線ラインは、隣接する前記メモリセル構造物の前記チャネルに共通に電気的に接続されるソースラインをさらに含むことを特徴とする請求項16に記載の半導体装置。

**【請求項18】**

基板と、前記基板上に配置される複数の回路素子と、及び前記回路素子上に各々配置される複数の第1接合パッドと、を含む第1半導体構造物と、

前記第1半導体構造物上で前記第1半導体構造物と接続され、ベース層と、前記ベース層の下面上で、前記下面に垂直な方向に沿って積層され、垂直に積層されたゲート電極を含む複数のメモリセル構造物と、前記メモリセル構造物の間に配置され、上下の前記メモリセル構造物の間で共有される少なくとも1つの配線ラインと、前記ゲート電極の上部で前記ベース層上に配置される第1導電層と、前記第1導電層と水平方向に離隔して配置され、外部装置との電気的接続のために提供される第2導電層と、前記第1及び第2導電層上に配置され、前記第2導電層の一部を露出させる開口部を有するパッド絶縁層と、前記第2導電層の下部で前記配線ラインと並行して配置され、前記第2導電層と電気的に接続される接続パッドと、前記メモリセル構造物の下部で前記第1接合パッドと対応するように配置される複数の第2接合パッドと、を含む第2半導体構造物と、を有し、

前記第1半導体構造物に含まれる前記複数の回路素子は、周辺回路領域の入出力回路を含み、

前記第2導電層は、前記周辺回路領域の入出力回路と電気的に接続されることを特徴とする半導体装置。

**【請求項19】**

10

20

30

40

50

前記第1導電層は、下部の前記メモリセル構造物に電気信号を印加するソースラインであることを特徴とする請求項1\_8に記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、集積度及び信頼性が向上した半導体装置に関する。

【背景技術】

【0002】

半導体装置は、その体積が次第に小さくなりながらも高容量のデータ処理を要することが求められている。

そのため、このような半導体装置を構成する半導体素子の集積度を高める必要がある。

【0003】

上記に対し、半導体装置の集積度を向上させるための方法の1つとして、既存の平面トランジスタ構造の代わりに垂直トランジスタ構造を有する半導体装置が提案されている。

そして、垂直トランジスタ構造の集積度及び信頼性を向上させることが課題となっている。

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明は上記従来の垂直トランジスタ構造を有する半導体装置における課題に鑑みてなされたものであって、本発明の目的は、集積度及び信頼性が向上した半導体装置を提供することにある。

【課題を解決するための手段】

【0005】

上記目的を達成するためになされた本発明による半導体装置は、基板と、前記基板上に配置される複数の回路素子と、前記回路素子上に各々配置される複数の第1接合パッドと、を含む第1半導体構造物と、前記第1半導体構造物上で前記第1半導体構造物と接続される第2半導体構造物と、を有し、前記第2半導体構造物は、前記第1半導体構造物に向かう第1面と前記第1面と対向する第2面とを有するベース層と、前記ベース層の第1面上で前記第1面に垂直な方向に沿って互いに離隔して積層される第1ゲート電極と、前記第1ゲート電極の少なくとも一部を貫通して延長される第1チャネルと、を含む第1メモリセル構造物と、前記第1ゲート電極の下部で前記第1面に垂直な方向に沿って互いに離隔して積層される第2ゲート電極と、前記第2ゲート電極の少なくとも一部を貫通して延長される第2チャネルと、を含む第2メモリセル構造物と、前記第1メモリセル構造物と前記第2メモリセル構造物との間に配置され、前記第1及び第2チャネルに共通に電気的に接続されるビットラインと、前記ベース層の第2面上で互いに離隔して配置される第1及び第2導電層と、前記第1及び第2導電層上に配置され、前記第2導電層の一部を露出させる開口部を有するパッド絶縁層と、前記第2導電層の下で前記第1面に垂直な方向に沿って延長され、前記第2導電層と電気的に接続される第1コントクトプラグと、前記第2メモリセル構造物の下部で前記第1接合パッドと対応するように配置される複数の第2接合パッドと、を含み、前記第1半導体構造物に含まれる前記複数の回路素子は、周辺回路領域の入出力回路を含み、前記第2導電層は、前記周辺回路領域の入出力回路と電気的に接続され、前記第2半導体構造物は、前記ビットラインと並行して配置され、前記第2導電層と電気的に接続される接続パッドをさらに含むことを特徴とする。

【0006】

また、上記目的を達成するためになされた本発明による半導体装置は、基板と、前記基板上に配置される複数の回路素子と、前記回路素子上に各々配置される複数の第1接合パッドとを含む第1半導体構造物と、前記第1半導体構造物上で前記第1半導体構造物と接続され、ベース層と、前記ベース層の下面上で、前記下面に垂直な方向に沿って積層される複数のメモリセル構造物と、前記メモリセル構造物の間に配置され、上下の前記メモリ

10

20

30

40

50

セル構造物の間で共有される少なくとも1つの配線ラインと、前記ベース層の上面上で互いに離隔して配置される第1及び第2導電層と、前記第1及び第2導電層上に配置され、前記第2導電層の一部を露出させる開口部を有するパッド絶縁層と、前記第2導電層の下部で前記配線ラインと並行して配置され、前記第2導電層と電気的に接続される接続パッドと、前記メモリセル構造物の下部で前記第1接合パッドと対応するように配置される複数の第2接合パッドと、を含む第2半導体構造物と、を有し、前記第1半導体構造物に含まれる前記複数の回路素子は、周辺回路領域の入出力回路を含み、前記第2導電層は、前記周辺回路領域の入出力回路と電気的に接続されることを特徴とする。

#### 【0007】

また、上記目的を達成するためになされた本発明による半導体装置は、基板と、前記基板上に配置される複数の回路素子と、及び前記回路素子上に各々配置される複数の第1接合パッドと、を含む第1半導体構造物と、前記第1半導体構造物上で前記第1半導体構造物と接続され、ベース層と、前記ベース層の下面上で、前記下面に垂直な方向に沿って積層され、垂直に積層されたゲート電極を含む複数のメモリセル構造物と、前記メモリセル構造物の間に配置され、上下の前記メモリセル構造物の間で共有される少なくとも1つの配線ラインと、前記ゲート電極の上部で前記ベース層上に配置される第1導電層と、前記第1導電層と水平方向に離隔して配置され、外部装置との電気的接続のために提供される第2導電層と、前記第1及び第2導電層上に配置され、前記第2導電層の一部を露出させる開口部を有するパッド絶縁層と、前記第2導電層の下部で前記配線ラインと並行して配置され、前記第2導電層と電気的に接続される接続パッドと、前記メモリセル構造物の下部で前記第1接合パッドと対応するように配置される複数の第2接合パッドと、を含む第2半導体構造物と、を有し、前記第1半導体構造物に含まれる前記複数の回路素子は、周辺回路領域の入出力回路を含み、前記第2導電層は、前記周辺回路領域の入出力回路と電気的に接続されることを特徴とする。

10

#### 【発明の効果】

#### 【0008】

本発明に係る半導体装置によれば、2つ以上の半導体構造物が接合された構造において、ソース導電層を用いて入出力パッドを配置することにより、集積度及び信頼性が向上した半導体装置を提供することができる。

#### 【図面の簡単な説明】

30

#### 【0009】

【図1】本発明の一実施形態による半導体装置の概略的な構成を示すブロック図である。

【図2】本発明の一実施形態による半導体装置のセルアレイの等価回路図である。

【図3】本発明の一実施形態による半導体装置の配置を説明するための概略的な斜視図である。

【図4】本発明の一実施形態による半導体装置の概略的な構成を示す断面図である。

【図5a】本発明の一実施形態による半導体装置の一部構成を示す概略的な断面図である。

【図5b】本発明の一実施形態による半導体装置の一部構成を示す概略的な断面図である。

【図6a】本発明の一実施形態による半導体装置の一部構成を示す概略的な断面図である。

【図6b】本発明の一実施形態による半導体装置の一部構成を示す概略的な断面図である。

【図7a】本発明の一実施形態による半導体装置の一部構成を示す概略的な平面図である。

【図7b】本発明の一実施形態による半導体装置の一部構成を示す概略的な平面図である。

40

【図8a】本発明の一実施形態による半導体装置の概略的な構成を示す断面図である。

【図8b】本発明の一実施形態による半導体装置の概略的な構成を示す断面図である。

【図8c】本発明の一実施形態による半導体装置の概略的な構成を示す断面図である。

【図9】本発明の一実施形態による半導体装置の概略的な構成を示す断面図である。

【図10a】本発明の一実施形態による半導体装置の製造方法を説明するための概略的な断面図である。

【図10b】本発明の一実施形態による半導体装置の製造方法を説明するための概略的な断面図である。

50

【図10c】本発明の一実施形態による半導体装置の製造方法を説明するための概略的な断面図である。

【図10d】本発明の一実施形態による半導体装置の製造方法を説明するための概略的な断面図である。

【図10e】本発明の一実施形態による半導体装置の製造方法を説明するための概略的な断面図である。

【図10f】本発明の一実施形態による半導体装置の製造方法を説明するための概略的な断面図である。

【図10g】本発明の例示的な実施形態による半導体装置の製造方法を説明するための概略的な断面図である。

【図10h】本発明の一実施形態による半導体装置の製造方法を説明するための概略的な断面図である。

【図10i】本発明の一実施形態による半導体装置の製造方法を説明するための概略的な断面図である。

【図10j】本発明の一実施形態による半導体装置の製造方法を説明するための概略的な断面図である。

【図11】本発明の一実施形態による半導体パッケージの概略的な構成を示す断面図である。

【図12】本発明の一実施形態による半導体装置を含む電子機器の概略構成を示すプロック図である。

#### 【発明を実施するための形態】

##### 【0010】

次に、本発明に係る半導体装置を実施するための形態の具体例を図面を参照しながら説明する。

##### 【0011】

以下、添付された図面を参照して、本発明の好ましい実施形態を以下のように説明する。

以下では、「上」、「上部」、「上面」、「下」、「下部」、「下面」、「側面」などの用語は、図面符号で表記されて別に称される場合を除き、図面を基準に称するものと理解するものとする。

##### 【0012】

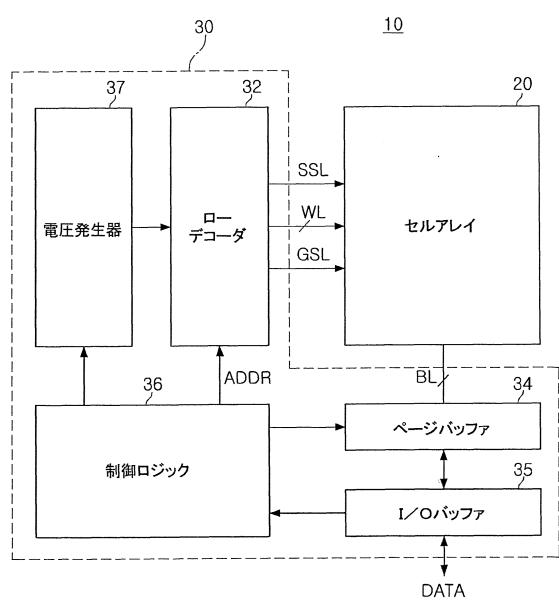

図1は、本発明の一実施形態による半導体装置の概略的な構成を示すプロック図である。

図1を参照すると、半導体装置10は、メモリセルアレイ20、及び周辺回路30を含む。

周辺回路30は、ローデコーダ32、ページバッファ34、入出力(I/O)バッファ35、制御ロジック36、及び電圧発生器37を含む。

##### 【0013】

メモリセルアレイ20は、複数のメモリブロックを含み、それぞれのメモリブロックは、複数のメモリセルを含む。

複数のメモリセルは、ストリング選択ラインSSL、ワードラインWL、及び接地選択ラインGSLを介してローデコーダ32と接続され、ビットラインBLを介してページバッファ34と接続される。

本発明の一実施形態において、同一の行に沿って配列される複数のメモリセルは、同一のワードラインWLに接続され、同一の列に沿って配列される複数のメモリセルは、同一のビットラインBLに接続される。

##### 【0014】

ローデコーダ32は、入力されたアドレスADDRをデコードし、ワードラインWLの駆動信号を発生させて伝達する。

ローデコーダ32は、制御ロジック36の制御に応答し、電圧発生器37から発生したワードライン電圧を選択されたワードラインWL及び非選択されたワードラインWLにそれぞれ提供する。

**【0015】**

ページバッファ34は、ビットラインBLを介してメモリセルアレイ20と接続され、メモリセルに記憶された情報を読み取る。

ページバッファ34は、動作モードに応じて、メモリセルに記憶されるデータを一時的に記憶したり、メモリセルに記憶されたデータを感知したりする。

ページバッファ34は、カラムデコーダ及び感知増幅器を含み得る。

カラムデコーダは、メモリセルアレイ20のビットラインBLを選択的に活性化することができ、感知増幅器は、読み出し動作時にカラムデコーダによって選択されたビットラインBLの電圧を感知し、選択されたメモリセルに記憶されたデータを読み出す。

**【0016】**

入出力(I/O)バッファ35は、プログラム動作時にデータDATAの入力を受けてページバッファ34に伝達し、読み出し動作時にページバッファ34から伝達されたデータDATAを外部に出力する。

入出力バッファ35は、入力されるアドレスまたはコマンドを制御ロジック36に伝達する。

**【0017】**

制御ロジック36は、ローデコーダ32及びページバッファ34の動作を制御する。

制御ロジック36は、外部から伝達される制御信号及び外部電圧を受信し、受信した制御信号に従って動作する。

制御ロジック36は制御信号に応答して、読み出し、書き込み、及び／または消去動作を制御する。

**【0018】**

電圧発生器37は、外部電圧を用いて内部動作に必要な電圧、例えば、プログラム電圧、読み出し電圧、消去電圧などを生成する。

電圧発生器37によって生成される電圧は、ローデコーダ32を介してメモリセルアレイ20に伝達される。

**【0019】**

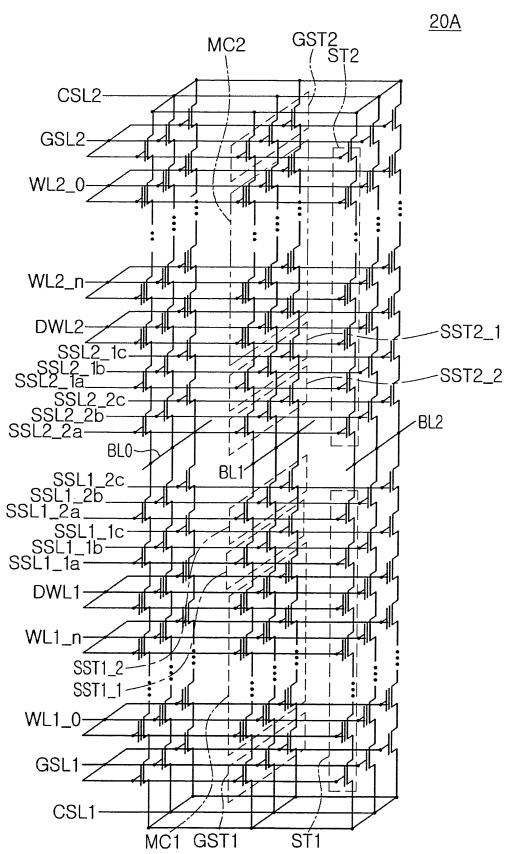

図2は、本発明の一実施形態による半導体装置のセルアレイの等価回路図である。

図2を参照すると、メモリセルアレイ20Aは、互いに直列に接続される第1メモリセルMC1、第1メモリセルMC1の両端に直列に接続される第1接地選択トランジスタGST1及び第1ストリング選択トランジスタ(SST1\_1、SST1\_2)を含む複数の第1メモリセルストリングST1を含む。

**【0020】**

複数の第1メモリセルストリングST1は、それぞれの共通ビットライン(BL0～BL2)に並列に接続される。

複数の第1メモリセルストリングST1は、第1共通ソースラインCSL1に共通に接続される。

即ち、複数の共通ビットライン(BL0～BL2)と1つの第1共通ソースラインCSL1との間に複数の第1メモリセルストリングST1が配置される。

本発明の一実施形態において、第1共通ソースラインCSL1は、複数個が2次元的に配列、配置させることもできる。

**【0021】**

また、メモリセルアレイ20Aは、共通ビットライン(BL0～BL2)の上部に配置され、互いに直列に接続される第2メモリセルMC2、第2メモリセルMC2の両端に直列に接続される第2接地選択トランジスタGST2、及び第2ストリング選択トランジスタ(SST2\_1、SST2\_2)を含む複数の第2メモリセルストリングST2を含む。

複数の第2メモリセルストリングST2は、それぞれの共通ビットライン(BL0～BL2)に並列に接続される。

複数の第2メモリセルストリングST2は、第2共通ソースラインCSL2に共通に接続される。

10

20

30

40

50

即ち、複数の共通ビットライン（B L 0 ~ B L 2）と1つの第2共通ソースラインC S L 2との間に複数の第2メモリセルストリングS T 2を配置させることもできる。

#### 【0022】

メモリセルアレイ20Aにおいて中央に配置される共通ビットライン（B L 0 ~ B L 2）は、上下の第1及び第2メモリセルストリング（S T 1、S T 2）に共通に電気的に接続される。

共通ビットライン（B L 0 ~ B L 2）を中心に、第1及び第2メモリセルストリング（S T 1、S T 2）は実質的に同一の回路構造を有する。

以下では、第1及び第2メモリセルストリング（S T 1、S T 2）の共通している説明について、第1及び第2メモリセルストリング（S T 1、S T 2）を区分せずに説明する。 10

#### 【0023】

互いに直列に接続されるメモリセル（M C 1、M C 2）は、メモリセル（M C 1、M C 2）を選択するためのワードライン（W L 1\_0 ~ W L 1\_n、W L 2\_0 ~ W L 2\_n）によって制御される。

それぞれのメモリセル（M C 1、M C 2）は、データの記憶要素を含む。

共通ソースライン（C S L 1、C S L 2）から実質的に同一の距離に配置されるメモリセル（M C 1、M C 2）のゲート電極は、ワードラインに（W L 1\_0 ~ W L 1\_n、W L 2\_0 ~ W L 2\_n）の内の1つに共通に接続されて等電位状態にある。

または、メモリセル（M C 1、M C 2）のゲート電極が共通ソースライン（C S L 1、C S L 2）から実質的に同一の距離に配置されても、互いに異なる行または列に配置されるゲート電極が独立に制御される。 20

#### 【0024】

接地選択トランジスタ（G S T 1、G S T 2）は、接地選択ライン（G S L 1、G S L 2）によって制御され、共通ソースライン（C S L 1、C S L 2）に接続される。

ストリング選択トランジスタ（S S T 1\_1、S S T 1\_2、S S T 2\_1、S S T 2\_2）は、ストリング選択ライン（S S L\_1a、S S L\_1b、S S L\_1c、S S L\_1\_2a、S S L\_1\_2b、S S L\_1\_2c、S S L\_2\_1a、S S L\_2\_1b、S S L\_2\_1c、S S L\_2\_2a、S S L\_2\_2b、S S L\_2\_2c）によって制御され、共通ビットライン（B L 0 ~ B L 2）に接続される。

図2では、互いに直列に接続される複数個のメモリセル（M C 1、M C 1）にそれぞれ1つの接地選択トランジスタ（G S T 1、G S T 2）と2つのストリング選択トランジスタ（S S T 1\_1、S S T 1\_2、S S T 2\_1、S S T 2\_2）が接続される構造を示したが、それぞれ1つのストリング選択トランジスタが接続されるか、または複数の接地選択トランジスタが接続されることもできる。 30

#### 【0025】

ワードライン（W L 1\_0 ~ W L 1\_n、W L 2\_0 ~ W L 2\_n）のうち最上位のワードライン（W L 1\_n、W L 2\_n）とストリング選択ライン（S S L\_1a、S S L\_1b、S S L\_1c、S S L\_1\_2a、S S L\_1\_2b、S S L\_1\_2c、S S L\_2\_1a、S S L\_2\_1b、S S L\_2\_1c、S S L\_2\_2a、S S L\_2\_2b、S S L\_2\_2c）との間に1つ以上のダミーライン（D W L 1、D W L 2）またはバッファラインがさらに配置され得る。 40

本発明の一実施形態において、最下位のワードライン（W L 1\_0、W L 2\_0）と接地選択ライン（G S L 1、G S L 2）との間にも1つ以上のダミーラインを配置することができる。

本明細書において「ダミー（d u m m y）」という用語は、他の構成要素と同一または類似の構造及び形状を有するが、装置内で実質的に機能しない構成を称するのに用いる。

#### 【0026】

ストリング選択トランジスタ（S S T 1\_1、S S T 1\_2、S S T 2\_1、S S T 2\_2）にストリング選択ライン（S S L\_1a、S S L\_1b、S S L\_1c、S S L\_1\_2a、S S L\_1\_2b、S S L\_1\_2c、S S L\_2\_1a、S S L\_2\_1b、S S L\_2\_1c、S S L\_2\_2a、S S L\_2\_2b、S S L\_2\_2c）によって制御され、ワードライン（W L 1\_0 ~ W L 1\_n、W L 2\_0 ~ W L 2\_n）に接続される。 50

—1c、SSL2\_2a、SSL2\_2b、SSL2\_2c)を介して信号が印加されると、共通ビットライン(BL0～BL2)を介して印加される信号が、互いに直列に接続されたメモリセル(MC1、MC2)に伝達されることにより、データの読み出し及び書き込み動作が行われる。

また、基板を介して所定の消去電圧を印加することにより、メモリセル(MC1、MC2)に記録されたデータを消去する消去動作も行われ得る。

本発明の一実施形態において、メモリセルアレイ20Aは、共通ビットライン(BL0～BL2)と電気的に分離される少なくとも1つのダミーメモリセルストリングを含み得る。

#### 【0027】

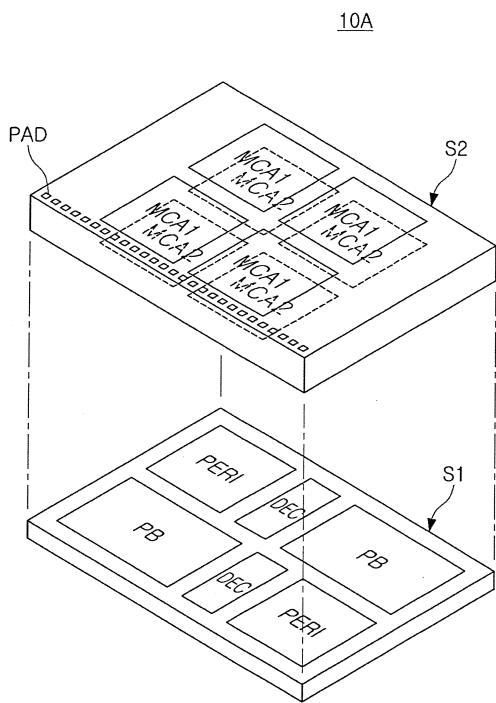

図3は、本発明の一実施形態による半導体装置の配置を説明するための概略的な斜視図である。

図3を参照すると、半導体装置10Aは、垂直方向に積層された第1及び第2半導体構造物(S1、S2)を含む。

第1半導体構造物S1は、図1の周辺回路30を構成し、第2半導体構造物S2は、図1のメモリセルアレイ20を構成する。

#### 【0028】

第1半導体構造物S1は、ローデコーダDEC、ページバッファPB、及びその他の周辺回路PERIを含む。

ローデコーダDECは、図1を参照して上述したローデコーダ32に該当し、ページバッファPBは、ページバッファ34に該当する領域である。

また、その他の周辺回路PERIは、図1の制御ロジック36及び電圧発生器37を含む領域であり得、例えば、ラッチ回路(latch circuit)、キャッシュ回路(cache circuit)、または感知増幅器(sense amplifier)を含み得る。

その他にも、その他の周辺回路PERIは、図1の入出力バッファ35を含むことができ、ESD(Electrostatic discharge)素子、又はデータ入出力回路を含み得る。

本発明の一実施形態において、入出力バッファ35は、その他の周辺回路PERIの周囲で別途の領域をなすように配置することもできる。

#### 【0029】

第1半導体構造物S1においてこのような様々な回路領域(DEC、PB、PERI)の少なくとも一部は、第2半導体構造物S2のメモリセルアレイ(MCA1、MCA2)の下部に配置される。

例えば、ページバッファPB及びその他の周辺回路PERIがメモリセルアレイ(MCA1、MCA2)の下部でメモリセルアレイ(MCA1、MCA2)と重なるように配置され得る。

但し、実施形態において、第1半導体構造物S1に含まれる回路及び配置形態は多様に変更することができ、これにより、メモリセルアレイ(MCA1、MCA2)と重なって配置される回路も多様に変更され得る。

また、実施形態において、回路領域(DEC、PB、PERI)は、メモリセルアレイ(MCA1、MCA2)の個数及び大きさに応じて、図3に示した配置形態が連続的に繰り返して配置される形態を有することもできる。

#### 【0030】

第2半導体構造物S2は、メモリセルアレイ(MCA1、MCA2)及びパッド領域PADを含む。

メモリセルアレイ(MCA1、MCA2)は、垂直に積層された第1及び第2メモリセルアレイ(MCA1、MCA2)を含み、第1及び第2メモリセルアレイ(MCA1、MCA2)はそれぞれ、同一平面上で互いに離隔して並行して配置される。

但し、実施形態において、第2半導体構造物S2に配置されるメモリセルアレイ(MC

10

20

30

40

50

A 1、M C A 2 ) の個数、層数及び配置形態は多様に変更することができる。

パッド領域 P A D は、メモリセルアレイ ( M C A 1、M C A 2 ) の少なくとも一側に配置され得、例えば、第 2 半導体構造物 S 2 の少なくとも一端に沿って列をなして配置され得る。

または、第 1 及び第 2 メモリセルアレイ ( M C A 1、M C A 2 ) のそれぞれの間の領域に列をなして配置することもできる。

パッド領域 P A D は、外部装置などと電気的信号を送受信するように構成される。

半導体装置 1 0 A の内部では、パッド領域 P A D は、第 1 半導体構造物 S 1 のその他の周辺回路 P E R I 内の回路の内の、例えば図 1 の入出力バッファ 3 5 に該当する入出力回路と電気的に接続される領域であり得る。

10

#### 【 0 0 3 1 】

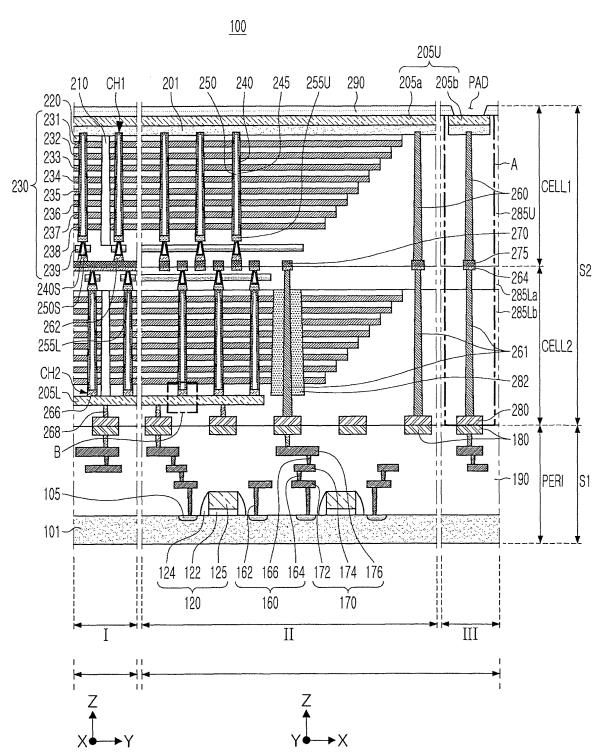

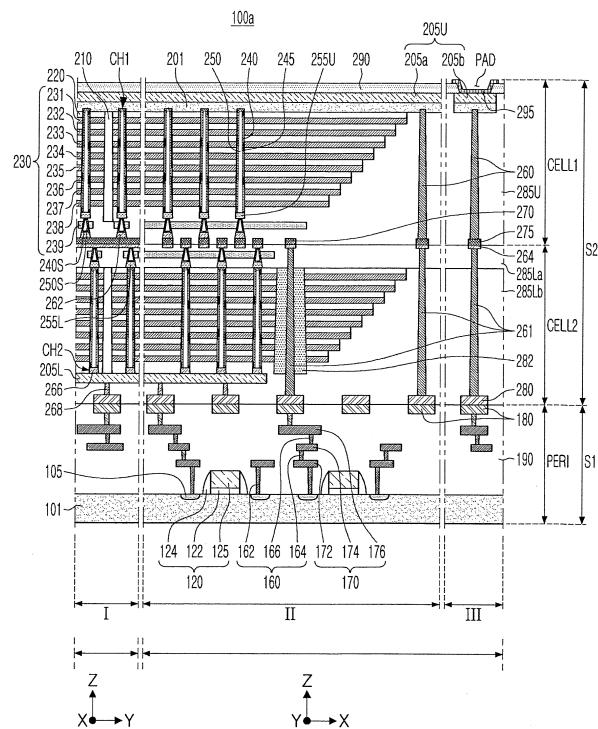

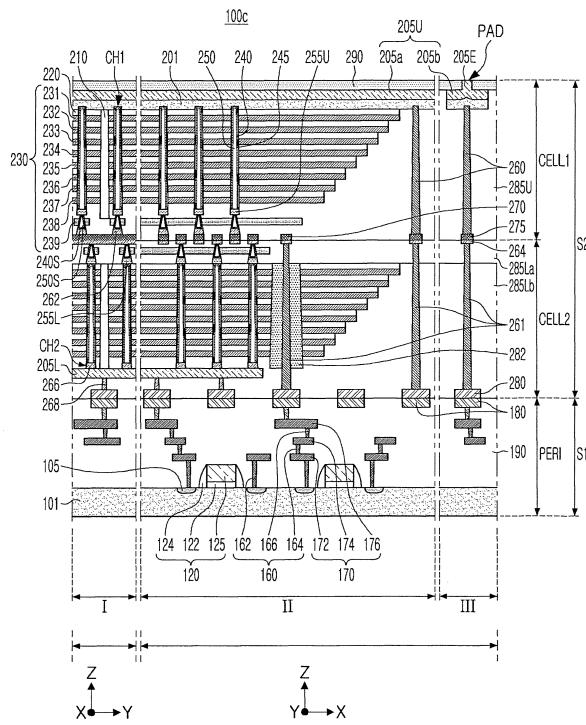

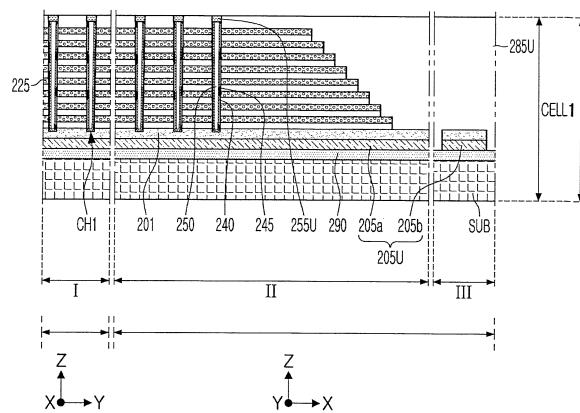

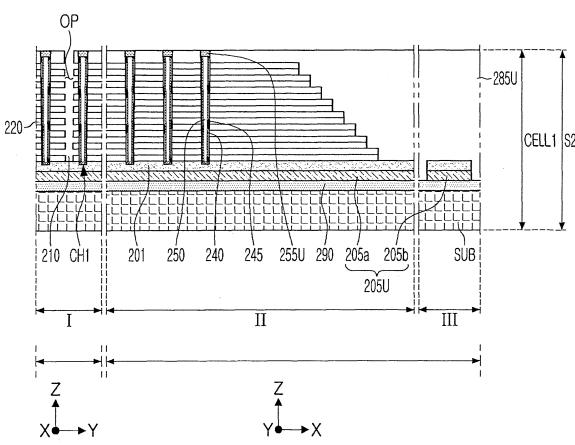

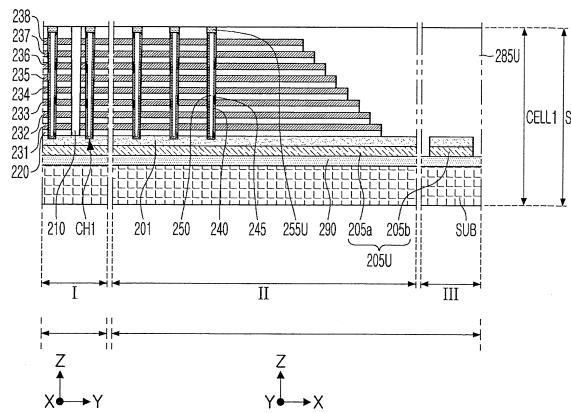

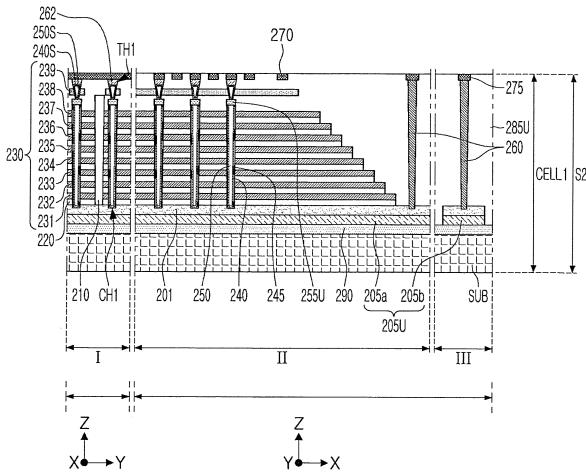

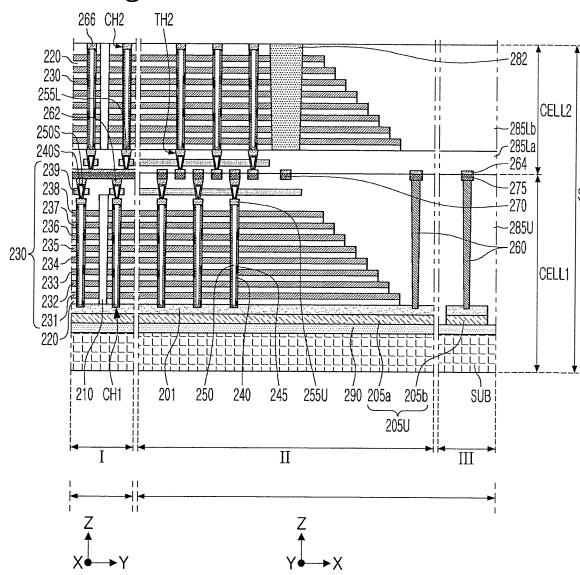

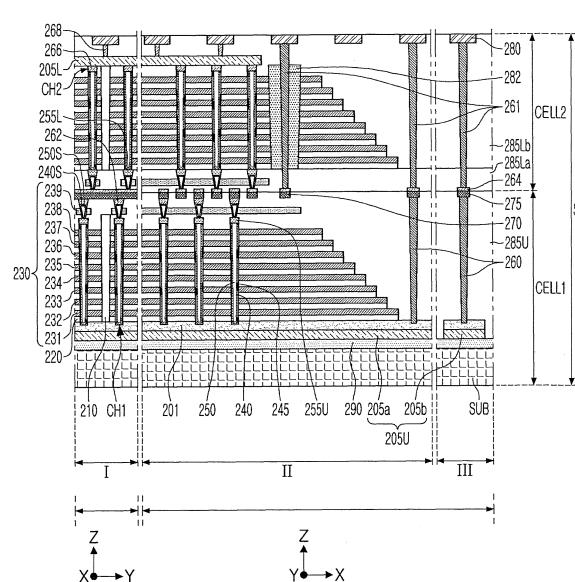

図 4 は、本発明の一実施形態による半導体装置の概略的な構成を示す断面図である。

図 4 を参照すると、半導体装置 1 0 0 は、上下に積層された第 1 半導体構造物 S 1 及び第 2 半導体構造物 S 2 を含む。

#### 【 0 0 3 2 】

第 1 半導体構造物 S 1 は、図 3 の第 1 半導体構造物 S 1 のように周辺回路領域 P E R I を含む。

第 2 半導体構造物 S 2 は、図 3 の第 2 半導体構造物 S 2 のようにメモリセル領域 ( C E L L 1、C E L L 2 ) を含む。

半導体装置 1 0 0 は、第 1 ~ 第 3 領域 ( I、I I、I I I ) を含み、第 1 及び第 2 領域 ( I、I I ) は、互いに垂直な方向にそれぞれ切断された領域である。

20

第 3 領域 I I I は、図 3 のパッド領域 P A D に対応するパッド領域 P A D が位置する領域を含むことができ、平面上において第 1 及び第 2 領域 ( I、I I ) の外側に位置し得る。

第 1 半導体構造物 S 1 は、基板 1 0 1、基板 1 0 1 上に配置された回路素子 1 2 0、回路コンタクトプラグ 1 6 0、回路配線ライン 1 7 0、及び第 1 接合パッド 1 8 0 を含む。

#### 【 0 0 3 3 】

基板 1 0 1 は、x 方向と y 方向に延長される上面を有する。

基板 1 0 1 は、別途の素子分離層が形成されて活性領域が定義される。

活性領域の一部には、不純物を含むソース / ドレイン領域 1 0 5 が配置される。

基板 1 0 1 は、半導体物質、例えば、I V 族半導体、I I I - V 族化合物半導体または I I - V I 族化合物半導体を含むことができる。

30

例えば、基板 1 0 1 は、単結晶のバルクウェハーとして提供され得る。

#### 【 0 0 3 4 】

回路素子 1 2 0 は、水平トランジスタを含む。

それぞれの回路素子 1 2 0 は、回路ゲート誘電層 1 2 2、スペーサ層 1 2 4、及び回路ゲート電極 1 2 5 を含む。

回路ゲート電極 1 2 5 の両側における基板 1 0 1 内には、ソース / ドレイン領域 1 0 5 が配置される。

#### 【 0 0 3 5 】

周辺領域絶縁層 1 9 0 は、基板 1 0 1 上において回路素子 1 2 0 上に配置される。

40

回路コンタクトプラグ 1 6 0 は、周辺領域絶縁層 1 9 0 を貫通してソース / ドレイン領域 1 0 5 に接続され、基板 1 0 1 から順次に位置する第 1 ~ 第 3 回路コンタクトプラグ ( 1 6 2、1 6 4、1 6 6 ) を含む。

回路コンタクトプラグ 1 6 0 によって回路素子 1 2 0 に電気的信号が印加される。

図に示していない領域において、回路ゲート電極 1 2 5 にも回路コンタクトプラグ 1 6 0 が接続され得る。

回路配線ライン 1 7 0 は、回路コンタクトプラグ 1 6 0 と接続され、複数の層をなす第 1 ~ 第 3 回路配線ライン ( 1 7 2、1 7 4、1 7 6 ) を含む。

#### 【 0 0 3 6 】

第 1 接合パッド 1 8 0 は、第 3 回路コンタクトプラグ 1 6 6 と接続されるように配置さ

50

れ、上面が周辺領域絶縁層 190 を介して第 1 半導体構造物 S1 の上面に露出する。

第 1 接合パッド 180 は、第 2 接合パッド 280 と共に、第 1 半導体構造物 S1 と第 2 半導体構造物 S2 とを接合するための接合層としての機能を果たす。

第 1 接合パッド 180 は、第 2 半導体構造物 S2 との接合及びそれによる電気的接続経路を提供するために、他の上記配線構造に比べて大きい平面積を有する。

第 1 接合パッド 180 は、第 2 接合パッド 280 と対応する位置に配置され、第 2 接合パッド 280 と同一または類似の大きさを有する。

第 1 接合パッド 180 は、導電性物質、例えば銅 (Cu) を含み得る。

#### 【0037】

第 2 半導体構造物 S2 は、ベース層 201 及びベース層 201 上に上下に積層された第 1 及び第 2 メモリセル領域 (CELL1, CELL2) を含む。 10

第 1 メモリセル領域 CELL1 は、ベース層 201 の下面に積層されたゲート電極 230 (231 ~ 239)、ゲート電極 230 と交互に積層される層間絶縁層 220、ゲート電極 230 を貫通するように配置される分離絶縁層 210、ゲート電極 230 を貫通するように配置される第 1 チャネル CH1、第 1 チャネル CH1 の下部のストリング選択チャネル領域 240S、ストリング選択チャネル領域 240S の下部の第 1 接続部 262、第 1 接続部 262 の下部の共通ビットライン 270、及びゲート電極 230 を覆う上部セル領域絶縁層 285U を含む。

第 1 メモリセル領域 CELL1 は、ベース層 201 の上面に順次に積層されて配置される上部導電層 205U 及びパッド絶縁層 290 をさらに含む。 20

また、第 1 メモリセル領域 CELL1 は、第 1 チャネル CH1 内のチャネル領域 240、ゲート誘電層 245、チャネル絶縁層 250、及び第 1 チャネルパッド 255U をさらに含む。

#### 【0038】

第 2 メモリセル領域 CELL2 は、共通ビットライン 270 の下面の第 2 接続部 264、第 2 接続部 264 の下部のストリング選択チャネル 240S、ストリング選択チャネル 240S の下部の第 2 チャネルパッド 255L、第 2 チャネルパッド 255L の下部の第 2 チャネル CH2、第 2 チャネル CH2 の下部の第 3 接続部 266、第 3 接続部 266 の下部の下部導電層 205L、下部導電層 205L の下部の第 4 接続部 268、及び第 4 接続部 268 と接続される第 2 接合パッド 280 を含む。 30

第 2 メモリセル領域 CELL2 は、第 1 メモリセル領域 CELL1 と同様に、第 2 チャネル CH2 を囲み、z 方向に互いに離隔して積層されたゲート電極 230、層間絶縁層 220、ゲート電極 230 を貫通するように配置される分離絶縁層 210、及びゲート電極 230 を覆う下部セル領域絶縁層 285La、285Lb をさらに含む。

#### 【0039】

第 2 半導体構造物 S2 は、配線構造物であって、上部導電層 205U に信号を印加する第 1 コンタクトプラグ 260、共通ビットライン 270 と並行して配置される接続パッド 275、接続パッド 275 の下部の第 2 接続部 264、及び第 2 接続部 264 と第 2 接合パッド 280 を接続する第 2 コンタクトプラグ 261 をさらに含む。 40

#### 【0040】

ベース層 201 は、x 方向と y 方向に延長される下面を有する。

ベース層 201 は、半導体物質を含み得る。

例えば、ベース層 201 は、多結晶シリコン層、またはエピタキシャル層として提供され得る。

ベース層 201 は、不純物を含むドープ領域を含み得る。

#### 【0041】

ゲート電極 230 は、ベース層 201 の下面に垂直に離隔して積層され、層間絶縁層 220 と共に積層構造をなす。

ゲート電極 230 は、図 2 の接地選択トランジスタ GST のゲートをなす下部ゲート電極 231、複数のメモリセル MC をなすメモリゲート電極 (232 ~ 238)、及びスト

10

20

30

40

50

リング選択トランジスタ (SST1、SST2) のゲートをなす上部ゲート電極 239 を含む。

半導体装置 100 の容量に応じて、メモリセル MC をなすメモリゲート電極 (232 ~ 238) の個数が決定される。

実施形態に応じて、ストリング選択トランジスタ (SST1、SST1) 及び接地選択トランジスタ GST1 の上部及び下部ゲート電極 (239、231) はそれぞれ 1 つまたは 2 つ以上であり得る。

#### 【0042】

下部ゲート電極 231 によって提供される接地選択トランジスタ GST は、メモリセル MC と同一または異なる構造を有することができ、上部ゲート電極 239 によって提供されるストリング選択トランジスタ (SST1、SST2) は、メモリセル MC と異なる構造を有することができる。10

特に、上部ゲート電極 239 は、他のゲート電極 (231 ~ 238) とは異なり、x - y 平面上において隣接するチャネル (CH1、CH2) の間に分割されて配置され得る。

一部のゲート電極 230、例えば、上部または下部ゲート電極 (231、239) に隣接したメモリゲート電極 (232 ~ 238) は、ダミーゲート電極であり得る。

#### 【0043】

ゲート電極 230 は、ベース層 201 の下面に垂直に互いに離隔して積層され、少なくとも一方向に互いに異なる長さに延長されて階段状の段差をなす。

ゲート電極 230 は x 方向に沿って、図 4 に示したような段差をなし、y 方向にも段差をなすように配置される。20

上記段差によって、ゲート電極 230 はゲート電極 230 の端部を含む所定領域が露出される。

ゲート電極 230 は、図に示していない領域において、上記段差を介して別途のコンタクトプラグと接続され得る。

#### 【0044】

ゲート電極 230 は、x 方向に沿って延長される分離絶縁層 210 によって一定の単位に分割されるように配置される。

一対の分離絶縁層 210 の間においてゲート電極 230 は、1 つのメモリブロックをなすことができるが、メモリブロックの範囲はこれに限定されない。30

ゲート電極 230 の一部、例えば、メモリゲート電極 (232 ~ 238) は、1 つのメモリブロック内で 1 つの層をなすことができる。

また、ゲート電極 230 は、少なくとも一部領域で貫通絶縁層 282 によって定義される貫通配線領域を有することができる。

#### 【0045】

層間絶縁層 220 は、ゲート電極 230 の間に配置される。

層間絶縁層 220 もゲート電極 230 と同様に、ベース層 201 の下面に垂直な方向に互いに離隔し、x 方向に延長されるように配置される。

層間絶縁層 220 は、シリコン酸化物及びシリコン窒化物のような絶縁性物質を含み得る。40

#### 【0046】

第 1 及び第 2 チャネル (CH1、CH2) は、ベース層 201 の下面に行と列をなして互いに離隔して配置される。

第 1 及び第 2 チャネル (CH1、CH2) は、格子柄を形成するように配置されるか、または一方向にジグザグ状に配置され得る。

第 1 及び第 2 チャネル (CH1、CH2) は、柱状を有し、横縦比によってベース層 201 に近いほど狭くなる傾斜した側面を有し得る。

第 1 及び第 2 チャネル (CH1、CH2) は、互いに同一の方向に傾斜した側面を有し得る。

例えば、第 1 及び第 2 チャネル (CH1、CH2) はいずれも、上部に向かうほど狭く

10

20

30

40

50

なるように傾斜した側面を有する。

本発明の一実施形態において、第1及び第2チャネル( C H 1、 C H 2 )の一部は、ダミーチャネルであり得る。

#### 【 0 0 4 7 】

第1及び第2チャネル( C H 1、 C H 2 )内には、チャネル領域 2 4 0 が配置される。

第1及び第2チャネル( C H 1、 C H 2 )内におけるチャネル領域 2 4 0 は、内部のチャネル絶縁層 2 5 0 を囲む環状( a n n u l a r )に形成することができるが、実施形態に応じて、チャネル絶縁層 2 5 0 無しに円柱または角柱のような柱形状を有することもできる。

チャネル領域 2 5 0 は、多結晶シリコンまたは単結晶シリコンのような半導体物質を含むことができ、上記半導体物質は、ドープされていない物質であるか、または p 型または n 型不純物を含む物質であり得る。 10

#### 【 0 0 4 8 】

第1及び第2チャネル( C H 1、 C H 2 )において共通ビットライン 2 7 0 に隣接したチャネル領域 2 4 0 の端部には、チャネルパッド( 2 5 5 U、 2 5 5 L )が配置される。

チャネルパッド( 2 5 5 U、 2 5 5 L )は、チャネル絶縁層 2 5 0 の上面を覆い、チャネル領域 2 4 0 と電気的に接続されるように配置される。

チャネルパッド( 2 5 5 U、 2 5 5 L )は、例えば、ドープされていない多結晶シリコンを含み得る。

#### 【 0 0 4 9 】

ゲート誘電層 2 4 5 は、ゲート電極 2 3 0 とチャネル領域 2 4 0 との間に配置される。

具体的に示していないが、ゲート誘電層 2 4 5 は、チャネル領域 2 4 0 から順次に積層されたトンネリング層、電荷保存層、及びブロッキング層を含む。 20

トンネリング層は、電荷を電荷保存層にトンネリングさせ、例えば、シリコン酸化物( SiO<sub>2</sub> )、シリコン窒化物( Si<sub>3</sub>N<sub>4</sub> )、シリコン酸窒化物( SiON )、またはそれらの組み合わせを含み得る。

電荷保存層は、電荷トラップ層またはフローティングゲート導電層であり得る。

ブロッキング層は、シリコン酸化物( SiO<sub>2</sub> )、シリコン窒化物( Si<sub>3</sub>N<sub>4</sub> )、シリコン酸窒化物( SiON )、高誘電率( h i g h - k )誘電物質、またはそれらの組み合わせを含み得る。 30

本発明の一実施形態において、ゲート誘電層 2 4 5 の少なくとも一部は、ゲート電極 2 3 0 に沿って水平方向に延長され得る。

#### 【 0 0 5 0 】

チャネル領域 2 4 0 は、チャネルパッド( 2 5 5 U、 2 5 5 L )が配置されない端部でベース層 2 0 1 または第3接続部 2 6 6 と直接接続される。

#### 【 0 0 5 1 】

ストリング選択チャネル 2 4 0 S は、チャネルパッド( 2 5 5 U、 2 5 5 L )と共にビットライン 2 7 0 との間に配置される。

ストリング選択チャネル 2 4 0 S は、上部ゲート電極 2 3 9 を貫通して一端がチャネルパッド( 2 5 5 U、 2 5 5 L )と接続され、他端が第1及び第2接続部( 2 6 2、 2 6 4 )にそれぞれ接続される。 40

第1メモリセル領域 C E L L 1 のストリング選択チャネル 2 4 0 S は、第1接続部 2 6 2 まで延長される 1 つの貫通孔内に配置され、第2メモリセル領域 C E L L 2 のストリング選択チャネル 2 4 0 S は、第2チャネルパッド 2 5 5 L まで延長される 1 つの貫通孔内に配置されるが、これに限定されない。

本明細書において、第1及び第2チャネル( C H 1、 C H 2 )という用語を広義に用いる場合には、貫通孔を含む領域までを称するように用いることができる。

ストリング選択チャネル 2 4 0 S は、多結晶シリコンまたは単結晶シリコンのような半導体物質を含むことができ、上記半導体物質は、ドープされていない物質であるか、または p 型または n 型不純物を含む物質であり得る。 50

**【0052】**

ストリング選択チャネル 240S と上部ゲート電極 239との間には、ゲート絶縁層が配置され、ストリング選択チャネル 240S の内部には、貫通孔を埋め込むストリング絶縁層 250S が配置される。

但し、実施形態に応じて、ストリング選択チャネル 240S が貫通孔を埋め込むことも可能である。

ストリング絶縁層 250S は、シリコン酸化物、シリコン窒化物などの絶縁物質を含み得る。

**【0053】**

第1接続部 262 は、第1チャネル CH1 の下部のストリング選択チャネル 240S と共通ビットライン 270 を接続するように配置される。 10

第2接続部 264 は、共通ビットライン 270 の下部で共通ビットライン 270 と第2チャネル CH2 の上部のストリング選択チャネル 240S を接続するように配置される。

第3接続部 266 は、第2チャネル CH2 の下部で第2チャネル CH2 と下部導電層 205L を接続するように配置される。

第4接続部 268 は、下部導電層 205L と第2接合パッド 280 を接続するコントラクトプラグであり得る。

**【0054】**

第1～第4接続部(262、264、266、268)はそれぞれ、導電性物質を含み得る。 20

例えば、第1～第3接続部(262、264、266)は、ドープされた多結晶シリコンを含むことができ、第4接続部 268 は、タンゲステン(W)、アルミニウム(A1)、銅(Cu)、タンゲステン窒化物(WN)、タンタル窒化物(TaN)、チタン窒化物(TiN)、またはそれらの組み合わせのような金属物質を含むことができる。

**【0055】**

共通ビットライン 270 は、第1接続部 262 の下端で第1接続部 262 と第2接続部 264 との間に配置される。

共通ビットライン 270 は、第1及び第2チャネル(CH1、CH2)に共通に接続され、図2のビットライン(BL0～BL2)に該当する。

共通ビットライン 270 によって、半導体装置 100 はさらに高密度に集積させることができる。 30

共通ビットライン 270 は、多結晶シリコンのような半導体物質、またはタンゲステン(W)、アルミニウム(A1)、銅(Cu)、タンゲステン窒化物(WN)、タンタル窒化物(TaN)、チタン窒化物(TiN)、またはそれらの組み合わせのような金属物質を含むことができる。

**【0056】**

上部導電層 205U は、互いに離隔して配置される第1及び第2導電層(205a、205b)を含む。

第1及び第2導電層(205a、205b)は、同一の工程段階で形成されて物質が互いに同一であり、互いに同一の高さレベルに同一の厚さを有して位置する。 40

即ち、第1及び第2導電層(205a、205b)は、上面及び下面がそれぞれ互いに同一平面上に位置する。

下部導電層 205L は、第2チャネル CH2 の下部に配置される。

上部及び下部導電層(205U、205L)は、金属物質を含むことができ、例えば、タンゲステン(W)、アルミニウム(A1)、銅(Cu)、タンゲステン窒化物(WN)、タンタル窒化物(TaN)、チタン窒化物(TiN)、またはそれらの組み合わせを含むことができる。

**【0057】**

上部導電層 205U において、第1導電層 205a はベース層 201 の第1及び第2領域(I、II)の上部に配置され、平面上でゲート電極 230 及び第1チャネル CH1 と

重なって配置される。

第1導電層205aは、プレート状を有し、半導体装置100において図2の共通ソースラインCSLとしての機能を果たす。

第1導電層205aは、第1コントラクトプラグ260及びベース層201を介して周辺回路領域PERIから電気信号の印加を受け、これにより、ベース層201は、少なくとも一部領域にドープ元素を含み得る。

または、第1導電層205aは、第1コントラクトプラグ260と直接接続することもできる。

#### 【0058】

第2導電層205bは、第1導電層205aと物理的及び電気的に分離されて位置し、10

x方向に沿って並んで位置する。

これにより、ベース層201も第1及び第2導電層(205a、205b)と共にベース層201の第1及び第2領域(I、II)と第3領域IIIで互いに分離されて配置される。

第2導電層205bは、平面上でゲート電極230及び第1チャネルCH1と重畠しないように配置される。

第2導電層205bは、ベース層201の第3領域IIIの上部に配置され、平面上で第1コントラクトプラグ260と重畠して配置される。

第2導電層205bは、上面を介して、半導体装置100が実装されるパッケージのような装置の信号伝達媒体のような電気的接続構造物と接続される。20

#### 【0059】

即ち、上部に露出した第2導電層205bは、パッド領域PADとしての機能を果たす。

半導体装置100の内部では、第2導電層205bが周辺回路領域PERIの入出力回路と電気的に接続される。

半導体装置100では、共通ソースラインCSLとして用いられる第1導電層205aの形成工程を用いて第2導電層205bを形成し、それを外部との入出力のためのパッド領域PADとして用いることにより、全体厚さを最小化しながら工程を単純化することができる。

第2導電層205bは、一方向における幅が、例えば、50μm～200μmの範囲を有し得るが、これに限定されない。30

#### 【0060】

下部導電層205Lは、ベース層201の第1及び第2領域(I、II)において第2チャネルCH2の下部に配置され、平面上でゲート電極230及び第2チャネルCH2と重畠して配置される。

下部導電層205Lは、プレート状を有し、第1導電層205aと共に、半導体装置100において図2の共通ソースラインCSLとしての機能を果たす。

下部導電層205Lは、第4接続部268及び第2接合パッド280を介して周辺回路領域PERIから電気信号の印加を受ける。

#### 【0061】

パッド絶縁層290は、上部導電層205U上に配置される。

パッド絶縁層290は、第2導電層205bの一部領域をオープンする開口部を有し、これにより第2導電層205bが上部に露出するようとする。

即ち、パッド絶縁層290は、パッド領域PADを定義する。

例えば、開口部は、複数個が図3のように列をなすように配置され得る。

開口部によって、半導体装置100の上面はリセスした領域を有する。

また、パッド絶縁層290は、半導体装置100を保護するパッシベーション層としての機能を果たすことができる。

#### 【0062】

パッド絶縁層290は、シリコン酸化物、シリコン窒化物、及び炭化窒化物の少なくとも1つを含むことができる。

10

20

30

40

50

本発明の一実施形態において、パッド絶縁層 290 は、複数の層が積層された形態を有し得る。

この場合、下部層は、相対的に上部導電層 205Uとの接合性に優れた物質からなり、上部層は、相対的にシリコンSiとの接合性に優れた物質からなる。

例えば、下部層はシリコン酸化物を含み、上部層はシリコン窒化物を含む。

また、本発明の一実施形態において、パッド絶縁層 290 上に半導体装置 100 を保護するためのパッシベーション層がさらに配置させることもできる。

パッシベーション層は、例えば、感光性ポリイミド (photosensitive polyimide: PSP) のような感光性樹脂物質からなることができるが、これに限定されず、シリコン窒化物、シリコン酸化物などの絶縁物質を含むことができる。 10

#### 【0063】

第1コントラクトプラグ 260 は、上部セル領域絶縁層 285U を貫通し、一端でベース層 201 または上部導電層 205U と接続され、他端で接続パッド 275 と接続される。

本発明の一実施形態において、第1コントラクトプラグ 260 は、ベース層 201 を貫通して上部導電層 205U と直接接続される。

第1コントラクトプラグ 260 は、図に示していない領域において、ゲート電極 230 とも接続され得る。

第2コントラクトプラグ 261 は、下部セル領域絶縁層 (285La, 285Lb) を貫通して第2接続部 264 と第2接合パッド 280 を接続する。 20

第2コントラクトプラグ 261 の一部は、ゲート電極 230 を貫通する貫通絶縁層 282 を貫通するように配置される。

貫通絶縁層 282 は、絶縁物質を含み、内部に第2コントラクトプラグ 261 を含む配線構造物が形成され得る。

#### 【0064】

第1及び第2コントラクトプラグ (260, 261) は、円筒形状を有する。

第1及び第2コントラクトプラグ (260, 261) は、縦横比によってベース層 201 に近いほど狭くなる傾斜した側面を有する。

本発明の一実施形態において、第1及び第2コントラクトプラグ (260, 261) は、第2領域IIと第3領域IIIで互いに異なる直径及び/または高さを有し得る。

実施形態に応じて、第1及び第2コントラクトプラグ (260, 261) の一部は、電気的信号が印加されないダミーコンタクトプラグであり得る。 30

#### 【0065】

接続パッド 275 は、共通ビットライン 270 と同一の工程段階で形成されて物質が互いに同一であり、互いに同一の高さレベルに同一の厚さを有して位置する。

即ち、接続パッド 275 及び共通ビットライン 270 は、上面及び下面がそれぞれ互いに同一平面上に位置する。

接続パッド 275 は、共通ビットライン 270 とは異なり、図2のビットライン (BL0 ~ BL2) には該当せず、接続パッド 275 の下面上の第2接続部 264 と共に、第1及び第2コントラクトプラグ (260, 261) を接続する接続部としての機能を果たす。 40

#### 【0066】

特に、第3領域IIIにおいて、パッド領域PADをなす第2導電層 205b は、順次に第1コントラクトプラグ 260、接続パッド 275、第2接続部 264、第2コントラクトプラグ 261、及び第2接合パッド 280 を介して下部の周辺回路領域PERIの回路素子 120 と電気的に接続される。

したがって、セル領域絶縁層 (285U, 285La, 285Lb) の高さが相対的に高い場合でも、安定的に周辺回路領域PERIと電気的に接続され得る。

#### 【0067】

第2接合パッド 280 は、第4接続部 268 の下部に配置され、下面が第2下部セル領域絶縁層 285Lb を介して第2半導体構造物 S2 の下面に露出する。

第2接合パッド 280 は、第1接合パッド 180 と共に、第1半導体構造物 S1 と第2

10

20

30

40

50

半導体構造物 S 2 を接合するための接合層としての機能を果たす。

第 2 接合パッド 2 8 0 は、第 1 半導体構造物 S 1 との接合及びそれによる電気的接続経路を提供するために、他の配線構造に比べて大きい平面積を有し得る。

#### 【 0 0 6 8 】

第 2 接合パッド 2 8 0 は、第 1 ~ 第 3 領域 ( I、I I、I I I ) でそれぞれ一定のパターンをなして配列される。

第 2 接合パッド 2 8 0 は、第 1 ~ 第 3 領域 ( I、I I、I I I ) で同一の高さレベルに配置され、互いに同一または異なる大きさを有し得る。

第 2 接合パッド 2 8 0 は平面上で、例えば、四角形、円形または橢円形の形状を有することができるが、これに限定されない。

第 2 接合パッド 2 8 0 は導電性物質、例えば、銅 ( Cu ) を含むことができる。

#### 【 0 0 6 9 】

セル領域絶縁層 ( 2 8 5 U、2 8 5 L a、2 8 5 L b ) は、絶縁物質からなる。

セル領域絶縁層 ( 2 8 5 U、2 8 5 L a、2 8 5 L b ) はそれぞれ、互いに異なる工程段階で形成された複数の絶縁層を含む。

したがって、セル領域絶縁層 ( 2 8 5 U、2 8 5 L a、2 8 5 L b ) 間の区分は、例示的なものと理解されることができる。

本発明の一実施形態において、第 2 下部セル領域絶縁層 2 8 5 L b は、第 2 接合パッド 2 8 0 が配置される下端に所定の厚さを有する接合誘電体層を含む。

接合誘電層は、第 1 半導体構造物 S 1 の下面にも配置され、これにより誘電体 - 誘電体接合が行われる。

接合誘電層は、第 2 接合パッド 2 8 0 の拡散防止層としての機能も果たすことができ、例えば、SiO、SiN、SiCN、SiOC、SiON、及びSiOCNの少なくとも 1 つを含むことができる。

#### 【 0 0 7 0 】

第 1 及び第 2 半導体構造物 ( S 1、S 2 ) は、第 1 及び第 2 接合パッド ( 1 8 0、2 8 0 ) の接合、例えば、銅 ( Cu ) - 銅 ( Cu ) 接合によって接合される。

第 1 及び第 2 接合パッド ( 1 8 0、2 8 0 ) は、配線構造物の他の構成よりも相対的に広い面積を有するため、第 1 及び第 2 半導体構造物 ( S 1、S 2 ) の間の電気的接続の信頼性が向上することができる。

本発明の一実施形態において、第 1 及び第 2 半導体構造物 ( S 1、S 2 ) は、第 1 及び第 2 接合パッド ( 1 8 0、2 8 0 ) の周囲に配置されたセル領域絶縁層 2 8 5 と周辺領域絶縁層 1 9 0 の誘電体 - 誘電体接合によるハイブリッド接合によって接合される。

#### 【 0 0 7 1 】

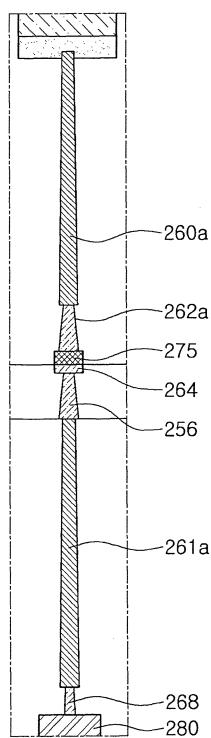

図 5 a 及び図 5 b は、本発明の一実施形態による半導体装置の一部構成を示す概略的な断面図である。

図 5 a 及び図 5 b では、図 4 の「 A 」領域に対応する領域を拡大して示す。

図 5 a を参照すると、本実施形態では、図 4 の実施形態とは異なり、パッド領域 P A D と接続される第 1 コンタクトプラグ 2 6 0 a 上に第 1 接続部 2 6 2 a がさらに配置される。

#### 【 0 0 7 2 】

第 1 接続部 2 6 2 a は、第 1 及び第 2 領域 ( I、I I ) における接続部とは異なり、ストリング選択チャネル 2 4 0 S を形成する貫通孔内に延長されて貫通孔をすべて埋め込む形態を有する。

また、本実施形態では、パッド領域 P A D と電気的に接続される第 2 コンタクトプラグ 2 6 1 a の上下にそれぞれ貫通部 2 5 6 及び第 4 接続部 2 6 8 がさらに配置される。

貫通部 2 5 6 は、第 1 及び第 2 領域 ( I、I I ) の第 2 チャネルパッド 2 5 5 L とは異なり、ストリング選択チャネル 2 4 0 S を形成する貫通孔内に延長されて貫通孔をすべて埋め込む形態を有する。

#### 【 0 0 7 3 】

10

20

30

40

50

したがって、パッド領域 P A D をなす第 2 導電層 2 0 5 b は、順次に配置される第 1 コンタクトプラグ 2 6 0 a、第 1 接続部 2 6 2 a、接続パッド 2 7 5、第 2 接続部 2 6 4 a、貫通部 2 5 6、第 2 コンタクトプラグ 2 6 1 a、第 4 接続部 2 6 8、及び第 2 接合パッド 2 8 0 を介して、下部の周辺回路領域 P E R I と接続される。

本実施形態の場合、第 1 接続部 2 6 2 a、貫通部 2 5 6、及び第 4 接続部 2 6 8 が配置されることにより、第 1 及び第 2 コンタクトプラグ ( 2 6 0 a、2 6 1 a ) が相対的に短い高さで形成することができ、工程が相対的に容易になることができる。

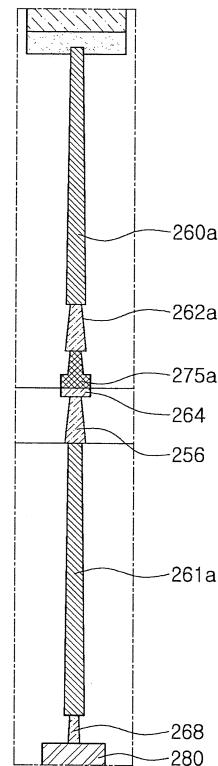

#### 【 0 0 7 4 】

図 5 b を参照すると、図 5 a の実施形態とは異なり、接続パッド 2 7 5 a が上部に延長されるプラグ部をさらに含む。

10

したがって、接続パッド 2 7 5 a は、プラグ部を介して第 1 接続部 2 6 2 a と接続される。

図に示してはいないが、第 1 及び第 2 領域 ( I、I I ) でも共通ビットライン 2 7 0 がこのようなプラグ部をそれぞれ含むことができる。

#### 【 0 0 7 5 】

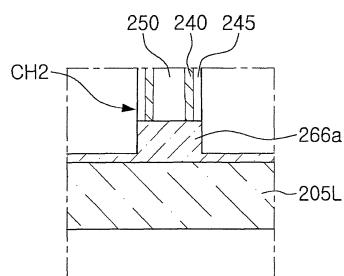

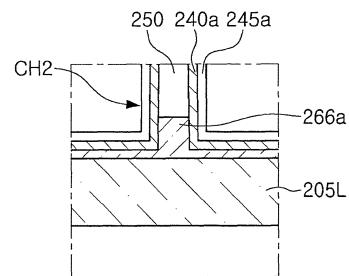

図 6 a 及び図 6 b は、本発明の一実施形態による半導体装置の一部構成を示す概略的な断面図である。

図 6 a 及び図 6 b では、図 4 の「 B 」領域に対応する領域を拡大して示す。

図 6 a を参照すると、本実施形態では、図 4 の実施形態とは異なり、第 3 接続部 2 6 6 a が第 2 チャネル C H 2 から下部導電層 2 0 5 L の上面に延長される形態を有する。

20

これにより、第 3 接続部 2 6 6 a は下部導電層 2 0 5 L のようにプレート状に下部に配置される。

図 6 b を参照すると、第 2 チャネル C H 2 のチャネル領域 2 4 0 a 及びゲート誘電層 2 4 5 a も、第 3 接続部 2 6 6 a と共に下部導電層 2 0 5 L の上面に延長される形態を有する。

#### 【 0 0 7 6 】

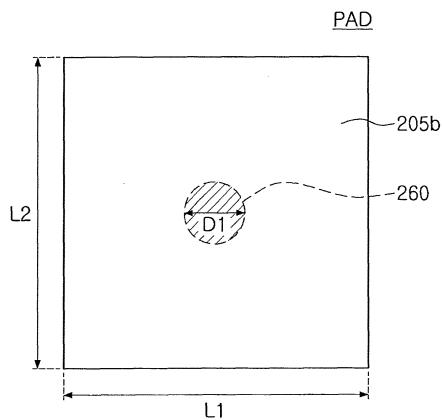

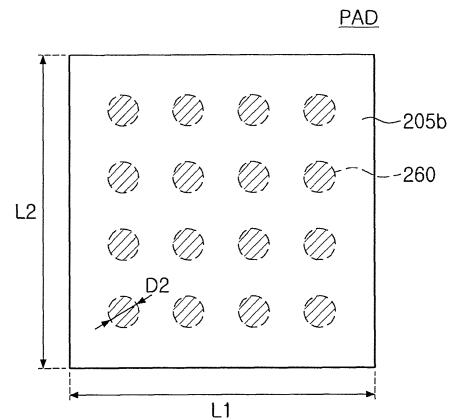

図 7 a 及び図 7 b は、本発明の一実施形態による半導体装置の一部構成を示す概略的な平面図である。

図 7 a 及び図 7 b を参照すると、図 4 のパッド領域 P A D における第 2 導電層 2 0 5 b 及び第 1 コンタクトプラグ 2 6 0 が平面に配置される様子を示している。

30

特に、第 2 導電層 2 0 5 b は、図 4 のパッド絶縁層 2 9 0 の開口部によって露出し、1 つのパッド領域 P A D をなす領域を示す。

#### 【 0 0 7 7 】

パッド領域 P A D における第 2 導電層 2 0 5 b は四角形状を有し、x 方向に沿って第 1 長さ L 1 を有し、y 方向に沿って第 2 長さ L 2 を有する。

第 1 及び第 2 長さ ( L 1、L 2 ) は、同一または異なり、例えば、2 0 μ m ~ 1 0 0 μ m の範囲を有することができる。

但し、実施形態に応じて、開口部を介して露出する第 2 導電層 2 0 5 b の形状は、四角形に限定されず、円形、橢円形、多角形など様々な形状を有することができる。

#### 【 0 0 7 8 】

図 7 a に示すように、1 つのパッド領域 P A D をなす第 2 導電層 2 0 5 b の下部には、1 つの第 1 コンタクトプラグ 2 6 0 が接続される。

40

第 1 コンタクトプラグ 2 6 0 の第 1 直径 D 1 または最大幅は、例えば、1 0 0 n m ~ 1 0 μ m の範囲を有することができる。

この場合、第 1 コンタクトプラグ 2 6 0 は、パッド領域 P A D をなす第 2 導電層 2 0 5 b の中央に位置することができるが、これに限定されない。

#### 【 0 0 7 9 】

図 7 b に示すように、1 つのパッド領域 P A D をなす第 2 導電層 2 0 5 b の下部には、複数の第 1 コンタクトプラグ 2 6 0 が接続される。

この場合、パッド領域 P A D にワイヤなどが接合されたときに支持力が上昇するため、

50

半導体装置に加わるストレスを緩和することができる。

第1コンタクトプラグ260は、行と列をして配列される。

第1コンタクトプラグ260のそれぞれの第2直径D2または最大幅は、例えば、100nm～500nmの範囲を有することができ、図7aの第1直径D1と同一または小さい。

#### 【0080】

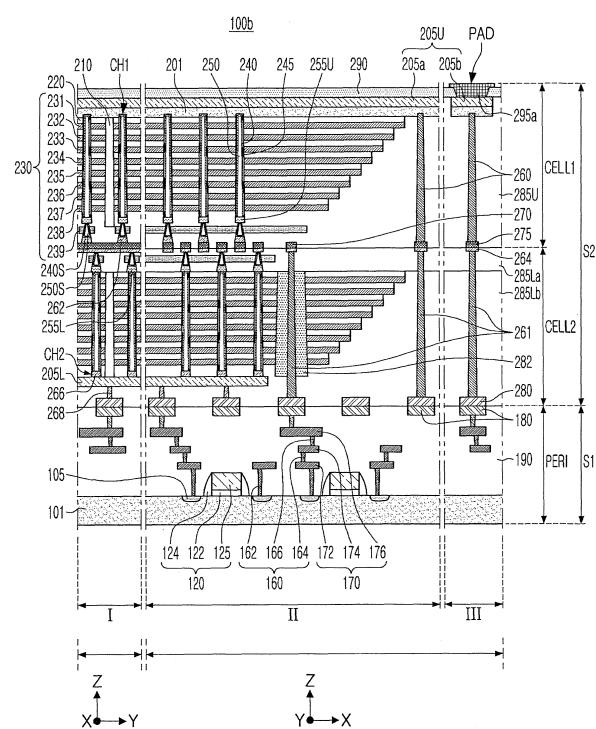

図8a～図8cは、本発明の一実施形態による半導体装置の概略的な断面図である。

図8aを参照すると、半導体装置100aの第2半導体構造物S2は、パッド領域PADの第2導電層205b上に配置される接続層295をさらに含む。

#### 【0081】

接続層295は、パッド絶縁層290の開口部を介して露出した第2導電層205bの上面に配置され、第2導電層205bの上面からパッド絶縁層290の側面に沿ってパッド絶縁層290の上面の一部領域上に延長される。

但し、本発明の一実施形態において、接続層295は、第2導電層205bの露出した上面のみに配置することもできる。

この場合、接続層295は表面処理層に該当する。

接続層295は、第2導電層205bと異なる物質を含み得、例えば、アルミニウム(A1)のような金属層であることができる。

特に、接続層295は、露出した第2導電層205bに接続される外部電気接続構造物、例えば、ワイヤ物質との相互拡散(interdiffusion)が円滑に行われ結合力に優れた金属物質からなることができる。

#### 【0082】

図8bを参照すると、半導体装置100bの接続層295aは、パッド絶縁層290の開口部を充填し、パッド絶縁層290の上面の一部領域上に配置される。

これにより、接続層295aは、半導体装置100bの上面から突出した形態を有する。接続層295aは、単一層または複数層からなることができる。

#### 【0083】

図8cを参照すると、半導体装置100cの第2半導体構造物S2において、パッド領域PADの第2導電層205bは、パッド絶縁層290を貫通するように延長される延長部205Eをさらに含む。

半導体装置100cは、図4の実施形態とは異なり、パッド絶縁層290の開口部によって第2導電層205bの一部が露出するのではなく、第2導電層205bの延長部205Eがパッド絶縁層290を貫通して上部に露出する形態を有する。

第2導電層205bの下面は、延長部205Eに対応する領域に凹部を有することができるが、これに限定されない。

上記凹部は、第2導電層205bを形成する際に、延長部205Eをなす導電物質を充填することにより形成される形状であり得る。

特に、パッド領域PADにおいて第2導電層205bの幅は、図4の実施形態における幅よりも小さい。

本実施形態の場合、パッド絶縁層290の開口部を形成する前に延長部205Eを先に形成するため、工程マージンが図4の実施形態の場合と異なって、相対的に小さく形成することができる。

#### 【0084】

本発明の一実施形態において、第2導電層205bの延長部205Eは、パッド絶縁層290の上面から所定の高さに突出することもできる。

また、実施形態に応じて、第2導電層205bの延長部205Eは、傾斜した側壁を有することもでき、例えば、上面の幅が下面の幅よりも狭いテーパ状を有することができる。

延長部205Eは、円筒状、テーパ付き円筒状、トレンチなどの形状を有することができるが、これに限定されない。

本発明の一実施形態において、延長部205E上にも図8aの実施形態と同様に、別途

10

20

30

40

50

の接続層がさらに配置することもできる。

**【0085】**

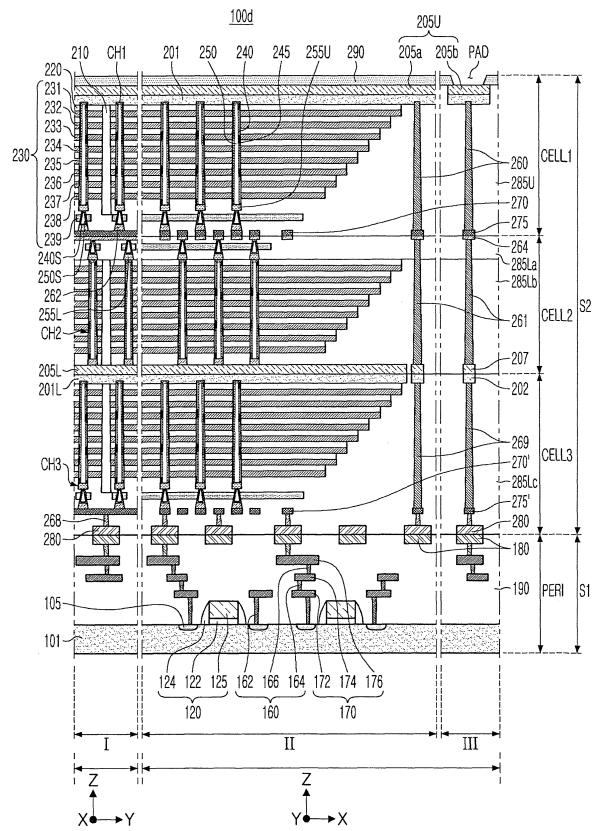

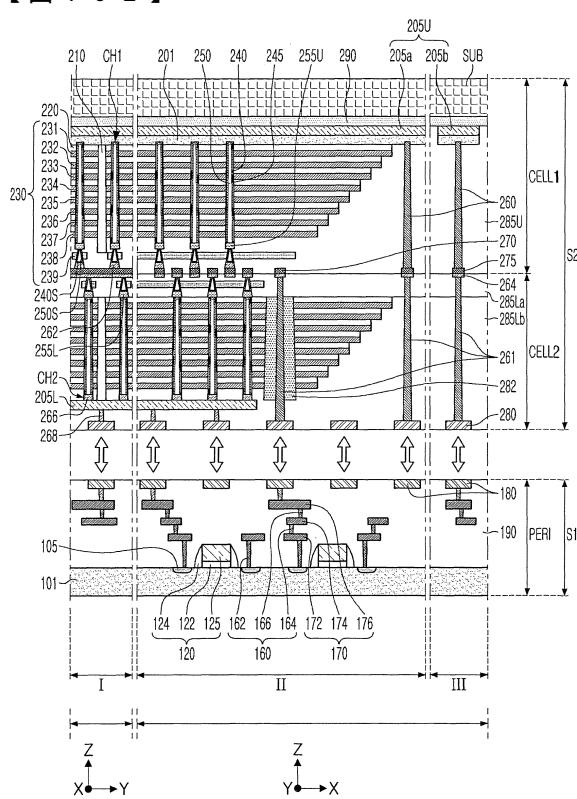

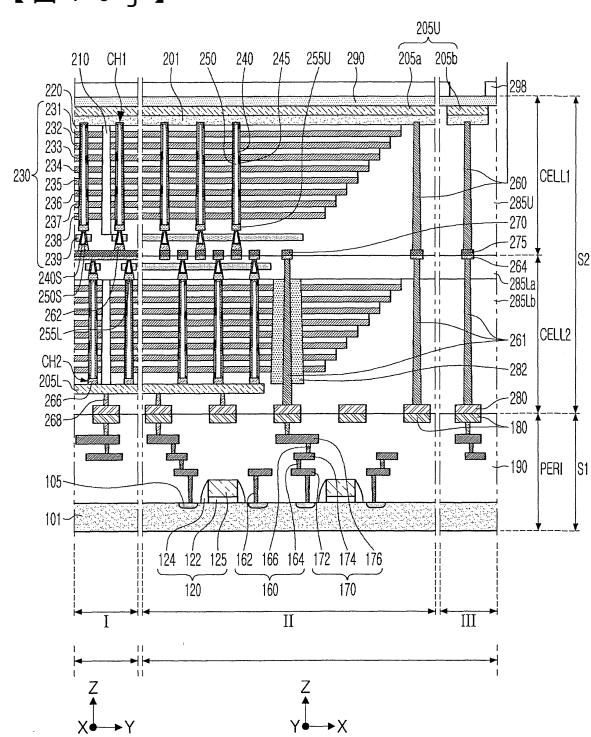

図9は、本発明の一実施形態による半導体装置の概略的な構成を示す断面図である。

図9を参照すると、半導体装置100dの第2半導体構造物S2は、第3メモリセル領域CELL3をさらに含む。

**【0086】**

第3メモリセル領域CELL3は、第2メモリセル領域CELL2の下部に配置され、下部導電層205Lの下面上の下部基板201L、下部基板201L上の第3チャネルCH3、第3チャネルCH3を囲み、z方向に互いに離隔して積層されたゲート電極230、層間絶縁層220、ゲート電極230を貫通するように配置される分離絶縁層210、及びゲート電極230を覆う下部セル領域絶縁層285Lcを含む。 10

**【0087】**

第3チャネルCH3は、上部の第2チャネルCH2と下部導電層205Lとして提供される共通ソースラインCSL(図2を参照)を共有する構造を有する。

第3チャネルCH3は、第1及び第2チャネル(CH1、CH2)の共通ビットライン270とは分離されたビットライン270' と下部で接続される。

本発明の一実施形態において、第2半導体構造物S2に配置されるメモリセル領域の個数は多様に変更することができる。

メモリセル領域が複数個に配置される場合、上下に隣接して配置されるメモリセル領域の間でビットライン270または共通ソースラインCSLが共有され得る。 20

**【0088】**

第3メモリセル領域CELL3は、第3チャネルCH3の下面上のストリング選択チャネル240S、ストリング選択チャネル240Sの下部の第1接続部262、第1接続部262の下部のビットライン270'、ビットライン270'の下部の第4接続部268、及び第4接続部268の下部の第2接合パッド280をさらに含む。

第3メモリセル領域CELL3は、第3領域IIIで下部導電層205Lと同一の高さレベルに配置される導電性パッド207、下部基板201Lと同一の高さレベルに配置される半導体パッド202、第3コンタクトプラグ269、及びビットライン270' と同一の高さレベルに配置される下部接続パッド275'をさらに含む。

**【0089】**

導電性パッド207は、下部導電層205Lと同一の工程で形成することができ、半導体パッド202は、下部基板201Lと同一の工程段階で形成され得る。 30

したがって、導電性パッド207及び半導体パッド202はそれぞれ、下部導電層205L及び下部基板201Lと同一の物質からなり、同一の厚さを有する。

第3コンタクトプラグ269は、下部セル領域絶縁層285Lcを貫通し、半導体パッド202と下部接続パッド275'を接続する。

パッド領域PADである第3領域IIIにおいて、第2導電層205bは、順次に第1コンタクトプラグ260、接続パッド275、第2接続部264、第2コンタクトプラグ261、導電性パッド207、半導体パッド202、第3コンタクトプラグ269、下部接続パッド275'、第4接続部268、及び第2接合パッド280を介して下部の周辺回路領域PERIの回路素子120と電気的に接続される。 40

**【0090】**

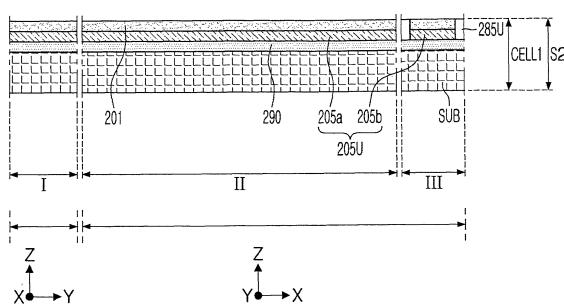

図10a～図10jは、本発明の一実施形態による半導体装置の製造方法を説明するための概略的な断面図である。

図10a～図10jは、図4に対応する領域を示す。

**【0091】**

図10aを参照すると、まず図4の第2半導体構造物S2を形成する。

そのために、ベース基板SUB上にパッド絶縁層290、上部導電層205U、及びベース層201を順次に形成する。

ベース基板SUBは、後続の工程を介して除去される層であり、シリコン(Si)のよ

うな半導体基板であり得る。

図4においてベース層201上に配置される層を、ベース基板SUB上に逆の順序で形成する。

#### 【0092】

上部導電層205U及びベース層201は、全面的に形成した後にパターニングし、第1及び第2領域I、IIと第3領域IIIの間のセル領域絶縁層285Uによって互いに分離されるようにする。

これにより、上部導電層205Uは、互いに離隔して配置される第1及び第2導電層(205a、205b)を含む。

セル領域絶縁層285Uは、後続の工程で形成される絶縁層と共に、図4の上部セル領域絶縁層285Uをなす層である。 10

図8cの実施形態の場合、本段階でパッド絶縁層290をパターニングして開口部を形成し、上部導電層205Uを形成する際に上記開口部を充填して延長部205Eを形成することにより製造することができる。

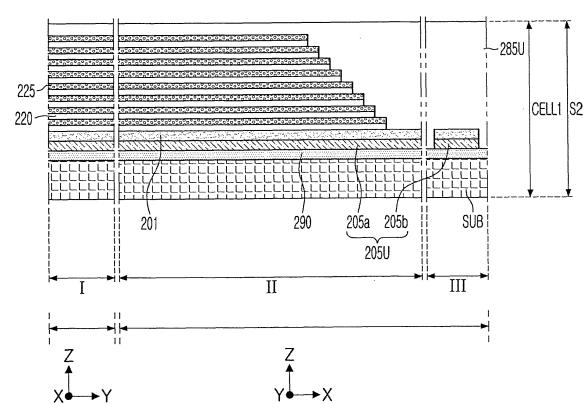

#### 【0093】

図10bを参照すると、ベース層201上に犠牲層225及び層間絶縁層220を交互に積層し、犠牲層225が互いに異なる長さに延長されるように犠牲層225及び層間絶縁層220の一部を除去する。

犠牲層225は、後続の工程を介してゲート電極230に交替される層である。

犠牲層225は、層間絶縁層220に対してエッチング選択性を有してエッチングされる物質で形成される。 20

例えば、層間絶縁層220は、シリコン酸化物及びシリコン窒化物の少なくとも1つからなることができ、犠牲層225は、シリコン、シリコン酸化物、シリコンカーバイド、及びシリコン窒化物の中から選択された層間絶縁層220と異なる物質からなることができる。

実施形態において、層間絶縁層220の厚さはすべて同一でなくてもよい。

#### 【0094】

次に、上部の犠牲層225が下部の犠牲層225よりも短く延長されるように、犠牲層225及び層間絶縁層220に対するフォトリソグラフィ工程及びエッチング工程を繰り返して行う。 30

これにより、犠牲層225は、階段形状をなす。

本発明の一実施形態において、犠牲層225は、端部で相対的に厚い厚さを有するようになることができ、そのための工程がさらに行うことができる。

次に、犠牲層225と層間絶縁層220の積層構造物の上部を覆う絶縁物質を蒸着することにより、上部セル領域絶縁層285Uを形成する。

#### 【0095】

図10cを参照すると、犠牲層225及び層間絶縁層220の積層構造物を貫通する第1チャネルCH1を形成する。

第1チャネルCH1を形成するために、まず、積層構造物を異方性エッチングしてチャネル孔を形成する。 40

積層構造物の高さのために、チャネル孔の側壁は、ベース層201の上面に対して垂直でないことがある。

本発明の一実施形態において、チャネル孔は、ベース層201の一部をリセスするようになる。

但し、チャネル孔は、上部導電層205Uまで延長されないように形成する。

#### 【0096】

次に、チャネル孔内にチャネル領域240、ゲート誘電層245、チャネル絶縁層250、及び第1チャネルパッド255Uを形成して第1チャネルCH1を形成する。

ゲート誘電層245は、原子層堆積(Atomic Layer Deposition: ALD)、化学気相蒸着(Chemical Vapor Deposition: CVD) 50

D) を用いて均一な厚さを有するように形成する。

本段階では、ゲート誘電層 245 の少なくとも一部がチャネル領域 240 に沿って垂直に延長されて形成される。

チャネル領域 240 は、第 1 チャネル CH1 内のゲート誘電層 245 上に形成する。

チャネル絶縁層 250 は、第 1 チャネル CH1 を充填するように形成され、絶縁物質である。

但し、実施形態に応じて、チャネル絶縁層 250 ではない導電性物質でチャネル領域 240 の間の空間を充填することもできる。

第 1 チャネルパッド 255U は、導電性物質からなり得、例えば、多結晶シリコンからなる。

10

#### 【0097】

図 10d を参照すると、犠牲層 225 及び層間絶縁層 220 の積層構造物を貫通する開口部 OP を形成し、開口部 OP を介して犠牲層 225 を除去する。

開口部 OP は、第 1 領域 I に示され、x 方向に延長されるトレンチ状に形成される。

犠牲層 225 は、例えば、湿式エッチングを用いて層間絶縁層 220 に対して選択的に除去される。

これにより、層間絶縁層 220 の間で第 1 チャネル CH1 の側壁が一部露出する。

#### 【0098】

図 10e を参照すると、犠牲層 225 が除去された領域に一部のゲート電極 (231 ~ 238) を形成する。

20

ゲート電極 (231 ~ 238) は、犠牲層 225 が除去された領域に導電性物質を充填して形成する。

ゲート電極 (231 ~ 238) は、金属、多結晶シリコン、または金属シリサイド物質を含み得る。

本発明の一実施形態において、ゲート電極 (231 ~ 238) を形成する前に、ゲート誘電層 245 のうち、ゲート電極 (231 ~ 238) に沿ってベース層 201 上に水平に延長される領域がある場合、上記領域を先に形成する。

次に、図に示していない領域で、開口部 OP 内に絶縁物質を充填して分離絶縁層 210 を形成する。

#### 【0099】

30

図 10f を参照すると、上部ゲート電極 239、ストリング選択チャネル 240S、ストリング絶縁層 250S、第 1 接続部 262、第 1 コンタクトプラグ 260、共通ビットライン 270、及び接続パッド 275 を形成する。

上部ゲート電極 239 は、第 1 チャネル CH1 上に導電性物質、例えば、多結晶シリコン層を蒸着して形成する。

次に、上部セル領域絶縁層 285U 物質をさらに積層し、上部セル領域絶縁層 285U を貫通する第 1 貫通孔 TH1 を形成する。

#### 【0100】

第 1 貫通孔 TH1 内にストリング選択チャネル 240S 及びストリング絶縁層 250S を埋め込み、上端に導電性物質を充填することで第 1 接続部 262 を形成する。

40

次に、上部セル領域絶縁層 285U を貫通するように貫通孔を形成した後、導電性物質を充填して第 1 コンタクトプラグ 260 を形成し、第 1 接続部 262 及び第 1 コンタクトプラグ 260 上にそれぞれ共通ビットライン 270 及び接続パッド 275 を形成する。

共通ビットライン 270 及び接続パッド 275 は、導電性物質の蒸着、パターニング工程を介して形成し、上部セル領域絶縁層 285U の一部をパターニングし、導電性物質を蒸着することで形成する。

これにより、第 1 メモリセル領域 CELL1 が形成される。

#### 【0101】

図 10g を参照すると、第 2 メモリセル領域 CELL2 の第 2 接続部 264、上部ゲート電極 239、ストリング選択チャネル 240S、ストリング絶縁層 250S、第 2 チャ

50

ネルパッド 255L、ゲート電極 230、第2チャネルCH2、及び第3接続部 266 を形成する。

第1メモリセル領域 CELL1 と同様の方式で第2メモリセル領域 CELL2 を形成する。

まず、共通ビットライン 270 及び接続パッド 275 上に第2接続部 264 を形成する。

第2接続部 264 は、共通ビットライン 270 及び接続パッド 275 と共にパターニングされて形成され得る。

#### 【0102】

次に、第2接続部 264 上に下部セル領域絶縁層 285La の一部を形成した後、上部ゲート電極 239 を形成する。10

次に、下部セル領域絶縁層 285La の一部を再び形成した後、それを貫通する第2貫通孔 TH2 を形成する。

第2貫通孔 TH2 内にストリング選択チャネル 240S 及びストリング絶縁層 250S を埋め込み、上端に導電性物質を充填して第2チャネルパッド 255L を形成する。

#### 【0103】

次に、図 10b 及び図 10c を参照して上述したように、ゲート電極 230、第2チャネルCH2、及び第3接続部 266 を形成する。

また、ゲート電極 230 の外郭領域にゲート電極 (231 ~ 238) を貫通する貫通絶縁層 282 を形成する。

#### 【0104】

図 10h を参照すると、下部導電層 205L、第4接続部 268、第2コンタクトプラグ 261、及び第2接合パッド 280 を形成する。20

まず、第3接続部 266 上に下部導電層 205L を形成し、下部導電層 205L 上に第4接続部 268 を形成する。

また、上部セル領域絶縁層 (285La、285Lb) 及び貫通絶縁層 282 を貫通する貫通孔を形成し、導電性物質を充填して第2コンタクトプラグ 261 を形成する。

#### 【0105】

次に、第4接続部 268 及び第2コンタクトプラグ 261 上に第2接合パッド 280 を形成する。

第2接合パッド 280 は、例えば、導電性物質の蒸着及びパターニング工程を介して形成することができる。30

第2接合パッド 280 は、下部セル領域絶縁層 285Lb を介して上面が露出され得、第2半導体構造物 S2 の上面の一部をなす。

実施形態に応じて、第2接合パッド 280 の上面は、下部セル領域絶縁層 285Lb の上面よりも上部に突出した形態で形成することもできる。

本段階によって、最終的に第2半導体構造物 S2 が準備され得る。

#### 【0106】

図 10i を参照すると、第1半導体構造物 S1 上に第2半導体構造物 S2 を接合する。

まず、第1半導体構造物 S1 は、基板 101 上に回路素子 120 及び回路配線構造を形成することにより設けられる。40

#### 【0107】

回路ゲート誘電層 122 と回路ゲート電極 125 を基板 101 上に順次に形成する。

回路ゲート誘電層 122 と回路ゲート電極 125 は、ALD または CVD を用いて形成し得る。

回路ゲート誘電層 122 は、シリコン酸化物で形成され、回路ゲート電極 125 は、多結晶シリコンまたは金属シリサイド層の少なくとも 1 つで形成され得るが、これに限定されない。

その次に、回路ゲート誘電層 122 と回路ゲート電極 125 の両側壁にスペーサ層 124 及びソース / ドレイン領域 105 を形成する。

実施形態に応じて、スペーサ層 124 は、複数の層からなることもできる。50

次に、イオン注入工程を行ってソース／ドレイン領域 105 を形成する。

#### 【0108】

回路配線構造内の回路コンタクトプラグ 160 は、周辺領域絶縁層 190 を一部形成した後に一部をエッティングして除去し、導電性物質を充填することにより形成する。

回路配線ライン 170 は、例えば、導電性物質を蒸着した後、それをパターニングすることにより形成することができる。

周辺領域絶縁層 190 は、複数個の絶縁層からなり得る。

周辺領域絶縁層 190 は、回路配線構造を形成する各段階で一部が形成され、第 3 回路配線ライン 176 の上部に一部を形成することにより、最終的に回路素子 120 及び回路配線構造を覆うように形成される。

10

#### 【0109】

第 1 半導体構造物 S1 と第 2 半導体構造物 S2 は、第 1 接合パッド 180 と第 2 接合パッド 280 を加圧して接合することにより接続する。

第 2 半導体構造物 S2 は、第 2 接合パッド 280 が下部に向かうように上下逆の状態で第 1 半導体構造物 S1 上に接合され得る。

本図面では、理解を助けるために、第 2 半導体構造物 S2 が、図 10h に示した構造のミラーイメージの形態で接合される様子を示した。

第 1 半導体構造物 S1 と第 2 半導体構造物 S2 は、別途の接着層のような接着剤を介さずに直接接合 (direct bonding) される。

例えば、第 1 接合パッド 180 と第 2 接合パッド 280 は、上記加圧工程によって原子レベルでの結合を形成することができる。

20

実施形態に応じて、接合する前に、接合力を強化するために、第 1 半導体構造物 S1 の上面及び第 2 半導体構造物 S2 の下面に対して水素プラズマ処理のような表面処理工程がさらに行うことができる。

#### 【0110】

本発明の一実施形態において、下部セル領域絶縁層 285Lb は、下部に上述の接合誘電体層を含み、第 1 半導体構造物 S1 も同一の層を有する場合、第 1 及び第 2 接合パッド (180、280) の間の接合だけでなく、接合誘電層の間の誘電体接合によって接合力がより一層確保される。

#### 【0111】

図 10j を参照すると、第 1 及び第 2 半導体構造物 (S1、S2) の接合構造上において、第 2 半導体構造物 S2 のベース基板 SUB を除去し、パッド絶縁層 290 をパターニングするためのマスク層 298 を形成する。

30

ベース基板 SUB を除去することにより、半導体装置の厚さが最小になり、貫通ビアのような配線のための構造物の形成を省略することができる。

#### 【0112】

ベース基板 SUB は、上面から一部がグラインディング (grinding) 工程のような研磨工程によって除去され、残りの一部は、湿式エッティングのようなエッティング工程によって除去される。

これにより、パッド絶縁層 290 が上部に露出する。

40

湿式エッティング工程時に、パッド絶縁層 290 はエッティング停止層として用いることができる。

したがって、パッド絶縁層 290 は、ベース基板 SUB と異なる物質を含むことができ、特定のエッティング条件でエッティング選択性を有することができる物質で形成することができる。

第 2 半導体構造物 S2 のベース基板 SUB を除去することにより、半導体装置の総厚さが最小になる。

#### 【0113】

次に、マスク層 298 は、フォトリソグラフィ工程によって、図 4 のパッド領域 PAD を露出させるようにパターニングする。

50

マスク層 298 は、例えば、感光性樹脂層である。

次に、図 4 を共に参照すると、マスク層 298 から露出したパッド絶縁層 290 を除去して図 4 のように開口部を形成する。

これにより、下部の第 2 導電層 205b がパッド領域 PAD の上部に露出する。

パッド絶縁層 290 を除去する際に、第 2 導電層 205b はエッチング停止層として用いることができ、これによりエッチング工程が容易に行われる。

これにより、最終的に図 4 の半導体装置 100 が製造される。

#### 【0114】

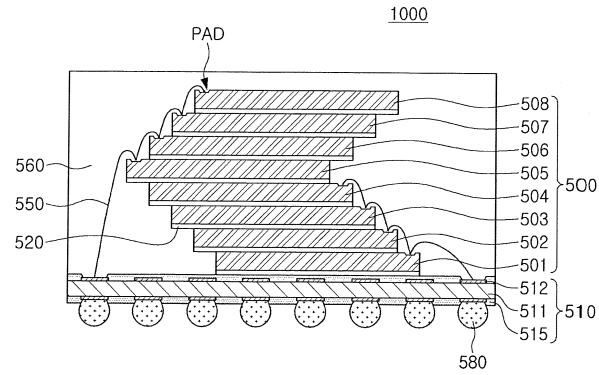

図 11 は、本発明の一実施形態による半導体パッケージの概略的な構成を示す断面図である。 10

図 11 を参照すると、半導体パッケージ 1000 は、パッケージ基板 510、パッケージ基板 510 上に積層されるメモリチップ 500 (501 ~ 508)、メモリチップ 500 を付着する接着層 520、メモリチップ 500 とパッケージ基板 510 との間を接続するワイヤ 550、メモリチップ 500 を封止する封止部 560、及びパッケージ基板 510 の下面に配置された接続端子 580 を含む。

#### 【0115】

パッケージ基板 510 は、本体部 511、本体部 511 の上下面に配置される導電性の基板パッド 512、及び基板パッド 512 を覆う絶縁性のパッシベーション層 515 を含む。

本体部 511 は、例えば、シリコン (Si)、ガラス (glass)、セラミック (ceramic)、またはプラスチック (plastic) を含み得る。 20

本体部 511 は、単一層であるか、またはその内部に配線パターンを含む多層構造を有することができる。

#### 【0116】

メモリチップ 500 は、接着層 520 を用いてパッケージ基板 510 及び下部のメモリチップ 500 上に積層される。

メモリチップ 500 は、図 4 ~ 図 9 を参照して上述した半導体装置 (100、100a、100b、100c、100d) を含むことができる。

メモリチップ 500 は、同一の種類のメモリチップからなるか、または他の種類のメモリチップを含むことができる。 30

メモリチップ 500 が他の種類のメモリチップを含む場合、上述の半導体装置 (100、100a、100b、100c、100d) 以外に、DRAM、SRAM、PRAM、ReRAM、FeRAM、またはMRAM を含むことができる。

#### 【0117】

メモリチップ 500 は、互いに同一または異なる大きさを有することができ、メモリチップ 500 の個数は、図に示したものに限定されない。

メモリチップ 500 は、上面にパッド領域 PAD が位置し、パッド領域 PAD は、メモリチップ 500 の端に隣接して位置するが、これに限定されない。

例えば、3D プリンティングを用いてワイヤ 550 に該当する信号伝達媒体を形成する場合、パッド領域 PAD は、端に位置しないことも可能である。 40

メモリチップ 500 は、パッド領域 PAD が露出するように順次にオフセットされて積層される。

#### 【0118】

ワイヤ 550 は、上部のメモリチップ 500 と下部のメモリチップ 500 を電気的に接続するか、またはメモリチップ 500 の少なくとも一部をパッケージ基板 510 の基板パッド 512 と電気的に接続する。

但し、ワイヤ 550 は、信号伝達構造物の一例であるため、実施形態に応じて、様々な形態の信号伝達媒体に変更することができる。

#### 【0119】

封止部 560 は、メモリチップ 500、ワイヤ 550、及びパッケージ基板 510 の上

50

面を覆うように配置され、メモリチップ 500 を保護する役割を果たす。

封止部 560 は、例えば、シリコン (silicone) 系物質、熱硬化性物質、熱可塑性物質、UV 处理物質などからなることができる。

封止部 560 は、樹脂のようなポリマーで形成され得、例えば、EMC (Epoxy Molding Compound) で形成される。

#### 【0120】

接続端子 580 は、半導体パッケージ 1000 を半導体パッケージ 1000 が実装される電子機器のマザーボードなどと接続する。

接続端子 580 は、導電性物質、例えば、半田 (solder)、錫 (Sn)、銀 (Ag)、銅 (Cu) 及びアルミニウム (Al) の少なくとも 1 つを含み得る。

実施形態において、接続端子 580 は、ランド (land)、ボール (ball)、ピン (pin) など様々な形態に変更することができる。

#### 【0121】

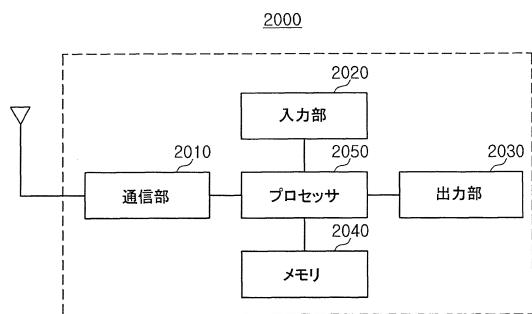

図 12 は、本発明の一実施形態による半導体装置を含む電子機器の概略構成を示すプロック図である。

図 12 を参照すると、本発明の一実施形態による電子機器 2000 は、通信部 2010、入力部 2020、出力部 2030、メモリ 2040、及びプロセッサ 2050 を含む。

#### 【0122】

通信部 2010 は、有線 / 無線通信モジュールを含むことができ、無線インターネットモジュール、近距離通信モジュール、GPS モジュール、移動通信モジュールなども含むことができる。

通信部 2010 に含まれる有線 / 無線通信モジュールは、様々な通信規格によって外部の通信網と接続されてデータを送受信する。

入力部 2020 は、ユーザーが電子機器 2000 の動作を制御するために提供されるモジュールであり、機械式スイッチ、タッチスクリーン、音声認識モジュールなどを含むことができ、その他にも、ユーザーがデータを入力することができる様々なセンサーモジュールをさらに含むこともできる。

#### 【0123】

出力部 2030 は、電子機器 2000 で処理される情報を音声または映像の形態で出力し、メモリ 2040 は、プロセッサ 2050 を処理及び制御するためのプログラムや、またはデータなどを記憶する。

メモリ 2040 は、図 4 ~ 図 9 を参照して上述したような様々な実施形態による半導体装置を 1 つ以上含むことができ、電子機器 2000 に内蔵されるか、または別途のインターフェースを介してプロセッサ 2050 と通信する。

プロセッサ 2050 は、電子機器 2000 に含まれる各部の動作を制御することができる。

プロセッサ 2050 は、音声通話、ビデオ通話、データ通信などに関する制御及び処理を行うか、またはマルチメディアを再生及び管理するための制御及び処理を行うこともできる。

また、プロセッサ 2050 は、入力部 2020 を介してユーザーから伝達される入力を処理し、その結果を出力部 2030 を介して出力すること、電子機器 2000 の動作を制御する上で必要なデータをメモリ 2040 に記憶すること、メモリ 2040 から引き出すことなどを行うことができる。

#### 【0124】

尚、本発明は、上述の実施形態に限られるものではない。本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

#### 【符号の説明】

#### 【0125】

10、10A、100、100a ~ d 半導体装置

20、20A メモリセルアレイ

10

20

30

40

50

|                                           |                       |    |

|-------------------------------------------|-----------------------|----|

| 3 0                                       | 周辺回路                  |    |

| 3 2                                       | ローデコーダ                |    |

| 3 4                                       | ページバッファ               |    |

| 3 5                                       | 入出力 ( I / O ) バッファ    |    |

| 3 6                                       | 制御ロジック                |    |

| 3 7                                       | 電圧発生器                 |    |

| 1 0 1                                     | 基板                    |    |

| 1 0 5                                     | ソース / ドレイン領域          |    |

| 1 2 0                                     | 回路素子                  |    |

| 1 2 2                                     | 回路ゲート誘電層              | 10 |

| 1 2 4                                     | スペーサ層                 |    |

| 1 2 5                                     | 回路ゲート電極               |    |

| 1 6 0                                     | 回路コンタクトプラグ            |    |

| 1 6 2、1 6 4、1 6 6                         | 第 1 ~ 第 3 回路コンタクトプラグ  |    |

| 1 7 0                                     | 回路配線ライン               |    |

| 1 7 2、1 7 4、1 7 6                         | 第 1 ~ 第 3 回路配線ライン     |    |

| 1 8 0                                     | ( 第 1 ) 接合パッド         |    |

| 1 9 0                                     | 周辺領域絶縁層               |    |

| 2 0 1                                     | ベース層                  |    |

| 2 0 5 a、2 0 5 b                           | ( 第 1 及、第 2 ) 導電層     | 20 |

| 2 0 5 L                                   | 下部導電層                 |    |

| 2 0 5 U                                   | 上部導電層                 |    |

| 2 1 0                                     | 分離絶縁層                 |    |

| 2 2 0                                     | 層間絶縁層                 |    |

| 2 3 0 ( 2 3 1 ~ 2 3 9 )                   | ( 上部、下部 ) ゲート電極       |    |

| 2 4 0                                     | チャネル領域                |    |

| 2 4 0 S                                   | ストリング選択チャネル ( 領域 )    |    |

| 2 4 5                                     | ゲート誘電層                |    |

| 2 5 0                                     | チャネル絶縁層               |    |

| 2 5 0 S                                   | ストリング絶縁層              | 30 |

| 2 5 5 U、2 5 5 L                           | ( 第 1 、第 2 ) チャネルパッド  |    |

| 2 5 6                                     | 貫通部                   |    |

| 2 6 0、2 6 0 a                             | 第 1 コンタクトプラグ          |    |

| 2 6 1、2 6 1 a                             | 第 2 コンタクトプラグ          |    |

| 2 6 2 ( a )、2 6 4 ( a )、2 6 6 ( a )、2 6 8 | ( 第 1 ~ 第 4 ) 接続部     |    |

| 2 7 0                                     | 共通ビットライン              |    |

| 2 7 5、2 7 5 a                             | 接続パッド                 |    |

| 2 8 0                                     | 第 2 接合パッド             |    |

| 2 8 2                                     | 貫通絶縁層                 |    |

| 2 8 5 U                                   | 上部セル領域絶縁層             | 40 |

| 2 8 5 L a、2 8 5 L b                       | 下部セル領域絶縁層             |    |

| 2 9 0                                     | パッド絶縁層                |    |

| 2 9 5、2 9 5 a                             | 接続層                   |    |

| 2 9 8                                     | マスク層                  |    |

| M C A 1、M C A 2                           | ( 第 1 、第 2 ) メモリセルアレイ |    |

| P A D                                     | パッド領域                 |    |

| P E R I                                   | 周辺回路 ( 領域 )           |    |

| C H 1、C H 2                               | ( 第 1 、第 2 ) チャネル     |    |

| C E L L 1、C E L L 2                       | メモリセル領域               |    |

| S 1、S 2                                   | ( 第 1 、第 2 ) 半導体構造物   | 50 |

【図面】

【図 1】

【図 2】

10

20

30

40

【図 3】

【図 4】

【図 5 a】

A

【図 5 b】

A

10

20

【図 6 a】

【図 6 b】

30

40

50

【図 7 a】

【図 7 b】

10

【図 8 a】

【図 8 b】

20

30

40

50

【図 8 c】

【図 9】

【図 10 a】

【図 10 b】

【図 10 c】

【図 10 d】

10

【図 10 e】

【図 10 f】

20

30

40

50

【図 10 g】

【図 10 h】

10

【図 10 i】

【図 10 j】

20

30

40

50

【図 1 1】

【図 1 2】

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

|         | F I              |         |       |

|---------|------------------|---------|-------|

| H 1 0 B | 41/40 (2023.01)  | H 0 1 L | 25/08 |

| H 1 0 B | 43/40 (2023.01)  | H 0 1 L | 21/88 |

| H 0 1 L | 25/07 (2006.01)  | H 0 1 L | 21/88 |

| H 0 1 L | 25/065 (2023.01) |         | T     |

| H 0 1 L | 25/18 (2023.01)  |         |       |

| H 0 1 L | 21/3205(2006.01) |         |       |

| H 0 1 L | 21/768(2006.01)  |         |       |

| H 0 1 L | 23/522(2006.01)  |         |       |

(72)発明者 朴 玄 瞳

大韓民国 京畿道 水原市 靈通区 三星路 129

(72)発明者 金 容 錫

大韓民国 京畿道 水原市 靈通区 三星路 129

(72)発明者 李 ギョン 契

大韓民国 京畿道 水原市 靈通区 三星路 129

(72)発明者 林 澄 熙

大韓民国 京畿道 水原市 靈通区 三星路 129

(72)発明者 韓 智 勳

大韓民国 京畿道 水原市 靈通区 三星路 129

審査官 脇水 佳弘

(56)参考文献 特開2016-062901 (JP, A)

特開2010-118659 (JP, A)

米国特許第09502471 (US, B1)

特開2018-148071 (JP, A)

米国特許第09691782 (US, B1)

特開2003-282573 (JP, A)

中国特許出願公開第107658315 (CN, A)

特開2011-187794 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H 1 0 B 4 1 / 0 0

H 1 0 B 4 3 / 0 0

H 0 1 L 2 1 / 3 3 6

H 0 1 L 2 5 / 0 7

H 0 1 L 2 1 / 3 2 0 5