(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-181523

(P2005-181523A)

(43) 公開日 平成17年7月7日(2005.7.7)

(51) Int.CI.<sup>7</sup>**G03F 1/08****G06F 17/50****H01L 21/027****H01L 21/82**

F 1

G03F 1/08

A

テーマコード(参考)

2 H095

G06F 17/50

5 B046

H01L 21/30

5 F064

H01L 21/82

C

審査請求 未請求 請求項の数 9 O L (全 17 頁)

(21) 出願番号

特願2003-419600(P2003-419600)

(22) 出願日

平成15年12月17日(2003.12.17)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(71) 出願人 000221199

東芝マイクロエレクトロニクス株式会社

神奈川県川崎市川崎区駅前本町25番地1

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100108855

弁理士 蔵田 昌俊

最終頁に続く

(54) 【発明の名称】設計パターン補正方法、マスクパターン作成方法、半導体装置の製造方法、設計パターン補正システム、及び設計パターン補正プログラム

## (57) 【要約】

【課題】 従来よりも小さいチップサイズのパターンで、仕上がり形状が保証された設計パターンを得る。

【解決手段】 半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して設計パターンを補正する設計パターン補正方法であって、第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状を算出し、第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出し、第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出し、第3の平面形状から得られる評価量が所定値を満たすか否かを判定し、評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して設計パターンを補正する方法であって、

第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する工程と、

第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する工程と、

第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する工程と、

第3の平面形状から得られる評価量が所定値を満たすか否かを判定する工程と、

前記判定工程により前記評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する工程と、

を含むことを特徴とする設計パターン補正方法。

**【請求項 2】**

第1及び第2の平面形状のうち、少なくとも一方は対応する設計パターンに対して光近接効果補正を含むリサイズ処理を行った後のマスクパターンから算出されることを特徴とする請求項1記載の設計パターン補正方法。

**【請求項 3】**

前記ブーリアン演算処理を、第1及び第2の平面形状の少なくとも一方をリサイズ若しくは移動させた後に行うことの特徴とする請求項1記載の設計パターン補正方法。

**【請求項 4】**

第1又は第2の平面形状は、露光装置の露光波長、レンズ開口数、照明形状、マスク寸法、露光量、焦点位置、収差、合わせずれ量、レジスト拡散長のうち少なくとも1つを含むプロセス条件下でそれぞれ算出されることを特徴とする請求項1記載の設計パターン補正方法。

**【請求項 5】**

前記各工程を、第3の平面形状から得られる評価量が前記所定値を満たすまで繰り返し行うことの特徴とする請求項1記載の設計パターン補正方法。

**【請求項 6】**

半導体集積回路の複数レイヤー間でのプロセスマージンを考慮したマスクパターン作成方法であって、

第1のレイヤーの第1の設計パターンに対して少なくとも1回のリサイズ処理を含む第1のマスクパターンを作成する工程と、

第2のレイヤーの第2の設計パターンに対して少なくとも1回のリサイズ処理を含む第2のマスクパターンを作成する工程と、

第1のマスクパターンから第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する工程と、

第2のマスクパターンから第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する工程と、

第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する工程と、

第3の平面形状から得られる評価量が所定値を満たすか否かを判定する工程と、

前記判定工程により前記評価量が所定値を満たさないと判定された場合に、第1及び第2のマスクパターンの少なくとも一方を修正する工程と、

を含むことを特徴とするマスクパターン作成方法。

**【請求項 7】**

半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して設計パターンを補正するシステムであって、

第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状

10

20

30

40

50

を算出する手段と、

第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する手段と、

第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する手段と、

第3の平面形状から得られる評価量が所定値を満たすか否かを判定する手段と、

前記判定手段により前記評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する手段と、

を具備してなることを特徴とする設計パターン補正システム。

#### 【請求項8】

請求項1～6の何れかに記載の設計パターン補正方法を用いて補正された設計パターンを基に半導体基板上に集積回路パターンを形成することを特徴とする半導体装置の製造方法。

#### 【請求項9】

半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して、コンピュータ制御の下に設計パターンを補正するための設計パターン補正プログラムであって、

第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する手順と、

第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する手順と、

第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する手順と、

第3の平面形状から得られる評価量が所定値を満たすか否かを判定する手順と、

前記判定手順により前記評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する手順と、

をコンピュータに実行させるためのコンピュータ読み取り可能な設計パターン補正プログラム。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体集積回路の設計パターンを修正するための設計パターン補正方法と設計パターン補正システム、該方法を用いて補正された設計パターンを基に半導体基板上に集積回路パターンを形成する半導体装置の製造方法、更に該方法をコンピュータにより実行するための設計パターン補正プログラムに関する。また本発明は、半導体集積回路のマスクパターンを作成するためのマスクパターン作成方法に関する。

#### 【背景技術】

#### 【0002】

近年の半導体製造技術の進歩は非常に目覚しく、最小加工寸法0.13μmサイズの半導体装置が量産されている。このような微細化は、マスクプロセス技術、光リソグラフィ技術、及びエッチング技術等の微細パターン形成技術の飛躍的な進歩により実現されている。

#### 【0003】

パターンサイズが十分大きい時代には、ウェハ上に形成したいLSIパターンの平面形状をそのまま設計パターンとして描き、その設計パターンに忠実なマスクパターンを作成し、そのマスクパターンを投影光学系によってウェハ上に転写し、下地をエッチングすることによってほぼ設計パターン通りのパターンがウェハ上に形成できた。しかし、パターンの微細化が進むにつれて、各プロセスでパターンを忠実に形成することが困難になってきており、最終仕上り寸法が設計パターン通りにならない問題が生じてきた。これらの問題を解決するために、各プロセスでの変換差を考慮して、最終仕上り寸法が設計パターン寸法と等しくなるように設計パターンと異なるマスクパターンを作成する、いわゆるマスク

10

20

30

40

50

クデータ処理が非常に重要になっている。

#### 【0004】

マスクデータ処理には、図形演算処理やデザインルールチェック（D.R.C.）等を用いてマスクパターンを変化させるMDP処理、光近接効果（OPE）を補正するためのOPC処理等があり、これらの処理を行うことによって最終仕上り寸法が所望になるようマスクパターンを適切に補正する。近年では、デバイスパターンの微細化に伴いリソグラフィプロセスにおけるk1値（ $k_1 = W / (NA / \dots)$ 、W：設計パターンの寸法、

NA：露光装置の露光波長、NA：露光装置に使用されているレンズの開口数）が益々低減し、その結果、OPEがより増大する傾向にある。このため、OPC処理の負荷が非常に大きくなっている。

10

#### 【0005】

このようなOPC処理の高精度化を達成するために、OPEを正確に予測できる光強度シミュレータを搭載して、マスクパターン毎に適切な補正值を計算できるモデルベースOPC手法が主流となっている。さらに、複雑なモデルベースOPCを行ったマスクの検証を行うために、リソグラフィシミュレーションを使ったモデルベースOPC検証技術が非常に重要なっている。

#### 【0006】

しかしながら、単層（單一レイヤー）に対してモデルベースOPC検証技術を適用し、リソグラフィマージンの小さい危険パターンを検出する技術は提案されているものの（例えば、特許文献1,2参照）、これらの技術では十分な検出精度は得られていない。さらに、複数の層間を見て、リソグラフィマージンがあるか否かを判定する技術は未だ開発されていないのが現状である。

20

【特許文献1】米国特許第6470489号

【特許文献2】米国特許第6415421号

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

このように従来、モデルベースOPC検証技術を適用しても、複数の層間でリソグラフィマージンがあるか否かを判定することはできず、このために十分な仕上がり形状を保証することは困難であった。また、十分な仕上がり形状を保証しようとすると、チップサイズの増大を招く問題があった。

30

#### 【0008】

本発明は、上記事情を考慮して成されたもので、その目的とするところは、従来よりも小さいチップサイズのパターンで、仕上がり形状が保証された設計パターンを得ることのできる設計パターン補正方法及び設計パターン補正システムを提供することにある。さらに、本発明の他の目的は、従来よりも小さいチップサイズのパターンで、仕上がり形状が保証されたマスクパターンを得ることのできるマスクパターン作成方法を提供することにある。

#### 【0009】

また、本発明の別の目的は、上記の設計パターン補正方法を用いた半導体装置の製造方法を提供することにある。また、本発明の更に別の目的は、上記の設計パターン補正方法をコンピュータに実行させるための設計パターン補正プログラムを提供することにある。

40

#### 【課題を解決するための手段】

#### 【0010】

上記課題を解決するために本発明は、次のような構成を採用している。

#### 【0011】

即ち、本発明の一態様は、半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して設計パターンを補正する方法であって、第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する工程と、第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する工程と、第1の

50

平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する工程と、第3の平面形状から得られる評価量が所定値を満たすか否かを判定する工程と、前記判定工程により前記評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する工程と、を含むことを特徴とする。

#### 【0012】

また、本発明の別の一態様は、半導体集積回路の複数レイヤー間でのプロセスマージンを考慮したマスクパターン作成方法であって、第1のレイヤーの第1の設計パターンに対して少なくとも1回のリサイズ処理を含む第1のマスクパターンを作成する工程と、第2のレイヤーの第2の設計パターンに対して少なくとも1回のリサイズ処理を含む第2のマスクパターンを作成する工程と、第1のマスクパターンから第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する工程と、第2のマスクパターンから第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する工程と、第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する工程と、第3の平面形状から得られる評価量が所定値を満たすか否かを判定する工程と、前記判定工程により前記評価量が所定値を満たさないと判定された場合に、第1及び第2のマスクパターンの少なくとも一方を修正する工程と、を含むことを特徴とする。10

#### 【0013】

また、本発明の別の一態様は、半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して設計パターンを補正するシステムであって、第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する手段と、第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する手段と、第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する手段と、第3の平面形状から得られる評価量が所定値を満たすか否かを判定する手段と、前記判定手段により前記評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する手段と、を具備してなることを特徴とする設計パターン補正システム。20

#### 【0014】

また、本発明の別の一態様は、半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して、コンピュータ制御の下に設計パターンを補正するためのコンピュータ読み取り可能な設計パターン補正プログラムであって、第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する手順と、第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する手順と、第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する手順と、第3の平面形状から得られる評価量が所定値を満たすか否かを判定する手順と、前記判定手順により前記評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する手順と、をコンピュータに実行させることを特徴とする。30

#### 【発明の効果】

#### 【0015】

本発明によれば、個々のパターン毎に層間での仕上がり形状を比較し、その仕上がり結果から得られる評価量に基づいて、設計パターンやマスクパターンなどに適切に修正を加えることにより、従来よりも小さいチップサイズのパターンで、かつ仕上がり形状が保証された設計パターン又はマスクパターンを自動で得ることが可能となる。40

#### 【発明を実施するための最良の形態】

#### 【0016】

以下、本発明の詳細を図示の実施形態によって説明する。

#### 【0017】

(第1の実施形態)

図1に、単一レイヤーに対してOPC検証を行った結果を示す。これは、メタル配線(M1)での一例であり、設計パターン(ターゲットパターン)のエッジからのずれ量を黒50

塗りで示している。図2に、本実施形態による複数レイヤーを考慮したOPC検証手法を示す。これは、第1の設計パターンに基づく第1のレイヤーとしてのM1と第2の設計パターンに基づく第2のレイヤーとしてのコンタクトホール(CS)の一例であり、プロセス条件は共に露光量、焦点位置共にベスト条件での結果である。

#### 【0018】

M1とCSとは、露光時に重ね合わせずれ(オーバーレイ誤差)が生じるため、少なくともこの誤差を考慮していない図2の状態では、M1仕上がり平面形状とCS仕上がり平面形状とのAND領域が一定面積、若しくは設計パターン同士のAND領域の面積を1としたときの面積比(以後、この面積比も含めて面積と総称する)以上確保されていることが必須である。

10

#### 【0019】

ところが、実際には、M1-CS間に重ね合わせずれが発生するため、図3に示すように、M1仕上がり平面形状(第1の平面形状)とCS仕上がり平面形状(第2の平面形状)との位置関係がずれてしまう。この場合でも、確実にAND領域が一定面積以上確保されていることが必須であり、面積が確保されないと設計パターン(デザインルール)、若しくはマスクパターンの修正を行う必要がある。これらのパターン修正は、AND領域の面積が増加するように修正が行われる。

#### 【0020】

具体的な修正方法としては、メタル配線M1とコンタクトホールCSとのAND領域を十分に確保する場合には、

20

- (1) メタル配線の幅を大きくする

- (2) コンタクトホールの穴径を大きくする

などの方法がある。

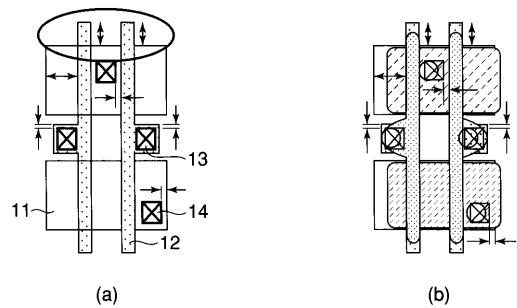

#### 【0021】

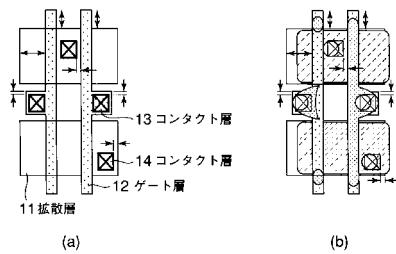

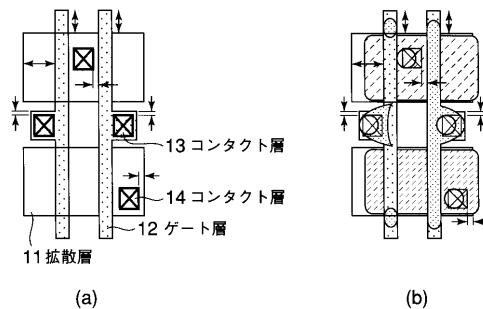

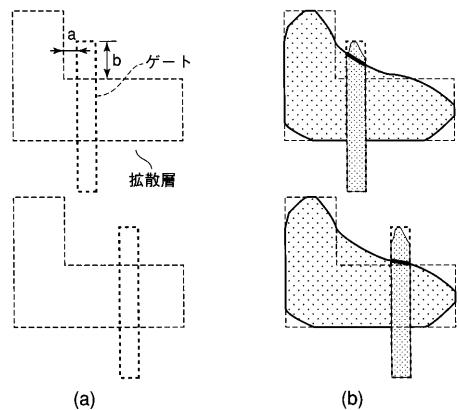

但し、(2)の方法でコンタクトホールの穴径を大きくする場合には、そのコンタクトホールがどこのレイヤー(層)に接続されているかを考慮して穴径を大きくする必要がある。例えば、図4(a)(b)に示すように、メタル層とゲート層とを接続するコンタクトホールや、メタル層と拡散層(ソース・ドレイン)と接続するコンタクトの場合には、コンタクトホール穴径を広げることにより、コンタクトを形成したい所望位置より広いコンタクトホールが形成されることになる。そのため、ゲート層からコンタクトがはみ出してしまうことや、拡散層からコンタクトがはみ出してしまうという問題が起こる場合がある。

30

#### 【0022】

なお、図4において、(a)は設計レイアウト、(b)はウェハ上の仕上がり平面形状であり、図中の11は拡散層、12はゲート層、13はゲート層12と接続するコンタクト層、14は拡散層11と接続するコンタクト層を示している。

40

#### 【0023】

従って、(2)の方法でコンタクトホール穴径を大きくしてメタル層とのAND領域を十分に確保する際には、コンタクト-ゲート間、コンタクト-拡散層間の設計パターン上での間隔、若しくは仕上がりパターン平面形状間の間隔を考慮し、さらにそれらの層間での重ね合わせずれがどの程度あるのかを見込んだ上で、どれくらいコンタクトホール穴径を大きくするかを見積もある必要がある。

#### 【0024】

さらに、コンタクトホールがメタルM1(1層目のメタル配線)-メタルM2(2層目のメタル配線)間を接続するコンタクトホールである(今後このようなコンタクトホールのことをビアと総称する)場合にも、上記と同様の注意が必要である。例えば、メタルM1と第1のビアV1とのAND領域を十分確保するためにビアV1を大きくすると、ビアV1とメタルM2との接続面積も広がってしまう。仮に、メタルM2の近傍に別の第2のビアV2が配置されているとすると、ビアV1を大きくすることによりビアV2との間隔が小さくなってしまい、ビアV1とビアV2とが接触してしまう可能性がある。

50

## 【0025】

従って、ビアV1を大きくする場合には、

1. 近傍に別のビアV2が存在するかどうか

2. ビアV2はビアV1に対してどういう方向に存在するのか

3. ビアV2とビアV1とは接触してもよいのかどうか（同電位に落ちるビアであれば

接触しても問題はない）

を判断し、その結果に基づいて、ビアV1を大きくするための方向と大きさとを決める必要がある。

## 【0026】

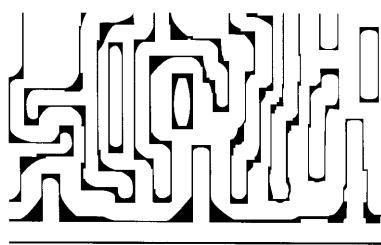

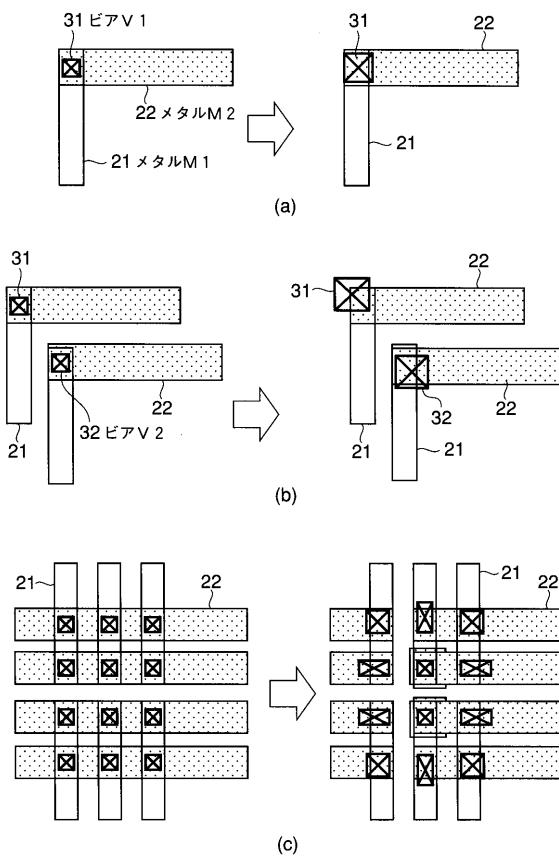

図5に一例を示すが、(a)は近傍にビアV2が存在しない場合、(b)は片方の近傍にビアV2が存在する場合、(c)は近傍にビアV2がある場合との混在する場合であり、図中の21は第1のメタル配線(M1)、22は第2のメタル配線(M2)、31は第1のビア(V1)、32は第2のビア(V2)を示している。

## 【0027】

図5(a)のように、近傍にビアV2が存在しない場合、ビア31を単純に大きくすることが可能である。また、図5(b)のように、片方の近傍にビア32が存在する場合、ビア32との接触を避けるために、ビア32の存在する方向と反対方向にだけビア31を大きくすることができます。また、図5(c)のように混在する場合、ビアを広げられるものは広げ、広げられないものは、メタルM1, M2の幅を太くして対応することが必要となる。図5(c)では、近傍に別のビアがある場合は、メタル先端部を太くし(中心の2個)、近傍に別のビアがない場合はビアを大きくしている(周辺の10個)。

## 【0028】

通常、メタル層は人手で配線されるよりもむしろ自動配置配線(Place & Routing: P&Rと呼ぶ)ツールを用いて、メタル配線及びビアの配置が行われることが多い。従って、ビアやメタルのウェハ上の仕上がり平面形状を算出し、その算出結果に基づいて、上記1-3で示したことを判定し、その判定に基づいてメタル若しくはビアの少なくとも一方を大きくすることにより、メタル-ビアのAND領域を十分に確保することを保証するP&Rツールによって実現することも可能である。

## 【0029】

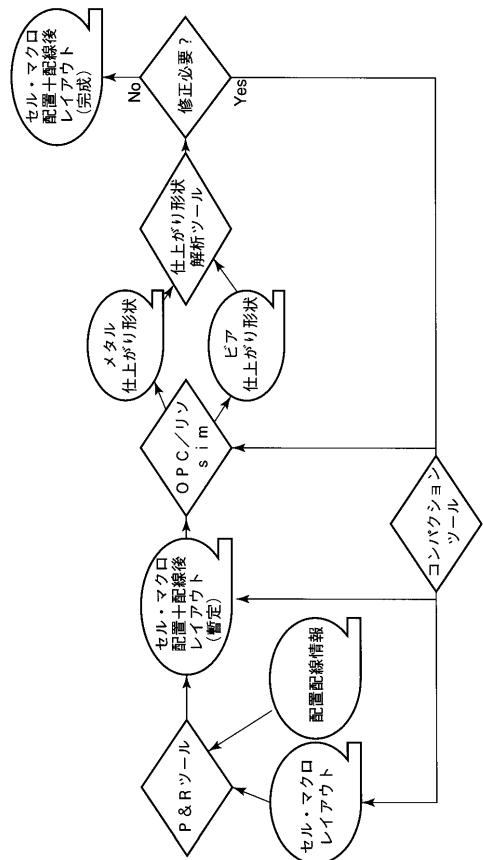

従来のP&Rツールでは、スタンダードセルやマクロセルのレイアウトをどこに配置し、レイアウト間をどのように接続させるのかを記載した配置配線情報に基づいて、配線された後の配線長ができるだけ短くなるように配線を行うというのが基本であった。これらのツールの機能に、メタルとビアとの仕上がり形状のAND領域を調べ、そのAND領域が十分に確保できるように、セル、マクロのレイアウトや、配置後のレイアウト形状を修正するような機能を搭載し、図6に示すようなシステムを作成した。このレイアウト形状を修正する機能としては、予め与えられたレイアウト作成ルールに従ってレイアウトを作成、修正可能なコンパクションツールなどが有効である。

## 【0030】

このシステムを用いれば、従来、自動配置配線工程で保証しきれなかったメタルとビアとのウェハ上の接続を保証できるように設計レイアウト、及びOPCを考慮したマスクパターンを自動で作成することができるので、ウェハ上の歩留まり向上に有効である。即ち、従来よりも小さいチップサイズのパターンで、仕上がり形状が保証された設計パターンを得ることが可能となる。なお、ここで示したP&Rツールやコンパクションツールなどを利用した設計レイアウト作成フローは一例であり、これらのツールを利用しなくても、メタルとビアのウェハ上の仕上がり形状に基づいて設計レイアウトを自動で修正することができるものであればよい。

## 【0031】

仕上がりパターンがNGの場合には、幾つかの要因が考えられ、その要因によって設計パターンの修正を行う場合と、マスクパターンの修正を行う場合とを場合分けする必要が

10

20

30

40

50

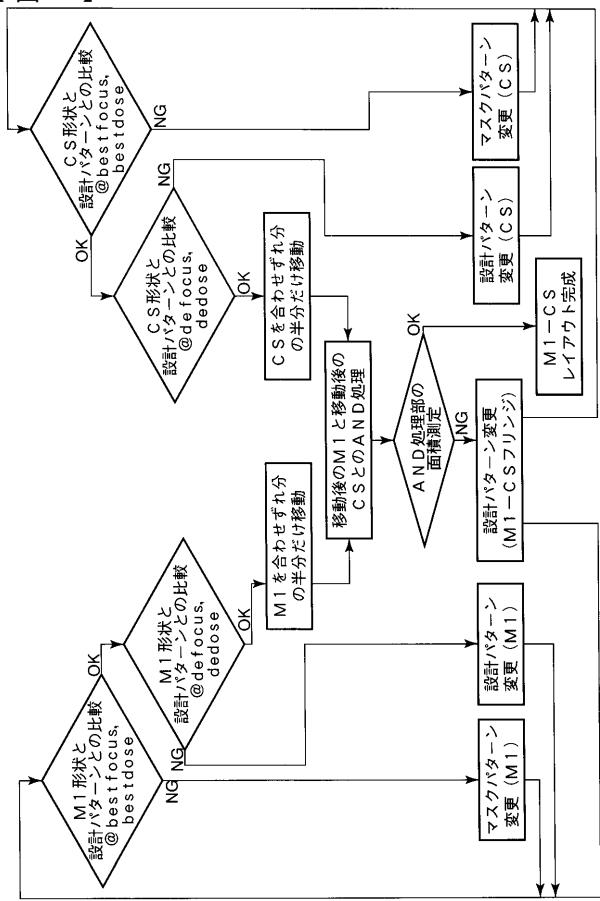

ある。M1とCSとの合わせを想定した場合では、図7に示す流れのようになる。

#### 【0032】

図7では、まず最初に、メタル層とコンタクト層をそれぞれ単層で評価する工程が入っている。単層での評価によりメタル配線やコンタクト層でそれぞれプロセスマージンが確保できるか、できないかが判定される。このときの具体的な処理フローは、特開2002-26126号公報、特開2003-303742号公報、に記載されている。

#### 【0033】

単層での評価により、まずはそれぞれの層でプロセスマージンの小さいパターンがなくなるように設計レイアウト、マスクパターンを作成・修正した後、メタル層とコンタクト層との仕上がり形状を考慮した危険パターンの抽出を行う。その結果をもとに、さらにメタル層、コンタクト層の設計レイアウト修正を行うことで、メタル層、コンタクト層のそれぞれの層での仕上がりと、層間での仕上がりとを共に保証することができた。

#### 【0034】

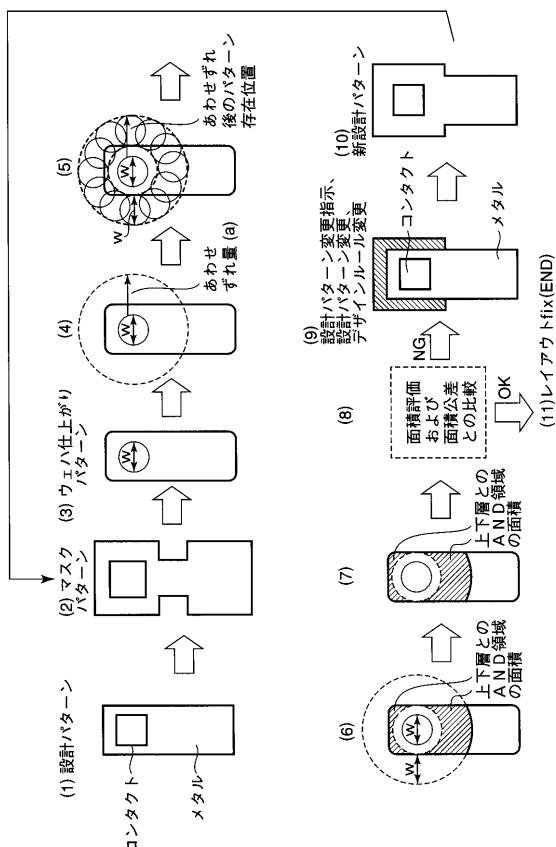

図7のフローで示した処理の流れの具体的な一例を、図8を参照して説明する。

#### 【0035】

与えられたメタルとコンタクトとの設計パターン形状(1)から、OPCを含むリサイズ処理、ブーリアン演算処理などによりマスクパターンをそれぞれ作成し(2)、それぞれのマスクパターンからウェハ上の仕上がり平面形状をそれぞれ予測する(3)。仮にコンタクトとメタルとの合わせずれ量がaだとし、注目するコンタクトの仕上がり寸法がwであるとすると、コンタクトがメタルと合わせずれを起こした場合に、コンタクトは(3)で予測された位置よりaだけずれた位置に形成される可能性がある(4)(5)。

#### 【0036】

ここで、(5)のリング形状のパターン(リングパターンと呼ぶ)が、合わせずれをaだけ起こした場合にコンタクトが存在する領域を示している。問題は、このリングパターンが、メタルの仕上がり形状とどれくらいの重なり領域(第3の平面形状)を持っているかである。

#### 【0037】

重なり領域が小さいということは、コンタクトとメタルとの導電性を確保するのが難しくなり、歩留まり劣化を招く可能性が高い。逆に十分に重なりがあれば、確実な導電性を確保することができる。重なり領域は、メタル仕上がり平面形状とのAND処理によって取ることができる(6)。そして、(6)で取られた面積は、一般的なデザインルールチェック(DRCと呼ぶ)ツールで算出することが可能である(7)。

#### 【0038】

次に、(7)で確保された面積が十分であるかを、面積公差として予め与え、公差よりも小さい場合には、設計パターンの変更が必要となるため、その変更指針、若しくはDR値を算出する必要がある(8)。その指針に従った新設計レイアウトを作成し(9)(10)、再度(2)以降を繰り返し行う。そして、最終的に(7)で確保された面積が面積公差以上になれば、レイアウトが完成する(11)。

#### 【0039】

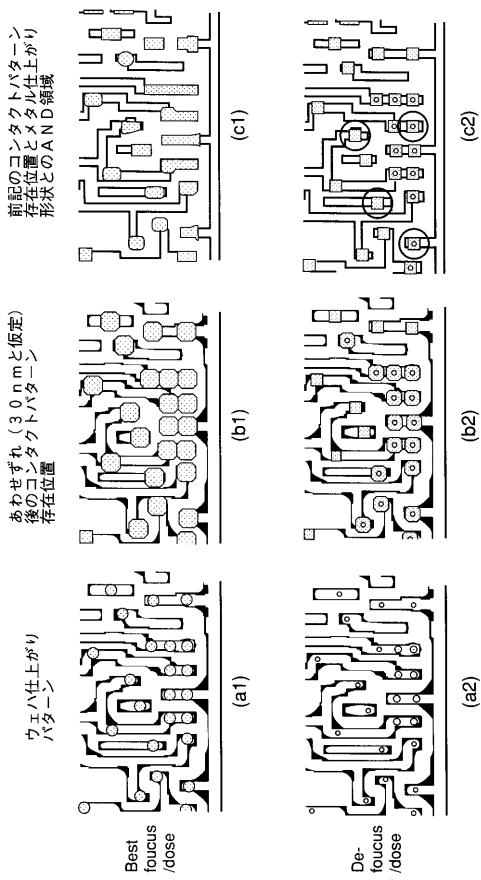

図8に示す複数層レイヤー検証の流れを、実際のレイアウトで行った一例を、図9に示す。

#### 【0040】

図9の上段(a1)(b1)(c1)は、コンタクトがベストフォーカス、ベスト露光量条件での結果であり、下段(a2)(b2)(c2)は、露光量、フォーカス共にベストから少しずれた位置での結果である(メタル層はベストフォーカス、ベスト露光量のみを想定)。なお、今回は、単純化のための露光量とフォーカスのみを変動させた例を示したが、仕上がり形状に対して影響を及ぼす全てのプロセスパラメータを変動させることができる。パラメータとしては、フォーカス、露光量の他に、露光装置の露光波長、レンズの開口数、レンズの収差、露光装置の照明形状、及び照明の光強度分布、レンズの光透過率、エッティング変換差等である。

## 【0041】

図9の(ai)(bi)(ci)がそれぞれ、図8の(3)(5)(7)に対応しており、図8の(7)で算出された面積をDRCツールで求め、その面積が公差を満たさなかったものが、黒丸で囲まれたパターンである。この黒丸で囲まれたパターンの設計パターンのみを修正し、再度同様の流れで評価した結果、チップサイズを増やすことなく、危険パターンを回避することができた。

## 【0042】

このように本実施形態によれば、第1のレイヤーの仕上がり平面形状である第1の平面形状と第2のレイヤーの仕上がり平面形状である第2の平面形状を算出し、第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出し、第3の平面形状から得られる評価量が所定値を満たすか否かを判定し、評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正することにより、従来よりも小さいチップサイズのパターンで、仕上がり形状が保証された設計パターンを得ることができる。

## 【0043】

即ち、複数層間の仕上がり平面形状に基づいて、マージンが十分にあるかどうかを検証することにより、従来では非常に困難であった個別パターン毎のレイアウト最適化が可能になり、非常に小さいチップを作成することが可能となる。従って、今後の半導体集積回路の微細加工にも十分対応することができる。

## 【0044】

## (第2の実施形態)

次に、本発明の第2の実施形態について説明する。

## 【0045】

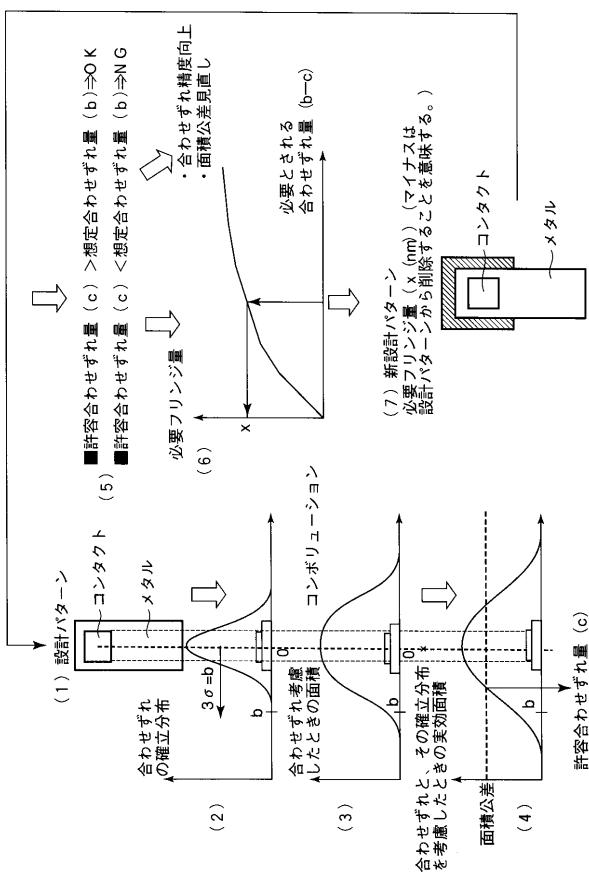

前記図8では、合わせずれ量がaという一様分布をしているという仮定をしたが、実際には、合わせずれはある確率に従って起こる。合わせずれが起こる確率分布が正規分布であり、その3がbであるとした場合の考え方の一例を、図10に示す。

## 【0046】

合わせずれの確率分布、 $3 = b$ の正規分布であるので、(2)のように示される。また、各合わせずれ位置でのリングパターンとメタルパターンとのAND領域面積は、前記図湯及び図9に示す手法によりそれぞれ算出することが可能である。それぞれの位置で求められた面積を縦軸に書くと(3)のようになる。(2)の確率分布と(3)の面積とを畳み込み積分することにより、(2)の確率分布で、合わせずれが生じた場合のリングパターンとメタルパターンとのAND領域の実効面積分布が算出される。

## 【0047】

一方で、この実効面積分布としてどれくらいの値が必要かは、デバイススペック及び実験などにより決まってくる値である(面積公差と記載)。この面積公差を確保できるような許容合わせずれ量(c)を算出し、その許容量が最初に想定している合わせずれ量(b)に対して大きいか否かを判定する。もし、cがbより小さい場合には、実際にはbだけずれる可能性があるにもかかわらず、cのずれに抑える必要があるということなので、bの値がcの値より小さく(0に近くなる)なるように、3つの点から見直すことが必要となる。

## 【0048】

1. 合わせ精度向上させ、 $3 = b$ の値をさらに小さくする

2. 面積公差の見直し

3. 実効面積を増加させる

上記の1.では、目標とする合わせ精度ターゲットを見直す必要があり、2.では、デバイススペックから規定された面積公差が本当に正しいかどうかを再度調査する必要があるため、これらの見直しには比較的時間を要する。最も簡便な方法は3.であり、リングパターンとメタルパターンとのAND領域の実効面積分布を全体的に増加させることである。これを行うためには、メタルフリンジ量を増加させる方法、若しくはコンタクト面積

10

20

30

40

50

を増大させる方法があるが、コンタクトサイズを変えると、他のレイヤー（例えば、ゲート層）との位置関係を考慮する必要があるので、メタルフリンジ量を増加させる方法が現実的である。

#### 【0049】

一例として、横軸に必要とされる合わせずれ量 ( $b - c$  の絶対値) をとり、それを達成するために必要なフリンジ量 ( $x$ ) を縦軸にして、関係グラフ (6) を作成しておき、この関係式に応じてフリンジ量を付加した新設計レイアウト (7) を作成する。この設計レイアウト (7) は再度 (1) に置き換えられて、同様の評価が繰り返し行われ、合わせずれ量 ( $c$ ) が  $b$  と一致、若しくは大きくなったら終了する。そして、この処理を全てのコンタクトホールに対して行った結果、それぞれのコンタクトホールに対して適切なフリンジ量を割り当てることが可能となる、チップサイズを従来よりも小さく作ることが可能となった。

#### 【0050】

このように、合わせずれは、ある確率分布に従って発生するので、その確率分布の考え方を導入して、前記図8及び図9に示す手法を適用することにより、より精度の良いレイアウト修正を行うことができる。

#### 【0051】

##### (第3の実施形態)

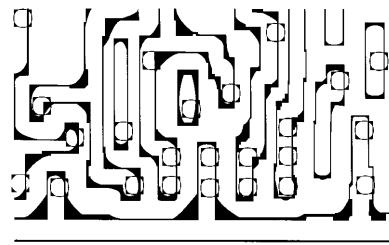

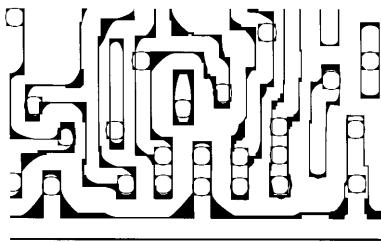

図11及び図12は、本発明の第3の実施形態を説明するための図であり、それぞれの(a)は設計レイアウト、(b)はウェハ上での仕上がり平面形状を示している。また、図中の11は拡散層、12はゲート層、13, 14はコンタクト層を示している。なお、図12(a)(b)において、上図は距離aが短い場合、下図は距離aが長い場合を示している。

#### 【0052】

本手法は、ゲート層、拡散層、コンタクト層との仕上がり形状に基づく評価でも利用することができる。メタル層とコンタクト層の場合は、AND領域の面積を指標として、その面積がある一定値以上あるか否かをレイアウト修正の判定基準とした。ゲート層と拡散層の場合、特に問題になりやすいのは、図11(a)の印で示したゲートライン端部である。ゲート特性を保持するためには、ゲートと拡散層との境界部で、所望のゲート幅となっていることが重要となる。

#### 【0053】

現状は、図12(a)の上図に示すように、拡散層端からの距離aと、拡散層からのゲート突き出し距離bによって、この部分のレイアウト形状が決められている。このとき、bの大きさは、拡散層のコーナー部分での仕上がりラインディング量、及びゲート先端部のショートニング量によって決められており、そのうち拡散層のラウンディング量が、距離aによって変化するため、bはaに依存する値となっている。bを小さくすることによって、チップ面積を小さくすることができるため、bの値は必要かつ最小限の値であることが望ましい。

#### 【0054】

上記のような最小のbの値を決定するためには、以下のようなフローを経てbの値を決定すればよい。

#### 【0055】

1. ゲート層の仕上がり平面形状を算出する。

2. 拡散層の仕上がり平面形状を算出する。

3. ゲート層の仕上がり平面形状のうち、拡散との重なり部分を引き算（ブーリアン演算ではNOTに対応）する。

#### 【0056】

4. NOT処理された境界部の長さを測定する。

5. 4で出力された長さが所定の範囲内にあるかどうかを判定する。

6. 所定範囲内に入っていたら、チップ面積を測定する。

## 【0057】

7. 現在の b の値でチップ面積が所定値を満たしていれば、終了する。

8. 現在の b の値でチップ面積が所定値を満たしていないければ、さらに b の値を小さくし（チップ面積を小さくして）1から再度検討する。

9. 5で所定の長さの範囲内に入っていない場合には、図12のaを大きくする、もしくは b の長さを大きくするといったレイアウト作成、修正を行う。

10. 9でできたレイアウトを1から検証する。

## 【0058】

以上の工程により、チップの要求面積を満たすように b の値を決定することが重要となる。この手法で、b の値を決定したところ、チップ面積を所定より大幅に低減させることができた。

10

## 【0059】

この手法は、ここで示した以外にも、コンタクトと拡散層との関係、コンタクトとゲート層との関係、インプラ層等との関係などに、リソグラフィプロセスなど特に微細加工プロセスによるウェハパターン忠実度の劣化に起因した設計レイアウトに付加されているレイアウトマージンを極力小さくすることができる。その結果、従来のデザインルールによるレイアウト指針で作成した設計レイアウトパターンより小さいチップを作成することが可能となる。

## 【0060】

## (変形例)

20

なお、本発明は上述した各実施形態に限定されるものではない。

## 【0061】

実施形態では、設計パターン補正方法及びシステム、更にはマスクパターン作成方法について説明したが、本発明はこれらに限らず、実施形態の設計パターン補正方法を用いて半導体装置を製造する半導体装置の方法に適用することができる。この場合、従来方法では非常に困難であった個別パターン毎のレイアウト最適化が可能になり、従来よりも小さいチップサイズのパターンを有する半導体装置を製造歩留まり良く実現することが可能となる。

30

## 【0062】

また本発明は、設計パターンの補正方法を利用したマスクの製造方法に適用することができる、更にレイアウト、セルライブリ等の設計や製造に適用することも可能である。

## 【0063】

また、第3の平面形状を算出するためのブーリアン演算処理は、必ずしも AND 処理に限らず NOT 処理であってもよいし、これらの両方を含むものであってもよい。さらに、ブーリアン演算処理を、第1及び第2の平面形状の少なくとも一方をリサイズ若しくは移動させた後に行うようにしてもよい。また、第3の平面形状から得られる評価量は面積に限るものではなく、それ以外に線幅、面積、周囲長、若しくはそれらの平均値、ばらつき量のうち少なくとも1つを用いてもよい。

40

## 【0064】

また、第1又は第2の平面形状を算出する際のプロセス条件としては、露光量と焦点位置に限るものではなく、これら以外に露光装置の露光波長、レンズ開口数、照明形状、マスク寸法、収差、合わせずれ量、及びレジスト拡散長等を用いることができる。また、本発明は、2つのレイヤー間でのプロセスマージンを考慮した設計パターンの補正に限るものではなく、3つ以上のレイヤー間でのプロセスマージンを考慮した設計パターンの補正に適用することができる。さらに、複数のレイヤーとしては、ゲート層、拡散層、コンタクト層、インプラ層、及びウェル層のうち少なくとも2つ以上を使用すればよい。

## 【0065】

また、実施形態では、露光手段に光を用いた場合の一例を記載したが、露光手段が X 線や電子ビームなど、光に代わるものであっても、本発明は同様に応用可能である。

50

## 【0066】

また、実施形態において記載した手法は、コンピュータに実行させることのできるプログラムとして、例えば磁気ディスク（フロッピー（登録商標）ディスク、ハードディスク等）、光ディスク（CD-ROM, DVD等）、半導体メモリなどの記録媒体に書き込んで適用したり、通信媒体により伝送して各種装置に適用することも可能である。本発明を実現するコンピュータは、記録媒体に記録されたプログラムを読み込み、このプログラムによって動作が制御されることにより、上述した処理を実行するものであればよい。

## 【0067】

その他、本発明の要旨を逸脱しない範囲で、種々変形して実施することができる。

## 【0068】

## (まとめ)

以上説明したように本発明の一態様は、半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して設計パターンを補正する設計パターン補正方法であって、第1の設計パターンに基づく第1のレイヤーの仕上がり平面形状である第1の平面形状を算出する工程と、第2の設計パターンに基づく第2のレイヤーの仕上がり平面形状である第2の平面形状を算出する工程と、第1の平面形状と第2の平面形状とのブーリアン演算処理により第3の平面形状を算出する工程と、第3の平面形状から得られる評価量が所定値を満たすか否かを判定する工程と、前記判定工程により前記評価量が所定値を満たさないと判定された場合に、第1及び第2の設計パターンの少なくとも一方を修正する工程と、を含むことを特徴とする。

## 【0069】

ここで、本発明の一態様の望ましい実施態様としては次のものがあげられる。

## 【0070】

(1) 第1及び第2の平面形状のうち、少なくとも一方は対応する設計パターンに対して光近接効果補正を含むリサイズ処理を行った後のマスクパターンから算出されること。

## 【0071】

(2) ブーリアン演算処理は、AND処理及びNOT処理のうち少なくとも一方を含むこと。

## 【0072】

(3) ブーリアン演算処理を、第1及び第2の平面形状の少なくとも一方をリサイズ若しくは移動させた後に行うこと。

## 【0073】

(4) 第3の平面形状から得られる評価量は、線幅、面積、周囲長、若しくはそれらの平均値、ばらつき量のうち少なくとも1つであること。

## 【0074】

(5) 第1又は第2の平面形状を、それぞれ複数のプロセス条件下で算出すること。

## 【0075】

(6) (5)において、複数のプロセス条件は、露光装置の露光波長、レンズ開口数、照明形状、マスク寸法、露光量、焦点位置、収差、合わせずれ量、及びレジスト拡散長のうち少なくとも1つを含むこと。

## 【0076】

(7) 各工程を、第3の平面形状から得られる評価量が所定値を満たすまで繰り返し行うこと。

## 【0077】

(8) 第1及び第2の設計パターンにはそれぞれ複数のパターンが存在し、パターンの修正処理は、各設計パターンに存在する複数のパターンに対して行うこと。

## 【0078】

(9) 第1のレイヤーはメタル配線層であり、第2のレイヤーはコンタクト層であること。

## 【0079】

10

20

30

40

50

(10) 第1及び第2のレイヤーに加え、第3以上のレイヤーを有する半導体集積回路の複数レイヤー間でのプロセスマージンを考慮して設計パターンを補正すること。

【0080】

(11)(10)において、複数のレイヤーとして、ゲート層、拡散層、コンタクト層、インプラ層、及びウェル層のうち少なくとも2つ以上を使用すること。

【0081】

(12) 評価量を算出するときには、レイヤー間の合わせずれ量及び合わせずれ量の確率分布が考慮されていること。

【図面の簡単な説明】

【0082】

10

【図1】単一レイヤーの場合の仕上がり形状を示す図。

【図2】複数レイヤーの場合の仕上がり形状を示す図。

【図3】複数レイヤー+合わせずれを考慮した仕上がり形状を示す図。

【図4】コンタクトの接続するゲート層、拡散層についての説明図。

【図5】メタル配線とビアとの配置の一例を示す図。

【図6】P & Rツール、OPCツール、リソグラフィ検証ツール、及びコンパクションツールを組み合わせたウェハ上の仕上がり平面形状情報に基づく設計レイアウトシステムの一例を示す図。

【図7】複数層レイヤーの検証の流れを示す図。

【図8】複数層レイヤー検証の流れの一例を示す図。

20

【図9】図5の実レイアウトへの適用結果を示す図。

【図10】合わせずれの確率分布を考慮した場合の設計パターンへのフィードバック手法を示す図。

【図11】ゲート層と拡散層とコンタクト層との関係を示す図。

【図12】ゲート先端部と拡散層との仕上がり平面形状の関係を示す図。

【符号の説明】

【0083】

30

1 1 ... 拡散層

1 2 ... ゲート層

1 3 , 1 4 ... コンタクト層

2 1 , 2 2 ... メタル配線

3 1 , 3 3 ... ビア

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

【図11】

【図12】

---

フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 小谷 敏也

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72)発明者 姜 帥現

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72)発明者 市川 裕隆

神奈川県川崎市川崎区駅前本町25番地1 東芝マイクロエレクトロニクス株式会社内

F ターム(参考) 2H095 BB01 BB36

5B046 AA08 BA05 DA02 FA04 FA07 JA02

5F064 DD08 DD10 DD31 HH06