(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4723919号

(P4723919)

(45) 発行日 平成23年7月13日(2011.7.13)

(24) 登録日 平成23年4月15日(2011.4.15)

(51) Int.Cl.

H04N 5/378 (2011.01)

F 1

H04N 5/335 780

請求項の数 3 (全 18 頁)

(21) 出願番号 特願2005-167142 (P2005-167142)

(22) 出願日 平成17年6月7日 (2005.6.7)

(65) 公開番号 特開2006-345074 (P2006-345074A)

(43) 公開日 平成18年12月21日 (2006.12.21)

審査請求日 平成20年1月18日 (2008.1.18)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 100093492

弁理士 鈴木 市郎

(72) 発明者 小松 裕之

神奈川県横浜市戸塚区吉田町292番地

株式会社 日立アドバンストデジタル内

(72) 発明者 西澤 明仁

神奈川県横浜市戸塚区吉田町292番地

株式会社 日立製作所 ユビキタスプラットフォーム開発研究所内

審査官 若林 治男

最終頁に続く

(54) 【発明の名称】タイミングパルス発生装置とこれを用いた撮像装置。

## (57) 【特許請求の範囲】

## 【請求項 1】

アドレスを発生するアドレス発生回路と、

該アドレスに応じた設定データと制御データ，駆動パルスのデータが格納されたメモリと、

該メモリから読み出された第1の設定データとカウント結果を比較しながら、カウント動作を行ない、所定のタイミングでクリアパルスを発生する第1のカウンタと、

該メモリから読み出された第2の設定データとカウント結果を比較しながら、カウント動作を行ない、所定のタイミングでインクリメントパルスを発生する第2のカウンタと、

該アドレス発生回路で発生したアドレスを、該メモリから読み出される該制御データに応じたタイミングで、保持するアドレス保持回路と

を備え、

該アドレス発生回路は、該第1のカウンタからの該クリアパルス毎に該アドレスをインクリメントするとともに、該アドレスを、該第1のカウンタからの該クリアパルス及び第2のカウンタからの該インクリメントに応じて、該アドレス保持回路に保持された保持アドレスにジャンプさせ、該アドレスに応じて該メモリから駆動パルスを出力することを特徴とするタイミングパルス発生装置。

## 【請求項 2】

アドレスを発生するアドレス発生回路と、

該アドレスに応じた設定データと制御データが格納されたメモリと、

10

20

該メモリから読み出された第1の設定データとカウント結果を比較しながら、カウント動作を行ない、所定のタイミングでクリアパルスを発生する第1のカウンタと、

該メモリから読み出された第2の設定データとカウント結果を比較しながら、カウント動作を行ない、所定のタイミングでインクリメントパルスを発生する第2のカウンタと、

該アドレス発生回路で発生したアドレスを、該メモリから読み出される該制御データに応じたタイミングで、保持するアドレス保持回路と

を備え、

該アドレス発生回路は、該第1のカウンタからの該クリアパルス毎に該アドレスをインクリメントするとともに、該アドレスを、該第1のカウンタからの該クリアパルス及び第2のカウンタからの該インクリメントに応じて、該アドレス保持回路に保持された保持アドレスにジャンプさせ、該アドレス発生回路から発生される該アドレスの所定ビットを駆動パルスとすることを特徴とするタイミングパルス発生装置。

### 【請求項3】

請求項1または2に記載のタイミングパルス発生装置をCCD撮像素子の駆動パルスの発生装置として用いたことを特徴とするCCD撮像装置。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、撮像素子などの素子を駆動するためのパルス（駆動パルス）を発生するタイミングパルス発生装置とこれを用いた撮像装置に関する。

#### 【背景技術】

#### 【0002】

CCD撮像素子やLCD素子などを駆動する場合、これら素子の駆動仕様に基いて、“1”（高レベル），“0”（低レベル）による駆動パルスを生成する必要があるが、従来では、カウンタ、デコーダなどを用いて所望の駆動パルスを生成していた（例えば、特許文献1参照）。

#### 【0003】

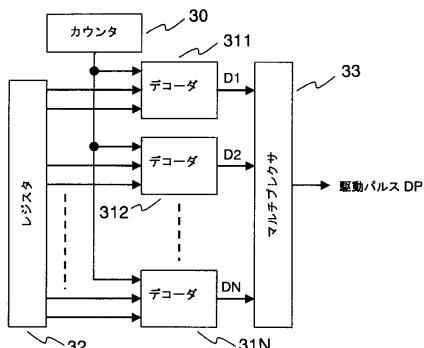

図12はかかる駆動パルス発生のためのタイミングパルス発生装置の一従来例を示すブロック図であって、30はカウンタ、311，……，31Nはデコーダ、32はレジスタ、33はマルチプレクサである。

#### 【0004】

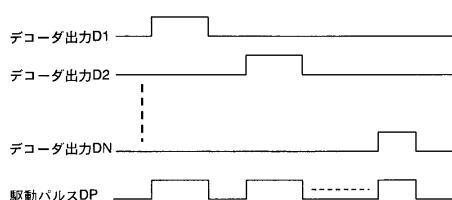

図13は図12でのデコーダ311，……，31Nの出力パルスD1，……，DN及びマルチプレクサ33から出力される駆動パルスを示すタイミング図である。

#### 【0005】

図12及び図13において、デコーダ311はカウンタ30のカウント値とレジスタ32の値とを比較し、これらが一致したとき、出力パルスD1を発生する。同様に、デコーダ312，……，31Nも夫々、出力パルスD2，……，DNを出力する。マルチプレクサ33は、これらデコーダ311，……，31Nの出力パルスD1，……，DNをマルチプレクサして駆動パルスを生成する。

#### 【0006】

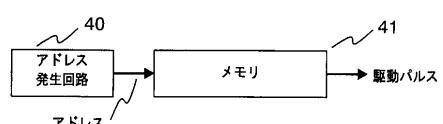

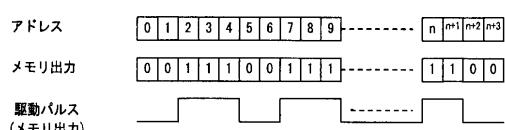

図14は駆動パルスを発生するタイミングパルス発生装置の他の従来例を示すブロック図であって、40はアドレス発生回路、41はメモリである。

#### 【0007】

図15は図14におけるアドレス発生回路からのアドレスに対するメモリの出力パルス及び駆動パルスを示すタイミング図である。

#### 【0008】

図14及び図15において、メモリ41には、所望の駆動パルスに対応して、アドレス毎に“1”（高レベル）あるいは“0”（低レベル）のデータが予め書き込まれている。メモリ41では、アドレス発生回路40で発生されるアドレス信号によって順次アドレス「0」，「1」，「2」，……がアクセスされ、アクセスされたアドレスから“1”ある

10

20

30

40

50

いは“0”のデータが読み出されて、駆動パルスとして、出力される。

【特許文献1】特開平10-257398号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

図12に示す従来の技術では、生成可能なパルス列の変化点（即ち、周期やパルス幅が異なるパルス列の切り替え点）の数がデコーダの数で決まってしまい、予め想定していた変化点以上の数の駆動パルスが必要になった場合は対応できない。これを、例えば、CCD撮像素子の垂直CCDの垂直転送駆動パルスのタイミングパルス発生装置として用いる場合、垂直CCDでの電荷の転送方法としては種々のものがあるが、その転送方法に応じてこのタイミングパルス発生装置の回路構成が決まってしまい、採用する転送方法毎に異なる回路構成のタイミングパルス発生装置を作成する必要がある。

10

【0010】

また、図14に示す従来の技術では、変化点の数に制限はなく、異なる垂直転送方法のCCD撮像素子に対し、同じ回路構成のタイミングパルス発生装置を共通に使用することを可能とするが、駆動パルスの1ステップ毎にメモリ41が1アドレス必要なため、例えば、レベル“0”的状態が1000ステップ続くような駆動パルスの場合においても、メモリ41では、アドレスが1000アドレス必要であり、メモリの使用効率が悪くなる。

20

【0011】

本発明の目的は、かかる問題を解消し、駆動パルスの変化点の数に対応でき、かつメモリの使用効率を高めることができるようとしたタイミングパルス発生装置とこれを用いた撮像装置を提供することにある。

【課題を解決するための手段】

【0012】

上記目的を達成するために、本発明によるタイミングパルス発生装置は、アドレスを発生するアドレス発生回路と、該アドレスに応じた設定データと制御データ、駆動パルスのデータが格納されたメモリと、該メモリから読み出された第1の設定データとカウント結果を比較しながら、カウント動作を行ない、所定のタイミングでクリアパルスを発生する第1のカウンタと、該メモリから読み出された第2の設定データとカウント結果を比較しながら、カウント動作を行ない、所定のタイミングでインクリメントパルスを発生する第2のカウンタと、該アドレス発生回路で発生したアドレスを、該メモリから読み出される該制御データに応じたタイミングで、保持するアドレス保持回路とを備え、該アドレス発生回路は、該第1のカウンタからの該クリアパルス毎に該アドレスをインクリメントするとともに、該アドレスを、該第1のカウンタからの該クリアパルス及び第2のカウンタからの該インクリメントに応じて、該アドレス保持回路に保持された保持アドレスにジャンプさせ、該アドレスに応じて該メモリから駆動パルスを出力することを特徴とするものである。

30

【0015】

また、本発明によるタイミングパルス発生装置は、アドレスを発生するアドレス発生回路と、該アドレスに応じた設定データと制御データが格納されたメモリと、該メモリから読み出された第1の設定データとカウント結果を比較しながら、カウント動作を行ない、所定のタイミングでクリアパルスを発生する第1のカウンタと、該メモリから読み出された第2の設定データとカウント結果を比較しながら、カウント動作を行ない、所定のタイミングでインクリメントパルスを発生する第2のカウンタと、該アドレス発生回路で発生したアドレスを、該メモリから読み出される該制御データに応じたタイミングで、保持するアドレス保持回路とを備え、該アドレス発生回路は、該第1のカウンタからの該クリアパルス毎に該アドレスをインクリメントするとともに、該アドレスを、該第1のカウンタからの該クリアパルス及び第2のカウンタからの該インクリメントに応じて、該アドレス保持回路に保持された保持アドレスにジャンプさせ、該アドレス発生回路から発生される

40

50

該アドレスの所定ビットを駆動パルスとすることを特徴とするものである。

【0016】

また、本発明による撮像装置は、上記タイミングパルス発生装置のいずれかをCCD撮像素子の駆動パルスの発生装置として用いたことを特徴とするものである。

【発明の効果】

【0017】

本発明によると、生成する駆動パルスの変化点の数が増えた場合でも対応がでけて、さらに、駆動パルスの状態が固定の期間では、メモリのアドレスを進める必要がないため、メモリの使用効率が高くなる。

【発明を実施するための最良の形態】

10

【0018】

以下、本発明の実施形態を図面により説明する。

【0019】

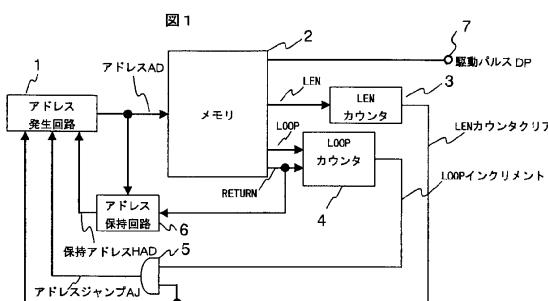

図1は本発明によるタイミングパルス発生装置の一実施形態を示すブロック図であって、1はアドレス発生回路、2はメモリ、3はLEN(長さ)カウンタ、4はLOOP(ループ)カウンタ、5はアンドゲート、6はアドレス保持回路、7は出力端子である。

【0020】

同図において、メモリ2の記憶エリアは、駆動パルスDPや、設定データとしてのLEN(長さ)データ及びLOOP(繰り返し周期)データ、制御データとしてのRETURN(戻り)データなどのデータ毎にデータ格納エリアが区分されており、夫々のデータ格納エリアでは、各アドレス毎に順次データの値が格納されている。かかるアドレスはアドレス発生回路1から発生されるアドレス信号によって指定され、各データ格納エリアでは、このアドレス信号によって指定されるアドレスからそこに格納されているデータ値が読み出される。

20

【0021】

アドレス発生回路1は、所定のタイミングで供給されるリセットパルスRによってアドレスADが値「0」にリセットされ、また、後述するLENカウンタ3から出力されるレベル“H”(高レベル)のLENカウンタクリア信号の立下りエッジにより、あるいは、アンドゲート5から出力されるレベル“H”的アドレスジャンプパルスAJの立下りエッジにより、アドレスADを更新する。

【0022】

30

メモリ2から出力されるLENデータはLENカウンタ3にセットされる。LENカウンタ3はクロックを初期値「1」からカウントアップし、このカウント値がセットされたLENデータの値と等しくなると、クロックの1周期の時間幅でレベル“H”的LENカウンタクリアパルスを発生し、また、カウント値を初期値「1」に戻す。

【0023】

アドレス発生回路1は、このLENカウンタクリアパルスのレベル“H”からレベル“L”(低レベル)への立下りエッジのタイミングでインクリメントし、次の値「1」だけ増加したアドレスADをメモリ2に供給する。そこで、メモリ2では、各データ格納エリアのこのアドレスADで指定されるアドレスから次のデータ値が読み出される。読み出されたLENデータはLENカウンタ3にセットされ、LENカウンタ3は、上記のように、初期値「1」からクロックをカウントアップする。

40

【0024】

また、アドレス発生回路1からのアドレスADに応じてメモリ2から出力されるLOOPデータが、LOOPカウンタ4にセットされる。このLOOPカウンタ4は、アドレス発生回路1からのアドレスADに応じてメモリ3から出力される“1”(高レベル)，“0”(低レベル)のRETURNデータのレベル“1”からレベル“0”への立下りエッジ毎にインクリメントし、RETURNデータのレベル“1”で、かつLOOPカウンタ4のカウント値がそのときセットされているLOOPデータと一致しないとき、LOOPインクリメントパルスを発生する。

【0025】

ここで、RETURNデータが“0”的とき、アドレス保持回路6にこのときのアドレスADが

50

、保持アドレスHADとして、アドレス保持回路6に保持される。

**【0026】**

LENカウンタ3から出力されるLENカウンタクリアパルスとLOOPカウンタ4から出力されるLOOPインクリメントパルスとはアンドゲート5で演算処理され、これらLENカウンタクリアパルスとLOOPインクリメントパルスとがともにレベル“H”的とき、制御信号としてのアドレスジャンプパルスAJが生成される。アドレス発生回路1は、通常、LENカウンタ3からのLENカウンタクリアパルスの立下りエッジ毎に順次インクリメントするアドレスADを生成出力するが、アンドゲート5からアドレスジャンプパルスAJが供給されると、これによる制御により、アドレス保持回路6に保持されている保持アドレスHADにアドレスADをクリアする(戻す)。従って、このときのアドレスADはこの保持アドレスHADとなり、次にアンドゲート5からアドレスジャンプパルスAJが供給されるまで、LENカウンタ3からのLENカウンタクリアパルスの立下りエッジ毎にアドレスADをこの保持アドレスHADから順次インクリメントする。10

**【0027】**

このようにして、アドレス発生回路1は、メモリ2から読み出されるLENデータ、LOOPデータ、RETURNデータに応じたアドレスADを発生し、かかるアドレスADによってメモリ2から駆動パルスDPが読み出され、出力端子7から外部に出力される。

**【0028】**

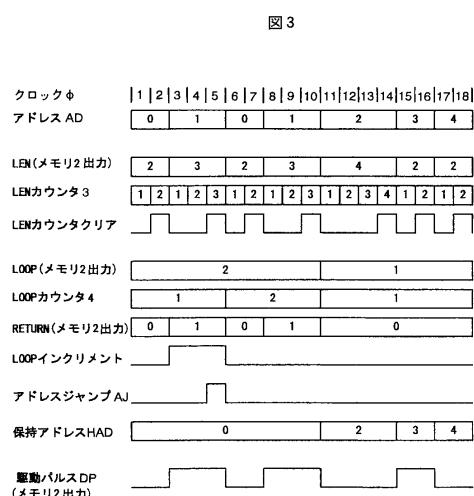

次に、この実施形態の動作の一具体例について説明する。

**【0029】**

ここで、メモリ2には、図2に示すように、データが格納されているものとする。なお、図2は各データ格納エリアでのアドレスAD毎のデータを模式的に示すものであって、例えば、LENデータ格納エリア2aには、アドレスADが「0」、「1」、「2」、「3」、「4」の順に値「2」、「3」、「4」、「2」、「2」のLENデータが格納されており、LOOPデータ格納エリア2bには、アドレスADが「0」、「1」、「2」、「3」、「4」の順に値「2」、「2」、「1」、「1」、「1」のLOOPデータが格納されており、RETURNデータ格納エリア2cには、アドレスADが「0」、「1」、「2」、「3」、「4」の順にレベル“0”、“1”、“0”、“0”、“0”的RETURNデータが格納されており(但し、レベル“0”は低レベル、レベル“1”は高レベルとする)、駆動パルス格納エリア2dには、アドレスADが「0」、「1」、「2」、「3」、「4」の順にレベル“L”、“H”、“L”、“H”、“L”的駆動パルスDPのデータが格納されている。30

**【0030】**

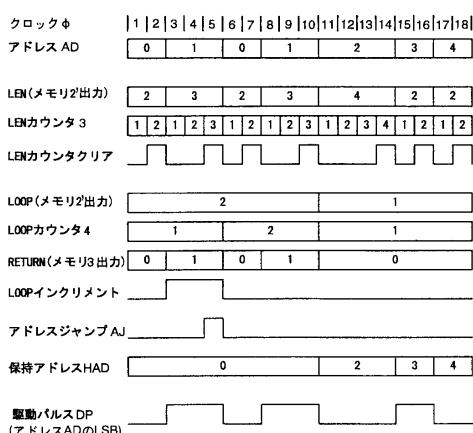

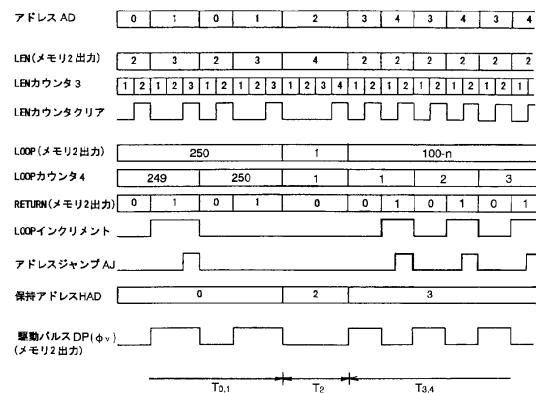

図3はクロックの周期毎のタイミングを基準とした図1の各部のデータ、信号を示すタイミング図であって、クロックの周期毎のタイミングを1、2、3、……、18で示す。

**【0031】**

以下では、図1～図3により、各タイミング(クロック1、2、3、……、18)毎に動作を説明する。

**【0032】**

A. クロック1～10の期間について

(1) クロック1のタイミング：

このタイミングでは、アドレス発生回路1がリセットパルスRでリセットされ、アドレス発生回路1から出力されるアドレスADを「0」となる。これにより、クロック1のタイミングでは、メモリ2の各データ格納エリア2a～2dから値「2」のLENデータ、値「2」のLOOPデータ、及び“0”的RETURNデータが読み出され、値「2」のLENデータはLENカウンタ3に、値「2」のLOOPデータはLOOPカウンタ4に夫々セットされる。このとき、LENカウンタ3とLOOPカウンタ4とのカウント値は初期値「1」にリセットされ、夫々のセット値と一致しない。従って、LENカウンタ3からは“H”的LENカウンタクリアパルスが出力されず、LOOPカウンタ4からも、“H”的LOOPインクリメントパルスは出力されない。40

**【0033】**

また、このクロック 1 のタイミングでは、RETURNデータが“0”であるから、アドレス保持回路 6 にこのときのアドレスAD、即ち、「0」のアドレスADが保持される。

**【0034】**

さらに、図 2 により、この「0」のアドレスADでは、メモリ 2 での駆動パルスのデータ格納エリアに“L”のデータが格納されており、このため、この“L”的データが読み出されて駆動パルスDPは“L”を出力する。

**【0035】**

## (2) クロック 2 のタイミング：

次のクロック 2 のタイミングでは、LENカウンタ 3 がクロック をアップカウントしてそのカウント値が「2」となり、LENカウンタ 3 のセット値「2」と等しくなる。これにより、このLENカウンタ 3 から“H”的LENカウンタクリアパルスが出力される。しかし、このときも、アドレス発生回路 1 からのアドレスADがそのまま「0」に保持されているので、メモリ 2 からのRETURNデータは“0”であり、LOOPカウンタ 4 はアップカウントしないで、そのカウント値がそのまま初期値「1」に保持される。従って、LOOPカウンタ 4 からは“H”的LOOPインクリメントパルスは出力されない。

**【0036】**

さらに、図 2 により、このときのアドレスADは「0」であり、メモリ 2 の駆動パルスDP のデータ格納エリアのアドレス「0」に“L”的データが格納されているので、メモリ 2 からは“L”的駆動パルスDPが出力される。

**【0037】**

## (3) クロック 3 のタイミング：

次のクロック 3 のタイミングでは、LENカウンタ 3 がクロック をアップカウントする際に、クロック 2 のタイミング時において、LENカウンタ 3 から“H”的LENカウンタクリアパルスが出力されていることから、事前に「次のクロック のタイミング、即ち、クロック 2 からクロック 3への切換えタイミングでは、LENカウンタ 3 はカウント値を初期値「1」にリセットする」ことが判っているため、立下りエッジで初期値「1」にリセットされ、同時に、LENカウンタクリアパルスは立ち下がる。

**【0038】**

一方、クロック 3 のタイミングでLENカウンタ 3 からのLENカウンタクリアパルスが立ち下がることにより、その立下りエッジでアドレス発生回路 1 がインクリメントし、アドレスADが「1」となる。

**【0039】**

これにより、メモリ 2 での各データ格納エリアでアドレス「1」がアクセスされ、図 2 により、メモリ 2 から値「3」のLENデータが読み出されてLENカウンタ 3 にセットされる。また、メモリ 2 から値「2」のLOOPデータが読み出されてLOOPカウンタ 4 にセットされるが、このセット値はクロック 1 のタイミングのときのセット値と変わりがない。

**【0040】**

このようにして、クロック 3 のタイミングでは、アドレスADが「1」であって、LENカウンタ 3 は値「3」にセットされ、LOOPカウンタ 4 は値「2」にセットされている。

**【0041】**

一方、図 2 により、アドレスADが「1」となると、メモリ 2 から出力されるRETURNデータは“1”となるが、LOOPカウンタ 4 はこの立上りエッジではアップカウントせず、そのカウント値はそのまま「1」に保持される。但し、このカウント値「1」はこのLOOPカウンタ 4 のセット値「2」と異なっており、しかも、RETURNデータが“1”となったことから、LOOPカウンタ 4 から“H”的LOOPインクリメントパルスが出力される。

**【0042】**

なお、図 2 により、メモリ 2 の駆動パルスDPのデータ格納エリアのアドレス「1」に“H”的データが格納されているので、メモリ 2 から“H”的駆動パルスDPが読み出されて出力端子 7 から出力される。

10

20

30

40

50

**【0043】**

また、RETURNデータが“1”であるので、アドレス保持回路6の書き替えが行なわれず、その保持アドレスHADは「0」のままである。

**【0044】**

## (4) クロック 4 のタイミング：

次のクロック 4 のタイミングでは、LENカウンタ3がクロック をアップカウントしてそのカウント値が「2」となるが、これがLENカウンタ3のセット値「3」と一致しないので、“H”的LENカウンタクリアパルスは発生しない。このため、アドレス発生回路1からのアドレスADは「1」のままである。そこで、メモリ2からのRETURNデータは“1”のままであり、LOOPカウンタ4のカウント値は初期値「1」のままであって、“H”的 LOOPインクリメントパルスの出力がそのまま継続する。10

**【0045】**

なお、このクロック 4 のタイミングでも、“H”的駆動パルスDPがメモリ2から読み出され続ける。

**【0046】**

## (5) クロック 5 のタイミング：

次のクロック 5 のタイミングでは、LENカウンタ3がクロック をアップカウントしてそのカウント値が「3」となり、LENカウンタ3のセット値「3」と等しくなる。これにより、LENカウンタ3から“H”的LENカウンタクリアパルスが出力され始める。このときも、LOOPカウンタ4のカウント値は初期値「1」のままであって、そのセット値「2」とは一致せず、また、RETURNデータは“1”的ままであるから、“H”的LOOPインクリメントパルスが出力され続ける。20

**【0047】**

このように、クロック 5 のタイミングでは、LENカウンタクリアパルスとLOOPインクリメントパルスとがともに“H”的であるから、アンドゲート5から“H”的アドレスジャンプパルスAJが出力される。

**【0048】**

## (6) クロック 6 のタイミング～クロック 10 のタイミング：

次のクロック 6 のタイミングでは、クロック 2 からクロック 3への切り換わりと同様、事前に次のクロック で LEN カウンタ3 が初期値にリセットされることが判るため、その立下りエッジでLENカウンタ3が初期値「1」にリセットされ、同時に、LEN カウンタクリアパルスが立ち下がる。また、アンドゲート5の出力レベルが“L”になってアドレスジャンプパルスAJが立ち下がる。このアドレスジャンプパルスAJの立下りエッジでアドレス保持回路6の「0」の保持アドレスHADがアドレス発生回路1に取り込まれ、アドレスADがこの保持アドレスHADに等しい値「0」に設定される。従って、メモリ2からは、上記クロック 1 のタイミングのときと同じ値「2」のLENデータが読み出されてLENカウンタ3にセットされ、また、上記クロック 1 のタイミングのときと同じ値「2」のLOOPデータが読み出されてLOOPカウンタ4にセットされる。30

**【0049】**

また、アドレスADが「0」となったことにより、図2により、メモリ2からのRETURNデータが“1”から“0”に反転する。これにより、LOOPカウンタ4からのLENカウンタクリアパルスは“1”から“0”にレベル反転して立ち下がる。従って、アンドゲート5の出力は“L”になる。40

**【0050】**

さらに、RETURNデータが“1”から“0”にレベル反転することにより、この時点でのアドレスAD、即ち、値「0」のアドレスADがアドレス保持回路6に、保持アドレスHADとして、保持される。

**【0051】**

このようにして、LENカウンタ3とLOOPカウンタ4とに夫々値「2」がセットされることにより、クロック 1 のタイミングからクロック 5 までの上記の動作が繰り返される50

ことになる。この期間がクロック 6 のタイミングからクロック 10 のタイミングまでの期間である。この期間でも、アドレスADが「1」の期間、メモリ2から“H”的駆動パルスDPが読み出されて出力端子7から出力される。

#### 【0052】

但し、かかる期間でのLOOPカウンタ4のカウント値は「2」であり、LOOPカウンタ4のセット値と等しい値となっている。従って、アドレスADが「1」となってRETURNデータが“1”なっても、LOOPカウンタ4からは“H”的LOOPインクリメントパルスは発生せず、従って、アンドゲート5からはアドレスジャンプパルスAJが発生しない。

#### 【0053】

以上のようにして、クロック 1 ~ 10 の期間、クロック の5倍の周期 5T でデューティ比 60% (= 3 × 100 / 5) の駆動パルスDPがメモリ2から2回出力されることになる。

#### 【0054】

B . クロック 11 ~ 18 の期間について

##### (7) クロック 11 のタイミング :

クロック 10 のタイミングでは、先のクロック 5 のタイミングのときと同様、LENカウンタ3のカウント値は「3」でそのセット値と等しく、このLENカウンタ3からは“H”的LENカウンタクリアパルスが出力されているため、次のクロック 11 のタイミングでクロック により、LENカウンタ3を初期値にリセットすることが事前に判るため、クロック で初期値にリセットされる。同時に、LENカウンタクリアパルスは“H”から“L”に反転して立ち下がる。このLENカウンタクリアパルスの立下りエッジでアドレス発生回路1はインクリメントし、そのアドレスADを「2」とする。

#### 【0055】

そこで、メモリ2では、各データ格納エリアのアドレス「2」が読み出されることになり、図2により、値「4」のLENデータが読み出されてLENカウンタ3にセットされ、値「1」のLOOPデータが読み出されてLOOPカウンタ4にセットされる。また、“0”的RETURNデータが読み出されてLOOPカウンタ4とアドレス保持回路6とに供給される。このRETURNデータが“0”なったことにより、また、このときのLOOPカウンタ4のカウント値「2」がそのセット値と一致していることから、LOOPカウンタ4のカウント値は初期値「1」にリセットされ、また、RETURNデータが“0”であることから、アドレス保持回路6にそのときの「2」のアドレスADが、保持アドレスHADとして、保持される。

#### 【0056】

##### (8) クロック 12 のタイミング～クロック 13 のタイミング :

次のクロック 12 のタイミングでLENカウンタ3がクロック をアップカウントしてそのカウント値が「2」となり、さらに、次のクロック 13 のタイミングでLENカウンタ3がクロック をアップカウントしてそのカウント値が「3」となるが、これらカウント値はセット値「4」に一致しないので、LENカウンタ3から“H”的LENカウンタクリアパルスが発生しない。

#### 【0057】

また、このときのLOOPカウンタ4のカウント値「1」はそのセット値「1」と一致しているので(仮に、RETURNデータが“1”なっても)、LOOPカウンタ4も“H”的LOOPインクリメントパルスを発生しない。

#### 【0058】

従って、LENカウンタ3がクロック をアップカウントするだけで、これ以外は同じ状態が維持される。

#### 【0059】

##### (9) クロック 14 ~ 15 のタイミング :

次のクロック 14 のタイミングでLENカウンタ3がクロック をアップカウントしてそのカウント値が「4」となると、これがLENカウンタ3のセット値に等しくなるから、LENカウンタ3から“H”的LENカウンタクリアパルスが発生する。しかし、LOOPカウンタ

10

20

30

40

50

4は、そのカウント値「1」がそのセット値と一致しているので“H”のLOOPインクリメントパルスを発生しない。

#### 【0060】

そして、次のクロック 15 のタイミングになると、クロック 2, 3, 5, 6, 7, 8, 10, 11などと同様に、LENカウンタ3が初期値にリセットされ、同時に、“H”的 LENカウンタクリアパルスは“H”から“L”へ立ち下がり、この立下りエッジでアドレス発生回路1がインクリメントし、アドレスADが「3」となる。

#### 【0061】

アドレスADが「3」になると、図2により、メモリ2から値「2」のLENデータが読み取られてLENカウンタ3にセットされ、値「1」のLOOPデータが読み取られてLOOPカウンタ4にセットされる。また、“0”的RETURNデータが読み取られてLOOPカウンタ4とアドレス保持回路6に供給される。これにより、アドレス保持回路6には、そのときの「3」のアドレスADが保持される。しかし、LOOPカウンタ4からは“H”的 LOOPインクリメントパルスは発生しない。10

#### 【0062】

また、アドレスADが「3」のときには、メモリ2から“H”的駆動パルスDPが読み取られ、出力端子7から出力される。

#### 【0063】

##### (10) クロック 16 のタイミング：

次のクロック 16 のタイミングでLENカウンタ3がクロック をアップカウントしてそのカウント値が「2」となると、これがLENカウンタ3のセット値と等しいから、LENカウンタ3から“H”的 LENカウンタクリアパルスが出力される。しかし、LOOPカウンタ4は、そのカウント値「1」がそのセット値に等しいから、“H”的 LOOPインクリメントパルスを発生しない。このときも、RETURNデータが“0”であるから、「3」のアドレスADがアドレス保持回路6に保持される。また、このときのアドレスADが「3」であるから、メモリ2から駆動パルスDPは発生している。20

#### 【0064】

##### (11) クロック 17 のタイミング：

次のクロック 17 のタイミングでLENカウンタ3が初期値にリセットされ、同時に、LENカウンタクリアパルスが“H”から“L”へ立ち下がる。このLENカウンタクリアパルスの立下りエッジにより、アドレス発生回路1はインクリメントし、アドレスADは「4」となる。30

#### 【0065】

アドレスADが「4」となると、図2により、メモリ2から値「2」のLENデータが読み取られてLENカウンタ3にセットされ、値「1」のLOOPデータが読み取られてLOOPカウンタ4にセットされる。また、“0”的RETURNデータが読み取られてLOOPカウンタ4とアドレス保持回路6に供給される。これにより、アドレス保持回路6には、そのときの「4」のアドレスADが保持される。しかし、LOOPカウンタ4からは“H”的 LOOPインクリメントパルスは発生しない。

#### 【0066】

また、アドレスADが「4」となると、メモリ2から出力されていた駆動パルスDPが立ち下がり、“L”を出力する。40

#### 【0067】

##### (12) クロック 18 のタイミング：

次のクロック 18 のタイミングでLENカウンタ3がクロック をアップカウントしてそのカウント値が「2」となると、これがLENカウンタ3のセット値と等しいから、LENカウンタ3から“H”的 LENカウンタクリアパルスが出力される。しかし、LOOPカウンタ4は、そのカウント値「1」がそのセット値に等しいから、“H”的 LOOPインクリメントパルスを発生しない。このときも、RETURNデータが“0”であるから、「4」のアドレスADがアドレス保持回路6に、保持アドレスHADとして、保持される。また、このときのアド50

レスADが「4」であることにより、メモリ2から駆動パルスDPは発生しない。

#### 【0068】

以上の動作説明から明らかなように、LENデータは、アドレスADの期間長を、クロックの周期Tを単位長として、規定するものである。例えば、LENデータの値が「2」であるときには、例えば、「0」のアドレスADの期間長が $2T$ となる。このことから、LENデータに応じて駆動パルスDPの周期やパルス幅が規定されることになる。

#### 【0069】

また、上記の例では、アドレスADが「1」であるクロック3～5のタイミング期間及びクロック8～10のタイミング期間や、アドレスADが「3」であるクロック15～16のタイミング期間に駆動パルスDPがメモリ2から出力される。

10

#### 【0070】

ここで、クロック1～10のタイミングの期間では、クロックの周期の5倍の周期 $5T$ で2回駆動パルスDPが発生されるものである。これは、「0」、「1」のアドレスADが続く期間を2回繰り返すことによって可能としており、この繰り返しはLOOPデータによって決められるものである。上記のタイミング期間の例では、アドレス値ADが「0」、「1」であるときのLOOPデータの値を「2」としているため、アドレス値ADが「0」、「1」の期間を2回繰り返すことになるが、LOOPデータを値「2」以上の値とすることにより、「0」、「1」のアドレス値ADが続く期間を任意回数繰り返すようにすることができます、一定周期の駆動パルスを任意個数を発生させることができる。

20

#### 【0071】

但し、このように、「0」、「1」のアドレスADを繰り返させる場合、「0」のアドレスADをアドレス保持回路6に、保持アドレスHADとして、保持し、「1」のアドレスADの経過後、アドレス保持回路6に保持されているこの「0」の保持アドレスHADをアドレス発生回路1に供給して、アドレスADを「0」に戻す。このアドレスADは、保持アドレスHDとして、アドレス保持回路6に保持される。かかる動作をLOOPデータの値の回数繰り返すのであるが、アドレス保持回路6へのアドレスADの保持タイミングとアドレス発生回路1への保持アドレスHADの供給タイミングをRETURNデータの“0”，“1”で規定しているのである。

#### 【0072】

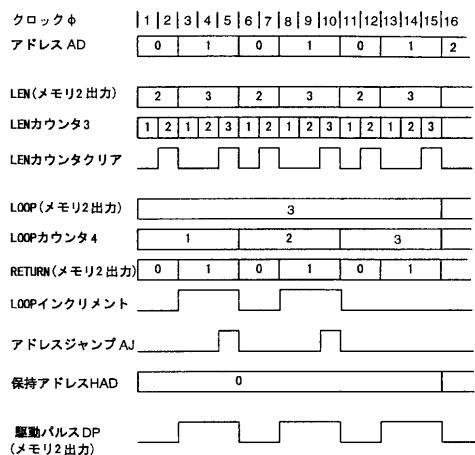

例えば、アドレスADが「0」、「1」のときにメモリ2から読み出されるLOOPデータの値が「3」の場合には、図4に示すように、LOOPカウンタ4は、初期値「1」から、RETURNデータが“1”から“0”にレベル反転する立下りエッジ毎に、インクリメントし、そのカウント値が「1」、「2」、「3」でアドレスADが「1」となる毎に駆動パルスDPを発生し、駆動パルスDPを3回発生することになる。

30

#### 【0073】

なお、LOOPデータの値が「1」である場合には、図3でのクロック11～18のタイミングの期間のように、アドレス発生回路1から順次インクリメントされるアドレスADが発生される状態となり、メモリ2での駆動パルスDPのデータ格納エリアでの適宜のアドレスで“H”的データを格納しておくことにより、適宜のタイミングで駆動パルスDPをメモリ2から出力させることができることになる。

40

#### 【0074】

以上のようにして、この第1の実施形態では、メモリ2の格納されているLENデータ、LOOPデータ、RETURNデータがアドレス発生回路1からのアドレスADに応じて読み出され、これら読み出されたこれらデータに応じてアドレス発生回路1からのアドレスADが制御されることにより、メモリ2からそこに格納されているデータに応じた所望のパターンの駆動パルスDPを得ることができる。

#### 【0075】

そして、一定周期の駆動パルスDPを連続して発生させる場合には、メモリ2の同じアドレスを繰り返し読み出すことが可能であるから、同じパルスパターン、周期やパルス幅が一定の駆動パルスを繰り返し読み出すことが可能となって、かかる駆動パルスを、僅か

50

なメモリ容量を利用して、発生させることができ、メモリの使用効率が大幅に向ふする。

#### 【0076】

また、この第1の実施形態によると、異なるパルスパターンの複数種のパルス列からなる駆動パルスを発生させるにしても、夫々のパルスパターンのパルス列のデータをメモリ2の格納するだけで発生させることができ、しかも、夫々、パルスパターンのパルス列を発生させるためのデータを格納するに要するメモリ容量は、上記のように、少なくて済むし、また、かかるデータを容易に追加格納することが可能であるから、回路構成を変更することなく、異なるパルスパターンの駆動パルスや、種々のパルスパターンのパルス列からなる変化点の数が異なる駆動パルスを使用する機器にも、適用可能である。即ち、任意のパルスパターンの駆動パルスを用いる機器に対して、この第1の実施形態は、回路構成を変更することなく、適用可能である。10

#### 【0077】

ところで、この第1の実施形態では、図2から明らかなように、アドレスADが「1」、「3」のとき、「H」の駆動パルスDPがメモリ2から出力されることになる。このことは、デジタル値であるアドレス値ADの最下位ビットが「1」のとき、「H」の駆動パルスDPが発生することを意味している。

#### 【0078】

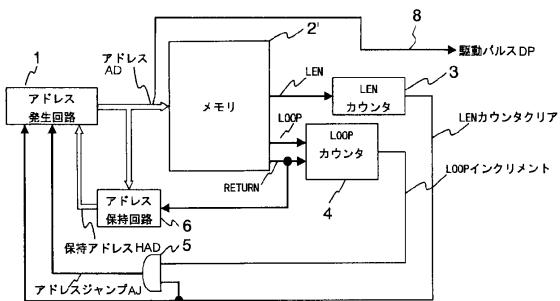

図5はこのことを利用して駆動パルスDPを得ることができるようにした本発明によるタイミングパルス発生装置の第2の実施形態を示すブロック図であって、2'はメモリ、8は信号線であり、図1に対応する部分には同一符号を付けて重複する説明を省略する。20

#### 【0079】

また、図6は図5における各部のデータ、信号を示すタイミング図である。

#### 【0080】

図5において、メモリ2'には、LENデータ、LOOPデータ及びRETURNデータ夫々のデータ格納エリアが設けられ、図1におけるメモリ2と同様、その各アドレス毎に図2に示すLENデータ、LOOPデータ、RETURNデータが格納されている。しかし、このメモリ2'には、駆動パルスDPのデータ格納エリアは設けられていない。

#### 【0081】

この第2の実施形態においても、アドレス発生回路1からのアドレスADに応じたLENデータ、LOOPデータ、RETURNデータが読み出され、かかるデータに応じて、図6に示すように、LENカウンタ3、LOOPカウンタ4、アンドゲート5、アドレス保持回路6及びアドレス発生回路1が図1におけるこれら回路と同様の動作を行なう。30

#### 【0082】

ここで、この第2の実施形態では、アドレス発生回路1からのアドレスADが奇数値のとき、「H」の駆動パルスDPが出力されるように構成されている。即ち、アドレス発生回路1から出力されるアドレスADは複数ビットからなるパラレルデジタルデータであり、アドレスADの信号線の最下位ビット(LSB)から引き出される信号線8が「H」の駆動パルスDPの出力線となっている。アドレスADが奇数値であるときには、アドレスADのLSBは「1」で「H」レベルであり、従って、図6に示すように、アドレスADが値「1」、「3」のとき、「H」の駆動パルスDPが信号線8を通して出力される。40

#### 【0083】

この第2の実施形態では、先の第1の実施形態と同様の効果が得られるが、さらに、実質的には、アドレス発生回路1が駆動パルスDPの発生回路ともなっており、メモリ2'は駆動パルスDPのデータを格納しておく必要がなく、メモリの利用効率がさらに向上して、メモリ2'の使用効率が、図1でのメモリ2に比べて、さらに向上することになる。

#### 【0084】

次に、本発明によるタイミングパルス発生装置を使用する機器の例として、CCD撮像装置について説明する。

#### 【0085】

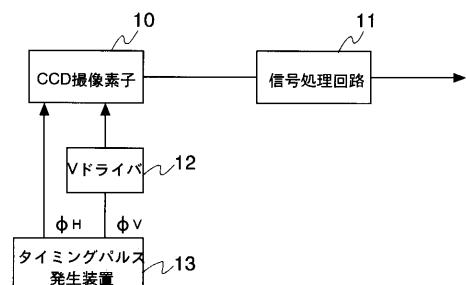

図7は本発明によるタイミングパルス発生装置を使用した本発明による撮像装置の一実50

施形態の要部を示すブロック図であって、10はCCD撮像素子、11は信号処理回路、12はV(垂直)ドライバ、13はタイミングパルス発生装置である。

#### 【0086】

同図において、タイミングパルス発生装置13からは、水平転送用パルス<sub>H</sub>と垂直転送用パルス<sub>V</sub>とが発生される。水平転送用パルス<sub>H</sub>はCCD撮像素子10に供給され、垂直転送用パルス<sub>V</sub>は、Vドライバ12で、例えば、-9V～21Vの電圧に増幅された後、CCD撮像素子10に供給される。CCD撮像素子10では、周知のように、垂直転送用CCD(図示せず)に取り込まれた画素電荷が垂直転送用パルス<sub>V</sub>によって垂直転送され、水平転送用CCD(図示せず)に送られる。この水平転送用CCDでは、垂直転送用CCDから送られてきた画素電荷が水平転送用パルス<sub>H</sub>によって水平転送され、映像信号として、CCD撮像素子10から出力される。この映像信号は、信号処理回路11で処理される。10

#### 【0087】

タイミングパルス発生装置13は、垂直転送用パルス<sub>V</sub>の発生用としてのタイミングパルス発生装置と水平転送用パルス<sub>H</sub>の発生用としてのタイミングパルス発生装置とかなり、これらタイミングパルス発生装置として、上記各実施形態として示す本願発明によるタイミングパルス発生装置が使用される。

#### 【0088】

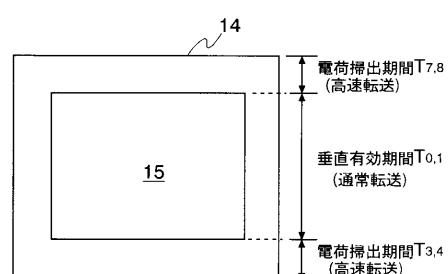

図8は図7におけるCCD撮像素子10の撮像画面での各動作期間の一具体例を示す図である。20

#### 【0089】

同図において、この具体例では、撮像画面14の一部を実際に撮像画面を得るための有効領域15とする。この有効領域15がアスペクト4:3の画面領域である。この有効領域15での電荷が有効な電荷として取り込まれ、かかる有効な電荷からなる信号が、CCD撮像素子10の出力映像信号として、信号処理回路11に供給される。そして、撮像画面14でのこの有効領域15を除いた領域での電荷は、破棄される。

#### 【0090】

CCD撮像素子10の垂直転送用CCDでの垂直転送についてみると、有効領域15での電荷を読み取る垂直有効期間T<sub>0,1</sub>では、通常速度による通常転送が行なわれ、この有効領域15以外の領域での電荷を掃き出す電荷掃出期間T<sub>7,8</sub>、T<sub>3,4</sub>では、高速転送が行なわれる。電荷掃出期間T<sub>7,8</sub>は、センサ(光電変換素子)からの電荷の読み出しに続いて電荷を掃き出しを行なう期間であり、また、電荷掃出期間T<sub>3,4</sub>は、垂直有効期間T<sub>0,1</sub>後に電荷を掃き出しを行なう期間である。30

#### 【0091】

なお、1フィールドについてみると、垂直有効期間T<sub>0,1</sub>は250ライン(水平走査線)分の期間であり、電荷掃出期間T<sub>7,8</sub>と電荷掃出期間T<sub>3,4</sub>との合計は一定のライン数分の期間(例えば、100ライン)である。このように、映像信号を得るための有効領域15を撮像画面14の一部としたのは、この有効領域15を撮像画面14内で上下、左右に移動できるようにするためであり、これにより、手ぶれなどによる再生画面の揺れを防止できるようにしている。40

#### 【0092】

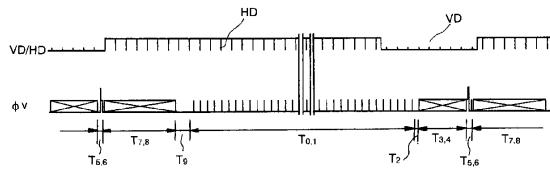

図9は図8に示す撮像画面14についての垂直転送のための1フィールド期間での垂直転送用パルス<sub>V</sub>の一具体例を示す図であって、VD(垂直同期信号)/HD(水平同期信号)のタイミングと対応させて示している。

#### 【0093】

同図において、期間T<sub>0,1</sub>は、図8における有効領域15での画素を垂直転送する垂直有効期間T<sub>0,1</sub>であり、このときの垂直転送用パルス<sub>V</sub>は画素を水平転送用CCDに転送するための通常転送を行なうものである。この垂直有効期間T<sub>0,1</sub>に続いて、“L”的期間T<sub>2</sub>が設けられ、これに続いて期間T<sub>3,4</sub>が設けられている。この期間T<sub>3,4</sub>は、図8における撮像画面14での有効領域15よりも下部の領域に対する電荷掃き出しのための垂50

直転送期間、即ち、電荷掃出期間  $T_{3,4}$  であり、この電荷掃出期間  $T_{3,4}$  の垂直転送用パルス  $v$  は画素を高速転送するものである。

#### 【0094】

この電荷掃出期間  $T_{3,4}$  に続く期間  $T_{5,6}$  は、各センサから垂直転送用 CCD に電荷を転送する期間である。次の期間  $T_{7,8}$  は、図 8 における撮像画面 14 での有効領域 15 よりも上部の領域に対する電荷掃き出しのための垂直転送期間、即ち、電荷掃出期間  $T_{7,8}$  であり、この電荷掃出期間  $T_{7,8}$  の垂直転送用パルス  $v$  は画素を高速転送するものである。この電荷掃出期間  $T_{7,8}$  が終了すると、“L”の期間  $T_9$  を経て次の上記垂直有効期間  $T_{0,1}$  に入る。

#### 【0095】

以上が 1 フィールド (NTSC 方式の場合、262.5H) 期間での垂直転送用パルス  $v$  の割り当てであるが、垂直転送用パルス  $v$  の発生装置として図 1 または図 5 に示すタイミングパルス発生装置を用いる場合、メモリ 2,2' に後述するデータを格納することにより、期間  $T_{0,1}$ 、 $T_{3,4}$ 、 $T_{5,6}$ 、 $T_{7,8}$  毎にパルスパターン（即ち、周期やパルス幅など）が異なる一連のパルス列からなる垂直転送用パルス  $v$  が得られる。

#### 【0096】

図 10 は図 9 に示す垂直転送用パルス  $v$  を発生するための図 1 に示す第 1 の実施形態におけるメモリ 2 の各データ格納エリアでのデータを模式的に示す図である。

#### 【0097】

同図において、垂直有効期間  $T_{0,1}$  では、メモリ 2 の読み出アドレスを「0」、「1」とし、読み出アドレスが「1」のときに RETURN データを“1”とし、LOOP データを値「250」として、アドレス「0」、「1」でのデータ読み出しを 5 クロック周期（値「2」と「3」の LEN データ）5T で 250 回繰り返すものとしている。アドレス「2」のとき、“H”の駆動パルスが読み出され、この垂直有効期間  $T_{0,1}$  では、250 回駆動パルス（垂直転送用パルス  $v$ ）が発生することになる。

#### 【0098】

期間  $T_2$  では、メモリ 2 の読み出アドレスを「2」とし、RETURN データ、LOOP データを夫々値「1」として、アドレス「2」での“L”的データ（駆動パルス）を 1 回読み出す。この期間長は、LEN データ = 「4」であることから、4 クロック周期の 4T である。

#### 【0099】

また、電荷掃出期間  $T_{3,4}$  と電荷掃出期間  $T_{7,8}$ との合計水平ライン数を 100 としており、そのうちの n 水平ラインは電荷掃出期間  $T_{7,8}$  で電荷の掃出しが行なわれ、残りの（100 - n）水平ラインは電荷掃出期間  $T_{3,4}$  で電荷の掃出しが行なわれるものとしている。

#### 【0100】

そこで、電荷掃出期間  $T_{3,4}$  では、メモリ 2 の読み出アドレスを「3」、「4」とし、読み出アドレスが「4」のときに RETURN データを“1”とし、LOOP データを値「100 - n」として、アドレス「3」、「4」でのデータ読み出しを 4 クロック周期（値「2」と「2」の LEN データ）4T で（100 - n）回繰り返すものとしている。アドレス「3」のとき、“H”的駆動パルスが発生されるから、この電荷掃出期間  $T_{3,4}$  では、（100 - n）回高速に駆動パルス（垂直転送用パルス  $v$ ）が発生することになる。また、電荷掃出期間  $T_{7,8}$  では、メモリ 2 の読み出アドレスを「7」、「8」とし、読み出アドレスが「8」のときに RETURN データを“1”とし、LOOP データを値「n」として、アドレス「7」、「8」でのデータ読み出しを 4 クロック周期（値「2」と「2」の LEN データ）4T で n 回繰り返すものとしている。アドレス「7」のとき、“H”的駆動パルスが発生されるから、この電荷掃出期間  $T_{7,8}$  では、n 回高速に駆動パルス（垂直転送用パルス  $v$ ）が発生することになる。

#### 【0101】

期間  $T_{5,6}$  では、メモリ 2 の読み出アドレスを「5」、「6」とし、読み出アドレスが「6」のときに RETURN データを“1”とし、LOOP データを値「1」として、アドレス「5」、

10

20

30

40

50

「6」でのデータ読み出しを1回行なう。この場合、アドレス「5」のとき、「H」の駆動パルスDPが発生し、これがセンサから垂直転送用CCDに電荷を送るのに用いられる。

#### 【0102】

期間 $T_9$ では、メモリ2の読み出アドレスを「9」とし、RETURNデータを値「3」、LOOPデータを値「1」として、アドレス「9」での“L”のデータ（駆動パルス）を1回読み出す。この期間長は、LENデータ＝「3」であることから、3クロック周期の $3T$ である。

#### 【0103】

図11により、図10に示すデータをもとにしたときの図7におけるタイミングパルス発生装置13から発生される垂直転送用パルス $\nu$ の、一例として、垂直有効期間 $T_{0,1}$ から電荷掃出期間 $T_{3,4}$ へ移る部分を示す。

10

#### 【0104】

このようにして、タイミングパルス発生装置でのメモリに格納されたデータに応じて駆動パルスを得ることができるものであって、かかるメモリに所望とするデータを格納することにより、垂直転送用パルス $\nu$ などのように、異なるパルスパターンのパルス列からなる一連の所望とする駆動パルスを発生させることができ、周期性を持つパルス列もわずかなメモリ容量を使用するだけで発生させることができるし、また、すでにデータが格納されているメモリにデータを追加することにより、新たなパルスパターンのパルス列を追加発生させることも可能である。

#### 【図面の簡単な説明】

20

#### 【0105】

【図1】本発明によるタイミングパルス発生装置の第1の実施例を示すブロック図である。

。

【図2】図1におけるメモリの各データ格納エリアでのデータを模式的に示す図である。

【図3】図1に示す第1の実施形態の一動作例での各部のデータ、パルス信号を示すタイミング図である。

【図4】図1に示す第1の実施形態の他の動作例での各部のデータ、パルス信号を示すタイミング図である。

【図5】本発明によるタイミングパルス発生装置の第2の実施例を示すブロック図である。

30

【図6】図5に示す第2の実施形態の一動作例での各部のデータ、パルス信号を示すタイミング図である。

【図7】本発明による撮像装置の一実施形態の要部を示すブロック図である。

【図8】図7におけるCCD撮像素子の撮像画面での各動作期間の一具体例を示す図である。

【図9】図8に示す撮像画面についての垂直転送のための1フィールド期間での垂直転送用パルス $\nu$ の一具体例を示す図である。

【図10】図9に示す垂直転送用パルス $\nu$ を発生するための図1に示す第1の実施形態におけるメモリに格納されているデータを模式的に示す図である。

【図11】図10に示すデータをもとにしたときの垂直有効期間 $T_{0,1}$ から電荷掃出期間 $T_{3,4}$ へ移るときの垂直転送用パルス $\nu$ を示すタイミング図である。

40

【図12】タイミングパルス発生装置の一従来例を示すブロック図である。

【図13】図12での各デコーダの出力パルスとマルチブレクサから出力される駆動パルスを示すタイミング図である。

【図14】タイミングパルス発生装置の他の従来例を示すブロック図である。

【図15】図14におけるアドレス発生回路からのアドレスに対するメモリの出力パルス及び駆動パルスを示すタイミング図である。

#### 【符号の説明】

#### 【0106】

- 2, 2' メモリ

3 LENカウンタ

4 LOOPカウンタ

5 アンドゲート

6 アドレス保持回路

7 出力端子

8 信号線

10 C C D 撮像素子

11 信号処理回路

12 V(垂直)ドライバ

13 タイミングパルス発生装置

【図1】

【図2】

| アドレス | LEN | LOOP | RETURN | 駆動パルス |

|------|-----|------|--------|-------|

| 0    | 2   | 2    | "0"    | "L"   |

| 1    | 3   | 2    | "1"    | "H"   |

| 2    | 4   | 1    | "0"    | "L"   |

| 3    | 2   | 1    | "0"    | "H"   |

| 4    | 2   | 1    | "0"    | "L"   |

図2

【図3】

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図 9】

【図 11】

図 9

【図 10】

図 10

| アドレス | LEN | LOOP  | RETURN | 駆動パルス |

|------|-----|-------|--------|-------|

| 0    | 2   | 250   | "0"    | "L"   |

| 1    | 3   | 250   | "1"    | "H"   |

| 2    | 4   | 1     | "0"    | "L"   |

| 3    | 2   | 100-n | "0"    | "H"   |

| 4    | 2   | 100-n | "1"    | "L"   |

| 5    | 2   | 1     | "0"    | "H"   |

| 6    | 2   | 1     | "1"    | "L"   |

| 7    | 2   | n     | "0"    | "H"   |

| 8    | 2   | n     | "1"    | "L"   |

| 9    | 3   | 1     | "0"    | "L"   |

図 11

【図 12】

図 12

【図 14】

図 14

【図 13】

図 13

図 15

---

フロントページの続き

(56)参考文献 特開平10-257391(JP,A)

特開2001-339645(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/378