(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4008699号

(P4008699)

(45) 発行日 平成19年11月14日(2007.11.14)

(24) 登録日 平成19年9月7日(2007.9.7)

(51) Int.C1.

F 1

G06F 9/48 (2006.01)

G06F 11/34 (2006.01)G06F 9/46 452 G

G06F 11/34 S

請求項の数 6 (全 10 頁)

(21) 出願番号 特願2001-348542 (P2001-348542)

(22) 出願日 平成13年11月14日 (2001.11.14)

(65) 公開番号 特開2002-215581 (P2002-215581A)

(43) 公開日 平成14年8月2日 (2002.8.2)

審査請求日 平成16年10月27日 (2004.10.27)

(31) 優先権主張番号 09/745,949

(32) 優先日 平成12年12月23日 (2000.12.23)

(33) 優先権主張国 米国(US)

(73) 特許権者 398038580

ヒューレット・パッカード・カンパニー

HEWLETT-PACKARD COMPANY

アメリカ合衆国カリフォルニア州パロアルト ハノーバー・ストリート 3000

(74) 代理人 100081721

弁理士 岡田 次生

(74) 代理人 100105393

弁理士 伏見 直哉

(74) 代理人 100111969

弁理士 平野 ゆかり

最終頁に続く

(54) 【発明の名称】動作中のコンピュータシステムにおけるサービスレベル推定のための方法

## (57) 【特許請求の範囲】

## 【請求項 1】

応答時間を推定するためにコンピュータで実行可能な方法であって、

コンピュータシステム上で実行されることが予想されるトランザクション要求を代表するものとして代表的なトランザクション要求を選択するステップと、

負荷が軽いコンピュータシステム上で前記代表的なトランザクション要求の応答時間である、第1の応答時間を測定するステップと、

前記代表的なトランザクション要求の第1のCPU利用率を測定するステップと、

少なくとも2つの同時発生する代表的なトランザクション要求が前記コンピュータシステムにおいてアクティブであり、前記コンピュータシステムにかかる負荷は、代表的なトランザクション要求を除けば軽い状況において、前記少なくとも2つの同時発生する代表的なトランザクション要求に対する平均応答時間である、第2の応答時間を測定するステップと、

前記第1の応答時間および前記第2の応答時間を含むデータから、同時発生する代表的なトランザクション要求の数と前記同時発生する代表的なトランザクション要求に対する応答時間との関係を求めるステップと、

前記コンピュータシステムが所与の動作負荷で動作している間に、第2のCPU利用率を測定するステップと、

前記所与の動作負荷の下で、同時発生するトランザクション要求の実際の数を特定するステップと、

10

代表的なトランザクションの有効数を計算するステップであって、前記代表的なトランザクションの有効数は、前記同時発生するトランザクション要求の実際の数に、前記第2のCPU利用率を掛け合わせ、前記第1のCPU利用率で割った値に等しい、該計算するステップと、

前記代表的なトランザクションの有効数を、同時発生する代表的なトランザクション要求の数として、前記関係から平均システム応答時間を推定するステップと、

推定された平均システム応答時間を報告するステップと、を含む方法。

#### 【請求項2】

応答時間を推定するための方法ステップを実行するために、コンピュータによって実行可能な命令からなるソフトウェアプログラムを具体的に具現する、コンピュータによって読み取り可能なプログラム記憶媒体であって、前記方法は、

10

コンピュータシステム上で実行されることが予想されるトランザクション要求を代表するものとして代表的なトランザクション要求を選択するステップと、

負荷が軽いコンピュータシステム上で前記代表的なトランザクション要求の応答時間である、第1の応答時間を測定するステップと、

前記代表的なトランザクション要求の第1のCPU利用率を測定するステップと、

少なくとも2つの同時発生する代表的なトランザクション要求が前記コンピュータシステムにおいてアクティブであり、前記コンピュータシステムにかかる負荷は、代表的なトランザクション要求を除けば軽い状況において、前記少なくとも2つの同時発生する代表的なトランザクション要求に対する平均応答時間である、第2の応答時間を測定するステップと、

20

前記第1の応答時間および前記第2の応答時間を含むデータから、同時発生する代表的なトランザクション要求の数と前記同時発生する代表的なトランザクション要求に対する応答時間との関係を求めるステップと、

前記コンピュータシステムが所与の動作負荷で動作している間に、第2のCPU利用率を測定するステップと、

前記所与の動作負荷の下で、同時発生するトランザクション要求の実際の数を特定するステップと、

代表的なトランザクションの有効数を計算するステップであって、前記代表的なトランザクションの有効数は、前記同時発生するトランザクション要求の実際の数に、前記第2のCPU利用率を掛け合わせ、前記第1のCPU利用率で割った値に等しい、該計算するステップと、

30

前記代表的なトランザクションの有効数を、同時発生する代表的なトランザクション要求の数として、前記関係から平均システム応答時間を推定するステップと、

推定された平均システム応答時間を報告するステップと、を含むコンピュータによって読み取り可能なプログラム記憶媒体。

#### 【請求項3】

平均システム応答時間に対する値であって、当該値を超えた場合にコンピュータシステムは有意に劣化していると判断される値を指定するステップと、コンピュータシステムが有意に劣化していると判断された場合に、その状況を報告するステップをさらに含む、請求項1に記載のコンピュータで実行可能な方法。

40

#### 【請求項4】

コンピュータシステムが有意に劣化していると報告された場合に、さらなる応答時間の劣化を防ぐための動作を行うステップをさらに含む請求項3に記載のコンピュータで実行可能な方法。

#### 【請求項5】

前記方法が、平均システム応答時間に対する値であって、当該値を超えた場合にコンピュータシステムは有意に劣化していると判断される値を指定するステップと、コンピュータシステムが有意に劣化していると判断された場合に、その状況を報告するステップをさらに含む、請求項2に記載のコンピュータによって読み取り可能なプログラム記憶媒体。

50

**【請求項 6】**

前記方法が、コンピュータシステムが有意に劣化していると報告された場合に、さらなる応答時間の劣化を防ぐための動作を行うステップをさらに含む請求項 5 に記載のコンピュータによって読み取り可能なプログラム記憶媒体。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は全般にコンピュータシステムに関し、より詳細には、コンピュータシステムがそのコンピュータシステム上で実行されるプロセスを提供するサービスレベルの推定に関する。 10

**【0002】****【従来の技術】**

特定のサービスに対して、最近のコンピュータシステムの管理者が関心を寄せる最も重要な測定基準は、そのコンピュータシステムが、そのコンピュータシステム上で実行されるプロセスからの、サービスのための要求を達成するのに要する時間である。この時間は応答時間あるいはサービスレベルと呼ばれ、多くの場合に、同じプロセスによる多数のそのような要求を平均したものである。よく見られるように、応答時間の測定は、ソースコードが利用できない応用形態においては、不可能ではないにしても困難であるという問題がある。応答時間は、稼動コンピュータ時間および全ての待機時間の両方を含む、コンピュータシステムがその要求に対してサービスを提供するのに要する全クロック時間である。 20

**【0003】**

この問題に対する1つの解決策は、「ダミー」トランザクションを作成し、その後、これらの応答時間を測定することである。しかしながら、この技術はかなり不正確であり、実際の応答時間を過小評価する傾向がある。ダミートランザクション要求の結果から生じるデータは、同じトランザクションが何度も要求される度にキャッシュされる傾向があるので、ユーザーのデータはキャッシュされる場合もあり、されない場合もある。こうして、ダミートランザクションに対する応答時間は、多くの場合に、通常の動作において観測されることになる応答時間より非常に速くなる。

**【0004】****【発明が解決しようとする課題】**

したがって、本発明の目的は、そのプロセスのためのソースコードが利用できない場合であっても、コンピュータシステム上で実行されるプロセスに対する応答時間に対して、より典型的な値を取得するための方法を提供することである。 30

**【0005】****【課題を解決するための手段】**

本特許明細書は、動作中のコンピュータシステムにおけるサービスレベルの推定値を得るために新規の方法に関する。この推定値は、所定のレベルの有意なサービスレベルの劣化と比較され、それによりシステム管理者にコンピュータシステムの動作状態の測定値を提供することができる。そのような測定値を得るために以前の方法は、ダミートランザクションを作成し、その応答時間を測定することに基づいていた。データキャッシュ処理に起因して、この技術によって得られた値は多くの場合に取得可能な値よりも速くなる。 40

**【0006】**

典型的な実施形態では、ユーザから以下の入力を要求する方法が開示される。（1）典型的なトランザクションの最適な応答時間：最適な応答時間は、負荷が軽いシステム上で典型的なトランザクションを計時することにより測定することができる。この値は、最適な応答時間として定義され、典型的なトランザクション（単数または複数）のためにコンピュータシステムから予想することができる最も速い応答時間である。別法では、いくつかの典型的なトランザクションの応答時間を負荷が軽いシステム上で測定することもでき、それらの結果を合成した平均値が、最適な応答時間として特定される。より負荷が重いシステム上で測定すれば、応答時間はさらに長くなるであろう。（2）典型的なトランザクションの応答時間：典型的なトランザクションの応答時間は、そのトランザクションが実行されるまでの時間である。 50

ションに必要とされる中央演算装置（C P U）利用率：この値は、実際のC P U利用率を測定する間に、所定の数のトランザクションを実行することによって測定することもできる。（3）システム性能がある所定の値だけ劣化する前に、典型的なトランザクションのために完了されることがある、同時発生するトランザクションの数。

#### 【0007】

コンピュータシステムが動作する際に、コンピュータシステムは種々の負荷状態を受ける。本特許明細書において開示される方法を用いると、これらの変化する負荷状態下で割り当てられるタスクを完了する際に、システムの有効性を測る(gage)ためにシステム管理者が用いることができる、推定されたシステム応答時間が得られる。システムが動作するのに応じて、2つの項目が測定される。それは、（1）未処理のトランザクション要求の数、および（2）システムC P U利用率である。ユーザから3つの入力が与えられると、未処理の要求の数およびC P U利用率を用いて、エンドユーザが経験する応答時間を近似することができる。10

#### 【0008】

本発明の他の態様および利点は、例を用いて本発明の原理を示す添付の図面とともに取り上げられる、以下に記載される詳細な説明から明らかになるであろう。

#### 【0009】

##### 【発明の実施の形態】

添付の図面は、本発明をより十分に記載するために用いられ、かつ本発明およびその固有の利点をさらに理解するために当業者によって用いられることができる視覚的な表現を提供する。これらの図面では、同様の参照番号は対応する要素を特定する。20

#### 【0010】

例示するための図面において示されるように、本特許明細書は、動作中のコンピュータシステムにおいてサービスレベルの推定値を得るために新規の方法に関する。この推定値は、所定のレベルの有意なサービスレベル劣化と比較され、それにより、システム管理者に、コンピュータシステムの動作状態の測定値を提供することができる。そのような測定値を得るために以前の方法は、ダミートランザクションを作成し、その応答時間を測定することに基づいていた。データキャッシュ処理に起因して、この技術によって得られた値は多くの場合に取得可能な値よりも速くなる。

#### 【0011】

図面に関する以下の詳細な説明およびいくつかの図面では、同様の要素は、同様の参照番号で特定される。30

#### 【0012】

代表的な実施形態では、ユーザから以下の入力を要求する方法が開示される。

（1）典型的なトランザクションの最適な応答時間：最適な応答時間は、負荷が軽いシステム上で典型的なトランザクションを計時することにより測定することができる。この値は、最適な応答時間になるように規定され、典型的なトランザクション（単数または複数）のためにコンピュータシステムから予想することができる最も速い応答時間である。別法では、いくつかの典型的なトランザクションの応答時間を負荷が軽いシステム上で測定することもでき、それらの結果を合成した平均値が、最適な応答時間として特定される。より負荷が重いシステム上で測定すれば、応答時間はさらに長くなるであろう。（2）典型的なトランザクションに必要とされる中央演算装置（C P U）利用率：この値は、実際のC P U利用率を測定する間に、所定の数のトランザクションを実行することによって測定することもできる。（3）システム性能がある所定の値だけ劣化する前に、典型的なトランザクションのために完了されることがある、同時発生するトランザクションの数。40

#### 【0013】

コンピュータシステムが動作する際に、コンピュータシステムは種々の負荷状態を受ける。本特許明細書において開示される方法を用いると、これらの変化する負荷状態下で割り当てられるタスクを完了する際に、システムの有効性を測るためにシステム管理者が用いることができる、推定されたシステム応答時間が得られる。システムが動作するのに応じ50

て、2つの項目が測定される。それは、(1)未処理のトランザクション要求の数、および(2)システムCPU利用率である。ユーザから3つの入力が与えられると、未処理の要求の数およびCPU利用率を用いて、エンドユーザが経験する応答時間を近似することができる。

#### 【0014】

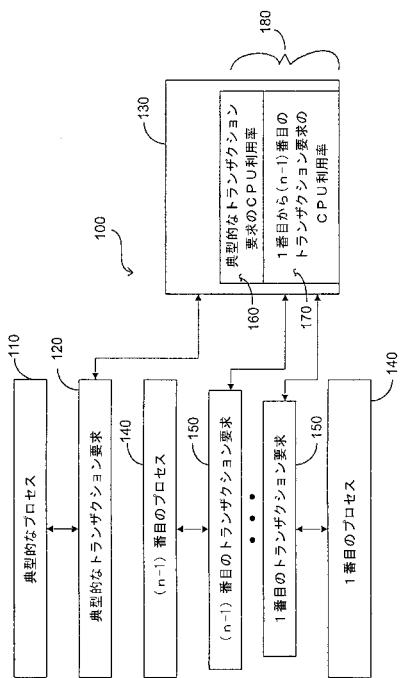

図1は、本特許明細書の種々の代表的な実施形態に記載されるコンピュータシステム100を示す図である。図1の例では、典型的なプロセス110が、中央演算装置(CPU)130の典型的なトランザクション要求120を作成する。プロセス110およびそのトランザクション要求120は、コンピュータシステム100上で実行されることが予想されるプロセスおよびトランザクション要求を代表するもの、あるいは典型的なものとしてシステム管理者によって選択される。いかなる特定の時点においても、典型的なトランザクション要求120はCPU130のために作成されているとは限らず、典型的なプロセス110はコンピュータシステム100上においてアクティブであるとは限らない。また図1には、1~(n-1)番目のプロセス140として示される他のプロセス140も示されており、そのプロセスは、この例ではコンピュータシステム100においてアクティブであり、1~(n-1)番目のトランザクション要求150としてそれぞれ示される未処理の他のトランザクション要求150を有する。各トランザクション要求120、150はCPU130のリソースを消費する。詳細には、典型的なトランザクション要求120は、第1のCUP利用率160とも呼ばれる、典型的なCUP利用率160を消費する。ここで典型的なCUP利用率160は、典型的なトランザクション要求120を達成する際に用いられるCPUの部分であり、また他の未処理のトランザクション要求150は他のCPU利用率170を消費し、他のCPU利用率170は、1~(n-1)番目のトランザクション要求150である他のトランザクション要求150を達成する際に用いられるCPUの部分である。消費される全CPUリソースは、全CPU利用率180として図1に示される。

#### 【0015】

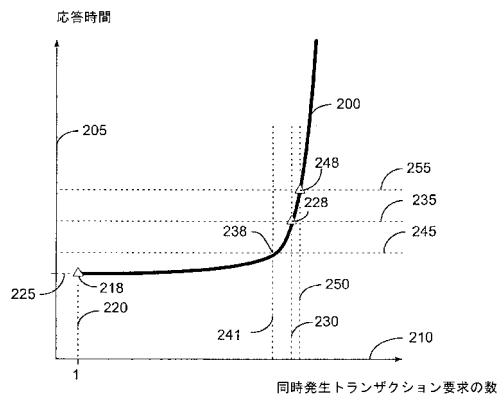

図2は、本特許明細書の種々の代表的な実施形態において記載されるようなコンピュータシステム100における、応答時間205対同時発生トランザクション要求210のグラフを示す図である。図2の曲線200は、システム応答時間205のいくつかの測定を、同時発生するトランザクション要求210の種々の数に対して平均することにより作成されており、トランザクション要求210は、コンピュータシステム100上で通常実行される典型的なものである。そのような測定を表現する多数の手段が存在しており、図2はこれらの手段のうちの1つである。他の手段には、たとえば、数値からなる表がある。図2の曲線200は、離散した1組の測定されたデータ点に対する近似を表すことは当業者には理解されよう。

#### 【0016】

第1の点218は、負荷が軽いコンピュータシステム100で行われた1つ(220)の典型的なトランザクション要求120の測定を表す。プロットされた応答時間225は、ここでは第1の応答時間225とも呼ばれ、典型的なトランザクション要求120に対する最適な応答時間225である。

#### 【0017】

曲線200は、必要に応じて、少なくとも1つの付加的な点228の測定を行うことにより延長されており、プロットされた応答時間205は、ここでは第2の応答時間235とも呼ばれ、2つ以上の典型的なトランザクション要求120を含む第2の数230の同時発生する典型的なトランザクション要求120に対する平均応答時間である。

#### 【0018】

第3の点238の意義、同時発生するトランザクション要求120の有効数241、およびここでは推定された応答時間245とも呼ばれる第3の応答時間245は、図3に関する説明とともに以下に説明されるであろう。

#### 【0019】

10

20

30

40

50

同時発生する典型的なトランザクション要求 210 がさらに増加するような、曲線 200 上のある点では、応答時間は有意に劣化し始め、第 4 の点 248 によって示されるように、第 4 の数 250 の典型的なトランザクション要求 120 が同時発生する結果として、第 4 の応答時間とも呼ばれる有意に劣化した応答時間 255 になるまで、ますます長くなる。この有意に劣化した応答時間 255 は、関心のあるレベルとしてシステム管理者によって規定され、さらに応答時間が劣化するのを防ぐために適当な動作を要することになる時間であり、その適当な動作は、たとえば、現在の作業負荷が低減するまで、コンピュータシステム 100 にさらにアクセスが行われるのを制限する動作である。この状況が発生し続ける場合には、システム管理者は、そのような再発生を低減するようにシステム 100 に対する拡張を計画することができる。

10

#### 【0020】

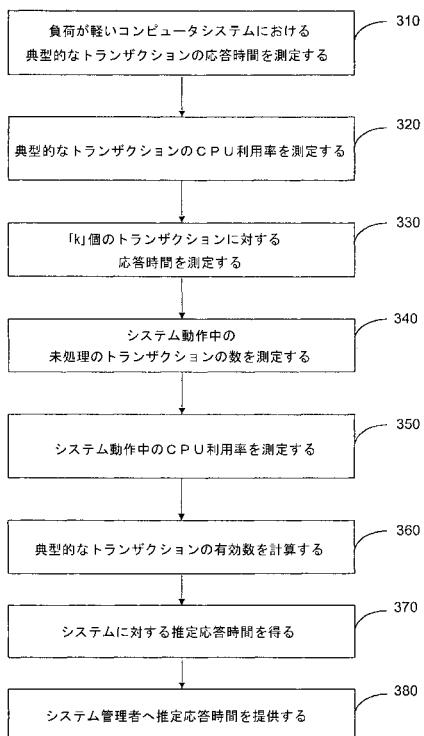

図 3 は、本特許明細書の種々の代表的な実施形態において記載されるようなシステム 100 に対する推定された応答時間を得るための方法の流れ図である。ブロック 310 では、最適な応答時間 225 が測定される。最適な応答時間 225 は、図 2 の説明において記載されるような、負荷が軽いコンピュータシステム 100 における 1 つの典型的なトランザクション要求 120 の応答時間である。その後、ブロック 310 はブロック 320 に制御を渡す。

#### 【0021】

ブロック 320 では、第 1 の CPU 利用率 160 が測定される。第 1 の CPU 利用率 160 は、1 つの典型的なトランザクション要求 120 に対する CPU 利用率である。その後、ブロック 320 はブロック 330 に制御を渡す。

20

#### 【0022】

ブロック 330 では、「k」個の典型的なトランザクション要求 120 に対する応答時間が測定される。ただし「k」は 1 より大きい数で、図 2 の第 2 の数 230 の値であり、測定された応答時間は第 2 の応答時間 235 である。その後、ブロック 330 はブロック 340 に制御を渡す。

#### 【0023】

ブロック 340 では、図には示されていないが、第 3 の数 240 とも呼ばれる、システム 100 の動作中の未処理のトランザクション要求の数がカウントされる。その後、ブロック 340 はブロック 350 に制御を渡す。

30

#### 【0024】

ブロック 350 では、システム 100 の動作中の全 CPU 利用率 180 が測定される。その後、ブロック 350 はブロック 360 に制御を渡す。

#### 【0025】

ブロック 360 では、動作時のシステム 100 に対する典型的なトランザクション要求 120 の有効数 241 が計算される。この計算は、たとえば、同時発生するトランザクション要求の実際の数を、全 CPU 利用率 180 と掛け合わせ、第 1 の CPU 利用率 160 (1 つの典型的なトランザクション要求 120 に対する CPU 利用率) で割ることにより実行することができる。その後、ブロック 360 はブロック 370 に制御を渡す。

40

#### 【0026】

ブロック 370 では、システム 100 に対する推定された応答時間 245 が、システム 100 の動作中の未処理のトランザクションの有効数 241 の第 3 の点 238 における交点によって得られ、図 2 の曲線 200 が得られる。その後、ブロック 370 はブロック 380 に制御を渡す。

#### 【0027】

ブロック 380 では、コンピュータシステム 100 の動作条件に対して推定された応答時間 245 が決定者に提供される。その決定者はここではシステム管理者とも呼ばれ、行われる決定は、たとえば、より許容可能なレベルまで応答時間を低減するための、コンピュータシステム 100 へのアクセスあるいはパラメータの変更を含むことができる。その決定は、変更しないことを含むこともできる。

50

**【0028】**

図2の曲線200をさらに正確に表現するために、より多くのデータ点を得るためにには、ブロック340および350が、種々の数の同時発生する典型的なトランザクション要求120に対して何度も繰り返されるであろう。

**【0029】**

本発明の態様を以下に例示する。

**【0030】**

1. 応答時間(205)を推定するためにコンピュータで実行可能な方法であって、第1の応答時間(225)を測定するステップであって、前記第1の応答時間(225)は負荷が軽いコンピュータシステム(100)上の典型的なトランザクション要求(120)によって用いられる第1のCPU容量(160)を測定するステップとを含み、少なくとも2つの同時発生する前記典型的なトランザクション要求(120)が前記コンピュータシステム(100)においてアクティブであり、前記コンピュータシステム(100)にかかる負荷は、前記典型的なトランザクション要求(120)を除けば軽く、また、第2の応答時間(235)を測定するステップであって、前記第2の応答時間(235)は、第2の数(230)の同時発生する前記典型的なトランザクション要求(120)に対する平均応答時間である、該測定するステップを含み、前記コンピュータシステム(100)が所与の動作負荷で動作している間に、全CPU利用率(180)を測定するステップと、第3の数(240)を特定するステップであって、前記第3の数(240)は同時発生する前記典型的なトランザクション要求(210)の数である、該特定するステップと、上記の結果を用いて、動作負荷条件下において、1つの前記典型的なトランザクション要求(120)に対する推定された応答時間(245)を取得するステップと、前記推定された応答時間(245)を報告するステップとを含む方法。10

**【0031】**

2. 前記推定された応答時間(245)を取得する前記ステップは、典型的なトランザクションの有効数(241)を計算するステップであって、前記典型的なトランザクションの前記有効数(241)は、アクティブなトランザクション(240)の実際の数に、前記全CPU利用率(180)を掛け合わせ、前記典型的なトランザクションCPU利用率(160)で割った値に等しい、該計算するステップと、前記典型的なトランザクション(120)に対する前記平均応答時間(205)と、前記同時発生するアクティブな典型的なトランザクション(210)の数との対からなる測定値から前記平均応答時間(245)を推定するステップとを含む上記1に記載のコンピュータにより実行される方法。30

**【0032】**

3. 応答時間(205)を推定するための方法ステップを実行するために、コンピュータによって実行可能な命令からなるソフトウェアプログラムを具体的に具現する、コンピュータによって読み取り可能なプログラム記憶媒体であって、前記方法は、第1の応答時間(225)を測定するステップであって、前記第1の応答時間(225)は負荷が軽いコンピュータシステム(100)上の典型的なトランザクション要求(120)の応答時間である、該測定するステップと、前記典型的なトランザクション要求(120)によって用いられる第1のCPU容量(160)を測定するステップとを含み、少なくとも2つの同時発生する前記典型的なトランザクション要求(120)が前記コンピュータシステム(100)においてアクティブであり、前記コンピュータシステム(100)にかかる負荷は、前記典型的なトランザクション要求(120)を除けば軽く、また、第2の応答時間(235)を測定するステップであって、前記第2の応答時間(235)は、第2の数(230)の同時発生する前記典型的なトランザクション要求(120)に対する平均応答時間である、該測定するステップを含み、前記コンピュータシステム(100)が所与の動作負荷で動作している間に、全CPU利用率(180)を測定するステップと、第3の数(240)を特定するステップであって、前記第3の数(240)は同時発生する前記典型的なトランザクション要求(210)の数である、該特定するステップと、上記の結40

果を用いて、動作負荷条件下において、1つの前記典型的なトランザクション要求(120)に対する推定された応答時間(245)を取得するステップと、前記推定された応答時間(245)を報告するステップとを含むコンピュータによって読み取り可能なプログラム記憶媒体。

#### 【0033】

4. 前記推定された応答時間(245)を取得する前記ステップは、典型的なトランザクションの有効数(241)を計算するステップであって、前記典型的なトランザクションの前記有効数(241)は、アクティブなトランザクション(240)の実際の数に、前記全CPU利用率(180)を掛け合わせ、前記典型的なトランザクションCPU利用率(160)で割った値に等しい、該計算するステップと、前記典型的なトランザクション(120)に対する前記平均応答時間(205)と、前記同時発生するアクティブな典型的なトランザクション(210)の数との対からなる測定値から、前記平均応答時間(245)を推定するステップとを含む上記3に記載のコンピュータによって読み取り可能なプログラム記憶媒体。 10

#### 【0034】

#### 【発明の効果】

本特許明細書に記載される方法の代表的な実施形態では、コンピュータシステム100上の負荷が変動する際の、典型的なトランザクション要求120に対する推定された応答時間が開示してきた。

#### 【0035】

本特許明細書に記載される実施形態に関する従来の方法より優れた主な利点は、本発明による方法が、システムリソースの消費を抑えつつ、負荷が変動する際の実際の応答時間をより正確に近似できることである。 20

#### 【0036】

本発明は、その代表的な実施形態に関連して詳細に記載されてきたが、記載された実施形態は例として提供されており、本発明を限定するものではない。特許請求の範囲内から逸脱することなく、記載された実施形態の形態および細部に種々の変更がなされ、均等な実施形態を生み出すこともできることは当業者には理解されよう。

#### 【図面の簡単な説明】

【図1】 本特許明細書の種々の典型的な実施形態において記載されるようなコンピュータシステムの図である。 30

【図2】 本特許明細書の種々の典型的な実施形態において記載されるようなコンピュータシステム上の、応答時間対同時発生トランザクション要求の数のグラフである。

【図3】 本特許明細書の種々の典型的な実施形態において記載されるようなシステムに対する推定された応答時間を得るための方法の流れ図である。

#### 【符号の説明】

- 100 コンピュータシステム

- 120 典型的なトランザクション要求

- 160 第1のCPU利用率

- 180 全CPU利用率

- 205 応答時間

- 210 同時発生するトランザクション要求

- 225 第1の応答時間

- 235 第2の応答時間

- 240 第3の数

- 241 典型的なトランザクションの有効数

40

【図1】

【図2】

【図3】

---

フロントページの続き

(72)発明者 トーマス・エド温ン・トウリッチ・ジュニア

アメリカ合衆国75206テキサス州ダラス、マッコーマス・ブルバード 5903

(72)発明者 ドーグ・グルマン

アメリカ合衆国95610カリフォルニア州シトラス・ハイツ、ダブリン・ウェイ 6019

審査官 間野 裕一

(56)参考文献 特開平10-143401(JP,A)

特開平8-82685(JP,A)

秋月巖,秋月巖のSQL Server解体新書 第10回 DBアプリ開発者必読 SQL

Serverをテストする, Visual Basic magazine, 株式会社翔泳社,

2000年 5月 1日, 第6巻, 第7号, 第175-182頁

(58)調査した分野(Int.Cl., DB名)

G06F 9/48-9/54

G06F 11/34

G06F 15/00