(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7339819号**

**(P7339819)**

(45)発行日 令和5年9月6日(2023.9.6)

(24)登録日 令和5年8月29日(2023.8.29)

(51)国際特許分類

|        |                   |     |        |        |       |

|--------|-------------------|-----|--------|--------|-------|

| H 01 L | 21/301 (2006.01)  | F I | H 01 L | 21/78  | L     |

| H 01 L | 21/3065 (2006.01) |     | H 01 L | 21/78  | B     |

| H 01 L | 29/861 (2006.01)  |     | H 01 L | 21/78  | S     |

| H 01 L | 29/868 (2006.01)  |     | H 01 L | 21/78  | F     |

| H 01 L | 29/872 (2006.01)  |     | H 01 L | 21/302 | 1 0 5 |

請求項の数 8 (全10頁) 最終頁に続く

(21)出願番号 特願2019-161250(P2019-161250)

(22)出願日 令和1年9月4日(2019.9.4)

(65)公開番号 特開2021-40068(P2021-40068A)

(43)公開日 令和3年3月11日(2021.3.11)

審査請求日 令和3年8月25日(2021.8.25)

(73)特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(73)特許権者 317011920

東芝デバイス＆ストレージ株式会社

東京都港区芝浦一丁目1番1号

(74)代理人 110004026

弁理士法人 i X

布谷 伸仁

東京都港区芝浦一丁目1番1号 東芝デ

バイス＆ストレージ株式会社内

(72)発明者 隠塚 信次

東京都港区芝浦一丁目1番1号 東芝デ

バイス＆ストレージ株式会社内

審査官 垣 哲次

最終頁に続く

(54)【発明の名称】 半導体装置の製造方法および半導体装置

**(57)【特許請求の範囲】****【請求項1】**

半導体部と、前記半導体部の裏面上に設けられた第1電極と、前記半導体部の表面上に設けられた第2電極と、を備える半導体装置の製造方法であって、

前記半導体部となる領域を含むウェーハの表面上に、前記第2電極を形成した後、前記ウェーハの裏面を覆う前記第1電極を形成する工程と、

前記半導体部となる領域の外縁に沿って、前記第1電極を選択的に除去した第1溝であって、前記ウェーハ中に位置する部分を含む第1溝を形成する工程と、

前記ウェーハの前記表面における前記半導体部となる領域の外縁に沿って、前記第1溝につながる第2溝を形成し、前記ウェーハを分割する工程と、

を備え、

前記ウェーハの表面に沿った第1方向における前記第2溝の幅は、前記第1溝の前記第1方向の幅よりも狭く形成され、

前記第1溝は、前記ウェーハ内に向かう方向に湾曲した内面を有するように形成され、前記第1溝の前記ウェーハ中に位置する部分の前記第1方向の幅の2分の1は、前記ウェーハの前記裏面に垂直な第2方向において前記裏面から前記ウェーハ中に至る前記第1溝の深さよりも広い半導体装置の製造方法。

**【請求項2】**

前記第1溝は、前記ウェーハの前記裏面に沿った第3方向であって、前記第1方向と交差する第3方向に延伸するように形成され、

前記第2溝は、前記ウェーハの前記表面に沿って、前記第1方向および前記第3方向に延伸するように形成される請求項1記載の製造方法。

**【請求項3】**

前記第1溝は、前記ウェーハの前記裏面側において、前記第1電極および前記半導体部をレーザー照射により選択的に除去することにより形成される請求項1または2に記載の製造方法。

**【請求項4】**

前記第1溝は、前記ウェーハの前記裏面を選択的にエッティングすることにより形成される請求項1または2に記載の製造方法。

**【請求項5】**

前記第2溝は、前記ウェーハをダイシングブレードを用いて切断することにより形成され、

前記ダイシングブレードの厚さは、前記第1溝の前記幅よりも薄い請求項1～4のいずれか1つに記載の製造方法。

**【請求項6】**

前記第2溝は、前記半導体部をドライエッティングにより選択的に除去することにより形成される請求項1～4のいずれか1つに記載の製造方法。

**【請求項7】**

半導体部と、

前記半導体部の裏面上に設けられた第1電極と、

前記半導体部の表面上に設けられた第2電極と、を備え、

前記半導体部は、前記表面につながる第1側面と、前記裏面と前記第1側面とをつなぐ第2側面と、を有し、前記第2側面は、前記半導体部内に向かう方向に湾曲し、前記第1側面および前記裏面に対して傾斜した部分を含み、

前記半導体部の前記裏面に平行な平面視における前記第1側面と前記第1電極との第1間隔は、前記第1側面に平行な平面視における前記第1側面と前記裏面との第2間隔よりも広い半導体装置。

**【請求項8】**

前記半導体部は、第1導電形の第1半導体層と、第2導電形の第2半導体層と、を含み、

前記第2半導体層は、前記第1半導体層と前記第2電極との間に位置し、前記第2電極に電気的に接続された請求項7記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

実施形態は、半導体装置の製造方法および半導体装置に関する。

**【背景技術】**

**【0002】**

半導体装置の製造過程では、ウェーハを半導体チップに個片化するために、例えば、ダイサーカットなどの機械加工を用いることが多い。しかしながら、このような機械加工により形成される半導体チップは、バリや欠けなどを含み、製造歩留りを低下させる場合がある。

**【先行技術文献】**

**【特許文献】**

**【0003】**

**【文献】特開平5-102300号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

実施形態は、半導体装置の製造歩留りを向上させることができ可能な製造方法および半導体装置を提供する。

10

20

30

40

50

**【課題を解決するための手段】**

**【0005】**

実施形態に係る半導体装置は、半導体部と、前記半導体部の裏面上に設けられた第1電極と、前記半導体部の表面上に設けられた第2電極と、を備える。前記半導体装置の製造方法は、前記半導体部となる領域を含むウェーハの表面上に、前記第2電極を形成した後、前記ウェーハの裏面を覆う前記第1電極を形成する工程と、前記半導体部となる領域の外縁に沿って、前記第1電極を選択的に除去した第1溝であって、前記ウェーハ中に位置する部分を含む第1溝を形成する工程と、前記ウェーハの前記表面における前記半導体部となる領域の外縁に沿って、前記第1溝につながる第2溝を形成し、前記ウェーハを分割する工程と、を備える。前記ウェーハの前記表面に沿った第1方向における前記第2溝の幅は、前記第1溝の前記第1方向の幅よりも狭く形成される。前記第1溝は、前記ウェーハ内に向かう方向に湾曲した内面を有するように形成され、前記第1溝の前記ウェーハ中に位置する部分の前記第1方向の幅の2分の1は、前記ウェーハの前記裏面に垂直な第2方向において前記裏面から前記ウェーハ中に至る前記第1溝の深さよりも広い。

10

**【図面の簡単な説明】**

**【0006】**

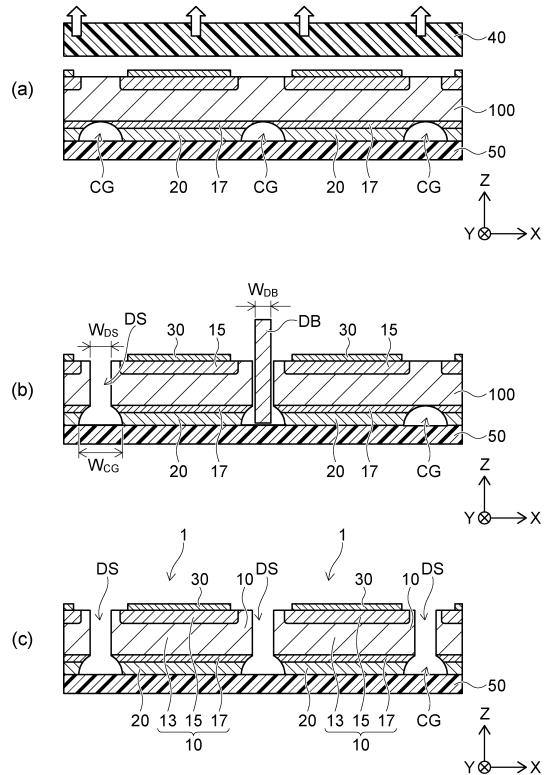

【図1】実施形態に係る半導体装置を示す模式図である。

【図2】実施形態に係る半導体装置の製造過程を示す模式断面図である。

【図3】図2に続く製造過程を示す模式断面図である。

20

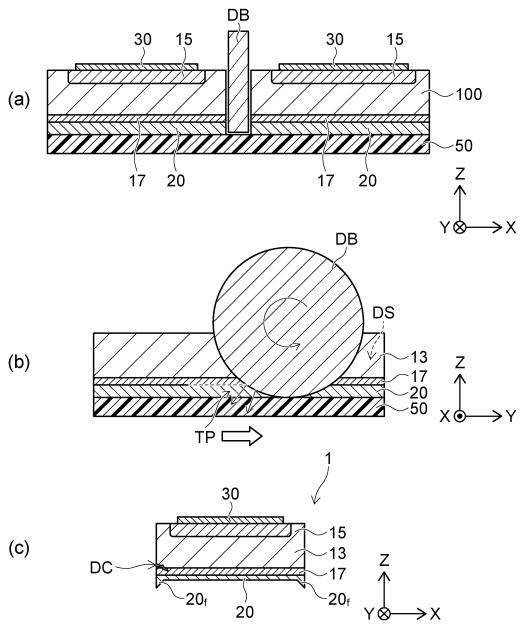

【図4】図3に続く製造過程を示す模式断面図である。

【図5】図4に続く製造過程を示す模式断面図である。

【図6】比較例に係る半導体装置の製造過程を示す模式断面図である。

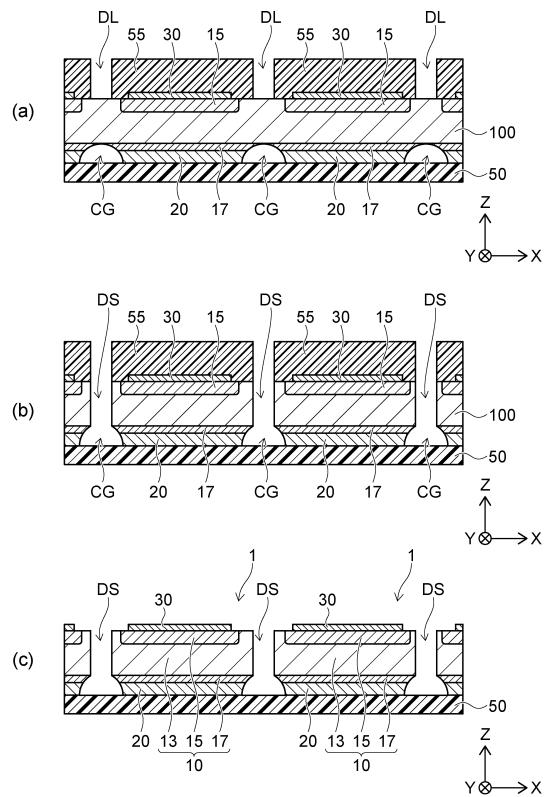

【図7】実施形態の変形例に係る半導体装置の製造過程を示す模式断面図である。

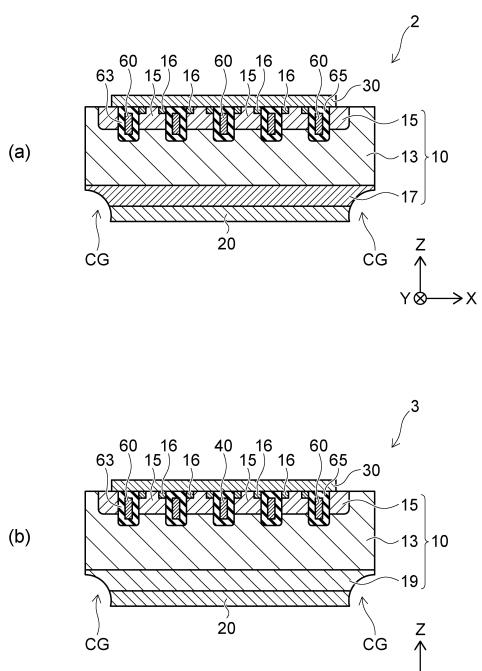

【図8】実施形態の変形例に係る半導体装置を示す模式断面図である。

**【発明を実施するための形態】**

**【0007】**

以下、実施の形態について図面を参照しながら説明する。図面中の同一部分には、同一番号を付してその詳しい説明は適宜省略し、異なる部分について説明する。なお、図面は模式的または概念的なものであり、各部分の厚みと幅との関係、部分間の大きさの比率などは、必ずしも現実のものと同一とは限らない。また、同じ部分を表す場合であっても、図面により互いの寸法や比率が異なって表される場合もある。

30

**【0008】**

さらに、各図中に示すX軸、Y軸およびZ軸を用いて各部分の配置および構成を説明する。X軸、Y軸、Z軸は、相互に直交し、それぞれX方向、Y方向、Z方向を表す。また、Z方向を上方、その反対方向を下方として説明する場合がある。

**【0009】**

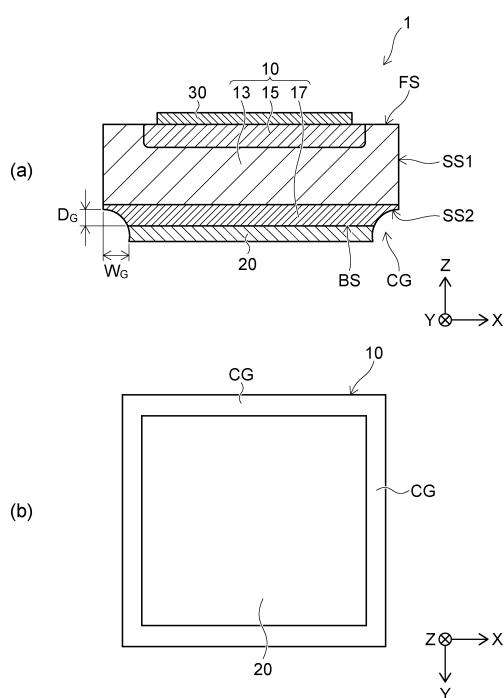

図1(a)および(b)は、実施形態に係る半導体装置1を示す模式図である。図1(a)は、半導体装置1の構造を示す模式断面図である。図1(b)は、半導体装置1の裏面を示す模式平面図である。半導体装置1は、例えば、PINダイオードである。

40

**【0010】**

図1(a)に示すように、半導体装置1は、例えば、半導体部10と、第1電極20と、第2電極30と、を含む。半導体部10は、例えば、シリコンである。第1電極20は、例えば、カソード電極であり、第2電極30は、例えば、アノード電極である。

**【0011】**

半導体部10は、例えば、第1半導体層13と、第2半導体層15と、第3半導体層17と、を含む。第1半導体層13は、例えば、I層(intrinsic layer)である。第2半導体層15は、例えば、p型アノード層であり、第3半導体層17は、例えば、n型カソード層である。

**【0012】**

第2半導体層15は、第1半導体層13と第2電極30との間に位置する。第3半導体

50

層 17 は、第 1 半導体層 13 と第 1 電極 20 との間に位置し、第 1 半導体層 13 の n 形不純物よりも高濃度の n 形不純物を含む。

#### 【 0 0 1 3 】

第 1 電極 20 は、半導体部 10 の裏面 BS を覆い、第 3 半導体層 17 に電気的に接続される。第 2 電極 20 は、半導体部 10 の表面 FS の上に設けられる。第 2 電極 20 は、第 2 半導体層 15 に電気的に接続される。

#### 【 0 0 1 4 】

半導体部 10 は、さらに、第 1 側面 SS1 および第 2 側面 SS2 を有する。第 1 側面 SS1 は、表面 FS につながり、第 2 側面 SS2 は、第 1 側面 SS1 と裏面 BS とをつなぐ。第 2 側面 SS2 は、半導体部 10 の裏面 BS 側に設けられた溝 CG ( 図 4 ( a ) 参照 ) の一部である。第 2 側面 SS2 は、第 1 側面 SS1 および裏面 BS に対して傾斜した部分を含む。

10

#### 【 0 0 1 5 】

溝 CG は、例えば、裏面 BS に沿った方向 ( X 方向 ) の幅 WG 、および、第 1 側面 SS1 に沿った方向 ( Z 方向 ) の深さ DG を有する。溝 CG は、例えば、幅 WG よりも深い深さ DG を有する (  $WG > DG$  ) 。

#### 【 0 0 1 6 】

図 1 ( b ) に示すように、溝 CG は、半導体部 10 の外縁に沿って設けられる。溝 CG は、例えば、X 方向および Y 方向に延在する。

#### 【 0 0 1 7 】

なお、半導体装置 1 がショットキーバリアダイオード ( SBD ) である場合、第 2 半導体層 15 ( p 形アノード層 ) は設けられず、第 2 電極 30 は、例えば、第 1 半導体層 13 に直接コンタクトする。

20

#### 【 0 0 1 8 】

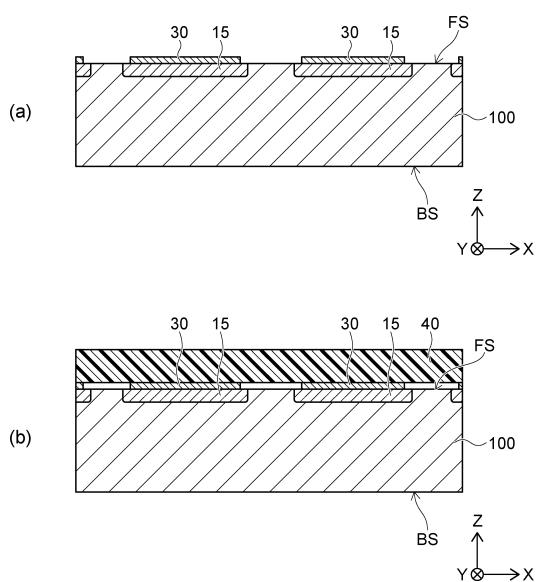

次に、図 2 ( a ) ~ 図 5 ( c ) を参照して、半導体装置 1 の製造方法を説明する。図 2 ( a ) ~ 図 5 ( c ) は、実施形態に係る半導体装置 1 の製造過程を示す模式断面図である。

#### 【 0 0 1 9 】

図 2 ( a ) に示すように、半導体ウェーハ 100 の表面 FS 側に第 2 半導体層 15 を形成した後、第 2 半導体層 15 の上に第 2 電極 30 を選択的に形成する。半導体ウェーハ 100 は、例えば、不純物濃度を低くした n 形シリコンウェーハである。第 2 半導体層 15 は、半導体ウェーハ 100 に p 形不純物、例えば、ボロン ( B ) を選択的にイオン注入することにより形成される。第 2 電極 30 は、第 2 半導体層 15 に電気的に接続される。第 2 電極 30 は、例えば、アルミニウム、タンゲステン、チタニウム等を含む。

30

#### 【 0 0 2 0 】

図 2 ( b ) に示すように、半導体ウェーハ 100 の表面 FS に支持部材 40 を貼り付ける。支持部材 40 は、例えば、表面保護シートである。支持部材 40 は、第 2 電極 30 を覆い、保護する。

#### 【 0 0 2 1 】

図 3 ( a ) に示すように、半導体ウェーハ 100 は、裏面 BS 側を研削、研磨もしくはエッティングすることにより薄層化される。半導体ウェーハ 100 は、半導体部 10 となる部分を残して、除去される。

40

#### 【 0 0 2 2 】

図 3 ( b ) に示すように、半導体ウェーハ 100 の裏面 BS 側に、例えば、n 形不純物であるリンをイオン注入する。

#### 【 0 0 2 3 】

図 3 ( c ) に示すように、第 3 半導体層 17 を形成した後、半導体ウェーハ 100 の裏面 BS を覆う第 1 電極 20 を形成する。第 3 半導体層 17 は、例えば、レーザアニール法を用いて、半導体ウェーハ 100 にイオン注入された n 形不純物を活性化させることにより形成される。第 1 電極 20 は、例えば、Al、Ni、Ti、Au、Ag、Pt、Cu、Sn のうちの少なくとも 1 つの元素を含む。

50

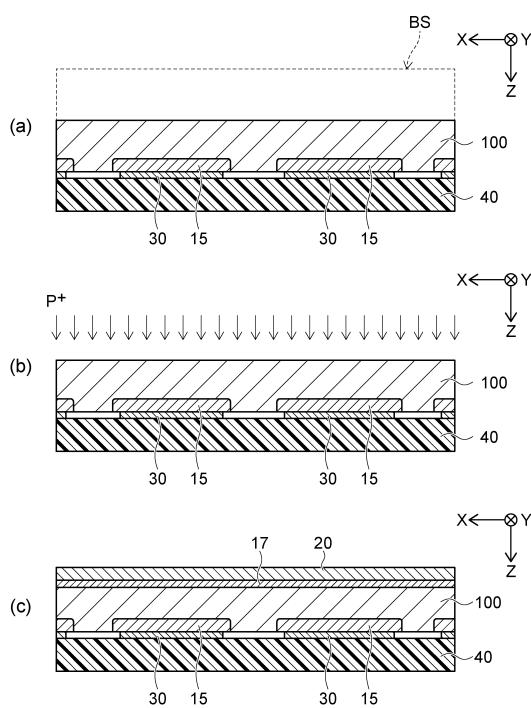

**【 0 0 2 4 】**

図4 (a) に示すように、半導体ウェーハ100の裏面BS側に、レーザー光を照射することにより、溝CGを形成する。溝CGは、第1電極20を選択的に除去し、さらに、半導体ウェーハ100の一部を選択的に除去することにより形成される。溝CGの半導体ウェーハ100中に形成される部分の深さDG(図1(a)参照)は、例えば、数マイクロメートルである。また、溝CGは、例えば、プラズマエッチング、RIE(Reactive Ion Etching)、CDE(Chemical Dry Etching)もしくはウェットエッチングにより、半導体ウェーハの裏面BSを選択的にエッチングすることにより形成されても良い。

**【 0 0 2 5 】**

溝CGは、例えば、X方向およびY方向に延伸し、格子状に交差するように形成される。溝CGは、例えば、半導体部10となる領域の外縁に沿って形成される。レーザー光は、同じ位置に1回もしくは複数回照射されるように制御される。

10

**【 0 0 2 6 】**

また、レーザー光は、所定のスポット径に集光されて照射されるため、中心のエネルギー強度が高く、外側に向かって強度が低下する。このため、溝CGは、その底面から上方に向かって傾斜した内壁を有するように形成される。底面に対する内壁の傾斜角θは、例えば、5度以下が好ましいが、それ以上でも良い。

**【 0 0 2 7 】**

図4 (b) に示すように、半導体ウェーハ100の裏面BS側に、例えば、ダイシングシート50を貼り付ける。

20

**【 0 0 2 8 】**

図4 (c) は、ダイシングシート50を貼り付けた後の半導体ウェーハ100を示している。図4 (b) の上下を逆にした構造を表している。

**【 0 0 2 9 】**

図5 (a) に示すように、半導体ウェーハ100の表面から支持部材40を剥離する。続いて、図5 (b) に示すように、溝CGにつながる溝(以下、ダイシングスペースDS)を形成する。ダイシングスペースDSは、その幅W<sub>DS</sub>が溝CGのX方向の幅W<sub>CG</sub>よりも狭くなるように形成される。

**【 0 0 3 0 】**

ダイシングスペースDSは、例えば、ダイシングブレードDBを用いて、半導体ウェーハ100を切断することにより形成される。ダイシングスペースDSを形成するために用いられるダイシングブレードDBの幅W<sub>DB</sub>は、溝CGの幅W<sub>CG</sub>よりも狭い。

30

**【 0 0 3 1 】**

図5 (c) に示すように、半導体ウェーハ100を切断することにより、半導体装置1をチップ化することができる。ダイシングスペースDSは、半導体部10の外縁に沿って、X方向およびY方向に延伸するように形成される。

**【 0 0 3 2 】**

図6 (a) ~ (c) は、比較例に係る半導体装置1の製造過程を示す模式断面図である。図6 (a) および (b) は、ダイシングブレードDBを用いて、半導体ウェーハ100を分断する過程を示す模式図である。図6 (c) は、比較例に係る製造方法を用いてチップ化された半導体装置1を示す断面図である。

40

**【 0 0 3 3 】**

図6 (a) に示すように、この例では、半導体ウェーハ100の裏面BSに溝CGが形成されない。このため、第1電極20もダイシングブレードDBにより分断される。

**【 0 0 3 4 】**

図6 (b) に示すように、ダイシングブレードDBを回転させながら、半導体ウェーハ100を、例えば、Y方向に移動させる。この際、半導体ウェーハ100の裏面側に、ダイシングブレードDBの外縁に沿って薄く研削される部分TPが生じ、ダイシングシート50に向けて押圧される。このため、所謂チッピングやクラックが生じ易くなる。

**【 0 0 3 5 】**

50

結果として、図6(c)に示すように、半導体装置1は、裏面側にクラックDCを含むことがある。また、第1電極20は、例えば、バリ20<sub>f</sub>を含むように切断されることがある。バリ20<sub>f</sub>は、例えば、第1電極20の切断時に、ダイシングブレードDBの巻き込みにより生じる。

#### 【0036】

このような欠陥は、例えば、半導体装置1の強度を低下させ、チップ破損などのトラブルの一因となる。また、第1電極20のバリ20<sub>f</sub>は、チップボンディング時に、ハンダ材中に気泡を生じさせ、ボイドの要因になる。また、半導体装置1から剥がれると、製造環境のクリーン度を低下させるダストにもなり得る。

#### 【0037】

本実施形態に係る製造方法では、半導体ウェーハ100の裏面側に、溝CGを形成することにより、薄く研削される部分TPをなくし、チッピングやクラックを防ぐことができる。また、第1電極20をダイシングブレードDBにより切断することができないので、バリ20<sub>f</sub>を生じさせることもない。

#### 【0038】

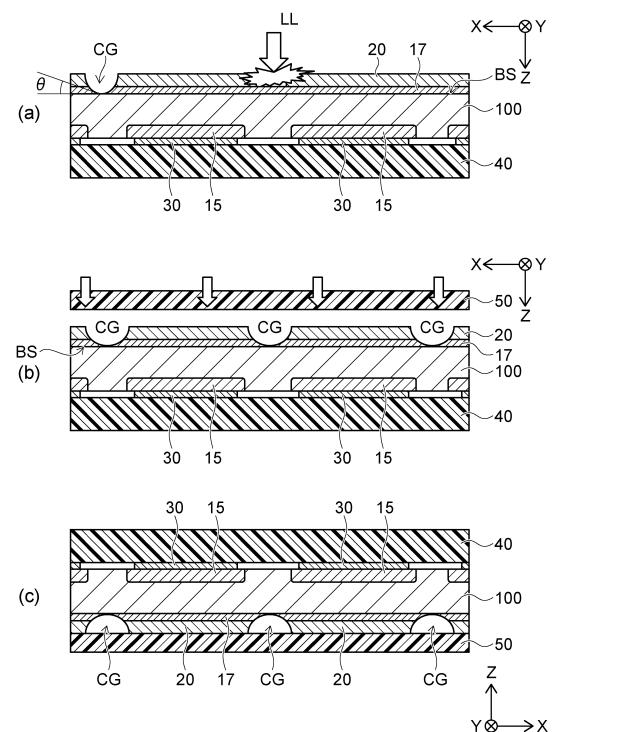

次に、図7(a)～(c)を参照して、実施形態の変形例に係る製造方法を説明する。図7(a)～(c)は、実施形態の変形例に係る半導体装置の製造過程を示す模式断面図である。

#### 【0039】

図7(a)に示すように、半導体ウェーハ100の表面から支持部材40を剥がした後(図5(a)参照)、エッチングマスク55を形成する。エッチングマスク55は、半導体ウェーハ100の表面上に形成され、半導体部10となる領域の外縁に沿った開口DLを含む。

#### 【0040】

図7(b)に示すように、例えば、ドライエッチング法を用いて、半導体ウェーハ100を選択的に除去し、ダイシングスペースDSを形成する。ダイシングスペースDSは、溝CGにつながるように形成される。

#### 【0041】

図7(c)に示すように、エッチングマスク55を除去することにより、チップ化された半導体装置1を得ることができる。

#### 【0042】

この例でも、半導体ウェーハ100の裏面側に溝CGを形成することにより、第1電極20が選択的に除去される。これにより、半導体ウェーハ100を分断する際に、第1電極20をエッチングする必要がなくなり、例えば、ドライエッチングが容易になる。また、半導体装置1の裏面側に溝CGが形成されることにより、例えば、チップボンディング時におけるハンダの這い上がりを抑制することが可能となる。

#### 【0043】

図8(a)および(b)は、実施形態の変形例に係る半導体装置2、3を示す模式断面図である。図8(a)および(b)に示す半導体装置2および3は、それぞれMOSFETおよびIGBT(Insulated Gate Bipolar Transistor)である。半導体装置2および3は、半導体部10の裏面側に設けられた溝CGを有する。

#### 【0044】

図8(a)に示す半導体装置2では、第1電極20は、例えば、ドレイン電極であり、第2電極30は、例えば、ソース電極である。第1半導体層13は、例えば、n形ドリフト層である。第2半導体層15は、例えば、p形拡散層であり、第3半導体層17は、n形ドレイン層である。

#### 【0045】

半導体装置2における半導体部10は、第4半導体層16をさらに含む。第4半導体層16は、例えば、n形ソース層であり、第2半導体層15と第2電極30との間に選択的に設けられる。第4半導体層16は、例えば、第1半導体層13のn形不純物よりも高濃

10

20

30

40

50

度の n 形不純物を含み、第 2 電極 30 に電気的に接続される。

【 0 0 4 6 】

半導体装置 2 は、制御電極 60 をさらに備える。制御電極 60 は、半導体部 10 の表面側に設けられたトレンチの内部に配置され、半導体部 10 と第 2 電極 30 との間に位置する。制御電極 60 は、絶縁膜 63 により半導体部 10 から電気的に絶縁される。また、制御電極 60 は、絶縁膜 65 により第 2 電極 30 から電気的に絶縁される。

【 0 0 4 7 】

図 8 ( b ) に示す半導体装置 3 では、第 1 電極 20 は、例えば、コレクタ電極であり、第 2 電極 30 は、例えば、エミッタ電極である。第 1 半導体層 13 は、例えば、n 形ベース層である。第 2 半導体層 15 は、例えば、p 形ベース層であり、第 3 半導体層 19 は、p 形コレクタ層である。10

【 0 0 4 8 】

半導体装置 3 における半導体部 10 は、第 4 半導体層 16 をさらに含む。第 4 半導体層 16 は、例えば、n 形エミッタ層であり、第 2 半導体層 15 と第 2 電極 30 との間に選択的に設けられる。第 4 半導体層 16 は、例えば、第 1 半導体層の n 形不純物よりも高濃度の n 形不純物を含み、第 2 電極 30 に電気的に接続される。

【 0 0 4 9 】

これらの例でも、半導体部 10 の裏面側に溝 CG を設けることにより、チップ化工程におけるチッピングやクラックの発生を回避することができる。また、第 1 電極 20 のバリ 20f ( 図 6 ( c ) 参照 ) の発生を防ぐことができる。20

【 0 0 5 0 】

以上、いくつかの実施例説明をしたが、実施形態は、これらに限定される訳ではない。例えば、溝 CG は、レーザー照射に代えて、半導体ウェーハを選択的にエッチングすることにより形成しても良い。

【 0 0 5 1 】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。30

【 符号の説明 】

【 0 0 5 2 】

1、2、3 … 半導体装置、 10 … 半導体部、 13 … 第 1 半導体層、 15 … 第 2 半導体層、 16 … 第 4 半導体層、 17 … 第 3 半導体層、 20 … 第 1 電極、 20f … バリ、 30 … 第 2 電極、 40 … 支持部材、 50 … ダイシングシート、 55 … エッチングマスク、 60 … 制御電極、 63、65 … 絶縁膜、 100 … 半導体ウェーハ、 FS … 表面、 BS … 裏面、 CG … 溝、 DB … ダイシングブレード、 DC … クラック、 DL … 開口、 DS … ダイシングスペース、 SS1 … 第 1 側面、 SS2 … 第 2 側面、 T P … 薄く研削された部分

40

50

## 【図面】

## 【図1】

## 【図2】

## 【図3】

## 【図4】

10

20

30

40

50

【図5】

【図6】

10

20

【図7】

【図8】

30

40

50

---

フロントページの続き

## (51)国際特許分類

|                         | F I           |         |

|-------------------------|---------------|---------|

| H 01 L 21/329 (2006.01) | H 01 L 29/91  | C       |

| H 01 L 29/78 (2006.01)  | H 01 L 29/86  | 3 0 1 F |

| H 01 L 29/739 (2006.01) | H 01 L 29/91  | A       |

| H 01 L 21/336 (2006.01) | H 01 L 29/86  | 3 0 1 P |

| B 23 K 26/364 (2014.01) | H 01 L 29/78  | 6 5 3 C |

| B 24 B 27/06 (2006.01)  | H 01 L 29/78  | 6 5 2 G |

|                         | H 01 L 29/78  | 6 5 5 C |

|                         | H 01 L 29/78  | 6 5 8 G |

|                         | B 23 K 26/364 |         |

|                         | B 24 B 27/06  | M       |

## (56)参考文献

特開2015-53428 (JP, A)

特開2009-105211 (JP, A)

特開平5-166926 (JP, A)

特開2017-84896 (JP, A)

米国特許出願公開第2012/0306056 (US, A1)

米国特許出願公開第2014/0264768 (US, A1)

## (58)調査した分野

(Int.Cl., DB名)

H 01 L 21 / 301

H 01 L 21 / 3065

H 01 L 29 / 861

H 01 L 29 / 872

H 01 L 21 / 329

H 01 L 29 / 78

H 01 L 29 / 739

H 01 L 21 / 336

B 23 K 26 / 364

B 24 B 27 / 06