(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5249080号

(P5249080)

(45) 発行日 平成25年7月31日(2013.7.31)

(24) 登録日 平成25年4月19日(2013.4.19)

(51) Int.Cl.

F 1

H01L 23/12 (2006.01)

H01L 21/60 (2006.01)H01L 23/12 501P

H01L 21/92 602L

H01L 21/92 602J

請求項の数 2 (全 9 頁)

(21) 出願番号 特願2009-36590 (P2009-36590)

(22) 出願日 平成21年2月19日 (2009.2.19)

(65) 公開番号 特開2010-192747 (P2010-192747A)

(43) 公開日 平成22年9月2日 (2010.9.2)

審査請求日 平成23年12月5日 (2011.12.5)

(73) 特許権者 000002325

セイコーインスツル株式会社

千葉県千葉市美浜区中瀬1丁目8番地

(74) 代理人 100154863

弁理士 久原 健太郎

(74) 代理人 100142837

弁理士 内野 則彰

(74) 代理人 100123685

弁理士 木村 信行

(72) 発明者 近江 俊彦

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

審査官 宮本 靖史

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板と、

前記半導体基板に設けられた半導体素子上に配置された金属配線と、

前記金属配線の上に形成され、前記金属配線を保護する保護膜と、

前記保護膜の上に形成された、セラミック膜と前記セラミック膜より機械的剛性の小さい材料の2層からなる応力緩衝層と、

前記保護膜及び、前記応力緩衝層を貫通して、前記金属配線上に設けられたビアホールと、

前記ビアホールの内面及び前記金属配線の表面、及び前記応力緩衝層の表面に形成された下地金属膜と、 10

前記ビアホールを埋め込むように形成された導電層と、

前記導電層の上に形成されたバンプ電極を有し、

平面視にて、前記ビアホールは前記バンプ電極の中心を避けて、前記バンプ電極の下ではあるが周囲の領域に形成されていることを特徴とする半導体装置。

## 【請求項 2】

半導体基板と、

前記半導体基板に設けられた半導体素子上に配置された第1の金属配線と、

前記第1の金属配線の上に絶縁膜を介して配置された第2の金属配線と、

前記第2の金属配線の上に形成され、前記金属配線を保護する保護膜と、

前記保護膜の上に形成された、セラミック膜と前記セラミック膜より機械的剛性の小さい材料の2層からなる応力緩衝層と、

前記保護膜及び、前記応力緩衝層を貫通して、前記第2の金属配線上に設けられたピアホールと、

前記ピアホールの内面及び前記第2の金属配線の表面、及び前記応力緩衝層の表面に形成された下地金属膜と、

前記ピアホールを埋め込むように形成された導電層と、

前記導電層の上に形成されたバンプ電極と、

前記半導体素子上に前記第1の金属配線により形成された入出力のための金属端子と、

を有し、

前記第2の金属配線は前記バンプ電極及び前記ピアホール内に形成された前記導電層と前記金属端子とを、前記金属端子上に設けられたピアを介してつなぐ再配線であり、

平面視にて、前記ピアホールは前記バンプ電極の中心を避けて、前記バンプ電極の下ではあるが周囲の領域に形成されていることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、バンプ電極を有する半導体装置に関し、ウエハレベルで半導体素子のパッケージを形成する半導体装置に関する。

【背景技術】

【0002】

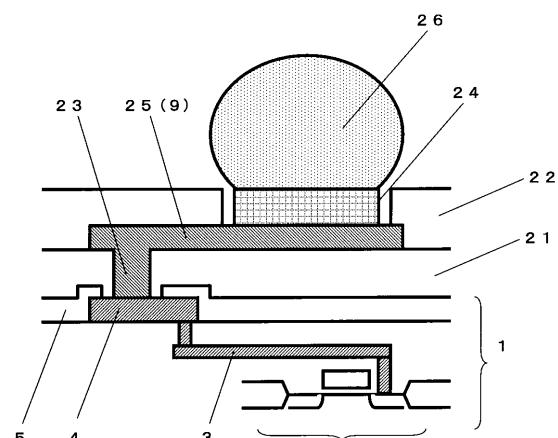

従来のウエハレベルでの半導体素子のパッケージの断面図を図5に示す。ウエハレベルで半導体素子の実装をする場合、半導体素子2上に金属配線3により形成した入出力のための金属端子4と金属配線3を保護する保護膜5を形成し、入出力の金属端子4の一部が露出するように保護膜5をエッチングした半導体基板1を製造する。その後、半導体基板1の上に第1の応力緩衝層21を形成し、半導体基板1に形成した入出力のための金属端子4の上に第1の応力緩衝層21を貫通するような第1の開口孔23を形成し、次に、第1の開口孔23の内面及び入出力のための金属端子4の表面、及び第1の応力緩衝層21の表面に下地金属を形成し、第1の開口孔23と最後に形成するバンプ電極26とを電気的に接続する再配線のパターンをフォトレジストで形成し、そこにメッキ等により第1の開口孔23及び再配線25のパターンに例えば銅などの金属を埋め込むように形成する。

【0003】

次に、再配線25のパターンを形成したフォトレジストを除去して、フォトレジストを除去することで露出した下地金属をエッチングする。次に、第1の応力緩衝層21及び再配線25の上に第2の応力緩衝層22を形成し、再配線25の上に第2の応力緩衝層22を貫通するように第2の開口孔24を形成し、第2の開口孔24にバンプ電極をスクリーニング印刷等により形成することで、バンプ電極を有するウエハレベルでの半導体素子のパッケージを形成している。

【0004】

一般に、前述のような形態のウエハレベルでの半導体素子のパッケージはその製造工程が複雑で、工程が長いため、製造コストが大きい問題がある。また、平面視にて、半導体素子を有する半導体ウエハに形成した入出力の金属端子からバンプ電極までつなげる再配線は、例えば、メッキで形成した金属により形成するため、その配置には制約があり、半導体素子のチップサイズに影響を与えることとなる。

【0005】

もう少し製造工程が簡素な形態として、例えば、フリップチップ等に使われている半導体素子のパッケージとして、特許文献1のような形態がある。

【先行技術文献】

【特許文献】

【0006】

10

20

30

40

50

【特許文献1】特開2006-165595号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献1の形態では、バンプ電極の中央部に開口孔が形成され、開口孔に金属等からなる導電層があるため、半導体装置を実装した際のバンプ電極の変形応力が半導体素子に伝わりやすく機械的な外部応力に弱い場合がある。

【0008】

また、前述のような形態のウエハレベルでの半導体素子のパッケージはその製造工程が複雑で、工程が長いため、製造コストが大きい問題がある。また、平面視にて、半導体素子を有する半導体ウエハに形成した入出力の金属端子からバンプ電極までつなげる再配線は、例えば、メッキで形成した金属により形成するため、その配置には制約があり、半導体素子のチップサイズに影響を与えることとなる。

10

【0009】

そこで、本発明は、製造工程が簡素であり、機械的な外部応力に強い、ウエハレベルでの半導体素子のパッケージを提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明は、前記目的を達成するために、半導体素子上に形成された金属配線を有する半導体基板と、金属配線の中の最上層の金属配線の上に形成され、前記金属配線を保護する保護膜と、前記保護膜の上に形成された応力緩衝層と、前記保護膜及び、前記応力緩衝層を貫通するように、前記金属配線上に設けられたピアホールと、前記ピアホールの内面及び前記金属配線の表面、及び前記応力緩衝層の表面に形成された下地金属膜と、前記ピアホールを埋め込むように形成された導電層と、前記導電層の上に形成されたバンプ電極を有し、平面視にて、前記ピアホールは前記バンプ電極の周辺の位置に形成されていることを特徴とする半導体装置を提供する。

20

【0011】

さらに、半導体素子上に形成された金属配線を有する半導体基板と、金属配線の中の最上層の金属配線の上に形成され、前記金属配線を保護する保護膜と、前記保護膜の上に形成された応力緩衝層と、前記保護膜及び、前記応力緩衝層を貫通するように、前記金属配線上に設けられたピアホールと、前記ピアホールの内面及び前記金属配線の表面、及び前記応力緩衝層の表面に形成された下地金属膜と、前記ピアホールを埋め込むように形成された導電層と、前記導電層の上に形成されたバンプ電極を有し、前記半導体素子上に前記金属配線により形成された入出力のための金属端子と、前記金属端子と前記バンプ電極及び前記ピアホール内に形成された前記導電層とをつなぐ再配線を有し、前記再配線が、前記保護膜の下に形成された第2の金属配線で形成されていることを特徴とする半導体装置を提供する。

30

【0012】

また、前記の半導体装置において、前記応力緩衝層はポリイミド膜あるいはエポキシを主剤とした有機樹脂膜であることを特徴とする半導体装置を提供する。

40

【0013】

また、前記の半導体装置において、前記応力緩衝層は絶縁性セラミック膜であることを特徴とする半導体装置を提供する。

【0014】

また、前記の半導体装置において、前記応力緩衝層は酸化アルミニウムあるいは窒化アルミニウムを含むセラミック膜であることを特徴とする半導体装置を提供する。

【0015】

また、前記の半導体装置において、前記応力緩衝層はセラミック膜と前記セラミック膜より機械的剛性の小さい材料の2層からなることを特徴とする半導体装置を提供する。

【発明の効果】

50

## 【0016】

本発明によれば、製造工程が簡素であり、機械的な外部応力に強い、ウエハレベルでの半導体装置を提供することができる。

## 【図面の簡単な説明】

## 【0017】

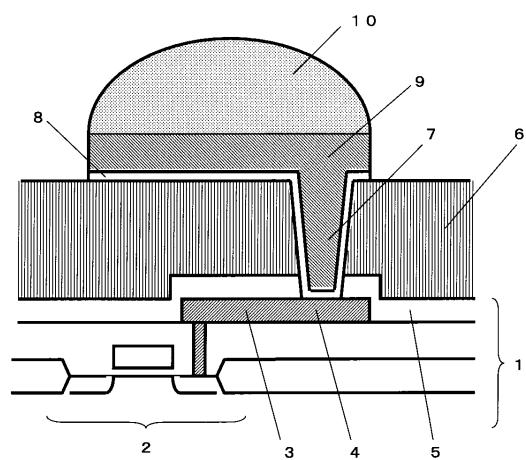

【図1】本発明の第1の実施例の断面図である。

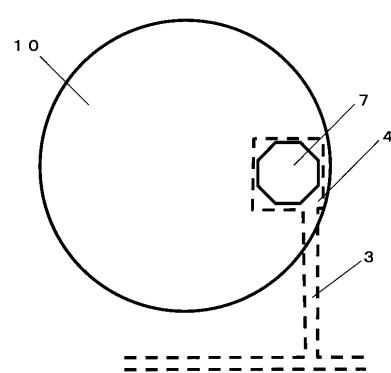

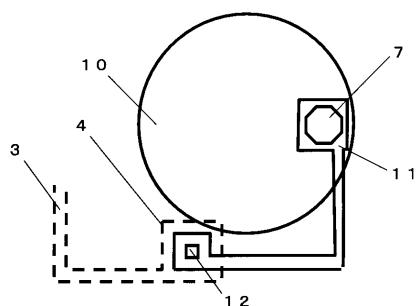

【図2】本発明の第1の実施例の平面図である。

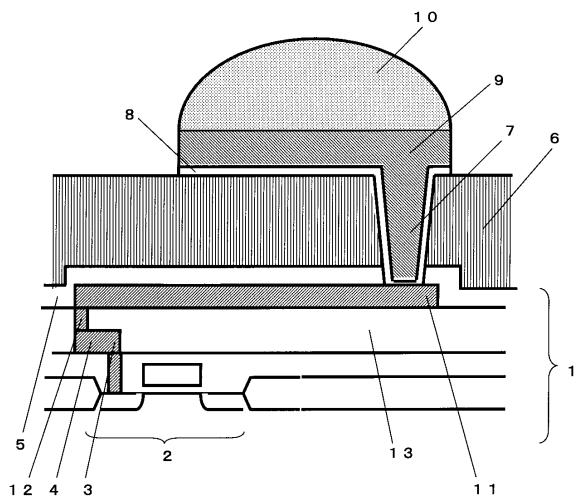

【図3】本発明の第2の実施例の断面図である。

【図4】本発明の第2の実施例の平面図である。

【図5】従来の形態のウエハレベルでの半導体素子のパッケージの断面図である。

10

## 【発明を実施するための形態】

## 【0018】

本発明の第1の実施例を図1および図2を利用して、以下に説明する。

## 【0019】

P型シリコンからなる半導体基板1にCMOS回路を構成する半導体素子2を形成する。CMOS回路の入力回路あるいは出力回路は、アルミニウムからなる金属配線3により入出力の金属端子4に接続されている。最上層の金属配線3及び入出力の金属端子4は、窒化シリコンからなる保護膜5に覆われている。このとき、半導体基板1はN型シリコンでも構わない。

## 【0020】

20

次に、保護膜5の上に応力緩衝層6を形成する。本実施例では、応力緩衝層6として感光性のポリイミドをスピンドルコートにより約20ミクロンの厚さとなるように形成した。その後、ポリイミドをフォトマスクによりビアホール7となる部分のポリイミドを感光、現像して、ポリイミドにビアホール7となる孔を形成する。ビアホール7の位置は後で形成されるバンプ電極の中心を避け、バンプ電極の下ではあるが周囲の領域に位置するようになる。その後に、ポリイミドをマスクとして6フロロヘキサンにより保護膜5をエッチングすることにより、金属配線3をビアホール7の底に露出させる。

## 【0021】

このとき、応力緩衝層6の厚さを20ミクロンとしたが、この厚さは例えば10ミクロンでも、30ミクロンでも構わない。

30

## 【0022】

また、応力緩衝層6の材質はポリイミドでなくとも構わない。例えば、エポキシを主剤とする樹脂、例えばPMMA、SU-8等でも同様の機能を果たす。また、ポリイミドあるいはエポキシを主剤とする樹脂は必ずしも感光性である必要はない。例えば、ポリイミドで保護膜5を覆った後に、例えば、クロム等の金属によりポリイミド表面を覆い、その上にフォトレジストを塗布してフォトマスクによりフォトレジストでビアホールの平面視のパターンを形成し、その後、ポリイミド表面のクロムをエッチングによりビアホールの平面視のパターンに加工し、フォトレジストを除去後に、クロムをエッチングのマスクとして使いポリイミドをビアホールの形状に加工する方法もある。また、ポリイミドで保護膜5を覆った後に、ポリイミドを半硬化し、その上にフォトレジストを塗布して露光・現像してフォトレジストとポリイミドに同時にビアホールのパターンを形成し、その後フォトレジストを除去してポリイミドにビアホールを形成するという方法もある。

40

## 【0023】

また、応力緩衝層6にセラミック膜を使っても良い。特に、酸化アルミニウム、窒化アルミニウム等は、熱伝導率がポリイミド等の樹脂に比べて大きいため半導体素子で発生する熱を外部へ放熱する観点では有効である。また、セラミック膜は樹脂に比べて機械的強度も高い。このため、ウエハレベルのパッケージの材質として、セラミック膜の有用性は高いと言える。

## 【0024】

セラミック膜は、例えば、セラミックの微粒子を保護膜5の表面に積層することで形成

50

することができる。

【0025】

応力緩衝層6にセラミック膜を使う場合、セラミック膜を保護膜5の上に直接形成しても良いが、セラミックよりも機械的剛性が小さい樹脂、例えばポリイミドで保護膜5を覆った上にセラミック膜を形成しても良い。

【0026】

応力緩衝層6及びビアホール7を形成した後、チタン・タングステンと銅からなる下地金属8をスパッタにより、応力緩衝層6の表面及び、ビアホール7の内面及びビアホール7の底面にある金属配線3の上に形成する。その後、下地金属8の表面にフォトレジストをスピンドルコートして、フォトマスクによる露光、現像によりバンプ電極10を形成する領域のフォトレジストを除去して下地金属8を露出させる。その後に、露出した下地電極8の上に電解メッキにより銅を析出させ、導電層9を形成し、次に、銅からなる導電層9の上に約60ミクロンの厚さのハンダをメッキにより形成し、バンプ電極10とする。最後に有機溶剤によりフォトレジストを溶解して除去した後に、エッチングにより表面に露出している下地金属を除去することで、バンプ電極10が存在しない領域に応力緩衝層6を露出させて半導体装置を完成させる。本実施例に係る構造を上から見ると図2に示されるように、ビアホール7はバンプ電極10の下ではあるが周囲の近傍に位置することになる。

10

【0027】

第1の実施例では、バンプ電極10の直下に入出力の金属端子4が存在する場合の例であったが、必ずしもバンプ電極の周囲の直下に入出力の金属端子があるとは限らない。バンプ電極に要求される位置が金属端子から離れていることがありうる。

20

【0028】

そこで、半導体素子2の入出力の金属端子4がバンプ電極10の直下にない場合について、第2の実施例を示す図3および図4を利用して説明する。

【0029】

入出力の金属端子4の上を酸化シリコンからなる絶縁膜13で覆った後に金属配線のビア12を形成する。その後、アルミニウムからなる第2の金属配線である再配線11を形成する。その後、再配線11を窒化シリコンからなる保護膜5で覆う。

30

【0030】

次に、保護膜5の上に応力緩衝層6を形成する。本実施例では、応力緩衝層6として感光性のポリイミドをスピンドルコートにより約20ミクロンの厚さとなるように形成した。その後、ポリイミドをフォトマスクによりビアホール7となる部分のポリイミドを感光、現像して、ポリイミドにビアホール7となる孔を形成する。ビアホール7の位置は後で形成されるバンプ電極の中心を避け、バンプ電極の下ではあるが周囲の領域に位置するようになる。その後に、ポリイミドをマスクとして6フロ化硫黄により保護膜5をエッチングすることにより、第2の金属配線である再配線11をビアホール7の底に露出させる。このとき、ビアホール7は半導体素子2や金属端子4の直上ではなく、半導体素子2や金属端子4から離れた位置に開口する。

30

【0031】

このとき、応力緩衝層6の厚さを20ミクロンとしたが、この厚さは例えば10ミクロンでも、30ミクロンでも構わない。

40

【0032】

また、応力緩衝層6の材質はポリイミドでなくとも構わない。例えば、エポキシを主剤とする樹脂、例えばPMMR、SU-8等でも同様の機能を果たす。また、ポリイミドあるいはエポキシを主剤とする樹脂は必ずしも感光性である必要はない。例えば、ポリイミドで保護膜5を覆った後に、例えば、クロム等の金属によりポリイミド表面を覆い、その上にフォトレジストを塗布してフォトマスクによりフォトレジストでビアホールの平面視のパターンを形成し、その後、ポリイミド表面のクロムをエッチングによりビアホールの平面視のパターンに加工し、フォトレジストを除去後に、クロムをエッチングのマスクと

50

して使いポリイミドをビアホールの形状に加工する方法もある。また、ポリイミドで保護膜5を覆った後に、ポリイミドを半硬化し、その上にフォトレジストを塗布して露光・現像してフォトレジストとポリイミドに同時にビアホールのパターンを形成し、その後フォトレジストを除去してポリイミドにビアホールを形成するという方法もある。

【0033】

また、応力緩衝層6にセラミック膜を使っても良い。特に、酸化アルミニウム、窒化アルミニウム等は、熱伝導率がポリイミド等の樹脂に比べて大きいため半導体素子で発生する熱を外部へ放熱する観点では有効である。また、セラミック膜は樹脂に比べて機械的強度も高い。このため、ウエハレベルのパッケージの材質として、セラミック膜の有用性は高いと考える。

10

【0034】

セラミック膜は、例えば、セラミックの微粒子を保護膜5の表面に積層することで形成することができる。

【0035】

応力緩衝層6にセラミック膜を使う場合、セラミック膜を保護膜5の上に直接形成しても良いが、セラミックよりも機械的剛性が小さい樹脂、例えばポリイミドで保護膜5を覆った上にセラミック膜を形成しても良い。

【0036】

応力緩衝層6及びビアホール7を形成した後、チタン・タングステンと銅からなる下地金属8をスパッタにより、応力緩衝層6の表面及び、ビアホール7の内面及びビアホール7の底面にある第2の金属配線である再配線11の上に形成する。その後、下地金属8の表面にフォトレジストをスピンドルコートして、フォトマスクによる露光、現像によりバンプ電極10を形成する領域のフォトレジストを除去して下地金属8を露出させる。その後に、露出した下地電極8の上に電解メッキにより銅を析出させ、導電層9を形成し、次に、銅からなる導電層9の上に約60ミクロンの厚さのハンダをメッキにより形成し、バンプ電極10とする。最後に有機溶剤によりフォトレジストを溶解して除去した後に、エッチングにより表面に露出している下地金属を除去することで、バンプ電極10が存在しない領域に応力緩衝層6を露出させて半導体装置を完成させる。本実施例では、図4に示すように金属端子4がバンプ電極10と重ならないように配置されることから、外部応力により損傷を受けにくい半導体装置とすることができます。

20

【符号の説明】

【0037】

- 1 半導体基板

- 2 半導体素子

- 3 金属配線

- 4 入出力の金属端子

- 5 保護膜

- 6 応力緩衝層

- 7 ビアホール

- 8 下地金属

- 9 導電層

- 10 バンプ電極

- 11 再配線（第2の金属配線）

- 12 金属配線のビア

- 13 絶縁膜

- 21 第1の応力緩衝層

- 22 第2の応力緩衝層

- 23 第1の開口孔

- 24 第2の開口孔

- 25 再配線（第1の応力緩衝層の上の導電層）

40

50

## 2 6 バンプ電極(スクリーニング印刷)

【図1】

【図2】

【図3】

【図5】

【図4】

---

フロントページの続き

(56)参考文献 特開2006-165595(JP, A)

特開2007-306033(JP, A)

特開2008-235573(JP, A)

国際公開第00/055898(WO, A1)

特開昭60-117633(JP, A)

特開平08-139128(JP, A)

特開2000-183089(JP, A)

特開2003-318324(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12 - 23/15

H01L 21/60

H01L 21/3205

H01L 21/3213

H01L 21/768

H01L 23/522