(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-129699

(P2007-129699A)

(43) 公開日 平成19年5月24日(2007.5.24)

(51) Int.C1.

HO3K 19/177 (2006.01)

F 1

HO3K 19/177

テーマコード(参考)

5J042

審査請求 未請求 請求項の数 10 O L 外国語出願 (全 13 頁)

(21) 出願番号 特願2006-271642 (P2006-271642)

(22) 出願日 平成18年10月3日 (2006.10.3)

(31) 優先権主張番号 11/242,509

(32) 優先日 平成17年10月3日 (2005.10.3)

(33) 優先権主張国 米国(US)

(71) 出願人 500575824

ハネウェル・インターナショナル・インコ

ーポレーテッド

アメリカ合衆国ニュージャージー州O79

62-2245, モーリスタウン, コロン

ビア・ロード 101, ピー・オー・ボッ

クス 2245

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100140109

弁理士 小野 新次郎

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

最終頁に続く

(54) 【発明の名称】チップ上の再構成可能なネットワーク

(57) 【要約】 (修正有)

【課題】容易にプログラム可能で高度に柔軟な、ネットワーク要素と機能の階層的構造を含む、半導体チップ上に実装可能な再構成可能なネットワーク用のアーキテクチャが開示される。

【解決手段】チップ上の再構成可能なネットワークは、汎用マイクロ・プロセッサと、複数のオン・チップ・メモリと、個々に再構成可能なプログラム可能論理アレイを含む複数の再構成可能実行ユニットと、オンチップ・メモリとネットワーク又はバス間に相互接続を提供する複数の構成可能なシステム・インターフェース・ユニットと、ネットワーク相互接続インターフェースを含むオンチップ・ネットワークと、特定のインターフェースに対する関連入出力信号を収集してそれらを指定されたシステム・インターフェース資源に付与する微粒子相互接続ユニットと、及び、外部ネットワーク又は装置インターフェース間にリンクを供給する複数の入出力ブロックとを含む。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

少なくとも 1 つのメモリ・ユニット (204) と、

前記少なくとも 1 つのメモリ・ユニット (204) に接続された少なくとも 1 つの処理

ユニット (202) と、

前記少なくとも 1 つの処理ユニット (202) に接続された少なくとも 1 つの再構成可能

な実行ユニット (206) と、

前記少なくとも 1 つの再構成可能な実行ユニット (206) に接続されたネットワーク

・インターフェース・ユニット (210) と、

前記ネットワーク・インターフェース・ユニット (210) に接続された少なくとも 1

10

つの構成可能なシステム・インターフェース・ユニット (208) と、及び

前記少なくとも 1 つの構成可能なシステム・インターフェース・ユニット (208) に

接続された微粒子相互接続ユニット (212) と、

からなる、再構成可能なネットワーク (200)。

**【請求項 2】**

前記微粒子相互接続ユニット (212) に接続された少なくとも 1 つの入出力ユニット

(214) を更に含む、

請求項 1 に記載の再構成可能なネットワーク (200)。

**【請求項 3】**

前記再構成可能なネットワーク (200) が半導体チップ上に配置されている事を特徴

とする、

20

請求項 1 に記載の再構成可能なネットワーク (200)。

**【請求項 4】**

前記少なくとも 1 つのメモリ・ユニット (204) が揮発性メモリ装置からなり、

前記少なくとも 1 つの処理ユニット (202) が 4 つのマイクロ・プロセッサからなり

、

前記少なくとも 1 つの再構成可能な実行ユニット (206) が 12 個の再構成可能な実

行ユニットからなり、

前記少なくとも 1 つの構成可能なシステム・インターフェース・ユニット (208) が

12 個の構成可能なシステム・インターフェース・ユニットからなる事を特徴とする、

30

請求項 1 に記載の再構成可能なネットワーク (200)。

**【請求項 5】**

前記少なくとも 1 つの処理ユニット (202) が埋め込まれたマイクロ・プロセッサから

なる事を特徴とする、

請求項 1 に記載の再構成可能なネットワーク (200)。

**【請求項 6】**

前記ネットワーク・インターフェース・ユニット (210) が、それらとの間でデータ

通信するために、前記少なくとも 1 つの再構成可能な実行ユニット (206) と、前記少

なくとも 1 つの構成可能なシステム・インターフェース・ユニット (208) と、及び前

記少なくとも 1 つの処理ユニット (202) と相互接続するように動作可能なオンチップ

・ネットワークからなる事を特徴とする、

40

請求項 1 に記載の再構成可能なネットワーク (200)。

**【請求項 7】**

前記少なくとも 1 つの再構成可能な実行ユニット (206) が少なくとも 1 つのプログ

ラム可能論理アレイからなる事を特徴とする、

請求項 1 に記載の再構成可能なネットワーク (200)。

**【請求項 8】**

前記少なくとも 1 つの構成可能なシステム・インターフェース・ユニット (208) が

、それらとの間でデータ通信するために、メモリ・ユニット、ネットワーク及びバスの内

の少なくとも 2 つと相互接続するように動作可能な、構成可能データ通信インターフェ

50

スからなる事を特徴とする、

請求項 1 に記載の再構成可能なネットワーク ( 2 0 0 )。

【請求項 9】

前記微粒子相互接続ユニット ( 2 1 2 ) が少なくとも 1 つのプログラム可能ルーティング装置からなる事を特徴とする、

請求項 1 に記載の再構成可能なネットワーク ( 2 0 0 )。

【請求項 10】

前記微粒子相互接続ユニット ( 2 1 2 ) に接続された少なくとも 1 つの入出力ユニット ( 2 1 4 ) を更に含み、

前記少なくとも 1 つの入出力ユニット ( 2 1 4 ) が少なくとも 1 つの入出力パッドと、

少なくとも 1 つのレジスタと及び少なくとも 1 つの 3 状態バッファとからなる事を特徴とする、

請求項 1 に記載の再構成可能なネットワーク ( 2 0 0 )。

【発明の詳細な説明】

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

【0 0 0 2】

本発明は一般的にはネットワーク処理分野に関し、より特定すれば、しかしながら排他的にではなく、半導体チップ上に実装可能な再構成可能ネットワーク・アーキテクチャに関する。

【従来の技術】

【0 0 0 3】

次世代の宇宙ベースのネットワークの展開を促進することの出来る実現可能な宇宙通信基盤を実装するミッション立案者による要求は、今日の宇宙船システム技術者のための多くの設計的挑戦を創造している。これらの設計的挑戦は、漸次に要求される宇宙応用と増加したミッション要求、また全体的なシステムコストの最小化に対する大きな圧力によって複雑化した。一般的には、趨勢はユーザ・アプリケーションとより多くのデータを伝送する努力をしながら、より少ないコストで宇宙通信システムを実装することである。この事について、システム設計者が遭遇する主な問題は、現在の宇宙システム・アーキテクチャと関連する設計手法が、新しい設計と負わされているコスト要件の全てに適合することが出来ない事である。従って、特にコスト、性能、信頼性、柔軟性、エネルギー消費及び重量において、現在及び将来の宇宙システム設計及びミッション要求に合った最善のバランスを提供することが出来る、新しい宇宙システム・アーキテクチャと設計手法が必要とされている。

【0 0 0 4】

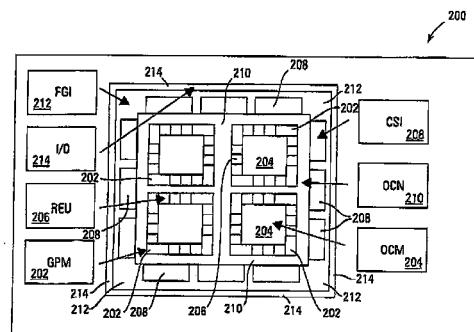

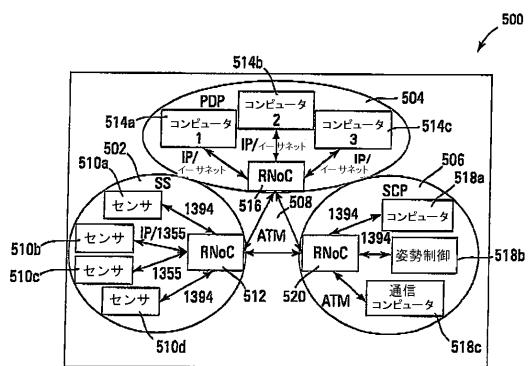

宇宙産業の現在の趨勢は、モジュール方式の商用規格設計手法である。しかしながら、多数の異なる業者からの規格の構成要素（例えばペイロード処理装置、ミッションに特有のセンサー、通信バス・システム等）を用いることは、まだ充分に用意されていない重大なインターフェース設計問題を惹起する。例えば業者の構成要素間の異なるインターフェースの使用は、含まれるシステムの全体的な柔軟性を減じ、循環しない工学的コスト（財政上の出費、エネルギー消費及び重量に関して）の増大を招く。また、この手法は、急速に変化する標準、宇宙航行に耐える規格のインターフェース構成要素の不足、及び今日利用可能なネットワーク・ソリューションの基本的非柔軟性の為に重大な設計的挑戦を呈する。これに関して、図 1 を参照すると、科学的応用の為の典型的な宇宙船システム・アーキテクチャが提示されており、現在の規格設計手法に伴う上述のインターフェース問題を示している。

【0 0 0 5】

図 1 は、センサーの組 ( S S ) 1 0 2 と、ペイロード・データ処理装置 ( P D P ) サブシステム 1 0 4 と、宇宙船制御処理装置 ( S C P ) 1 0 6 とを含む、従来の商用規格設計

手法を用いた、現在の宇宙船システム 100 に対する典型的なアーキテクチャのブロック図を示す。SSサブシステム 102 は複数のセンサー 108a 乃至 108d を含み、PDPサブシステム 104 は複数のペイロード・データ処理装置 110a 乃至 110c を含み、SCPサブシステム 106 は複数の宇宙船制御処理装置 112a 乃至 112c を含む。この例示的アーキテクチャに示されているように、現在の設計手法は SSサブシステム 102 と PDPサブシステム 104 の構成要素間に標準的な 1 対 1 インターフェースを用いている。従ってインターフェース 114a 乃至 114d は、IEEE1394 及び 1355 高速シリアル・リンクを用いた 1 対 1 インターフェースとして実装されている。加えて、PDPサブシステム 104 内のペイロード・データ処理装置 110a 乃至 110c は、標準的コンパクト周辺機器構成要素相互接続 (CPCI) バックプレーン・バス 116 によって相互接続された、商用規格のコンピュータ処理装置として実装されている。この例示的アーキテクチャによって示されているように、典型的な SS - PDP インターフェースに対する従来のソリューションは、1 つのセンサー・コンピュータ対に対して 1 つのインターフェースが実装されていることに注意されたい。

#### 【0006】

図 1 に示された宇宙船システム 100 はまた、PDP 及び SCP サブシステム 104 と 106 とを相互接続する 2 つの主要インターフェース 118、120 を含む。この例では、インターフェース 120 は、制御情報を交換するための SCP 処理装置 112a と PDP 処理装置 110a 間の IEEE1394 シリアル・リンクによって実装されている。その代りにインターフェース 120 は IEEE1355 シリアル・リンクで実装されてもよい。制御情報は SCP サブシステム 106 内の処理装置 112a と 112b との間でも、IEEE1394 シリアル・リンクを用いて交換される。インターフェース 118 は、標準的ネットワーク通信プロトコル (例えば ATM) を用いてデータのダウンリンク、アップリンク及び交叉リンク転送機能を提供する。この点で、上述の全てのシステム相互接続は設計サイクルの早期に定義され、特定の設計は関連するシステムの生涯にわたって固定的かつ硬直的な状態に残されることに注意することが重要である。その結果、この様な設計の硬直性はユーザーのミッション中のデータ再配布の能力をひどく制限し、実装され得るアプリケーションのタイプをも限定する。

#### 【0007】

図 1 に示されたシステムのタイプにおいては、使用される種々のプロトコルの管理のために (ハードウェアでなく) ソフトウェアを用いる。しかしながら、そのようなソフトウェア / ハードウェア実装のトレードオフは追加のソフトウェア開発コスト及び全体的な計算能力の損失を招く。従って、異なるインターフェース標準を用いて、処理オーバーヘッド、設計コスト及び / 又はプロジェクトの危険性等の増加を被ることも無く、システム構成要素の相互接続を容易にすることの出来る柔軟なネットワーク基盤を開発することが強く求められている。

#### 【0008】

この分野で生じている他の問題は、チップ技術と商用領域での通信速度の著しい進歩がより早いパケット処理装置の必要性を推し進め、プロトコルが大いに多様化したことである。しかしながら 2 つの基本的な設計原理がこの問題を解決するために開発された。1 つの手法は設計の柔軟性を増すことを際立たせ、他は処理速度の増加を際立たせた。例えば、その様な 1 つの設計手法は柔軟性を増すためにネットワーク・トラフィックを扱うための「汎用プロセス」を用いるが、この増加は速度を犠牲にした。第 2 の手法は速度を増すためにネットワーク・トラフィック処理機能用のアプリケーション特化集積回路 (ASIC) を用いるが、この増加は柔軟性を犠牲にした。

#### 【0009】

結局リンク速度の著しい増加が「通信速度」処理を現在の「汎用処理装置」ソリューションで達成できなくしてしまった。また ASIC の固定的な性質が、それらを多くのアプリケーションに対してあまりに柔軟性の無いものにしている。しかしながら処理システム構成要素 (例えばルーティング・スイッチ、エッジ・スイッチ、ネットワーク・インター

10

20

30

40

50

フェース・カード等)の業者は、現在彼等の製品が柔軟性又は速度のどちらかにおいてさえも充分最適化されておらず、彼等の製品が両方の手法の最適な特性を提供できない限り、将来の商用領域に合わせることができない事を了解している。従ってこれら及び他の同様の挑戦に応じるために、相当数の設計者が柔軟性と速度の両方の最適な特性を合併するべくネットワーク装置(「ネットワーク処理装置」の分野)の改良に取り組んで来た。

### 【0010】

それにもかかわらず、たとえ製造業者の今日のネットワーク処理装置の設計が、柔軟性対速度の最適化問題をそれなりに解決することに成功してきたとは言え、まだ多くの解決すべき重大な問題が存在する。例えば既存のネットワーク処理装置のアーキテクチャは「汎用処理装置」を比較的高価なプログラム不可能なASICと合併する従来の技術に依存している。しかしながら、フィールド・プログラム可能ゲート・アレイ(FPGA)を用いる再構成可能計算技術の進歩が、再構成可能であって将来の宇宙空間ミッション要件に適合できる特注のハードウェア・ソリューションを提供することによって将来のネットワーク処理装置アーキテクチャの付加的な柔軟性をもたらした。そのような進歩にもかかわらず、この手法の主要な欠点は、得られる柔軟性の量を著しく制限するFPGAの設計における本質的な欠陥があることである。例えば今日のFPGA装置は、多数の固定的に接続された微粒子状のプログラム可能資源から構成されている。しかしながら、これらのFPGAのプログラム可能な基本構造の固定的に接続された性質は、再構成可能な計算パラダイムの全ての構想を実装する目標にはとても及ばないものにしている。なぜなら、現在のFPGA設計は粗粒子状のアプリケーション(例えば物理的相互接続及び設計技術者の活動に関して)を実装する事に対してスケーラブルでないからである。従って例えば宇宙を基礎とするアプリケーションに対して用いる事ができる、再構成可能計算パラダイムによって必要とされる全ての構成要素を効果的に統合し、柔軟性と速度の間の最適なバランスを提供するネットワーク・アーキテクチャを提供することが有利である。以下に詳細に説明するように、本願発明はチップ上に実装でき、上述のインターフェース設計問題と他の関連する問題を解決する、新規な再構成可能ネットワークを提供する。

### 【発明の開示】

#### 【課題を解決するための手段】

### 【0011】

本願発明は、容易にプログラム可能で高度に柔軟な、構成要素と機能の階層的構造を含む、半導体チップ上に実装可能な再構成可能ネットワーク用のアーキテクチャを提供する。本願発明の好適な実施例によって、再構成可能なコンピューティング、チップ上のシステム、及びチップ上のネットワークの各設計局面を含む、チップ上の再構成可能なネットワークが提供される。より正確には、チップ上の再構成可能なネットワークは、ソフトウェア・タスクを実装するための複数の汎用マイクロ・プロセッサと、プロセッサの協調とともに大きなデータ構造の処理を容易にするための複数のオン・チップ・メモリと、組み込みの個々に再構成可能なプログラム可能論理アレイを含む複数の再構成可能実行ユニットと、オンチップ・メモリとネットワーク又はバス間に相互接続を提供する複数の構成可能なシステム・インターフェース・ユニットと、全ての再構成可能実行ユニット、構成可能なシステム・インターフェース・ユニット及び汎用マイクロ・プロセッサ間で通信を可能とするネットワーク相互接続インターフェースを含むオンチップ・ネットワークと、特定のインターフェースに対する関連入出力信号を収集してそれらを指定されたシステム・インターフェース資源に付与する微粒子相互接続ユニットと、及び、オンチップ・インターフェース資源と特定の外部ネットワーク又は装置インターフェース間にリンクを供給する複数の入出力ブロックとを含む。都合の良いことには、本願発明は、このネットワークは再構成可能な実行ユニットの構成待ち時間を最小化し、進行中に再構成を可能とする、チップ上に実装可能な再構成可能ネットワークを提供する。

### 【0012】

発明の新規と信じられる特徴は、添付の請求項に規定されている。しかしながらこの発明それ自身は、使用の好適な態様と、更にはその目的と利点と共に、添付の図面に関して

10

20

30

40

50

例示する以下の実施例の詳細な説明を参考し読むことによって最適に理解されるであろう。

【実施例】

【0013】

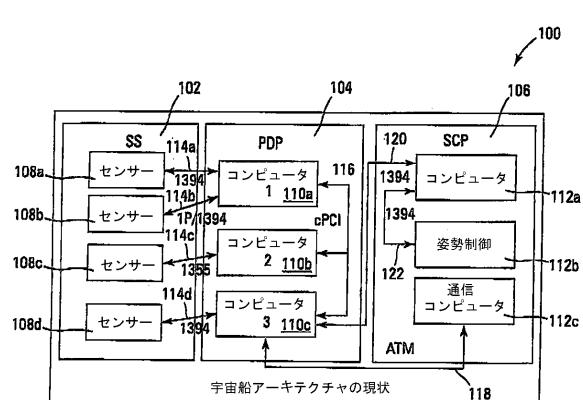

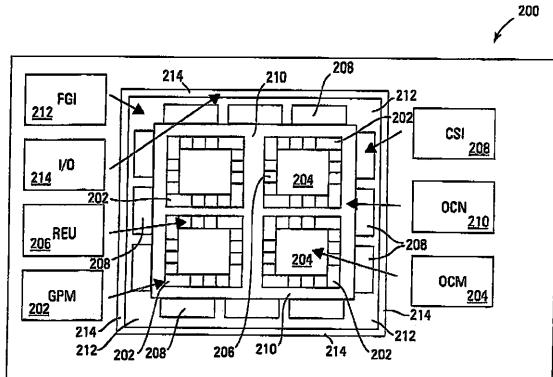

再度図面を参考すると、図2は本願発明の好適な実施例を実装するために使用出来る再構成可能ネットワーク200のアーキテクチャの一例のブロック図を示す。図示のように、この実施例に対しては、図2の再構成可能ネットワーク200は半導体チップ上の複数のネットワーク処理資源としての特定の構成に設計されている。しかしながら、本願発明はこれに限定されることを意図しておらず、任意の適当な設計及び/又は多くの示されたネットワーク処理資源をその範囲に含むものとして理解されるべきである。ネットワーク処理資源の実際の数や設計は、目標となる半導体プロセスや含まれる応用の技術によって大部分は規定される。また、本願発明は半導体チップにのみ限定されるものではない。それとして、この実施例に対しては、再構成可能ネットワーク200は、16個の汎用マイクロプロセッサ202と、4個のオンチップ記憶ユニット204と、48個の再構成可能実行ユニット206と、12個の構成可能システム・インターフェースユニット208と、1個のオンチップ・ネットワーク210と、1個の微粒子相互接続ユニット212と、複数の入出力ブロック214とを含む。

【0014】

より正確には、図2に示されたように、再構成可能ネットワーク200は、4個のマイクロプロセッサ・ユニット202と、各オンチップ記憶ユニット204と関連しつつ極めて接近して配置されている12個の再構成可能実行ユニット206とを含む。各マイクロプロセッサ・ユニット202は、例えば、主としてソフトウェア・タスクを実行し、ローカル・メモリと、関連するオンチップ記憶ユニット204及びオンチップ・ネットワークへの適当なインターフェースとをも含む埋め込みマイクロプロセッサであり得る。好適には、各オンチップ記憶ユニット204は、必要とする実行資源のサブセットへアクセス可能なマルチポート記憶装置である。従って、各オンチップ記憶ユニット204は、メモリ集約的な応用に対する共有記憶資源（この例では4個のマイクロプロセッサによって共有される）を提供し、大きなデータ構造の処理を容易にし、必要とするマイクロプロセッサ間の協同を向上させる。

【0015】

加えて、図2に示されたように、連続する2個の汎用マイクロプロセッサ・ユニット202の各々の間に配置された、3個の再構成可能実行ユニット206がある。この実施例では、各再構成可能実行ユニット206は、組み込みの独立した再構成可能なプログラム可能論理アレイとして実装され得る。また、各再構成可能実行ユニット206は、関連するオンチップ記憶ユニット204とオンチップ・ネットワーク210へのハードウェイの専用インターフェースを含む。例えば、動作において、FPGAを目標とするために用いられるのと同じ技術を用いて、単一タスクが特定の再構成可能実行ユニット206への実行に対して目標とされ得る。選択的に、再構成可能実行ユニット206の隣接する3個の内の2個又は全てを、大きなプログラム可能アレイを形成するために組み合わせる事ができ、これは応用が单一の再構成可能実行ユニットに対して大きすぎる場合及び/又はその応用がサブセットに分割することが容易でない場合に有利である。

【0016】

オンチップ・ネットワーク210（例えば、関連する汎用マイクロプロセッサと再構成可能実行ユニットとを伴う4組のオンチップ記憶ユニットを包含する矩形の領域として表わされる）は、再構成可能ネットワーク200内の再構成可能実行ユニット206と構成可能システム・インターフェース・ユニット208と汎用マイクロプロセッサ・ユニット202の全ての通信を可能にするネットワーク相互接続インターフェースを提供する。構成可能システム・インターフェース・ユニット208は、任意のオンチップ記憶ユニット204、オンチップ・ネットワーク210へインターフェースするのに必要な基本的可能 性、即ち通信/データバスを提供する。従って、構成可能システム・インターフェース・

10

20

30

40

50

ユニット 208 は、異なるネットワーク・プロトコルを扱うために適合でき、この事に関して他のインターフェース対応性を提供することも出来る、完全に構成可能なシステム資源である。

【0017】

微粒子相互接続ユニット 212（例えば、オンチップ・ネットワーク 210 と 12 個の構成可能システム・インターフェース・ユニット 208 とを包含する矩形の領域として表わされる）は、再構成可能ネットワーク 200 内にある、第 1 の相互接続層を提供する。この実施例では、微粒子相互接続ユニット 212 は、複数のビットレベル・プログラム可能ルーティング資源からなる。それとして、微粒子相互接続ユニット 212 の主要な機能は、特定のインターフェースに対して関連する入出力信号を取り入れ、これらの関連する入出力信号を構成可能システム・インターフェース・ユニット 208 の割り当てられた資源へ結びつけることである。

【0018】

各入出力ブロック 214（例えば、微粒子相互接続 212 を包含する濃い矩形領域として表わされる）は、外部 pin インターフェース（例えば I/O パッド）、1 個以上のレジスタ、1 個以上の 3 状態バッファ及び他の関連する支援論理装置からなる。従って、各入出力ブロック 214 の主要な機能は、オンチップ・インターフェース資源間の適当なリンクと、特定の外部（オフチップ）ネットワーク、システム又は装置に対するインターフェースを提供することである。この事に関して有利なことは、物理層に実装された多くの基準がこの入出力ブロック 214 に統合され得、それによって外部要素の必要が減ることである。

【0019】

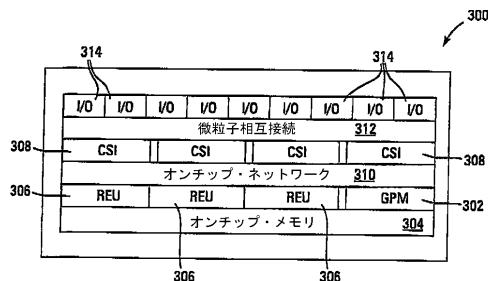

図 3 は、図 2 に示された再構成可能ネットワーク 200 の例の階層構造によって与えられる機能の高度なプログラム可能性と柔軟性とを示す図である。例えば、階層的配置 300 は、外部（オフチップ）ネットワーク、システム又は装置による再構成可能ネットワーク 200 へのアクセスを提供する入出力層 314 としての階層内の最高レベルを示す。階層の次に高いレベルは、特定のインターフェースに対して関連する入出力信号を取り入れ、これらの入出力信号を階層の次の層内の割り当てられた資源（例えば、構成可能システム・インターフェース 308）に結びつける微粒子相互接続層 312 である。階層内の次に低いレベルは、次の（低いレベルの）層内の再構成可能実行ユニット 306 及び汎用マイクロプロセッサ 302 全てと、上の層内の構成可能システム・インターフェース・ユニット 308 との間にネットワーク相互接続インターフェースを提供するオンチップ・ネットワーク層 310 である。図示の層内の最低レベルは、（例えば、次の高いレベルの 4 個のマイクロプロセッサ 302 に対する）共有記憶資源を提供するオンチップ記憶層 304 である。

【0020】

要約すれば、図 2 の再構成可能ネットワークの例は、16 個の処理クラスタ（例えば、汎用マイクロプロセッサ 202 と関連する）及び 12 個の構成可能システム・インターフェース（例えば、構成可能システム・インターフェース・ユニット 208）を含む、チップ上の再構成可能ネットワークの 2 次元構造的設計を示している。しかしながら、チップ上の再構成可能ネットワークの実際の実装に用いる設計やその様な資源の数は必要とされる実際の処理技術によって規定されることを理解されたい。好適には、目標とする宇宙空間の環境は著しい放射線許容量を要求するので、チップ上の再構成可能ネットワークの市販版の実装には CMOS プロセスが用いられるべきである。しかしながら、より極端な宇宙環境では、チップ上の再構成可能ネットワークに対する増強した放射線強度を提供するためにシリコン・オン・インシュレータ（SOI）プロセスが用いられ得る。加えて、もう 1 つの重要な目的の達成に関しては、チップ上の再構成可能ネットワークの電力消費は、広域非同期局所同期（GALS）処理手法、遊休資源の電源断、及び高周波クロック使用の制限を採用することによって著しく削減できる。

【0021】

10

20

30

40

50

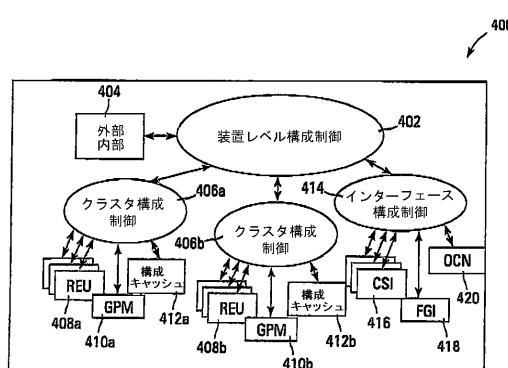

前述のように、チップ上の再構成可能ネットワークの2つの主要な目的は、再構成可能実行ユニットの構成1待ち時間(遅延)の削減と、実行時再構成の実現であった。本願発明によれば、チップ上の再構成可能ネットワーク(例えば、再構成可能ネットワーク200)は、図4に図示された構成制御システム400の例示的構造に示されたような、構成制御及びオンチップ構成キャッシュの新規な階層を用いることによって、これらの目的を達成する。本願発明の好適な実施例によれば、構成制御システム400は、示された階層の最高レベルにあり、チップ上の再構成可能ネットワーク(例えば、図2に示されたチップ上に実装された再構成可能ネットワーク200)の全構成を制御する、装置レベル構成制御ユニット402を含む。装置レベル構成制御ユニット402は、外部(例えば、オフチップ)インターフェース404への単一構成インターフェースを与え、多くの異なる構成セッティング及び構成制御スケジュールを、例えば不揮発性記憶装置(図示せず)に関連するインターフェースやオンチップネットワーク210を介して、構成可能インターフェース・ユニット208から受け取る。従って、不揮発性記憶装置(例えば、ROM、PROM、EEPROM等)は電源投入時に用いるブートストラップ構成セットを提供する。一旦装置レベル構成制御ユニット402の電源が投入されてオンラインになると、(例えば、1つ以上の構成可能システム・インターフェース・ユニット208を介して)必要とされる構成の更新を受け取り、必要に応じて、不揮発性記憶装置に記憶されている構成セット・イメージも更新する。

#### 【0022】

構成制御システム400は、示されたような階層の第2レベルである、複数のクラスタ構成制御ユニット406a、406bを含む。特に、2つのクラスタ構成制御ユニット406a、406bだけが示されているが、本願発明はこれに限定する意図はなく、用いられる処理クラスタの数に応じて追加のクラスタ構成制御ユニットを含み得る。例えば、本願発明の好適な実施例では、図2に示された再構成可能ネットワーク200内の各処理クラスタに対して1つのクラスタ構成制御ユニット406a又は406bが用いられる。結果として、この実施例に対しては、16個の処理クラスタ(16個の汎用マイクロプロセッサ202とそれらに関連する再構成可能実行ユニット206に集中された)があり、従って、図2に示した実施例に対して16個のクラスタ構成制御ユニットがある。とにかく、各クラスタ構成制御ユニット406a、406bは主としてその処理クラスタの再構成可能実行ユニット408a、408bの構成と、その処理クラスタの汎用マイクロプロセッサ410a、410bによって実行されるプログラムのロードについて責任がある。各クラスタ構成制御ユニット406a、406bの2番目の機能は、関連する処理クラスタの必要な構成スケジュールの管理である。また各クラスタ構成制御ユニット406a、406bは、関連する再構成可能実行ユニット408a、408bの組の必要な構成のローカル・キャッシュ412a、412bの管理にも責任がある。

#### 【0023】

加えて、構成制御システム400は、これも図4に示された構成制御階層の第2のレベルである、インターフェース構成制御ユニット414を含む。それとして、インターフェース構成制御ユニット414は主として構成可能システム・インターフェース・ユニット416(例えば、図2の要素208)、微粒子相互接続418(例えば、要素212)及びオンチップネットワーク420(例えば、要素210)の構成の管理をする。特に、この実施例では、インターフェース構成制御ユニット414によって管理される資源の再構成の頻度が比較的小さいので、ローカル構成キャッシュはインターフェース構成制御ユニット414には必要ない。とにかく、本願発明によって提供されるスケジュール指向構成機能に加えて、インターフェース構成もオンチップネットワーク420を通じて伝達される指令を介してトリガーされ得る。これらの指令は再構成可能ネットワーク外の(オフチップ)資源で又は内部(例えば、オンチップ)処理要素から発せられ得る。有利なことには、本願発明によって提供されるこの機能は、必要なシステムやネットワークを自律的に再構成できる適応性のある応用の実現を助ける。

#### 【0024】

現状のネットワーク構造及び設計の上述の柔軟性対速度の問題は、必要なインターフェース間をブリッジすることの可能なネットワーク・ブリッジ又はルーターとして機能できる再構成可能実行ユニットを組み込むことによって、本願発明の再構成可能ネットワークによってかなりの程度まで解決される。従って本願発明は、例えば半導体チップ上に実装され得る、柔軟な異質なネットワーク処理装置システムを提供する。これに関して、図5は、本願発明の好適な実施例を実装するために用い得る、宇宙船システム500の例を図示する。特にシステム500は、本願発明が、現状のネットワーク処理及び宇宙船システム構造（例えば、図1に示された宇宙船システムによって典型的に示されたような）のインターフェースの柔軟性と速度の問題をいかにして解決できるかを示しており、かつ必要とされる全宇宙船内の全ての構成要素間の有効な通信を提供する。

10

## 【0025】

この実施例では、宇宙船システム500はSSサブシステム502と、PDPサブシステム504と、SCPサブシステム506とを含む。これらの3つのサブシステム502、504及び506は、ATMネットワーク508で相互接続されている。特に、本願発明によれば、SSサブシステム内の種々のインターフェース・プロトコルを用いる複数のセンサー510a～510dが、再構成可能ネットワーク512によって（ATMネットワーク508を介して）サブシステム504及び506の構成要素を相互接続されている。この実施例では、再構成可能ネットワーク512は、半導体チップ上に実装されている。同様にPDPサブシステム504内のIP/イーサネット（登録商標）・プロトコルを用いる複数のコンピュータ処理装置514a～510cが、再構成可能ネットワーク516によって（ATMネットワーク508を介して）サブシステム502及び506の構成要素と相互接続されている。またSCPサブシステム内の種々のインターフェース・プロトコルを用いる複数の宇宙船制御処理装置518a～518cも、再構成可能ネットワーク520によって（ATMネットワーク508を介して）サブシステム502及び504の構成要素と相互接続されている。従って、本願発明の教示によれば、サブシステム504内のペイロード・データ処理コンピュータは局所化IP/イーサネット（登録商標）・ネットワークを用いて通信でき、各々のサブシステム502及び506内で、必要な構成要素間の通信のために局所化された異質なネットワークを与えるために、相応するインターフェースの混成を用いることができる。

20

## 【0026】

要するに、図5に示されたように、本願発明は、分散宇宙船制御応用、宇宙船ペイロード・ネットワーク及び宇宙ベースのバックボーン基盤のための強力な新しいプラットフォームを提供する。また、本願発明は、例えばチップ再構成上の動作時再構成可能ネットワーク、再構成可能実行ユニットを用いるパイプライン、そしてそれらの付随する利点を伴う組み込み汎用マイクロプロセッサを用いる、他の高効率応用を実装する適切な構造を提供する。例えば、チップ上の再構成可能ネットワークの実施例は、信号処理、制御、イメージ処理及び通信応用に用いることもできる。それとして、チップ上の再構成可能ネットワークは、単独のプロセッサとしても、または複数の再構成可能ネットワーク装置をマルチ処理システムを形成するように組み合わせるようにも用いることができる。従って本願発明は、制限されたコストで呼称しがちな環境で柔軟な資源を用いて変化するミッション要求に動的に適応することの出来る、再構成可能で、再プログラム可能な、異質システムを提供する。また本願発明は、使用される異質なインターフェースとネットワークの統合と開発時間を削減し、必要なシステムの全体的な大きさと体積を削減することによって、宇宙船ペイロードの開発時間とコストを著しく削減できる、再構成可能ネットワーク設計を提供する。

30

## 【0027】

本発明は、フルに機能する再構成可能ネットワークの文脈で説明したが、当業者は本発明のプロセスが命令のコンピュータ可読媒体の形態や種々の形態で頒布され得、本発明が実際に頒布用に用いられる信号伝達媒体の特定のタイプにかかわらず同様に応用され得ることを認めるであろう。コンピュータ可読媒体の例としては、フロッピー（登録商標）デ

40

50

イスク、ハードディスク・ドライブ、RAM、CD-ROM、DVD-ROMのような記録可能タイプ媒体、デジタル及びアナログ通信リンク、例えば高周波数及び光通信のような通信形態を用いる有線又は無線通信リンク媒体のような通信タイプ媒体を含む。コンピュータ可読媒体は、特定の再構成可能ネットワーク内で実際に用いられるために復号される、符号化フォーマットの形式をとり得る。

#### 【0028】

本発明の説明を例示と説明のために示したが、これは開示された形式に発明を網羅的に限定することを意図していない。当業者には多くの修正や変形が明瞭であろう。これらの実施例は、発明の本質、実際的な応用の最良の説明の為に選択されたもので、当業者は本発明の予想される特定の利用に適当な種々の修正を施された種々の実施例が推察できるであろう。

#### 【図面の簡単な説明】

#### 【0029】

【図1】図1は従来商用の既成の設計方法を用いた宇宙船システムの現状に対する典型的なアーキテクチャのブロック図を示す。

【図2】図2は本願発明の好適な実施例を実装する為に用い得る再構成可能なネットワークに対する例示的なアーキテクチャのブロック図を示す。

【図3】図3は図2に示した再構成可能なネットワークの例の階層的構成によってもたらされる高度なプログラム可能性及び機能の柔軟性を示す図である。

【図4】図4は本願発明の好適な実施例を実装する為に用い得る構成制御システムの1例の為のアーキテクチャを示す。

【図5】図5は本願発明の好適な実施例を実装する為に用い得る宇宙船システムの1例の図を示す。

【図1】

【図2】

【図3】

【図4】

【 四 5 】

---

フロントページの続き

(74)代理人 100096013

弁理士 富田 博行

(72)発明者 ジェレミー・ラモス

アメリカ合衆国フロリダ州33626,タンパ,エデントン・ウェイ 9401

(72)発明者 スコット・ディー・スタッклハウス

アメリカ合衆国フロリダ州33762,クリアウォーター,フェザー・サウンド・ドライブ 23

33,エイ107

(72)発明者 イアン・エイ・トロクセル

アメリカ合衆国フロリダ州32607,ゲインズヴィル,サウスウェスト・セブンティフィフス・

ストリート 705,ナンバー 103

F ターム(参考) 5J042 BA08 CA00 CA20 DA06

【外國語明細書】

2007129699000001.pdf