등록특허 10-2662460

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2024년04월30일

(11) 등록번호 10-2662460

(24) 등록일자 2024년04월26일

- (51) 국제특허분류(Int. Cl.)

*HO4W 72/04* (2009.01) *HO4L 1/18* (2023.01)

*HO4L 5/00* (2006.01) *HO4W 72/12* (2023.01)

- (52) CPC특허분류

*HO4W 72/21* (2023.01)

*HO4L 1/1812* (2023.01)

- (21) 출원번호 10-2019-7016376

- (22) 출원일자(국제) 2017년11월22일

심사청구일자 2020년11월05일

- (85) 번역문제출일자 2019년06월07일

- (65) 공개번호 10-2019-0096993

- (43) 공개일자 2019년08월20일

- (86) 국제출원번호 PCT/US2017/063125

- (87) 국제공개번호 WO 2018/111519

국제공개일자 2018년06월21일

(30) 우선권주장

62/435,495 2016년12월16일 미국(US)

15/677,851 2017년08월15일 미국(US)

## (56) 선행기술조사문헌

3GPP R1-1612074\*

3GPP R1-1613162\*

3GPP R1-1611517\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 15 항

심사관 : 노상민

## (54) 발명의 명칭 뉴 라디오에서 대용 업링크 제어 정보의 송신을 구성하기 위한 기법들 및 장치들

**(57) 요 약**

무선 통신을 위한 방법, 장치, 및 컴퓨터 프로그램 제품이 제공된다. 장치는 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 수신할 수도 있다. 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함할 수도 있다. 제 2 부분은 다운링크 제어 부분과 업링크 짧은 버스트 부분 사이에 (뒷면에 계속)

**대 표 도**

위치될 수도 있다. 장치는 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 제 1 업링크 제어 정보 (UCI) 의 송신을 위해, 제 2 부분 또는 제 1 슬롯의 업링크 짧은 버스트 부분 중 적어도 하나에 물리적 업링크 제어 채널 (PUCCH) 을 구성할 수도 있고, 제 1 UCI 는 제 1 슬롯 또는 제 2 슬롯에서 송신되는 제 2 UCI 에 대응한다. 제 1 UCI 는 제 1 슬롯 또는 제 2 슬롯에서 송신되는 제 2 UCI 에 대응할 수도 있다. 장치는 구성된 UCI 상에 제 1 UCI 를 송신할 수도 있다.

## (52) CPC특허분류

*H04L 1/1854* (2013.01)*H04L 5/0053* (2013.01)*H04L 5/0094* (2013.01)*H04W 72/0446* (2023.01)

## (72) 발명자

## 수 하오

미국 92121 캘리포니아주 샌디에고 모어하우스 드

라이브 5775

## 왕 웬추

미국 92121 캘리포니아주 샌디에고 모어하우스 드

라이브 5775

---

## 천 완시

미국 92121 캘리포니아주 샌디에고 모어하우스 드

라이브 5775

## 박 세용

미국 92121 캘리포니아주 샌디에고 모어하우스 드

라이브 5775

## 명세서

### 청구범위

#### 청구항 1

무선 통신의 방법으로서,

사용자 장비 (UE) 에 의해, 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 수신하는 단계로서, 상기 제 1 슬롯은 상기 다운링크 제어 부분, 업링크 긴 버스트 부분, 및 업링크 짧은 버스트 부분을 포함하고, 상기 업링크 긴 버스트 부분은 상기 다운링크 제어 부분과 상기 업링크 짧은 버스트 부분 사이에 위치되는, 상기 업링크 제어 구성 표시를 수신하는 단계;

상기 UE 에 의해, 상기 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 제 1 업링크 제어 정보 (UCI) 및 제 2 UCI 의 송신을 위해, 상기 제 1 슬롯의 상기 업링크 긴 버스트 부분 및 상기 업링크 짧은 버스트 부분 양자에 물리적 업링크 제어 채널 (PUCCH) 을 구성하는 단계로서, 상기 제 1 UCI 및 상기 제 2 UCI 는 공동으로 인코딩된 UCI 로서 공동으로 인코딩되고, 상기 제 1 UCI 및 상기 제 2 UCI 는 상기 제 1 슬롯에서 송신되는, 상기 PUCCH 를 구성하는 단계; 및

상기 UE 에 의해, 구성된 상기 PUCCH 상에서 상기 제 1 UCI 및 상기 제 2 UCI 를 송신하는 단계;

를 포함하는, 무선 통신의 방법.

#### 청구항 2

제 1 항에 있어서,

상기 업링크 제어 구성 표시는 상기 PUCCH 가 단지 상기 업링크 긴 버스트 부분에서 또는 상기 업링크 긴 버스트 부분과 상기 업링크 짧은 버스트 부분 쌍방에서 구성되어야 하는지 여부를 표시하는, 무선 통신의 방법.

#### 청구항 3

제 2 항에 있어서,

상기 공동으로 인코딩된 UCI 의 하나 이상의 비트들은, 상기 PUCCH 가 단지 상기 업링크 긴 버스트 부분에서 구성되어야 한다고 상기 업링크 제어 구성 표시가 표시하는 때 절단되는 (truncated), 무선 통신의 방법.

#### 청구항 4

제 2 항에 있어서,

상기 공동으로 인코딩된 UCI 의 하나 이상의 비트들은, 상기 PUCCH 가 상기 업링크 긴 버스트 부분과 상기 업링크 짧은 버스트 부분 쌍방에서 구성되어야 한다고 상기 업링크 제어 구성 표시가 표시하는 때 상기 업링크 짧은 버스트 부분에서 반복 및 송신되는, 무선 통신의 방법.

#### 청구항 5

무선 통신의 방법으로서,

사용자 장비 (UE) 에 의해, 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 수신하는 단계로서, 상기 제 1 슬롯은 상기 다운링크 제어 부분, 업링크 긴 버스트 부분, 및 업링크 짧은 버스트 부분을 포함하고, 상기 업링크 긴 버스트 부분은 상기 다운링크 제어 부분과 상기 업링크 짧은 버스트 부분 사이에 위치되는, 상기 업링크 제어 구성 표시를 수신하는 단계;

상기 UE 에 의해, 상기 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 제 1 업링크 제어 정보 (UCI) 및 제 2 UCI 의 송신을 위해, 상기 제 1 슬롯의 상기 업링크 긴 버스트 부분 및 상기 업링크 짧은 버스트 부분 양자에 물리적 업링크 제어 채널 (PUCCH) 을 구성하는 단계로서, 상기 제 2 UCI 는 상기 제 1 UCI 의 반복이고, 상기 제 1 UCI 및 상기 제 2 UCI 는 상기 제 1 슬롯에서 송신되는, 상기 PUCCH 를 구성하는 단계; 및

상기 UE 에 의해, 구성된 상기 PUCCH 상에서 상기 제 1 UCI 및 상기 제 2 UCI 를 송신하는 단계;

를 포함하는, 무선 통신의 방법.

#### 청구항 6

제 1 항 또는 제 5 항에 있어서,

상기 PUCCH 는 상기 업링크 제어 구성 표시에서 시그널링되거나 상기 업링크 제어 구성 표시의 수신과 관련된 특성으로부터 도출된 하나 이상의 주파수 대역들 상에서 구성되는, 무선 통신의 방법.

#### 청구항 7

제 6 항에 있어서,

상기 하나 이상의 주파수 대역들은 상기 업링크 긴 버스트 부분에서의 하나 이상의 제 1 주파수 대역들 및 상기 업링크 짧은 버스트 부분에서의 하나 이상의 제 2 주파수 대역들을 포함하고, 상기 하나 이상의 제 1 주파수 대역들은,

상기 하나 이상의 제 2 주파수 대역들과 동일하거나, 또는

상기 하나 이상의 제 2 주파수 대역들과 상이한, 무선 통신의 방법.

#### 청구항 8

제 1 항 또는 제 5 항에 있어서,

물리적 업링크 공유 채널 (PUSCH) 은 상기 제 1 UCI 또는 상기 제 2 UCI 중 적어도 하나의 송신과 동시에 콘텐츠의 송신을 위해 상기 업링크 긴 버스트 부분 또는 상기 업링크 짧은 버스트 부분 중 적어도 하나에서 구성되는, 무선 통신의 방법.

#### 청구항 9

삭제

#### 청구항 10

삭제

#### 청구항 11

삭제

#### 청구항 12

삭제

#### 청구항 13

삭제

#### 청구항 14

삭제

#### 청구항 15

삭제

#### 청구항 16

삭제

#### 청구항 17

삭제

### 청구항 18

삭제

### 청구항 19

삭제

### 청구항 20

삭제

### 청구항 21

삭제

### 청구항 22

삭제

### 청구항 23

제 1 항 또는 제 5 항에 있어서,

상기 제 1 UCI 및 상기 제 2 UCI 는,

상기 제 1 UCI 및 상기 제 2 UCI 를 포함하는 UCI 의 페이로드가 임계치 이하의 크기를 갖는 때, 반복된 UCI,

상기 UCI 의 페이로드를 송신하는데 사용될 슬롯들의 수가 임계치 이상인 때, 반복된 UCI ,

상기 UCI 의 페이로드가 임계치 이상의 크기를 갖는 때, 공동으로 인코딩된 UCI, 또는

상기 UCI 의 페이로드를 송신하는데 사용될 슬롯들의 수가 임계치 이하인 때, 공동으로 인코딩된 UCI

이도록 구성되는, 무선 통신의 방법.

### 청구항 24

무선 통신의 방법으로서,

기지국에 의해, 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 송신하는 단계로서, 상기 제 1 슬롯은 상기 다운링크 제어 부분, 업링크 긴 버스트 부분, 및 업링크 짧은 버스트 부분을 포함하고, 상기 업링크 긴 버스트 부분은 상기 다운링크 제어 부분과 상기 업링크 짧은 버스트 부분 사이에 위치되고,

상기 업링크 제어 구성 표시는 사용자 장비 (UE) 에게 제 1 업링크 제어 정보 (UCI) 및 제 2 UCI 의 송신을 위해, 상기 제 1 슬롯의 상기 업링크 긴 버스트 부분 및 상기 업링크 짧은 버스트 부분 양자에 물리적 업링크 제어 채널 (PUCCH) 을 구성할 것을 명령하고, 상기 제 1 UCI 및 상기 제 2 UCI 는 공동으로 인코딩된 UCI 로서 공동으로 인코딩되고, 상기 제 1 UCI 및 상기 제 2 UCI 는 상기 제 1 슬롯에서 송신되는, 상기 업링크 제어 구성 표시를 송신하는 단계; 및

상기 기지국에 의해, 구성된 상기 PUCCH 상에서 상기 제 1 UCI 및 상기 제 2 UCI 를 수신하는 단계;

를 포함하는, 무선 통신의 방법.

### 청구항 25

무선 통신을 위한 사용자 장비 (UE) 로서,

메모리; 및

상기 메모리에 동작가능하게 커플링된 하나 이상의 프로세서들을 포함하고, 상기 메모리 및 상기 하나 이상의 프로세서들은,

제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 수신하는 것으로서, 상기 제 1 슬롯은 상기 다운링크 제어 부분, 업링크 긴 버스트 부분, 및 업링크 짧은 버스트 부분을 포함하고, 상기 업링크 긴 버스트 부분은 상기 다운링크 제어 부분과 상기 업링크 짧은 버스트 부분 사이에 위치되는, 상기 업링크 제어 구성 표시를 수신하고;

상기 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 제 1 업링크 제어 정보 (UCI) 및 제 2 UCI 의 송신을 위해, 상기 제 1 슬롯의 상기 업링크 긴 버스트 부분 및 상기 업링크 짧은 버스트 부분 양자에 물리적 업링크 제어 채널 (PUCCH) 을 구성하는 것으로서, 상기 제 1 UCI 및 상기 제 2 UCI 는 공동으로 인코딩된 UCI 로서 공동으로 인코딩되고, 상기 제 1 UCI 및 상기 제 2 UCI 는 상기 제 1 슬롯에서 송신되는, 상기 PUCCH 를 구성하고; 그리고

구성된 상기 PUCCH 상에서 상기 제 1 UCI 및 상기 제 2 UCI 를 송신하도록

구성되는, 무선 통신을 위한 사용자 장비 (UE).

### 청구항 26

무선 통신을 위한 기지국으로서,

메모리; 및

상기 메모리에 동작가능하게 커플링된 하나 이상의 프로세서들을 포함하고, 상기 메모리 및 상기 하나 이상의 프로세서들은,

제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 송신하는 것으로서, 상기 제 1 슬롯은 상기 다운링크 제어 부분, 업링크 긴 버스트 부분, 및 업링크 짧은 버스트 부분을 포함하고, 상기 업링크 긴 버스트 부분은 상기 다운링크 제어 부분과 상기 업링크 짧은 버스트 부분 사이에 위치되고,

상기 업링크 제어 구성 표시는 사용자 장비 (UE) 에게 제 1 업링크 제어 정보 (UCI) 및 제 2 UCI 의 송신을 위해, 상기 제 1 슬롯의 상기 업링크 긴 버스트 부분 및 상기 업링크 짧은 버스트 부분 양자에 물리적 업링크 제어 채널 (PUCCH) 을 구성할 것을 명령하고, 상기 제 1 UCI 및 상기 제 2 UCI 는 공동으로 인코딩된 UCI 로서 공동으로 인코딩되고, 상기 제 1 UCI 및 상기 제 2 UCI 는 상기 제 1 슬롯에서 송신되는, 상기 업링크 제어 구성 표시를 송신하고; 그리고

구성된 상기 PUCCH 상에서 상기 제 1 UCI 및 상기 제 2 UCI 를 수신하도록

구성되는, 무선 통신을 위한 기지국.

### 청구항 27

무선 통신의 방법으로서,

기지국에 의해, 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 송신하는 단계로서, 상기 제 1 슬롯은 상기 다운링크 제어 부분, 업링크 긴 버스트 부분, 및 업링크 짧은 버스트 부분을 포함하고, 상기 업링크 긴 버스트 부분은 상기 다운링크 제어 부분과 상기 업링크 짧은 버스트 부분 사이에 위치되고,

상기 업링크 제어 구성 표시는 사용자 장비 (UE) 에게 제 1 업링크 제어 정보 (UCI) 및 제 2 UCI 의 송신을 위해, 상기 제 1 슬롯의 상기 업링크 긴 버스트 부분 및 상기 업링크 짧은 버스트 부분 양자에 물리적 업링크 제어 채널 (PUCCH) 을 구성할 것을 명령하고, 상기 제 2 UCI 는 상기 제 1 UCI 의 반복이고, 상기 제 1 UCI 및 상기 제 2 UCI 는 상기 제 1 슬롯에서 송신되는, 상기 업링크 제어 구성 표시를 송신하는 단계; 및

상기 기지국에 의해, 구성된 상기 PUCCH 상에서 상기 제 1 UCI 및 상기 제 2 UCI 를 수신하는 단계;

를 포함하는, 무선 통신의 방법.

### 청구항 28

무선 통신을 위한 사용자 장비 (UE) 로서,

메모리; 및

상기 메모리에 동작가능하게 커플링된 하나 이상의 프로세서들을 포함하고, 상기 메모리 및 상기 하나 이상의

프로세서들은,

제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 수신하는 것으로서, 상기 제 1 슬롯은 상기 다운링크 제어 부분, 업링크 긴 버스트 부분, 및 업링크 짧은 버스트 부분을 포함하고, 상기 업링크 긴 버스트 부분은 상기 다운링크 제어 부분과 상기 업링크 짧은 버스트 부분 사이에 위치되는, 상기 업링크 제어 구성 표시를 수신하고;

상기 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 제 1 업링크 제어 정보 (UCI) 및 제 2 UCI 의 송신을 위해, 상기 제 1 슬롯의 상기 업링크 긴 버스트 부분 및 상기 업링크 짧은 버스트 부분 양자에 물리적 업링크 제어 채널 (PUCCH) 을 구성하는 것으로서, 상기 제 2 UCI 는 상기 제 1 UCI 의 반복이고, 상기 제 1 UCI 및 상기 제 2 UCI 는 상기 제 1 슬롯에서 송신되는, 상기 PUCCH 를 구성하고; 그리고

구성된 상기 PUCCH 상에서 상기 제 1 UCI 및 상기 제 2 UCI 를 송신하도록

구성되는, 무선 통신을 위한 사용자 장비 (UE).

## 청구항 29

무선 통신을 위한 기지국으로서,

메모리; 및

상기 메모리에 동작가능하게 커플링된 하나 이상의 프로세서들을 포함하고, 상기 메모리 및 상기 하나 이상의 프로세서들은,

제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 송신하는 것으로서, 상기 제 1 슬롯은 상기 다운링크 제어 부분, 업링크 긴 버스트, 및 업링크 짧은 버스트 부분을 포함하고, 상기 업링크 긴 버스트 부분은 상기 다운링크 제어 부분과 상기 업링크 짧은 버스트 부분 사이에 위치되고,

상기 업링크 제어 구성 표시는 사용자 장비 (UE) 에게 제 1 업링크 제어 정보 (UCI) 및 제 2 UCI 의 송신을 위해, 상기 제 1 슬롯의 상기 업링크 긴 버스트 부분 및 상기 업링크 짧은 버스트 부분 양자에 물리적 업링크 제어 채널 (PUCCH) 을 구성할 것을 명령하고, 상기 제 2 UCI 는 상기 제 1 UCI 의 반복이고, 상기 제 1 UCI 및 상기 제 2 UCI 는 상기 제 1 슬롯에서 송신되는, 상기 업링크 제어 구성 표시를 송신하고; 그리고

구성된 상기 PUCCH 상에서 상기 제 1 UCI 및 상기 제 2 UCI 를 송신하도록

구성되는, 무선 통신을 위한 기지국.

## 청구항 30

삭제

## 발명의 설명

### 기술 분야

[0001]

본 개시의 양태들은 일반적으로 무선 통신에 관한 것이고, 특히, 뉴 라디오에서 대응 업링크 제어 정보의 송신을 구성하기 위한 기법들 및 장치들에 관한 것이다.

### 배경 기술

[0002]

무선 통신 시스템들은, 전화, 비디오, 데이터, 메시징, 및 브로드캐스트와 같은 다양한 전기통신 서비스들을 제공하기 위해 널리 전개되어 있다. 통상적인 무선 통신 시스템들은 이용가능한 시스템 리소스들 (예를 들어, 대역폭, 송신 전력 등) 을 공유함으로써 다수의 사용자들과의 통신을 지원할 수 있는 다중 액세스 (multiple-access) 기술들을 채용할 수도 있다. 그러한 다중 액세스 기술들의 예들은, 코드분할 다중 액세스 (CDMA) 시스템, 시분할 다중 액세스 (TDMA) 시스템, 주파수 분할 다중 액세스 (FDMA) 시스템, 직교주파수 분할 다중 액세스 (OFDMA) 시스템, 단일-캐리어 주파수 분할 다중 액세스 (SC-FDMA) 시스템, 시분할 동기 코드분할 다중 액세스 (TD-SCDMA) 시스템, 및 롱 텀 에볼루션 (LTE) 을 포함한다. LTE/LTE-어드밴스드는 제3세대 파트너쉽 프로젝트 (3GPP) 에 의해 공포된 유니버설 모바일 원격통신 시스템 (UMTS) 모바일 표준에 대한 개선들의 세트이다.

[0003] 무선 통신 네트워크는, 다수의 사용자 장비들 (UE들)에 대한 통신을 지원할 수 있는 다수의 기지국들 (BS)을 포함할 수도 있다. UE는 다운링크 및 업링크를 통해 BS와 통신할 수도 있다. 다운링크 (또는 순방향 링크)는 BS로부터 UE로의 통신 링크를 지칭하고, 업링크 (또는 역방향 링크)는 UE로부터 BS로의 통신 링크를 지칭한다. 본원에서 더 상세히 설명되는 것처럼, BS는 노드 B, gNB, 액세스 포인트 (AP), 무선 헤드, 송신 수신 포인트 (TRP), 뉴 라디오 (NR) BS, 5G 노드 B 등으로서 지칭될 수도 있다.

[0004] 이 다중 액세스 기술들은, 상이한 무선 통신 디바이스들로 하여금 도시, 국가, 지방 및 심지어 글로벌 레벨에서 통신할 수 있게 하는 공통 프로토콜을 제공하기 위해 다양한 전기통신 표준들에서 채택되었다. 5G로서도 지칭될 수도 있는 뉴 라디오 (NR)는 제 3 세대 파트너쉽 프로젝트 (3GPP)에 의해 공표된 LTE 모바일 표준에 대한 향상률들의 세트이다. NR은 스펙트럼 효율을 개선하고, 비용들을 저하시키고, 서비스들을 개선시키고, 새로운 스펙트럼을 이용하고, 다운링크 (DL) 상에서 사이클릭 프리픽스 (cyclic prefix; CP)를 갖는 OFDM (CP-OFDM)를 이용하고, 업링크 (UL) 상에서 CP-OFDM 및/또는 SC-FDM (예를 들어, 이산 푸리에 변환 확산 OFDM (DFT-s-OFDM)으로도 알려짐)을 사용할 뿐아니라 베이밍 (beamforming), 다중-입력 다중-출력 (MIMO) 안테나 기술, 및 캐리어 집성 (carrier aggregation)을 지원하는 다른 개방 표준들과 더 양호하게 통합함으로써 이동 광대역 인터넷 액세스를 더 양호하게 지원하도록 설계된다. 하지만, 이동 광대역 액세스에 대한 수요가 계속 증가함에 따라, NR 및 LTE 기술에서 추가 개선의 필요성이 존재한다. 바람직하게, 이 개선들은 다른 다중 액세스 기술들에 그리고 이 기술들을 채용하는 전기통신 표준들에 적용가능해야 한다.

### 발명의 내용

[0005] 본 개시의 일 양태에서, 방법, 장치 및 컴퓨터 프로그램 제품이 제공된다.

[0006] 몇몇 양태들에서, 방법은, 사용자 장비 (UE)에 의해, 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 수신하는 단계로서, 상기 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함하고, 상기 제 2 부분은 상기 다운링크 제어 부분과 상기 업링크 짧은 버스트 부분 사이에 위치되는, 상기 업링크 제어 구성 표시를 수신하는 단계를 포함할 수도 있다. 방법은, UE에 의해, 상기 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 제 1 업링크 제어 정보 (UCI)의 송신을 위해, 상기 제 1 슬롯의 상기 제 2 부분 또는 상기 업링크 짧은 버스트 부분 중 적어도 하나에 물리적 업링크 제어 채널 (PUCCH)을 구성하는 단계로서, 상기 제 1 UCI는 상기 제 1 슬롯 또는 제 2 슬롯에서 송신될 제 2 UCI에 대응하는, 상기 PUCCH를 구성하는 단계를 포함할 수도 있다. 방법은, UE에 의해, 구성된 PUCCH 상에서 상기 제 1 UCI를 송신하는 단계를 포함할 수도 있다.

[0007] 몇몇 양태들에서, 장치는 메모리 및 메모리에 커플링된 적어도 하나의 프로세서를 포함할 수도 있다. 적어도 하나의 프로세서는 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 수신하도록 구성될 수도 있고, 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함하고, 제 2 부분은 다운링크 제어 부분과 업링크 짧은 버스트 부분 사이에 위치된다. 적어도 하나의 프로세서는, 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 제 1 UCI의 송신을 위해, 제 1 슬롯의 제 2 부분 또는 업링크 짧은 버스트 부분 중 적어도 하나에 PUCCH를 구성하도록 구성될 수도 있고, 제 1 UCI는 제 1 슬롯 또는 제 2 슬롯에서 송신되는 제 2 UCI에 대응한다. 적어도 하나의 프로세서는 구성된 PUCCH 상에서 제 1 UCI를 송신하도록 구성될 수도 있다.

[0008] 몇몇 양태들에서, 장치는, 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 수신하기 위한 수단을 포함할 수도 있고, 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함하고, 제 2 부분은 다운링크 제어 부분과 업링크 짧은 버스트 부분 사이에 위치된다. 장치는, 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 제 1 UCI의 송신을 위해, 제 1 슬롯의 제 2 부분 또는 업링크 짧은 버스트 부분 중 적어도 하나에 PUCCH를 구성하기 위한 수단을 포함할 수도 있고, 제 1 UCI는 제 1 슬롯 또는 제 2 슬롯에서 송신되는 제 2 UCI에 대응한다. 장치는 구성된 PUCCH 상에 제 1 UCI를 송신하기 위한 수단을 포함할 수도 있다.

[0009] 몇몇 양태들에서, 컴퓨터 프로그램 제품은 컴퓨터 실행가능 코드를 저장하는 비일시적 컴퓨터 판독가능 매체를 포함할 수도 있다. 코드는, 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 수신하기 위한 코드를 포함할 수도 있고, 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함하고, 제 2 부분은 다운링크 제어 부분과 업링크 짧은 버스트 부분 사이에 위치된다. 코드는, 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 제 1 UCI의 송신을 위해, 제 1 슬롯의 제 2 부분 또는 업링크 짧은 버

스트 부분 중 적어도 하나에 PUCCH 를 구성하기 위한 코드를 포함할 수도 있고, 제 1 UCI 는 제 1 슬롯 또는 제 2 슬롯에서 송신되는 제 2 UCI 에 대응한다. 코드는 구성된 PUCCH 상에 제 1 UCI 를 송신하기 위한 코드를 포함할 수도 있다.

[0010] 몇몇 양태들에서, 방법은, 기지국에 의해, 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 송신하는 단계를 포함할 수도 있고, 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함하고, 제 2 부분은 다운링크 제어 부분과 업링크 짧은 버스트 부분 사이에 위치되고, 업링크 제어 구성 표시는 제 1 업링크 제어 정보 (UCI) 의 송신을 위해 사용자 장비 (UE) 에게 제 1 슬롯의 제 2 부분 또는 업링크 짧은 버스트 부분 중 적어도 하나에서 물리적 업링크 제어 채널 (PUCCH) 을 구성할 것을 명령하고, 제 1 UCI 는 제 1 슬롯 또는 제 2 슬롯에서 UE 에 의해 송신되는 제 2 UCI 에 대응한다. 방법은, 기지국에 의해, 구성된 PUCCH 상에서 제 1 UCI 를 수신하는 단계를 포함할 수도 있다.

[0011] 몇몇 양태들에서, 장치는 메모리 및 메모리에 커플링된 적어도 하나의 프로세서를 포함할 수도 있다. 적어도 하나의 프로세서는 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 송신하도록 구성될 수도 있고, 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함하고, 제 2 부분은 다운링크 제어 부분과 업링크 짧은 버스트 부분 사이에 위치되고, 업링크 제어 구성 표시는 제 1 UCI 의 송신을 위해 UE 에게 제 1 슬롯의 제 2 부분 또는 업링크 짧은 버스트 부분 중 적어도 하나에서 PUCCH 을 구성할 것을 명령하고, 제 1 UCI 는 제 1 슬롯 또는 제 2 슬롯에서 UE 에 의해 송신되는 제 2 UCI 에 대응한다. 적어도 하나의 프로세서는 구성된 PUCCH 상에서 제 1 UCI 를 수신하도록 구성될 수도 있다.

[0012] 몇몇 양태들에서, 장치는 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 송신하기 위한 수단을 포함할 수도 있고, 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함하고, 제 2 부분은 다운링크 제어 부분과 업링크 짧은 버스트 부분 사이에 위치되고, 업링크 제어 구성 표시는 제 1 UCI 의 송신을 위해 UE 에게 제 1 슬롯의 제 2 부분 또는 업링크 짧은 버스트 부분 중 적어도 하나에서 PUCCH 을 구성할 것을 명령하고, 제 1 UCI 는 제 1 슬롯 또는 제 2 슬롯에서 UE 에 의해 송신되는 제 2 UCI 에 대응한다. 장치는 구성된 PUCCH 상에 제 1 UCI 를 수신하기 위한 수단을 포함할 수도 있다.

[0013] 몇몇 양태들에서, 컴퓨터 프로그램 제품은 컴퓨터 실행가능 코드를 저장하는 비일시적 컴퓨터 판독가능 매체를 포함할 수도 있다. 코드는 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 송신하기 위한 코드를 포함할 수도 있고, 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함하고, 제 2 부분은 다운링크 제어 부분과 업링크 짧은 버스트 부분 사이에 위치되고, 업링크 제어 구성 표시는 제 1 UCI 의 송신을 위해 UE 에게 제 1 슬롯의 제 2 부분 또는 업링크 짧은 버스트 부분 중 적어도 하나에서 PUCCH 을 구성할 것을 명령하고, 제 1 UCI 는 제 1 슬롯 또는 제 2 슬롯에서 UE 에 의해 송신되는 제 2 UCI 에 대응한다. 코드는 구성된 PUCCH 상에 제 1 UCI 를 수신하기 위한 코드를 포함할 수도 있다.

[0014] 양태들은 일반적으로, 첨부 도면들을 참조하여 본원에서 실질적으로 설명되는 바와 같은 그리고 첨부 도면들에 의해 도시된 바와 같은 방법, 장치, 시스템, 컴퓨터 프로그램 제품, 비일시적 컴퓨터 판독가능 매체, 사용자 장비, 무선 통신 디바이스, 및 프로세싱 시스템을 포함한다.

[0015] 전술한 바는 이하의 상세한 설명을 더 잘 이해할 수 있도록 본 개시에 따른 예들의 특징들 및 기술적 이점들을 다소 폭넓게 약술하였다. 부가적인 특징들 및 이점들이 이하에서 설명될 것이다. 개시된 개념 및 특정 예들은 본 개시의 동일한 목적들을 수행하는 다른 구조들을 수정 또는 설계하기 위한 기반으로서 용이하게 활용될 수도 있다. 그러한 균등한 구성들은 첨부된 청구항들의 범위로부터 벗어나지 않는다. 본원에 개시된 개념들의 특징들, 그 구성 및 동작 방법 쌍방은, 관련된 이점들과 함께, 첨부 도면들과 관련하여 고려되는 때에 이하의 설명으로부터 더 잘 이해될 것이다. 도면들 각각은 오직 예시 및 설명의 목적으로만 제공되며, 청구 항들의 한계들의 정의로서 제공되는 것은 아니다.

## 도면의 간단한 설명

[0016] 도 1 은 무선 통신 네트워크의 일례를 도시한 다이어그램이다.

도 2 는 무선 통신 네트워크에서 사용자 장비 (UE) 와 통신하는 기지국의 일례를 도시한 다이어그램이다.

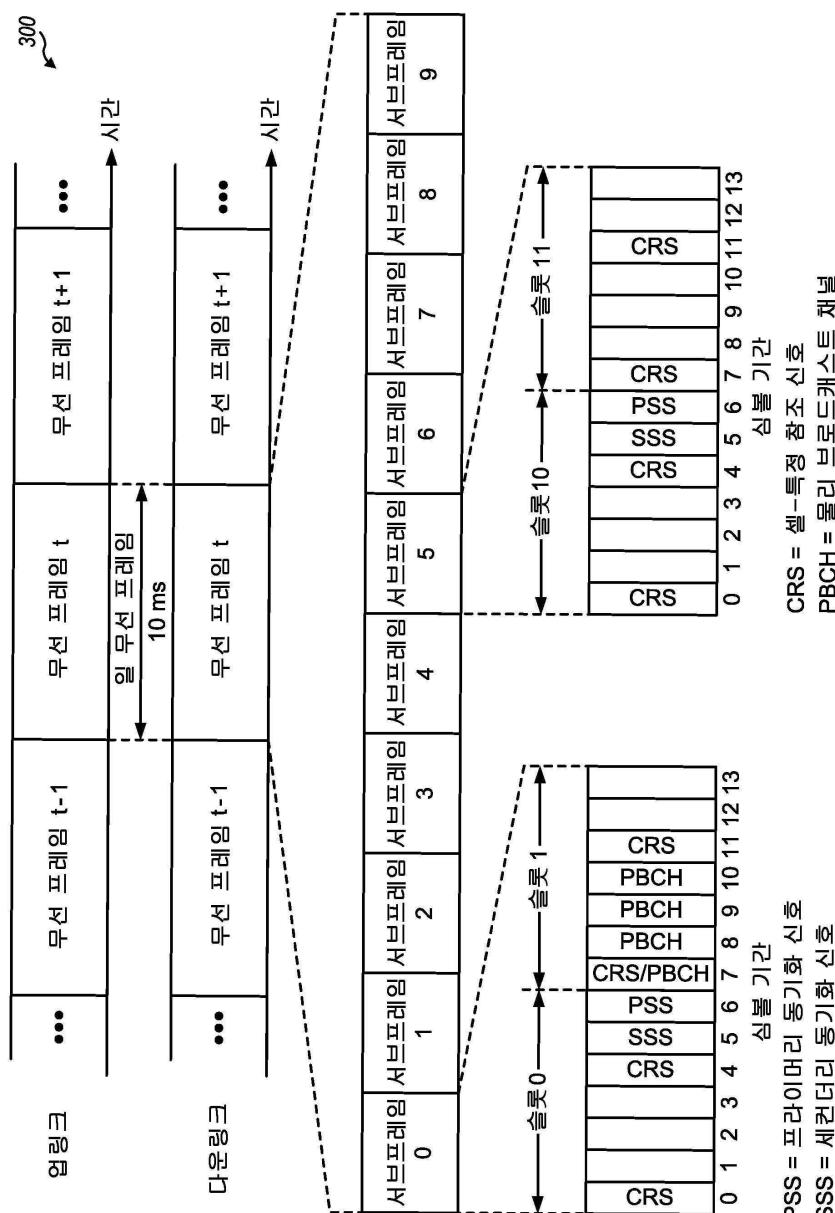

도 3 은 무선 통신 네트워크에서의 프레임 구조의 일례를 도시한 다이어그램이다.

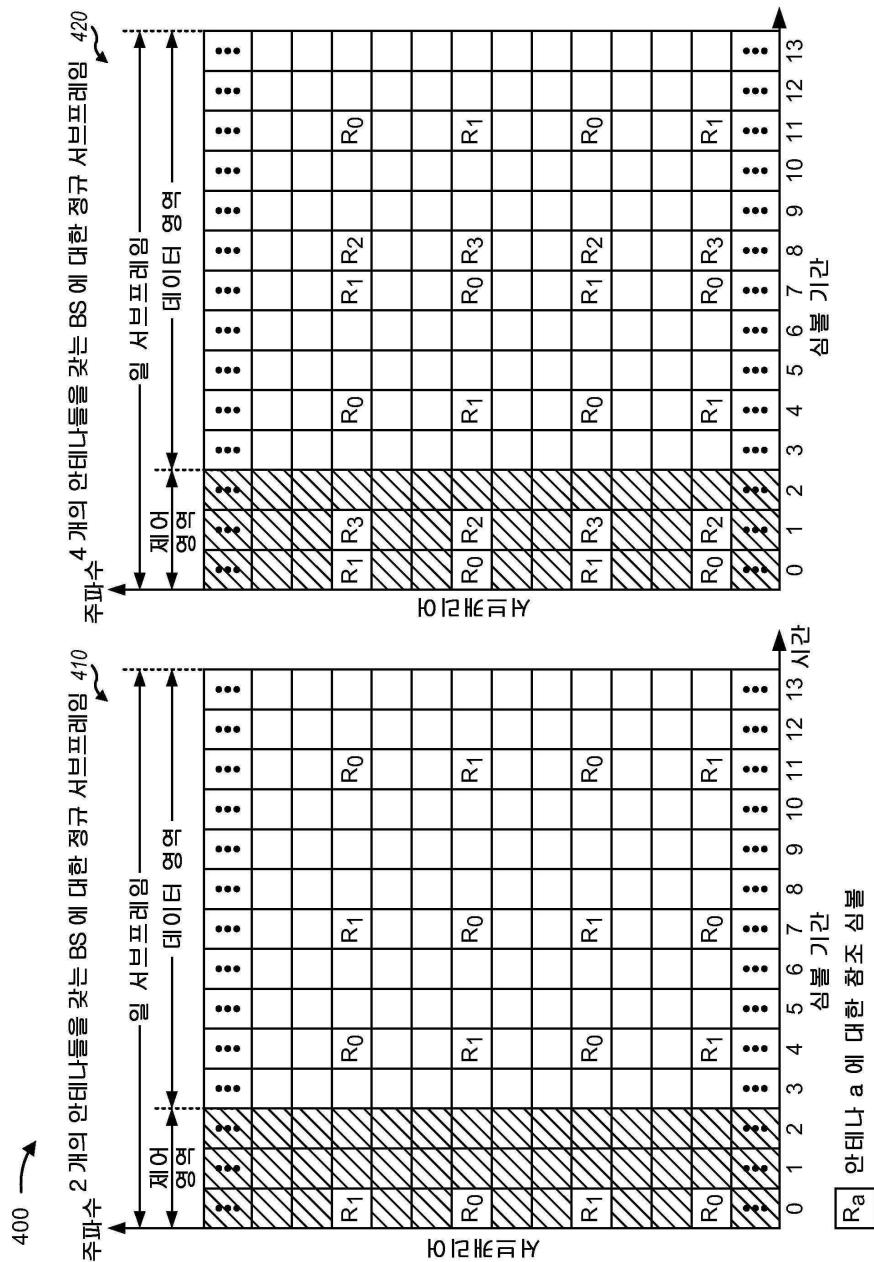

도 4 는 정규의 사이클릭 프리픽스를 갖는 2개의 예시적인 서브프레임 포맷들을 도시한 다이어그램이다.

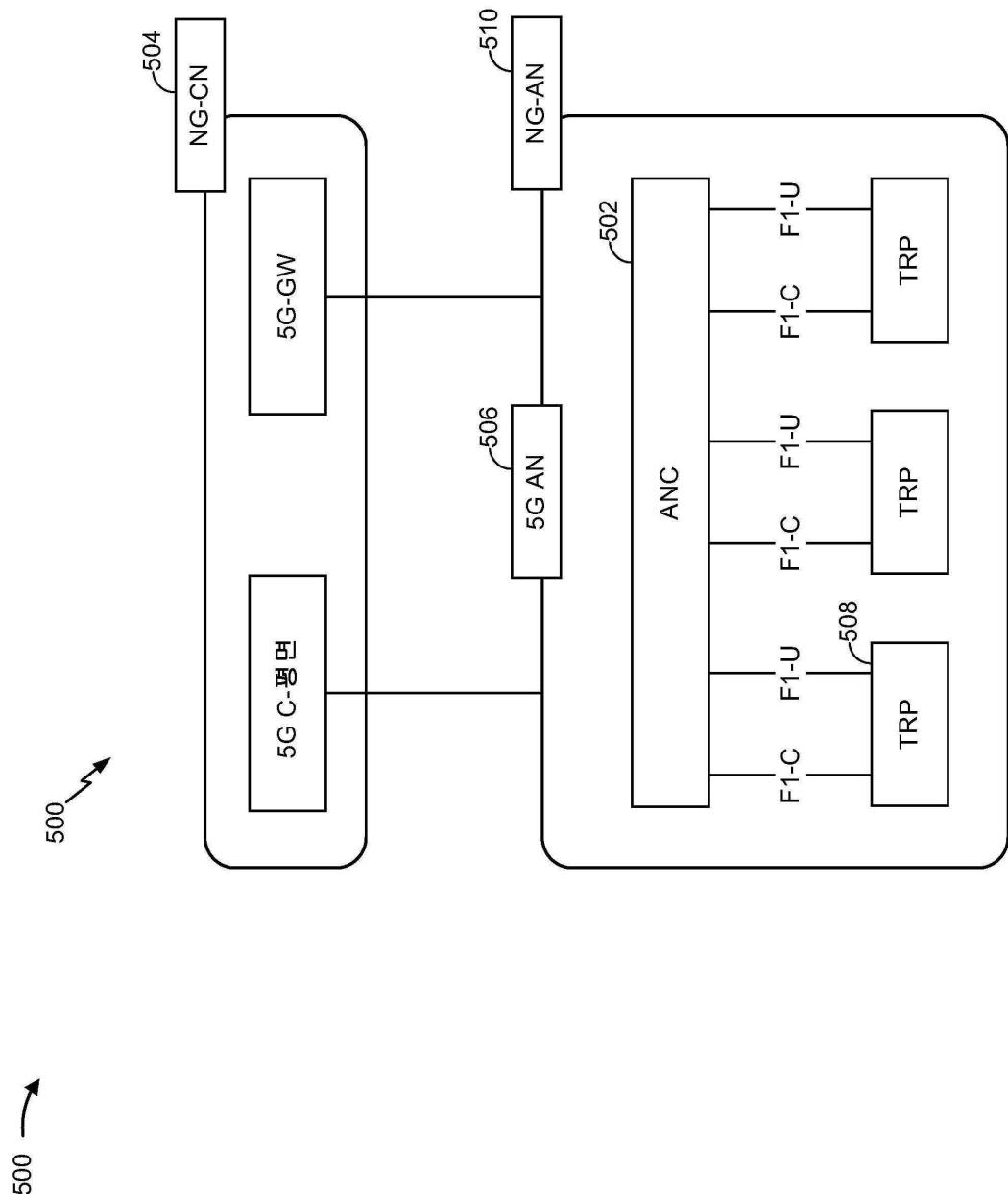

도 5 는 분포된 무선 액세스 네트워크 (RAN) 의 예시적인 논리적 아키텍처를 도시한 다이어그램이다.

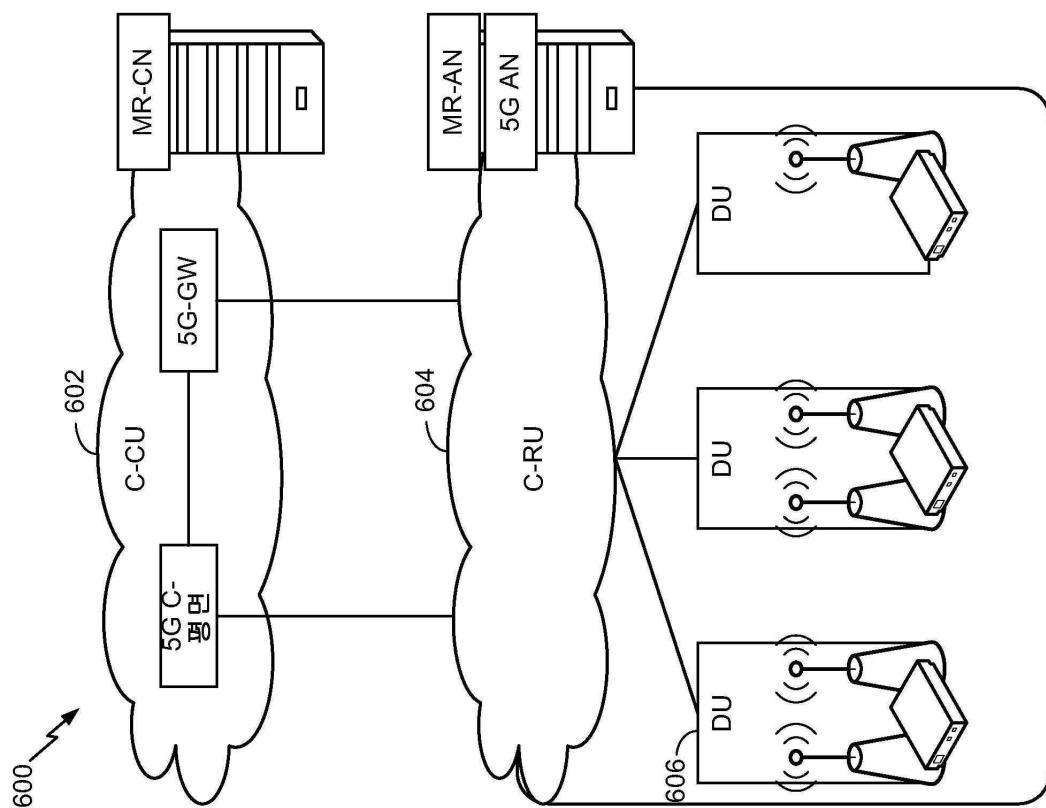

도 6 은 분포된 RAN 의 예시적인 물리적 아키텍처를 도시한 다이어그램이다.

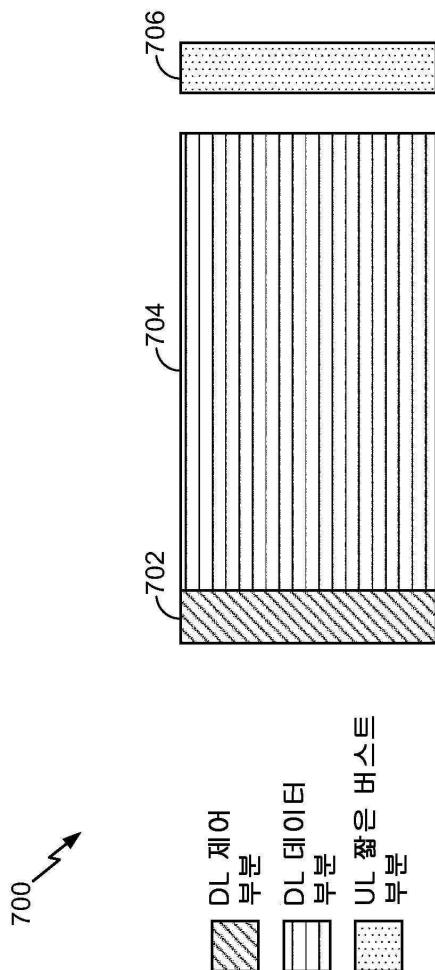

도 7 은 다운링크 (DL)-중심 슬롯의 일례를 도시한 다이아그램이다.

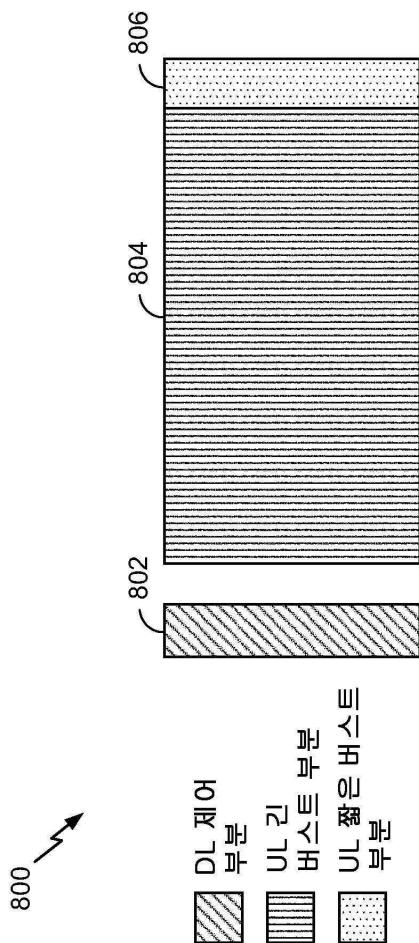

도 8 은 업링크 (UL)-중심 슬롯의 일례를 도시한 다아아그램이다.

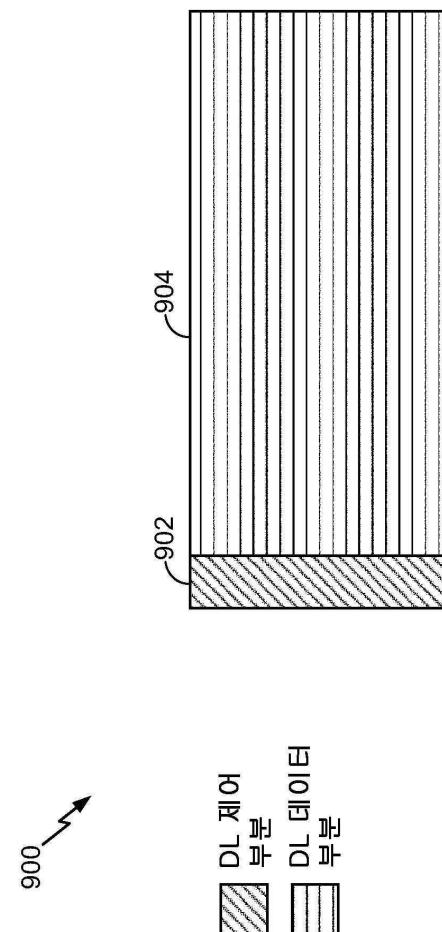

도 9 는 풀-DL 슬롯의 일례를 도시한 다이어그램이다.

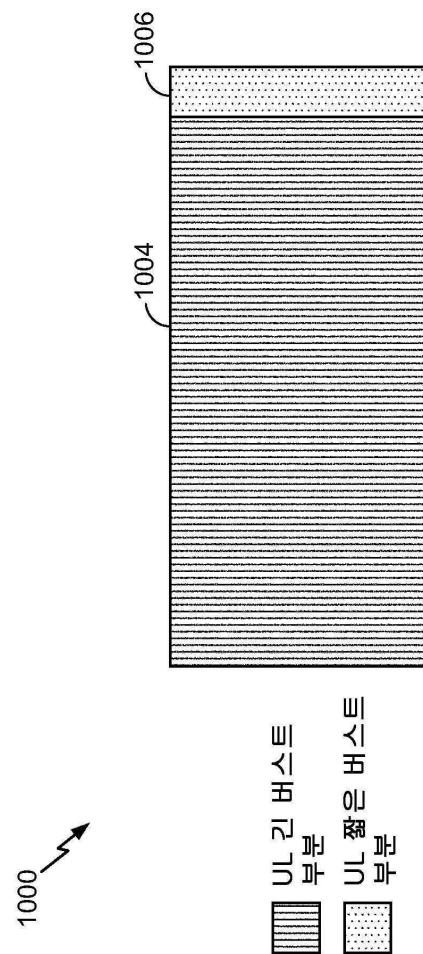

도 10 은 풀-DL 슬롯의 일례를 도시한 다이어그램이다.

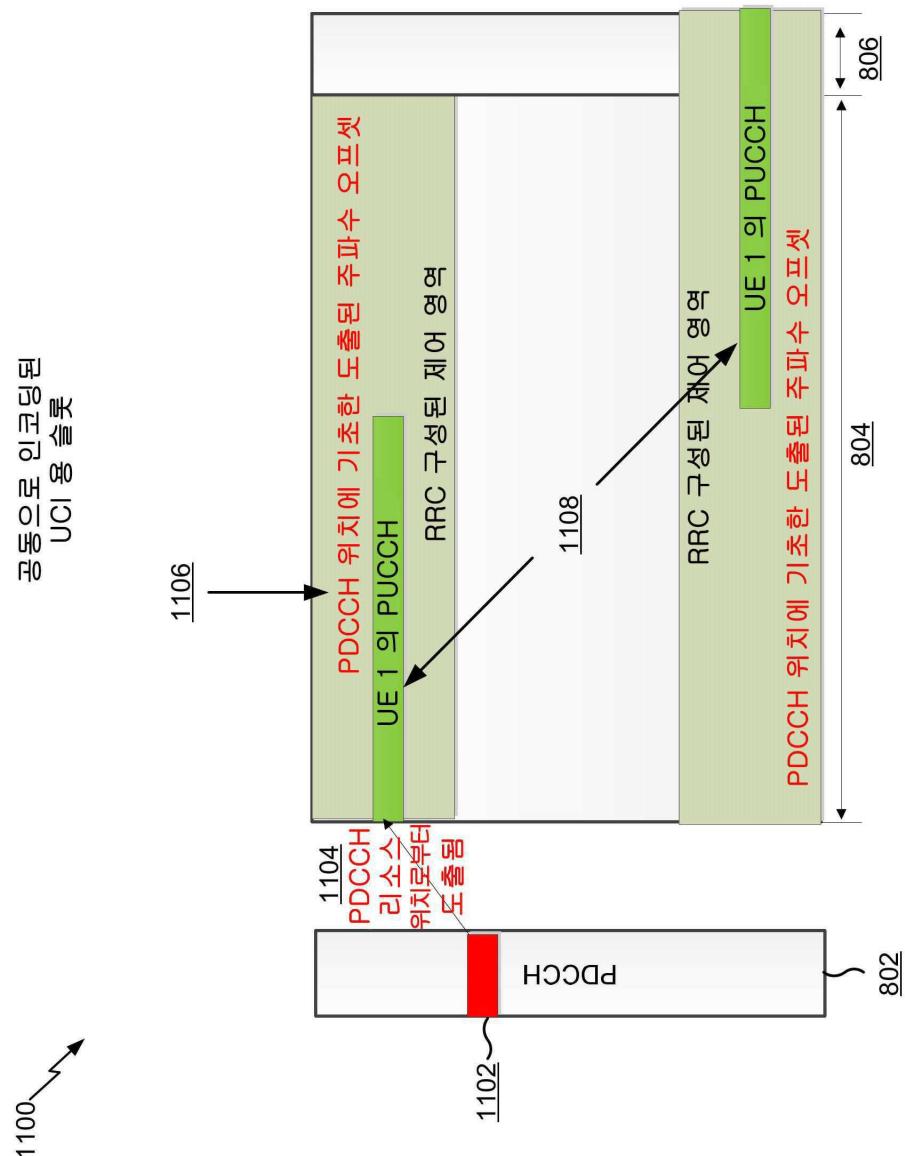

도 11a 및 도 11b 는 뉴 라디오에서 대응 업링크 제어 정보의 전송을 구성하는 예를 도시한 다이어그램이다.

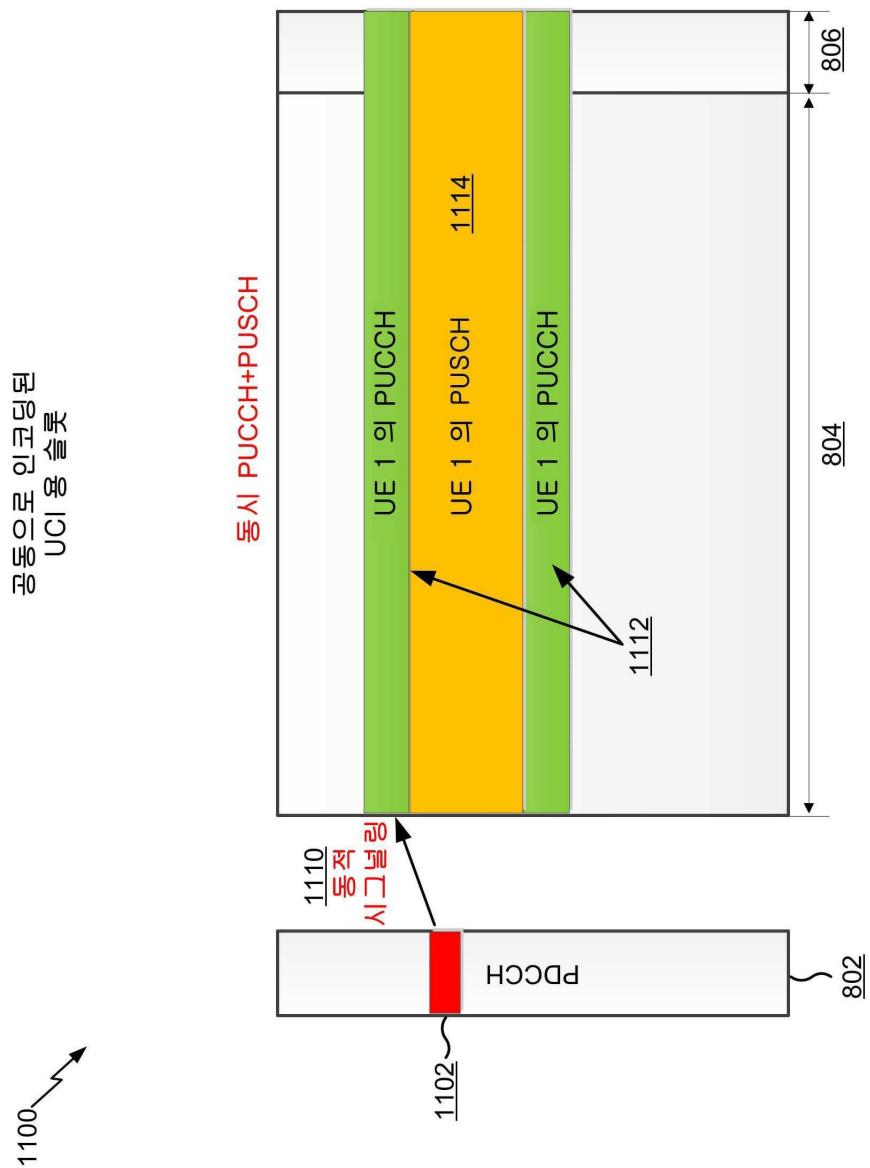

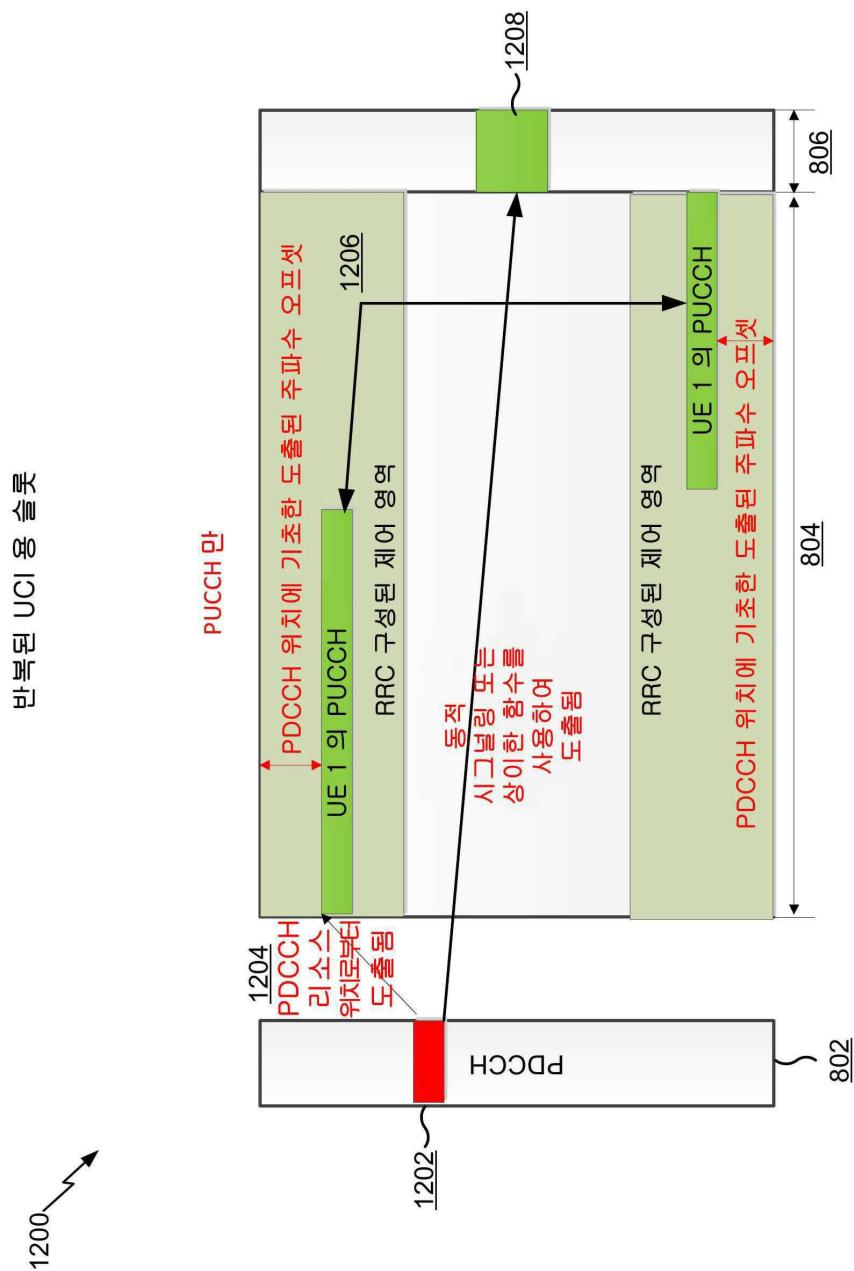

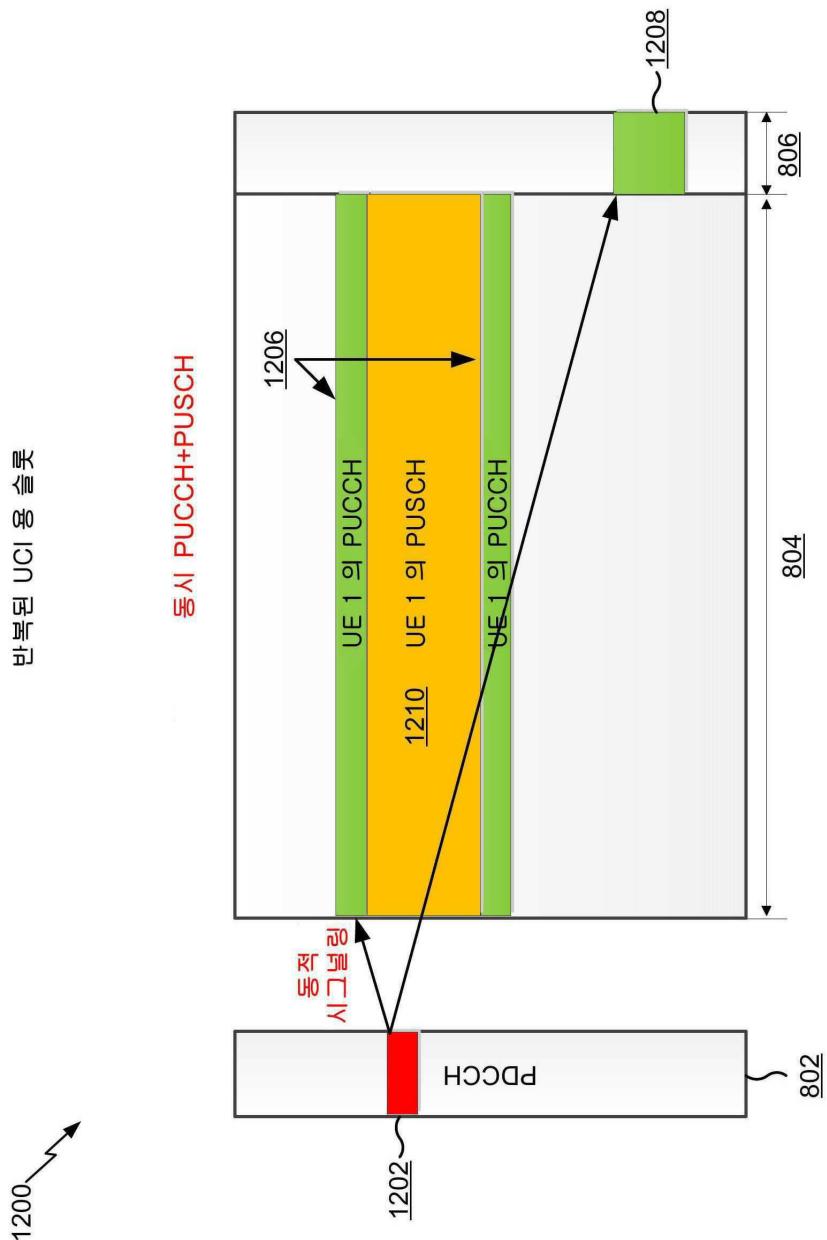

도 12a 및 도 12b 는 뉴 라디오에서 대응 업링크 제어 정보의 전송을 구성하는 예를 도시한 다이어그램이다.

도 13a 및 도 13b 는 뉴 라디오에서 대응 업링크 제어 정보의 전송을 구성하는 예를 도시한 다이어그램이다.

도 14a 및 도 14b 는 뉴 라디오에서 대응 업링크 제어 정보의 전송을 구성하는 예를 도시한 다이어그램이다.

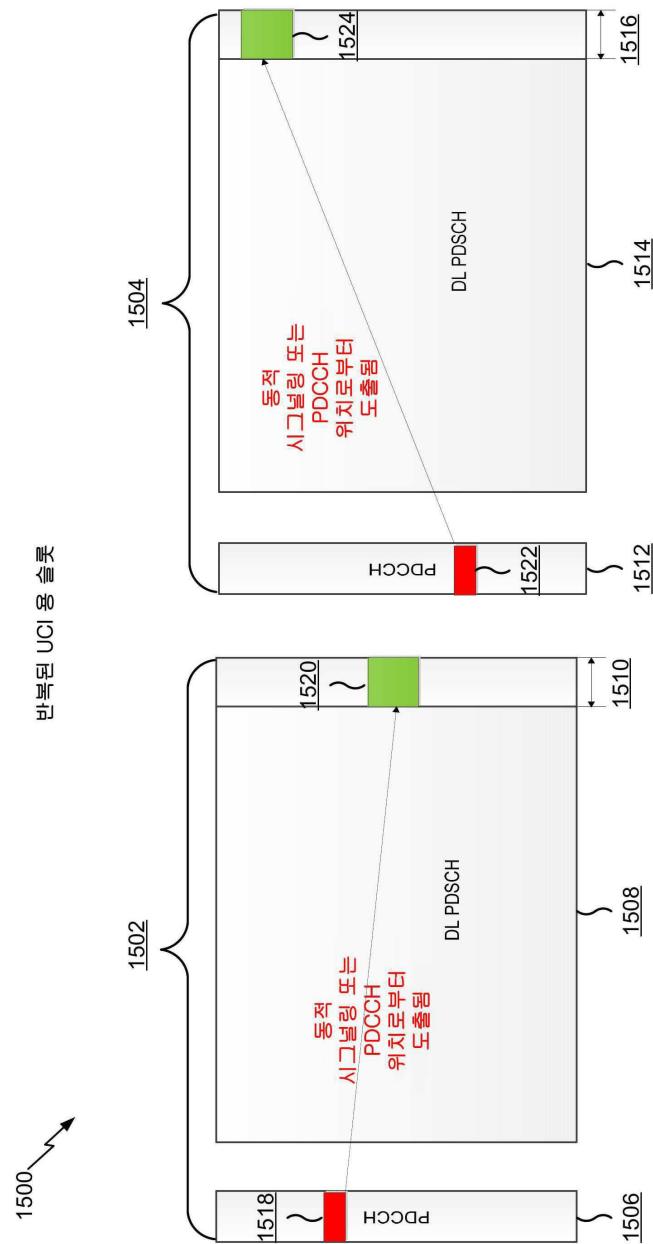

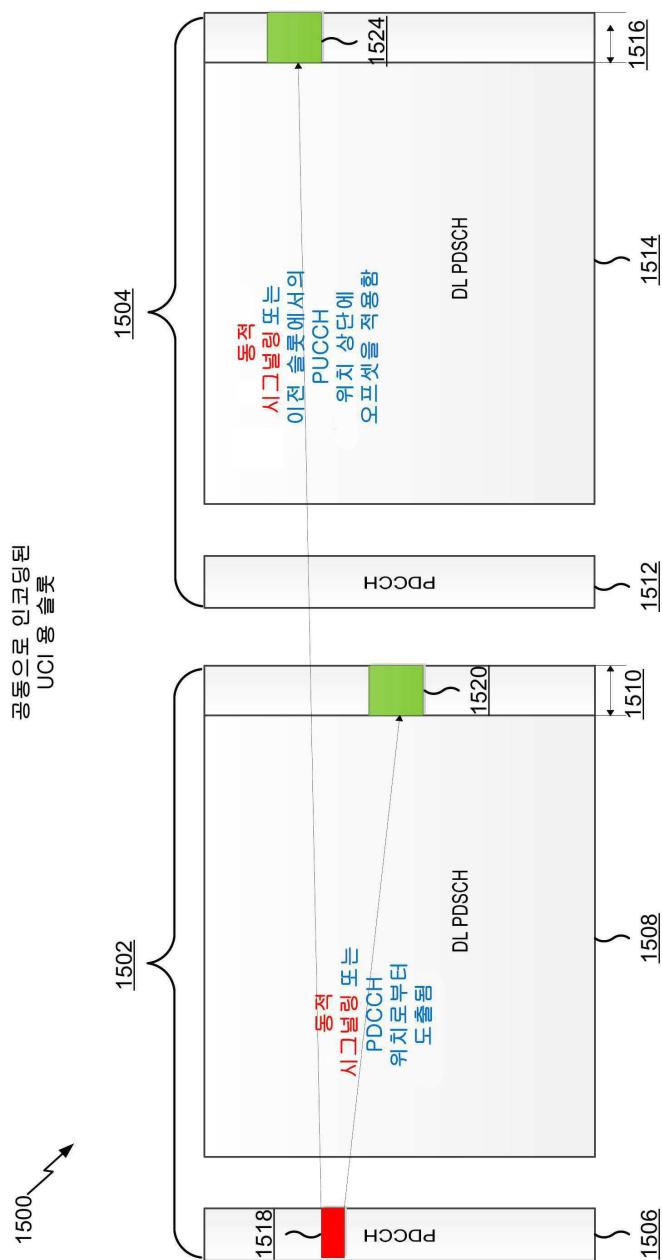

도 15a 및 도 15b 는 뉴 라디오에서 대응 업링크 제어 정보의 전송을 구성하는 예를 도시한 다이어그램이다.

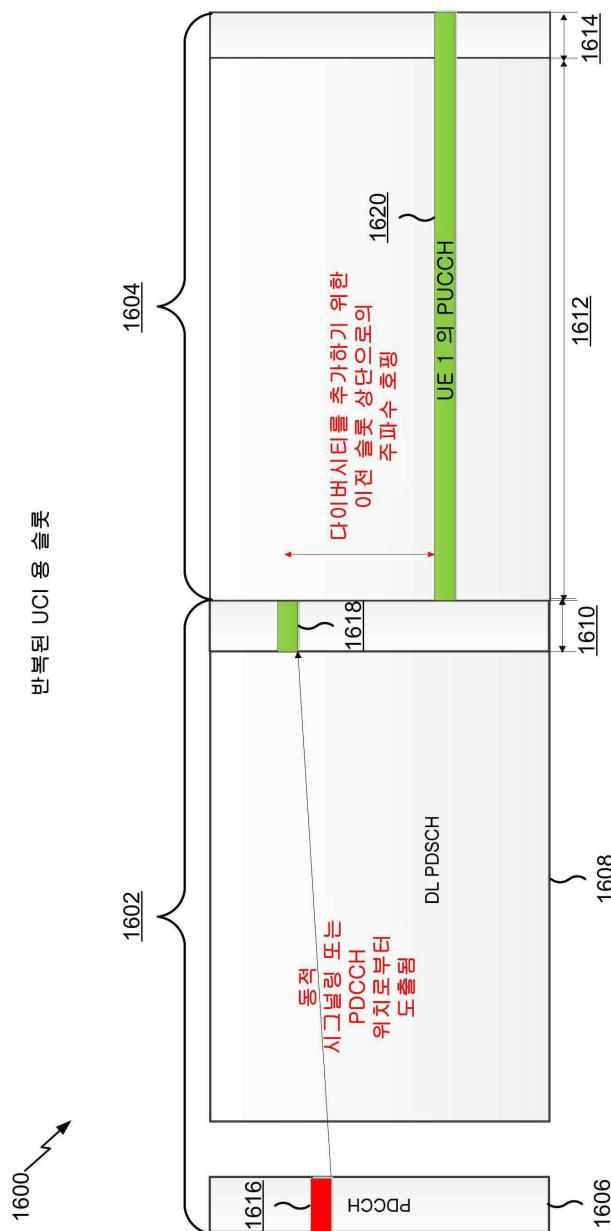

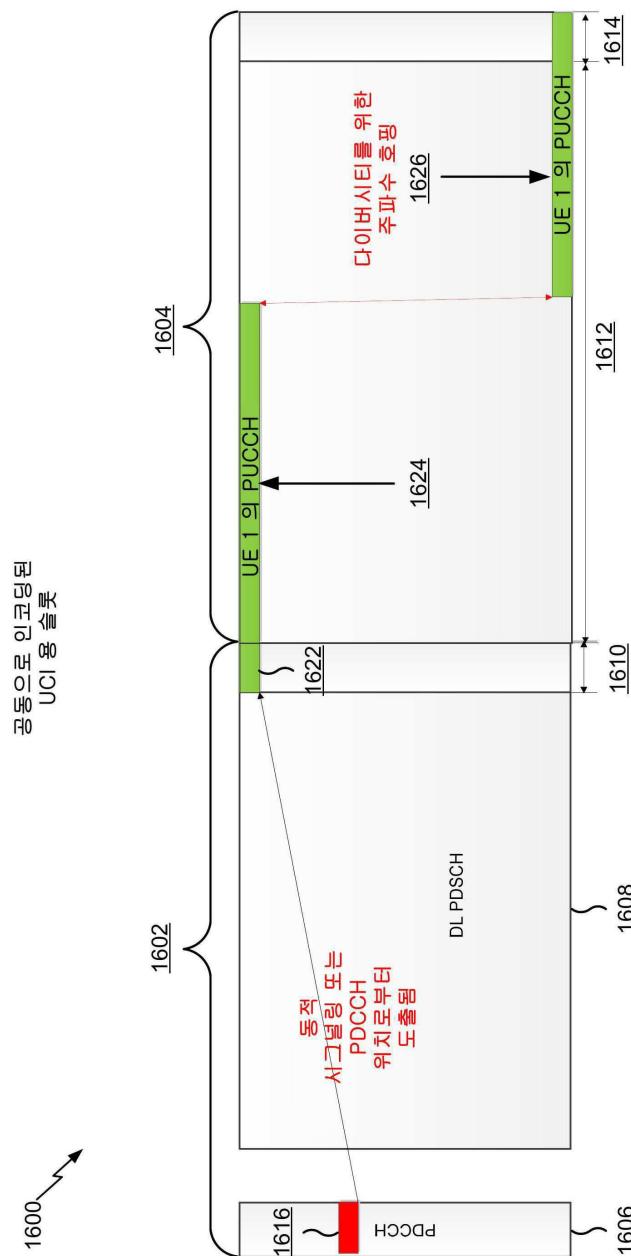

도 16a 및 도 16b 는 뉴 라디오에서 대응 업링크 제어 정보의 전송을 구성하는 예를 도시한 다이어그램이다.

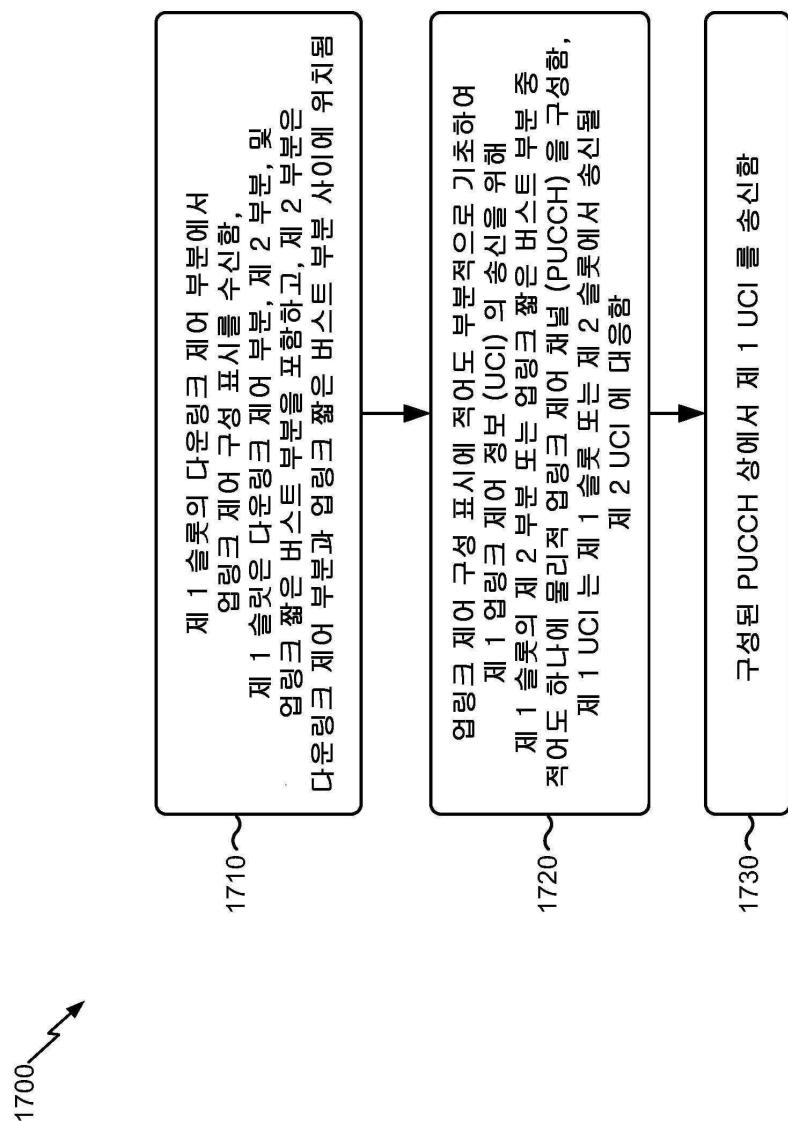

도 17 은 무선 통신의 방법의 플로우 차트이다.

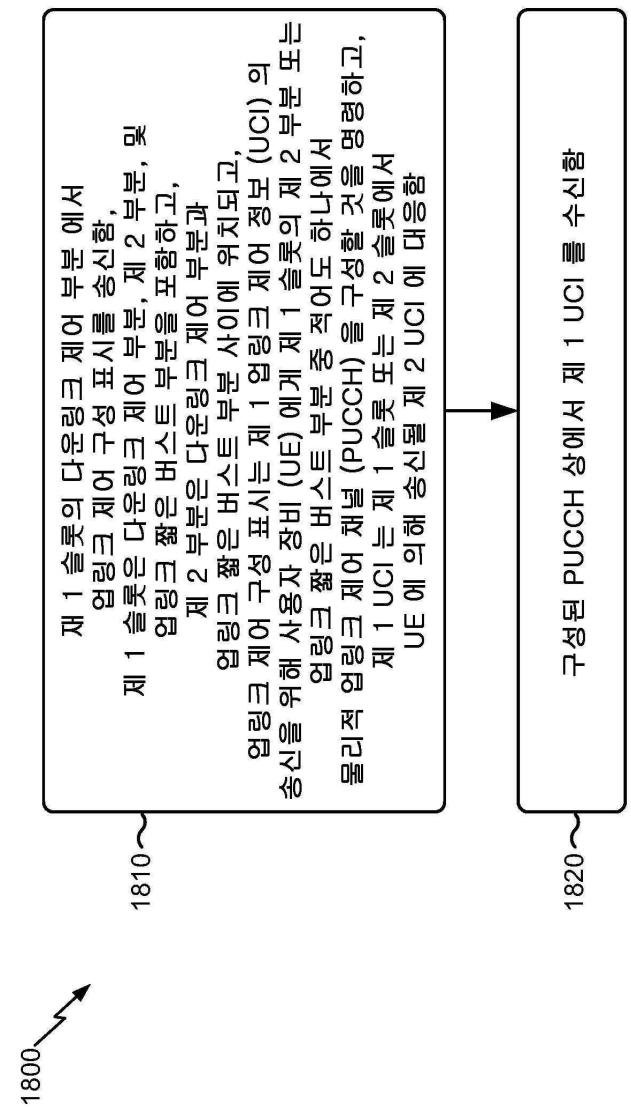

도 18 은 무선 통신의 다른 방법의 플로우 차트이다.

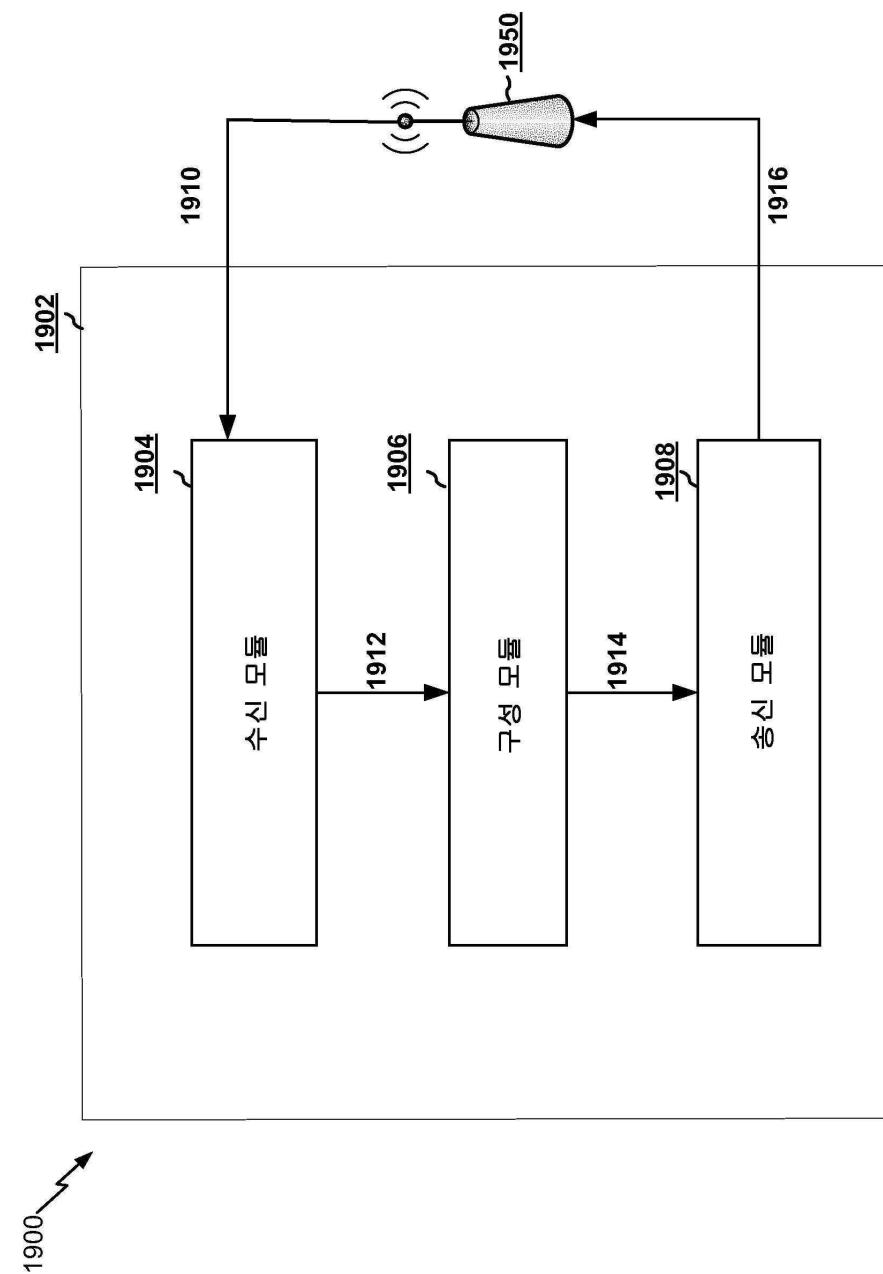

도 19 는 예시적인 장치에서 상이한 모듈들/수단들/컴포넌트들 간의 데이터 흐름을 도시하는 개념적인 데이터 흐름 다이어그램이다.

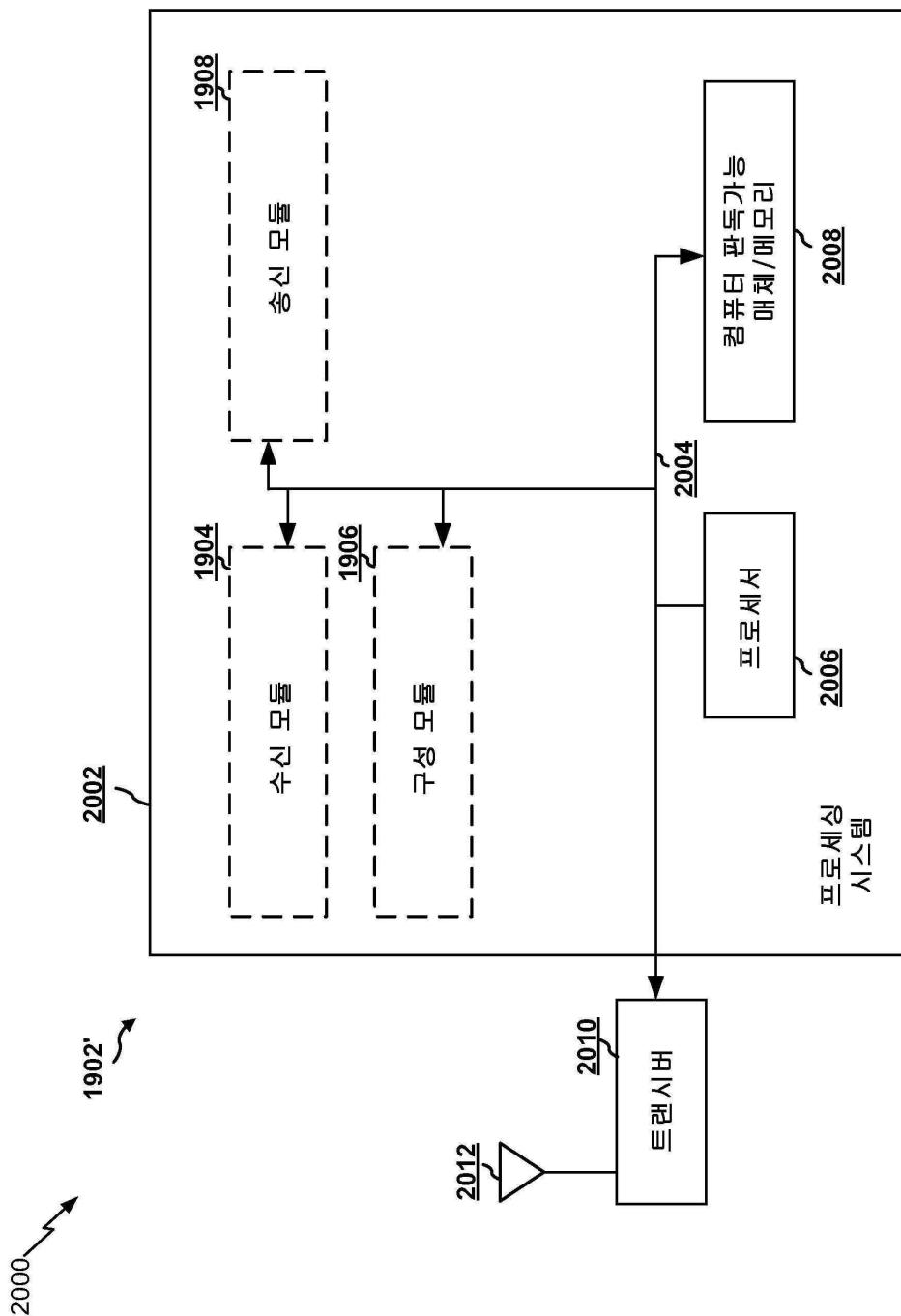

도 20 은 프로세싱 시스템을 채용하는 장치에 대한 하드웨어 구현의 일례를 도시한 다이어그램이다.

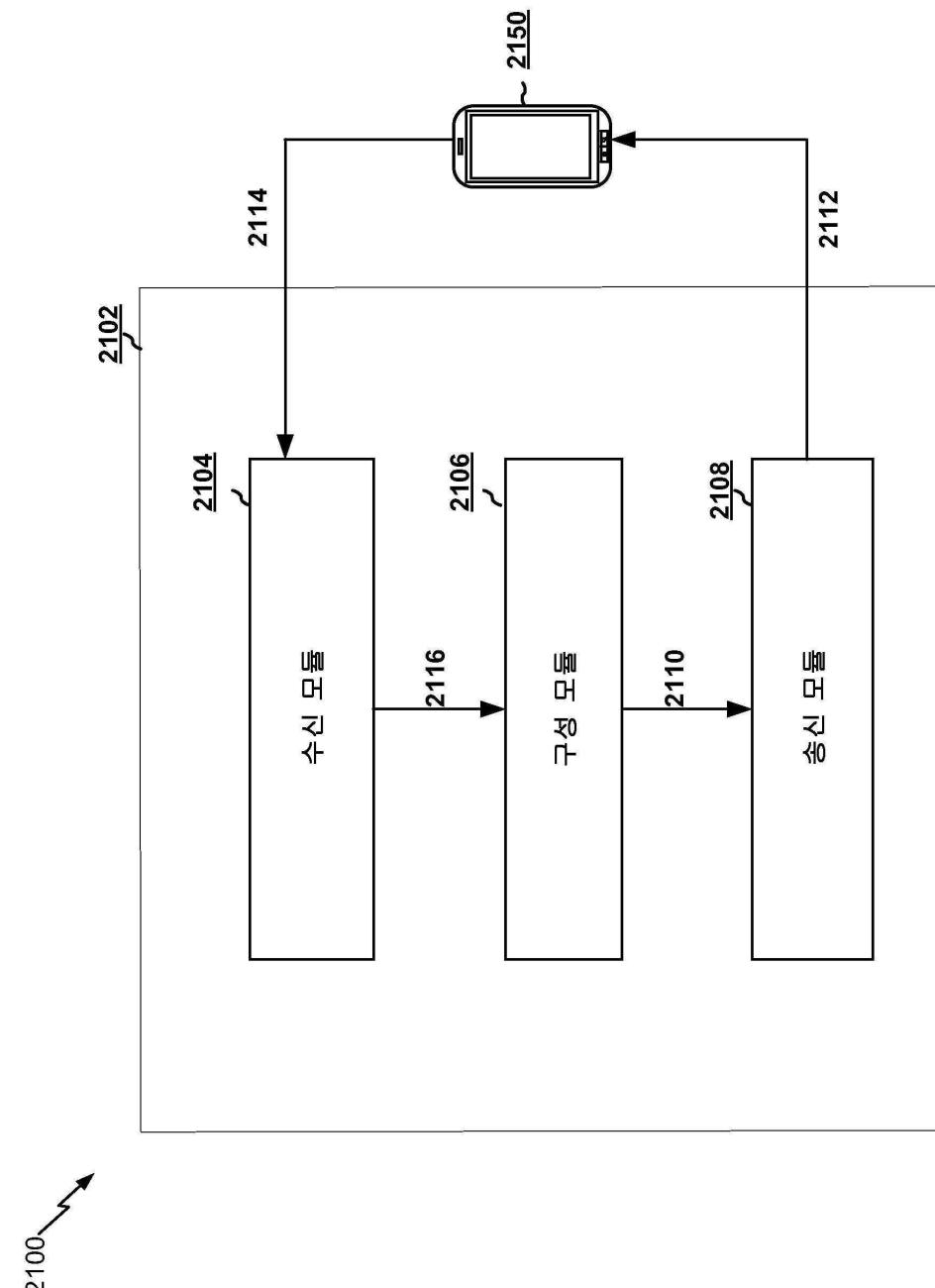

도 21 은 다른 예시적인 장치에서 상이한 모듈들/수단들/컴포넌트들 간의 데이터 흐름을 도시하는 개념적인 데이터 흐름 다이어그램이다.

도 22 는 프로세싱 시스템을 채용하는 장치에 대한 하드웨어 구현의 다른 예를 도시한 다이어그램이다.

### 발명을 실시하기 위한 구체적인 내용

[0017]

첨부 도면들과 관련하여 하기에 기재된 상세한 설명은 다양한 구성들의 설명으로서 의도되고, 본 명세서에 설명된 개념들이 실시될 수도 있는 구성들을 나타내도록 의도되지 않는다. 상세한 설명은 다양한 개념들의 철저한 이해를 제공할 목적으로 특정 상세들을 포함한다. 하지만, 이들 개념들은 이들 특정 상세들 없이도 실시될 수도 있음이 당업자에게 명백할 것이다. 일부 경우들에 있어서, 널리 공지된 구조들 및 컴포넌트들은 그러한 개념들을 불명료하게 하는 것을 회피하기 위하여 별록 다이어그램 형태로 도시된다.

[0018]

이제, 전기통신 시스템들의 여러 양태들이 다양한 장치 및 방법을 참조하여 제시될 것이다. 이들 장치 및 방법들은 다양한 블록들, 모듈들, 컴포넌트들, 회로들, 단계들, 프로세스들, 알고리즘들 등 ("엘리먼트들"로서 총칭함)에 의해 다음의 상세한 설명에서 설명되고 첨부 도면들에서 도시될 것이다. 이 엘리먼트들은 전자 하드웨어, 컴퓨터 소프트웨어, 또는 그 임의의 조합을 이용하여 구현될 수도 있다. 이러한 엘리먼트들이 하드웨어 또는 소프트웨어로서 구현되는지 여부는 특정한 애플리케이션과, 전체적인 시스템에 부과된 설계 제약들에 종속된다.

[0019]

예로서, 엘리먼트, 또는 엘리먼트의 임의의 부분, 또는 엘리먼트들의 임의의 조합은, 하나 이상의 프로세서들을 포함한 "프로세싱 시스템"으로 구현될 수도 있다. 프로세서들의 예들은 마이크로프로세서들, 마이크로 제어기들, 디지털 신호 프로세서들 (DSP들), 필드 프로그래밍가능 게이트 어레이들 (FPGA들), 프로그래밍가능 로직 디바이스들 (PLD들), 상태 머신들, 게이트형 로직, 이산 하드웨어 회로들, 및 본 개시 전반에 걸쳐 설명된 다양한 기능을 수행하도록 구성된 다른 적합한 하드웨어를 포함한다. 프로세싱 시스템에 있어서의 하나 이상의 프로세서들은 소프트웨어를 실행할 수도 있다. 소프트웨어는, 소프트웨어, 펌웨어, 미들웨어, 마이크로코드, 하드웨어 디스크립션 언어, 또는 기타 등등으로서 지정되든 아니든, 명령들, 명령 셋트들, 코드, 코드 세그먼트들, 프로그램 코드, 프로그램들, 서브프로그램들, 소프트웨어 모듈들, 애플리케이션들, 소프트웨어 애플리케이션들, 소프트웨어 패키지들, 루틴들, 서브루틴들, 오브젝트들, 실행 가능 물들, 실행 스레드들, 절차들,

함수들 등을 의미하도록 넓게 해석될 것이다.

[0020] 이에 따라, 하나 이상의 예시적인 실시형태들에서, 설명된 기능들은 하드웨어, 소프트웨어, 펌웨어 또는 이들의 임의의 조합으로 구현될 수도 있다. 소프트웨어로 구현된다면, 그 기능들은 하나 이상의 명령들 또는 코드로서 컴퓨터 판독가능 매체 상으로 저장 또는 인코딩될 수도 있다. 컴퓨터 판독가능 매체들은 컴퓨터 저장 매체들을 포함한다. 저장 매체는 컴퓨터에 의해 액세스될 수 있는 임의의 가용 매체일 수도 있다. 한정이 아닌 예로서, 그러한 컴퓨터 판독가능 매체는 랜덤 액세스 메모리 (RAM), 판독 전용 메모리 (ROM), 전기적으로 소거가능한 프로그래밍가능 ROM (EEPROM), 컴팩트 디스크 ROM (CD-ROM) 또는 다른 광학 디스크 스토리지, 자기 디스크 스토리지 또는 다른 자기 저장 디바이스들, 전술된 타입들의 컴퓨터 판독가능 매체의 조합들, 또는 컴퓨터에 의해 액세스될 수 있는 명령들 또는 데이터 구조들의 형태로 컴퓨터 실행가능 코드를 저장하는데 사용될 수 있는 임의의 다른 매체를 포함할 수 있다.

[0021] 액세스 포인트 ("AP")는 노드B, 무선 네트워크 제어기 ("RNC"), e노드B (eNB), 기지국 제어기 ("BSC"), 기지국 송수신기 ("BTS"), 기지국 ("BS"), 송수신기 기능부 ("TF"), 무선 라우터, 무선 송수신기, 기본 서비스 세트 ("BSS"), 확장형 서비스 세트 ("ESS"), 무선 기지국 ("RBS"), 노드 B (NB), gNB, 5G NB, NR BS, 송신 수신 포인트 (TRP), 또는 일부 다른 용어를 포함하거나, 그 용어로서 구현되거나, 또는 그 용어로서 공지될 수도 있다.

[0022] 액세스 단말 ("AT")은 액세스 단말, 가입자국, 가입자 유닛, 이동국, 원격국, 원격 단말기, 사용자 단말기, 사용자 에이전트, 사용자 디바이스, 사용자 장비 (UE), 사용자국, 무선 노드, 또는 일부 다른 용어를 포함하거나, 그 용어로서 구현되거나, 또는 그 용어로서 공지될 수도 있다. 일부 구현예들에서, 액세스 단말은 셀룰러 전화, 스마트폰, 코드리스 전화 (cordless telephone), 세션 개시 프로토콜 (Session Initiation Protocol) ("SIP") 전화, 무선 로컬 루프 (wireless local loop) ("WLL") 스테이션, 개인 정보 단말 (personal digital assistant) ("PDA"), 태블릿, 넷북, 스마트북, 울트라북, 무선 접속 능력을 가지는 핸드헬드 디바이스 (handheld device), 스테이션 ("STA"), 또는 무선 모뎀에 접속된 일부 다른 적당한 프로세싱 디바이스를 포함할 수도 있다. 따라서, 본원에서 교시된 하나 이상의 양태들은 전화 (예컨대, 셀룰러 전화, 스마트폰), 컴퓨터 (예컨대, 데스크톱), 휴대용 통신 디바이스, 휴대용 컴퓨팅 디바이스 (예컨대, 랩톱, 개인용 데이터 어시스턴트 (personal data assistant), 태블릿, 넷북, 스마트북, 울트라북), 웨어러블 디바이스 (예를 들어, 스마트 위치, 스마트 안경, 스마트 팔찌, 스마트 손목 밴드, 스마트 링, 스마트 의복 등), 의료용 디바이스들 또는 장비, 생체계측 센서들/디바이스들, 엔터테인먼트 디바이스 (예컨대, 음악 디바이스 또는 비디오 디바이스, 또는 위성 라디오, 게이밍 디바이스 등), 차량 컴퓨팅 또는 센서, 스마트 계측기들/센서들, 산업용 제조 장비, 글로벌 위치결정 시스템 디바이스, 또는 무선 또는 유선 매체를 통해 통신하도록 구성되는 임의의 다른 적당한 디바이스 내로 편입될 수도 있다. 일부 양태들에서, 노드는 무선 노드이다. 무선 노드는 예를 들어, 유선 또는 무선 통신 링크를 통해 네트워크 (예컨대, 인터넷 또는 셀룰러 네트워크와 같은 광역 네트워크)를 위한 또는 이러한 네트워크로의 접속성을 제공할 수도 있다. 일부 UE 들은 기지국, 다른 원격 디바이스 또는 일부 다른 엔티티와 통신할 수도 있는 원격 디바이스들을 포함할 수도 있는 머신 타입 통신 (MTC) UE 들로 고려될 수도 있다. 머신 타입 통신 (MTC)는 통신의 적어도 하나의 엔드 상에 적어도 하나의 원격 디바이스를 수반하는 통신을 지칭할 수도 있고 반드시 인간 상호 작용을 필요로 하는 것은 아닌 하나 이상의 엔티티를 수반하는 데이터 통신의 형태를 포함할 수도 있다. MTC UE들은 예를 들어 PLMN (Public Land Mobile Networks)를 통해 MTC 서버들 및/또는 다른 MTC 디바이스들과 MTC 통신할 수 있는 UE들을 포함할 수도 있다. MTC 디바이스의 예로는 센서, 미터, 위치 태그, 모니터, 드론, 로봇/로봇식 디바이스 등이 있다. MTC UE들 및 다른 유형의 UE들은 NB-IoT (협대역 사물인터넷) 디바이스들로서 구현될 수도 있다.

[0023] 양태들은 3G 및/또는 4G 무선 기술들과 공통으로 연관된 기술을 사용하여 본원에 설명될 수도 있지만, 본 개시의 양태들은 NR 기술들을 포함하는, 5G 및 그 후속과 같은 다른 세대-기반의 통신 시스템들에 적용될 수 있음에 유의한다.

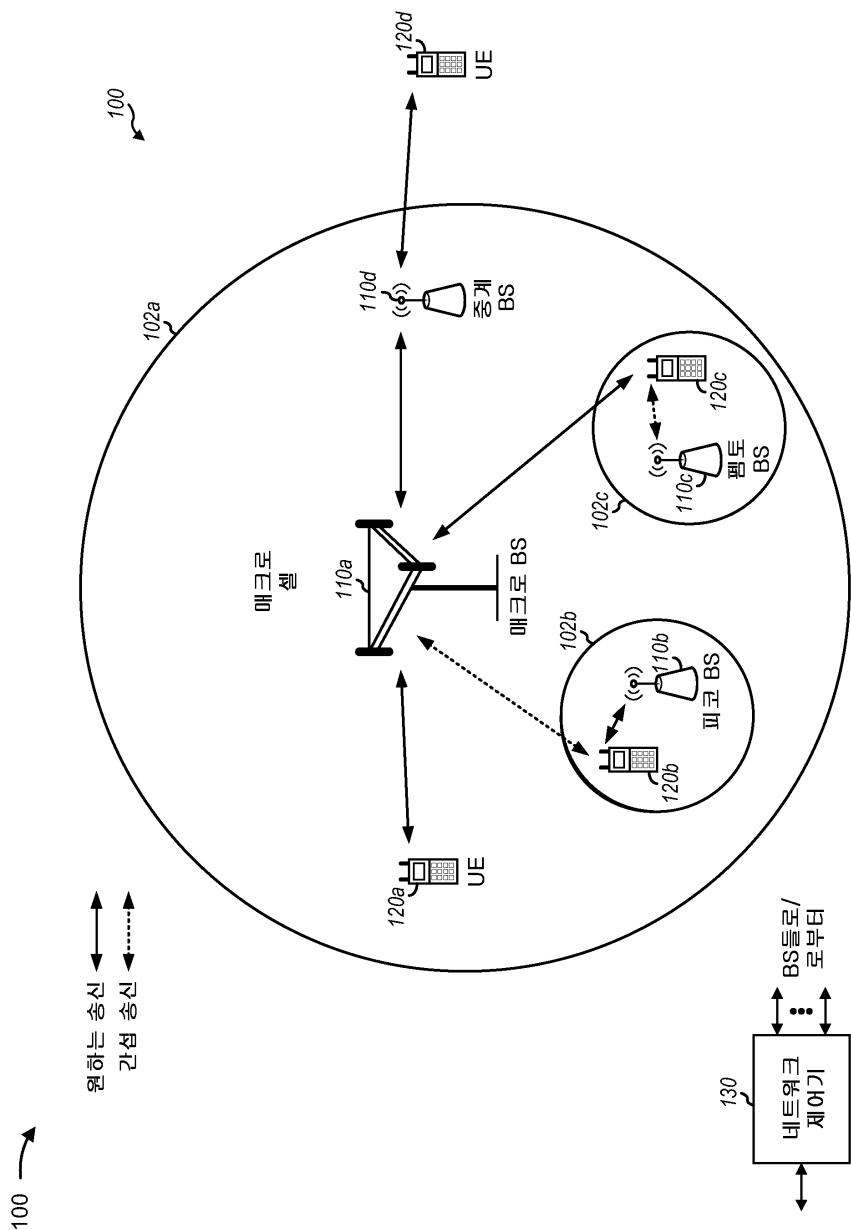

[0024] 도 1은 본 개시의 양태들이 실시될 수도 있는 네트워크 (100)를 도시한 다이어그램이다. 네트워크 (100)는 LTE 네트워크 또는 5G 또는 NR 네트워크와 같은 일부 다른 무선 네트워크일 수도 있다. 무선 네트워크 (100)는 (BS (110a), BS (110b), BS (110c) 및 BS (110d)로 도시된) 다수의 BS 들 (110) 및 다른 네트워크 엔티티들을 포함할 수도 있다. BS는 사용자 장비 (UE)와 통신하는 엔티티이고, 기지국, NR BS, 노드 B, gNB, 5G NB, 액세스 포인트, TRP 등으로 지칭될 수도 있다. 각각의 BS는 특정한 지리적 영역에 대한 통신 커버리지를 제공할 수도 있다. 3GPP에서, 용어 "셀"은 그 용어가 사용된 맥락에 따라, BS의 커버리지 영

역 및/또는 이 커버리지 영역을 서빙 (serving) 하는 BS 서비스체계를 지칭할 수 있다.

[0025]

BS 는 매크로 셀, 피코 셀, 펨토 셀, 및/또는 다른 타입들의 셀에 대한 통신 커버리지를 제공할 수도 있다. 매크로 셀은 상대적으로 큰 지리적 영역 (예를 들어, 반경이 수 킬로미터임) 을 커버할 수도 있고, 서비스 가입으로 UE들에 의한 무제한 액세스를 허용할 수도 있다. 피코 셀은 상대적으로 작은 지리적 영역 (예를 들어, 흠풀) 을 커버할 수도 있고, 펨토 셀과 연관을 갖는 UE들 (예를 들어, 폐쇄 가입자 그룹 (CSG) 에 있는 UE들) 에 의한 제한적 액세스를 허용할 수도 있다. 매크로 셀에 대한 BS 는 매크로 BS 로 지칭될 수도 있다. 피코 셀에 대한 BS 는 피코 BS 로 지칭될 수도 있다. 펨토 셀에 대한 BS 는 펨토 BS 또는 흠풀 BS 로 지칭될 수도 있다. 도 1에 도시된 예에서, BS (110a) 는 매크로 셀 (102a) 을 위한 매크로 BS 일 수도 있고, BS (110b) 는 피코 셀 (102b) 을 위한 피코 BS 일 수도 있고, BS (110c) 는 펨토 셀 (102c) 을 위한 펨토 BS 일 수도 있다. BS 는 하나 또는 다수의 (예를 들어, 3개의) 셀들을 지원할 수도 있다. "eNB", "기지국", "NR BS", "gNB", "TRP", "AP", "노드 B", "5G NB" 및 "셀"이라는 용어는 여기에서 서로 바꿔 사용될 수도 있다.

[0026]

일부 예들에서, 셀은 반드시 정적일 필요는 없고, 셀의 지리적 영역은 이동 BS 의 위치에 따라 이동할 수도 있다. 일부 예들에서, BS 들은, 임의의 적합한 전송 네트워크를 이용하여 직접적인 물리적 접속, 가상 네트워크 등과 같은 다양한 타입들의 백홀 (backhaul) 인터페이스들을 통해 액세스 네트워크 (100) 에서 서로 및/또는 하나 이상의 다른 기지국들 또는 네트워크 노드들 (미도시) 에 상호접속될 수도 있다.

[0027]

무선 네트워크 (100) 는 또한 중계국들을 포함할 수도 있다. 중계국은, 업스트림 국 (예를 들어, BS 또는 UE) 으로부터 데이터의 송신을 수신하고 다운스트림 국 (예를 들어, UE 또는 BS) 로의 그 데이터의 송신을 전송 할 수 있는 엔티티이다. 중계국은 또한, 다른 UE 들을 위한 송신을 중계할 수 있는 UE 일 수도 있다. 도 1에 도시된 예에서, BS (110a) 와 UE (120d) 간의 통신을 용이하게 하기 위하여 매크로 BS (110a) 및 UE (120d) 와 통신할 수도 있다. 중계국은 또한, 중계 BS, 중계 기지국, 중계기 등으로서 지칭될 수도 있다.

[0028]

무선 네트워크 (100) 는 상이한 타입들의 BS들, 예를 들어, 매크로 BS들, 피코 BS들, 펨토 BS들, 중계 BS들 등을 포함하는 이종 네트워크일 수도 있다. 이 상이한 타입들의 BS들은 상이한 송신 전력 레벨들, 상이한 커버리지 영역들, 및 무선 네트워크 (100) 에서의 간섭에 대한 상이한 영향을 가질 수도 있다. 예를 들어, 매크로 BS들은 높은 송신 전력 레벨 (예를 들어, 5 내지 40 와트) 을 가질 수도 있는 반면에, 피코 BS들, 펨토 BS들, 그리고 중계 BS들은 보다 낮은 송신 전력 레벨 (예를 들어, 0.1 내지 2 와트) 을 가질 수도 있다.

[0029]

네트워크 제어기 (130) 가 BS들의 세트에 커플링할 수도 있고 이 BS들에 대한 조정 및 제어를 제공할 수도 있다. 네트워크 제어기 (130) 는 백홀을 통해 BS들과 통신할 수도 있다. BS들은 또한, 무선 또는 유선 백홀을 통해 예를 들어 직접적으로 또는 간접적으로 서로 통신할 수도 있다.

[0030]

UE들 (120) (예를 들어, 120a, 120b, 120c) 은 무선 네트워크 (100) 전체에 걸쳐 분산될 수도 있고, 각각의 UE 는 고정식 또는 이동식일 수도 있다. UE 는 또한, 액세스 단말기, 단말기, 이동국, 가입자 유닛, 스테이션 등으로서 지칭될 수도 있다. UE 는 셀룰러 폰 (예컨대, 스마트 폰), 개인 휴대 정보 단말기 (PDA), 무선 모뎀, 무선 통신 디바이스, 핸드헬드 디바이스, 랩톱 컴퓨터, 코드리스 폰, 무선 로컬 루프 (WLL) 국, 태블릿, 카메라, 게이밍 디바이스, 넷북, 스마트북, 울트라북, 의료 디바이스 또는 장비, 생체인식 센서/디바이스, 웨어러블 디바이스 (스마트 시계, 스마트 의류, 스마트 안경, 스마트 손목 밴드, 스마트 주얼리 (예컨대, 스마트 반지, 스마트 팔찌)), 엔터테인먼트 디바이스 (예컨대, 음악 또는 비디오 디바이스, 또는 위성 라디오), 차량 컴퓨트 또는 센서, 스마트 미터/센서, 산업 제조 장비, 글로벌 포지셔닝 시스템 디바이스, 또는 무선 또는 유선 매체를 통해 통신하도록 구성된 임의의 다른 적절한 디바이스일 수도 있다. 일부 UE들은 진화된 또는 향상된 머신-타입 통신 (eMTC) UE들로 간주될 수도 있다. MTC 및 eMTC UE들은, 예를 들어, 기지국, 다른 디바이스 (예를 들어, 원격 디바이스), 또는 일부 다른 엔티티와 통신할 수도 있는 로봇들, 드론들, 원격 디바이스들, 예를 들어 센서들, 미터들, 모니터들, 위치 태그들 등을 포함한다. 무선 노드는, 예를 들면, 유선 또는 무선 통신 링크를 통해 네트워크 (예를 들면, 인터넷 또는 셀룰러 네트워크와 같은 광역 네트워크) 에 대한 또는 네트워크로의 접속성을 제공할 수도 있다. 일부 UE들은 사물 인터넷 (IoT) 디바이스들로 간주될 수도 있다. 일부 UE들은 CPE (Customer Premises Equipment) 로 간주될 수도 있다.

[0031]

도 1에서, 이중 화살표들을 갖는 실선은, 다운링크 및/또는 업링크 상에서 UE 를 서빙하도록 지정된 BS 인 서빙 BS 및 UE 사이의 원하는 송신들을 나타낸다. 이중 화살표들을 갖는 점선은 UE 와 BS 간의 잠재적으로 간섭하는 송신들을 표시한다.

[0032]

일반적으로, 임의의 수의 무선 네트워크가 주어진 지리적 영역에 배치될 수 있다. 각각의 무선 네트워크는 특정 RAT를 지원할 수도 있고, 하나 이상의 주파수들 상에서 동작할 수도 있다. RAT는 또한 무선 기술, 에어 인터페이스 등으로서 지정될 수도 있다. 주파수는 또한 캐리어, 주파수 채널 등으로서 지정될 수도 있다. 각각의 주파수는, 상이한 RAT들의 무선 네트워크들 사이의 간섭을 회피하기 위하여 주어진 지리적 영역에서 단일 RAT를 지원할 수도 있다. 일부 경우들에 있어서, NR 또는 5G RAT 네트워크들이 전개될 수도 있다.

[0033]

일부 예들에서, 공중 인터페이스에 대한 액세스는 스케줄링될 수도 있으며, 여기서 스케줄링 엔티티(예컨대, 기지국)는 그 스케줄링 엔티티의 서비스 영역 또는 셀 내의 일부 또는 모든 디바이스들 및 장비 간의 통신을 위해 자원들을 할당한다. 본 개시 내에서, 하기에서 더 논의되는 바와 같이, 스케줄링 엔티티는 하나 이상의 종속 엔티티들에 대한 리소스들을 스케줄링하는 것, 할당하는 것, 재구성하는 것, 및 해제하는 것을 책임질 수도 있다. 즉, 스케줄링된 통신에 대해, 종속 엔티티들은 스케줄링 엔티티에 의해 할당된 리소스들을 활용한다.

[0034]

기지국들은 스케줄링 엔티티로서 기능할 수도 있는 유일한 엔티티들은 아니다. 즉, 일부 예들에서, UE는 하나 이상의 종속 엔티티들(예컨대, 하나 이상의 다른 UE들)을 위한 리소스들을 스케줄링하는 스케줄링 엔티티로서 기능할 수도 있다. 이 예에 있어서, UE는 스케줄링 엔티티로서 기능하고 있고, 다른 UE들은 무선 통신을 위해 UE에 의해 스케줄링된 리소스들을 활용한다. UE는, 피어-투-피어(P2P) 네트워크에서 그리고 /또는 메시 네트워크에서 스케줄링 엔티티로서 기능할 수도 있다. 메시 네트워크 예에 있어서, UE들은 선택적으로, 스케줄링 엔티티와 통신하는 것에 부가하여 서로 직접 통신할 수도 있다.

[0035]

따라서, 시간-주파수 리소스들로의 스케줄링된 액세스를 갖고 셀룰러 구성, P2P 구성 및 메시 구성을 갖는 무선 통신 네트워크에 있어서, 스케줄링 엔티티 및 하나 이상의 종속 엔티티들은 스케줄링된 리소스들을 활용하여 통신할 수도 있다.

[0036]

상기한 바와 같이, 도 1은 단지 일례로서 제공된다. 다른 예들이 가능하며, 도 1에 대하여 설명된 것과 상이할 수도 있다.

[0037]

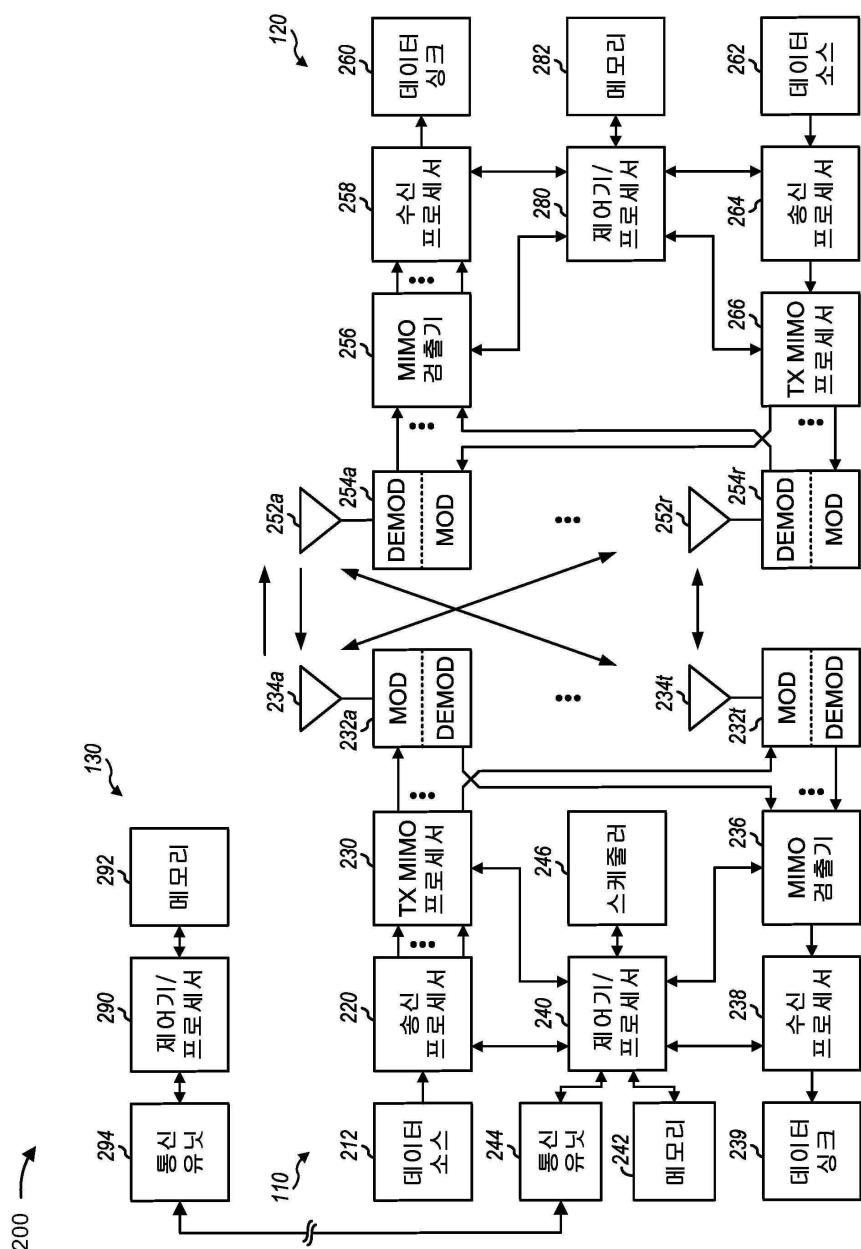

도 2는 도 1의 기지국들 중 하나 및 UE들 중 하나일 수도 있는 기지국(110) 및 UE(120)의 설계의 볼록도를 보여준다. 기지국(110)에는 T개의 안테나들(234a 내지 234t)이 장착될 수도 있고, UE(120)에는 R개의 안테나들(252a 내지 252r)이 장착될 수도 있으며, 여기서 일반적으로  $T \geq 1$ 이고  $R \geq 1$ 이다.

[0038]

기지국(110)에서, 송신 프로세서(220)는 하나 이상의 UE들에 대한 데이터를 데이터 소스(212)로부터 수신하고, UE로부터 수신된 채널 품질 표시자들(CQI들)에 적어도 부분적으로 기초하여 각각의 UE에 대한 하나 이상의 변조 및 코딩 방식들(MCS)을 선택하고, UE에 대해 선택된 MCS(들)에 적어도 부분적으로 기초하여 각각의 UE에 대한 데이터를 프로세싱(예를 들어, 인코딩 및 변조)하고, 모든 UE들에 대해 데이터 심볼들을 제공할 수도 있다. 송신 프로세서(220)는 또한, (예를 들어, 준정적 리소스 파티셔닝 정보(SRPI) 등에 대한) 시스템 정보 및 제어 정보(예를 들어, CQI 요청들, 승인들, 상위 계층 시그널링 등)를 프로세싱하고 오버헤드 심볼들 및 제어 심볼들을 제공할 수도 있다. 송신 프로세서(220)는 또한, 참조 신호들(예를 들어, CRS) 및 동기화 신호들(예를 들어, 프라이머리 동기화 신호(PSS) 및 세컨더리 동기화 신호(SSS))에 대한 참조 심볼들을 생성할 수도 있다. 송신(TX) 다중입력 다중출력(MIMO) 프로세서(230)는 적용가능할 경우 데이터 심볼들, 제어 심볼들, 오버헤드 심볼들, 및/또는 참조 심볼들에 대한 공간 프로세싱(예를 들어, 프리코딩)을 수행할 수도 있고, T개의 출력 심볼 스트림들을 T개의 변조기들(MOD들)(232a 내지 232t)에 제공할 수도 있다. 각각의 변조기(232)는 출력 샘플 스트림을 획득하기 위하여(예를 들어, OFDM 등에 대해) 개별 출력 심볼 스트림들을 프로세싱할 수도 있다. 각각의 변조기(232)는 또한, 다운링크 신호를 획득하기 위하여 출력 샘플 스트림을 프로세싱(예를 들어, 아날로그로 변환, 증폭, 필터링 및 상향변환) 할 수도 있다. 변조기들(232a 내지 232t)로부터의 T개의 다운링크 신호들은 각각 T개의 안테나들(234a 내지 234t)을 통해 송신될 수도 있다. 아래에서 보다 상세히 설명되는 특정 양태들에 따르면, 동기화 신호들은 추가 정보를 전달하기 위해 위치 인코딩으로 생성될 수 있다.

[0039]

UE(120)에서, 안테나들(252a 내지 252r)은 기지국(110) 및/또는 다른 기지국들로부터 다운링크 신호들을 수신할 수도 있고, 수신된 신호들을 복조기(DEMOD)들(254a 내지 254r)에 각각 제공할 수도 있다. 각각의 복조기(254)는 입력 샘플들을 획득하기 위하여 수신된 신호를 컨디셔닝(예를 들어, 필터링, 증폭, 하향변환 및 디지털화) 할 수도 있다. 각각의 복조기(254)는 수신된 심볼들을 획득하기 위하여(예를 들어, OFDM 등에 대해) 입력 샘플들을 추가로 프로세싱할 수도 있다. MIMO 검출기(256)는 모든 R개의 복조기들

(254a 내지 254r)로부터의 수신된 심볼들을 획득하고, 적용 가능하다면, 수신된 심볼들에 대한 MIMO 검출을 수행하며, 검출된 심볼들을 제공할 수도 있다. 수신 프로세서 (258)는 검출된 심볼들을 프로세싱 (예를 들어, 복조 및 디코딩) 하고, UE (120)를 위한 디코딩된 데이터를 데이터 싱크 (260)에 제공하고, 디코딩된 제어 정보 및 시스템 정보를 제어기/프로세서 (280)에 제공할 수도 있다. 채널 프로세서는 RSRP, RSSI, RSRQ, CQI 등을 결정할 수도 있다.

[0040] 업링크 상에서, UE (120)에서, 송신 프로세서 (264)는 데이터 소스 (262)로부터 데이터를, 그리고 제어기/프로세서 (280)로부터 (예를 들어, RSRP, RSSI, RSRQ, CQI 등을 포함하는 리포트들에 대한) 제어 정보를 수신 및 프로세싱할 수도 있다. 송신 프로세서 (264)는 또한 하나 이상의 참조 신호들에 대한 참조 심볼들을 생성할 수도 있다. 송신 프로세서 (264)로부터의 심볼들은, 적용 가능하다면, TX MIMO 프로세서 (266)에 의해 프리코딩되고, (예를 들어, DFT-s-OFDM, CP-OFDM 등을 위해) 변조기들 (254a 내지 254r)에 의해 더 프로세싱되고, 그리고/또는 기지국 (110)으로 송신될 수도 있다. 기지국 (110)에서, UE (120) 및 다른 UE들로부터의 업링크 신호들은 안테나들 (234)에 의해 수신되고, 복조기들 (232)에 의해 프로세싱되고, 적용 가능하다면, MIMO 검출기 (236)에 의해 검출되고, 수신 프로세서 (238)에 의해 더 프로세싱되어, UE (120)에 의해 전송된 디코딩된 데이터 및 제어 정보를 획득할 수도 있다. 수신 프로세서 (238)는 디코딩된 데이터를 데이터 싱크 (239)로 그리고 디코딩된 제어 정보를 제어기/프로세서 (240)에 제공할 수도 있다. 기지국 (110)은 통신 유닛 (244)을 포함하고 통신 유닛 (244)을 통해 네트워크 제어기 (130)와 통신할 수도 있다. 네트워크 제어기 (130)는 통신 유닛 (294), 제어기/프로세서 (290) 및 메모리 (292)를 포함할 수도 있다.

[0041] 제어기들/프로세서들 (240 및 280) 및/또는 도 2의 임의의 다른 컴포넌트(들)는 뉴 라디오에서 대응 업링크 제어 정보의 전송을 구성하도록 각각 기지국 (110) 및 UE (120)에서 동작을 지시할 수도 있다. 예를 들어, 제어기/프로세서 (280) 및/또는 기지국 (110)에서의 다른 프로세서들 및 모듈들은 뉴 라디오에서 대응 업링크 제어 정보의 전송을 구성하도록 UE (120)의 동작들을 수행하거나 지시할 수도 있다. 예를 들어, 제어기/프로세서 (280) 및/또는 BS (110)에서의 다른 제어기들/프로세서들 및 모듈들은 예를 들어 도 17의 프로세스 (1700), 도 18의 프로세스 (1800) 및/또는 여기에 기술된 다른 프로세스들의 동작들을 수행하거나 지시할 수도 있다. 일부 양태들에서, 도 2에 도시된 하나 이상의 컴포넌트들은 도 17의 예시적인 프로세스 (1700), 도 18의 예시적인 프로세스 (1800), 및/또는 여기에 기술된 기술들에 대한 다른 프로세스들을 수행하기 위해 채용될 수도 있다. 메모리들 (242 및 282)은 각각 BS (110) 및 UE (120)에 대한 데이터 및 프로그램 코드들을 저장할 수도 있다. 스케줄러 (246)는 다운링크 및/또는 업링크 상에서 데이터 송신을 위해 UE들을 스케줄링할 수도 있다.

[0042] 상기한 바와 같이, 도 2는 단지 일례로서 제공된다. 다른 예들이 가능하며, 도 2에 대하여 설명된 것과 상이할 수도 있다.

[0043] 도 3은 전기통신 시스템 (예를 들어, LTE)에서의 FDD에 대한 예시적인 프레임 구조 (300)를 도시한다. 다운링크 및 업링크의 각각에 대한 송신 타임라인은 무선 프레임들의 유닛들로 파티셔닝될 수도 있다. 각각의 무선 프레임은 미리 결정된 지속기간 (예를 들어, 10 밀리초 (ms))을 가질 수도 있으며, 0 내지 9의 인덱스들을 갖는 10개의 서브프레임들로 파티셔닝될 수도 있다. 각각의 서브프레임은 2개의 슬롯들을 포함할 수도 있다. 따라서, 각각의 무선 프레임은 0 내지 19의 인덱스들을 갖는 20개의 슬롯들을 포함할 수도 있다. 각각의 슬롯은 L개의 심볼 기간들, 예를 들어, (도 3에 도시된 바와 같은) 정규의 사이클릭 프리픽스에 대한 7개의 심볼 기간들 또는 확장된 사이클릭 프리픽스에 대한 6개의 심볼 기간들을 포함할 수도 있다. 각 서브프레임에서의 2L개의 심볼 기간들에는, 0 내지 2L-1의 인덱스들이 할당될 수도 있다.

[0044] 일부 기법들이 프레임, 서브프레임, 슬롯 등과 관련하여 본원에서 설명되지만, 이 기법들은 5G NR에서 "프레임", "서브프레임", "슬롯" 이외의 용어들을 사용하여 지칭될 수도 있는 다른 유형의 무선 통신 구조에도 동일하게 적용될 수 있다. 몇몇 양태들에서, 무선 통신 구조는 무선 통신 표준 및/또는 프로토콜에 의해 정의된 주기적인 시간-제한 (time-bounded) 통신 유닛을 지정할 수도 있다.

[0045] 특정 전기통신들 (예를 들어, LTE)에 있어서, BS는 BS에 의해 지원된 각각의 셀에 대한 시스템 대역폭의 중심에서 다운링크 상에서 프라이머리 동기화 신호 (PSS) 및 세컨더리 동기화 신호 (SSS)를 송신할 수도 있다. PSS 및 SSS는 도 3에 도시된 바와 같이 정규의 사이클릭 프리픽스를 갖는 각각의 무선 프레임의 서브프레임들 0 및 5에서 각각 심볼 기간들 6 및 5에서 송신될 수도 있다. PSS 및 SSS는 셀 검색 및 획득을 위해 UE들에 의해 이용될 수도 있다. BS는 BS에 의해 지원되는 각각의 셀에 대한 시스템 대역폭에 걸쳐 셀 특정 참조 신호 (CRS)를 송신할 수도 있다. CRS는 각 서브프레임의 특정 심볼 기간들에서 송신될 수도

있고, 채널 추정, 채널 품질 측정 및/또는 다른 기능들을 수행하기 위하여 UE 들에 의해 사용될 수도 있다. BS 는 또한, 특정 무선 프레임들의 슬롯 1에서 심볼 기간들 0 내지 3에서 물리 브로드캐스트 채널 (PBCH) 을 송신할 수도 있다. PBCH 는 일부 시스템 정보를 반송할 수도 있다. BS 는 특정 서브프레임들에서의 물리 다운링크 공유 채널 (PDSCH) 상에서 시스템 정보 블록들 (SIB들) 과 같은 다른 시스템 정보를 송신할 수도 있다. BS 는 서브프레임의 제 1 의 B 심볼 기간들에서 물리 다운링크 제어 채널 (PDCCH) 상에서 제어 정보/데이터를 송신할 수도 있으며, 여기서 B 는 각각의 서브프레임에 대해 구성가능할 수도 있다. BS 는 각각의 서브프레임의 나머지 심볼 기간들에서 PDSCH 상에서 트래픽 데이터 및/또는 다른 데이터를 송신할 수도 있다.

[0046] (예를 들어, NR 또는 5G 시스템들과 같은) 다른 시스템들에 있어서, 노드 B 는 서브프레임의 이 위치들에서 또는 상이한 위치들에서 이를 또는 다른 신호들을 송신할 수도 있다.

[0047] 상기한 바와 같이, 도 3 은 단지 일례로서 제공된다. 다른 예들이 가능하며, 도 3 에 대하여 설명된 것과 상이할 수도 있다.

[0048] 도 4 는 정규의 사이클릭 프리팹스를 갖는 2개의 예시적인 서브프레임 포맷들 (410 및 420) 을 도시한다. 가용 시간 주파수 리소스들은 리소스 블록들로 파티셔닝될 수도 있다. 각각의 리소스 블록은 하나의 슬롯에서 12개의 서브캐리어들을 커버할 수도 있고, 다수의 리소스 엘리먼트들을 포함할 수도 있다. 각각의 리소스 엘리먼트는 하나의 심볼 기간에서 하나의 서브캐리어를 커버할 수도 있고, 실수 또는 복소수 값일 수도 있는 하나의 변조 심볼을 전송하는 데 사용될 수도 있다.

[0049] 서브프레임 포맷 (410) 은 2개의 안테나들에 사용될 수도 있다. CRS 는 심볼 기간들 0, 4, 7 및 11에서 안테나들 0 및 1로부터 송신될 수도 있다. 참조 신호는 송신기 및 수신기에 의해 선형적으로 공지된 신호이고, 또한 파일럿으로서도 지칭될 수도 있다. CRS 는, 예를 들어, 셀 아이덴티티 (ID) 에 적어도 부분적으로 기초하여 생성된, 셀에 대해 특정된 참조 신호이다. 도 4 에서, 라벨 Ra 를 갖는 주어진 리소스 엘리먼트에 대해, 변조 심볼이 그 리소스 엘리먼트 상에서 안테나 a 로부터 송신될 수도 있고, 변조 심볼들은 그 리소스 엘리먼트 상에서 다른 안테나들로부터 송신되지 않을 수도 있다. 서브프레임 포맷 (420) 은 4개의 안테나들과 함께 사용될 수도 있다. CRS 는 심볼 기간들 0, 4, 7 및 11에서 안테나들 0 및 1로부터 그리고 심볼 기간들 1 및 8에서 안테나들 2 및 3 으로부터 송신될 수도 있다. 서브프레임 포맷들 (410 및 420) 쌍방에 대해, CRS 는, 셀 ID 에 적어도 부분적으로 기초하여 결정될 수도 있는 균등하게 이격된 서브캐리어들 상에서 송신될 수도 있다. CRS들은, 그들의 셀 ID 들에 따라, 동일 또는 상이한 서브캐리어들 상에서 송신될 수도 있다. 서브프레임 포맷들 (410 및 420) 양자에 대해, CRS 를 위해 사용되지 않는 리소스 엘리먼트들은 데이터 (예를 들어, 트래픽 데이터, 제어 데이터, 및/또는 다른 데이터) 를 송신하기 위해 사용될 수도 있다.

[0050] LTE 에서 PSS, SSS, CRS, 및 PBCH 는, 공개적으로 이용가능한 “Evolved Universal Terrestrial Radio Access (E-UTRA); Physical Channels and Modulation” 의 제목으로, 3GPP TS 36.211 에 기재되어 있다.

[0051] 인터레이스 구조가 소정의 전기통신 시스템들 (예를 들어, LTE) 에서 FDD 에 대한 다운링크 및 업링크의 각각을 위해 사용될 수도 있다. 예를 들어, 0 내지 Q-1 의 인덱스들을 갖는 Q 개의 인터레이스들이 정의될 수도 있으며, 여기서, Q 는 4, 6, 8, 10, 또는 기타 다른 값과 동일할 수도 있다. 각각의 인터레이스는 Q 개의 프레임들에 의해 이격되는 서브프레임들을 포함할 수도 있다. 특히, 인터레이스 q 는 서브프레임들 q, q+Q, q+2Q 등을 포함할 수도 있으며, 여기서,  $q \in \{0, \dots, Q-1\}$  이다.

[0052] 무선 네트워크는 다운링크 및 업링크 상에서의 데이터 송신을 위해 하이브리드 자동 재송신 요청 (HARQ) 을 지원할 수도 있다. HARQ 에 대해, 송신기 (예를 들어, BS) 는, 패킷이 수신기 (예를 들어, UE) 에 의해 정확하게 디코딩되거나 일부 다른 종료 조건이 조우될 때까지 패킷의 하나 이상의 송신들을 전송할 수도 있다. 동기 HARQ 에 대해, 패킷의 모든 송신들은 단일 인터레이스의 서브프레임들에서 전송될 수도 있다. 비동기 HARQ 에 대해, 패킷의 각각의 송신은 임의의 서브프레임에서 전송될 수도 있다.

[0053] UE 는 다수의 BS들의 커버리지 내에 위치될 수도 있다. 이들 BS들 중 하나가 UE 를 서빙하도록 선택될 수도 있다. 서빙 BS 는 수신 신호 강도, 수신 신호 품질, 경로 손실 등과 같은 다양한 기준들에 적어도 부분적으로 기초하여 선택될 수도 있다. 수신 신호 품질은 신호대 잡음 및 간섭 비 (SINR), 또는 참조 신호 수신 품질 (RSRQ), 또는 기타 다른 메트릭에 의해 정량화될 수도 있다. UE 는, UE 가 하나 이상의 간섭 SB 들로부터 높은 간섭을 관측할 수도 있는 지배적 간섭 시나리오에서 동작할 수도 있다.

[0054] 본 명세서에서 설명된 예들의 양태들이 LTE 기술들과 연관될 수도 있지만, 본 개시의 양태들은 NR 또는 5G 기술들과 같은 다른 무선 통신 시스템들로 적용가능할 수도 있다.

[0055]

뉴 라디오 (NR) 는 (예를 들어, 직교 주파수 분할 다중 액세스 (OFDMA) 기반 에어 인터페이스들 이외의) 새로운 에어 인터페이스 또는 (예를 들어, 인터넷 프로토콜 (IP) 이외의) 고정된 전송 계층에 따라 동작하도록 구성된 라디오들을 지칭할 수도 있다. 양태들에서, NR은 업링크상에서 CP를 갖는 OFDM (본 명세서에서 사이클릭 프리픽스 OFDM 또는 CP-OFDM 으로 칭함) 및/또는 SC-FDM 을 이용할 수도 있고, 다운 링크상에서 CP-OFDM 을 이용하고 TDD 를 사용하는 하프-듀플렉스 동작에 대한 지원을 포함할 수도 있다. 양태들에서, NR은 예를 들어 업링크상에서 CP를 갖는 OFDM (본 명세서에서 CP-OFDM 으로 칭함) 및/또는 이산 푸리에 변환 확산 직교 주파수 분할 멀티플렉싱 (DFT-s-OFDM) 을 이용할 수도 있고, 다운 링크상에서 CP-OFDM 을 이용하고 TDD 를 사용하는 하프-듀플렉스 동작에 대한 지원을 포함할 수도 있다. NR은 넓은 대역폭 (예를 들어, 80 메가헤르츠 (MHz) 이상) 을 타겟팅하는 향상된 모바일 브로드밴드 (eMBB) 서비스, 높은 캐리어 주파수 (예를 들어, 60 기가 헤르츠 (GHz)) 를 타겟팅하는 밀리미터파 (mmW), 비-역방향 호환가능 MTC 기법들을 타겟팅하는 대규모 MTC (mMTC), 및/또는 초신뢰성 저 레이턴시 통신 (URLLC) 서비스를 타겟팅하는 미션 크리티컬을 포함할 수도 있다.

[0056]

100 MHz 의 단일 컴포넌트 캐리어 대역폭이 지원될 수도 있다. NR 자원 블록들은 0.1 ms 지속기간 상에서 75 킬로헤르츠 (kHz) 의 서브캐리어 대역폭을 갖는 12 개의 서브캐리어들에 걸쳐 있을 수도 있다. 각각의 무선 프레임은 10 ms 의 길이를 갖는 50 개의 서브프레임들을 포함할 수도 있다. 결과적으로, 각각의 서브프레임은 0.2 ms 의 길이를 가질 수도 있다. 각각의 서브프레임은 데이터 송신을 위한 링크 방향 (예를 들어, DL 또는 UL) 을 나타낼 수도 있고, 각 서브프레임에 대한 링크 방향은 동적으로 스위칭될 수도 있다. 각각의 서브프레임은 DL/UL 데이터 뿐만 아니라, DL/UL 제어 데이터를 포함할 수도 있다. NR에 대한 UL 및 DL 서브프레임들은 도 7 및 도 8에 대하여 이하에 더 상세히 설명된 바와 같을 수도 있다.

[0057]

빔포밍이 지원될 수도 있으며, 빔 방향이 동적으로 구성될 수도 있다. 프리코딩을 갖는 MIMO 송신들이 또한 지원될 수도 있다. DL에서의 MIMO 구성들은, UE 당 2 개까지의 스트림들 및 8 개까지의 스트림들의 멀티-계층 DL 송신들을 갖는 8 개까지의 송신 안테나들을 지원할 수도 있다. UE 당 2 개까지의 스트림들을 갖는 멀티-계층 송신들이 지원될 수도 있다. 다중 셀들의 접성은 8 개까지의 서빙 셀들로 지원될 수도 있다. 대안적으로, NR은 OFDMA 기반 인터페이스 이외의 상이한 에어 인터페이스를 지원할 수도 있다. NR 네트워크들은 이러한 중앙 유닛들 또는 분산된 유닛들과 같은 엔티티 (entity) 들을 포함할 수도 있다.

[0058]

RAN은 중앙 유닛 (CU) 및 분산 유닛들 (DU들) 을 포함할 수도 있다. NR BS (예를 들어, gNB, 5G 노드 B, 노드 B, 송신 수신 포인트 (TRP), 액세스 포인트 (AP)) 는 하나 또는 다수의 BS 들에 대응할 수도 있다. NR 셀들은 액세스 셀들 (ACells) 또는 데이터 전용 셀들 (DCells) 로서 구성될 수 있다. 예를 들어, RAN (예를 들어, 중앙 유닛 또는 분산형 유닛) 이 셀들을 구성할 수도 있다. DCel1들은 캐리어 접성 또는 이중 접속성에 사용되는 셀들일 수도 있지만, 초기 액세스, 셀 선택/재선택 또는 핸드오버에는 사용되지 않는다. 일부 경우들에서, DCel1들은 동기화 신호들을 송신하지 않을 수도 있다-일부 경우에, DCel1들이 SS 를 송신할 수도 있다. NR BS들은 셀 태입을 표시하는 다운링크 신호들을 UE들에 송신할 수도 있다. 셀 태입 표시에 적어도 부분적으로 기초하여, UE는 NR BS 와 통신할 수도 있다. 예를 들어, UE는 표시된 셀 태입에 적어도 부분적으로 기초하여 셀 선택, 액세스, 핸드오버, 및/또는 측정에 대해 고려할 NR BS들을 결정할 수도 있다.

[0059]

상기한 바와 같이, 도 4 는 단지 일례로서 제공된다. 다른 예들이 가능하며, 도 4에 대하여 설명된 것과 상이할 수도 있다.

[0060]

도 5 는 본 개시의 양태들에 따른 분산 RAN (500) 의 예시적인 논리적 아키텍처를 나타낸다. 5G 액세스 노드 (506) 는 액세스 노드 제어기 (ANC) (502) 를 포함할 수도 있다. ANC는 분산 RAN (500) 의 중앙 유닛 (CU) 일 수도 있다. 차세대 코어 네트워크 (NG-CN) (504) 에 대한 백홀 인터페이스는 ANC에서 종단될 수도 있다. 이웃하는 차세대 액세스 노드들 (NG-AN들) 에 대한 백홀 인터페이스는 ANC에서 종단될 수도 있다. ANC는 (BS들, NR BS들, 노드 B들, 5G NB들, AP들, gNB, 또는 일부 다른 용어로도 지칭될 수도 있는) 하나 이상의 TRP들 (508) 을 포함할 수도 있다. 상기 설명된 바와 같이, TRP는 "셀" 과 상호교환가능하게 사용될 수도 있다.

[0061]

TRP들 (508) 은 분산 유닛 (DU) 일 수도 있다. TRP들은 하나의 ANC (ANC (502)) 또는 2 이상의 ANC (도시 되지 않음) 에 접속될 수도 있다. 예를 들어, RAN 공유, RaaS (radio as a service) 및 서비스 특정 AND 배치를 위해, TRP는 2 이상의 ANC에 접속될 수도 있다. TRP는 하나 이상의 안테나 포트들을 포함할 수도 있다. TRP들은 개별적으로 (예를 들어, 동적 선택) 또는 공동으로 (예를 들어, 공동 송신) UE에 트래픽을 서비스하도록 구성될 수도 있다.

[0062]

RAN (500) 의 로컬 아키텍처는 프론트홀 정의 (fronthaul definition) 를 예시하기 위해 사용될 수도 있다.

상이한 전개 타입들에 걸쳐 프론트홀링 솔루션들을 지원하는 아키텍처가 정의될 수도 있다. 예를 들어, 아키텍처는 송신 네트워크 능력들 (예를 들어, 대역폭, 레이턴시, 및/또는 지터)에 적어도 부분적으로 기초할 수도 있다.

[0063] 아키텍처는 LTE 와 특징들 및/또는 컴포넌트들을 공유할 수도 있다. 양태들에 따르면, 차세대 AN (NG-AN) (510)은 NR 과의 이종 접속성을 지원할 수도 있다. NG-AN은 LTE 및 NR에 대해 공동 프론트홀을 공유할 수도 있다.

[0064] 아키텍처는 TRP들 (508) 간의 및 중의 협력을 가능하게 할 수도 있다. 예를 들어, 협력은 ANC (502)를 통해 TRP 내에서 및/또는 TRP들에 걸쳐서 사전설정될 수도 있다. 양태들에 따르면, 어떠한 TRP간 인터페이스도 필요/존재하지 않을 수도 있다.

[0065] 양태들에 따르면, 분할된 논리 기능들의 동적 구성이 RAN (500)의 아키텍처 내에 존재할 수도 있다. PDCP, RLC, MAC 프로토콜은 ANC 또는 TRP에 적응가능하게 배치될 수도 있다.

[0066] 소정의 양태들에 따르면, BS는 중앙 유닛 (CU) (예를 들어, ANC (502)) 및/또는 하나 이상의 분산 유닛들 (예컨대, 하나 이상의 TRP들 (508))을 포함할 수도 있다.

[0067] 상기한 바와 같이, 도 5는 단지 일례로서 제공된다. 다른 예들이 가능하며, 도 5에 대하여 설명된 것과 상이할 수도 있다.

[0068] 도 6은 본 개시의 특정 양태들에 따른, 분산형 RAN (600)의 예시적인 물리적 아키텍처를 예시한다. 중앙 집중형 코어 네트워크 유닛 (C-CU) (602)은 코어 네트워크 기능들을 호스팅할 수도 있다. C-CU는 중앙집 중식으로 전개될 수도 있다. C-CU 기능성은 피크 용량을 핸들링하려는 노력으로, (예를 들어, AWS (advanced wireless services)로) 오프로딩될 수도 있다.

[0069] 중앙 집중형 RAN 유닛 (C-RU) (604)은 하나 이상의 ANC 기능들을 호스팅할 수도 있다. 옵션적으로, C-RU는 코어 네트워크 기능들을 로컬로 호스팅할 수도 있다. C-RU는 분산된 전개를 가질 수도 있다. C-RU는 네트워크 에지에 더 가까울 수도 있다.

[0070] 분산 유닛 (DU) (606)은 하나 이상의 TRP들을 호스팅할 수도 있다. DU는 무선 주파수 (RF) 기능성을 가진 네트워크의 에지들에 위치될 수도 있다.

[0071] 상기한 바와 같이, 도 6은 단지 일례로서 제공된다. 다른 예들이 가능하며, 도 6에 대하여 설명된 것과 상이할 수도 있다.

[0072] 도 7은 DL-중심 슬롯 또는 무선 통신 구조의 예를 도시하는 다이어그램 (700)이다. DL-중심 슬롯은, DL 제어 부분 (702)과 같은 제 1 부분; DL 데이터 부분 (704)과 같은 제 2 부분; 및 UL 짧은 버스트 부분 (706)과 같은 제 3 부분을 포함할 수도 있다. DL 제어 부분 (702)은 DL-중심 슬롯의 시작부에 위치될 수도 있다. DL 제어 부분 (702)은 DL-중심 슬롯의 다양한 부분들에 대응하는 다양한 스케줄링 정보 및/또는 제어 정보를 포함할 수도 있다. 일부 구성들에서, DL 제어 부분 (702)은 물리적 DL 제어 채널 (PDCCH) 상에 통신을 위해 사용될 수도 있다.

[0073] DL 데이터 부분 (704)은 DL 제어 부분 (702)과 UL 짧은 버스트 부분 (706) 사이에 위치될 수도 있다. DL 데이터 부분 (704)은 때때로 DL-중심 슬롯의 페이로드로서 지정될 수도 있다. DL 데이터 부분 (704)은 스케줄링 엔티티 (예를 들어, UE 또는 BS)로부터 종속 엔티티 (예컨대, UE)로 DL 데이터를 통신하는데 이용되는 통신 리소스들을 포함할 수도 있다. 일부 구성들에서, DL 데이터 부분 (704)은 물리적 DL 공유 채널 (PDSCH) 상에 통신을 위해 사용될 수도 있다.

[0074] UL 짧은 버스트 부분 (706)은 DL-중심 슬롯의 끝에 위치될 수도 있다. UL 짧은 버스트 부분 (706)은 때때로 공동 UL 부분, UL 버스트, UL 버스트 부분, 공동 UL 버스트, 짧은 버스트, UL 짧은 버스트, 공동 UL 짧은 버스트, 공동 UL 짧은 버스트 부분, 및/또는 다양한 다른 적절한 용어로서 지정될 수도 있다. 일부 양태들에서, DL 짧은 버스트 부분 (706)은 물리적 UL 제어 채널 (PUCCH) 상에 통신을 위해 사용될 수도 있다. 추가적으로 또는 대안적으로, UL 짧은 버스트 부분 (706)은 스케줄링 요청 (SR), HARQ 정보 (예를 들어, PUCCH ACK, PUSCH ACK, PUCCH NACK, PUSCH NACK 등)와 같은 업링크 제어 정보, 채널 품질 표시자 (CQI), 채널 상태 표시 (CSI), 베티 상태 보고 (BSR), 사운딩 참조 신호 (SRS), 복조 참조 신호 (DMRS) 및/또는 다양한 다른 적절한 타입의 정보의 통신을 위해 사용될 수도 있다.

- [0075] 도 7 에 나타낸 바와 같이, DL 데이터 부분 (704) 의 끝은 UL 짧은 버스트 부분 (706) 의 시작으로부터 시간적으로 분리될 수도 있다. 이 시간 분리는 때때로 캡, 가드 기간, 가드 인터벌, 및/또는 다양한 다른 적합한 용어들로 지칭될 수도 있다. 이러한 분리는 DL 통신 (예를 들어, 종속 엔티티 (예를 들어, UE) 에 의한 수신 동작) 으로부터 UL 통신 (예를 들어, 종속 엔티티 (예를 들어, UE) 에 의한 송신) 으로의 스위치-오버를 위한 시간을 제공한다. 전술한 내용은 단지 DL-중심 슬롯의 일례이며, 유사한 특징을 갖는 대안적인 구조들이 본원에서 설명된 양태들을 반드시 벗어남이 없이 존재할 수도 있다.

- [0076] 상기한 바와 같이, 도 7 은 단지 일례로서 제공된다. 다른 예들이 가능하며, 도 7 에 대하여 설명된 것과 상이할 수도 있다.

- [0077] 도 8 은 UL-중심 슬롯 또는 무선 통신 구조의 예를 보여주는 다이어그램 (800) 이다. DL-중심 슬롯은, DL 제어 부분 (802) 과 같은 제 1 부분; UL 긴 버스트 부분 (804) 과 같은 제 2 부분; 및 UL 짧은 버스트 부분 (806) 과 같은 제 3 부분을 포함할 수도 있다. DL 제어 부분 (802) 은 DL-중심 슬롯의 시작부에 위치될 수도 있다. 도 8 에서의 DL 제어 부분 (802) 은 도 7 을 참조하여 전술된 DL 제어 부분 (702) 과 유사할 수도 있다. 일부 구성들에서, DL 제어 부분 (802) 은 물리적 DL 제어 채널 (PDCCH) 상에 통신을 위해 사용될 수도 있다.

- [0078] UL 긴 버스트 부분 (804) 은 DL 제어 부분 (802) 과 UL 짧은 버스트 부분 (806) 사이에 위치될 수도 있다. UL 긴 버스트 부분 (804) 은 때때로 DL-중심 슬롯의 페이로드로서 지칭될 수도 있다. UL 긴 버스트 부분 (804) 은 종속 엔티티 (예를 들어, UE) 로부터 스케줄링 엔티티 (예를 들어, UE 또는 BS) 로 UL 데이터를 통신하는데 활용되는 통신 리소스들을 지칭할 수도 있다. 일부 구성들에서, UL 긴 버스트 부분 (804) 은 여기에 설명된 바와 같이 물리적 UL 공유 채널 (PUSCH) 및/또는 물리적 업링크 제어 채널 (PUCCH) 상에 통신을 위해 사용될 수도 있다.

- [0079] 도 8 에 나타낸 바와 같이, DL 제어 부분 (802) 의 끝은 UL 긴 버스트 부분 (804) 의 시작으로부터 시간적으로 분리될 수도 있다. 이 시간 분리는 때때로 캡, 가드 기간, 가드 인터벌, 및/또는 다양한 다른 적합한 용어들로 지칭될 수도 있다. 이러한 분리는 DL 통신 (예를 들어, 종속 엔티티에 의한 수신 동작) 으로부터 UL 통신 (예를 들어, 스케줄링 엔티티에 의한 송신) 으로의 스위치-오버를 위한 시간을 제공한다.

- [0080] UL 짧은 버스트 부분 (806) 은 UL-중심 슬롯의 끝에 위치될 수도 있다. 도 8 의 UL 짧은 버스트 부분 (806) 은 도 7 을 참조하여 전술한 UL 짧은 버스트 부분 (706) 과 유사할 수도 있고, 도 7 과 관련하여 전술한 정보 중 임의의 것을 포함할 수도 있다. 전술한 내용은 단지 UL-중심 슬롯의 일례일 뿐이며, 유사한 특징들을 갖는 대안적인 구조들이 여기에서 설명된 양태들을 반드시 벗어남이 없이 존재할 수도 있다.

- [0081] 일부 상황들에서, 2 개 이상의 종속 엔티티들 (예컨대, UE들) 이 사이드링크 신호들을 사용하여 서로 통신할 수도 있다. 이러한 사이드 링크 통신들의 현실 세계 애플리케이션들은 공공 안전, 근접 서비스, UE-대-네트워크 릴레이, V2V (Vehicle-to-Vehicle) 통신, IoE (Internet of Everything) 통신, IoT 통신, 미션 크리티컬 메쉬 및/또는 다양한 다른 적합한 애플리케이션들을 포함할 수도 있다. 일반적으로, 사이드링크 신호는, 스케줄링 엔티티가 스케줄링 및/또는 제어 목적을 위해 활용될 수도 있지만, 스케줄링 엔티티 (예컨대, UE 또는 BS) 를 통해 그 통신을 중계함이 없이 하나의 종속 엔티티 (예를 들어, UE1) 로부터 다른 종속 엔티티 (예를 들어, UE2) 로 통신되는 신호를 지칭할 수도 있다. 일부 예들에서, (통상적으로 비허가 스펙트럼을 사용하는 무선 로컬 영역 네트워크와 달리) 사이드링크 신호들은 허가 스펙트럼을 사용하여 통신될 수도 있다.

- [0082] 일 예에서, 프레임과 같은 무선 통신 구조는 UL-중심 슬롯들 및 DL-중심 슬롯들 쌍방을 포함할 수도 있다. 이 예에서, 프레임 내의 UL-중심 슬롯들 대 DL-중심 슬롯들의 비율은 송신되는 UL 데이터의 양 및 DL 데이터의 양에 적어도 부분적으로 기초하여 동적으로 조정될 수도 있다. 예를 들어, 더 많은 UL 데이터가 존재하는 경우, UL-중심 슬롯들 대 DL-중심 슬롯들의 비율이 증가될 수도 있다. 반대로, 더 많은 DL 데이터가 존재하는 경우, UL-중심 슬롯들 대 DL-중심 슬롯들의 비율이 감소될 수도 있다.

- [0083] 상기한 바와 같이, 도 8 은 단지 일례로서 제공된다. 다른 예들이 가능하며, 도 8 에 대하여 설명된 것과 상이할 수도 있다.

- [0084] 도 9 는 풀-DL 슬롯 또는 무선 통신 구조의 일례를 보여주는 다이어그램 (900) 이다. 풀-DL 슬롯은 DL 제어 부분 (902) 및 DL 데이터 부분 (904) 으로서 나타낸, 도 7 과 관련하여 전술한 제 1 부분 및 제 2 부분 (예컨대, DL 제어 부분 (702) 및 DL 데이터 부분 (704)) 을 포함할 수도 있다. 풀-DL 슬롯은 도 7 과 관련하여 전술한 제 3 부분 (예를 들어, UL 짧은 버스트 부분 (706)) 을 배제할 수도 있다.

- [0085] DL 제어 부분 (902) 은 풀-DL 슬롯의 시작부에 위치될 수도 있다. DL 제어 부분 (902) 은 도 7 및 도 8 과 관련하여 전술한 DL 제어 부분 (702) 및/또는 DL 제어 부분 (802) 과 유사한 방식으로 사용될 수도 있다.

- [0086] DL 데이터 부분 (904) 은 DL 제어 부분 (902) 뒤에 그리고 풀-DL 슬롯의 끝에 위치될 수도 있다. DL 데이터 부분 (904) 은 도 7 과 관련하여 전술한 DL 데이터 부분 (704) 과 유사한 방식으로 사용될 수도 있다.

- [0087] 상기한 바와 같이, 도 9 는 단지 일례로서 제공된다. 다른 예들이 가능하며, 도 9 에 대하여 설명된 것과 상이할 수도 있다.

- [0088] 도 10 은 풀-UL 슬롯 또는 무선 통신 구조의 일례를 보여주는 다이어그램 (1000) 이다. 풀-DL 슬롯은 UL 긴 버스트 부분 (1004) 및 UL 짧은 버스트 부분 (1006) 으로서 나타낸, 도 8 과 관련하여 전술한 제 2 부분 및 제 3 부분 (예컨대, UL 긴 버스트 부분 (804) 및 UL 짧은 버스트 부분 (806)) 을 포함할 수도 있다. 풀-UL 슬롯은 도 8 과 관련하여 전술한 제 1 부분 (예컨대, DL 제어 부분 (802)) 을 배제할 수도 있다.

- [0089] UL 긴 버스트 부분 (1004) 은 풀-UL 슬롯의 시작부에 위치될 수도 있다. UL 긴 버스트 부분 (1004) 은 도 8 과 관련하여 전술한 UL 긴 버스트 부분 (804) 과 유사한 방식으로 사용될 수도 있다.

- [0090] UL 짧은 버스트 부분 (1006) 은 UL 긴 버스트 부분 (1004) 뒤에 그리고 풀-UL 슬롯의 끝에 위치될 수도 있다. UL 짧은 버스트 부분 (1006) 은 도 7 및 도 8 과 관련하여 전술한 UL 짧은 버스트 부분 (706) 및/또는 UL 짧은 버스트 부분 (806) 과 유사한 방식으로 사용될 수도 있다.

- [0091] 상기한 바와 같이, 도 10 은 단지 일례로서 제공된다. 다른 예들이 가능하며, 도 10 에 대하여 설명된 것과 상이할 수도 있다.

- [0092] 뉴 라디오에서, 슬롯은 LTE 에서 1 밀리초 서브프레임과 비교하여 0.5 밀리초 이하의 길이를 가질 수도 있다. 결과적으로, UE 는 LTE 와 비교하여 뉴 라디오에서 정보를 송신하는데 더 적은 에너지를 사용할 수도 있고, 이는 감소된 업링크 성능을 초래할 수도 있다. 뉴 라디오에서 업링크 성능을 향상시키기 위해, 그리고 특히 PUCCH 를 통해 송신된 업링크 제어 정보 (UCI) 가 기지국에 의해 수신될 가능성을 높이기 위해, UE 는, 특히 UE 가 셀 애지에 위치되는 경우, UCI 를 송신하기 위해 다중 슬롯들 및/또는 슬롯의 다중 부분들을 사용할 수도 있다. 본원에서 설명된 양태들은 UE 가 슬롯의 다중 부분들 및/또는 다중 슬롯들에서 대응 UCI 의 송신을 구성할 수 있게 함으로써, 업링크 성능을 증가시킨다. 대응 UCI 는 예컨대 반복된 UCI 또는 공동으로 인코딩된 UCI 를 포함할 수도 있다.

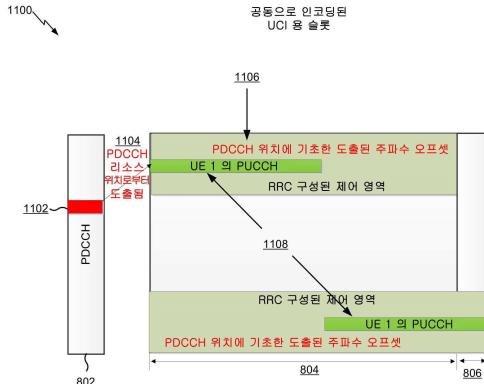

- [0093] 도 11a 및 도 11b 는 뉴 라디오에서 대응 UCI 의 송신을 구성하는 예 (1100) 를 도시한 다이어그램이다. 도 11a 및 도 11b 는 제 1 UCI 및 제 2 UCI 가 공동으로 인코딩되어 동일한 UL-중심 슬롯에서 송신되는 예를 보여준다. UL-중심 슬롯은, 도 8 과 관련하여 전술한 바와 같이, DL 제어 부분 (802), UL 긴 버스트 부분 (804) 및 UL 짧은 버스트 부분 (806) 을 포함할 수도 있다. UL-중심 슬롯은 UE (도 1 의 UE (120) 등) 와 기지국 (예컨대, 도 1 의 기지국 (110) 등) 사이의 통신을 위해 사용될 수도 있다.

- [0094] 도 11a 에 도시된 바와 같이, UE 는 UL-중심 슬롯의 DL 제어 부분 (802) 에서 UL 제어 구성 표시 (1102) 를 수신할 수도 있다. UE 는 UL 제어 구성 표시 (1102) 에 적어도 부분적으로 기초하여 공동으로 인코딩된 UCI (예컨대 공동으로 인코딩된 제 1 UCI 및 제 2 UCI) 의 송신을 위해 UL-중심 슬롯의 적어도 하나의 다른 부분 상에 PUCCH 를 구성할 수도 있다. 예를 들어, UE 는 UL 긴 버스트 부분 (804) 및/또는 UL 짧은 버스트 부분 (806) 상에 PUCCH 를 구성할 수도 있다. UE 는 UL-중심 슬롯의 부분(들) 상에 구성된 PUCCH 상에 공동으로 인코딩된 UCI 를 송신할 수도 있다.

- [0095] 몇몇 양태들에서, UE 는 UL 긴 버스트 부분 (804) 및 UL 짧은 버스트 부분 (806) 쌍방에서 PUCCH 를 구성할 수도 있고, UL 긴 버스트 부분 (804) 및 UL 짧은 버스트 부분 (806) 쌍방에서 PUCCH 상에 공동으로 인코딩된 UCI 를 송신할 수도 있다. 예를 들어, PUCCH 는 UL 긴 버스트 부분 (804) 의 끝 경계 및 UL 짧은 버스트 부분 (806) 의 시작 경계를 가로질러 연장될 수도 있다.

- [0096] 몇몇 양태들에서, UL 제어 구성 표시 (1102) 는 PUCCH 가 단지 UL 긴 버스트 부분 (804) 에서 또는 UL 긴 버스트 부분 (804) 과 UL 짧은 버스트 부분 (806) 쌍방에서 구성되어야 하는지 여부를 표시할 수도 있다. 예를 들어, UL 제어 구성 표시 (1102) 의 하나 이상의 비트는 PUCCH 가 UL 긴 버스트 부분 (804) 의 끝 경계 및 UL 짧은 버스트 부분 (806) 의 시작 경계를 가로질러 연장되어야 하는지 여부를 표시할 수도 있다.

- [0097] 몇몇 양태들에서, UE 는 UL-중심 슬롯들의 UL 긴 버스트 부분 (804) 및 UL 짧은 버스트 부분 (806) 쌍방에서 PUCCH 를 구성하도록 디폴트 구성으로 구성될 수도 있다. 이 경우, PUCCH 가 UL-중심 슬롯의 UL 긴 버스트

부분 (804) 에서만 (또는 UL 짧은 버스트 부분 (806) 에서만) 구성되어야 한다고 UL 제어 구성 표시 (1102) 가 표시하면, UE 는 공동으로 인코딩된 UCI 의 하나 이상의 비트를 절단(truncate) 할 수도 있다. 예를 들어, PUCCH 가 UL 긴 버스트 부분 (804) 에서만 구성되어야 한다고 UL 제어 구성 표시 (1102) 가 표시하면, UE 는 디폴트 구성에 따라 UL 짧은 버스트 부분 (806) 에서 송신된 공동으로 인코딩된 UCI 의 하나 이상의 비트를 절단 할 수도 있고, UL 긴 버스트 부분 (804) 에서 공동으로 인코딩된 UCI 의 나머지 비트(들)를 송신할 수도 있다.

이런 식으로, UE 는 디폴트 구성에 기초하여 제 1 UCI 및 제 2 UCI를 공동으로 인코딩하기 위해 동일한 인코딩 계획을 사용할 수도 있고, 이로써 복잡성을 줄이고 UE 리소스를 보존하면서, 디폴트 구성과는 상이한 송신을 핸들링하는 유연성을 갖는다.

[0098] 몇몇 양태들에서, UE 는 UL-중심 슬롯들의 UL 긴 버스트 부분 (804) 에서만 (또는 UL 짧은 버스트 부분 (806) 에서만) PUCCH 를 구성하도록 디폴트 구성으로 구성될 수도 있다. 이 경우, PUCCH 가 UL 긴 버스트 부분 (804) 및 UL 짧은 버스트 부분 (806) 쌍방에서 구성되어야 한다고 UL 제어 구성 표시 (1102) 가 표시하면, UE 는 공동으로 인코딩된 UCI 의 하나 이상의 비트를 반복할 수도 있다. 예를 들어, 디폴트 구성이 UL-중심 슬롯들의 UL 긴 버스트 부분 (804) 에서만 PUCCH 를 구성하고, PUCCH 가 UL-중심 슬롯의 UL 긴 버스트 부분 (804) 및 UL 짧은 버스트 부분 (806) 쌍방에서 구성되어야 한다고 UL 제어 구성 표시 (1102) 가 표시하면, UE 는 UL 긴 버스트 부분 (804) 에서 송신되는 공동으로 인코딩된 UCI 의 하나 이상의 비트를 반복 (예를 들어, 복사) 할 수도 있고, UL 짧은 버스트 부분 (806) 에서 반복된 비트(들)를 송신할 수도 있다. 이런 식으로, UE 는 디폴트 구성에 기초하여 제 1 UCI 및 제 2 UCI를 공동으로 인코딩하기 위해 동일한 인코딩 계획을 사용할 수도 있고, 이로써 복잡성을 줄이고 UE 리소스를 보존하면서, 디폴트 구성과는 상이한 송신을 핸들링하는 유연성을 갖는다.

[0099] 일부 양태들에서, DL 제어 부분 (802) 의 지속기간은 상이한 슬롯들에서 상이할 수도 있다. 이 경우, UE 는 전술한 것과 유사한 방식으로 DL 제어 부분 (802) 의 지속기간에 적어도 부분적으로 기초하여 공동으로 인코딩 된 UCI 의 하나 이상의 비트를 절단 또는 반복할 수도 있다. 예를 들어, 슬롯에 대한 DL 제어 부분 (802) 이 디폴트 DL 제어 부분보다 짧다면, UE 는 공동으로 인코딩된 UCI 의 하나 이상의 비트를 반복할 수도 있고, 더 짧은 DL 제어 부분 (802) 으로 인해 길어질 수도 있는, UL 긴 버스트 부분 (804) 및/또는 UL 짧은 버스트 부분 (806) 에서 이 비트(들)를 송신할 수도 있다. 유하사계, 슬롯에 대한 DL 제어 부분 (802) 이 디폴트 DL 제어 부분보다 길다면, UE 는 공동으로 인코딩된 UCI 의 하나 이상의 비트를 절단할 수도 있고, 더 긴 DL 제어 부분 (802) 으로 인해 짧아질 수도 있는, UL 긴 버스트 부분 (804) 및/또는 UL 짧은 버스트 부분 (806) 에서 나머지 비트(들)를 송신할 수도 있다. 이런 식으로, UE 는 디폴트 구성에 기초하여 제 1 UCI 및 제 2 UCI를 공동으로 인코딩하기 위해 동일한 인코딩 계획을 사용할 수도 있고, 이로써 복잡성을 줄이고 UE 리소스를 보존하면서, 디폴트 구성과는 상이한 송신을 핸들링하는 유연성을 갖는다.

[0100] 몇몇 양태들에서, UE 는 하나 이상의 주파수 대역들에서 PUCCH 를 구성할 수도 있다. 도면부호 1104 에 의해 나타낸 바와 같이, 몇몇 양태들에서, 하나 이상의 주파수 대역들은 UL 제어 구성 표시 (1102) 의 수신과 관련된 특성으로부터 도출될 수도 있다. 예를 들어, 특성은 UL 제어 구성 표시 (1102) 의 수신에 사용되는 주파수 대역을 포함할 수도 있고, PUCCH 의 하나 이상의 주파수 대역들은 UL 제어 구성 표시 (1102) 의 수신에 사용된 주파수 대역으로부터 도출될 수도 있다.

[0101] 도면부호 1106 에 의해 나타낸 바와 같이, 몇몇 양태들에서, UE 는 주파수 오프셋을 도출하기 위해 특성을 사용할 수도 있고, 주파수 오프셋에 적어도 부분적으로 기초하여 하나 이상의 주파수 대역들을 결정할 수도 있다.

예를 들어, UE 는 (예를 들어, RRC (radio resource control) 구성 메시지에서 식별된) 주파수 대역 제어 영역으로 구성될 수도 있으며, 나타낸 것처럼 주파수 오프셋을 주파수 대역 제어 영역의 경계에 적용함으로써 하나 이상의 주파수 대역들을 결정할 수도 있다. 본원에서 사용된 바와 같이, UE 는 다른 값 (예를 들어, UL 제어 구성 표시 (1102) 의 수신에 사용되는 주파수 대역) 에 함수를 적용함으로써 값 (예를 들어, PUCCH 에 대한 하나 이상의 주파수 대역) 을 도출할 수도 있다. 함수는 UE 에 의해 저장된 디폴트 함수이거나 또는 기지국에 의해 UE 에 시그널링되는 함수 (예를 들어, RRC 접속 구성 메시지에서) 일 수도 있다.

[0102] 도면부호 1108 에 의해 나타낸 바와 같이, 몇몇 양태들에서, UE 는 다중 주파수 대역들에서 PUCCH 를 구성할 수도 있다. 예를 들어, UE 는 전술한 바와 같이 UL 제어 구성 표시 (1102) 의 특성에 적어도 부분적으로 기초하여 다중 주파수 대역들을 도출할 수도 있다. 몇몇 양태들에서, UE 는 다중 주파수 대역 제어 영역들로 구성될 수도 있고, PUCCH 에 대한 다중 주파수 대역들을 결정하기 위해 다중 주파수 대역 제어 영역들로 특성으로부터 도출된 동일한 오프셋을 적용할 수도 있다. 몇몇 양태들에서, UE 는 상이한 오프셋을 적용할 수도 있다. 이런 식으로, UE 는 기지국에 의한 UCI 의 성공적인 수신 및 디코딩의 가능성을 증가시키기 위해 주파

수 다이버시티를 사용할 수도 있다.

[0103] 또한 나타낸 바와 같이, 몇몇 양태들에서, UE는 상이한 시간 기간들 동안 상이한 주파수 대역들에서 PUCCH를 구성할 수도 있다. 이 경우, UE는 제1시간 기간에서 제1주파수 대역을 사용하여 공동으로 인코딩된 UCI의 제1부분을 송신할 수도 있고, 제2시간 기간에서 제2주파수 대역을 사용하여 공동으로 인코딩된 UCI의 제2부분을 송신할 수도 있다. 몇몇 양태들에서, 시간 기간들은 나타된 바와 같이 중첩되지 않을 수도 있다. 이런 식으로, UE는 기지국에 의한 UCI의 성공적인 수신 및 디코딩의 가능성을 증가시키기 위해 주파수 다이버시티를 사용할 수도 있다.

[0104] 도 11b에 그리고 도면부호 1110에 의해 나타낸 바와 같이, 몇몇 양태들에서, PUCCH에 대한 하나 이상의 주파수 대역들은 UL 제어 구성 표시(1102)에서 시그널링될 수도 있다. 예를 들어, UL 제어 구성 표시(1102)는 하나 이상의 주파수 대역들을 식별하는 정보를 포함할 수도 있고, UE는 이 정보에 기초하여(예를 들어, 하나 이상의 주파수 대역들을 도출하기 위한 함수를 적용함이 없이) 하나 이상의 주파수 대역들을 결정할 수도 있다.

[0105] 도면부호 1112에 의해 나타낸 바와 같이, 몇몇 양태들에서, UE는 다중 주파수 대역들에서 PUCCH를 구성할 수도 있다. 예를 들어, 다중 주파수 대역들은 전술한 바와 같이 UL 제어 구성 표시(1102)에서 시그널링될 수도 있다. 추가적으로 또는 대안적으로, 주파수 대역들 중 하나가 UL 제어 구성 표시(1102)에서 시그널링될 수도 있고, UE는 시그널링된 주파수 대역(들)에 적어도 부분적으로 기초하여 다른 주파수 대역(들)을 도출할 수도 있다. 예를 들어, UE는 다른 주파수 대역(들)을 결정하기 위해 시그널링된 주파수 대역(들)에 주파수 오프셋을 적용할 수도 있다. 이런 식으로, UE는 기지국에 의한 UCI의 성공적인 수신 및 디코딩의 가능성을 증가시키기 위해 주파수 다이버시티를 사용할 수도 있다. 몇몇 양태들에서, 나타낸 바와 같이, UE는 동일한 시간 기간 동안 상이한 주파수 대역들에서 PUCCH를 구성할 수도 있다.

[0106] 도면부호 1114에 의해 나타낸 바와 같이, 몇몇 양태들에서, UE는 UL 긴 버스트 부분(804) 및/또는 UL 짧은 버스트 부분(806) 상에 PUSCH를 구성할 수도 있다. PUSCH는 제1UCI 및/또는 제2UCI와 동시에 콘텐츠의 송신을 위해 구성될 수도 있다. 예를 들어, UE는 PUSCH에서(예를 들어, 하나 이상의 PUSCH 주파수 대역들에서) 콘텐츠의 송신과 동시에 PUCCH에서(예를 들어, 하나 이상의 PUCCH 주파수 대역들에서) 공동으로 인코딩된 UCI를 송신할 수도 있다. 이런 식으로, UE는 동시 송신(concurrent transmissions)을 사용하여 업링크 처리량을 증가시킬 수도 있다.

[0107] 전술한 바와 같이, 도 11a 및 도 11b는 예시로서 제공된다. 다른 예들이 가능하며, 도 11a 및 도 11b에 대하여 설명된 것과 상이할 수도 있다.

[0108] 도 12a 및 도 12b는 뉴 라디오에서 대응 UCI의 송신을 구성하는 예(1200)를 도시한 다이어그램이다. 도 12a 및 도 12b는 제1UCI 및 제2UCI가 반복된 UCI이고 동일한 UL-중심 슬롯에서 송신되는 예를 보여준다. 예를 들어, UE는(예를 들어, 제1UCI의 비트들을 복사함으로써) 제2UCI를 생성하기 위해 제1UCI를 반복할 수도 있다. UL-중심 슬롯은, 도 8과 관련하여 전술한 바와 같이, DL 제어 부분(802), UL 긴 버스트 부분(804) 및 UL 짧은 버스트 부분(806)을 포함할 수도 있다. UL-중심 슬롯은 UE(도 1의 UE(120) 등)와 기지국(예컨대, 도 1의 기지국(110) 등) 사이의 통신을 위해 사용될 수도 있다.

[0109] 도 12a에 도시된 바와 같이, UE는 UL-중심 슬롯의 DL 제어 부분(802)에서 UL 제어 구성 표시(1202)를 수신할 수도 있다. UE는 UL 제어 구성 표시(1202)에 적어도 부분적으로 기초하여 UL-중심 슬롯의 UL 긴 버스트 부분(804) 및 UL 짧은 버스트 부분(806) 상에 PUCCH를 구성할 수도 있다. 몇몇 양태들에서, UE는 UL 긴 버스트 부분(804) 상에 구성된 PUCCH 상에서 제1UCI를 송신할 수도 있고, UL 짧은 버스트 부분(806) 상에 구성된 PUCCH 상에서 제2UCI를 송신할 수도 있다.

[0110] 몇몇 양태들에서, UE는 하나 이상의 주파수 대역들에서 PUCCH를 구성할 수도 있다. 도면부호 1204에 의해 나타낸 바와 같이, 몇몇 양태들에서, 하나 이상의 주파수 대역들은 도 11a 및 도 11b와 관련하여 전술한 바와 같이 UL 제어 구성 표시(1202)의 수신과 관련된 특성으로부터 도출될 수도 있고/있거나 UL 제어 구성 표시(1202)에서 시그널링될 수도 있다.

[0111] 몇몇 양태들에서, 하나 이상의 주파수 대역들은 UL 긴 버스트 부분(804)에서의 하나 이상의 제1주파수 대역들(1206) 및 UL 짧은 버스트 부분(806)에서의 하나 이상의 제2주파수 대역들(1208)을 포함할 수도 있다. 몇몇 양태들에서, 제1주파수 대역(들)(1206)은 제2주파수 대역(들)(1208)과 상이할 수도 있으며, 이는 주파수 대역(들) 중 하나가 불량한 성능을 겪는 때에 주파수 다이버시티를 사용하여 UCI의 성공적인 수신

및 디코딩의 가능성을 증가시킬 수도 있다. 몇몇 양태들에서, 제 1 주파수 대역(들) (1206) 은 제 2 주파수 대역(들) (1208) 과 동일할 수도 있으며, 이는 PUCCH 를 위해 사용된 주파수 대역이 불량한 성능을 겪는 때에 성공적인 수신 및 디코딩의 가능성을 증가시킬 수도 있다. 몇몇 양태들에서, UE 는 도 11a 및 도 11b 와 관련하여 전술한 바와 같이, 다중 주파수 대역들을 결정하는 것과 유사한 방식으로 제 1 주파수 대역(들) (1206) 및 제 2 주파수 대역(들) (1208) 을 결정할 수도 있다.

[0112] 몇몇 양태들에서, 제 1 주파수 대역(들) (1206) 및 제 2 주파수 대역(들) (1208) 은 모두 UL 제어 구성 표시 (1202) 에서 시그널링될 수도 있다. 몇몇 양태들에서, 제 1 주파수 대역(들) (1206) 및 제 2 주파수 대역(들) (1208) 중 하나는 UL 제어 구성 표시 (1202) 에서 시그널링될 수도 있고, 다른 하나는 시그널링된 주파수 대역(들)에 주파수 오프셋을 적용함으로써 결정될 수도 있다.

[0113] 몇몇 양태들에서, 제 1 주파수 대역(들) (1206) 및 제 2 주파수 대역(들) (1208) 은 모두 UL 제어 구성 표시 (1202) 에서 도출될 수도 있다. 이 경우, UE 는 제 1 주파수 대역(들) (1206) 을 결정하기 위해 제 1 함수를 특성에 적용할 수도 있고, 제 2 주파수 대역(들) (1208) 을 결정하기 위해 제 2 함수를 특성에 적용할 수도 있다. 추가적으로 또는 대안적으로, UE 는 제 1 주파수 대역(들) (1206) 및 제 2 주파수 대역(들) (1208) 중 하나를 결정하기 위해 함수를 적용할 수도 있고, 도출된 주파수 대역(들)에 주파수 오프셋을 적용함으로써 다른 하나를 결정할 수도 있다. 몇몇 양태들에서, 제 1 주파수 대역(들) (1206) 및 제 2 주파수 대역(들) (1208) 중 하나는 UL 제어 구성 표시 (1202) 에서 시그널링될 수도 있고, 다른 하나는 UL 제어 구성 표시 (1202) 의 특성으로부터 도출될 수도 있다.

[0114] 또한 나타낸 바와 같이, 몇몇 양태들에서, UE 는 상이한 시간 기간들 동안 상이한 주파수 대역들에서 PUCCH 를 구성할 수도 있다. 이 경우, UE 는 제 1 시간 기간에서 (예를 들어, UL 긴 버스트 부분 (804) 동안) 제 1 주파수 대역(들) (1206) 을 사용하여 제 1 UCI 를 송신할 수도 있고, 제 2 시간 기간에서 (예를 들어, UL 짧은 버스트 부분 (806) 동안) 제 2 주파수 대역(들) (1208) 을 사용하여 제 2 UCI 를 송신할 수도 있다. 몇몇 양태들에서, 시간 기간들은 나타낸 바와 같이 중첩되지 않을 수도 있다. 이런 식으로, UE 는 기지국에 의한 UCI 의 성공적인 수신 및 디코딩의 가능성을 증가시키기 위해 주파수 다이버시티를 사용할 수도 있다.

[0115] 도 12b 에 나타낸 바와 같이, 몇몇 양태들에서, UE 는 UL 긴 버스트 부분 (804) 에서 다중 제 1 주파수 대역들 (1206) 상에 PUCCH 를 구성할 수도 있고, 다중 제 1 주파수 대역들 (1206) 상에서 UCI 를 동시에 송신할 수도 있다. 몇몇 양태들에서, UE 는 UL 긴 버스트 부분 (804) 상에 구성된 PUCCH 상에서 제 1 UCI 를 송신할 수도 있고, UL 짧은 버스트 부분 (806) 상에 구성된 PUCCH 상에서 제 2 UCI (예컨대, 제 1 UCI 의 반복) 를 송신할 수도 있다.

[0116] 도면부호 1210 에 의해 나타낸 바와 같이, 몇몇 양태들에서, UE 는 도 11b 와 관련하여 전술한 바와 같이 UL 긴 버스트 부분 (804) (및/또는 UL 짧은 버스트 부분 (806), 도시 안 됨) 상에 PUSCH 를 구성할 수도 있다. 이런 식으로, UE 는 동시 송신을 사용하여 업링크 처리량을 증가시킬 수도 있다.

[0117] 전술한 바와 같이, 도 12a 및 도 12b 는 예시로서 제공된다. 다른 예들이 가능하며, 도 12a 및 도 12b 에 대하여 설명된 것과 상이할 수도 있다.

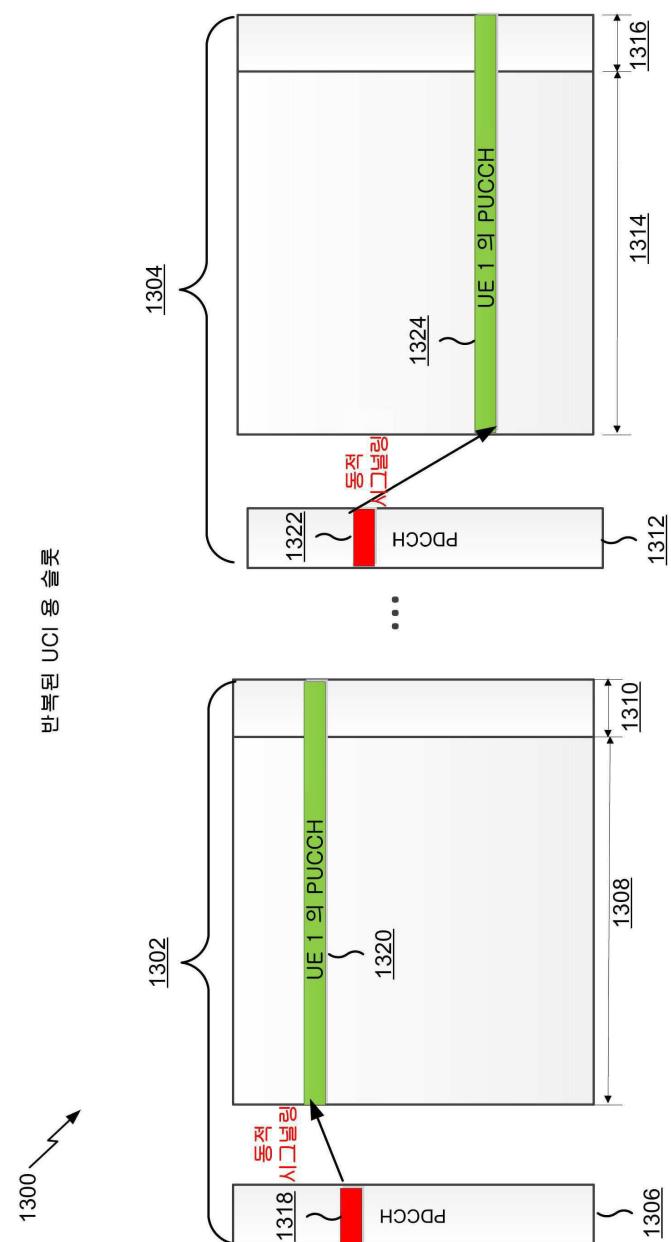

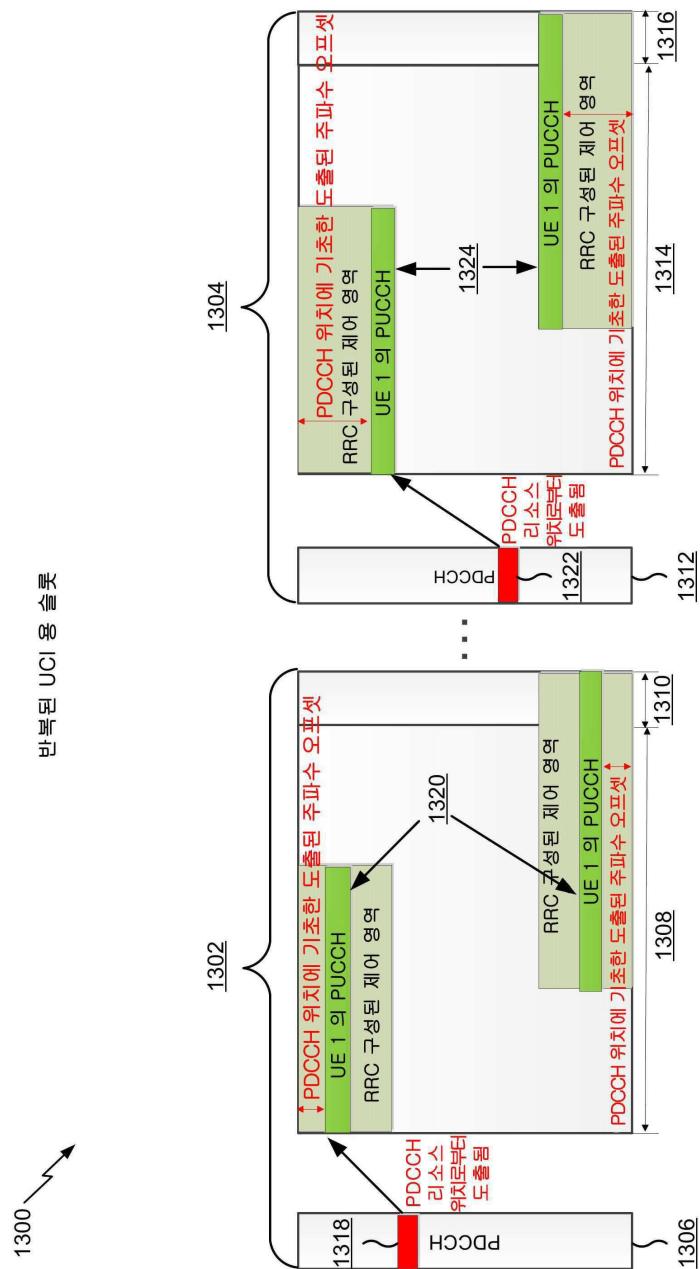

[0118] 도 13a 및 도 13b 는 뉴 라디오에서 대응 UCI 의 송신을 구성하는 예 (1300) 를 도시한 다이어그램이다. 도 13a 및 도 13b 는, 제 1 UCI 및 제 2 UCI 가 반복된 UCI 이고, 제 1 UL-중심 슬롯 (1302) 및 제 2 UL-중심 슬롯 (1304) 으로 나타낸 상이한 UL-중심 슬롯들에서 송신되는 예를 보여준다. 예를 들어, UE 는 (예를 들어, 제 1 UCI 의 비트들을 복사함으로써) 제 2 UCI 를 생성하기 위해 제 1 UCI 를 반복할 수도 있다. UL-중심 슬롯들은 도 8 과 관련하여 전술한 바와 같이, DL 제어 부분 (802), UL 긴 버스트 부분 (804) 및 UL 짧은 버스트 부분 (806) 을 각각 포함할 수도 있다. 예를 들어, 제 1 UL-중심 슬롯 (1302) 은 제 1 DL 제어 부분 (1306), 제 1 UL 긴 버스트 부분 (1308), 및 제 1 UL 짧은 버스트 부분 (1310) 을 포함할 수도 있으며, 제 2 UL-중심 슬롯 (1304) 은 제 2 DL 제어 부분 (1312), 제 2 UL 긴 버스트 부분 (1314), 및 제 2 UL 짧은 버스트 부분 (1316) 을 포함할 수도 있다. UL-중심 슬롯들은 UE (도 1 의 UE (120) 등) 와 기지국 (예를 들어, 도 1 의 기지국 (110) 등) 간의 통신을 위해 사용될 수도 있다.

[0119] 도 13a 에 도시된 바와 같이, UE 는 제 1 UL-중심 슬롯 (1302) 의 제 1 DL 제어 부분 (1306) 에서 제 1 UL 제어 구성 표시 (1318) 를 수신할 수도 있다. UE 는 제 1 UL 제어 구성 표시 (1318) 에 적어도 부분적으로 기초하여 제 1 UL-중심 슬롯 (1302) 의 하나 이상의 제 1 주파수 대역들 (1320) 상에 PUCCH 를 구성할 수도 있다. 예를 들어, UE 는 제 1 UL-중심 슬롯 (1302) 의 제 1 UL 긴 버스트 부분 (1308) 및/또는 제 1 UL 짧은 버스트 부분 (1310) 을 각각 포함할 수도 있다. 예를 들어, 제 1 UL-중심 슬롯 (1302) 은 제 1 DL 제어 부분 (1306), 제 1 UL 긴 버스트 부분 (1308), 및 제 1 UL 짧은 버스트 부분 (1310) 을 포함할 수도 있으며, 제 2 UL-중심 슬롯 (1304) 은 제 2 DL 제어 부분 (1312), 제 2 UL 긴 버스트 부분 (1314), 및 제 2 UL 짧은 버스트 부분 (1316) 을 포함할 수도 있다. UL-중심 슬롯들은 UE (도 1 의 UE (120) 등) 와 기지국 (예를 들어, 도 1 의 기지국 (110) 등) 간의 통신을 위해 사용될 수도 있다.

트 부분 (1310) 상에 제 1 주파수 대역(들) (1320) 을 구성할 수도 있다. 몇몇 양태들에서, UE 는 제 1 UL 긴 버스트 부분 (1308) 및/또는 제 1 UL 짧은 버스트 부분 (1310) 상에 구성된 PUCCH 상에서 제 1 UCI 를 송신 할 수도 있고, UL 짧은 버스트 부분 (1310) 상에 구성된 PUCCH 상에서 제 2 UCI 를 송신할 수도 있다.

[0120] 더 나타낸 바와 같이, UE 는 제 2 UL-중심 슬롯 (1304) 의 제 2 DL 제어 부분 (1312) 에서 제 2 UL 제어 구성 표시 (1322) 를 수신할 수도 있다. UE 는 제 2 UL 제어 구성 표시 (1322) 에 적어도 부분적으로 기초하여 제 2 UL-중심 슬롯 (1304) 의 하나 이상의 제 2 주파수 대역들 (1324) 상에 PUCCH 를 구성할 수도 있다. 예를 들어, UE 는 제 2 UL-중심 슬롯 (1304) 의 제 2 UL 긴 버스트 부분 (1314) 및/또는 제 2 UL 짧은 버스트 부분 (1316) 상에 제 2 주파수 대역(들) (1324) 을 구성할 수도 있다. 몇몇 양태들에서, UE 는 제 2 UL 긴 버스트 부분 (1314) 및/또는 제 2 UL 짧은 버스트 부분 (1316) 상에 구성된 PUCCH 상에서 제 2 UCI 를 송신할 수도 있다.

[0121] 몇몇 양태들에서, 제 1 주파수 대역(들) (1320) 은 제 2 주파수 대역(들) (1324) 과 상이할 수도 있으며, 이는 주파수 대역(들) 중 하나가 불량한 성능을 겪는 때에 주파수 다이버시티를 사용하여 UCI 의 성공적인 수신 및 디코딩의 가능성을 증가시킬 수도 있다. 몇몇 양태들에서, 제 1 주파수 대역(들) (1320) 은 제 2 주파수 대역(들) (1324) 과 동일할 수도 있으며, 이는 PUCCH 를 위해 사용된 주파수 대역이 불량한 성능을 겪는 때에 성공적인 수신 및 디코딩의 가능성을 증가시킬 수도 있다.

[0122] 일부 양태들에서, UE 는 제 1 UL 제어 구성 표시 (1318) 에 적어도 부분적으로 기초하여 제 1 주파수 대역(들) (1320) 을 결정할 수도 있다. 예를 들어, 제 1 주파수 대역(들) (1320) 은 본원에서 기술한 바와 같이 제 1 UL 제어 구성 표시 (1318) 에서 시그널링될 수도 있다. 추가적으로 또는 대안적으로, 제 1 주파수 대역(들) (1320) 은 본원에서 기술한 바와 같이 제 1 UL 제어 구성 표시 (1318) 의 특성에 적어도 부분적으로 기초하여 도출될 수도 있다.

[0123] 유사하게, UE 는 제 2 UL 제어 구성 표시 (1322) 에 적어도 부분적으로 기초하여 제 2 주파수 대역(들) (1324) 을 결정할 수도 있다. 예를 들어, 제 2 주파수 대역(들) (1324) 은 본원에서 기술한 바와 같이 제 2 UL 제어 구성 표시 (1322) 에서 시그널링될 수도 있다. 추가적으로 또는 대안적으로, 제 2 주파수 대역(들) (1324) 은 본원에서 기술한 바와 같이 제 2 UL 제어 구성 표시 (1322) 의 특성에 적어도 부분적으로 기초하여 도출될 수도 있다.

[0124] 제 1 UL 제어 구성 표시 (1318) 를 사용하여 제 1 주파수 대역(들) (1320) 을 결정하고 제 2 UL 제어 구성 표시 (1322) 를 사용하여 제 2 주파수 대역(들) (1324) 을 결정함으로써, UE 는 (예전대, 제 2 슬롯에서 제 2 UCI 를 송신하지 않음으로써) UCI 송신의 조기 종료를 허용한다. 예를 들어, UE 는 제 1 UL-중심 슬롯 (1302) 에서 제 1 UCI 를 송신할 수도 있고, 제 1 UCI 가 성공적으로 수신 및/또는 디코딩되었다는 표시 (예를 들어, 기지국 으로부터) 를 수신할 수도 있다. 예를 들어, UE 는 제 2 UL-중심 슬롯 (1304) 의 제 2 DL 제어 부분 (1312) 에서 표시를 수신할 수도 있다. 이 경우, UE 는 제 2 UL-중심 슬롯 (1304) 에서 제 2 UCI 를 송신하지 않을 수도 있으며, 이로써 네트워크 리소스들을 보존한다.

[0125] 몇몇 양태들에서, 제 1 UL-중심 슬롯 (1302) 및 제 2 UL-중심 슬롯 (1304) 은 인접한다. 이는 비인접 슬롯 들에서 반복된 UCI 를 송신하는 것에 비해 반복된 UCI 가 보다 짧은 시간 기간 동안 저장될 수 있기 때문에 UE 의 메모리 리세스들을 보존할 수도 있다. 몇몇 양태들에서, 제 1 UL-중심 슬롯 (1302) 및 제 2 UL-중심 슬롯 (1304) 은 비인접한다. 이는 비인접 슬롯들 사이에 더 많은 시간이 경과함에 따라 채널 조건이 향상될 수 있으므로 반복된 UCI 의 성공적인 수신의 가능성을 증가시킬 수도 있다.

[0126] 몇몇 양태들에서, 제 1 UL 제어 구성 표시 (1318) 는 반복된 UCI (예를 들어, 반복되는 제 1 UCI, 제 2 UCI 및/또는 다른 UCI) 가 인접 슬롯들 또는 비인접 슬롯들에서 반복되어야 하는지 여부를 표시할 수도 있고, UE 는 표시에 적어도 부분적으로 기초하여 반복된 UCI 의 송신을 위해 하나 이상의 슬롯들을 구성할 수도 있다. 추가적으로 또는 대안적으로, 제 1 UL 제어 구성 표시 (1318) 는 반복된 UCI (예를 들어, 모든 다른 슬롯의 패턴, 하나의 비인접 슬롯이 뒤따르는 반복된 UCI 에 대한 2 개의 인접 슬롯들의 패턴 등) 의 송신을 위한 슬롯 패턴을 표시할 수도 있다.

[0127] 추가적으로 또는 대안적으로, 제 1 UL 제어 구성 표시 (1318) 는 UCI 가 반복되어야 하는 슬롯의 수를 표시할 수도 있다. 본원에 기술된 예들은 UCI 가 2 개의 슬롯들 (예를 들어, 제 1 UCI 및 제 2 UCI 를 사용하는) 에 걸쳐 반복되는 것을 보여주지만, 몇몇 양태들에서, UCI 는 3 개의 슬롯들 (예를 들어, 제 1 UCI, 제 2 UCI 및 제 3 UCI 를 사용하는), 4 개의 슬롯들 (예를 들어, 제 1 UCI, 제 2 UCI, 제 3 UCI 및 제 4 UCI 를

사용하는) 또는 더 많은 슬롯들에 걸쳐 반복될 수도 있다.

[0128] 도 13b 에 도시된 바와 같이, 제 1 UL-중심 슬롯 (1302) 에서의 하나 이상의 제 1 주파수 대역들 (1320) 은 다중 주파수 대역들을 포함할 수도 있고, 이는 본원에서 설명되는 바와 같이 결정될 수도 있다. 유사하게, 제 2 UL-중심 슬롯 (1304) 에서의 하나 이상의 제 1 주파수 대역들 (1324) 은 다중 주파수 대역들을 포함할 수도 있고, 이는 본원에서 설명되는 바와 같이 결정될 수도 있다. 다중 슬롯들 각각에서의 다중 주파수 대역들을 사용함으로써, UE 는 (예를 들어, 도 13a 에 도시된 바와 같이, 다중 슬롯들 각각에서 단일 주파수 대역을 사용하는 것에 비해) UCI 의 성공적인 수신 및 디코딩의 가능성을 더 증가시킨다. 그러나, 다중 슬롯들 각각에서 단일 주파수 대역을 사용하는 것은 복잡성을 감소시키고 UE 리소스를 보존할 수도 있다.

[0129] 전술한 바와 같이, 도 13a 및 도 13b 는 예시로서 제공된다. 다른 예들이 가능하며, 도 13a 및 도 13b 에 대하여 설명된 것과 상이할 수도 있다.

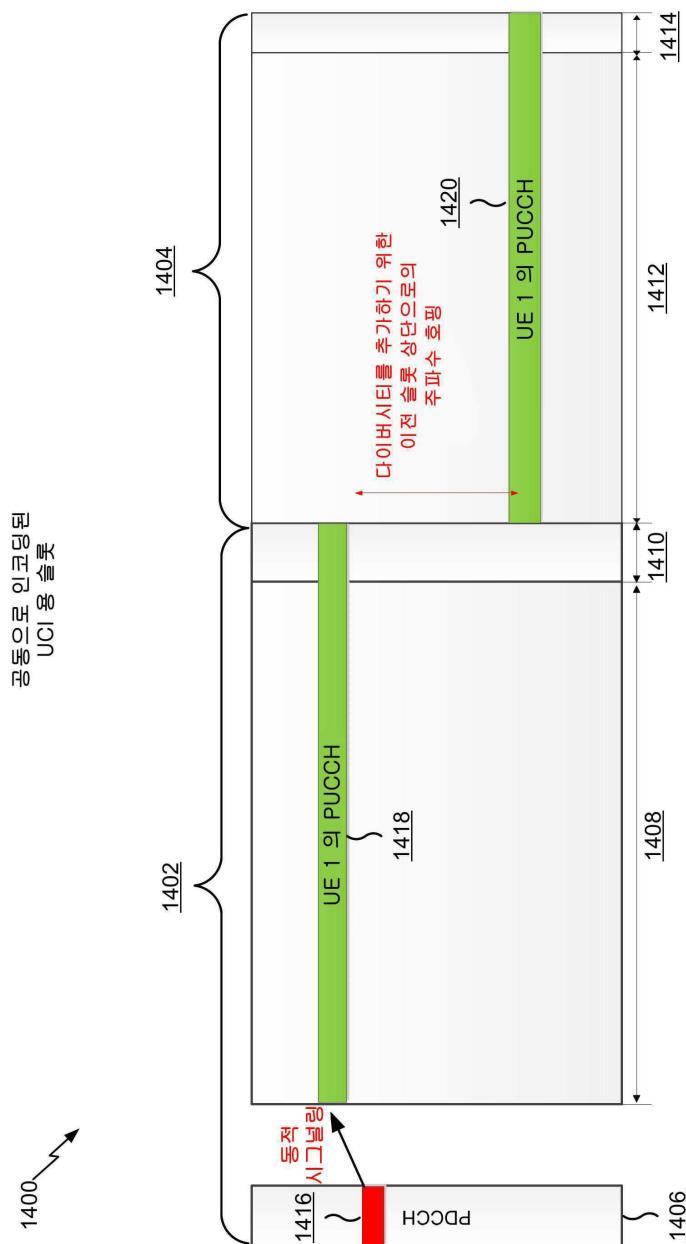

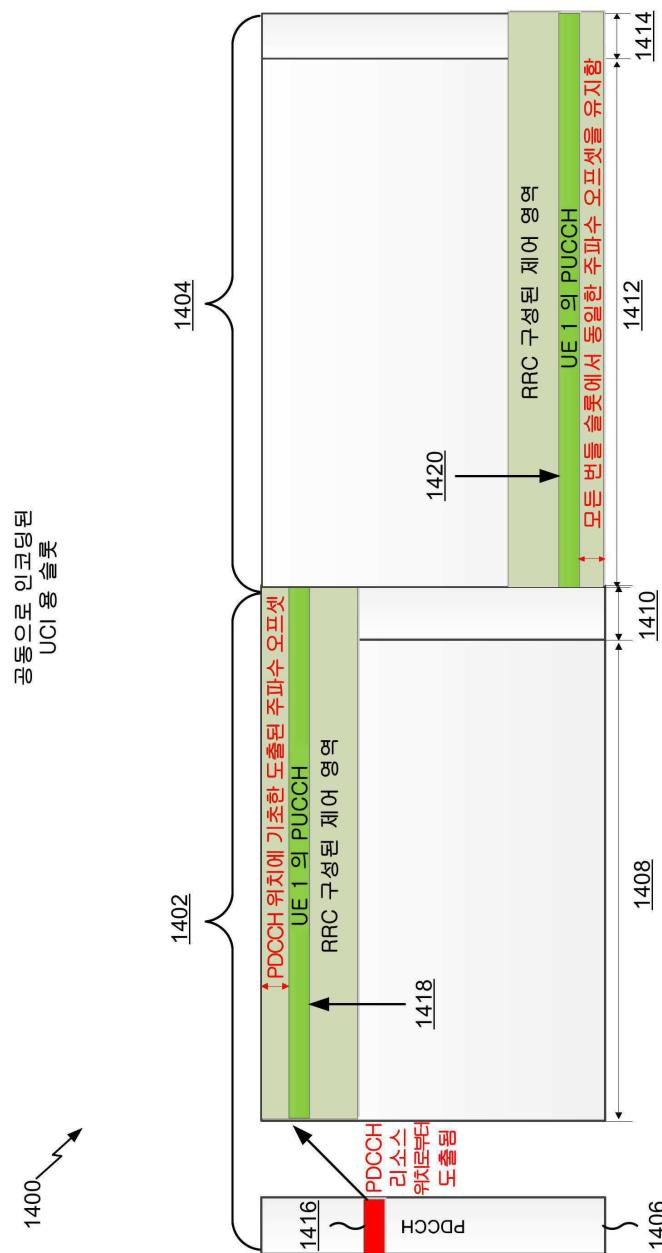

[0130] 도 14a 및 도 14b 는 뉴 라디오에서 대응 UCI 의 송신을 구성하는 예 (1400) 를 도시한 다이어그램이다. 도 14a 및 도 14b 는, 제 1 UCI 및 제 2 UCI 가 공동으로 인코딩된 UCI 로서 공동으로 인코딩되고, 공동으로 인코딩된 UCI 가 제 1 슬롯 (1402) 및 제 2 슬롯 (1404) 으로서 나타낸 상이한 슬롯들에서 송신되는 예를 보여준다. 예 (1400) 에서, 제 1 슬롯 (1402) 은 UL-중심 슬롯이고, 제 2 슬롯 (1404) 은 풀-UL 슬롯이다. 그러나, 제 1 UL-중심 슬롯 및 제 2 UL-중심 슬롯과 같은 다른 타입의 슬롯 조합이 사용될 수도 있다.

[0131] 몇몇 양태들에서, 도 8 과 관련하여 전술한 바와 같이, 제 1 슬롯 (1402) 은 DL 제어 부분 (802), UL 긴 버스트 부분 (804), 및 UL 짧은 버스트 부분 (806) 을 포함할 수도 있고, 제 2 슬롯 (1404) 은 UL 긴 버스트 부분 (804) 및 UL 짧은 버스트 부분 (806) 을 포함할 수도 있다. 예를 들어, 제 1 슬롯 (1402) 은 DL 제어 부분 (1406), 제 1 UL 긴 버스트 부분 (1408), 및 제 1 UL 짧은 버스트 부분 (1410) 을 포함할 수도 있으며, 제 2 슬롯 (1404) 은 제 2 UL 긴 버스트 부분 (1412) 및 제 2 UL 짧은 버스트 부분 (1414) 을 포함할 수도 있다. 슬롯들은 UE (도 1의 UE (120) 등) 와 기지국 (예컨대, 도 1 의 기지국 (110) 등) 사이의 통신을 위해 사용될 수도 있다.

[0132] 도 14a 에 도시된 바와 같이, UE 는 제 1 슬롯 (1402) 의 제 1 DL 제어 부분 (1406) 에서 UL 제어 구성 표시 (1416) 를 수신할 수도 있다. UE 는 UL 제어 구성 표시 (1416) 에 적어도 부분적으로 기초하여 제 1 슬롯 (1402) 의 하나 이상의 제 1 주파수 대역들 (1418) 및 제 2 슬롯 (1404) 의 하나 이상의 제 2 주파수 대역들 (1420) 상에 PUCCH 를 구성할 수도 있다. 예를 들어, UE 는 제 1 슬롯 (1402) 의 제 1 UL 긴 버스트 부분 (1408) 및/또는 제 1 UL 짧은 버스트 부분 (1410) 상에 제 1 주파수 대역(들) (1418) 을 구성할 수도 있고, 제 2 슬롯 (1404) 의 제 2 UL 긴 버스트 부분 (1412) 및/또는 제 2 UL 짧은 버스트 부분 (1414) 상에 제 2 주파수 대역(들) (1420) 을 구성할 수도 있다. 몇몇 양태들에서, UE 는 제 1 주파수 대역(들) (1418) 및 제 2 주파수 대역(들) (1420) 상에 구성된 PUCCH 상에서 공동으로 인코딩된 UCI 를 송신할 수도 있다.

[0133] 몇몇 양태들에서, 제 1 주파수 대역(들) (1418) 은 본원에서 설명되는 바와 같이 제 2 주파수 대역(들) (1420) 과 상이할 수도 있다. 몇몇 양태들에서, 제 1 주파수 대역(들) (1418) 은 본원에서 설명되는 바와 같이 제 2 주파수 대역(들) (1420) 과 동일할 수도 있다.

[0134] 몇몇 양태들에서, UE 는 본원에서 설명되는 바와 같이 UL 제어 구성 표시 (1416) 에 적어도 부분적으로 기초하여 제 1 주파수 대역(들) (1418) 및 제 2 주파수 대역(들) (1420) 을 결정할 수도 있다. 예를 들어, 제 1 주파수 대역(들) (1418) 및/또는 제 2 주파수 대역(들) (1420) 은 본원에서 설명되는 바와 같이 UL 제어 구성 표시 (1416) 에서 시그널링될 수도 있다. 추가적으로 또는 대안적으로, 제 1 주파수 대역(들) (1418) 및/또는 제 2 주파수 대역(들) (1420) 은 본원에서 기술한 바와 같이 UL 제어 구성 표시 (1416) 의 특성에 적어도 부분적으로 기초하여 도출될 수도 있다. 예를 들어, 그리고 도 14a 에 도시된 바와 같이, 제 1 주파수 대역(들) (1418) 은 UL 제어 구성 표시 (1416) 에서 시그널링될 수도 있고, UE 는 제 2 주파수 대역(들) (1420) (예컨대, 이들은 제 1 주파수 대역(들) (1418) 로부터 오프셋됨) 을 결정하기 위해 제 1 주파수 대역(들) (1418) 에 주파수 호핑을 적용할 수도 있다.

[0135] UL 제어 구성 표시 (1416) 를 사용하여 제 1 주파수 대역(들) (1418) 및 제 2 주파수 대역(들) (1420) 쌍방이 결정되는 때, 제 2 슬롯 (1404) 은 DL 제어 부분 (802) 을 포함하지 않도록 구성될 수도 있고, 이로써 업링크 송신을 위한 길이를 연장시키고 (예컨대, 제 2 슬롯 (1404) 을 채우도록 UL 긴 버스트 부분 (1412) 및/또는 UL 짧은 버스트 부분 (1414) 의 길이를 연장시키고) 업링크 처리량을 증가시킨다. 몇몇 양태들에서, 제 1 슬롯 (1402) 및 제 2 슬롯 (1404) 은 공동으로 인코딩된 UCI 가 단일 DL 제어 부분 (1406) (예컨대, 단일 UL 제어

구성 표시 (1416)) 을 사용하여 인접 슬롯들에서 송신될 수 있도록 인접한다. 몇몇 양태들에서, UL 제어 구성 표시 (1416) 는 공동으로 인코딩된 UCI 가 인접 슬롯들에서 송신되어야 한다는 것을 표시할 수도 있고, UE 는 표시에 적어도 부분적으로 기초하여 공동으로 인코딩된 UCI 의 송신을 위해 하나 이상의 슬롯들을 구성할 수도 있다. 추가적으로 또는 대안적으로, UL 제어 구성 표시 (1416) 는 본원에서 설명되는 바와 같이 공동으로 인코딩된 UCI 의 송신을 위한 슬롯 패턴을 표시할 수도 있다.

[0136] 추가적으로 또는 대안적으로, UL 제어 구성 표시 (1416) 는 제 1 슬롯 (1402) 및/또는 제 2 슬롯 (1404) 을 위한 구성을 표시할 수도 있다. 예를 들어, UL 제어 구성 표시 (1416) 는, 제 2 슬롯 (1404) 이 DL 제어 부분 (802) 을 배제해야 한다는 것, UL 긴 버스트 부분 (1412) 및/또는 UL 짧은 버스트 부분 (1414) 이 제 2 슬롯 (1404) 에서 연장되어야 한다는 것 등을 표시할 수도 있다. 추가적으로 또는 대안적으로, UL 제어 구성 표시 (1416) 는 UCI 가 공동으로 인코딩되어야 하는 슬롯의 수를 표시할 수도 있다. 본원에 설명된 예들은 UCI 가 2 개의 슬롯들에 걸쳐 공동으로 인코딩되는 것으로 보여주지만, 몇몇 양태들에서, UCI 는 3 개의 슬롯들, 4 개의 슬롯들, 또는 더 많은 슬롯들에 걸쳐 공동으로 인코딩될 수도 있다.

[0137] 도 14b 에 도시된 바와 같이, 몇몇 양태들에서, UE 는 UL 제어 구성 표시 (1416) (예를 들어, 주파수 오프셋이 시그널링되거나 도출될 수 있음) 에 적어도 부분적으로 기초하여 주파수 오프셋을 결정할 수도 있고, 제 1 주파수 대역(들) (1418) 및 제 2 주파수 대역(들) (1420) 을 결정하기 위해 주파수 오프셋을 사용할 수도 있다. 몇몇 양태들에서, UE 는 제 1 주파수 대역(들) (1418) 및 제 2 주파수 대역(들) (1420) 쌍방을 결정하기 위해 동일한 주파수 오프셋을 사용할 수도 있고, 이러써 그렇지 않으면 다중 주파수 오프셋들을 계산하기 위해 소비될 UE 리소스들을 보존한다.

[0138] 도 14a 및 도 14b 는 제 1 슬롯 (1402) 및 제 2 슬롯 (1404) 이 인접한 것으로 도시하지만, 몇몇 양태들에서, 제 1 슬롯 (1402) 및 제 2 슬롯 (1404) 은 비인접할 수도 있다. 몇몇 양태들에서, UL 제어 구성 표시 (1416) (예컨대, 제 1 슬롯 1402) 에서는 인접 슬롯들 또는 비인접 슬롯들에서 대응 UCI 를 송신하는지 여부를 표시할 수도 있고, UE 는 표시에 적어도 부분적으로 기초하여 대응 UCI 의 송신을 위해 하나 이상의 슬롯들을 구성할 수도 있다. 추가적으로 또는 대안적으로, UL 제어 구성 표시 (1416) 는 대응 UCI 의 송신을 위해 사용되는 슬롯의 수를 표시할 수도 있고, 대응 UCI 의 송신을 위한 슬롯 패턴 등을 표시할 수도 있다.

[0139] 전술한 바와 같이, 도 14a 및 도 14b 는 예시로서 제공된다. 다른 예들이 가능하며, 도 14a 및 도 14b 에 대하여 설명된 것과 상이할 수도 있다.

[0140] 도 15a 및 도 15b 는 뉴 라디오에서 대응 UCI 의 송신을 구성하는 예 (1500) 를 도시한 다이어그램이다. 도 15a 및 도 15b 는, 대응 UCI (예컨대, 제 1 UCI 및 제 2 UCI) 가 제 1 DL-중심 슬롯 (1502) 및 제 2 DL-중심 슬롯 (1504) 로서 나타낸 상이한 DL-중심 슬롯들에서 송신되는 예를 보여준다. DL-중심 슬롯들은 도 7 과 관련하여 전술한 바와 같이, DL 제어 부분 (702), UL 데이터 부분 (704), 및 UL 짧은 버스트 부분 (706) 을 각각 포함할 수도 있다. 예를 들어, 제 1 DL-중심 슬롯 (1502) 은 제 1 DL 제어 부분 (1506), 제 1 DL 데이터 부분 (1508), 및 제 1 UL 짧은 버스트 부분 (1510) 을 포함할 수도 있고, 제 2 DL-중심 슬롯 (1504) 은 제 2 DL 제어 부분 (1512), 제 2 DL 데이터 부분 (1514), 및 제 2 UL 짧은 버스트 부분 (1516) 을 포함할 수도 있다. DL-중심 슬롯들은 UE (도 1 의 UE (120) 등) 와 기지국 (예를 들어, 도 1 의 기지국 (110) 등) 간의 통신을 위해 사용될 수도 있다.

[0141] 도 15a 는 제 1 UCI 및 제 2 UCI 가 반복된 UCI 이고, 상이한 DL-중심 슬롯들에서 송신되는 일례를 보여준다. 도 15a 에 도시된 바와 같이, UE 는 제 1 DL-중심 슬롯 (1502) 의 제 1 DL 제어 부분 (1506) 에서 제 1 UL 제어 구성 표시 (1518) 를 수신할 수도 있다. UE 는 제 1 UL 제어 구성 표시 (1518) 에 적어도 부분적으로 기초하여 제 1 UL-중심 슬롯 (1502) 의 하나 이상의 제 1 주파수 대역들 (1520) 상에 PUCCH 를 구성할 수도 있다. 예를 들어, UE 는 제 1 DL-중심 슬롯 (1502) 의 제 1 UL 짧은 버스트 부분 (1510) 상에 제 1 주파수 대역(들) (1520) 을 구성할 수도 있다. 몇몇 양태들에서, UE 는 제 1 UL 짧은 버스트 부분 (1510) 상에 구성된 PUCCH 상에서 제 1 UCI 를 송신할 수도 있다.

[0142] 더 나타낸 바와 같이, UE 는 제 2 DL-중심 슬롯 (1504) 의 제 2 DL 제어 부분 (1512) 에서 제 2 UL 제어 구성 표시 (1522) 를 수신할 수도 있다. UE 는 제 2 UL 제어 구성 표시 (1522) 에 적어도 부분적으로 기초하여 제 2 DL-중심 슬롯 (1504) 의 하나 이상의 제 2 주파수 대역들 (1524) 상에 PUCCH 를 구성할 수도 있다. 예를 들어, UE 는 제 2 DL-중심 슬롯 (1504) 의 제 2 UL 짧은 버스트 부분 (1516) 상에 제 2 주파수 대역(들) (1524) 을 구성할 수도 있다. 몇몇 양태들에서, UE 는 제 2 UL 짧은 버스트 부분 (1516) 상에 구성된 PUCCH 상에서 제 2 UCI 를 송신할 수도 있다.

- [0143] 몇몇 양태들에서, 제 1 주파수 대역(들) (1520) 은 본원에서 설명되는 바와 같이 제 2 주파수 대역(들) (1524) 과 상이할 수도 있다. 몇몇 양태들에서, 제 1 주파수 대역(들) (1520) 은 본원에서 설명되는 바와 같이 제 2 주파수 대역(들) (1524) 과 동일할 수도 있다.

- [0144] 몇몇 양태들에서, UE 는 제 1 UL 제어 구성 표시 (1518) 에 적어도 부분적으로 기초하여 제 1 주파수 대역(들) (1520) 을 결정할 수도 있다. 예를 들어, 제 1 주파수 대역(들) (1520) 은 본원에서 기술한 바와 같이 시그널링 또는 도출될 수도 있다. 유사하게, UE 는 제 2 UL 제어 구성 표시 (1522) 에 적어도 부분적으로 기초하여 제 2 주파수 대역(들) (1524) 을 결정할 수도 있다. 예를 들어, 제 2 주파수 대역(들) (1524) 은 본원에서 기술한 바와 같이 시그널링 또는 도출될 수도 있다. 제 1 DL-중심 슬롯 (1502) 및 제 2 DL-중심 슬롯 (1504) 은 본원에서 설명되는 바와 같이 인접하거나 비인접할 수도 있다. 추가적으로 또는 대안적으로, 제 1 UL 제어 구성 표시 (1518) 및/또는 제 2 UL 제어 구성 표시 (1522) 는 본원에서 설명되는 하나 이상의 표시를 포함할 수도 있다.

- [0145] 도 15b 는, 제 1 UCI 및 제 2 UCI 가 공동으로 인코딩된 UCI 로서 공동으로 인코딩된 UCI 가 상이한 DL-중심 슬롯들 (예컨대, 제 1 DL-중심 슬롯 (1502) 및 제 2 DL-중심 슬롯 (1504)) 에서 송신되는 예를 보여준다. 몇몇 양태들에서, UCI 가 공동으로 인코딩되어야 하는 때, UE 는 제 1 DL-중심 슬롯 (1502) 의 제 1 DL 제어 부분 (1506) 에서 제 1 UL 제어 구성 표시 (1518) 을 수신할 수도 있고, 제 2 DL-중심 슬롯 (1504) 에서 제 2 UL 제어 구성 표시 (1522) 를 수신하지 않을 수도 있다. 이 경우, UE 는 제 1 UL 제어 구성 표시 (1518) 에 적어도 부분적으로 기초하여 제 1 DL-중심 슬롯 (1502) 의 하나 이상의 제 1 주파수 대역들 (1520) 및 제 2 DL-중심 슬롯 (1504) 의 하나 이상의 제 2 주파수 대역들 (1524) 상에 PUCCH 를 구성할 수도 있다. 예를 들어, UE 는 제 1 DL-중심 슬롯 (1502) 의 제 1 UL 짧은 베스트 부분 (1510) 상에 제 1 주파수 대역(들) (1520) 을 구성할 수도 있고, 제 2 DL-중심 슬롯 (1504) 의 제 2 UL 짧은 베스트 부분 (1516) 상에 제 2 주파수 대역(들) (1524) 을 구성할 수도 있다. 몇몇 양태들에서, UE 는 제 1 UL 짧은 베스트 부분 (1510) 및 제 2 UL 짧은 베스트 부분 (1516) 상에 구성된 PUCCH 상에서 공동으로 인코딩된 UCI 를 송신할 수도 있다. UE 는 본원에서 설명되는 바와 같이 제 1 주파수 대역(들) (1520) 및/또는 제 2 주파수 대역(들) (1524) 을 결정할 수도 있다.

- [0146] 이런 식으로, UE 는 제 1 주파수 대역(들) (1520) 및 제 2 주파수 대역(들) (1524) 쌍방을 결정하기 위해 하나의 UL 제어 구성 표시를 사용함으로써 다운링크 리소스들을 보존할 수도 있다. 또한, UE 는 공동 인코딩을 사용함으로써 코딩 이득 (coding gain) 을 획득할 수도 있다.

- [0147] 도 15a 및 도 15b 는 제 1 DL-중심 슬롯 (1502) 및 제 2 DL-중심 슬롯 (1504) 이 인접한 것으로 도시하지만, 몇몇 양태들에서, 제 1 DL-중심 슬롯 (1502) 및 제 2 DL-중심 슬롯 (1504) 은 비인접할 수도 있다. 몇몇 양태들에서, 제 1 UL 제어 구성 표시 (1518) 는 인접 슬롯들 또는 비인접 슬롯들에서 대응 UCI 를 송신하는지 여부를 표시할 수도 있고, UE 는 표시에 적어도 부분적으로 기초하여 대응 UCI 의 송신을 위해 하나 이상의 슬롯들을 구성할 수도 있다. 추가적으로 또는 대안적으로, 제 1 UL 제어 구성 표시 (1518) 는 대응 UCI 의 송신을 위해 사용되는 슬롯의 수를 표시할 수도 있고, 대응 UCI 의 송신을 위한 슬롯 패턴 등을 표시할 수도 있다.

- [0148] 전술한 바와 같이, 도 15a 및 도 15b 는 예시로서 제공된다. 다른 예들이 가능하며, 도 15a 및 도 15b 에 대하여 설명된 것과 상이할 수도 있다.

- [0149] 도 16a 및 도 16b 는 뉴 라디오에서 대응 UCI 의 송신을 구성하는 예 (1600) 를 도시한 다이어그램이다. 도 16a 및 도 16b 는, 대응 UCI (예를 들어, 제 1 UCI 및 제 2 UCI) 가 DL 슬롯들 (예를 들어, DL-중심 슬롯들 또는 풀-DL 슬롯들) 및 UL 슬롯들 (예를 들어, UL-중심 슬롯들 또는 풀-UL 슬롯들) 의 조합에서 송신되는 예를 보여준다. 예를 들어, 도 16a 및 도 16b 는 DL-중심 슬롯으로서 제 1 슬롯 (1602) 을, 그리고 풀-UL 슬롯으로서 제 2 슬롯 (1604) 을 보여준다. 몇몇 양태들에서, 슬롯들의 다른 타입들 및 순서들이 사용될 수도 있다. 그러나, 풀-UL 슬롯이 뒤따르는 DL-중심 슬롯을 사용함으로써, UE 는 제 2 슬롯 (1604) 으로부터 가드 인터벌 및 DL 제어 부분을 제거하여 업링크 처리량을 증가시킬 수도 있다.

- [0150] 도시된 바와 같이, 제 1 슬롯 (1602) 은 DL 제어 부분 (1606), DL 데이터 부분 (1608) 및 제 1 UL 짧은 베스트 부분 (1610) 을 포함하는 DL-중심 슬롯일 수도 있으며, 이는 도 7 과 관련하여 전술한 바와 같이 부분들 (702, 704, 706) 에 각각 대응할 수도 있다. 또한 도시된 바와 같이, 제 2 슬롯 (1604) 은 UL 긴 베스트 부분 (1612) 및 제 2 UL 짧은 베스트 부분 (1614) 을 포함하는 풀-UL 슬롯일 수도 있으며, 이는 도 10 과 관련하여 전술한 바와 같이 부분들 (1004, 1006) 에 각각 대응할 수도 있다. 슬롯들은 UE (도 1의 UE (120) 등) 와

기지국 (예컨대, 도 1 의 기지국 (110) 등) 사이의 통신을 위해 사용될 수도 있다.

[0151] 도 16a 는 제 1 UCI 및 제 2 UCI 가 반복된 UCI 이고, 상이한 혼합된 슬롯들 (예컨대 혼합된 DL 및 UL 슬롯들)에서 송신되는 일례를 보여준다. 도 16a 에 도시된 바와 같이, UE 는 제 1 슬롯 (1602) 의 DL 제어 부분 (1606) 에서 UL 제어 구성 표시 (1616) 를 수신할 수도 있다. UE 는 UL 제어 구성 표시 (1616) 에 적어도 부분적으로 기초하여 제 1 슬롯 (1602) 의 하나 이상의 제 1 주파수 대역들 (1618) 및 제 2 슬롯 (1604) 의 하나 이상의 제 2 주파수 대역들 (1620) 상에 PUCCH 를 구성할 수도 있다. 예를 들어, UE 는 제 1 슬롯 (1602) 의 제 1 UL 짧은 버스트 부분 (1610) 상에 제 1 주파수 대역(들) (1618) 을 구성할 수도 있고, 제 2 슬롯 (1604) 의 UL 긴 버스트 부분 (1612) 및/또는 제 2 UL 짧은 버스트 부분 (1614) 상에 제 2 주파수 대역(들) (1620) 을 구성할 수도 있다. 몇몇 양태들에서, UE 는 제 1 주파수 대역(들) (1618) 상에 구성된 PUCCH 상에서 제 1 UCI 를 송신할 수도 있고, 제 2 주파수 대역(들) (1620) 상에 구성된 PUCCH 상에서 제 2 UCI 를 송신할 수도 있다.

[0152] 몇몇 양태들에서, 제 1 주파수 대역(들) (1618) 은 본원에서 설명되는 바와 같이 제 2 주파수 대역(들) (1620) 과 상이할 수도 있다. 몇몇 양태들에서, 제 1 주파수 대역(들) (1618) 은 본원에서 설명되는 바와 같이 제 2 주파수 대역(들) (1620) 과 동일할 수도 있다.

[0153] 몇몇 양태들에서, UE 는 UL 제어 구성 표시 (1616) 에 적어도 부분적으로 기초하여 제 1 주파수 대역(들) (1618) 및/또는 제 2 주파수 대역(들) (1620) 을 결정할 수도 있다. 예를 들어, 제 1 주파수 대역(들) (1618) 및/또는 제 2 주파수 대역(들) (1620) 은 본원에서 설명되는 바와 같이 시그널링 또는 도출될 수도 있다. 예를 들어, 그리고 도 16a 에 도시된 바와 같이, 제 1 주파수 대역(들) (1618) 은 UL 제어 구성 표시 (1616) 에서 시그널링되거나 이로부터 도출될 수도 있고, UE 는 제 2 주파수 대역(들) (1620) 을 결정하기 위해 제 1 주파수 대역(들) (1618) 에 주파수 호핑을 적용할 수도 있다.

[0154] UL 제어 구성 표시 (1616) 를 사용하여 제 1 주파수 대역(들) (1618) 및 제 2 주파수 대역(들) (1620) 쌍방이 결정되는 때, 제 2 슬롯 (1604) 은 DL 제어 부분을 포함하지 않도록 구성될 수도 있고, 이로써 업링크 송신을 위한 길이를 연장시키고 (예컨대, 제 2 슬롯 (1604) 을 채우도록 UL 긴 버스트 부분 (1612) 및/또는 UL 짧은 버스트 부분 (1614) 의 길이를 연장시키고) 업링크 처리량을 증가시킨다. 몇몇 양태들에서, 제 1 슬롯 (1602) 및 제 2 슬롯 (1604) 은 제 1 UCI 및 제 2 UCI 가 단일 DL 제어 부분 (1606) (예컨대, 단일 UL 제어 구성 표시 (1616)) 을 사용하여 인접 슬롯들에서 송신될 수 있도록 인접하도록 구성된다. 몇몇 양태들에서, UL 제어 구성 표시 (1616) 는 반복된 UCI 가 인접 슬롯들에서 송신되어야 한다는 것을 표시할 수도 있고, UE 는 표시에 적어도 부분적으로 기초하여 반복된 UCI 의 송신을 위해 하나 이상의 슬롯들을 구성할 수도 있다. 추가적으로 또는 대안적으로, UL 제어 구성 표시 (1616) 는 본원에서 설명되는 하나 이상의 다른 표시들을 포함할 수도 있다.

[0155] 도 16b 는, 제 1 UCI 및 제 2 UCI 가 공동으로 인코딩된 UCI 로서 공동으로 인코딩되고, 공동으로 인코딩된 UCI 가 상이한 혼합된 슬롯들 (예컨대, 혼합된 DL 및 UL 슬롯들) 에서 송신되는 예를 보여준다. 이 경우, 제 1 주파수 대역(들) (1618) 및 제 2 주파수 대역(들) (1620) 은 전술한 것과 유사한 방식으로 결정될 수도 있다.

몇몇 양태들에서, 제 1 주파수 대역(들) (1618) 은 제 1 주파수 (1622) 를 포함할 수도 있고, 제 2 주파수 대역(들) (1620) (예컨대, UL 슬롯 상에) 은 제 2 주파수 (1624) 및 제 3 주파수 (1626) 로서 나타낸, 주파수 다이버시티를 위해 다중 주파수 대역들을 포함할 수도 있다.

[0156] 몇몇 양태들에서, 제 2 슬롯 (1604) 의 시작에서의 주파수는 제 1 슬롯 (1602) 의 끝에서의 주파수와 동일한 주파수일 수도 있다. 예를 들어, 제 1 주파수 (1622) 는 제 2 주파수 (1624) 와 동일한 주파수로서 도시된다.

이런 식으로, 동일한 주파수가 공동으로 인코딩된 UCI 의 송신을 위해 제 1 슬롯 (1602) 의 끝 경계 및 제 2 슬롯 (1604) 의 시작 경계를 가로질러 연장될 수도 있고, 이로써 복잡성을 줄이고 UE 리소스들을 보존한다.

이 경우, 제 1 슬롯 (1602) 및 제 2 슬롯 (1604) 은 몇몇 양태들에서 인접할 수도 있다.

[0157] 제 1 슬롯 (1602) 및 제 2 슬롯 (1604) 은 DL-중심 슬롯 및 풀-UL 슬롯으로 각각 도시되지만, 몇몇 양태들에서, 슬롯들의 다른 타입들 및 순서들이 사용될 수도 있다. 예를 들어, 제 1 슬롯 (1602) 또는 제 2 슬롯 (1604) 중 하나는 DL 데이터 부분 및 제 1 UL 짧은 버스트 부분을 포함할 수도 있고, 제 1 슬롯 (1602) 또는 제 2 슬롯 (1604) 중 다른 하나는 UL 긴 버스트 부분 및 제 2 UL 짧은 버스트 부분을 포함할 수도 있다. UCI 가 공동으로 인코딩되는 때, UE 는 제 1 UL 짧은 버스트 부분 그리고 UL 긴 버스트 부분 또는 제 2 UL 짧은 버스트 부분 중 적어도 하나에서 공동으로 인코딩된 UCI 를 송신할 수도 있다. UCI 가 반복되는 때, UE 는 제 1 UL 짧은 버스트 부분에서 제 1 UCI 또는 제 2 UCI 중 하나를 송신할 수도 있고, UL 긴 버스트 부분 또는 제 2 UL

짧은 버스트 부분의 적어도 하나에서 제 1 UCI 또는 제 2 UCI 중 다른 하나를 송신할 수도 있다.

[0158] 또한, 도 16a 및 도 16b 는 제 1 슬롯 (1602) 및 제 2 슬롯 (1604) 이 인접한 것으로 도시하지만, 몇몇 양태들에서, 제 1 슬롯 (1602) 및 제 2 슬롯 (1604) 은 비인접할 수도 있다. 몇몇 양태들에서, UL 제어 구성 표시 (1616) (예컨대, 제 1 슬롯 1602 에서) 는 인접 슬롯들 또는 비인접 슬롯들에서 대응 UCI 를 송신하는지 여부를 표시할 수도 있고, UE 는 표시에 적어도 부분적으로 기초하여 대응 UCI 의 송신을 위해 하나 이상의 슬롯들을 구성할 수도 있다. 추가적으로 또는 대안적으로, UL 제어 구성 표시 (1616) 는 대응 UCI 의 송신을 위해 사용되는 슬롯의 수를 표시할 수도 있고, 대응 UCI 의 송신을 위한 슬롯 패턴 등을 표시할 수도 있다.

[0159] 몇몇 양태들에서, UE 는 제 1 UCI 및 제 2 UCI 를 포함하는 UCI 의 페이로드의 크기에 적어도 부분적으로 기초하여 UCT 를 반복할지 또는 UCI 를 공동으로 인코딩할지 여부를 결정할 수도 있다. 추가적으로 또는 대안적으로, UE 는 UCI 의 페이로드를 송신하는데 사용되는 슬롯들의 수에 적어도 부분적으로 기초하여 UCT 를 반복할지 또는 UCI 를 공동으로 인코딩할지 여부를 결정할 수도 있다. 예를 들어, UE 는 제 1 UCI 및 제 2 UCI 를 포함하는 UCI 의 페이로드가 (예컨대, 8 비트 미만인) 임계치 이하의 크기를 갖는 때 UCI 를 반복할 수도 있다.

추가적으로 또는 대안적으로, UE 는 제 1 UCI 및 제 2 UCI 를 포함하는 UCI 의 페이로드를 송신하는데 사용되는 슬롯들의 수가 (예컨대, 2 슬롯들 보다 큰) 임계치 이상인 때 UCI 를 반복할 수도 있다. 추가적으로 또는 대안적으로, UE 는 제 1 UCI 및 제 2 UCI 를 포함하는 UCI 의 페이로드가 (예컨대, 8 비트 이상인) 임계치 이상의 크기를 갖는 때 UCI 를 공동으로 인코딩할 수도 있다. 추가적으로 또는 대안적으로, UE 는 제 1 UCI 및 제 2 UCI 를 포함하는 UCI 의 페이로드를 송신하는데 사용되는 슬롯들의 수가 (예컨대, 2 슬롯들 이하인) 임계치 이하인 때 UCI 를 공동으로 인코딩할 수도 있다.

[0160] 전술한 바와 같이, 도 16a 및 도 16b 는 예시로서 제공된다. 다른 예들이 가능하며, 도 16a 및 도 16b 에 대하여 설명된 것과 상이할 수도 있다.

[0161] 도 17 은 무선 통신의 방법의 플로우차트 (1700) 이다. 이 방법은 UE (예를 들어, 도 1 의 UE (120), 도 19-20 의 장치 (1902/1902') 등) 에 의해 수행될 수도 있다.

[0162] 1710 에서, UE 는 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 수신하고, 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함하고, 제 2 부분은 다운링크 제어 부분과 업링크 짧은 버스트 부분 사이에 위치된다. 몇몇 양태들에서, UE 는 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 수신한다. 몇몇 양태들에서, 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함한다. 몇몇 양태들에서, 제 2 부분은 다운링크 제어 부분과 업링크 짧은 버스트 부분 사이에 위치된다. 업링크 제어 구성 표시, 제 1 슬롯, 및 제 1 슬롯의 부분들은 도 7-16B 와 관련하여 위에서 상세히 설명된다.

[0163] 1720 에서, UE 는, 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 제 1 업링크 제어 정보 (UCI) 의 송신을 위해, 제 1 슬롯의 제 2 부분 또는 업링크 짧은 버스트 부분 중 적어도 하나에 물리적 업링크 제어 채널 (PUCCH) 을 구성할 수도 있고, 제 1 UCI 는 제 1 슬롯 또는 제 2 슬롯에서 송신되는 제 2 UCI 에 대응한다. 몇몇 양태들에서, UE 는 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 제 1 슬롯의 제 2 부분 또는 업링크 짧은 버스트 부분 중 적어도 하나에 PUCCH 를 구성한다. 몇몇 양태들에서, UE 는 UCI 의 송신을 위해 PUCCH 를 구성한다. 몇몇 양태들에서, 제 1 UCI 는 제 1 슬롯 또는 제 2 슬롯에서 송신되는 제 2 UCI 에 대응한다. 구성, PUCCH, 제 1 UCI, 제 2 UCI, 및 제 2 슬롯은 도 7-16B 와 관련하여 위에서 상세하게 설명된다.

[0164] 1730 에서, UE 는 구성된 PUCCH 상에 제 1 UCI 를 송신할 수도 있다. 몇몇 양태들에서, UE 는 구성된 PUCCH 상에 제 1 UCI 를 송신한다. 송신은 도 7-16B 와 관련하여 위에서 상세하게 설명된다.

[0165] 몇몇 양태들에서, 제 2 부분은 업링크 긴 버스트 부분이고, 제 1 UCI 및 제 2 UCI 는 제 1 슬롯에서 송신된다. 몇몇 양태들에서, PUCCH 는 업링크 긴 버스트 부분 및 업링크 짧은 버스트 부분 쌍방에 구성된다. 몇몇 양태들에서, 제 1 UCI 및 제 2 UCI 는 공동으로 인코딩된 UCI 로서 공동으로 인코딩된다. 몇몇 양태들에서, 업링크 제어 구성 표시는 PUCCH 가 단지 업링크 긴 버스트 부분에서 또는 업링크 긴 버스트 부분과 업링크 짧은 버스트 부분 쌍방에서 구성되어야 하는지 여부를 표시한다. 몇몇 양태들에서, 공동으로 인코딩된 UCI 의 하나 이상의 비트들은, PUCCH 가 단지 업링크 긴 버스트 부분에서 구성되어야 한다고 업링크 제어 구성 표시가 표시하는 때 절단된다. 몇몇 양태들에서, 공동으로 인코딩된 UCI 의 하나 이상의 비트들은, 업링크 제어 구성 표시가 PUCCH 가 업링크 긴 버스트 부분 및 업링크 짧은 버스트 부분 쌍방에서 구성되어야 한다고 표시하는 때

업링크 짧은 버스트 부분에서 반복 및 송신된다.

[0166] 몇몇 양태들에서, 제 2 UCI 는 제 1 UCI 의 반복이고, 제 1 UCI 는 제 1 슬롯의 업링크 긴 버스트 부분에서 송신되고, 제 2 UCI 는 제 1 슬롯의 업링크 짧은 버스트 부분에서 송신된다. 몇몇 양태들에서, PUCCH 는 업링크 제어 구성 표시의 수신과 관련된 특성으로부터 도출되거나 업링크 제어 구성 표시에서 시그널링된 하나 이상의 주파수 대역들에서 구성된다. 몇몇 양태들에서, 특성은 업링크 제어 구성 표시의 수신을 위해 사용된 주파수 대역이다. 몇몇 양태들에서, 하나 이상의 주파수 대역들은 업링크 긴 버스트 부분에서 하나 이상의 제 1 주파수 대역들을, 그리고 업링크 짧은 버스트 부분에서 하나 이상의 제 2 주파수 대역들을 포함한다. 몇몇 양태들에서, 하나 이상의 제 1 주파수 대역들은 하나 이상의 제 2 주파수 대역들과 상이하다. 몇몇 양태들에서, 물리적 업링크 공유 채널 (PUSCH) 은 제 1 UCI 또는 제 2 UCI 중 적어도 하나의 송신과 동시에 콘텐츠의 송신을 위해 업링크 긴 버스트 부분 또는 업링크 짧은 버스트 부분 중 적어도 하나에 구성된다.

[0167] 몇몇 양태들에서, 제 2 UCI 는 제 1 UCI 의 반복이고, PUCCH 는 제 1 UCI 의 송신을 위해 제 1 슬롯의 하나 이상의 제 1 주파수 대역들에, 그리고 제 2 UCI 의 송신을 위해 제 2 슬롯의 하나 이상의 제 2 주파수 대역들에 구성된다. 몇몇 양태들에서, 하나 이상의 제 1 주파수 대역들은 하나 이상의 제 2 주파수 대역들과 상이하다. 몇몇 양태들에서, 하나 이상의 제 1 주파수 대역들은 제 1 슬롯의 다운링크 제어 부분에서 수신된 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 결정되고, 하나 이상의 제 2 주파수 대역들은 제 2 슬롯의 다운링크 제어 부분에서 수신된 상이한 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 결정된다. 몇몇 양태들에서, 제 2 UCI 는 제 1 UCI 가 기지국에 의해 성공적으로 디코딩되었다는 표시의 수신에 적어도 부분적으로 기초하여 송신되지 않는다. 몇몇 양태들에서, 하나 이상의 제 1 주파수 대역들 및 하나 이상의 제 2 주파수 대역들은 제 1 슬롯의 다운링크 제어 부분에서 수신된 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 결정된다.

[0168] 몇몇 양태들에서, 제 1 슬롯의 다운링크 제어 부분은 제 1 다운링크 제어 부분이고, 제 1 슬롯의 제 2 부분은 제 1 업링크 긴 버스트 부분이고, 제 1 슬롯의 업링크 짧은 버스트 부분은 제 1 업링크 짧은 버스트 부분이고, 제 2 슬롯은 제 2 다운링크 제어 부분, 제 2 업링크 긴 버스트 부분, 및 제 2 업링크 짧은 버스트 부분을 포함한다. 몇몇 양태들에서, 제 1 UCI 는 제 1 슬롯의 제 1 업링크 긴 버스트 부분 또는 제 1 업링크 짧은 버스트 부분 중 적어도 하나에서 송신되고, 제 2 UCI 는 제 2 슬롯의 제 2 업링크 긴 버스트 부분 또는 제 2 업링크 짧은 버스트 부분 중 적어도 하나에서 송신된다.

[0169] 몇몇 양태들에서, 제 1 슬롯의 다운링크 제어 부분은 제 1 다운링크 제어 부분이고, 제 1 슬롯의 제 2 부분은 제 1 다운링크 데이터 부분이고, 제 1 슬롯의 업링크 짧은 버스트 부분은 제 1 업링크 짧은 버스트 부분이고, 제 2 슬롯은 제 2 다운링크 제어 부분, 제 2 다운링크 데이터 부분, 및 제 2 업링크 짧은 버스트 부분을 포함한다. 몇몇 양태들에서, 제 1 UCI 는 제 1 슬롯의 제 1 업링크 짧은 버스트 부분에서 송신되고, 제 2 UCI 는 제 2 슬롯의 제 2 업링크 짧은 버스트 부분에서 송신된다.

[0170] 몇몇 양태들에서, 제 1 슬롯 또는 제 2 슬롯 중 하나는 다운링크 데이터 부분 및 제 1 업링크 짧은 버스트 부분을 포함하고, 제 1 슬롯 또는 제 2 슬롯 중 다른 하나는 업링크 긴 버스트 부분 및 제 2 업링크 짧은 버스트 부분을 포함하고, 제 1 UCI 또는 제 2 UCI 중 하나는 제 1 업링크 짧은 버스트 부분에서 송신되고, 제 1 UCI 또는 제 2 UCI 중 다른 하나는 업링크 긴 버스트 부분 또는 제 2 업링크 짧은 버스트 부분 중 적어도 하나에서 송신된다.

[0171] 몇몇 양태들에서, 제 1 UCI 및 제 2 UCI 는 공동으로 인코딩된 UCI 로서 공동으로 인코딩되고, PUCCH 는 공동으로 인코딩된 UCI 의 송신을 위해 제 1 슬롯의 하나 이상의 제 1 주파수 대역들 및 제 2 슬롯의 하나 이상의 제 2 주파수 대역들에서 구성된다. 몇몇 양태들에서, 하나 이상의 제 1 주파수 대역들은 하나 이상의 제 2 주파수 대역들과 상이하다. 몇몇 양태들에서, 하나 이상의 제 1 주파수 대역들은 제 1 슬롯의 다운링크 제어 부분에서 수신된 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 결정되고, 하나 이상의 제 2 주파수 대역들은 제 2 슬롯의 다운링크 제어 부분에서 수신된 상이한 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 결정된다. 몇몇 양태들에서, 하나 이상의 제 1 주파수 대역들 및 하나 이상의 제 2 주파수 대역들은 제 1 슬롯의 다운링크 제어 부분에서 수신된 업링크 제어 구성 표시에 적어도 부분적으로 기초하여 결정된다. 몇몇 양태들에서, 하나 이상의 제 1 주파수 대역들 및 하나 이상의 제 2 주파수 대역들은 업링크 제어 구성 표시의 수신과 관련된 특성으로부터 도출된 주파수 오프셋에 적어도 부분적으로 기초하여 결정된다.

[0172] 몇몇 양태들에서, 제 1 슬롯의 제 2 부분은 제 1 업링크 긴 버스트 부분이고, 제 1 슬롯의 업링크 짧은 버스트 부분은 제 1 업링크 짧은 버스트 부분이고, 제 2 슬롯은 제 2 업링크 긴 버스트 부분 및 제 2 업링크 짧은 버스

트 부분을 포함한다. 몇몇 양태들에서, 제 2 슬롯은 다운링크 제어 부분을 포함하지 않는다. 몇몇 양태들에서, 공동으로 인코딩된 UCI 는 제 1 슬롯의 제 1 업링크 긴 버스트 부분 또는 제 1 업링크 짧은 버스트 부분 중 적어도 하나 그리고 제 2 슬롯의 제 2 업링크 긴 버스트 부분 또는 제 2 업링크 짧은 버스트 부분의 적어도 하나에서 송신된다.

[0173] 몇몇 양태들에서, 제 1 슬롯의 다운링크 제어 부분은 제 1 다운링크 제어 부분이고, 제 1 슬롯의 제 2 부분은 제 1 다운링크 데이터 부분이고, 제 1 슬롯의 업링크 짧은 버스트 부분은 제 1 업링크 짧은 버스트 부분이고, 제 2 슬롯은 제 2 다운링크 제어 부분, 제 2 다운링크 데이터 부분, 및 제 2 업링크 짧은 버스트 부분을 포함한다. 몇몇 양태들에서, 공동으로 인코딩된 UCI 는 제 1 슬롯의 제 1 업링크 짧은 버스트 부분 및 제 2 슬롯의 제 2 업링크 짧은 버스트 부분에서 송신된다.

[0174] 몇몇 양태들에서, 제 1 슬롯 또는 제 2 슬롯 중 하나는 다운링크 데이터 부분 및 제 1 업링크 짧은 버스트 부분을 포함하고, 제 1 슬롯 또는 제 2 슬롯 중 다른 하나는 업링크 긴 버스트 부분 및 제 2 업링크 짧은 버스트 부분을 포함하고, 공동으로 인코딩된 UCI 는 제 1 업링크 짧은 버스트 부분 및 업링크 긴 버스트 부분 또는 제 2 업링크 짧은 버스트 부분 중 적어도 하나에서 송신된다. 몇몇 양태들에서, 제 1 슬롯 및 제 2 슬롯은 인접한다. 몇몇 양태들에서, 제 1 슬롯 및 제 2 슬롯은 비인접한다. 몇몇 양태들에서, 업링크 제어 구성 표시는, UCI 가 반복되거나 공동으로 인코딩되어야 하는 슬롯의 수, 제 1 UCI 및 제 2 UCI 가 인접 슬롯들 또는 비인접 슬롯들에서 반복되거나 공동으로 인코딩되어야 하는지 여부, 반복된 UCI 또는 공동으로 인코딩된 UCI 의 송신을 위한 슬롯 패턴, 제 2 슬롯이 다운링크 제어 부분을 포함하도록 구성되어야 하는지 여부, 또는 이들의 일부 조합 중 적어도 하나를 표시한다.

[0175] 몇몇 양태들에서, 제 1 UCI 및 제 2 UCI 는 제 1 UCI 및 제 2 UCI 를 포함하는 UCI 의 페이로드가 임계치 이하의 크기를 갖는 때 반복된 UCI 이도록 구성된다. 몇몇 양태들에서, 제 1 UCI 및 제 2 UCI 는 제 1 UCI 및 제 2 UCI 를 포함하는 UCI 의 페이로드가 임계치 이상의 크기를 갖는 때 공동으로 인코딩된 UCI 이도록 구성된다. 몇몇 양태들에서, 제 1 UCI 및 제 2 UCI 는 제 1 UCI 및 제 2 UCI 를 포함하는 UCI 의 페이로드를 송신하는데 사용되는 슬롯들의 수가 임계치 이하인 때 공동으로 인코딩된 UCI 이도록 구성된다. 몇몇 양태들에서, 제 1 UCI 및 제 2 UCI 는 제 1 UCI 및 제 2 UCI 를 포함하는 UCI 의 페이로드를 송신하는데 사용되는 슬롯들의 수가 임계치 이상인 때 반복된 UCI 이도록 구성된다.

[0176] 도 17 은 무선 통신의 방법의 예시적인 블록을 도시하지만, 몇몇 양태들에서, 이 방법은 도 17 에 도시된 것과 상이한 추가의 블록들, 더 적은 블록들, 상이한 블록들 또는 상이하게 배치된 블록들을 포함할 수도 있다. 추가적으로 또는 대안적으로, 도 17 에 나타낸 2 이상의 블록들은 병렬적으로 수행될 수도 있다.

[0177] 도 18 은 무선 통신의 방법의 플로우차트 (1800) 이다. 이 방법은 기지국 (예를 들어, 도 1 의 기지국 (110), 도 21-22 의 장치 (2102/2102') 등) 에 의해 수행될 수도 있다.

[0178] 1810 에서, 기지국은 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 송신할 수도 있고, 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함하고, 제 2 부분은 다운링크 제어 부분과 업링크 짧은 버스트 부분 사이에 위치되고, 업링크 제어 구성 표시는 제 1 업링크 제어 정보 (UCI) 의 송신을 위해 사용자 장비 (UE) 에게 제 1 슬롯의 제 2 부분 또는 업링크 짧은 버스트 부분 중 적어도 하나에서 물리적 업링크 제어 채널 (PUCCH) 을 구성할 것을 명령하고, 제 1 UCI 는 제 1 슬롯 또는 제 2 슬롯에서 UE 에 의해 송신되는 제 2 UCI 에 대응한다. 몇몇 양태들에서, 기지국은 제 1 슬롯의 다운링크 제어 부분에서 업링크 제어 구성 표시를 송신할 수도 있다. 몇몇 양태들에서, 제 1 슬롯은 다운링크 제어 부분, 제 2 부분, 및 업링크 짧은 버스트 부분을 포함한다. 몇몇 양태들에서, 제 2 부분은 다운링크 제어 부분과 업링크 짧은 버스트 부분 사이에 위치된다. 몇몇 양태들에서, 업링크 제어 구성 표시는 제 1 UCI 의 송신을 위해 제 2 부분 또는 제 1 슬롯의 업링크 짧은 버스트 부분 중 적어도 하나에 PUCCH 를 구성하도록 UE 에 명령한다. 몇몇 양태들에서, 제 1 UCI 는 제 1 슬롯 또는 제 2 슬롯에서 UE 에 의해 송신되는 제 2 UCI 에 대응한다. 추가적인 세부 사항은 도 7-16b 와 관련하여 위에서 설명된다.

[0179] 1820 에서, 기지국은 구성된 PUCCH 상에 제 1 UCI 를 수신할 수도 있다. 몇몇 양태들에서, UE 는 구성된 PUCCH 상에 제 1 UCI 를 송신할 수도 있다. 기지국은 구성된 PUCCH 상에 제 1 UCI 를 수신할 수도 있다. 추가적인 세부 사항은 도 7-16b 와 관련하여 위에서 설명된다.

[0180] 도 18 은 무선 통신의 방법의 예시적인 블록들을 도시하지만, 몇몇 양태들에서, 이 방법은 도 18 에 도시된 것과 상이한 추가의 블록들, 더 적은 블록들, 상이한 블록들 또는 상이하게 배치된 블록들을 포함할 수도 있다.

추가적으로 또는 대안적으로, 도 18 에 나타낸 2 이상의 블록들은 병렬적으로 수행될 수도 있다.

[0181] 도 19 는 예시적인 장치 (1902) 에 있어서 상이한 모듈들/수단들/컴포넌트들 간의 데이터 플로우를 도시한 개념적 데이터 플로우 다이어그램 (1900) 이다. 장치 (1902) 는 UE (예를 들어, 도 1 의 UE (120) 등) 일 수도 있다. 몇몇 양태들에서, 장치 (1902) 는 수신 모듈 (1904), 구성 모듈 (1906), 및/또는 송신 모듈 (1908) 을 포함한다. 수신 모듈 (1904) 은 본원에서 설명되는 바와 같이 기지국 (1950) 으로부터 데이터 (1910) 로서 하나 이상의 업링크 제어 구성 표시들을 수신할 수도 있다. 수신 모듈 (1904) 은 데이터 (1912) 로서 구성 모듈 (1906) 에 하나 이상의 업링크 제어 구성 표시들을 제공할 수도 있다. 구성 모듈은 본원에서 상세히 설명되는 바와 같이 하나 이상의 업링크 제어 구성 표시들에 적어도 부분적으로 기초하여 PUCCH 를 구성할 수도 있다. 구성 모듈 (1906) 은 구성과 관련된 데이터 (1914) 를 송신 모듈 (1908) 에 제공할 수도 있다.

송신 모듈 (1908) 은 데이터 (1914) 에 적어도 부분적으로 기초하여 (예를 들어, 구성 모듈 (1906) 에 의해 구성된 하나 이상의 슬롯들, 주파수 대역들 등을 사용하여) UCI 를 데이터 (1916) 로서 기지국 (1950) 에 송신 할 수도 있다.

[0182] 장치는, 도 17 의 상기한 플로우 차트에서의 알고리즘의 블록들 각각을 수행하는 추가적인 모듈들을 포함할 수도 있다. 따라서, 도 17 의 상기한 플로우 차트에서의 각각의 블록은 모듈에 의해 수행될 수도 있으며, 장치는 그 모듈들 중 하나 이상을 포함할 수도 있다. 모듈들은 언급된 프로세스들/알고리즘을 수행하도록 구체적으로 구성되거나, 언급된 프로세스들/알고리즘을 수행하도록 구성된 프로세서에 의해 구현되거나, 프로세서에 의한 구현을 위해 컴퓨터 판독가능 매체 내에 저장되거나, 이들의 일부 조합인 하나 이상의 하드웨어 컴포넌트들일 수도 있다.

[0183] 도 19 에 도시된 모듈의 수 및 배치는 예시로서 제공된다. 실제로, 추가적인 모듈들, 더 적은 모듈들, 상이한 모듈들, 또는 도 19 에 도시된 것과 상이하게 배치된 모듈들이 있을 수도 있다. 또한, 도 19 에 도시된 2 개 이상의 모듈들은, 단일 모듈 내에 구현될 수도 있거나, 또는 도 19 에 도시된 단일 모듈은 다중의 분산된 모듈들로서 구현될 수도 있다. 추가적으로 또는 대안적으로, 도 19 에 도시된 모듈들의 세트 (예를 들어, 하나 이상의 모듈들) 는 도 19 에 도시된 모듈들의 다른 세트에 의해 수행되는 것으로 기술된 하나 이상의 기능을 수행할 수도 있다.

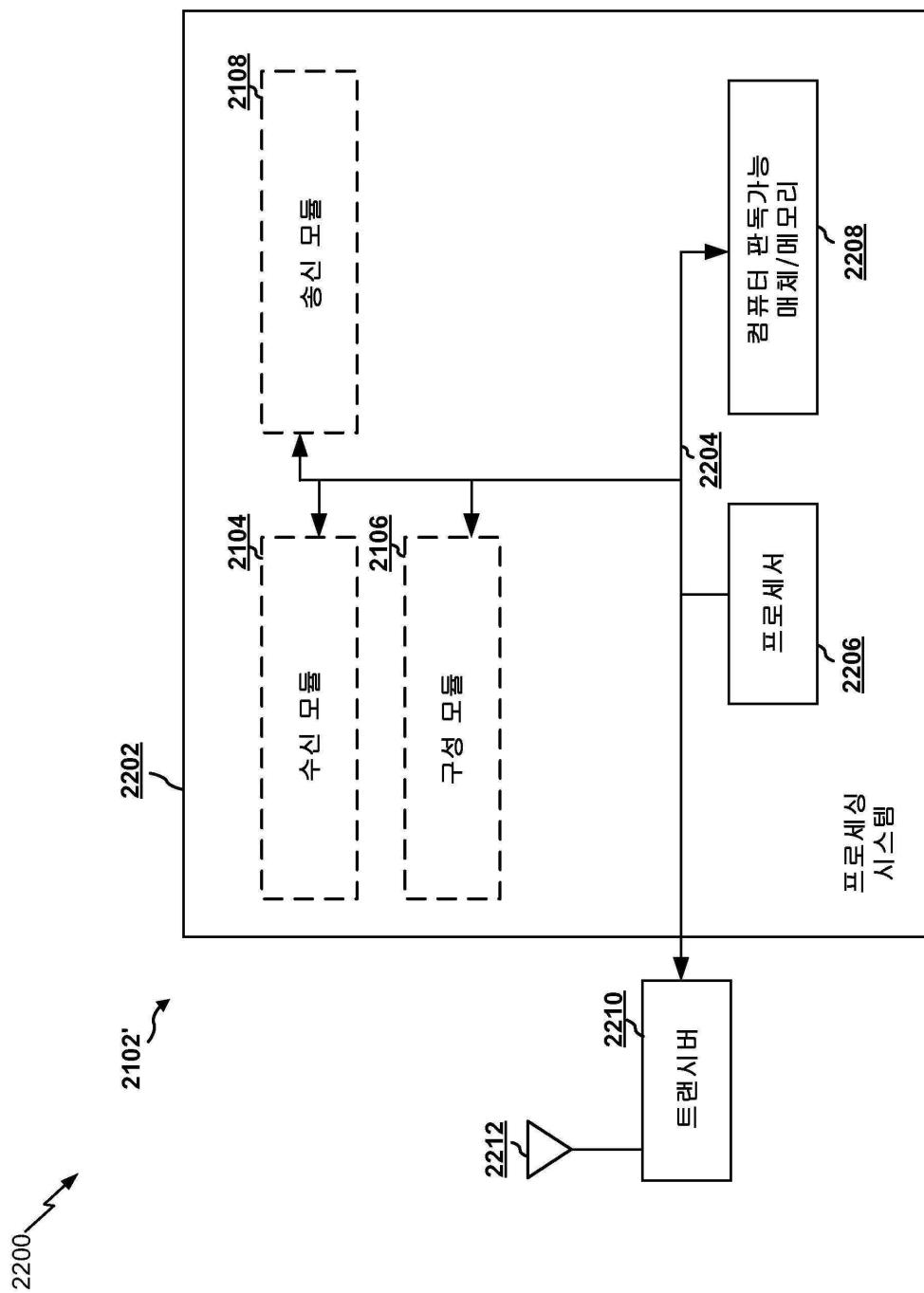

[0184] 도 20 은 프로세싱 시스템 (2002) 을 채용하는 장치 (1902') 에 대한 하드웨어 구현의 일례를 예시하는 다이어그램 (2000) 이다. 장치 (1902') 는 UE (예를 들어, 도 1 의 UE (120) 등) 일 수도 있다.

[0185] 프로세싱 시스템 (2002) 은 버스 (2004) 에 의해 일반적으로 표현되는 버스 아키텍처로 구현될 수도 있다. 버스 (2004) 는 프로세싱 시스템 (2002) 의 특정 애플리케이션 및 전체적인 설계 제약들에 따라 임의의 수의 상호접속하는 버스들 및 브릿지들을 포함할 수도 있다. 버스 (2004) 는 프로세서 (2006), 모듈들 (1904, 1906, 및/또는 1908), 및 컴퓨터 판독가능 매체/메모리 (2008) 에 의해 표현된, 하나 이상의 프로세서들 및/또는 하드웨어 모듈들을 포함한 다양한 회로들을 함께 링크시킨다. 버스 (2004) 는 또한, 타이밍 소스들, 주변기기들, 전압 레귤레이터들, 및 전력 관리 회로들과 같은 다양한 다른 회로들을 링크할 수도 있으며, 이는 본 기술분야에서 잘 알려져 있으므로 더 설명하지 않는다.

[0186] 프로세싱 시스템 (2002) 은 트랜시버 (2010) 에 커플링될 수도 있다. 트랜시버 (2010) 는 하나 이상의 안테나들 (2012) 에 커플링된다. 트랜시버 (2010) 는 송신 매체에 걸쳐 다양한 다른 장치와 통신하기 위한 수단을 제공한다. 트랜시버 (2010) 는 하나 이상의 안테나들 (2012) 로부터 신호를 수신하고, 수신된 신호로부터 정보를 추출하고, 추출된 정보를 프로세싱 시스템 (2002), 구체적으로, 수신 모듈 (1904) 에 제공한다. 부가적으로, 트랜시버 (2010) 는 프로세싱 시스템 (2002), 구체적으로, 송신 모듈 (1908) 로부터 정보를 수신하고, 수신된 정보에 적어도 부분적으로 기초하여, 하나 이상의 안테나들 (2012) 에 적용될 신호를 생성한다.

프로세싱 시스템 (2002) 은 컴퓨터-판독가능 매체/메모리 (2008) 에 커플링된 프로세서 (2006) 를 포함한다.