(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6261476号

(P6261476)

(45) 発行日 平成30年1月17日(2018.1.17)

(24) 登録日 平成29年12月22日(2017.12.22)

|                       |               |

|-----------------------|---------------|

| (51) Int.Cl.          | F 1           |

| HO2M 7/48 (2007.01)   | HO2M 7/48 M   |

| HO2M 7/487 (2007.01)  | HO2M 7/487    |

| HO2M 1/08 (2006.01)   | HO2M 1/08 A   |

| HO3K 17/687 (2006.01) | HO3K 17/687 F |

| HO3K 17/16 (2006.01)  | HO3K 17/16 L  |

請求項の数 21 (全 31 頁)

(21) 出願番号 特願2014-176913 (P2014-176913)

(22) 出願日 平成26年9月1日 (2014.9.1)

(65) 公開番号 特開2016-52198 (P2016-52198A)

(43) 公開日 平成28年4月11日 (2016.4.11)

審査請求日 平成28年10月18日 (2016.10.18)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100073759

弁理士 大岩 増雄

(74) 代理人 100088199

弁理士 竹中 岳生

(74) 代理人 100094916

弁理士 村上 啓吾

(74) 代理人 100127672

弁理士 吉澤 憲治

(72) 発明者 加藤 将

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】電力変換装置および電力変換装置の出力電圧検出方法

## (57) 【特許請求の範囲】

## 【請求項 1】

2 以上のスイッチング部を有する電力変換主回路と、

前記各スイッチング部をそれぞれ駆動する複数のゲート駆動部と、

前記ゲート駆動部の間に接続されるインピーダンス素子と、

前記インピーダンス素子の電圧または電流を検出する検出部と

を備え、

前記インピーダンス素子の一端は前記複数のゲート駆動部のうちの一つと接続され、前記インピーダンス素子の他端は前記一端と接続された前記ゲート駆動部と異なる他の前記複数のゲート駆動部のうちの一つと接続されることを特徴とする電力変換装置。

10

## 【請求項 2】

前記スイッチング部は、正極側としての第1のスイッチング部と前記第1のスイッチング部に直列に接続される負極側としての第2のスイッチング部を有し、前記ゲート駆動部は、前記第1のスイッチング部を駆動する第1のゲート駆動部と前記第2のスイッチング部を駆動する第2のゲート駆動部とを有し、前記インピーダンス素子は、前記第1のゲート駆動部と前記第2のゲート駆動部との間に接続されることを特徴とする請求項1に記載の電力変換装置。

## 【請求項 3】

前記スイッチング部は、3相のうち一の相としての第1のスイッチング部と他の相としての第2のスイッチング部を有し、前記ゲート駆動部は、前記第1のスイッチング部を駆

20

動する第1のゲート駆動部と前記第2のスイッチング部を駆動する第2のゲート駆動部とを有し、前記インピーダンス素子は、前記第1のゲート駆動部と前記第2のゲート駆動部との間に接続されることを特徴とする請求項1に記載の電力変換装置。

【請求項4】

前記検出部からの信号に応じて前記ゲート駆動部を制御する制御部をさらに備えたことを特徴とする請求項2に記載の電力変換装置。

【請求項5】

前記第1のスイッチング部および前記第2のスイッチング部は、それぞれ1のスイッチング素子で構成され、前記第1のゲート駆動部および前記第2のゲート駆動部は、それぞれ1のゲート駆動回路が前記各スイッチング素子に対応して設けられ、2レベルの電圧を出力することを特徴とする請求項4に記載の電力変換装置。 10

【請求項6】

前記制御部は、前記検出部からの信号に基づいて出力電圧信号を補正する補正回路と、前記出力電圧信号のうち正極側の前記スイッチング素子の駆動信号にデッドタイムを付加して正極側の前記スイッチング素子を駆動する前記ゲート駆動回路に出力する第1の付加回路と、前記出力電圧信号のうち負極側の前記スイッチング素子の反転した駆動信号にデッドタイムを付加して負極側の前記スイッチング素子を駆動する前記ゲート駆動回路に出力する第2の付加回路とを備えることを特徴とする請求項5に記載の電力変換装置。

【請求項7】

前記第1のスイッチング部および前記第2のスイッチング部は、それぞれ2のスイッチング素子を直列接続して構成され、前記第1のゲート駆動部および前記第2のゲート駆動部は、それぞれ2のゲート駆動回路が前記各スイッチング素子に対応して設けられ、3レベルの電圧を出力することを特徴とする請求項4に記載の電力変換装置。 20

【請求項8】

前記インピーダンス素子は、正極側の2の前記スイッチング素子のうち下位電位側の前記スイッチング素子を駆動する前記ゲート駆動回路と、負極側の2の前記スイッチング素子のうち下位電位側の前記スイッチング素子を駆動する前記ゲート駆動回路とに接続されていることを特徴とする請求項7に記載の電力変換装置。

【請求項9】

前記制御部は、正極側の前記スイッチング素子および負極側の前記スイッチング素子の各上位電位側の前記スイッチング素子を駆動する前記各ゲート駆動回路への出力電圧信号を、前記検出部からの信号に基づいて補正する第1の補正回路と、正極側の前記スイッチング素子および負極側の前記スイッチング素子の各下位電位側の前記スイッチング素子を駆動する前記各ゲート駆動回路への前記出力電圧信号を、前記検出部からの信号に基づいて補正する第2の補正回路と、前記第1の補正回路からの前記出力電圧信号のうち正極側の上位電位側の前記スイッチング素子の駆動信号にデッドタイムを付加して、正極側の上位電位側の前記スイッチング素子を駆動する前記ゲート駆動回路に出力する第1の付加回路と、前記第1の補正回路からの前記出力電圧信号のうち負極側の上位電位側の前記スイッチング素子の反転した駆動信号にデッドタイムを付加して、負極側の上位電位側の前記スイッチング素子を駆動する前記ゲート駆動回路に出力する第2の付加回路と、前記第2の補正回路からの前記出力電圧信号のうち正極側の下位電位側の前記スイッチング素子の駆動信号にデッドタイムを付加して、正極側の下位電位側の前記スイッチング素子を駆動する前記ゲート駆動回路に出力する第3の付加回路と、前記第2の補正回路からの前記出力電圧信号のうち負極側の下位電位側の前記スイッチング素子の反転した駆動信号にデッドタイムを付加して、負極側の下位電位側の前記スイッチング素子を駆動する前記ゲート駆動回路に出力する第4の付加回路とを備えることを特徴とする請求項8に記載の電力変換装置。 30 40

【請求項10】

前記制御部は、絶縁回路を介して前記各ゲート駆動回路および前記検出部と接続されていることを特徴とする請求項6または請求項9に記載の電力変換装置。 50

## 【請求項 1 1】

前記インピーダンス素子は、1の抵抗、または2以上の抵抗を直列に接続したものであることを特徴とする請求項5から請求項10のいずれか1項に記載の電力変換装置。

## 【請求項 1 2】

前記インピーダンス素子は、1のコンデンサ、または2以上のコンデンサを直列に接続したものであることを特徴とする請求項5から請求項10のいずれか1項に記載の電力変換装置。

## 【請求項 1 3】

前記インピーダンス素子は、1のダイオード、または2以上のダイオードを直列に接続したものであることを特徴とする請求項5から請求項10のいずれか1項に記載の電力変換装置。 10

## 【請求項 1 4】

前記各ゲート駆動回路と前記インピーダンス素子は、同一の基板上に配設されていることを特徴とする請求項5から請求項13のいずれか1項に記載の電力変換装置。

## 【請求項 1 5】

正極側の前記スイッチング素子と対応する前記ゲート駆動回路とを接続する第1の信号線と、負極側の前記スイッチング素子と対応する前記ゲート駆動回路とを接続する第2の信号線とを備え、前記第1の信号線と前記第2の信号線は、隣接して配設されることを特徴とする請求項5から請求項14のいずれか1項に記載の電力変換装置。

## 【請求項 1 6】

前記インピーダンス素子と正極側の前記スイッチング素子を駆動する前記ゲート駆動回路の接続部が、前記第1の信号線と正極側の前記スイッチング素子を駆動する前記ゲート駆動回路の接続部の近傍に設けられ、前記インピーダンス素子と負極側の前記スイッチング素子を駆動する前記ゲート駆動回路の接続部が、前記第2の信号線と負極側の前記スイッチング素子を駆動する前記ゲート駆動回路の接続部の近傍に設けられていることを特徴とする請求項15に記載の電力変換装置。 20

## 【請求項 1 7】

前記各スイッチング素子は、IGBT、MOSFET、またはバイポーラトランジスタからなることを特徴とする請求項5から請求項16のいずれか1項に記載の電力変換装置。 30

## 【請求項 1 8】

正極側の前記スイッチング素子および負極側の前記スイッチング素子は、2in1モジュールで形成していることを特徴とする請求項5から請求項17のいずれか1項に記載の電力変換装置。

## 【請求項 1 9】

前記各スイッチング部に、ワイドバンドギャップ半導体を用いることを特徴とする請求項1から請求項18のいずれか1項に記載の電力変換装置。

## 【請求項 2 0】

前記ワイドバンドギャップ半導体は、炭化ケイ素、窒化ガリウム系材料または、ダイアモンドを用いた半導体であることを特徴とする請求項19に記載の電力変換装置。 40

## 【請求項 2 1】

第1のスイッチング部を駆動する第1のゲート駆動部と、第2のスイッチング部を駆動する第2のゲート駆動部との間に接続されるインピーダンス素子を用い、前記インピーダンス素子の電圧または電流を検出することにより、第1のスイッチング素子と第2のスイッチング素子の接続点の電圧を検出することを特徴とする電力変換装置の電圧検出方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

この発明は、複数個のスイッチング素子を内蔵した電力変換装置および電力変換装置が内蔵するスイッチング素子間の電圧検出方法に関するものである。 50

## 【背景技術】

## 【0002】

インバータ装置、サーボアンプ装置、スイッチング電源装置といった電力変換装置は複数個のスイッチング素子を内蔵している。複数個のスイッチング素子を組み合わせて電気回路を構成している。多くの電力変換装置において、正極側を第1のスイッチング部、負極側を第2のスイッチング部とし、第1のスイッチング部と第2のスイッチング部の接続点を出力端子として電力を出力する電力変換主回路を採用している。スイッチング部は、1個または複数個の直列接続されたスイッチング素子により構成される。このような電力変換主回路では直列接続されたスイッチング素子間に貫通電流が流れないように、予めスイッチング信号にデッドタイム期間を設ける必要がある。

10

## 【0003】

このスイッチング信号のデッドタイム期間により、電力変換主回路の出力電圧は、指令値に対して誤差を含むことになる。更に、スイッチング素子のターンオン時間、ターンオフ時間がスイッチング電圧、スイッチング電流、温度などのさまざまな条件によりバラツキを持つ。よって、電力変換装置が内蔵するスイッチング素子間の電圧が、意図した電圧とは異なる場合がある。電力変換主回路のデッドタイム期間が、意図したスイッチング信号のデッドタイム期間と異なる場合がある。そこで、電力変換装置が内蔵するスイッチング素子間の電圧を検出したいという要求がある。スイッチング信号のデッドタイム補正のため、電力変換主回路の出力電圧を検出したいという要求がある。

## 【0004】

20

従来の電力変換装置では、インバータの2個直列に接続されたスイッチング素子の負極側のスイッチング素子の主端子間に取り付けられ、負極側のスイッチング素子の主端子間が導通状態であることを検出する導通検出手段であるセンサーと、このセンサーからの検出信号により負極側のスイッチング素子の主端子間の導通時間をカウントし、そのカウント値を電流制御演算装置に対して、電力変換主回路の出力電圧指令値の補償信号として出力する計数手段であるカウンタと、からなるデットタイム補償装置を備えた構成が知られている。(例えば、特許文献1)。

## 【0005】

また、デッドタイムを自動制御する技術として、降圧型DC-DCコンバータにおいて、メインスイッチング素子のゲート電圧と同期整流用スイッチング素子のゲート電圧の特徴を監視し、これら検出結果に基づいて、上記の2つのスイッチング素子のON、OFFタイミングを調整することでデットタイム期間を最小にする技術が知られている。(例えば、特許文献2)

30

## 【0006】

更に、上記の特許文献2のように、スイッチング素子のゲート電圧の特徴を監視し、その検出結果に基づいて、電力変換主回路の出力電圧を検出し、上記の特許文献1のようなデッドタイム補償を実施する技術が知られている(例えば、特許文献3)。

## 【先行技術文献】

## 【特許文献】

## 【0007】

40

【特許文献1】特開平5-252795号公報(段落0014、図1)

【特許文献2】特開2007-329748号公報(段落0033~0070、図7)

【特許文献3】特開2010-016937号公報(段落0016、図1)

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0008】

特許文献1のような構成では、導通検出手段によりスイッチング素子の主端子間の導通状態を検出し、この検出信号から計数手段により導通時間をカウントすることで、このカウント値を電圧指令値の補償信号として、電流制御演算手段によって実際の電力変換主回路の出力電圧を認識し、電圧指令値にデッドタイム補償の演算処理を行う。

50

## 【0009】

しかし、一般に、電力変換主回路と電力変換主回路周辺は、寄生インダクタンスの削減のためや、発生電力損失の冷却のため、部品が複雑に入り組んでいる。よって、これら導通検出手段等を電力変換主回路へ取り付ける作業は高度な技術を要し、電力変換装置の製造が困難であるという課題があった。

## 【0010】

また、特許文献2,3のようなゲート電圧の特徴を監視する方式のものは、スイッチング素子のゲート電圧を検出して、その電圧状態から電力変換主回路の出力電圧を検出している。しかしながら、ゲート電圧に表れる特徴は、スイッチング素子の半導体特性が決めており、電力変換装置の設計者が調整することはできない。ゲート電圧に表れる特徴は、典型的には数V程度、数マイクロ秒程度の電圧変動である。このような微細な電圧変動を検出する必要があるが、電磁ノイズに弱く、電力変換装置が誤動作する場合があり、信頼性という観点で課題があった。

10

## 【0011】

この発明は、上記のような課題を解決するためになされたものであり、電力変換主回路の出力電圧を検出する電力変換装置であって、製造が容易で、かつ誤動作しない電力変換装置を提供することを目的としている。また、電力変換装置が内蔵するスイッチング素子間の電圧検出方法であって、製造が容易で、かつ誤動作しない電圧検出方法を提供することを目的としている。

## 【課題を解決するための手段】

20

## 【0012】

この発明の電力変換装置は、2以上のスイッチング部を有する電力変換主回路と、前記各スイッチング部をそれぞれ駆動する複数のゲート駆動部と、前記ゲート駆動部の間に接続されるインピーダンス素子と、前記インピーダンス素子の電圧または電流を検出する検出部とを備え、前記インピーダンス素子の一端は前記複数のゲート駆動部のうちの一つと接続され、前記インピーダンス素子の他端は前記一端と接続された前記ゲート駆動部と異なる他の前記複数のゲート駆動部のうちの一つと接続されることを特徴とする。

## 【0013】

また、この発明の電力変換装置の電圧検出方法は、第1のスイッチング部を駆動する第1のゲート駆動部と、第2のスイッチング部を駆動する第2のゲート駆動部との間に接続されるインピーダンス素子を用い、インピーダンス素子の電圧または電流を検出することにより、第1のスイッチング部と第2のスイッチング部との間の電圧を検出することを特徴とする。

30

## 【発明の効果】

## 【0014】

この発明によれば、スイッチング部の間の電位差を、それぞれ対応するゲート駆動回路の間に接続するインピーダンス素子の電圧または電流から検出することで、電力変換主回路の出力電圧を検出でき、かつ、容易に製造することができ、かつ、誤動作しない。

## 【図面の簡単な説明】

## 【0015】

40

【図1】この発明の実施の形態1による電力変換装置を示す構成図である。

【図2】この発明の実施の形態1による電力変換装置を示す回路図である。

【図3】この発明の実施の形態1による他の電力変換装置を示す回路図である。

【図4】この発明の実施の形態1による電力変換装置の部品の配置図である。

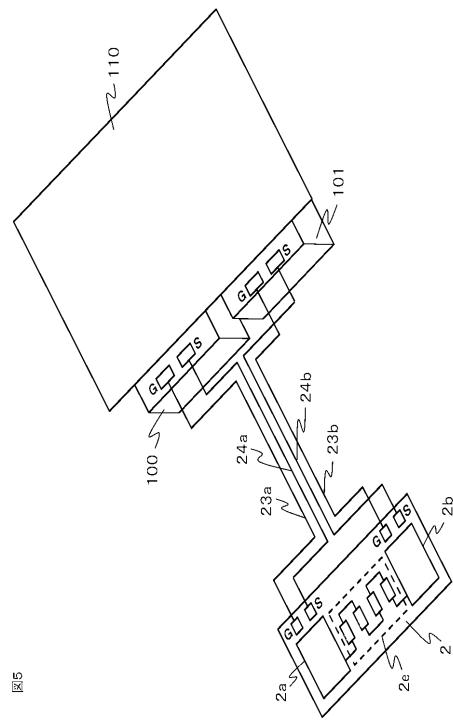

【図5】この発明の実施の形態1による他の電力変換装置の部品の配置図である。

【図6】この発明の実施の形態2による電力変換装置を示す構成図である。

【図7】この発明の実施の形態2による電力変換装置を示す回路図である。

【図8】この発明の実施の形態2による他の電力変換装置を示す回路図である。

【図9】この発明の実施の形態2による電力変換装置の絶縁回路のタイムチャートである。

。

50

【図10】この発明の実施の形態2による電力変換装置のデッドタイム補正回路のプロック図である。

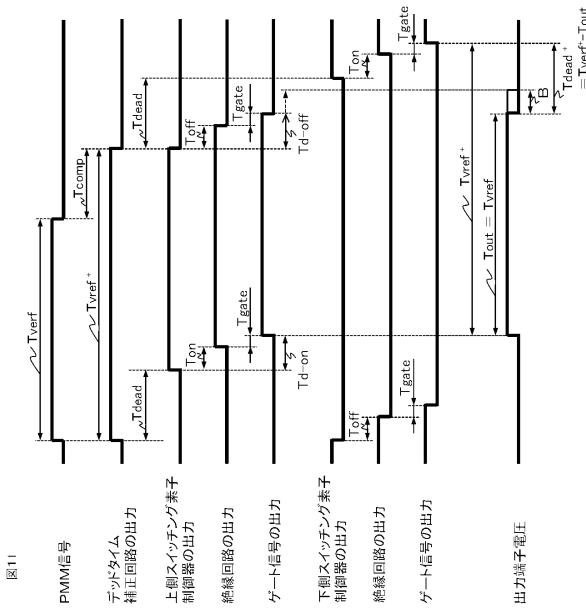

【図11】この発明の実施の形態2による電力変換装置のデッドタイム補正回路で、負荷電流が正の場合のデッドタイム補正の動作を示すタイムチャートである。

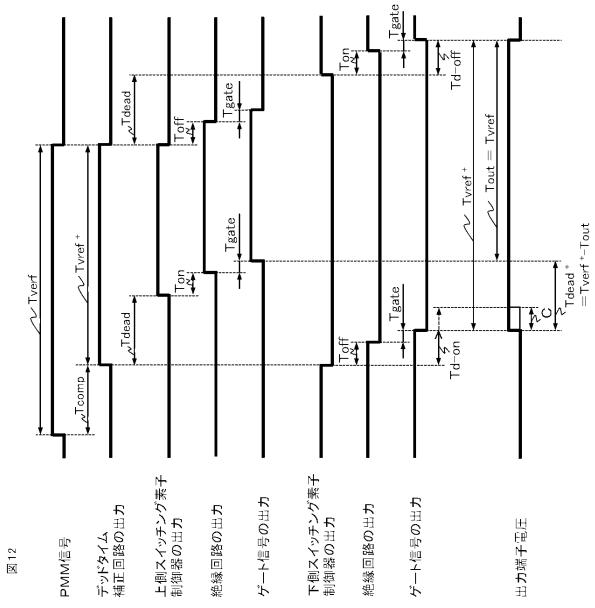

【図12】この発明の実施の形態2による電力変換装置のデッドタイム補正回路で、負荷電流が負の場合のデッドタイム補正の動作を示すタイムチャートである。

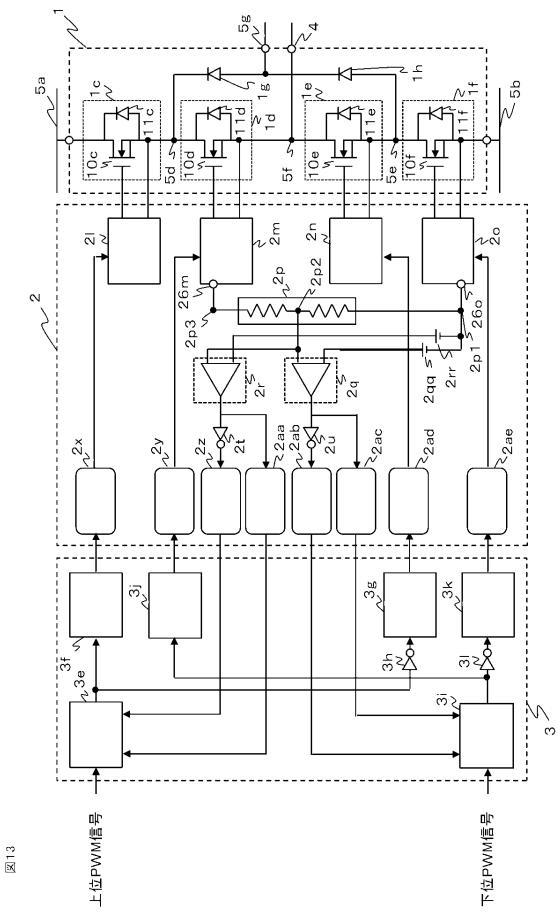

【図13】この発明の実施の形態3による電力変換装置を示す構成図である。

【図14】この発明の実施の形態3による他の電力変換装置を示す構成図である。

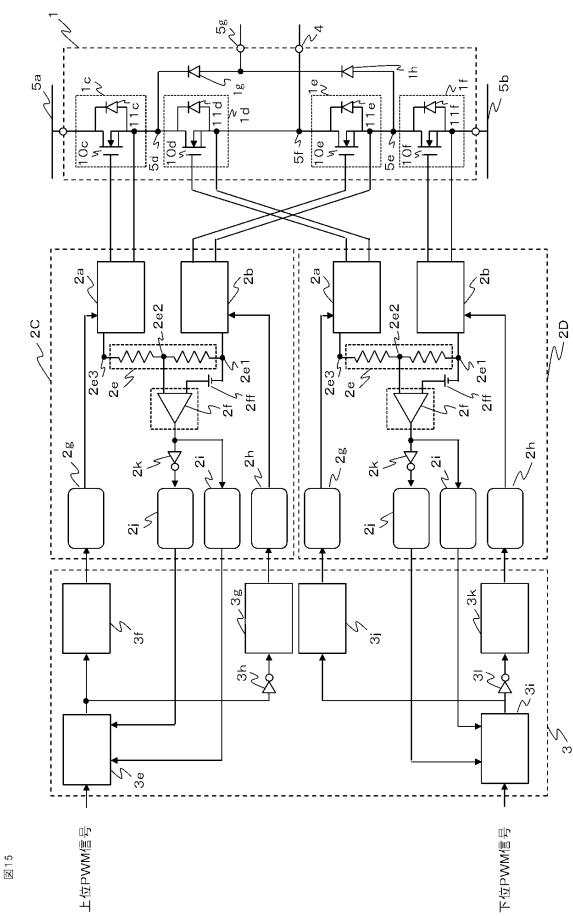

【図15】この発明の実施の形態3による他の電力変換装置を示す構成図である。

【図16】この発明の実施の形態4による電力変換装置を示す配置図である。

【図17】この発明の実施の形態4による他の電力変換装置を示す配置図である。

【発明を実施するための形態】

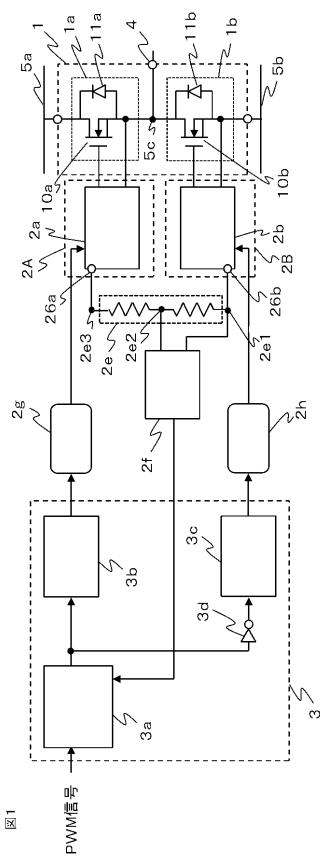

【0016】

実施の形態1.

図1は、この発明の実施の形態1による電力変換装置を示す構成図であり、電力変換主回路1、ゲート駆動回路基板2a、2B、制御部3、および周辺部品の構成を図示している。図1に示すように、電力変換主回路1は、2レベルの電力変換回路として構成される。

【0017】

この実施の形態1における電力変換主回路1は、電力変換主回路1の正極が直流母線5aに接続され、電力変換主回路1の負極が直流母線5bに接続される。電力変換主回路1は、正極側の直流母線5aに接続される第1のスイッチング部としてのスイッチング素子1aと、負極側の直流母線5bに接続される第2のスイッチング部としてのスイッチング素子1bと、スイッチング素子1aとスイッチング素子1bが直列に接続され、その電気的接続点5cに電力変換主回路1の出力端子4を備える。電力変換主回路1は、出力端子4から負荷(図示せず)に電力を供給する。第1のスイッチング部が導通すれば電力変換主回路1は直流母線5aの電位を出力端子4から負荷に供給する。第2のスイッチング部が導通すれば電力変換主回路1は直流母線5bの電位を出力端子4から負荷に供給する。このように2通りの電位を出力することから、2レベルの電力変換回路として機能する。

【0018】

スイッチング素子1aは、トランジスタ素子10aとダイオード素子11aが並列に接続され、スイッチング素子1bは、トランジスタ素子10bとダイオード素子11bが並列に接続されている。なお、負荷の特性によっては、例えば抵抗負荷である場合にはダイオード素子11a、ダイオード素子11bの接続が省略されることがある。

【0019】

なお、トランジスタ素子10a、10bは、図1ではMOSFETを図示しているが、特に限定するものではない。電気信号により低抵抗状態、高抵抗状態が切り替えられるデバイスであればよく、例えば、IGBT、バイポーラトランジスタといったデバイスを用いてもよい。スイッチング素子1a、1bの材料としては、広く用いられているSiの他に、SiC、GaN、ダイヤモンドなどのワイドバンドギャップ半導体を用いてもよい。

【0020】

第1のゲート駆動部としてのゲート駆動回路2aは、スイッチング素子1aのゲート(G)-ソース(S)間に電圧印加できるように電気的に接続し、絶縁回路2gを介して入力された駆動信号に基づき、スイッチング素子1aにゲート電圧を印加する。同様に、第2のゲート駆動部としてのゲート駆動回路2bは、絶縁回路2hを介して入力された駆動信号に基づき、スイッチング素子1bにゲート電圧を印加する。

【0021】

この発明の実施の形態1による電力変換装置では、図1に示すように、ゲート駆動回路2aとゲート駆動回路2bとの間にインピーダンス素子2eが設けられている。インピーダンス素子2eは、正極側の一端2e3がゲート駆動回路2aの接続端26aと接続され

10

20

30

40

50

ており、負極側の他端 2 e 1 がゲート駆動回路 2 b の接続端 2 6 b と接続されている。

【0022】

検出部 2 f は、接続端 2 6 b と接続するインピーダンス素子 2 e の一端 2 e 1 と、中間部の接続点 2 e 2 とに接続し、インピーダンス素子 2 e の電圧を検出する。

【0023】

出力端子 4 の電圧の変化に伴ってゲート駆動回路 2 a とゲート駆動回路 2 b の間の電圧が変化すると、インピーダンス素子 2 e の両端にかかる電圧が変化する。このインピーダンス素子 2 e の電圧を検出部 2 f が検出することにより、出力端子 4 の電位を検知できる。なお、図 1 では、検出部 2 f はインピーダンス素子 2 e の分圧を検出する例を示すが、検出部 2 f の入力耐圧が高ければ分圧は不要である。検出部 2 f をインピーダンス素子 2 e の両端に接続し、検出部 2 f はインピーダンス素子 2 e の両端にかかる電圧を検出する構成とすればよい。 10

【0024】

図 1 に示す構成においては、検出部 2 f は絶縁回路を内蔵している。検出部 2 f は、絶縁回路を介して制御部 3 に接続され、検出部 2 f から制御部 3 に出力端子 4 の電位を表す出力電圧信号が入力される。なお、図 1 では矢印付きの線を信号線、矢印無しの線を電気的配線として図示している。

【0025】

制御部 3 は、補正回路としてのデッドタイム補正回路 3 a、第 1 の付加回路としてのデッドタイム付加回路 3 b、および第 2 の付加回路としてのデッドタイム付加回路 3 c により構成される。デッドタイム補正回路 3 a は、電力変換主回路 1 の出力電圧指令値である PWM 信号を受け、検出部 2 f から検出された出力電圧信号に基づいて、デッドタイム補正を行う。 20

【0026】

デッドタイム付加回路 3 b は、スイッチング素子 1 a の駆動信号に対してデッドタイムを付加してゲート駆動回路 2 a に駆動信号を出力する。デッドタイム付加回路 3 c は、反転論理部 3 d により反転したスイッチング素子 1 b の駆動信号に対してデッドタイムを付加してゲート駆動回路 2 b に駆動信号を出力する。

【0027】

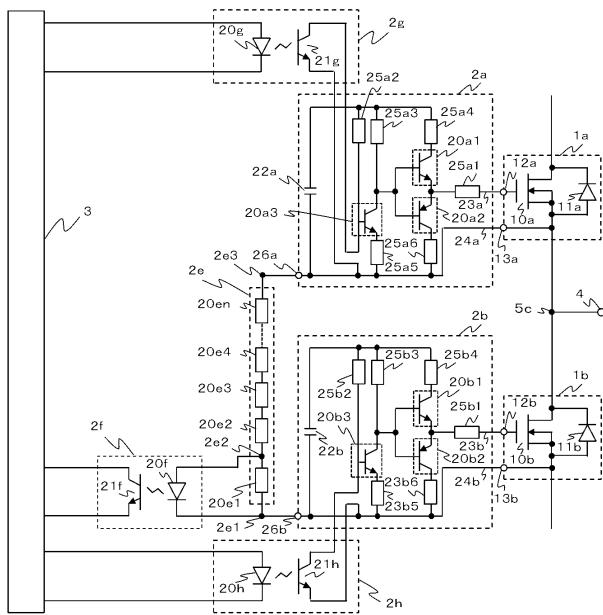

次に、図 2 を参照して、出力端子 4 から出力される電圧の検出方法の詳細を示す。図 2 は、この発明の実施の形態 1 による電力変換装置の回路図であり、スイッチング素子 1 a、スイッチング素子 1 b、ゲート駆動回路 2 a、ゲート駆動回路 2 b、インピーダンス素子 2 e、および周辺の部品の回路を示す。 30

【0028】

制御部 3 からのオン指令信号およびオフ指令信号は、制御信号絶縁部である絶縁回路 2 g、2 h を介してゲート駆動回路 2 a およびゲート駆動回路 2 b に伝わる。制御部 3 は、電力変換装置の通常動作中はゲート駆動回路 2 a およびゲート駆動回路 2 b に対して、一方にオフ指令でもう一方にオン指令の信号を出すこともある。双方にオフ指令信号を出すことがある。制御部 3 は、電力変換装置の通常動作中はゲート駆動回路 2 a およびゲート駆動回路 2 b に対して、双方にオン指令の信号を数十マイクロ秒以上出すことはない。 40

【0029】

制御部 3 からのオン指令信号が、フォトカプラで構成される絶縁回路 2 g、2 h に入力されるとフォトカプラの 1 次側の発光ダイオード 2 0 g、2 0 h がそれぞれ点灯する。すると、フォトカプラの 2 次側のフォトトランジスタ 2 1 g、2 1 h がそれぞれ導通状態になる。

【0030】

ゲート駆動回路 2 a およびゲート駆動回路 2 b の各部の電位が変化し、結局、ゲート駆動回路 2 a およびゲート駆動回路 2 b のオン用トランジスタ 2 0 a 1、2 0 b 1 は導通状態に、オフ用トランジスタ 2 0 a 2、2 0 b 2 は非導通状態になる。

【0031】

10

20

30

40

50

オン用コンデンサ 22a、22b に蓄えられた電荷は、それぞれオン用コンデンサ 22a、22b の各正極から、それぞれオン用トランジスタ 20a1、20b1、ゲート信号線 23a、23b、スイッチング素子 1a、1b の制御用ゲート端子 12a、12b、制御用ソース端子 13a、13b、ソース信号線 24a、24b、オン用コンデンサ 22a、22b の各負極への経路を通り、スイッチング素子 1a およびスイッチング素子 1b に供給される。

【0032】

スイッチング素子 1a の制御用ゲート端子 12a と制御用ソース端子 13a の間、およびスイッチング素子 1b の制御用ゲート端子 12b と制御用ソース端子 13b の間には正の電圧がかかり、スイッチング素子 1a およびスイッチング素子 1b は導通状態になる。

10

【0033】

一方、制御部 3 からのオフ指令信号が絶縁回路 2g、2h に入力されると、フォトカプラの 1 次側の 20g、20h がそれぞれ消灯する。すると、フォトカプラの 2 次側のフォトトランジスタ 21g、21h がそれぞれ非導通状態になる。

【0034】

ゲート駆動回路 2a およびゲート駆動回路 2b の各部の電位が変化し、結局、ゲート駆動回路 2a およびゲート駆動回路 2b のオン用トランジスタ 20a1、20b1 が非導通状態に、オフ用トランジスタ 20a2、20b2 は導通状態になる。

【0035】

スイッチング素子 1a およびスイッチング素子 1b の制御用ゲートに蓄えられた電荷は、それぞれゲート信号線 23a、23b、ゲート抵抗 25a1、25b1、オフ用トランジスタ 20a2、20b2、ソース信号線 24a、24b、制御用ソース端子 13a、13b の各経路を通り、スイッチング素子 1a およびスイッチング素子 1b から引き抜かれる。

20

【0036】

スイッチング素子 1a の制御用ゲート端子 12a と制御用ソース端子 13a の間、およびスイッチング素子 1b の制御用ゲート端子 12b と制御用ソース端子 13b の間は同電位となり、スイッチング素子 1a およびスイッチング素子 1b は非導通状態になる。

【0037】

このように、ゲート駆動回路 2a およびゲート駆動回路 2b の構成から明らかのように、スイッチング素子 1a およびスイッチング素子 1b の各ソース電位とゲート駆動回路 2a およびゲート駆動回路 2b のオン用コンデンサ 22a、22b の負極の電位はそれぞれ一致する。

30

【0038】

ここで、正極側のスイッチング素子 1a のソース電位は、電力変換主回路 1 の出力電位に一致する。よって、ゲート駆動回路 2a のオン用コンデンサ 22a の負極の電位は、電力変換主回路 1 の出力の電位に一致する。負極側のスイッチング素子 1b のソース電位は電力変換主回路 1 の負極の電位に一致する。よって、ゲート駆動回路 2b のオン用コンデンサ 22b の負極の電位は、電力変換主回路 1 の負極の電位に一致する。

【0039】

40

また、ゲート駆動回路 2a のオン用コンデンサの負極の電位は、ゲート駆動回路 2a の接続端 26a での電位に一致する。ゲート駆動回路 2b のオン用コンデンサ 22b の負極の電位は、ゲート駆動回路 2b の接続端 26b での電位と一致する。

【0040】

インピーダンス素子 2e は、ゲート駆動回路 2a とゲート駆動回路 2b との間で電気的に接続されている。よって、インピーダンス素子 2e の正極側の一端である 2e3 の電位は電力変換主回路 1 の出力電位に一致する。インピーダンス素子 2e の負極側の一端である 2e1 の電位は電力変換主回路 1 の負極電位に一致する。検出部 2f は、インピーダンス素子 2e にかかる電圧を検出することで、電力変換主回路 1 の出力端子 4 から出力される電圧を電力変換主回路 1 の負極を基準電圧にして検出することができる。

50

## 【0041】

負極電位を基準とした電力変換主回路の出力電圧値の一例としては、電気鉄道用途では750V、1500V、3000V程度、FA機器用途では300V、600Vである。車載用機器用途では48V～750V程度まで様々である。いずれにせよインピーダンス素子2eにかかる電圧は電磁ノイズよりも十分に大きい。このように、信号レベルの低いゲート電圧の特徴を監視する方式のものとは異なり、本発明によれば検出部2fは誤動作することなく電力変換主回路の出力電圧を検出することができる。また、検出部2fからの信号に基づいて制御部により第1のゲート駆動部および第2のゲート駆動部を制御することで、誤動作することなくデッドタイムを補償することができる。

## 【0042】

10

以上のように、この発明の実施の形態1における電力変換装置では、寄生インダクタンスの削減や発生電力損失の冷却のために部品が複雑に入り組んでいる電力変換主回路や電力変換主回路周辺ではなく、ゲート駆動回路周辺に電力変換主回路の出力電位を検出するためのインピーダンス素子2eおよび検出部2fを設けるようにしたので、高度な技術を要することなく取り付け作業を行うことができる。このように、製造が容易でありながら、電力変換主回路の出力電圧を検出することができる。さらには、製造が容易でありながら、検出部2fからの信号に基づいて制御部により第1のゲート駆動部および第2のゲート駆動部を制御することでデッドタイムを補償することができる。

## 【0043】

20

なお、この実施の形態1においては、図2に示すインピーダンス素子2eの接続点は、インピーダンス素子2eの負極側である一端2e1が、ゲート駆動回路2bの接続端26bに接続し、正極側である他端2e3は、ゲート駆動回路2aの接続端26aに接続するとした。接続端26bの電位はゲート駆動回路2bのオン用コンデンサ22bの負極の電位に一致し、接続端26aの電位はゲート駆動回路2aのオン用コンデンサ22aの負極の電位に一致するとしたが、これに限るものではない。

## 【0044】

接続端26aの電位がゲート駆動回路2aのオン用コンデンサ22aの正極の電位と一致するようにしてもよい。オン用コンデンサ22aの正極は、オン用コンデンサ22aの負極よりもオン用コンデンサ22aの充電電圧だけ高い電位にある。オン用コンデンサ22aの充電電圧は安定していることから好都合である。オン用コンデンサ22aの充電電圧は典型的には10Vから20Vの間にある。オン用コンデンサ22aの負極の電位は電力変換主回路1の出力の電位に一致することは先に述べた通りだが、接続端26aの電位はオン用コンデンサ22aの充電電圧だけ電力変換主回路1の出力の電位からずれることになる。インピーダンス素子2eにかかる電圧がオン用コンデンサ22aの充電電圧だけずれるものの、検出部2fがずれを考慮してインピーダンス素子2eの電圧を検出すれば本発明の効果を得られる。

30

## 【0045】

同様に、接続端26aの電位がゲート駆動回路2aのゲート信号線23aの電位と一致するようにしてもよい。接続端26aの電位がゲート駆動回路2aのトランジスタ20a1、あるいはトランジスタ20a2の端子の電位と一致するようにしてもよい。このように、接続端26aの電位をゲート駆動回路2aの任意の電位と一致するようにしてもよい。いずれの場合も、接続端26aの電位は電力変換主回路1の出力の電位からずれることになる。インピーダンス素子2eにかかる電圧がずれるものの、検出部2fが電圧のずれを考慮してインピーダンス素子2eの電圧を検出すれば本発明の効果を得られる。

40

## 【0046】

負極電位を基準とした電力変換主回路の出力電圧が大きく、例えば300V以上の場合であれば、インピーダンス素子2eにかかる電圧がオン用コンデンサ22aの充電電圧だけずれるものの、ずれが小さいため、ずれを許容できる場合がある。この場合には検出部2fは特にずれを考慮することなく、インピーダンス素子2eの電圧を検出すればよい。

## 【0047】

50

あるいは、電力変換主回路のスイッチング素子の電位状態（ON / OFF 状態）を単に検出したい場合には、数百Vから数千Vの電位差に対して閾値を設定すればよく、数十V程度の誤差電圧の影響を考慮せずとも主回路であるスイッチング素子の電位状態（ON / OFF 状態）を検出できる。電力変換主回路のスイッチング素子の電位状態（ON / OFF 状態）を検出できればデッドタイム補償を行うことができる。

#### 【0048】

なお、図2に示すように、ゲート駆動回路2aの中には、正極側のスイッチング素子1aのドレン端子（IGBTであればコレクタ端子）と同電位の配線は存在しないが、ゲート駆動回路の構成によってはドレン端子と同電位の配線が存在する場合がある。もし、接続端26aをドレン端子と同電位の配線に設けると、接続端26aの電位と電力変換主回路1の出力の電位とのずれが大きくなってしまう。検出部2fが電位のずれを考慮してインピーダンス素子2eの電圧を検出することが困難となるため、避けることが望ましい。

10

#### 【0049】

接続端26bについても同様である。接続端26bの電位がゲート駆動回路2bのオン用コンデンサ22bの正極の電位と一致するようにしてもよい。接続端26aの電位をゲート駆動回路2bの任意の電位と一致するようにしてもよい。いずれの場合も、接続端26bの電位は電力変換主回路1の負極の電位からずれることになる。インピーダンス素子2eにかかる電圧がずれるものの、検出部2fが電圧のずれを考慮してインピーダンス素子2eの電圧を検出すれば本発明の効果を得られる。

20

#### 【0050】

特に、トランジスタ素子に、SiC、GaN、ダイヤモンドといったSiと較べてバンドギャップが広い、いわゆるワイドバンドギャップ半導体材料を用い、高耐圧および高温動作が可能なスイッチング素子を用いて小型化を図る場合に、本発明は効果的である。電力変換主回路と電力変換主回路周辺の部品が複雑に入り組むが、本発明では、電力変換主回路の出力電位を検出するためのインピーダンス素子2eおよび検出部2fをゲート駆動回路周辺に設けるようにしたので、高度な技術を要することなく取り付け作業を行うことができる。このように、製造が容易でありながら電力変換主回路の出力電圧を検出することができる。さらには、製造が容易でありながら、検出部2fからの信号に基づいて制御部により第1のゲート駆動部および第2のゲート駆動部を制御することでデッドタイムを補償することができる。

30

#### 【0051】

この実施の形態1において、インピーダンス素子2eは、図2に示すように、2以上直列接続した抵抗20e1、20e2、…20enにより構成される。制御部3の電位がゲート駆動回路2aよりもゲート駆動回路2bの電位に近い場合は、2以上直列接続した抵抗20e1、20e2、…20enのうち、一端がゲート駆動回路2bの接続端26bに接続されている抵抗20e1の両端2e1、2e2に、検出部2fを接続することが望ましい。

#### 【0052】

なお、制御部3の電位がゲート駆動回路2bよりもゲート駆動回路2aの電位に近い場合は、2以上直列接続した抵抗20e1、20e2、…20enのうち、一端がゲート駆動回路2aの接続端26aに接続されている抵抗20enの両端に、検出部2fが接続することが望ましい。

40

#### 【0053】

このように、制御部3とゲート駆動回路2aとゲート駆動回路2bの電位の関係に応じて検出部2fが接続される抵抗20e1（または抵抗20en）を変更することで、検出部fに絶縁耐圧の低いフォトカプラを用いることができ、絶縁回路としても機能する。

#### 【0054】

このようなインピーダンス素子2eと検出部2fの構成においては、出力端子4の電位が高電位状態にある場合、インピーダンス素子2eの両端には高電圧がかかり、フォトカ

50

プラからなる検出部 2 f が接続された抵抗 2 0 e 1 ( または抵抗 2 0 e n ) には、分圧された電圧がかかる。フォトカプラからなる検出部 2 f の絶縁電圧に応じてインピーダンス素子 2 e を構成する抵抗 2 0 e 1 、 2 0 e 2 、 · · 2 0 e n の直列数を調整することが望ましい。

【 0 0 5 5 】

フォトカプラからなる検出部 ( 絶縁回路 ) 2 f においては、 1 次側は発光ダイオード 2 0 f で構成されており、インピーダンス素子 2 e の端部の抵抗 2 0 e 1 ( または抵抗 2 0 e n ) に接続されている。

【 0 0 5 6 】

検出部 2 f としてのフォトカプラの 1 次側に電圧がかかると、フォトカプラの 1 次側である発光ダイオード 2 0 f が点灯し、フォトカプラの 2 次側であるフォトトランジスタ 2 1 f が導通状態となる。 10

【 0 0 5 7 】

フォトカプラの 2 次側であるフォトトランジスタ 2 1 f が導通状態になったことにより、制御部 3 は、電力変換主回路の負極の電位を基準にして出力端子 4 の電位が高電位状態にあることを検知する。

【 0 0 5 8 】

一方、電力変換主回路の負極の電位を基準にして出力端子 4 の電位が低くなり電位が零になった場合、インピーダンス素子 2 e の両端には電圧がかからないため、フォトカプラからなる検出部 2 f が接続された抵抗にも電圧がかからない。 20

【 0 0 5 9 】

検出部 2 f としてのフォトカプラの 1 次側に電圧がかからないことから、フォトカプラの 2 次側である発光ダイオード 2 0 f が消灯し、フォトカプラの 2 次側であるフォトトランジスタ 2 1 f が非導通状態となる。

【 0 0 6 0 】

フォトカプラの 2 次側であるフォトトランジスタ 2 1 f が非導通状態になったことにより、制御部 3 は、電力変換主回路の負極の電位を基準にして出力端子 4 の電位が零であることを検知する。

【 0 0 6 1 】

上述のように、この発明の実施の形態 1 では、インピーダンス素子 2 e を 2 以上直列接続した抵抗 ( 2 0 e 1 、 2 0 e 2 、 · · 2 0 e n ) により電圧を分圧することで、出力電圧を検知できるだけでなく、検出部としてフォトカプラを用いることにより、絶縁回路として制御部を保護できる。なお、この発明の実施の形態 1 では、検出部 2 f はインピーダンス素子 2 e の分圧を検出する例を示したが、検出部 2 f の入力耐圧が高ければ分圧は不要である。検出部 2 f をインピーダンス素子 2 e の両端に接続し、検出部 2 f はインピーダンス素子 2 e の両端にかかる電圧を検出する構成とすればよい。この場合には、インピーダンス素子 2 e を 2 以上直列接続した抵抗で構成してもよいが 1 個の抵抗で構成することもできる。 30

【 0 0 6 2 】

さらに、従来技術のように出力端子と直流母線の低圧側との間にセンサーを設ける場合は、ゲート駆動回路の電源とは別にセンサーの電源が必要であるのに対し、上記構成では検出部の電源をゲート駆動回路の電源より得ることができ、さらに小型かつ簡素な電力変換装置を得ることができる。 40

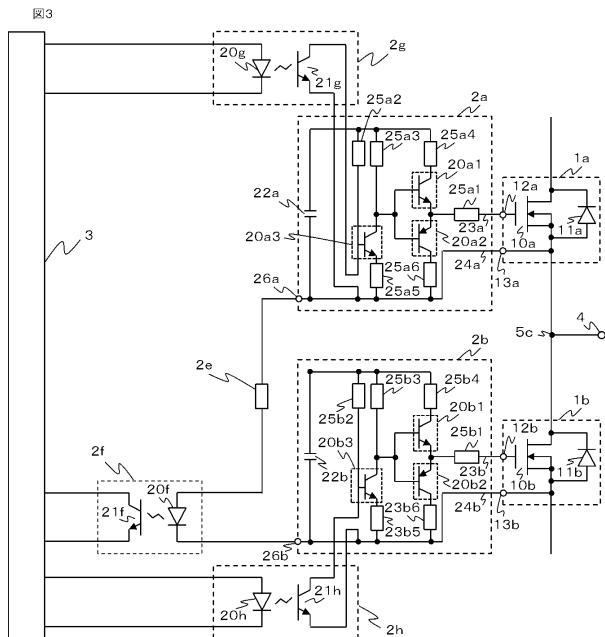

【 0 0 6 3 】

上記においては、検出部 2 f がインピーダンス素子 2 e の電圧を検出する構成にて説明したが、検出部がインピーダンス素子に通流する電流を検出する構成としてもよい。図 3 を用いて説明する。

【 0 0 6 4 】

図 3 の構成では、検出部 2 f であるフォトカプラの 1 次側が、ゲート駆動回路 2 a の接続端 2 6 a に一端を接続するインピーダンス素子 2 e の他端と、ゲート駆動回路 2 b の接

続端 2 6 b との間に、直列で挿入されている。図 3 ではインピーダンス素子 2 e は 1 個の抵抗で構成されているが、2 以上直列接続した抵抗で構成してもよい。その他の構成は図 2 と同様であり、その詳細な説明は省略する。

【 0 0 6 5 】

電力変換主回路の負極の電位を基準にして出力端子 4 の電位が高電位状態にある場合、インピーダンス素子 2 e の両端には高電圧がかかり、よって電流が通流する。フォトカプラの 1 次側に電流が通流するため、1 次側の発光ダイオード 2 0 f が点灯し、フォトカプラの 2 次側のフォトトランジスタ 2 1 f が導通状態となり、制御部 3 は、出力端子 4 の電位が高電位状態にあることを検知する。

【 0 0 6 6 】

一方、電力変換主回路の負極の電位を基準にして出力端子 4 の電位が低くなり零になつた場合、インピーダンス素子 2 e の両端には電圧がかからないため、よって電流が通流しない。フォトカプラの 1 次側に電流が通流しないため、1 次側の発光ダイオード 2 0 f が消灯し、フォトカプラ 2 次側のフォトトランジスタ 2 1 f が非導通状態となり、制御部 3 は、出力端子 4 の電位が零であることを検知する。

【 0 0 6 7 】

このように、検出部がインピーダンス素子に通流する電流を検出する構成であつても、検出部 2 f がインピーダンス素子 2 e の電圧を検出する構成と同様の効果を得ることができる。

【 0 0 6 8 】

なお、検出部 2 f ではフォトカプラを用いたが、フォトカプラ以外にもホール素子を用いてインピーダンス素子に流れる電流を検出する構成としてもよい。また、シャント抵抗を用いてインピーダンス素子に流れる電流を検出する構成としてもよい。いずれにおいても、フォトカプラを用いた場合と同様の効果を得ることができる。

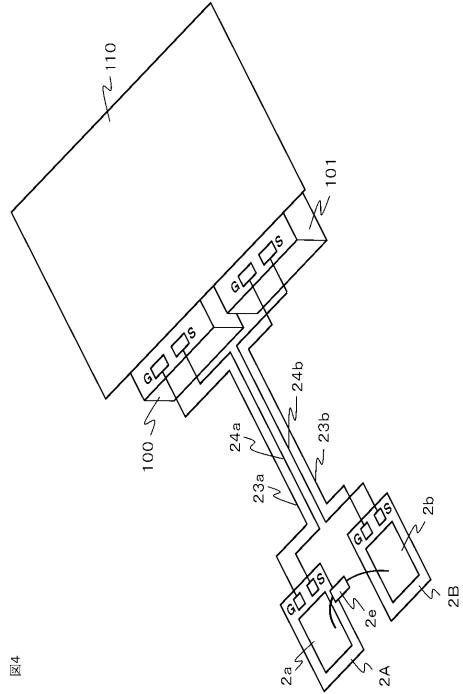

【 0 0 6 9 】

図 4 は、この発明の実施の形態 1 による電力変換装置の配置図であり、スイッチング素子 1 a からなるモジュール 1 0 0 、スイッチング素子 1 b からなるモジュール 1 0 1 、ゲート駆動回路 2 a 、ゲート駆動回路 2 b 、インピーダンス素子 2 e 、および周辺の部品の配置を示す。

【 0 0 7 0 】

図 4 に示すように、スイッチング素子 1 a およびスイッチング素子 1 b は、それぞれ 1 つの筐体に納められた、いわゆる 1 in 1 モジュールとなっている。モジュールは 1 個のスイッチング半導体チップ、または 2 個以上のスイッチング半導体チップを内蔵している。スイッチング素子 1 a からなるモジュール 1 0 0 とスイッチング素子 1 b からなるモジュール 1 0 1 は、ブスバー 1 1 0 にとりつけられており、電力変換主回路 1 を構成している。なお、図 4 では、スイッチング素子を 1 個のモジュールにより構成したが、これに限るものではない。2 個以上のモジュールを電気的に並列接続することによりスイッチング素子を構成してもよい。

【 0 0 7 1 】

ゲート駆動回路 2 a およびゲート駆動回路 2 b は、それぞれ 1 枚のゲート駆動回路基板 2 a 、 2 b に配設されている。モジュール 1 0 0 およびモジュール 1 0 1 は、それぞれゲート駆動回路 2 a 、ゲート駆動回路 2 b とゲート信号線 2 3 a 、 2 3 b 、ソース信号線 2 4 a 、 2 4 b で結ばれている。

【 0 0 7 2 】

つまり、スイッチング素子 1 a からなるモジュール 1 0 0 は、ゲート駆動回路 2 a のゲート・ソース間電圧がそれぞれゲート信号線 2 3 a 、ソース信号線 2 4 a で接続され、伝達される。同様に、スイッチング素子 1 b からなるモジュール 1 0 1 は、ゲート駆動回路 2 b のゲート・ソース間電圧がそれぞれゲート信号線 2 3 b 、ソース信号線 2 4 b で接続され、伝達される。

【 0 0 7 3 】

10

20

30

40

50

従来より、スイッチング素子のスイッチング動作に伴って、スイッチング素子の周辺は電磁ノイズが大きいことが知られている。電磁ノイズにより、ゲート信号線、ソース信号線の伝達信号が変形し、スイッチング素子が誤動作する恐れがある。

【0074】

これに対しては、ゲート信号線、ソース信号線を隣接して配置し、ゲート信号線とソース信号線が作るループを小さくすることが行われている。電磁ノイズの影響を抑え、ゲート駆動回路のゲート・ソース間電圧が変形することなくスイッチング素子のゲート・ソース間に伝達される。

【0075】

図4の構成においても、ゲート信号線23aとソース信号線24a、およびゲート信号線23bとソース信号線24bは、隣接して配置されている。図4の構成の特徴は、ソース信号線24aとソース信号線24bも隣接して配置されていることである。すなわち、ソース信号線24aとソース信号線24bとの距離は、ゲート信号線23aとソース信号線24aとの距離およびゲート信号線23bとソース信号線24bとの距離のいずれかと同じかそれ未満である。このように、ソース信号線24aとソース信号線24bが作るループを小さくしていることである。

【0076】

この構成により、電磁ノイズの影響を抑え、出力端子の電位が変形することなくインピーダンス素子に伝達される。制御部は出力端子の電位を精度よく検知できる。

【0077】

図4の構成においては、インピーダンス素子2eは、ゲート駆動回路2aとゲート駆動回路2bとの間の空間において配線して接続している。インピーダンス素子2eは、ゲート駆動回路2aとゲート駆動回路2bとの空間絶縁距離を考慮して配置すればよい。

【0078】

一般に、絶縁を確保するにあたっては、空間絶縁距離の方が沿面絶縁距離よりも短くて済む。図4の構成によれば、インピーダンス素子の配線長を短く抑えることができる。

【0079】

図5は、この発明の実施の形態1による電力変換装置の他の配置例を示す図である。図5の構成では、スイッチング素子1aとスイッチング素子1bが1枚のゲート駆動回路基板2で構成されている。インピーダンス素子2eは、ゲート駆動回路基板2の上に設置されており、回路パターンにより結線されている。

【0080】

この構成であれば、ゲート駆動回路基板の製造段階でインピーダンス素子の取り付け作業を完了することができる。インピーダンス素子の取り付け工程を別に設ける必要がないため、低コスト化を図ることができる。さらに、この構成においても、デッドタイムを補償することができる。

【0081】

実施の形態2.

実施の形態1では、検出部2fにフォトカプラを用いて絶縁回路と兼用したが、実施の形態2では、絶縁回路と検出部は別とし、検出部としてコンパレータを用いた場合について説明する。

【0082】

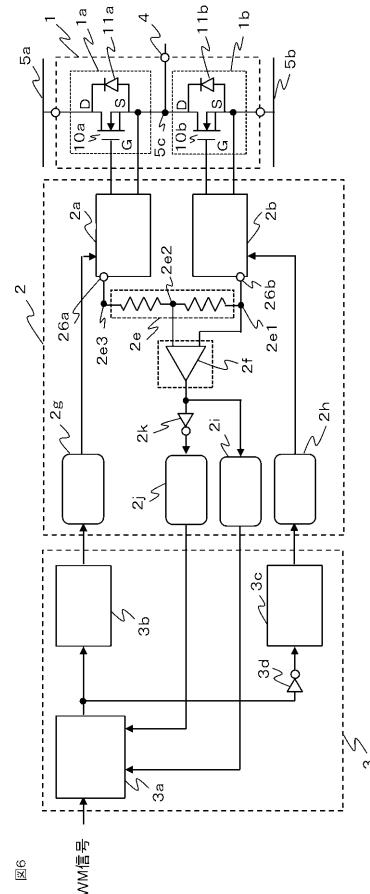

図6は、この発明の実施の形態2による電力変換装置を示す構成図であり、電力変換主回路1、ゲート駆動回路基板2、制御部3、および周辺部品の構成を図示している。なお、図6では矢印付きの線を信号線、矢印無しの線を電気的配線として図示している。

【0083】

図6に示すように、ゲート駆動回路2aとゲート駆動回路2bとの間にインピーダンス素子2eが設けられている。インピーダンス素子2eは、正極側の一端2e3がゲート駆動回路2aの接続端26aと接続されており、負極側の他端2e1がゲート駆動回路2bの接続端26bと接続されている。インピーダンス素子2eには、電圧を検出する検出部

10

20

30

40

50

2 f としてコンパレータが接続されている。コンパレータからなる検出部 2 f により検出した出力電圧信号を、絶縁回路 2 i を介して制御部 3 のデッドタイム補正回路 3 a に出力し、また、反転論理部 2 k により反転した反転出力電圧信号も、絶縁回路 2 j を介してデッドタイム補正回路 3 a に出力するように構成されている。

【0084】

図7は、この発明の実施の形態2による電力変換装置の回路図であり、スイッチング素子1a、スイッチング素子1b、ゲート駆動回路2a、ゲート駆動回路2b、インピーダンス素子2e、および周辺の部品の回路を示す。

【0085】

図7に示すように、ゲート駆動回路2aおよびゲート駆動回路2bには、それぞれオン用コンデンサ22a、22bとオフ用コンデンサ27a、27bがあり、オン用コンデンサ22a、22bの負極とオフ用コンデンサ27a、27bの正極が直列接続されている。オン用コンデンサ22a、22bとオフ用コンデンサ27a、27bの接続点は、それぞれソース信号線24a、24bを介して、スイッチング素子1aおよびスイッチング素子1bの各制御用ソース端子13a、13bに接続されている。

【0086】

その他の構成については図1および図2と同様であり、その説明を省略する。結局、ゲート駆動回路2aの接続端26aの電位はオン用コンデンサ22aの負極の電位に一致し、さらには電力変換主回路1の出力の電位に一致する。ゲート駆動回路2bの接続端26bの電位はオン用コンデンサ22bの負極の電位に一致し、さらには電力変換主回路1の負極の電位に一致する。

【0087】

次に、電力変換主回路の出力端子4から出力される電圧の検出方法の詳細について、図7を用いて説明する。図7に示すように、制御部3からのオン指令信号は、制御信号絶縁部である絶縁回路2g、2hを介してゲート駆動回路2aおよびゲート駆動回路2bに伝わる。絶縁回路2g、2hは、フォトカプラ部品により構成される。

【0088】

制御部3からのオン指令信号が、絶縁回路2g、2hに入力されるとフォトカプラの1次側の発光ダイオード20g、20hがそれぞれ点灯する。すると、フォトカプラの2次側のフォトトランジスタ21g、21hがそれぞれ導通状態になる。

【0089】

ゲート駆動回路2aおよびゲート駆動回路2bの各部の電位が変化し、結局、ゲート駆動回路2aおよびゲート駆動回路2bのオン用トランジスタ20a1、20b1は導通状態に、オフ用トランジスタ20a2、20b2は非導通状態になる。

【0090】

オン用コンデンサ22a、22bに蓄えられた電荷は、それぞれオン用コンデンサ22a、22bの各正極から、それぞれオン用トランジスタ20a1、20b1、ゲート信号線23a、23b、スイッチング素子1a、1bの制御用ゲート端子12a、12b、制御用ソース端子13a、13b、ソース信号線24a、24b、オン用コンデンサ22a、22bの各負極への経路を通り、スイッチング素子1aおよびスイッチング素子1bに供給される。

【0091】

スイッチング素子1aおよびスイッチング素子1bの制御用ゲート端子12a、12bと制御用ソース端子13a、13bには正の電圧がかかり、スイッチング素子1aおよびスイッチング素子1bは導通状態になる。

【0092】

一方、制御部3からのオフ指令信号が絶縁回路2g、2hに入力されると、フォトカプラの1次側の発光ダイオード20g、20hがそれぞれ消灯する。すると、フォトカプラの2次側のフォトトランジスタ21g、21hがそれぞれ非導通状態になる。

【0093】

10

20

30

40

50

ゲート駆動回路 2 a およびゲート駆動回路 2 b の各部の電位が変化し、結局、ゲート駆動回路 2 a およびゲート駆動回路 2 b のオン用トランジスタ 20 a 1、20 b 1 が非導通状態に、オフ用トランジスタ 20 a 2、20 b 2 は導通状態になる。

【0094】

オフ用コンデンサ 27 a、27 b に蓄えられた電荷が、オフ用コンデンサ 27 a、27 b の各正極から、ソース信号線 24 a、24 b、スイッチング素子 1 a、1 b の制御用ソース端子 13 a、13 b、スイッチング素子 1 a、1 b の制御用ゲート端子 12 a、12 b、ゲート信号線 23 a、23 b、オフ用トランジスタ 20 a 2、20 b 2、オフ用コンデンサ 27 a、27 b の各負極への経路を通り、スイッチング素子 1 a およびスイッチング素子 1 b にそれぞれ供給される。

10

【0095】

スイッチング素子 1 a およびスイッチング素子 1 b の制御用ゲート端子 12 a、12 b と制御用ソース端子 13 a、13 b には、それぞれ負の電圧がかかり、スイッチング素子 1 a およびスイッチング素子 1 b は非導通状態となる。

【0096】

このように、ゲート駆動回路 2 a およびゲート駆動回路 2 b の構成から明らかのように、スイッチング素子 1 a およびスイッチング素子 1 b の各ソース電位とゲート駆動回路 2 a およびゲート駆動回路 2 b のオン用コンデンサ 22 a、22 b の負極の電位はそれぞれ一致する。

【0097】

20

ここで、正極側のスイッチング素子 1 a のソース電位は、電力変換主回路 1 の出力電位に一致する。よって、ゲート駆動回路 2 a のオン用コンデンサ 22 a の負極の電位は、電力変換主回路 1 の出力の電位に一致する。負極側のスイッチング素子 1 b のソース電位は、電力変換主回路 1 の負極電位に一致する。よって、ゲート駆動回路 2 b のオン用コンデンサ 22 b の負極の電位は、電力変換主回路 1 の負極電位に一致する。

【0098】

また、ゲート駆動回路 2 a のオン用コンデンサの負極の電位は、ゲート駆動回路 2 a の接続端 26 a での電位に一致する。ゲート駆動回路 2 b のオン用コンデンサ 22 b の負極の電位は、ゲート駆動回路 2 b の接続端 26 b での電位と一致する。

【0099】

30

ゲート駆動回路 2 a とゲート駆動回路 2 b との間にインピーダンス素子 2 e が設けられている。インピーダンス素子 2 e は、正極側の一端 2 e 3 がゲート駆動回路 2 a の接続端 26 a と接続されており、負極側の他端 2 e 1 がゲート駆動回路 2 b の接続端 26 b と接続されている。検出部 2 f は、インピーダンス素子 2 e での電圧を検出することで、電力変換主回路 1 の出力端子 4 から出力される電圧を検出することができる。

【0100】

実施の形態 2 においては、図 7 に示すように、検出部 2 f はコンパレータにより構成される。インピーダンス素子 2 e は、2 以上直列接続した抵抗 (20 e 1、20 e 2、… 20 e n) により構成される。検出部 2 f の入力電圧仕様に応じてインピーダンス素子 2 e を構成する抵抗 20 e 1、20 e 2、… 20 e n の直列数を調整することが望ましい。なお、図 7 では、検出部 2 f はインピーダンス素子 2 e の分圧を検出する例を示すが、検出部 2 f の入力耐圧が高ければ分圧は不要である。検出部 2 f をインピーダンス素子 2 e の両端に接続し、検出部 2 f はインピーダンス素子 2 e の両端にかかる電圧を検出する構成とすればよい。この場合には、インピーダンス素子 2 e を 2 以上直列接続した抵抗で構成してもよいが 1 個の抵抗で構成することもできる。

40

【0101】

制御部 3 の電位がゲート駆動回路 2 a よりもゲート駆動回路 2 b の電位に近い場合、ゲート駆動回路 2 b の接続端 26 b に 2 以上直列接続したインピーダンス素子 2 e の一端、つまり、抵抗 20 e 1 の一端が接続され、抵抗 20 e 1 の他端に、検出部 2 f であるコンパレータの一方の入力端 2 f 1 に接続される。

50

## 【0102】

本実施例では検出部2fであるコンパレータの電源はゲート駆動回路2bの電源より得ている。オン用コンデンサ22b、オフ用コンデンサ27bを用いることにより両極電源を得ることができる。従来技術のように出力端子と直流母線の低圧側との間にセンサーを設ける場合は、ゲート駆動回路の電源とは別にセンサーの電源が必要であるのに対し、上記構成では検出部の電源をゲート駆動回路の電源より得ることができ、さらに小型かつ簡素な電力変換装置を得ることができる。

## 【0103】

検出部2fであるコンパレータの他方の入力端2f2には、ドライバ電源を抵抗分圧して得られる基準電圧が入力される。出力端子4の電位が高電位状態にある場合、インピーダンス素子2eの両端には高電圧がかかり、コンパレータが接続されている抵抗20e1にも分圧された電圧がかかる。コンパレータの他端の基準電圧を越えるのでコンパレータの出力はhigh状態となる。一方、出力端子4の電位が低くなり電位差が零になった場合、インピーダンス素子2eの両端には電圧がかからないため、コンパレータが接続された抵抗にも電圧がかからない。コンパレータの他端の基準電圧を越えないでコンパレータの出力はlow状態となる。

## 【0104】

一般に、コンパレータの入力端子は入力インピーダンスが高く、感度が高い。本実施の形態のように検出部2fとしてコンパレータを用いれば、インピーダンス素子2eを構成する抵抗の抵抗値を大きくしても検出部2fはインピーダンス素子2eの電圧を感度良く検出することができる。インピーダンス素子2eの通流電流を少なくすることができ、インピーダンス素子2eの発熱を抑えることができる。

## 【0105】

さらに、本実施の形態であれば、電力変換装置の動作時についてコンパレータの入力端子の入力電圧範囲をコンパレータの両極電源電圧値よりも内側に収めることができる。コンパレータの入力端子の入力電圧がコンパレータの両極電源電圧値に一致すると、コンパレータの内部回路が飽和し、コンパレータ動作が遅くなることがある。コンパレータの入力端子の入力電圧がコンパレータの両極電源電圧よりも外側にあると、コンパレータの内部回路の絶縁が劣化し、コンパレータが破壊することがある。本実施の形態であれば、コンパレータ動作が遅くなることはなく、コンパレータが破壊することはない。

## 【0106】

なお、この実施の形態2では、インピーダンス素子2eを2以上直列接続した抵抗または1個の抵抗により構成することができるとして説明したが、特に限定するものではない。インピーダンス素子2eを2以上直列接続したコンデンサまたは1個のコンデンサにより構成した場合でも、同様の効果を得られる。さらに、インピーダンス素子2eを2以上直列接続したダイオードまたは1個のダイオードにより構成した場合でも、同様の効果を得られる。

## 【0107】

また、この実施の形態2では、検出部2fがインピーダンス素子2eの電圧を検出する構成にて説明したが、特に限定するものではない。検出部2fがインピーダンス素子に通流する電流を検出する構成とした場合においても、同様の効果を得られる。

## 【0108】

なお、検出部2fであるコンパレータの他方の入力端2f2に入力される基準電圧の電圧値は、直流母線の電位に応じて適切に調整しておく必要がある。通常、電力変換装置に電力を供給する直流母線の電位は安定しており、前記基準電圧の電圧値の調整は一度行えば良い。本実施の形態では、ドライバ電源を抵抗分圧して調整することにより基準電圧を得ている。しかしながら、特殊な用途の電力変換装置においては、直流母線の通常時の電位が大きく変動することがある。この場合には検出部2fの閾値を生成する前記基準電圧の電圧値は、直流母線の電位によって可変となるように構成することが望ましい。

## 【0109】

10

20

30

40

50

上記の変形例として、図8に示すように、直流母線5aとゲート駆動回路2b中のオフ用コンデンサ27bの負極側の接続端とを抵抗23b7と23b8で電気的に接続し、その分圧電位を利用する電力変換装置がある。この分圧電位を前記基準電圧の電圧値として用いる。これにより、直流母線5aの通常時の電位が変動しても、それに応じて閾値電圧が変動するため検出部2fの誤検知、誤動作を防止できる。さらに、本構成であれば、落雷などで母線電圧が異常に変動して瞬時低下又は瞬時上昇した場合であっても、検出部2fの誤検知、誤動作を防止できる。

#### 【0110】

本実施の形態では図8に示すように、ゲート駆動回路2aの中には、正極側のスイッチング素子1aのドレイン端子（IGBTであればコレクタ端子）と同電位の配線は存在しないが、ゲート駆動回路の構成によっては存在する場合がある。上記図8の変形例として述べる。この場合、ゲート駆動回路2a上にある正極側のスイッチング素子1aのドレイン端子（IGBTであればコレクタ端子）と同電位の配線の電位は直流母線5aとも同電位である。したがって、上記ゲート駆動回路2a上にある同電位の配線とゲート駆動回路2b中のオフ用コンデンサ27bの負極側の接続端とを抵抗23b7と23b8で電気的に接続することで、図8と同様の効果を得ることができる。さらなる効果として、直流母線5aからの電気的な接続線を配線する必要が無く、装置の構成が容易になる。

#### 【0111】

次に、デッドタイム補正方法について説明する。

一般に、デッドタイムは、スイッチング素子や、そのゲート駆動回路の遅延時間等を考慮して、電力変換主回路の出力端子でのデッドタイムは、下記の式（1）を満たすようスイッチング信号を出力する制御部のデッドタイム付加回路により、予め設定される。

#### 【0112】

$$T_{dead^+} = T_{dead} + T_{d-on} - T_{d-off} > 0 \quad \dots \quad (1)$$

#### 【0113】

ここで、

$T_{dead}$  : 制御部にて生成されるデッドタイム

$T_{dead^+}$  : 電力変換主回路1の出力端子4でのデッドタイム

$T_{d-on}$  : オン遅延時間

$T_{d-off}$  : オフ遅延時間

（ $T_{d-on}$ 、 $T_{d-off}$ には、信号の上昇時間 $T_r$ や下降時間 $T_f$ を含む）

#### 【0114】

また、制御部から出力されたスイッチング信号は、高電圧部から低電圧部へのノイズを防止する目的や、絶縁破壊に対する安全性を確保するために、絶縁回路であるフォトカプラを介してゲート駆動回路に供給される。

#### 【0115】

フォトカプラは、入力電流により発光ダイオードが発光し、この光をフォトトランジスタで出力電流に変換している。しかしフォトトランジスタのベースキャリアのライフタイムの影響と、コレクタからベースへ負帰還がかかるミラー積分効果により、フォトトランジスタがオフからオンに変化するためにはオフ遅延時間よりも、オンからオフに変化するためにはオフ遅延時間の方が大幅に長くなる。

#### 【0116】

このことは、ルネサスエレクトロニクス株式会社のホームページに「汎用フォトカプラの応答速度」（URL：<http://japan.renesas.com/products/opto/technology/speed/index.jsp>）として記載されているとおりである。

#### 【0117】

従って、フォトトランジスタ分の遅延時間が  $T_{d-on} - T_{d-off} < 0$  であるため、式（1）において、 $T_{dead^+}$ として正の値を確保するためには、デッドタイム $T_{dead}$ として大きな値を設ける必要があった。

#### 【0118】

10

20

30

40

50

さらに、上述のような遅れ要素は負荷電流や温度条件などさまざまな要因により一定の遅れ要素ではなく、実際に補正すべきデッドタイムである  $T_{dead^+}$  は上述のような変動要因により一定値ではないことが知られている。

【0119】

従来技術のような出力端子の電位を検出してデッドタイム補正に用いる方法では、上述のような遅れ要素があっても、出力端子の電位を直接検出することで電力変換主回路の出力端子でのデッドタイム  $T_{dead^+}$  を正確に知ることができるので、精度よくデッドタイム補正を実施することができる。

【0120】

しかしながら、従来技術では示されていないが、実際に従来技術を実施する場合には、センサーの信号とカウンタの間にはフォトカプラのような絶縁回路が必要となる。この理由は上述と同様の理由である。 10

【0121】

特別な例として、電力変換主回路の低圧側に接続された直流母線の低圧側の電位と制御器のグランド（接地電位）が同電位であり、ノイズ等の問題がない場合には、センサーの信号とカウンタ間の絶縁回路は省略しても問題ない場合もあるが、ほとんどの場合は、絶縁回路を介して信号を授受するのが一般的である。

【0122】

したがって、従来技術ではフォトカプラのような絶縁回路の遅れ要素により、カウンタが検出したデッドタイムは絶縁回路のON遅延時間 - OFF遅延時間だけ誤差を持つことになる。 20

【0123】

この発明の実施の形態2による電力変換装置では、検出部2fにより検出された出力電圧信号は、絶縁回路2iを介して制御部3に出力し、また、反転論理部2kにより反転した反転出力電圧信号も、絶縁回路2jを介して制御部3に出力するように構成している。

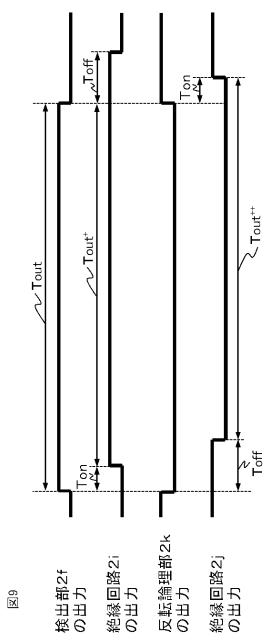

【0124】

図9に、絶縁回路2i、2jのタイムチャートを示す。通常の絶縁回路2iの検出パルス時間  $T_{out^+}$  は、式(2)で求まり、反転論理部2kを介した絶縁回路2jの検出パルス時間  $T_{out^{++}}$  は、式(3)で求まる。したがって、出力端子4の電位検出パルス時間  $T_{out}$  は、式(4)で正確に求めることができる。 30

【0125】

$$T_{out^+} = T_{out} - T_{on} + T_{off} \quad \dots (2)$$

$$T_{out^{++}} = T_{out} - T_{off} + T_{on} \quad \dots (3)$$

$$T_{out} = (T_{out^+} + T_{out^{++}}) / 2 \quad \dots (4)$$

【0126】

ここで、

$T_{out}$  : 出力端子4の電位検出パルス時間

$T_{out^+}$  : 通常の絶縁回路2iの検出パルス時間

$T_{out^{++}}$  : 反転論理部2kを介する絶縁回路2jの検出パルス時間

$T_{on}$  : 絶縁回路のオン遅延時間

$T_{off}$  : 絶縁回路のオフ遅延時間

【0127】

したがって、式(4)で求めた出力端子4の電位検出パルス時間用いてデッドタイム補正を実施することで、従来技術に比べてデッドタイム補正の精度を向上することができる。ここで、2個のフォトカプラである絶縁回路2i、2jは近接して配置することが望ましい。電気的条件、温度条件が揃うことからフォトカプラの遅れ時間が揃う効果が得られる。

【0128】

なお、絶縁回路2i、2jの遅れが十分無視できる時間であれば、反転論理部は省略してもよい。一般に、高性能な絶縁回路ほど上記信号伝達遅れ時間が短くなるが、高価にな 50

る。反転論理部を用いることで、安価な絶縁回路であっても高精度に出力端子の電位検出パルス時間  $T_{out}$  を検出でき、コスト低減にも繋がる。

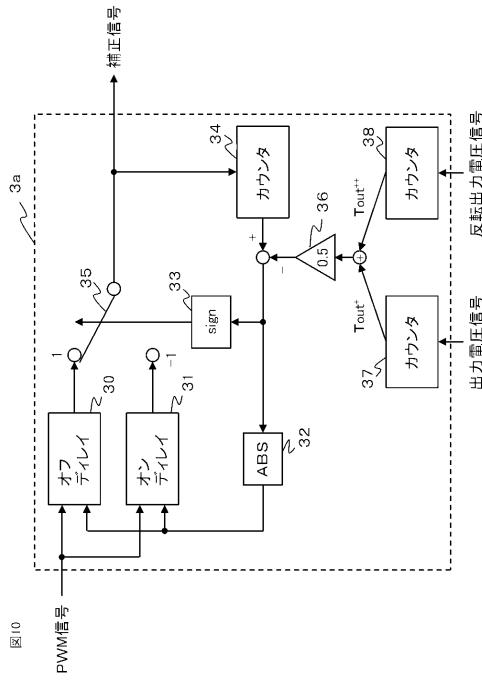

【0129】

図10に、デッドタイム補正回路3aのブロック図を示す。デッドタイム補正回路3aでは、式(4)に基づき出力端子4の電位検出パルス時間  $T_{out}$  をカウントし、補正信号のカウント値  $T_{vref^+}$  との差分から誤差電圧である電力変換主回路1の出力端子4でのデッドタイム  $T_{dead^+}$  を  $T_{vref^+} - T_{out}$  から算出する。この  $T_{dead^+}$  を次回の補正量  $T_{comp}$  とする。

【0130】

補正量  $T_{comp}$  が正值であれば、 $|T_{comp}|$  のオフディレイ、補正量  $T_{comp}$  が負値であれば、 $|T_{comp}|$  のオンディレイとなるように、PWM信号を補正する。なお、図示していないが、カウンタは入力信号の立ち上がりでカウントクリアするように構成し、補正量  $T_{comp}$  はキャリアピーカでラッチするようにしている。

【0131】

図11に、負荷電流が正の場合のデッドタイム補正の動作を示すタイムチャートを示す。また、図12に負荷電流が負の場合のデッドタイム補正の動作を示すタイムチャートを示す。

【0132】

図11および図12に示すように、補正量  $T_{comp}$  が正值であれば、 $|T_{comp}|$  のオフディレイ(図11)、補正量  $T_{comp}$  が負値であれば、 $|T_{comp}|$  のオンディレイ(図12)となるように、PWM信号を補正することで、出力電流の正負によらず出力端子電圧の遅れを同一にでき、1パルス前の補正量  $T_{comp}$  ではあるが、PWM信号のパルス時間  $T_{verf}$  と出力端子電圧のパルス時間  $T_{out}$  をほぼ同じに制御できる。

【0133】

なお、図10および図12において、デッドタイム  $T_{dead^+}$  のうち、BおよびCの部分は、主回路の電流により変化する部分である。

【0134】

以上のように、この発明の実施の形態2における電力変換装置では、検出部2fにより検出された出力電圧信号を、絶縁回路2iを介して制御部3に出力し、また、反転論理部2kにより反転した反転出力電圧信号も、絶縁回路2jを介して制御部3に出力するように構成したので、フォトカプラのような絶縁回路の遅れ要素に起因する誤差を補正することができ、デッドタイム補正の精度を向上することができる。

【0135】

さらに、上述のとおり、スイッチング素子やダイオード素子にワイドバンドギャップ半導体を用いることで、小型、低コストも実現できる。

【0136】

なお、上述の実施の形態1でも述べたように、電力変換主回路1のスイッチング素子およびダイオード素子としてはどのような素子を用いてもよいが、例えば、ワイドバンドギャップ半導体を用いることができる。ワイドバンドギャップ半導体としては、例えば、炭化珪素、窒化ガリウム系材料またはダイヤモンド等により形成されたものがある。

【0137】

このようなワイドバンドギャップ半導体によって形成されたスイッチング素子やダイオード素子は、耐電圧性が高く、許容電流密度も高いため、スイッチング素子やダイオード素子の小型化が可能であり、これら小型化されたスイッチング素子やダイオード素子を用いることにより、これらの素子を組み込んだ半導体モジュールの小型化が可能となる。

【0138】

また、ワイドバンドギャップ半導体は、耐熱性も高いため、ヒートシンクの放熱フィンの小型化や、水冷部の空冷化が可能であるので、半導体モジュールの一層の小型化が可能になる。さらに、電力損失が低いため、スイッチング素子やダイオード素子の高効率化が可能であり、延いては半導体モジュールの高効率化が可能になる。

10

20

30

40

50

## 【0139】

## 実施の形態3

実施の形態1および実施の形態2では、2レベルの電力変換回路の場合について示したが、実施の形態3では、3レベルの電力変換回路を用いた場合について説明する。

## 【0140】

図13は、この発明の実施の形態3による電力変換装置の構成図であり、電力変換主回路1、ゲート駆動回路基板2、制御部3、および周辺部品の構成を図示している。電力変換主回路1は、3レベルの電力変換回路として構成されている。電力変換主回路1の正極には高電位を供給する直流母線5aが接続されている。電力変換主回路1の負極には零電位を供給する直流母線5bが接続されている。さらに、電力変換主回路1の中間電位端子5gには中間電位を供給する直流母線が接続されている。内蔵するスイッチング素子のオン、オフを切り替えることにより、電力変換主回路1は出力端子4より3レベルの電位(高電位、中間電位、零電位)を出力する。

10

## 【0141】

この実施の形態1における電力変換主回路1は、4つのスイッチング素子1c、1d、1e、1fと、2つの中性点クランプダイオード1g、1hと、から構成される。4つのスイッチング素子1c、1d、1e、1fは、それぞれトランジスタ素子10c、10d、10e、10fとダイオード11c、11d、11e、11fとが逆並列に接続されて構成されている。

## 【0142】

20

電力変換主回路1では、正極側の第1のスイッチング部として、スイッチング素子1cとスイッチング素子1dが直列に接続され、負極側の第2のスイッチング部として、スイッチング素子1eとスイッチング素子1fが直列に接続される。この第1のスイッチング部と第2のスイッチング部は、正極側の下位電位側のスイッチング素子1dと負極側の上位電位側のスイッチング素子1eとで直列に接続される。

## 【0143】

正極側の上位電位側に位置するスイッチング素子1cと下位電位側に位置するスイッチング素子1dとの接続点5dに上位電位側の中性点クランプダイオード1gのカソードが接続される。

## 【0144】

30

中性点クランプダイオード1gのアノードは、下位電位側の中性点クランプダイオード1hのカソードに接続されると共に、直列接続された2つの中性点クランプダイオード1g、1hの接続点は、中間電位端子5gに電気的に接続される。

## 【0145】

一方、負極側の上位電位側に位置するスイッチング素子1eと下位電位側に位置するスイッチング素子1fとの接続点5eに下位電位側の中性点クランプダイオード1hのアノードが接続される。

## 【0146】

中性点クランプダイオード1hのカソードは、上述の通り、中間電位端子5gに電気的に接続される。スイッチング素子1dとスイッチング素子1eの接続点5fは、出力端子4として引き出され負荷(図示しない)に接続される。

40

## 【0147】

ゲート駆動回路基板2には、4つのゲート駆動回路21、2m、2n、2oが設けられる。ゲート駆動回路21とゲート駆動回路2mは、第1のゲート駆動部として、それぞれスイッチング素子1cとスイッチング素子1dに接続される。

## 【0148】

同様に、ゲート駆動回路2nとゲート駆動回路2oは、第2のゲート駆動部として、それぞれスイッチング素子1eとスイッチング素子1fに接続される。ゲート駆動回路21、2m、2n、2oは、それぞれをスイッチング素子1c、1d、1e、1fを駆動する。

50

## 【0149】

この発明の実施の形態3による電力変換装置では、図13に示すように、インピーダンス素子2Pの一端2p3は、正極側の下位電位側に位置するスイッチング素子1dを駆動するゲート駆動回路2mの接続端26mに接続されている。インピーダンス素子2Pの他端2p1は、負極側の下位電位側に位置するスイッチング素子1fを駆動するゲート駆動回路2oの接続端26oに接続されている。

## 【0150】

本発明の実施の形態ではコンパレータからなる検出部を2個用いる。コンパレータからなる検出部2qの一端を、インピーダンス素子2pの中間部の接続点2p2に接続する。コンパレータからなる検出部2qの他端は、直流電圧源2qqを介してインピーダンス素子2pの一端2p1に接続する。コンパレータからなる検出部2rの一端を、インピーダンス素子2pの中間部の接続点2p2に接続する。コンパレータからなる検出部2qの他端は、直流電圧源2rrを介してインピーダンス素子2pの一端2p1に接続する。

10

## 【0151】

電力変換主回路1の出力端子4の電位は高電位、中間電位、零電位のいずれかにあるが、出力端子4の電位によってインピーダンス素子2eの電圧が変化する。検出部2qは、出力端子4の電位が零電位にあるのか中間電位以上（中間電位または高電位）にあるのかを検出し、検出結果を下位側出力電圧信号として送出する。検出部2rは、出力端子4の電位が高電位にあるのか中間電位以下（中間電位または零電位）にあるのかを検出し、検出結果を上位側出力電圧信号として送出する。このように、インピーダンス素子2eの電圧を、検出部2q、2rにより検出することにより、電力変換主回路1の出力端子4の電位が高電位、中間電位、零電位のいずれにあるのかを検出することができる。

20

## 【0152】

直流電圧源2qq、2rrの電圧値は直流母線の電位に応じてそれぞれ適切に調整しておく。直流電圧源2qq、2rrはゲート駆動回路2oの電源を用いれば簡単に構成することができる。ゲート駆動回路2oの電源電圧を抵抗分圧すれば所望の電圧値を持つ直流電圧源を得ることができる。あるいは、レギュレータICを用いることにより、ゲート駆動回路2oの電源電圧より所望の電圧値を持つ直流電圧源を得てもよい。

## 【0153】

各ゲート駆動回路21、2m、2n、2oは、それぞれスイッチング素子1c、1d、1e、1fのゲート-ソース間（トランジスタ素子がIGBTの場合はゲート-エミッタ間）に電圧印加できるように電気的に接続し、絶縁回路2x、2y、2ad、2aeを介して入力された各駆動信号に基づき、各スイッチング素子1c、1d、1e、1fにゲート電圧を印加する。

30

## 【0154】

検出部2q、2rにより検出された出力電圧信号は、絶縁回路2aa、2acを介して制御部3に出力し、また、反転論理部2t、2uにより反転した反転出力電圧信号も、絶縁回路2z、2abを介して制御部3に出力するように構成する。なお、図13も、図1、図6と同様に、矢印付きの線を信号線、矢印無しの線を電気的配線として図示している。

40

## 【0155】

制御器3は、第1の補正回路であるデッドタイム補正回路3e、第1の付加回路であるデッドタイム付加回路3f、第2の付加回路であるデッドタイム付加回路3g、第2の補正回路であるデッドタイム補正回路3i、第3の付加回路であるデッドタイム付加回路3j、および第4の付加回路であるデッドタイム付加回路3kにより構成される。

## 【0156】

デッドタイム補正回路3eは、電力変換主回路1の正極側の出力電圧指令値である上位PWM信号を受けて、ゲート駆動回路基板2から入力される上位側出力電圧信号とその反転出力電圧信号に基づきデッドタイム補正を行う。

## 【0157】

50

デッドタイム付加回路3fは、デッドタイム補正回路3eからのスイッチング素子1cの駆動信号に対してデッドタイムを付加してゲート駆動回路21に駆動信号を出力する。デッドタイム付加回路3gは、デッドタイム補正回路3eからの信号を反転論理部3hにより反転した第5のスイッチング素子1eの駆動信号に対してデッドタイムを付加してゲート駆動回路2nに駆動信号を出力する。

【0158】

デッドタイム補正回路3iは、電力変換主回路1の負極側の出力電圧指令値である下位PWM信号を受けて、ゲート駆動回路基板2から入力された下位側出力電圧信号とその反転出力電圧信号に基づきデッドタイム補正を行う。

【0159】

デッドタイム付加回路3jは、デッドタイム補正回路3iからのスイッチング素子1dの駆動信号に対してデッドタイムを付加してゲート駆動回路2mに駆動信号を出力する。デッドタイム付加回路3kは、デッドタイム補正回路3iからの信号を反転論理部3lにより反転したスイッチング素子1fの駆動信号に対してデッドタイムを付加してゲート駆動回路2oに駆動信号を出力する。

【0160】

このように、実施の形態3による電力変換装置では、出力端子4から出力される電位状態は3レベル（高電位、中間電位、零電位）のいずれかであるが、出力電位を検出できるように2つの検出部2q、2rを設け、これに対応するように制御部3に、デッドタイム補正回路3e、3iと、デッドタイム付加回路3f、3g、3j、3kを設けた以外は、実施の形態2と同様の構成であるため、ここでは詳細な説明は省略する。

【0161】

この構成によれば、3レベルの電圧を出力する場合であっても、基本的に、出力端子4から出力される電圧の検出方法の原理は、実施の形態1と同じであり、実施の形態1および実施の形態2と同様の効果が得られるだけでなく、上位および下位それぞれのPWM信号に対して2レベルの電力変換回路と同様のデッドタイム補正回路を用いることで、3レベルの電力変換回路においてもデッドタイム補正をすることができる。

【0162】

実施の形態3では、ゲート駆動回路21、2m、2n、2o、絶縁回路2x、2y、2ad、2aeといった部品を同一基板であるゲート駆動回路基板2の上に構成している。本発明に特有の部品である、インピーダンス素子2p、検出部2r、2q、絶縁回路2z、2aa、2ab、2acといった部品もゲート駆動回路基板2の上に構成している。このように構成することで、ゲート駆動回路基板の製造時に本発明に特有の部品をゲート駆動回路部品と合わせて実装することができる。本発明の効果を得られる電力変換装置を製造工程が増加することなく製造することができる。

【0163】

なお、本実施の形態では、直流電圧源2qq、2rrの電圧値は直流母線の電位に応じてそれぞれ適切に調整しておくことを述べた。通常、電力変換装置に電力を供給する直流母線の電位は安定しており、直流電圧源2qq、2rrの電圧値の調整は一度行えば良い。しかしながら、特殊な用途の電力変換装置においては、直流母線の通常時の電位が大きく変動することがある。この場合には検出部2q、2rの閾値をそれぞれ生成する直流電圧源2qq、2rrの電圧値は、直流母線の電位によって可変となるように構成することが望ましい。

【0164】

上記の変形例として、図14に示すように、直流母線5aとゲート駆動回路2oの接続端26oとをインピーダンス素子2afで電気的に接続し、その分圧電位を利用する電力変換装置がある。2個の分圧電位があり、それぞれ直流電圧源2qq、2rrとして用いる。これにより、直流母線5aの通常時の電位が変動しても、それに応じて閾値電圧が変動するため検出部2q、2rの誤検知、誤動作を防止できる。さらに、本構成であれば、落雷などで母線電圧が異常に変動して瞬時低下した場合であっても、検出部2q、2rの

10

20

30

40

50

誤検知、誤動作を防止できる。

【0165】

図15では、別の変形例を示す。この電力変換装置は、実施の形態2で説明したゲート駆動回路基板2と同じものを2枚用いて、上位電位側のゲート駆動回路基板2Cはスイッチング素子1cとスイッチング素子1eを駆動するように配線し、下位電位側のゲート駆動回路基板2Dはスイッチング素子1dとスイッチング素子1fを駆動するように配線している。

【0166】

図15のように構成することで、2レベルの電力変換回路用のゲート駆動回路基板を流用することができることから、設計コストや部品調達コストを低減できる。

10

【0167】

以上のように、この発明の実施の形態3における電力変換装置では、実施の形態1および実施の形態2の2レベルの電力変換装置の構成を基本として、3レベルの電力変換主回路に対応するように、出力端子4から出力される各電位差を検出できるように2つの検出部2q、2rを設け、制御部3にデッドタイム補正回路3e、3iおよびデッドタイム付加回路3f、3g、3j、3kを設けることで、3レベルの電圧を出力する場合であっても、実施の形態1および実施の形態2の2レベルの場合と同様の効果を得られる。すなわち、電力変換主回路の出力電圧を検出し、デッドタイム補償する電力変換装置であって、製造が容易で、かつ誤動作しない電力変換装置を得ることができる。また、製造が容易で、かつ誤動作しない電力変換主回路の出力電圧検出方法を得ることができる。

20

【0168】

また、3レベルの電力変換主回路に対しても従来技術に比べてフォトカプラのような絶縁素子の遅れ要素に起因する誤差を補正することができ、デッドタイム補正の精度を向上することができる。

【0169】

さらに上述の通り、検出部2r、2qの閾値をそれぞれ生成する直流電圧源2rr、2qqを、直流母線5aの電位によって閾値が可変となるように構成することで、直流母線の電位が変動しても検出部2r、2qの誤検知、誤動作を防止できる。

【0170】

実施の形態4。

30

実施の形態1では、スイッチング素子1a、1bからなるモジュール100、101とゲート駆動回路2a、2bとが分離して配置されており、配線にて接続されている場合を示した。実施の形態4においては、一体として配置されている場合について示す。

【0171】

図16および図17は、この発明の実施の形態4による電力変換装置の配置例を示す図である。ゲート駆動回路2a、ゲート駆動回路2b、インピーダンス素子2e、スイッチング素子1aとスイッチング素子1bからなるモジュール102、および周辺の部品の配置を示す。

【0172】

モジュール102は、スイッチング素子1aおよびスイッチング素子1bが1つの筐体に納められた、いわゆる2in1モジュールとなっている。ゲート駆動回路2aおよびゲート駆動回路2bは、1枚のゲート駆動回路基板2で構成されている。

40

【0173】

図16は、ゲート駆動回路2aおよびゲート駆動回路2bを搭載するゲート駆動回路基板2が、スイッチング素子1aとスイッチング素子1bとを収めたモジュール102に載設する前の、分離した状態を示す。

【0174】

スイッチング素子1aとスイッチング素子1bとを収めたモジュール102には、制御用ゲート端子12a、12bと制御用ソース端子13a、13bが、金属ピンの形でそれぞれ設けられている。

50

## 【0175】

一方、ゲート駆動回路基板2のゲート駆動回路2aとゲート駆動回路2bには、制御用ゲート端子12a、12bと制御用ソース端子13a、13bにそれぞれ対応して、制御用ゲート端子の取り付け部28a、28bと制御用ソース端子の取り付け部29a、29bが、ソケットの形で設けられている。

## 【0176】

ゲート駆動回路基板2は、矢印Aの方向に従って、モジュール102の直上に載設され、図17に示すように、モジュール102の制御用ゲート端子12a、12bと制御用ソース端子13a、13bが、制御用ゲート端子の取り付け部28a、28bと制御用ソース端子の取り付け部29a、29bを介して、ゲート駆動回路2aおよびゲート駆動回路2bと、それぞれ電気的に接続される。

10

## 【0177】

このように、外付けのソース信号線およびゲート信号線を用いずにゲート駆動回路基板2をモジュール102の直上に近づけて配置していることから、電磁ノイズの影響を抑え、電力変換主回路の出力端子4の電位が変形することなくインピーダンス素子2eに伝達される。制御部は出力端子4の電位を精度よく検出できる。

## 【0178】

さらに、インピーダンス素子2eとゲート駆動回路2aの接続端26aがゲート駆動回路2aの制御用ソース端子13aの近傍に配置されている。すなわち、接続端26aと制御用ソース端子13aとの距離は、制御用ゲート端子12aと制御用ソース端子13aとの距離と同じか、それ未満である。また、インピーダンス素子2eとゲート駆動回路2bの接続端26bがゲート駆動回路2bの制御用ソース端子13bの近傍に配置されている。すなわち、接続端26bと制御用ソース端子13bとの距離は、制御用ゲート端子12bと制御用ソース端子13bとの距離と同じか、それ未満である。本構成により、さらに電磁ノイズの影響を抑え、電力変換主回路の出力端子4の電位が変形することなくインピーダンス素子2eに伝達される。制御部は出力端子4の電位をさらに精度よく検出できる。

20

## 【0179】

以上のように、この発明の実施の形態4による電力変換装置では、ゲート駆動回路基板2をモジュール102の直上に近づけて配置するだけでなく、インピーダンス素子2eとゲート駆動回路2aの接続端26aが、スイッチング素子1aの制御用ソース端子13aの近傍に配置し、インピーダンス素子2eとゲート駆動回路2bの接続端26bがスイッチング素子1bの制御用ソース端子13bの近傍に配置することで、電磁ノイズの影響を抑え、電力変換主回路の出力端子4の電位が変形することなくインピーダンス素子2eに伝達される。制御部は出力端子4の電位を精度よく検出できる。

30

## 【0180】

なお、この実施の形態4では、実施の形態1の電力変換主回路1とゲート駆動回路基板2との接続の場合について説明したが、これに限るものではない。実施の形態2および実施の形態3での電力変換主回路1とゲート駆動回路基板2の接続に用いた場合にも、同様の効果を得ることができる。

40

## 【0181】

また、この実施の形態4では、インピーダンス素子2eを空中配線にゲート駆動回路基板と接続する構成にて説明したが、インピーダンス素子2eが回路パターンにてゲート駆動回路基板2と接続する構成とした場合においても、同様の効果を得ることができる。

## 【0182】

以上、実施の形態1から実施の形態4においては、それぞれ電力変換主回路1が1つの構成の場合について説明したが、これに限るものではない。これらの電力変換主回路1をそれぞれ3個並列に構成して三相インバータとして構成してもよい。また、DCDCコンバータとして構成してもよい。さらに、AC/DC変換するPWMコンバータとして構成してもよい。いずれにおいても、この発明の実施の形態1から実施の形態4と同様の効果

50

を得ることができる。

#### 【0183】

なお、本実施の形態1から実施の形態4においては、同一の電力変換主回路に属する2個のスイッチング素子に注目し、それぞれのスイッチング素子を駆動するゲート駆動回路の間をインピーダンス素子で接続した。本発明はこの構成に限るものではなく、別々の電力変換主回路に属するスイッチング素子に着目し、それぞれのスイッチング素子を駆動するゲート駆動回路の間をインピーダンス素子で接続してもよい。

#### 【0184】

例えば、3相電動機を駆動する3相2レベルインバータを考える。U相正極側のスイッチング素子を駆動するゲート駆動回路とV相正極側のスイッチング素子を駆動するゲート駆動回路をインピーダンス素子2eUVで結ぶ。インピーダンス素子2eUVの電圧または電流を検出器2fUVにより検出すれば、3相2レベルインバータのU相出力とV相出力の相間電圧を検出することができる。同様に、V相正極側のスイッチング素子を駆動するゲート駆動回路とW相正極側のスイッチング素子を駆動するゲート駆動回路をインピーダンス素子2eVWで結ぶ。インピーダンス素子2eVWの電圧または電流を検出器2fVWにより検出すれば、3相2レベルインバータのV相出力とW相出力の相間電圧を検出することができる。W相正極側のスイッチング素子を駆動するゲート駆動回路とU相正極側のスイッチング素子を駆動するゲート駆動回路をインピーダンス素子2eWUで結ぶ。インピーダンス素子2eWUの電圧または電流を検出器2fWUにより検出すれば、3相2レベルインバータのW相出力とU相出力の相間電圧を検出することができる。

10

#### 【0185】

3相2レベルインバータの制御部は、検出器2fUV、2fVW、2fWUの出力を受けることにより、3相2レベルインバータが実際に出力した相間電圧を知ることができる。一方で、制御部は、送出したオン指令信号、オフ指令信号から3相2レベルインバータが出力した相間電圧を推定する。制御部は、両者の相間電圧のずれ時間を計ることにより、デッドタイム補正量を得ることができる。デッドタイム補正量を考慮してオン指令信号、オフ指令信号を送出するように制御部を構成すれば、デッドタイム補償を行う電力変換装置を得ることができる。

20

#### 【符号の説明】

#### 【0186】

30

1 電力変換主回路、1a、1b、1c、1d、1e、1f スイッチング素子、2、

2a、2B、2C、2D ゲート駆動回路基板、2a、2b、2l、2m、2n、2o

ゲート駆動回路、2e、2p、2af インピーダンス素子、2f、2q、2r 検出

部、2g、2h、2i、2j、2x、2y、2z、2aa、2ab、2ac、2ad、2

ae 絶縁回路、3 制御部、3a、3e、3i デッドタイム補正回路、2k、2t、

2u 反転論理部、3b、3c、3f、3g、3j、3k デッドタイム付加回路、3d

、3h、3l 反転論理部、23a、23b ゲート信号線、24a、24b ソース信

号線、100、101、102 モジュール

【 図 1 】

【 図 2 】

### 【 义 3 】

## 【図4】

【図5】

図5

【図6】

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

【図15】

### 【図14】

【図16】

【図17】

---

フロントページの続き

(72)発明者 三木 隆義

東京都千代田区丸の内二丁目 7 番 3 号 三菱電機株式会社内

(72)発明者 山崎 尚徳

東京都千代田区丸の内二丁目 7 番 3 号 三菱電機株式会社内

(72)発明者 中嶋 幸夫

東京都千代田区丸の内二丁目 7 番 3 号 三菱電機株式会社内

審査官 栗栖 正和

(56)参考文献 特開平 11 - 275868 (JP, A)

特開昭 62 - 077065 (JP, A)

特開平 05 - 252795 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 02 M 7 / 48 - 7 / 487

H 02 M 1 / 08

H 03 K 17 / 687

H 03 K 17 / 16