(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5189995号

(P5189995)

(45) 発行日 平成25年4月24日(2013.4.24)

(24) 登録日 平成25年2月1日(2013.2.1)

|                      |              |

|----------------------|--------------|

| (51) Int.Cl.         | F 1          |

| H05K 3/46 (2006.01)  | H05K 3/46 Z  |

| G01R 1/073 (2006.01) | G01R 1/073 E |

| H05K 3/00 (2006.01)  | H05K 3/46 X  |

| H01L 21/66 (2006.01) | H05K 3/46 H  |

|                      | H05K 3/00 N  |

請求項の数 9 (全 15 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2008-558291 (P2008-558291)  |

| (86) (22) 出願日 | 平成19年2月22日 (2007.2.22)        |

| (65) 公表番号     | 特表2009-529238 (P2009-529238A) |

| (43) 公表日      | 平成21年8月13日 (2009.8.13)        |

| (86) 国際出願番号   | PCT/US2007/004668             |

| (87) 国際公開番号   | W02007/102998                 |

| (87) 国際公開日    | 平成19年9月13日 (2007.9.13)        |

| 審査請求日         | 平成22年1月29日 (2010.1.29)        |

| (31) 優先権主張番号  | 11/308,094                    |

| (32) 優先日      | 平成18年3月6日 (2006.3.6)          |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                             |

|-----------|---------------------------------------------------------------------------------------------|

| (73) 特許権者 | 505377474<br>フォームファクター、 インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 945<br>51, リバーモア, サウスフロント<br>ロード 7005 |

| (74) 代理人  | 100079108<br>弁理士 稲葉 良幸                                                                      |

| (74) 代理人  | 100109346<br>弁理士 大貫 敏史                                                                      |

| (72) 発明者  | エルドリッジ, ベンジャミン, エヌ.<br>アメリカ合衆国, カリフォルニア州 945<br>26, ダンビル, シエリ レーン 65<br>1                   |

最終頁に続く

(54) 【発明の名称】積重ねガード構造

## (57) 【特許請求の範囲】

## 【請求項 1】

導電層と絶縁層とが交互に積層された多層基板を含む電気装置であって、複数の前記導電層のうちの少なくとも1つに形成された信号トレースと、前記信号トレースに前記絶縁層の1つを介して対向する導電層の面内に、前記多層基板を構成する当該導電層の部分から電気的に分離して設けられた、前記信号トレースを電磁的に遮蔽するガード構造部を備え、

前記ガード構造部は、前記信号トレースと略同一の形状で、かつ、当該信号トレースに対して積層方向に整列する位置に設けられる、電気装置。

## 【請求項 2】

前記信号トレースは、前記多層基板を構成する当該信号トレースの周囲の部分から離間して設けられる、請求項1に記載の電気装置。

## 【請求項 3】

前記絶縁構造部は、前記多層基板を構成する当該絶縁構造部の周囲の部分から離間して設けられる、請求項2に記載の電気装置。

## 【請求項 4】

前記信号トレースおよびガード構造部は、前記信号トレースの輪郭に沿うように、前記多層基板に設けられたトレンチによって形成される、請求項3に記載の電気装置。

## 【請求項 5】

10

20

前記多層基板は、前記トレンチに入れられた電気的絶縁材料を含む、請求項4に記載の電気装置。

**【請求項6】**

前記多層基板が、互いに電気的に絶縁された複数の前記導電層を有するセラミック基板からなる、請求項1に記載の電気装置。

**【請求項7】**

前記信号トレースおよび前記ガード構造部の一方は、前記多層基板の表面の導電層の面内に形成され、前記信号トレースおよび前記ガード構造部の他方は、前記多層基板内に埋め込まれた前記導電層の面内に形成される、請求項1に記載の電気装置。

**【請求項8】**

前記信号トレースの少なくとも一部に取り付けられた導電プローブをさらに備える、請求項1に記載の電気装置。

**【請求項9】**

導電層と絶縁層とが交互に積層された多層基板を含む電気装置を備えるプローブカードアセンブリであって、

前記電気装置は、

複数の前記導電層のうちの少なくとも1つに形成された信号トレースと、

前記信号トレースに前記絶縁層の1つを介して対向する導電層の面内に、前記多層基板を構成する当該導電層の部分から電気的に分離して設けられた、前記信号トレースを電磁的に遮蔽するガード構造部と、

前記信号トレースの少なくとも一部に取り付けられた導電プローブと、を備え、

前記ガード構造部は、前記信号トレースと略同一の形状で、かつ、当該信号トレースに対して積層方向に整列する位置に設けられる、

プローブカードアセンブリ。

**【発明の詳細な説明】**

**【背景技術】**

**【0001】**

ガード構造技術を使用して、信号トレース（例えば、基板上に配置され、または基板内に埋め込まれ、1つまたは複数の電気信号を伝えるように構成された材料の導電性トレース）は、近傍のトレースとの容量結合、他のトレースからのクロストーク、電気的干渉、または漏電等から電気的に保護できる。本明細書で開示された本発明の例示の実施形態は、改善されたガード構造およびそのようなガード構造を作る方法および使用する方法に関する。

**【発明の開示】**

**【課題を解決するための手段】**

**【0002】**

本発明のいくつかの実施形態は、積重ねガード構造を提供することに関する。本発明のいくつかの実施形態によれば、電気装置を、複数の層を備えるスタックを形成することによって作ることができる。これらの層は、導電層および電気絶縁層を交互に備えることができる。導電層の少なくとも1つは、信号トレースを備えることができ、導電層の他の少なくとも1つは、信号トレースを容量結合、クロストーク、および／または他の電気干渉から保護するように構成されたガード構造を備えることができる。1つまたは複数の信号トレース、および、1つまたは複数のガード構造は、当該スタック中において互いに整列されることができる。

**【0003】**

本発明の実施形態のこれらおよび他の特徴および有利点は、以下に説明され、以下の詳細な説明および添付の特許請求の範囲で、いっそう十分に明らかになるであろう。これらの特徴および有利点は、添付の特許請求の範囲で特に指摘された、器具および組合せによって実現され、また得られるであろう。さらに、本発明の特徴および有利点は、以下で説明されるように、本発明の実施によって理解され、または説明から明らかになるであろう

10

20

30

40

50

。

#### 【0004】

本発明の実施形態の上記の特徴および他の特徴並びに有利点が得られるように、本発明の実施形態のより具体的な説明が特定の実施形態を参照して行われ、これらの実施形態は、添付の図面に示されている。これらの図面は、本発明の代表的な実施形態を示すだけであり、したがって、本発明の範囲を限定するものとして解釈されるべきでないことを理解して、本発明の実施形態は、添付の図面を使用することによって、さらに明確に、かつ詳細に記述され、また説明される。

#### 【発明を実施するための最良の形態】

#### 【0005】

本明細書は、本発明の例示の実施形態および適用を説明する。しかし、本発明は、これらの例示の実施形態および適用に、または例示の実施形態および適用が動作するまたは本明細書で説明される方法に限定されない。さらに、図は簡単化された、または部分的な図を示すことがあり、図の要素の寸法は、図示を容易にし、明確にするために、誇張されていることがある、または、その他、比例していないことがある。さらに、本明細書において「の上に」という用語は、1つの物体または要素（例えば、材料、層、基板、その他）が、他の物体または要素の直ぐ上にあるかどうか、1つの物体または要素と他の物体または要素との間に1つまたはそれ以上の介在する物体または要素があるかどうかにかかわらず、他の物体または要素「の上に」あることがあり得る。また、方向（例えば、上に、下に、一番上の、底、その他）は、与えられた場合、相対的なものであり、単なる例として、また説明および議論を容易にするために与えられるだけであり、限定として与えられない。

10

#### 【0006】

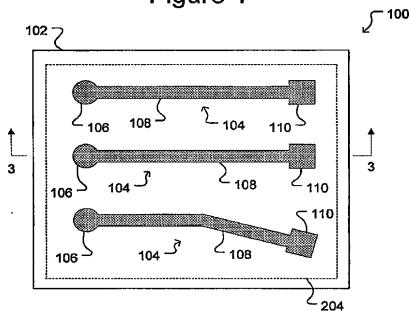

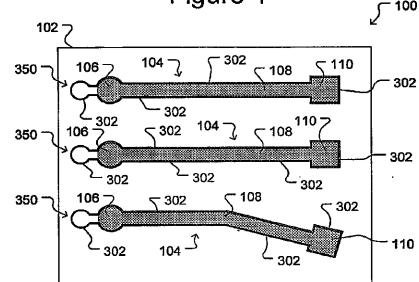

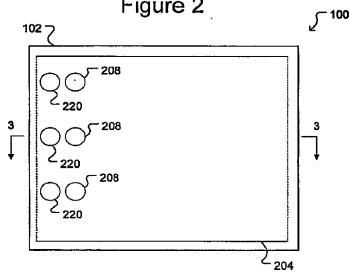

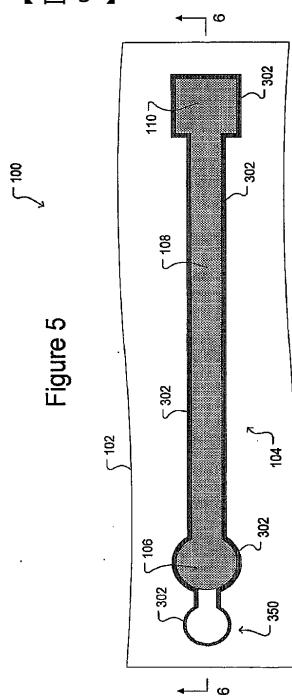

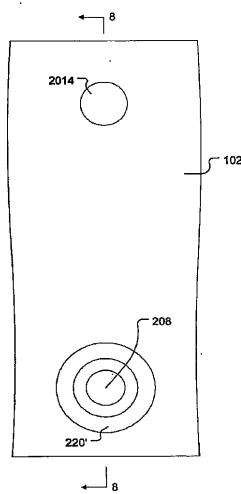

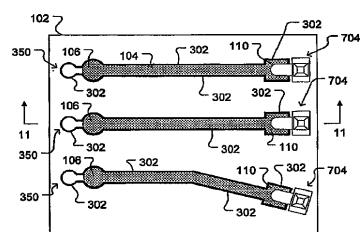

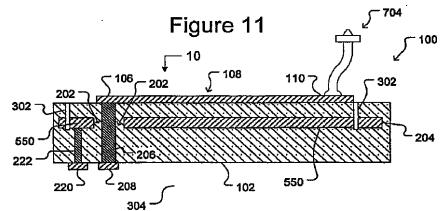

図1～図3は、基板102を備える例示の電気装置100を示し、本発明のいくつかの実施形態に従って、複数の信号トレース104（明確化および他の要素との対比のために、図1、図4、図5、および図8では、網掛けされ、薄い灰色の外観を有している）が基板102の1つの表面に配置され、複数の信号端子208および複数のガード端子220が基板102の反対側の表面に配置されている。（図1は電気装置100の上面図を示し、図2は底面図を示し、図3は側面断面図を示している。）例として、基板102は、セラミック基板、プリント回路基板、または他の適切な配線基板であることがあり、電気装置100の配線基板またはある他の基板として機能し得る。導電性トレース104は、導電性ランド106、導電性トレース部分108、および導電性パッド110を含むことができる。トレース部分108は、ランド106およびパッド110に電気的に接続することができる。図1は3つの導電性トレース104を示すが、本発明の実施形態が、3よりも多い、または少ないトレース104を有する電気装置を包含することを、当業者は理解するであろう。同様に、3よりも多いまたは少ない信号端子208、および、3よりも多いまたは少ないガード端子220が設けられることもある。加えて、本発明の実施形態がトレース104の様々な構成およびレイアウトを包含することを、当業者は理解するであろう。さらに、図に示されるランド106、トレース部分108、およびパッド110の形状は例示に過ぎず、ランド106、トレース部分108、およびパッド110はどんな形状でも取ることができる。

20

30

40

#### 【0007】

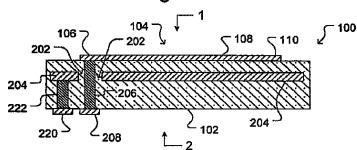

図3から良く理解されるように、導電面204は基板102の中に埋め込まれていてよい。面204は、トレース104に全体として平行であることがあり、図1および図2（面204を破線で示す）に示されるように、面204は、面204の一部がトレース104の下にあるように基板102の所望の範囲にわたって広がっていることがある。理解されるように、各信号トレース104のガード構造は、面204から切り出されていることがある。

#### 【0008】

図1～図3に示された例では、信号トレース104は、ランド106とパッド110と

50

の間で電気信号（例えば、データ信号、制御信号、その他）を伝えるように構成されることがある。ランド106および/またはパッド110は、他の電子デバイス（不図示）に電気的に接続されるように設定され得る。図1～図3に示された例では、導電信号端子208は、トレース104が配置されている表面の反対側の基板102の表面に設けることができる。導電性ピア206は、各信号端子208をランド106の1つに電気的に接続することができ、絶縁路202は、各ピア206を導電面204から電気的に絶縁することができる。例えば、各絶縁路202は、面204に孔またはギャップを含むことができ、これによって、ピア206は面204と電気的に接続することなしに面204を通過することができるようになる。図3に示されるように、絶縁路202を形成する面204の孔またはギャップは、必然的に、基板102を構成する材料で占められ、すなわち満たされることがある。ランド106ごとに、1つの信号端子208および1つのピア206が設けられることがある。したがって、他の電子デバイス（不図示）が信号端子208を通してランド106に電気的に接続されることがある。或いは、信号端子208およびピア206無しに、他の電子デバイス（不図示）からランド106に直接電気接続がなされることもある。

#### 【0009】

図2および図3に示されるように、ガード端子220および対応するピア222は、面204への電気的接続を行うことができる。上述したように、また以下で議論するように、ガード構造は、面204から切り出されることがあり、各ガード端子220およびピア222は、ガード構造の1つへの別個の電気的接続を行うことができる。

#### 【0010】

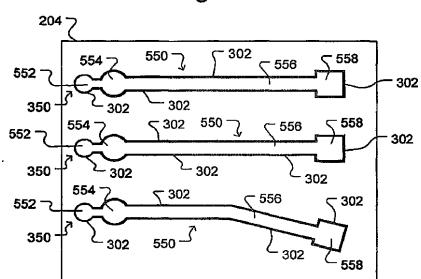

図4～図7は、本発明のいくつかの実施形態に従ってトレース104の各々のためのガード構造を面204から作る例を示す。（図4は、電気装置100の上面図を示す。図5は、電気装置100の部分上面図を示し、信号トレース104の1つを示している。図6は、図5の側面断面図を示す。さらに、図7は、導電面204を示す。）図4～図7に示されるように、各トレース104のまわりには、トレーンチ302を掘ることができる。（明確化及び周囲の要素との対比のために、図4、図5、および図7において、トレーンチ302は網掛けされ暗灰色に示されている。）トレーンチ302は、限定することなしにレーザまたは鋸を含んだどんな適切な器具を使用して掘られてもよい。代替的に、トレーンチ302は、エッティングや、別な方法で化学的に形成されてもよい。例えば、ドライまたはウェットエッティングプロセスを、トレーンチ302を形成するために使用してもよい。

#### 【0011】

図6から良く理解されるように、各トレーンチ302は、トレーンチ302が導電面204を貫通して信号トレース104の各々のガード構造を導電面から切り出すように、基板102の中へ延在できる。図4および図5に示されるように、各トレーンチ302は、概ね、トレース104の1つを縁取っている。また、図4および図5に示されるように、各トレーンチ302は、トレース104を縁取らない部分350を含んでもよい。理解されるように、部分350は、ピア222（図3参照）が接続可能な領域を各ガード構造に作ることができる。

#### 【0012】

図7は、トレーンチ302が基板102に掘り込まれた後の導電面204だけの上面図を示す。理解されるように、各トレーンチ302は、導電面204からガード構造550を切り出す。トレーンチ302で作られたスペースが、面204の残り部分および他のガード構造550から各ガード構造550を電気的に分離している。各ガード構造を電気的にさらに絶縁するために、電気絶縁材料（不図示）をトレーンチ302に入れててもよい。

#### 【0013】

図7に示されるように、各ガード構造550は、信号トレース104の1つに全体として似た形状に作ることができる。したがって、各ガード構造550は、信号トレース104のランド106に似た形に作られた部分554、信号トレース104のトレース部分108に似た形に作られた部分556、および信号トレース104のパッド110に似た形

10

20

30

40

50

に作られた部分 558 を含むことがある。また、図 7 に示されるように、各ガード構造 550 は、延長部分 552 も含むことがあり、この延長部分 552 は、上述したように、図 3 に 222 で示すようなビアがガード構造 550 に電気的に接続できる領域を提供し得る。

【0014】

トレンチ 302 が基板 102 に掘り込まれた後で、電気装置 100 は、基板 102 の表面の信号トレース 104 と、基板 102 の中に埋め込まれたガード構造 550 とを備える。さらに、各ガード構造 550 は、信号トレース 104 の 1 つに対応することがあり、さらに、各ガード構造 550 は、その対応する信号トレース 104 に全体として似た形状に作られてもよく、さらにその対応する信号トレース 104 に対して全体として平行で、かつ、その対応する信号トレース 104 と整列されてもよい。各ガード構造 550 は、他の信号トレース 104 との容量結合、他の信号トレース 104 とのクロストーク、電磁干渉、または漏れ電流などの電気的干渉から対応する信号トレース 104 を保護するように配線され得る。さらに、ガード構造 550 は信号トレース 104 と積重ね関係にあるので、ガード構造 550 は、隣接した信号トレース 104 の間のスペースを占めない。その結果として、信号トレース 104 は、ガード構造が基板 102 の信号トレース 104 と同じ表面でトレース 104 のまわりに配置された場合に可能であるよりもいっそう互いに近接した間隔で配置することができる。

【0015】

いくつかの実施形態では、トレース 104 ごとに、信号源（不図示）が、パッド 110 または信号端子 208 の一方に接続されることがあり、電気信号はトレース 104 に沿って伝達され得る。また、同じまたは実質的に同じ電位が信号トレース 104 とその対応するガード構造 550 の両方に存在するように、第 2 の信号源（不図示）が、ガード端子 220 に接続されてもよく、これによって、信号トレース 104 と、これに隣接する信号トレース 104 との間の容量結合を大幅に減少させるか、無くすことができる。（代替的に、ガード端子 220 は、基板 102 のいずれの表面のどこに存在してもよく、ガード端子 220 をガード構造 550 に電気的に接続するように、ビア 222 が修正され、及び／又は、他のまたは追加の電気的接続が行われることがある。）代替的に、ガード構造 550 が所望の電位に保たれるように、異なる電位（例えば、接地または特定の電圧）がガード端子 220 に接続されることがある。そのような構成は、そうしなければ対応する信号トレース 104 に影響を及ぼすかもしれない様々なタイプの電気干渉を減少させるか、無くすことができ、さらに、対応する信号トレース 104 のインピーダンスを制御するのに使用されることもある。印加された電位は、固定されてもよく（例えば、直流（DC）型の電圧）、または時間変化してもよい（例えば、交流（AC）型の電圧）。

【0016】

図 1～図 7 に示された電気装置 100 の構成は、単なる例示に過ぎず、多くの変形が可能である。例えば、トレース 108 はガード構造であってもよく、信号トレースが導電面 204 から切り出されてもよい。他の例として、端子 220 は、基板 102 の反対側の表面に配置してもよい。さらに他の例として、トレース 104 は、図 1 および図 3～図 6 に示されたように基板 102 の外面に配置されるのではなく基板 102 の中に埋め込まれてもよい。さらに他の例として、2 よりも多い層の導電層が積重ね関係で形成されてもよい。例えば、1 よりも多い導電面（例えば、各々面 204 のような）が基板 102 の中に埋め込まれてもよく、したがって、複数の導電構造が基板 102 から切り出されことがある。図 1～図 7 に示された電気装置 100 の構成の可能な変形のさらに他の例では、ガード端子 220 が信号端子 208 のまわりに環状リングとして形成されてもよい。そのような場合には、208 を 220 から電気的に絶縁するために、信号端子 208 と、ガード端子 220 の環状リング実装との間にスペースまたは絶縁材料が設けられることがある。

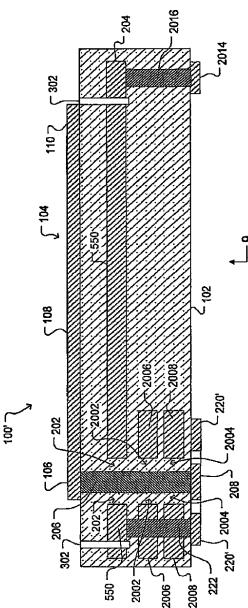

【0017】

図 8 および図 9 は、前述の変形のいくつかの例を示す。図 8 は、図 6 に示された図と同様な側面断面図で、修正電気部品 100' を示し、図 9 は、電気部品 100' の部分底面

10

20

30

40

50

図を示す。図6、図8、および図9の同様な番号の付いた要素は同じものであることがある。

【0018】

図8に示されるように、追加の導電面2006、2008が基板102の中および信号ビア206のまわりに埋め込まれることがある。(2つの追加の面2006、2008が示されているが、より多い、またはより少ない面が用いられることがある。)また、図8に示されるように、ビア206のために面2006、2008を貫通して絶縁路2002、2004を設けることができる。絶縁路2002、2004は、絶縁路202と同様であってよい。すなわち、絶縁路2002、2004は、ビア206が面2006、2008に電気接続することなしに面2006、2008を貫通することができるようとする孔またはギャップを、面2006、2008に備えることができる。したがって、面2006、2008は、ビア206を囲繞し、ビア206に対するガード構造としての役割を果たすことができる。一組の面2006、2008を各ビア206に設けることができ、そのような各組の面2006、2008は、互いに電気的に絶縁されることができる。代替的に、面2006、2008は、面204と同様の大きさであってもよく、面204と同様に、基板102の長さおよび幅の大部分にわたって延在していてもよい。そのような場合、図8に示された面2006、2008と同様の大きさに作られ、かつ、位置付けされたガード構造は、ガード構造550が面204から切り出されるのと同じやり方で、これらの面から切り出すことができる。

【0019】

ガード構造は、端子208に設けられることもある。例えば、図8および図9に示されるように、ガード端子220'は、端子208のまわりに配置された環状リングの形状とすることができる、したがって、端子208に対してガード構造として振る舞うことができる。

【0020】

したがって、図8に示されるようにガード構造として構成されると、面2006、2008は、近傍のビアとの容量結合、他のビアからのクロストーク、電気干渉、または電気漏れからビア206を保護することができ、ガード端子220'は、同様に、近傍の端子との容量結合、他の端子からのクロストーク、電気干渉、または電気漏れから端子208を保護することができる。図8を参照して、導電端子2014およびビア2016が、面204の使用されない部分、すなわちトレニチ302によってガード構造550から分離された面204の部分に電気接続するように設けられることがある。

【0021】

図10および図11は、本発明のいくつかの実施形態に係る図4～図7の電気部品100の例示の構成を示す。図10および図11に示されていないが、図8および図9の電気部品100'は、図10および図11に示されるように構成されることもある。

【0022】

図10に示されるように、導電性プローブ704が、導電性パッド110に結合されることがある。プローブ704は、押し付けられ、それによって、第1の電子デバイス(不図示)に電気接続することができる。加えて、第2の電子デバイス(図示されない)が信号端子208に電気的に接続されることがある。そして、電気信号は、プローブ704、トレース104、ビア206および信号端子208を通って、第1の電子デバイス(不図示)と第2の電子デバイス(不図示)との間に供給されることができ、トレース104は、上述したようにガード構造550によって保護することができる。

【0023】

プローブ704は、弾性のあるバネ状のプローブであってもよい。適切なプローブ704の限定しない例には、米国特許第5,476,211号、米国特許第5,917,707号、および米国特許第6,336,269号に記載されているように、パッド110の1つに接合され、かつ、上に弾性材料をコーティングされた心線から形成された複合構造がある。或いは、プローブ704は、米国特許第5,994,152号、米国特許第6,

10

20

30

40

50

033, 935号、米国特許第6, 255, 126号、米国特許出願公開第2001/0044225号、および米国特許出願公開第2001/0012739号に開示されたバネ素子などのリソグラフィで形成された構造であってもよい。プローブ704の他の限定しない例には、導電性ポゴピン、バンプ、スタッド、打抜きバネ、針、座屈梁、その他がある。

【0024】

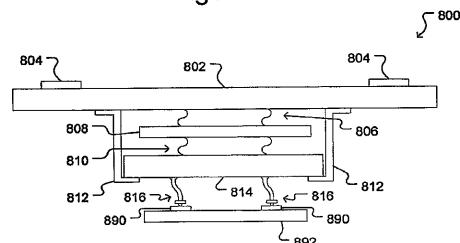

図10および図11に示されるように構成された電気装置100または100'は、半導体チップなどの電子デバイスを試験するために使用することができる。図12は、本発明のいくつかの実施形態に従う例示のプローブカードアセンブリ800を示し、このアセンブリ800において、図10および図11に示されるように構成された電気装置100がプローブ基板814として機能し得る。 10

【0025】

前述したように、プローブ704のようなプローブが、図8および図9に示された構成100' と同様な電子部品100の構成に同様に取り付けられることがある。実際は、プローブ704のようなプローブは、図8および図9に示された電子部品100の多くの可能な変形のどれにでも取り付けることができる。

【0026】

ここで、100、100' と同様な電子部品の例示の使用についての議論に進むと、図12は、例示のプローブカード組立品800を示し、これは、図示のように、3つの基板、すなわち配線基板802、インターポーラ808およびプローブ基板814を含むことができる。端子804は、テスタ(不図示)への電気的接続およびテスタからの電気的接続を行うことができ、さらに、ポゴピン、ジフ(ZIF: zero-insertion-force)コネクタ、または、テスタ(不図示)と電気接続するのに適した任意の他の接続デバイスを受けるパッドを限定することなしに含んだ任意の適切な電気的接続構造であってもよい。 20

【0027】

導電端子、ビアおよび/またはトレース(不図示)などの電気的接続(不図示)は、端子804から配線基板802を通って導電バネコンタクト806への電気的接続を行うことができる。加えて、電気的接続(例えば、導電端子、ビアおよび/またはトレース)(不図示)は、インターポーラ808を通してバネコンタクト806をバネコンタクト810に接続するようにインターポーラ808によって行われることがあり、このバネコンタクト810はバネコンタクト806と同様であってもよい。さらに、電気的接続(例えば、導電端子、ビアおよび/またはトレース)(不図示)は、プローブ基板814を通してバネコンタクト810をプローブ816に電気的に接続することができ、プローブ816は、試験されるべき1つの電子デバイスまたは複数の電子デバイス892の入力および/または出力端子890に接触するように使用されることがある。したがって、端子804からプローブカード組立品を通ってプローブ816に、さらにプローブ816から試験されるべき1つの電子デバイスまたは複数の電子デバイス892の入力および/または出力端子890に、電気的接続(不図示)が行われことがある。 30

【0028】

プローブ基板814およびインターポーラ808は、限定することなしにボルト、ネジ、クランプ、ブラケット、その他を含んだ任意の適切な手段を使用して、配線基板802に固定され得る。図示の実施形態では、プローブ基板814およびインターポーラ808は、ブラケット812によって配線基板802に固定することができる。図10に示されたプローブカード組立品800は、単なる例示に過ぎず、プローブカード組立品の多くの代替えおよび異なる構成を使用することもできる。例えば、プローブカード組立品は、図12に示されたプローブカード組立品よりも少ない、または多い基板を含むことができる。米国特許第5, 974, 622号および米国特許第6, 509, 751号は、例示のプローブカード装置を記載している。加えて、2005年6月24日に出願された「Method And Apparatus For Adjusting A Multi-Substrate Probe Structure」という名称の米国特許出願第11/165, 833号は、複数のプローブヘッドに配置されたより小さなブ 40

ロープ配列から大きなプロープ配列が作られ、かつ各プロープヘッドが独立に調整可能であるようなプロープカード組立品を開示している。前述の特許または特許出願のいずれかに記載されたプロープカード装置の様々な特徴は、プロープカード組立品 800 に適用することができる。

【0029】

プロープカード組立品 800 は、次のように使用することができる。端子 804 は、テスタ（不図示）に接続されることがある、1つまたは複数の電子デバイス 892 の入力および／または出力端子 890 は、プロープ 816 と接触されることがある。そして、テスタは、試験データまたはアナログ電圧レベルまたは電流を生成することができ（本明細書で使用される「試験データ」という用語は、アナログ電圧レベルおよび電流を含んだデジタル信号およびアナログ信号を含む）、この試験データは、プロープカード組立品 800 と、1つの電子デバイスまたは複数の電子デバイス 892 の入力端子 890 に接触したプロープ 816 の1つを通して、1つの電子デバイスまたは複数の電子デバイス 892 に供給され得る。テスタによって生成された試験データに応答して1つの電子デバイスまたは複数の電子デバイス 892 によって生成された応答データは、1つの電子デバイスまたは複数の電子デバイス 892 の出力端子 890 に接触したプロープ 816 によって感知され、プロープカード組立品 800 を通してテスタ（不図示）に供給され得る。テスタ（不図示）は、1つの電子デバイスまたは複数の電子デバイス 892 が試験に合格するかどうかを決定し、および／または、1つの電子デバイスまたは複数の電子デバイス 892 をランク付けするように応答データを評価することができる。例えば、テスタ（不図示）は、1つの電子デバイスまたは複数の電子デバイス 892 によって生成された応答データを、期待される応答データと比較して、応答データを評価することができる。プロープカード組立品 800 は、このように、テスタ（不図示）と試験されるべき1つまたは複数の電子デバイス 892 との間の電気的インターフェースとして機能することができる。試験されるべき1つの電子デバイスまたは複数の電子デバイスは、個別化されない半導体ウェーハのダイ、ウェーハから個別化されたダイ（パッケージ化された、またはされない）、キャリアまたは他の保持デバイスに配置された個別化半導体ダイの配列のダイ、1つまたは複数のマルチダイ電子モジュール、その他であることがある。

【0030】

上述したように、プロープ基板 814 は、図 1～図 11 のいずれかに示されるようにして作ることができる。例えば、図 10 および図 11 に示されるようにプロープ 704 を備えて構成された電子部品 100 または 100' は、図 12 のプロープ基板 814 として使用することができる（この場合、プロープ 704 はプロープ 816 であることがある）。そのような場合、端子 208 は、バネコンタクト 810 の1つに電気的に接続されるであろう。バネコンタクト 810 の別のものは、上述したようにガード構造 550 にガード電圧を供給するようにガード端子 220 に電気的に接続され得る。このようにして、試験信号は、端子 804 に接続されたテスタ（不図示）と、端子 890 がプロープ 816 に接触した、試験される1つの電子デバイスまたは複数の電子デバイス 892 との間に供給されることがある。さらに、配線基板 802 および／またはインターポーラ 808 の上、または中の信号トレースおよび／またはビアには、上述した方法のいずれかを使用してガード構造を設けることもできる。

【0031】

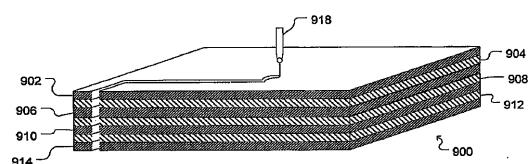

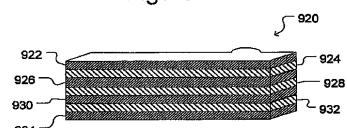

図 13 および図 14 は、本発明のいくつかの実施形態に係る、信号トレースおよびガード構造が多層基板から同時に切り出される電子部品 920 の形成を示す。図 13 に示されるように、多層基板 900 が用意されることがある、層 902～914 は、交互になる導電層と絶縁層とであることがある。例えば、図 13 において、層 902、906、910 および 914 は電気絶縁材料を有することがあり、層 904、908、912 は導電材料を有することがある。限定しない一例として、基板 900 は、多層セラミック基板であつてよく、層 902、906、910 および 914 はセラミック材料を有し、層 904、908、912 は、銅などの金属を有する。

10

20

30

40

50

## 【0032】

図4～図6のように前もって形成された信号導体（例えば、図4～図6のトレース104の1つ）に合うように埋込み導電面（例えば、図4～図6の204）からガード構造を切り出すのではなく、図13では、信号導体と、この信号導体の両側に配置されたガード面とを、基板900から同時に切り出すことができる。

## 【0033】

図13は、基板900から構造（図13の920）を切り出す切削ツール918（例えば、レーザ、鋸、その他）を示す。図13に示されるように、基板900から切り出された積重ねガード構造920は、導電面908から切り出された信号導体928および導電面904、912から切り出されたガード導体924、932を備えることができる。構造920の絶縁層922、926、930、934は、基板900の層902、906、910、914から切り出すことができる。4つの絶縁層902、906、910、914および3つの導電層904、908、912を有する基板900が図13に示されているが、絶縁層および導電層の異なる数およびパターンを備えた多層基板を使用することもできる。さらに、図13に示されるような基板からガード保護スタックを切り出すことによって、多くの異なる型の電子部品を作ることもできる。さらに、初期の基板900は、セラミック以外の材料を有することもある。例えば、基板900は、プリント回路基板材料、有機材料、無機材料、その他を有していてもよい。

## 【0034】

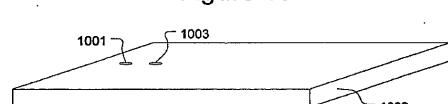

図15～図22は、本発明のいくつかの実施形態に係る積重ねガード構造を作る他の例示の方法を示す。図15に示されるように、基板1002が用意されることがある。この基板1002は、限定することなしに半導体基板（例えば、シリコンウェーハ）、セラミック基板、プリント回路基板、金属基板、その他を含んだどんな適切な基板であってもよい。基板1002は、導電性ビア1001、1003を含むことができる。理解されるように、ビア1001は、基板1002を貫通して延び、基板1002の反対側の表面の導電性パッド1020に電気的に接続されることができ、ビア1003は、基板1002を貫通して延び、基板1002の反対側の表面の他の導電端子1018に電気的に接続されることができる。（図22参照。）理解されるように、端子1020およびビア1001は、作られことになっているガード構造1008への電気的接続を行うことができ、端子1018およびビア1003は、作られことになっている信号トレースへの電気的接続を行うことができる。（図22参照。）

## 【0035】

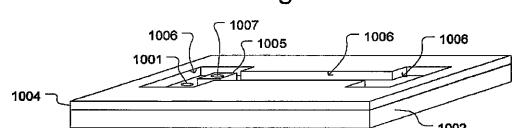

ここで、積重ね構造の形成についての議論に戻って、図16に示されるように、マスク材料1004の第1の層が基板1002に堆積されることがある。適切なマスク材料1004の例は、フォトレジストまたは他のタイプのパターンニング可能な材料である。マスク材料1004は、層の状態で堆積され、開口1006、開口1006内のマスク材料1004のアイランド1005、およびアイランド1005内の開口1007を形成するようにパターニングされる。理解されるように、ガード構造1008（図17参照）は、開口1006の中に形成することができ、したがって、開口1006は、ガード構造1008の所望の形状に対応する形状で形成することができる。また、理解されるように、ガード構造を貫通してビア1003からの電気的接続を行う導電性ビア1009（図17参照）は、開口1007の中に形成されることがある。したがって、開口1007は、ビア1003と揃えられることがある。

## 【0036】

図17に示されるように、開口1006、1007は、ガード構造1008およびビア1009を形成するように導電材料で満たすことができる。前述したように、ビア1009がビア1003の上に形成され、かつ、これに電気的に接続されるように、開口1007は、ビア1003と揃えられることがある。マスク材料1004のアイランド1005は、ガード構造1008とビア1009とが分離され電気的に接続されないように、ガード構造1008とビア1009との間にスペースを与えることができる。

10

20

30

40

50

## 【0037】

開口 1006、1007 に導電材料を満たすプロセスは、電気メッキ、スパッタリング、または他の堆積方法を使用することを含んでもよい。導電材料が開口 1006、1007 の中に電気メッキされる場合、基板 1002 の表面は、マスク材料 1004 を形成する前に導電性の材料層（不図示）をコーティングして用意されることがある。知られているように、そのとき、導電層（不図示）はメッキ装置（不図示）の陽極または陰極に接続されることがある。基板 1002 は、開口 1006、1007 の中に電気メッキされる導電材料を含むメッキ溶液を含んだメッキ槽（不図示）の中に配置されることがある。そのとき、導電材料は、開口 1006、1007 によって露出された導電層（不図示）の部分にメッキされる。図に示されていないが、導電材料が開口 1006、1007 に堆積された後で、マスク材料のアイランド 1005 は、除去され、電気絶縁材料に置き換えることができる。

## 【0038】

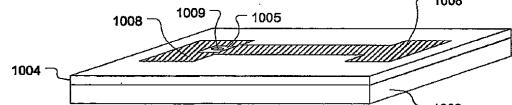

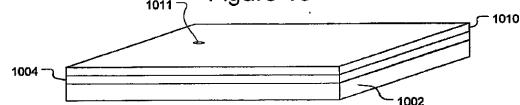

図 18 に示されるように、マスク材料 1010 の第 2 の層が、第 1 のマスク材料 1004、ガード構造 1008、およびビア 1009 の上に堆積され、さらに、ビア 1011 を形成するように導電材料を満たされる開口（不図示）をもつようにパターニングされることがある。ビア 1011 が形成される開口（不図示）は、ビア 1011 がビア 1009 の上に形成され、かつ、これに電気的に接続されるように、ビア 1009 と揃えられることがある。そして、第 2 のマスク層 1010 が除去されて、ビア 1011 を後に残す。

## 【0039】

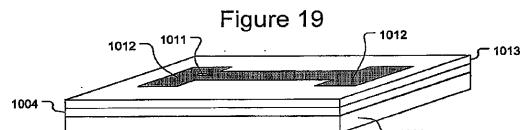

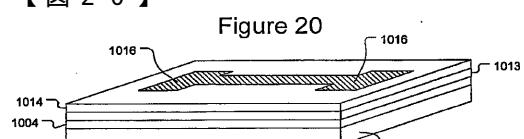

図 19 に示されるように、マスク材料 1013 の第 3 の層が、第 1 のマスク材料 1004 およびガード構造 1008 の上およびビア 1011 のまわりに堆積されることがある。そして、マスク材料 1013 の第 3 の層は、ガード構造 1008 の上に絶縁層 1012 を形成し導電性ビア 1011 が絶縁層 1012 を貫通しているように絶縁材料で満たされる開口（不図示）をもつようにパターニングされることがある。絶縁層 1012 を形成する絶縁材料は、限定することなしに化学気相成長法、物理気相成長法、電子ビーム堆積、熱蒸着、その他を含んだどんな適切な方法を使用して堆積してもよい。他の限定しない例示の方法には、マスク材料 1013 の第 3 の層の開口（不図示）の中への流動可能な材料の注入、流しこみ、または他の堆積材料の硬化がある。図 20 に示されるように、マスク材料 1014 の第 4 の層が、設けられ、信号トレース 1016 を形成するように導電材料で満たされる開口をもつようにパターニングされることがある。

## 【0040】

マスク層 1010、1013、1014 の各々は、マスク層 1004 と同じか同様であつてもよく、マスク層 1004 と同様に堆積されパターンニングされてもよい。ビア 1009、ビア 1011、および信号トレース 1016 を形成する導電材料は、ガードトレース 1008 を形成する導電材料と同じでもよいし、異なっていてもよい。ビア 1009、ビア 1011、および信号トレース 1016 を形成する導電材料は、ガードトレース 1008 を形成する導電材料と同じ方法か、異なる方法で堆積することができる。さらに、図示しないが、1 つの層を形成する材料および要素は、マスク材料の次の層が堆積される前に平坦化されてもよい。

## 【0041】

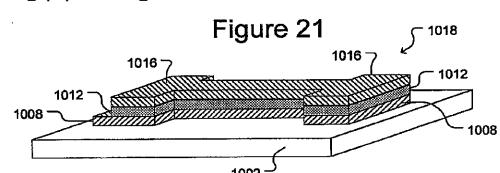

図 21 に示されるように、マスク材料層 1004、1013、1014 は除去され、後にガード構造 1008、絶縁層 1012、および信号トレース 1016 を有する層状構造 1018 を残すことができる。他の実施形態では、図 21 に示されたガードトレース 1008 は、信号トレースとして機能するように構成されてもよく、また図 21 の信号トレース 1016 は、ガードトレースとして機能するように構成されてもよい。加えて、ガード構造 1008、絶縁層 1012、および信号トレース 1016 を有する複数のスタックが、基板 1002 上に形成されてもよい。したがって、図 21 の電子デバイスは、図 4～図 9 に示された電気装置 100 または 100' のようになる場合がある。

## 【0042】

10

20

30

40

50

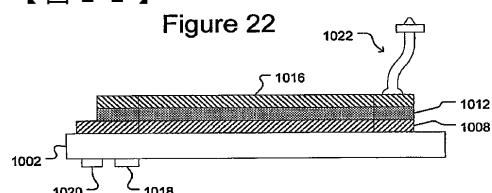

図22に示されるように、プローブ1022(図10および図11のプローブ704に類似していることがある)が、信号トレース1016に取り付けられることがある。上述したように、信号端子1018(図3の信号端子208に類似していることがある)およびガード端子1020(図3のガード端子220に類似していることがある)が、図21に示されるように設けられることがある。或いは、ガード端子220は、図8および図9のガード端子220' と同様に信号端子1018を囲繞する環状端子であってもよい。基板1002を貫通するビア1003、ガード構造1008を貫通するビア1009、および絶縁層1012を貫通するビア1011は、信号端子1018をガード端子1008に電気的に接続することができ、基板1002を貫通するビア1001は、ガード端子1020をガード構造に電気的に接続することができる。上述のように、アイランド1005は、ビア1009とガード構造1008とが電気的に接続されないように、ビア1009とガード構造1008との間に電気的な分離を生じさせる。動作中に、信号端子1018は、データ信号の供給源または宛先に接続されがあり、またガード端子1020は、ガード信号の供給源に接続されることがある。したがって、信号トレース1016は、他の信号トレース(不図示)との容量結合またはクロストークおよび/または他の電気干渉から保護され得る。

【0043】

本発明の特定の実施形態および用途がこの明細書で説明されたが、本発明がこれらの例示の実施形態および用途に、または、例示の実施形態および用途が動作する、または本明細書で説明された方法に、限定されるという意図はない。

【図面の簡単な説明】

【0044】

【図1】本発明のいくつかの実施形態に係る、基板および導電性トレースを有する代表的な電気装置を示す上面図である。

【図2】図1の電気装置の底面図である。

【図3】図1の電気装置の側面断面図である。

【図4】本発明のいくつかの実施形態に係る、各導電性トレースに積重ねガード構造を形成するようにトレンチが掘られた後の図1の電気装置を示す上面図である。

【図5】導電性トレースの一つを示す図4の部分図である。

【図6】図5の側面断面図を示す。

【図7】図4～図6の電気装置の導電面を示す上面図であり、この導電面から切り出されたガード構造を示す図である。

【図8】図6に示された図に全体として対応する側面断面図で、図4～図6に示された電気装置への例示の追加部品を示す図である。

【図9】図8に示された構成の底面図である。

【図10】プローブが導電性トレースのパッドに取り付けられた図4～図6の電気装置を示す上面図である。

【図11】図10の電気装置の側面断面図である。

【図12】本発明のいくつかの実施形態に係る代表的なプローブカード組立品を示す図である。

【図13】本発明のいくつかの実施形態に係る積重ねガード構造を含む電子部品を形成するための多層基板からの電子部品の切り出しを示す図である。

【図14】図13の基板から切り出された電子部品を示す図である。

【図15】本発明の実施形態に係る積重ねガード構造を作るための他の代表的なプロセスを示す図である。

【図16】本発明のいくつかの実施形態に係る積重ねガード構造を作るための他の代表的なプロセスを示す図である。

【図17】本発明の実施形態に係る積重ねガード構造を作るための他の代表的なプロセスを示す図である。

【図18】本発明の実施形態に係る積重ねガード構造を作るための他の代表的なプロセス

10

20

30

40

50

を示す図である。

【図19】本発明の実施形態に係る積重ねガード構造を作るための他の代表的なプロセスを示す図である。

【図20】本発明の実施形態に係る積重ねガード構造を作るための他の代表的なプロセスを示す図である。

【図21】本発明の実施形態に係る積重ねガード構造を作るための他の代表的なプロセスを示す図である。

【図22】本発明の実施形態に係る積重ねガード構造を作るための他の代表的なプロセスを示す図である。

【図1】

Figure 1

【図4】

Figure 4

【図2】

Figure 2

【図3】

Figure 3

【 5 】

Figure 5

【図6】

Figure 6

【 四 7 】

Figure 7

【図8】

Figure 8

【図9】

Figure 9【図10】

Figure 10

【図11】

【図12】

Figure 12【図13】

Figure 13【図14】

Figure 14【図15】

Figure 15

【図16】

Figure 16

【図17】

Figure 17

【図18】

Figure 18

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 21/66

B

審査官 西村 泰英

(56)参考文献 特開2002-141711 (JP, A)

特開2000-307312 (JP, A)

特開2001-044716 (JP, A)

特開2002-016340 (JP, A)

特開2001-007525 (JP, A)

特開昭60-032401 (JP, A)

特開昭61-114601 (JP, A)

実開昭61-007101 (JP, U)

(58)調査した分野(Int.Cl., DB名)

H05K 3/46

G01R 1/073

H01L 21/66

H05K 3/00