(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4326609号

(P4326609)

(45) 発行日 平成21年9月9日(2009.9.9)

(24) 登録日 平成21年6月19日(2009.6.19)

(51) Int.Cl.

F 1

H01L 23/50 (2006.01)

H01L 23/28 (2006.01)H01L 23/50

H01L 23/28U

G

J

請求項の数 1 (全 6 頁)

(21) 出願番号 特願平10-230095

(22) 出願日 平成10年7月30日(1998.7.30)

(65) 公開番号 特開平11-126865

(43) 公開日 平成11年5月11日(1999.5.11)

審査請求日 平成17年7月13日(2005.7.13)

(31) 優先権主張番号 904989

(32) 優先日 平成9年8月1日(1997.8.1)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78735 テキサス州

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100116322

弁理士 桑垣 衡

(72) 発明者 ブライアン・エイ・ウェブ

アメリカ合衆国アリゾナ州チャンドラー、

サウス・オウリアンダー・ドライブ384

5

審査官 山本 雄一

最終頁に続く

(54) 【発明の名称】半導体素子を製造する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体素子を製造する方法であって：

穴(15)およびリード(13)を具備するフラグ(14)を有するリードフレーム(12)を準備する段階；

周辺部に位置するパッドを有する電子チップ(11)を準備し該電子チップ(11)を前記フラグ(14)上に配置する段階であって、前記電子チップは前記穴を覆い、かつ前記チップのパッドは前記フラグの方向を向く、段階；および

前記電子チップ(11)および前記リードフレーム(12)の周りにパッケージング材料(17)を配置する段階であって、前記フラグの穴は前記パッケージング材料を配置する段階の後にも露出されており、かつ前記リード(13)は前記半導体素子が回路板に実装される時に、前記穴が回路板ではなく外界方向を向くように曲げられる、段階；

を具備することを特徴とする半導体素子を製造する方法。

## 【発明の詳細な説明】

## 【0001】

## 【産業上の利用分野】

本発明は、一般に、半導体素子に関し、さらに詳しくは、パッケージングされた半導体素子に関する。

## 【0002】

## 【従来の技術】

10

20

例えば、加速度計、圧力センサ、化学センサ、温度センサなどのマイクロマシンデバイス(micromachined device)は、マイクロマシン機構の上に保護カバーを最初に設けないと、低コストのプラスチック・パッケージに成形できない。しかし、保護カバーは、マイクロマシンデバイスを製造する複雑さおよびコストを増す。さらに、圧力センサ、化学センサおよび温度センサは、圧力、化学作用または温度の変化を検出するために、少なくとも部分的に外界に晒されるので、従来の低コスト・プラスチック・パッケージに完全密封できない。

#### 【0003】

##### 【発明が解決しようとする課題】

従って、マイクロマシンデバイスなどの半導体素子用の低コストかつ製造が簡単なパッケージを提供する必要がある。 10

#### 【0004】

##### 【実施例】

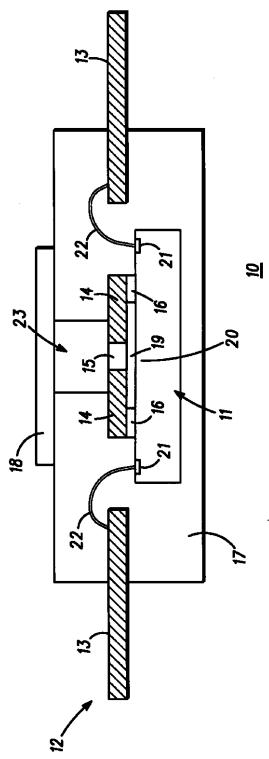

図1は、電子チップまたは基板11およびリードフレーム12を含む電子素子または半導体素子10の断面図を示す。電子デバイス20は、基板11内に形成され、この基板は、デバイス20が半導体デバイスの場合には半導体からなる。好適な実施例では、デバイス20は、例えば、圧力センサ、化学センサまたは温度センサなどのマイクロマシンセンサである。複数の露出金属領域またはボンディング・パッド21は、基板11の周辺に設けられる。パッド21は、デバイス20に隣接し、かつ電気結合される。基板11およびデバイス20の他の詳細については、素子10の説明を簡単にするために図1では図示しない。 20

#### 【0005】

リードフレーム12は、基板11を支持するために用いられる任意の基板でもよい。リードフレーム12は、好ましくは薄い銅合金からなるが、銅トレースなどを具備する厚めのセラミック基板からなってもよい。リードフレーム12は、リード13と、このリード13に隣接する実装部、支持部、物理的結合部またはフラグ14とを含む。一実施例では、フラグ14および少なくとも一つのリード13は、約5度以内で実質的に同一面上にある。ただし、好適な実施例では、フラグ14はすべてのリード13と実質的に同一面上にある。フラグ14の中心部は開口部または穴15を有し、この穴はフラグ14によって好ましくは全体的に画定される。 30

#### 【0006】

基板11は、リードフレーム12のフラグ14の上に配置され、かつこのフラグに物理的に結合される。基板11は、パッド21がフラグ14の方向を向くように配置される。基板11の周辺内には、基板11の中心部がフラグ14の穴15の上に好ましくは配置あるいは整合される。基板11のフットプリントは、フラグ14が好ましくは基板11またはパッド21の周辺を覆わないように、フラグ14のフットプリントよりも好ましくは大きい。

#### 【0007】

接着部16は、基板11とリードフレーム12との間の結合機構を提供する。接着部16は、好ましくは、フラグ14の周辺の周りのリングである。接着部16は、穴15を覆わない。一例として、接着部16は、接着テープまたは熱可塑性接着剤でもよい。好適な実施例では、接着部は、Grand Island, NYのOccidental Chemical Corporation社製の"SumiOxy"と呼ばれるダイ装着テープ(die-attach tape)である。 40

#### 【0008】

また、接着部16は、好ましくは、フラグ14と基板11との間のスタンドオフとして機能する。本好適な実施例では、スペース、ギャップまたはキャビティ19がフラグ14と基板11の中央部との間に形成される。デバイス20がマイクロマシンセンサである場合、デバイス20のマイクロマシン部分(すなわち、圧力センサまたは化学センサなどの薄い半導体膜またはダイアフラム)は、キャビティ19内で保護される。従って、キャビティ19の高さは、デバイス20が、例えば、圧力センサである場合に、デバイス20のダ 50

イアフラムの適切な動きを可能にするために十分大きくなければならない。好適な実施例では、キャビティ 19 は約 25 ~ 75 マイクロメートルの深さを有し、接着部 16 は約 25 ~ 75 マイクロメートルの高さを有する。従って、素子 10 は、デバイス 20 のマイクロマシン部分を保護するために個別のカバーまたはキャップを必要としない。よって、素子 10 は少ない工程で製造でき、その結果、より迅速かつ安価な製造プロセスが得られる。

#### 【 0 0 0 9 】

素子 10 の製造または作製における以降の工程は、パッド 21 をリードフレーム 12 のリード 13 に電気結合することを含む。好適な実施例では、複数のワイヤ・ボンド 22 が電気結合を行う。ただし、TAB (tape-automated-bonding)、フリップ・チップ・ボンディング技術なども、電気結合を行うために利用できる。フリップ・チップ・ボンディングを利用した場合、リードフレーム 12 の上に基板 11 を実装する段階は、本質的に電気結合段階を含む。さらに、フリップ・チップ・ボンディングを利用した場合、ボンディング・パッド 21 はリード 13 の反対面に電気結合される。

10

#### 【 0 0 1 0 】

電気結合段階の次に、封入材料またはパッケージング材料 17 が基板 11 およびリードフレーム 12 の周りに設けられる。材料 17 は、デバイス 20 およびワイヤ・ボンド 22 を湿気、腐食、汚染、物理的衝撃などから保護するために用いられる。材料 17 は、特にリードフレーム 12 がセラミック基板からなる場合に、プラスティック・カバーまたは金属蓋でもよいが、材料 17 は好ましくは高圧のトランスファ成形材料などである。好適な実施例では、フラグ 14 とリード 13 の同一面性はパッケージング工程でも維持される。

20

#### 【 0 0 1 1 】

材料 17 は、材料 17 がフラグ 14 の穴 15 を覆わないように、穴または開口部 23 を有して形成される。従って、穴 15 は、パッケージング工程後も露出されたままである。開口部 23 および穴 15 は、デバイス 20 が温度、化学作用、圧力などについて外界を検出することを可能にする。

#### 【 0 0 1 2 】

次に、任意のキャップまたはカバー 18 を穴 15 の上に実質的に配置し、材料 17 に接着できる。一例として、カバー 18 は、デバイス 20 が化学センサである場合には、フィルタからなってもよい。別の例では、カバー 18 は、デバイス 20 が圧力センサまたは温度センサである場合には、ポートからなってもよい。この例の代替例として、カバー 18 は、パッケージング工程の前、あるいは基板 11 をリードフレーム 12 に接着する前に、基板 11 の反対のフラグ 14 の表面に接着できる。これらの代替実施例でも、材料 17 はデバイス 20 を外界に晒すための開口部 23 を有する。

30

#### 【 0 0 1 3 】

図 1 では図示しないが、素子 10 のリード 13 は典型的な構成で実質的に曲げられる。好ましくは、リード 13 は、素子 10 が回路板に実装されるときに、デバイス 20、穴 15 および開口部 23 が回路板ではなく外界方向を向くように、カバー 18 から離して曲げられる。このように、リード 13 は、素子 10 が表面実装デバイスとなるように、曲げられて、パッケージング材料 17 に近接して形成できる。

40

#### 【 0 0 1 4 】

素子 10 について、多くの代替実施例が存在する。一代替実施例では、フラグ 14 が十分大きければ、第 2 電子基板（図示せず）をフラグ 14 上に実装して、パッケージング材料 17 内に封入できる。この代替実施例では、第 2 電子基板は、基板 11 が実装されたフラグ 14 と同じ面または反対面に実装してもよい。第 2 電子基板がフラグ 14 の反対面に実装される場合、第 2 素子は上記の理由によりフラグ 14 の穴 15 を覆ってはならない。この例では、第 2 電子基板は、デバイス 20 に電気結合された集積回路を含むことができ、センサまたはデバイス 20 の機能または精度を向上させるために利用できる。この実施例では、第 2 電子基板のボンディング・パッドは、集積回路をデバイス 20 に電気結合するためにワイヤ・ボンドを利用する場合には、基板 11 から離れて対向できる。あるいは、

50

第2電子基板のボンディング・パッドは、第2電子基板がフリップ・チップ基板である場合には、基板11の方向に対向できる。

【0015】

別の代替実施例として、第2電子基板(図示せず)をリードフレーム12の第2フラグ(図示せず)の上に実装できる。さらに別の図示しない代替実施例では、複数の電子基板を支持するためにフラグレス・リードフレーム(flagless leadframe)を利用するなどを含む。さらに、素子10において第3、第4または他の追加電子基板を基板11とともにパッケージングする場合に、前記の代替実施例のさまざまな組み合わせも利用できる。

【0016】

従って、改善されたパッケージング半導体素子が提供され、従来技術の欠点を克服する。

この半導体素子の製造プロセスは、半導体素子のマイクロマシン部分を保護するために個別のキャップ用チップを必要としないので、低コストで、複雑でない。

10

【図面の簡単な説明】

【図1】本発明による半導体素子の実施例の断面図である。

【符号の説明】

- 10 電子素子または半導体素子

- 11 電子チップまたは基板

- 12 リードフレーム

- 13 リード

- 14 フラグ

- 15 開口部または穴

- 16 接着部

- 17 封入またはパッケージング材料

- 18 キャップまたはカバー

- 19 キャビティ

- 20 電子デバイス

- 21 ボンディング・パッド

- 22 ワイヤ・ボンド

- 23 穴または開口部

20

【図1】

---

フロントページの続き

(56)参考文献 特開平09-119875(JP,A)

特開平07-038046(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/50

H01L 23/28

H01L 23/08