**PCT**

WELTORGANISATION FÜR GEISTIGES EIGENTUM

Internationales Büro

INTERNATIONALE ANMELDUNG VERÖFFENTLICHT NACH DEM VERTRAG ÜBER DIE

INTERNATIONALE ZUSAMMENARBEIT AUF DEM GEBIET DES PATENTWESENS (PCT)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |                                                                                                                            |                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| (51) Internationale Patentklassifikation 5 :<br><br>H05K 3/24, 3/06, 3/34, 3/40, 3/42, 3/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  | A1                                                                                                                         | (11) Internationale Veröffentlichungsnummer: <b>WO 94/26081</b>           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |                                                                                                                            | (43) Internationales Veröffentlichungsdatum: 10. November 1994 (10.11.94) |

| (21) Internationales Aktenzeichen: PCT/EP93/01004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  | (81) Bestimmungsstaaten: JP, KR, US, europäisches Patent (AT, BE, CH, DE, DK, ES, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE). |                                                                           |

| (22) Internationales Anmeldedatum: 26. April 1993 (26.04.93)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  | Veröffentlicht<br><i>Mit internationalem Recherchenbericht.</i>                                                            |                                                                           |

| (71) Anmelder ( <i>für alle Bestimmungsstaaten ausser US</i> ): P.A.C. DI BEZZETTO SANDRO & C.S.N.C. [IT/IT]; Via Ronchi - Z.A.I., I-37050 Angiari (IT).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |                                                                                                                            |                                                                           |

| (72) Erfinder; und<br>(75) Erfinder/Anmelder ( <i>nur für US</i> ): BEZZETTO, Sandro [IT/IT]; Viale Ungheria, 69, I-37050 Cerea (IT).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |                                                                                                                            |                                                                           |

| (74) Anwalt: HILGERS, Hans; Grünecker, Kinkeldey, Stockmair & Partner, Maximilianstrasse 58, D-8000 München 22 (DE).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                                                                                                                            |                                                                           |

| (54) Title: PROCESS FOR PRODUCING PRINTED CIRCUIT BOARDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |                                                                                                                            |                                                                           |

| (54) Bezeichnung: VERFAHREN ZUR HERSTELLUNG EINER LEITERPLATTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |                                                                                                                            |                                                                           |

| <b>(57) Abstract</b><br><p>A process is disclosed for producing a printed circuit board with a first and a second face. A plurality of connections (pads) for soldering electronic components and a plurality of tracks which interconnect the pads are applied on at least the first surface. A layer of solder (6) is applied on the pads by means of a first photoresist layer (3); the tracks are structured thereon by etchants by means of a second photoresist layer (7) which remains on the tracks and on the layer of solder (6) applied on the connections (10) of the pads (4). A solder resist (8) may then be applied on the printed circuit board outside of the pads (4). A process is also disclosed for manufacturing a mask suitable for implementing this printed circuit board production process. According to said process, said masks are produced in a simple manner from known base masks.</p> |  |                                                                                                                            |                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |                                                                                                                            |                                                                           |

**(57) Zusammenfassung**

Bei einem Verfahren zur Herstellung einer Leiterplatte mit einer ersten und einer zweiten Oberfläche, wobei wenigstens auf der ersten Oberfläche eine Vielzahl von Anschlußkontakten (Pads) zum Auflöten von elektronischen Bauelementen und eine Vielzahl von die Pads verbindenden Leiterbahnen aufgebracht sind, wird mittels einer ersten Photoresistschicht (3) eine Lötsschicht (6) auf die Pads (4) aufgetragen; darauf werden die Leiterbahnen mittels einer zweiten Photoresistschicht (7) strukturiert durch Ätzen, wobei die zweite Photoresistschicht (7) auf den Leiterbahnen und auf der Lötsschicht (6) von Anschlußstücken (10) der Pads (4) verbleibt. Nachfolgend kann ein Lötstopplack (8) auf die Leiterplatte außerhalb der Pads (4) aufgetragen werden. Weiterhin wird ein Herstellungsverfahren für eine bei dem Herstellungsverfahren der Leiterplatten verwendbare Masken vorgeschlagen. Bei dem letztgenannten Verfahren sind die erfindungsgemäßen Masken in einfacher Weise aus bekannten Grundmasken herstellbar.

**LEDIGLICH ZUR INFORMATION**

Codes zur Identifizierung von PCT-Vertragsstaaten auf den Kopfbögen der Schriften, die internationale Anmeldungen gemäss dem PCT veröffentlichen.

|    |                                |    |                                   |    |                                |

|----|--------------------------------|----|-----------------------------------|----|--------------------------------|

| AT | Österreich                     | GA | Gabon                             | MR | Mauretanien                    |

| AU | Australien                     | GB | Vereinigtes Königreich            | MW | Malawi                         |

| BB | Barbados                       | GE | Georgien                          | NE | Niger                          |

| BE | Belgien                        | GN | Guinea                            | NL | Niederlande                    |

| BF | Burkina Faso                   | GR | Griechenland                      | NO | Norwegen                       |

| BG | Bulgarien                      | HU | Ungarn                            | NZ | Neuseeland                     |

| BJ | Benin                          | IE | Irland                            | PL | Polen                          |

| BR | Brasilien                      | IT | Italien                           | PT | Portugal                       |

| BY | Belarus                        | JP | Japan                             | RO | Rumänien                       |

| CA | Kanada                         | KE | Kenya                             | RU | Russische Föderation           |

| CF | Zentrale Afrikanische Republik | KG | Kirgisistan                       | SD | Sudan                          |

| CG | Kongo                          | KP | Demokratische Volksrepublik Korea | SE | Schweden                       |

| CH | Schweiz                        | KR | Republik Korea                    | SI | Slowenien                      |

| CI | Côte d'Ivoire                  | KZ | Kasachstan                        | SK | Slowakei                       |

| CM | Kamerun                        | LI | Liechtenstein                     | SN | Senegal                        |

| CN | China                          | LK | Sri Lanka                         | TD | Tschad                         |

| CS | Tschechoslowakei               | LU | Luxemburg                         | TG | Togo                           |

| CZ | Tschechische Republik          | LV | Lettland                          | TJ | Tadschikistan                  |

| DE | Deutschland                    | MC | Monaco                            | TT | Trinidad und Tobago            |

| DK | Dänemark                       | MD | Republik Moldau                   | UA | Ukraine                        |

| ES | Spanien                        | MG | Madagaskar                        | US | Vereinigte Staaten von Amerika |

| FI | Finnland                       | ML | Mali                              | UZ | Usbekistan                     |

| FR | Frankreich                     | MN | Mongolei                          | VN | Vietnam                        |

## Verfahren zur Herstellung einer Leiterplatte

Die Erfindung betrifft ein Verfahren zur Herstellung einer Leiterplatte mit einer ersten und zweiten Oberfläche, wobei wenigstens auf der ersten Oberfläche eine Vielzahl von Anschlußkontakten (Pads) zum Auflöten von elektronischen Bauelementen und eine Vielzahl von die Pads verbindenden Leiterbahnen aufgebracht sind. Weiterhin betrifft die Erfindung ein Verfahren zur Herstellung von Masken zur Belichtung von Photoresistschichten, welche bei der Herstellung einer Leiterplatte nach dem vorangegangenen Verfahren einsetzbar sind. Schließlich betrifft die Erfindung eine Leiterplatte mit auf wenigstens auf einer Oberfläche angeordneten Pads und Leiterbahnen aus einem auf einem isolierenden Substrat der Leiterplatte aufgetragenen Metall, mit zumindest auf den Pads aufgetragener Lötschicht und mit einer auf der Leiterplatte außer auf den Pads aufgetragener Lötstoppschicht. Eine solche Leiterplatte ist nach dem erstgenannten Verfahren herstellbar.<sup>2</sup>

Es ist allgemein bekannt, daß Schaltkreise der Mikroelektronik überwiegend auf aus elektrisch isolierenden, mit strukturierten Leiterbahnen versehenen Platten aufgebaut sind. Die Leiterplatte bildet im allgemeinen die untere Ebene elektronischer Aufbauten in Schaltkreisebenen. Die Größe der Leiterplatten kann bis zu mehreren  $\text{dm}^2$  betragen, wobei die Leiterplatte beispielsweise aus Polymeren, wie Epoxidharz, hergestellt und meist mit einer Kupfermetallisierung beschichtet ist. Bei Zwei- und Mehrlagenverdrahtung sind in der Leiterplatte Verbindungslöcher zu stanzen und durchgehend zu metallisieren, damit die elektrischen Verbindungen durch das Verbindungsloch durchreichen. Der Aufbau der mikroelektronischen Schaltkreise erfolgt auf den Leiterplatten durch entsprechendes Auflöten der einzelnen Mikroelektronikbauelemente. Dazu werden bei einer Technologie die Bauelemente auf einer Bauteileseite der Leiterplatte mit

ihren Anschlüssen auf mit einer Lötschicht versehene Kontaktstellen (Pads) gesetzt und entsprechend angelötet. Diese Technik wird als SMD-Technik (Service Mount Devices) bezeichnet.

Bei einer anderen Technik werden die Bauelemente mit ihren Anschlüssen in Verbindungsbohrungen der Leiterplatte eingesetzt und auf einer der Bauteileseite gegenüberliegenden Lötseite der Leiterplatte zur Verbindung mit entsprechenden Leiterbahnen verlötet.

Zur Herstellung einer solchen Leiterplatte ist beispielsweise aus dem Hobbybereich ein Verfahren bekannt, das allerdings nicht für höherintegrierte Schaltkreise verwendbar ist. Bei diesem Verfahren wird auf der Leiterplatte die gesamte Schaltung aus Pads, Leiterbahnen und dergleichen, beispielsweise durch Aufdrucken (Siebdruckverfahren) oder lithographische Verfahren auf eine Kupfermetallisierung der Leiterplatte übertragen. Darauf folgend werden Verbindungsbohrungen zur Verbindung der Bauteileseite und Lötseite in der Leiterplatte durch Bohren oder Stanzen erzeugt. Durch eine Kupferbeschichtung im Inneren der Verbindungsbohrungen wird eine leitende Verbindung zwischen den beiden Seiten der Leiterplatte hergestellt. Anschließend wird galvanisch auf der gesamten Schaltung eine Lötschicht, insbesondere auch als Ätzschutz aufgetragen. Die Lötschicht ist ebenfalls innerhalb der Durchgangsbohrungen aufgetragen. Danach wird die freiliegende Kupfermetallisierung durch Ätzen entfernt und es verbleibt die strukturierte Schaltung, die durch mit der Lötschicht beschichtetes Kupfer gebildet ist.

Schließlich wird auf der Schaltung ein Lötstopplack durch Siebdruck oder einen Photoprozeß aufgebracht, wobei dieser Lack nicht auf den Pads und den Verbindungsbohrungen angeordnet wird. Als letztes werden die elektronischen Bauteile auf den Pads oder in den Verbindungsbohrungen durch die aufgetragene Lötschicht auf der Leiterplatte angelötet.

Nachteilig bei dem vorstehenden Verfahren ist, daß durch Auftragen der Lötschicht auf den Leiterbahnen beim Verlöten der elektronischen Bauteile Wärme entlang der Leiterbahnen und Lötschicht transportiert wird, wodurch die Lötschicht auf den Leiterbahnen eine unebene, wellige Struktur annimmt. Aufgrund der Welligkeit der Lötschicht auf den Leiterbahnen ist dieses Verfahren für höherintegrierte Schaltkreise nicht verwendbar.

Bei einem weiteren, aus der Praxis bekannten Verfahren, das insbesondere auch für höherintegrierte Schaltkreise der Mikroelektronik verwendbar ist, wird ein Schaltungsentwurf für Leiterbahnen, Pads und dergleichen durch CAD-Verfahren hergestellt. Der Schaltungsentwurf wird beispielsweise über einen Photoplotter auf ein photographisches Negativ (oder Positiv) als Maske übertragen. Die Strukturierung der Metallisierung auf der Leiterplatte erfolgt dann durch Belichten einer lichtempfindlichen Photoresistschicht mittels der Maske. Nach teilweisem Entfernen der Photoresistschicht ist die gewünschte Struktur auf die Metallisierung (Kupferschicht) übertragen. Die gesamte Schaltung wird mittels einer Maske strukturiert. Darauf folgt wie bei dem oben genannten Verfahren ein Bohren oder Stanzen von Verbindungsbohrungen, eine Metallbeschichtung der Verbindungsbohrungen im Inneren, ein galvanisches Auftragen einer Lötschicht als Ätzschutz und das Entfernen der freiliegenden Metallisierung.

Im Gegensatz zu dem vorhergehend genannten Verfahren wird nun die gesamte Lötschicht von der Schaltung entfernt, so daß eine nur aus der auf der Leiterplatte aufgebrachten Metallschicht gebildete Schaltung verbleibt. Diese wird mechanisch poliert, um sie zum Auftragen eines Lötstopplackes vorzubereiten. Dieser Lack wird auf der gesamten Schaltung außer auf den Pads und den Verbindungsbohrungen aufgetragen. Darauffolgend werden die Pads chemisch poliert und das sogenannte H.A.L.-Verfahren (Hot Air Levelling) angewendet. Bei diesem Verfahren wird die Leiterplatte in ein Bad mit der flüssigen Lötschicht eingetaucht. Beim

Herausnehmen der Leiterplatte haftet die Lötschicht hauptsächlich auf den Pads. Überschüssiges Material der Lötschicht wird von den Pads und vom Rest der Leiterplatte durch Abblasen mit heißer Luft entfernt. Die Lötschicht ist in der Regel aus einer Legierung von Blei und Zinn gebildet. Die Lötschicht kann insbesondere zur Bildung einer glänzenden Oberfläche nochmals aufgeschmolzen werden. Dies erfolgt in der Regel durch Infrarotbestrahlung.

Danach können in üblicher Weise die elektronischen Bauteile aufgelötet werden.

Bei dem letztgenannten Verfahren ist insbesondere von Nachteil, daß die auf der gesamten Schaltung aufgetragene Lötschicht insgesamt entfernt werden muß. Dies erfolgt durch ein chemisches Verfahren unter Verwendung von Säuren. Diese, wie auch die abgeätzte Lötschicht müssen aufwendig entsorgt und gegebenenfalls zurückgewonnen werden. Da die Lötschicht auch von den Pads abgeätzt wird, muß in einem zusätzlichen Verfahrensschritt die Lötschicht erneut auf den Pads aufgetragen werden. Bei dem H.A.L.-Verfahren wird die Lötschicht heiß aufgetragen, wobei insbesondere bei einem Bleianteil an der Lötschicht dessen Toxizität zu beachten und entsprechende Maßnahmen zu ergreifen sind. Insbesondere ist zu beachten, daß einige Länder, wie beispielsweise die USA ein Verbot des Einsatzes von flüssigem Blei bei Produktionsprozessen in Betracht ziehen oder zumindest mit strengen Auflagen versehen wollen.

Ein weiterer Nachteil bei dem letztgenannten Verfahren ist, daß beim heißen Abblasen von überschüssiger Lötschicht beim H.A.L.-Verfahren kleine, heiße Tröpfchen der Lötschicht auf der Lötstoppschicht verbleiben können und dort zu einem Defekt der Lötstoppschicht führen können. Dies kann zu Kurzschlüssen der Leiterbahnen führen.

Ebenfalls von Nachteil bei dem H.A.L.-Verfahren ist, daß die Schichtdicke der Lötschicht ungleichmäßig ist. Bei dem Herausziehen der Leiterplatte aus der flüssigen Lötschicht und bei dem nachfolgenden Abblasen von überschüssigem Material erstarrt die Lötschicht nicht mit gleichmäßiger Schichtdicke, sondern ungleichmäßig aufgeworfen. Dadurch kann beim Auflöten der elektronischen Bauteile eine schlechte Kontaktierung erfolgen, da eine Verbindungsleitung des elektronischen Bauteils beispielsweise in einem Bereich der Lötschicht angeordnet ist, wo diese mit einer zu geringen Dicke ausgebildet ist. Auch bei dem Aufschmelzen der Lötschicht zur Herstellung einer glänzenden Oberfläche der Lötschicht wird deren Schichtdicke hinsichtlich ihrer Gleichförmigkeit nicht verbessert. Stattdessen kann sich die Lötschicht aufgrund ihrer Oberflächenspannung beim Aufschmelzen zusammenziehen und beispielsweise halbkugelförmig erstarren. Wird die auf diese Weise "zusammengeschrumpfte" Lötschicht nicht genau von einer Verbindungsleitung des elektronischen Bauteils getroffen, ergibt sich eine schlechte oder möglicherweise gar keine leitende Verbindung.

Der Erfindung liegt daher die Aufgabe zugrunde, ein vereinfachtes Verfahren zur Herstellung einer Leiterplatte bereitzustellen, bei dem eine Lötschicht gleichförmiger Schichtdicke einmalig nur auf den zum Verlöten benötigten Kontaktstellen der Leiterplatte aufgetragen wird.

Diese Aufgabe wird durch die im Anspruch 1 aufgelisteten Verfahrensschritte gelöst. Bei dem erfindungsgemäßen Verfahren werden zuerst die Pads mittels einer ersten Maske strukturiert. Sind die Pads nach entsprechender Belichtung mit der ersten Maske von der zugehörigen Photoresistschicht befreit, wird eine Lötschicht nur auf die Pads mit vorbestimmter Schichtdicke aufgetragen. Danach kann der verbliebene Rest der ersten Photoresistschicht entfernt werden. Ein nachfolgendes Entfernen der Lötschicht wie beim H.A.L.-Verfahren ist nicht notwendig, da

diese Schicht nur auf die zum Verlöten benötigten Kontaktstellen (Pads) der Leiterplatte aufgetragen wurde. Vor Entfernen der überflüssigen Metallisierung der Leiterplatte wird eine zweite Photoresistschicht mittels einer zweiten Maske zum Strukturieren der Leiterbahn aufgetragen. Dabei verbleibt die zweite Photoresistschicht nach Belichten auf den Leiterbahnen und zumindest teilweise auf den Pads, wobei der Übergangsbereich von Pads und zugehöriger Leiterbahn ebenfalls von der zweiten Photoresistschicht bedeckt ist. Wird nun die freiliegende Metallisierung entfernt, sind die Leiterbahnen durch die zweite Photoresistschicht und die Pads durch die Lötschicht geschützt, so daß in diesen Bereichen die Metallisierung nicht entfernt wird. Dabei ist zu beachten, daß die Pads sowohl von Lötschicht als auch zumindest teilweise von der zweiten Photoresistschicht geschützt werden. Eine Unterbrechung der Verbindung von Anschlußstück und Leiterbahn kann bei dem erfindungsgemäßen Verfahren nicht erfolgen, da die Metallisierung durch die zweite Photoresistschicht und die Lötschicht vor einem Entfernen geschützt ist. Nachfolgend kann in üblicher Weise ein Lötstopplack auf der Leiterplatte außerhalb der Pads aufgetragen werden.

Nach einer bevorzugten Ausführungsform der Erfindung werden die Pads bei ihrer Strukturierung mit Anschlußstücken hergestellt. Die Anschlußstücke weisen im wesentlichen in Richtung der nachfolgend zu strukturierenden Leiterbahnen und dienen zur Verbindung von Pads und Leiterbahnen. Die zweite Photoresistschicht ist außer auf den Leiterbahnen insbesondere auf den die Anschlußstücke bildenden Teilen der Pads aufgetragen, wodurch ein Überlapp von Lötschicht und zweiter Photoresistschicht auftritt.

Bei dem erfindungsgemäßen Verfahren entfällt das Entfernen der Lötschicht von den Leiterbahnen. Dadurch entfällt die entsprechende chemische Behandlung und Abfallentsorgung beziehungsweise Rückgewinnung der chemischen Mittel (Säuren) und der Lötschicht. Ebenso entfällt beim erfindungsgemäßen Verfahren das

erneute Auftragen der Lötschicht, wobei insbesondere keine giftige, flüssige Lötschicht benötigt wird. Ein heißes Abblasen von überschüssiger Lötschicht ist ebensowenig bei dem erfindungsgemäßen Verfahren notwendig. Dadurch können keine Defekte im Lötstopplack durch heiße Tröpfchen der Lötschicht auftreten. Da die Lötschicht mit gleichmäßiger Schichtdicke aufgetragen wird, ist ein Auflöten der elektronischen Bauteile im gesamten Bereich des Pads sichergestellt.

Das in Anspruch 1 beschriebene Verfahren ist insbesondere für SMD verwendbar, wobei die elektrischen Kontakte der elektronischen Bauteile auf den Kontakt- oder Anschlußflächen (Pads) der Leiterplatten aufgesetzt und anschließend beispielsweise durch Wellenlöten verlötet werden. Zur Verbindung beider Seiten einer Leiterplatte, wobei zumindest auf der Bauteileseite das erfindungsgemäße Verfahren angewendet wird, können im Verfahrensschritt ii) nach Anspruch 1 zusätzliche, Bohrungspunkte bildende Pads mit entsprechenden Anschlußstücken zur Herstellung von Verbindungsbohrungen zur Verbindung beider Seiten der Leiterplatte strukturiert werden. Nach Bohren oder Stanzen der Verbindungsbohrungen werden diese zumindest in ihrem Inneren mit einer Metallisierung versehen. Im Folgenden werden die auf diese Weise metallisierten Verbindungsbohrungen in gleicher Weise wie die Pads im Anspruch 1 weiterbehandelt, das heißt, eine Lötschicht wird mit gleichmäßiger Dicke innerhalb der Verbindungsbohrungen und auf deren Anschlußstücken aufgetragen, eine zweite Photoresistschicht wird aufgetragen, belichtet und anschließend zumindest teilweise entfernt. Werden die Verbindungsbohrungen auch zum Einsticken von Anschlußdrähten von elektronischen Bauteilen verwendet, wird entsprechend nach Verfahrensschritt vi) aus Anspruch 1 in analoger Weise kein Lötstopplack auf den Verbindungsbohrungen aufgetragen. Der Lötstopplack kann entsprechend zu den vorbekannten Verfahren durch Siebdruck oder einen Photoprozeß aufgetragen werden.

Um eine sehr gleichmäßige Schichtdicke der Lötschicht in einfacher Weise zu erzielen, ist es von Vorteil, wenn die Lötschicht galvanisch aufgetragen wird. Durch diese Art der Auftragung erzielt man eine sehr ebene Oberfläche der Lötschicht mit einer kontrollierten Schichtdicke.

Je nach dem, ob eine positive oder negative Photoresistschicht als erste oder zweite Photoresistschicht verwendet wird, sind die entsprechenden Masken als Negativ- oder Positivmaske ausgebildet. Bei einer bevorzugten Ausführungsform wird in den Schritten ii) und v) aus Anspruch 1 als erste Maske eine Positivmaske und als zweite Maske eine Negativmaske verwendet, wobei die erste Photoresistschicht außerhalb der Pads/Bohrungspunkte und zugehörigen Anschlußstücke und die zweite Photoresistschicht auf den Leiterbahnen belichtet wird. In diesem Fall wird der unbelichtete Teil der ersten Photoresistschicht vor dem Auftragen der Lötschicht entfernt. Von der zweiten Photoresistschicht wird ebenfalls der unbelichtete Teil entfernt, wobei der belichtete Teil oberhalb der zu strukturierenden Leiterbahnen verbleibt.

Obwohl nach dem erfindungsgemäßen Verfahren ein nachträgliches Aufschmelzen der Lötschicht zur Herstellung einer gut lötbaren Legierung nicht notwendig ist, kann die Aufschmelzung durchgeführt werden. Dadurch erhält die im wesentlichen eine matte Oberfläche aufweisende Lötschicht eine glänzende Oberfläche. Die Schichtdicke wird bei dem Aufschmelzen nicht verändert.

Dabei ist es weiterhin von Vorteil, wenn das Aufschmelzen durch entsprechende Infrarotbestrahlung erfolgt.

Der Lötstopplack kann bei dem erfindungsgemäßen Verfahren sowohl durch einen Photoprozeß als auch durch Siebdruck oder der gleichen aufgetragen werden.

Bei sehr feinen Leiterbahnen ist es günstig, wenn die Strukturierung des Anschlußstücks mit einem Vergleich zur Leiterbahn größeren Breite im Schritt ii) in Anspruch 1 erfolgt. Bei breiteren Leiterbahnen weist das Anschlußstück in der Regel die gleiche Breite wie die Leiterbahn auf, wobei es im wesentlichen aus einem Endstück der beispielsweise zwei Pads verbindenden Leiterbahn gebildet ist. Bei nicht zu feinen Leiterbahnen ergeben sich keine Schwierigkeiten bei dem Überlappen von zweitem Photoresist und Anschlußstück, so daß nach dem Entfernen der Metallisierung eine Kontaktierung der Leiterbahn unterhalb des zweiten Photoresist und Anschlußstück über die gesamte Breite der Leiterbahn beziehungsweise des Anschlußstückes erfolgt. Bei feineren Leiterbahnen besteht die Möglichkeit, daß die zweite Photoresistschicht zur Strukturierung der Leiterbahnen das Anschlußstück nur teilweise überlappt. Wird in diesem Fall die nicht von der zweiten Photoresistschicht bedeckte Metallisierung entfernt, könnte der Kontakt zwischen von dem zweiten Photoresist bedeckter Leiterbahn und Anschlußstück nur über einen Teil der Breite der Leiterbahn oder gegebenenfalls garnicht erfolgen. Ist allerdings das Anschlußstück breiter als die Leiterbahn ausgebildet, so ergibt sich auch bei einer geringen Fehlausrichtung der zweiten Photoresistschicht zur Strukturierung der Leiterbahnen ein guter Kontakt zwischen Anschlußstück und Leiterbahn.

Bei einem einfachen Ausführungsbeispiel der Erfindung erfolgt die Metallisierung der Leiterplatte durch Auftragen einer Kupferschicht und die Lötschicht ist durch eine PbSn-Schicht gebildet.

Bei dem erfindungsgemäßen Verfahren wird insbesondere zur Vermeidung einer Unterbrechung der Verbindung zwischen Pads/Verbindungsbohrungen und Leiterbahnen bei Entfernen der nicht notwendigen Metallisierung der Leiterplatte ein Überlapp im Kontaktbereich von Leiterbahnen und Pads/Verbindungsbohrungen hergestellt. Der Überlapp erfolgt durch sich im Kontaktbereich

überdeckende Lötschicht und zweite Photoresistschicht. Die Lötschicht verhindert ein Abätzen der Metallisierung im Bereich der Pads/Verbindungsbohrungen und die zweite Photoresistschicht verhindert ein Abätzen der Metallisierung im Bereich der zu strukturierenden Leiterbahnen. Dabei kann der Überlapp im Bereich eines Anschlußstückes der Pads beziehungsweise der Verbindungsbohrung hergestellt werden. Analog zur Erfindung ist ein entsprechender Überlapp auch dadurch herstellbar, daß beispielsweise die Leiterbahnen nach Strukturieren der Pads und Auftragen einer entsprechenden Lötschicht durch Aufdampfen, Sputtern oder dergleichen so hergestellt werden, daß sie die Pads zumindest teilweise überlappen. Dabei kann eine auf der Leiterplatte aufgetragene Metallisierung vor Auftragen der Leiterbahnen in üblicher Weise entfernt werden. In diesem Fall findet ein direkter Überlapp von Pad und Leiterbahn statt.

Bei dem erfindungsgemäßen Verfahren zur Herstellung einer Leiterplatte wird eine erste und eine zweite Maske zum aufeinanderfolgenden Beschichten einer ersten und einer entsprechenden zweiten Photoresistschicht verwendet. Demgegenüber wird die mit dem H.A.L.-Verfahren hergestellte Leiterplatte durch eine Maske insgesamt belichtet. Bei einem einfachen Verfahren zur Herstellung von Masken zur Verwendung bei dem erfindungsgemäßen Verfahren zur Herstellung der Leiterplatte weist dieses Verfahren die Verfahrensschritte nach Anspruch 12 auf. Bei dem Maskenherstellungsverfahrens werden die erste und zweite Maske in einfacher Weise aus einer ersten Grundmaske mit einem Gesamt-Lay-out der Schaltung und einer zweiten Grundmaske nur mit Pads/Bohrungspunkten hergestellt. Die zweite Grundmaske dient insbesondere zum Entfernen der Lötstoppschicht von den Pads/Bohrungspunkten.

Die erste Hilfsmaske wird aus der zweiten Grundmaske dadurch hergestellt, daß Pads und/oder Bohlungspunkte um einen ersten Vergrößerungsfaktor vergrößert werden. Dabei ist zu beachten,

daß Abstände von Flächenschwerpunkten oder Mittelpunkten der Pads und/oder Bohrungspunkte nicht vergrößert werden, sondern nur der Querschnitt dieser Strukturen vergrößert wird. Wird die erste Grundmaske mit der ersten Hilfsmaske überlagert, wird durch die vergrößerten Strukturen auf der ersten Hilfsmaske eine gewisse Umgebung von Pads und/oder Bohrungspunkten mit auf die erste Maske übertragen. Die Umgebung der Pads und/oder Bohrungspunkte der ersten Grundmaske ist dabei so groß gewählt, daß benachbarte Pads und/oder Bohrungspunkte nicht erfaßt werden. Allerdings wird ein Teil der mit den Pads und/oder Bohrungspunkten verbundenen Leiterbahn als im Anspruch 2 erwähntes Anschlußstück mit auf die erste Maske übertragen. Folglich zeigt das Lay-out der ersten Maske die Anordnung aller Pads und/oder Bohrungspunkte zusammen mit an diesen anschließenden Endbereichen der Leiterbahnen als Anschlußstücke.

Eine zweite Hilfsmaske wird aus der zweiten Grundmaske durch entsprechende Vergrößerung der Pads und/oder Bohrungspunkte wie bei der ersten Hilfsmaske hergestellt. In diesem Fall erfolgt die Vergrößerung mit einem im Vergleich zum ersten Vergrößerungsfaktor kleineren zweiten Vergrößerungsfaktor. Durch Überlagerung der zweiten Hilfsmaske und der ersten Grundmaske wird die zweite Maske hergestellt. Diese weist nur die Leiterbahnen von der ersten Grundmaske auf, da die zweite Hilfsmaske insbesondere die Pads und/oder Bohrungspunkte aus der ersten Grundmaske ausblendet. Da der zweite Vergrößerungsfaktor kleiner als der erste Vergrößerungsfaktor ist, ist eine auf der zweiten Maske dargestellte Leiterbahn beispielsweise zwischen zwei ausgewählten Pads länger als die Entfernung zwischen den entsprechenden Anschlußstücken der ersten Maske. Dadurch überlappen sich die mittels der ersten Maske erzeugten Anschlußstücke und die mittels der zweiten Maske belichteten Bereiche einer Photore sistsschicht zur Bildung der Leiterbahnen.

Bei diesem erfindungsgemäßen Verfahren zur Herstellung der Masken ist insbesondere von Vorteil, daß durch Vergrößerung der Pads und/oder Bohrungspunkte auf der ersten beziehungsweise zweiten Hilfsmaske die Geometrie von Pads, Bohrungspunkten und Leiterbahnen oder sonstiger Bestandteile der Schaltung erhalten bleibt. Das heißt, bei einem kreisförmigen Pad wird mittels der ersten Hilfsmaske eine kreisförmige Umgebung dieses Pads zusammen mit dem Pad auf der ersten Maske erzeugt. Entsprechendes gilt für beliebig geformte Pads und/oder Bohrungspunkte. In jedem Fall sind die Pads und/oder Bohrungspunkte auf allen Masken geometrisch ähnlich zueinander:

In diesem Zusammenhang ist es weiterhin von Vorteil, wenn die Überlagerung von erster und zweiter Hilfsmaske mit der ersten Grundmaske so erfolgt, daß Flächenschwerpunkte von Pads und/oder Bohrungspunkten auf Hilfsmaske und Grundmaske übereinanderliegen. Auf diese Weise wird die auf die erste Maske übertragene beziehungsweise von der zweiten Maske ausgeblendete Umgebung von Pads und/oder Bohrungspunkten symmetrisch um Pads und/oder Bohrungspunkte gebildet.

Der Entwurf und die Herstellung von Grundmasken, erster und zweiter Maske und zugehöriger Hilfsmasken ist insbesondere vereinfacht, wenn dies durch ein CAD-Verfahren erfolgt. Dadurch ist die gesamte Schaltung in einfacher Weise an einem Computer als Entwurf herstellbar. Der Entwurf wird in bekannter Weise auf eine Maske übertragen, wobei durch eine entsprechende Software beim CAD-Verfahren aus den so gebildeten Grundmasken die erste und zweite Hilfsmaske einfach mittels des Computers herstellbar sind. In ebenso einfacher Weise kann die Überlagerung von erster und zweiter Hilfsmaske mit der ersten Grundmaske zur Herstellung der ersten und zweiten Maske erfolgen.

In diesem Zusammenhang ist es weiterhin von Vorteil, wenn insbesondere bei feinen Leiterbahnen, an einer Verbindungsstelle von

Leiterbahn und Pad und/oder Bohrungspunkt an diesen ein gegenüber der Leiterbahn verbreitertes Anschlußstück ausgebildet ist. Das Anschlußstück kann in einfacher Weise durch Verbreiterung eines am Pad beziehungsweise Bohrungspunkt anschließenden Leiterbahnendes hergestellt werden. Weiterhin kann eine sogenannte "Teardrop"-Funktion, die bei CAD-Verfahren implementiert ist, zur Bildung der Anschlußstücke verwendet werden. In diesem Fall wird beispielsweise das in der ersten Maske vorhandene Anschlußstück nach Anspruch 12 durch den "Teardrop" ersetzt. Dieser bildet einen in Richtung der Leiterbahnen weisenden Fortsatz des Pads beziehungsweise Bohrungspunktes, wobei er so weit in Richtung der Leiterbahn reicht, daß die auf der zweiten Maske dargestellte Leiterbahnstruktur den "Teardrop" zumindest teilweise überlappt.

Bei einer nach dem erfundungsgemäßen Verfahren zur Herstellung einer Leiterplatte hergestellten Leiterplatte ergibt sich abweichend zu durch bekannte Verfahren hergestellten Leiterplatten, daß in einem Kontaktbereich von Pads und Leiterbahnen die Lötschicht auf diesen aufgetragen ist. Diese dient zum Schutz der Leiterbahn beim Abätzen der Metallisierung der Leiterplatte. Beim Stand der Technik, siehe H.A.L.-Verfahren, sind auch die Leiterbahnen beim Abätzen der Metallisierung von einer Lötschicht bedeckt.

Dabei ist es weiterhin von Vorteil, wenn der Kontaktbereich durch ein zur Verbindung von Pad und zugeordneter Leiterbahn ausgebildetes Anschlußstück gebildet ist, auf welchem die Lötschicht und auf dieser die Photoresistschicht aufgetragen ist. Durch den Überlapp von Photoresistschicht und Lötschicht wird die Verbindung von Leiterbahn zum Anschlußstück und damit zum Pad beim Abätzen der Metallisierung sichergestellt. Eine Unterbrechung durch Entfernen der Metallisierung zwischen Pad beziehungsweise Anschlußstück und Leiterbahn kann nicht erfolgen.

In diesem Zusammenhang ist es günstig, wenn das Anschlußstück von einem Endstück der Leiterbahn gebildet ist. Auf diese Weise sind Anschlußstück und Leiterbahn mit gleicher Breite ausgebildet. Dabei kann es auch von Vorteil sein, insbesondere bei feinen Leiterbahnen, wenn das Anschlußstück ein im Vergleich zur Leiterbahn größere Breite aufweist..

Wenn die Photoresistschicht im Vergleich zur Lötstoppschicht in einem größeren Abstand vom Pad endet, ergibt sich als Vorteil, daß die Lötschicht weitestgehend nur in ihrem freiliegenden Bereich auf dem Pad beim Auflöten von elektronischen Bauteilen aufgeschmolzen wird. Folglich erfolgt kein Aufschmelzen der Lötschicht bis zur Photoresistschicht.

Weist die Leiterplatte Verbindungsbohrungen zur elektrischen Verbindung von gegenüberliegenden Seiten der Leiterplatte auf, wobei die Verbindungsbohrungen auf beiden Seiten mit Leiterbahnen verbunden sein können, ist es von Vorteil, wenn wenigstens auf einer Innenseite der Verbindungsbohrung ein Metall und die Lötschicht aufgetragen sind und auf zumindest einer Seite der Leiterplatte von der Verbindungsbohrung ein entsprechendes Anschlußstück mit aufgetragener Lötschicht und Photoresistschicht sowie Lötstoppschicht absteht. Als Metall beziehungsweise Material der Lötschicht sind insbesondere Cu beziehungsweise PbSn verwendbar.

Bei dem erfindungsgemäßen Verfahren zur Herstellung einer Leiterplatte beziehungsweise bei der nach diesem Verfahren hergestellten Leiterplatte ist weiterhin von Vorteil, daß durch die gleichmäßige Schichtdicke der aufgetragenen Lötschicht eine optische Kontrolle der Leiterplatte vereinfacht ist. Diese Kontrolle erfolgt dadurch, daß das von den Lötschichten reflektierte Licht erfaßt und zur Überprüfung der Anordnung zumindest der Pads ausgewertet wird. Eine solche optische Kontrolle der Leiterplatte ist bei dem bekannten Verfahren mit H.A.L. nur

schwierig oder gar nicht möglich, da das Licht durch die unebene, wellenförmige Oberfläche der Lötschicht in viele Richtungen reflektiert wird. Stattdessen wird bei der erfindungsgemäß hergestellten Leiterplatte das Licht im wesentlichen nur senkrecht zur Lötschicht reflektiert. Auf diese Weise kann eine genauere Lokalisierung, insbesondere der Pads auf der Leiterplatten bei der optischen Kontrolle erfolgen, wodurch die Kontrolle einfacher und genauer erfolgen kann. In diesem Zusammenhang sei weiterhin angemerkt, daß die optische Kontrolle insbesondere bei matten Oberflächen der Lötschicht zuverlässig ist. Solche Oberflächen liegen bei dem erfindungsgemäßen Verfahren zur Herstellung der Leiterplatten naturgemäß vor, wenn nicht ein Aufschmelzen der Lötschicht beispielsweise durch Infrarotstrahlung zusätzlich durchgeführt wird. Wie vorstehend ausgeführt, dient ein solches Aufschmelzen nur zum Erzeugen glänzender Oberflächen der Lötschichten, welche für die Funktionsfähigkeit der Lötschicht beziehungsweise der Leiterplatte ohne Bedeutung sind.

Im folgenden werden vorteilhafte Ausführungsbeispiele der Erfindung anhand der in der Zeichnung beigefügten Figuren näher erläutert und beschrieben.

Es zeigen:

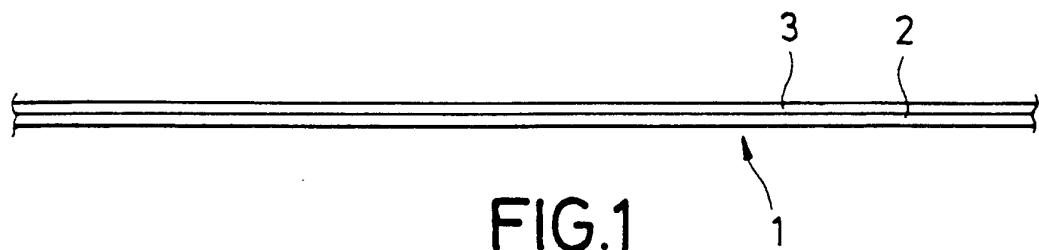

Fig.1

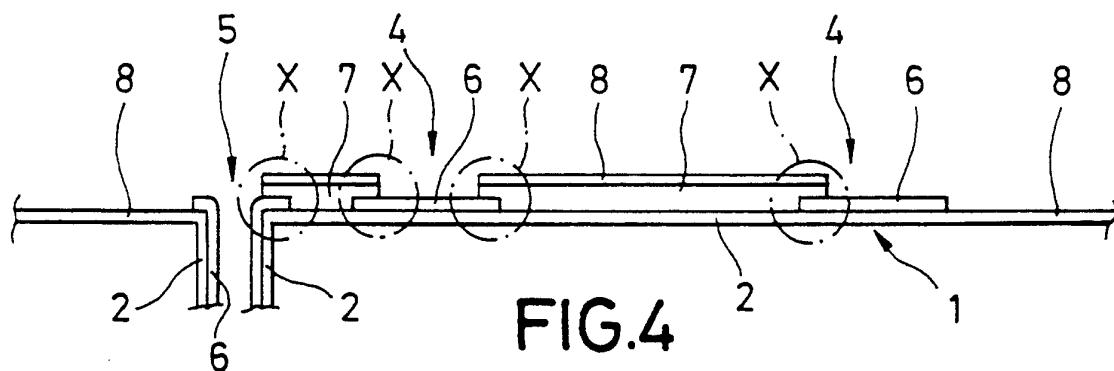

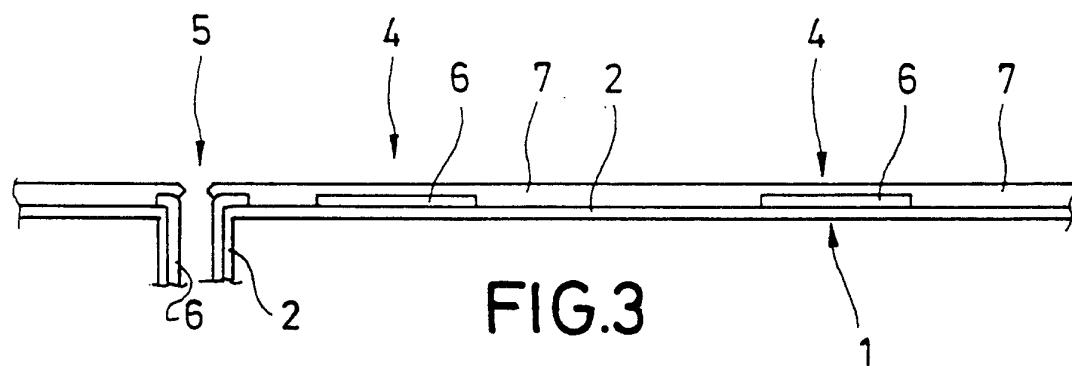

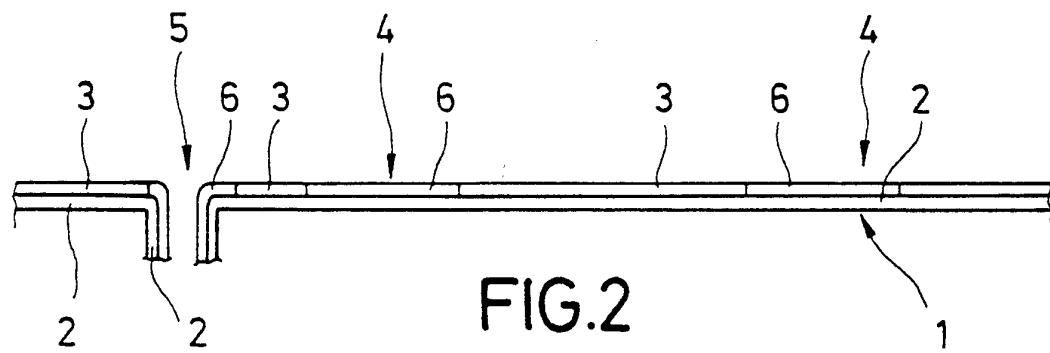

bis 4 aufeinanderfolgende Schritte des erfindungsgemäßen Verfahrens zur Herstellung einer Leiterplatte;

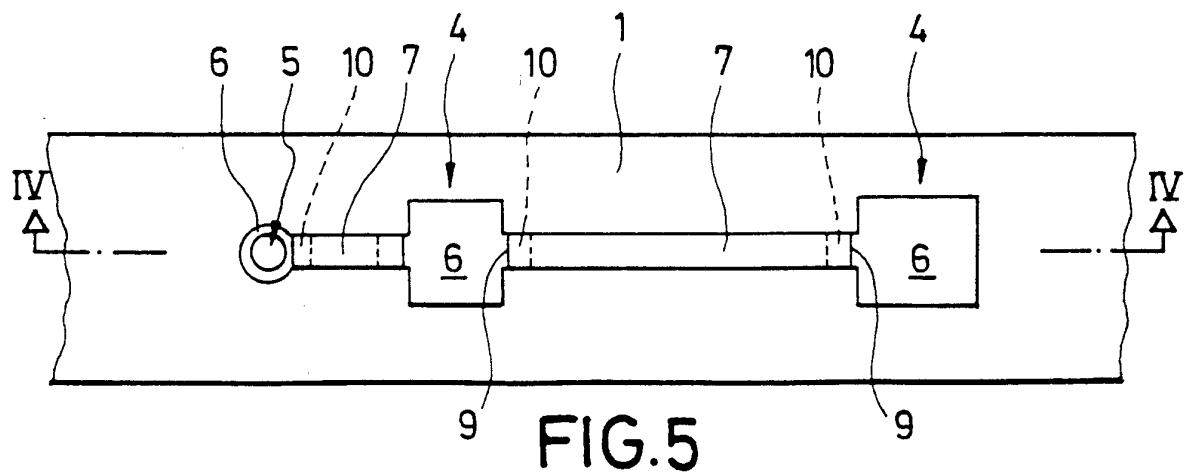

Fig.5 eine Draufsicht auf einen Ausschnitt einer Leiterplatte, wobei die Figur 4 einem Schnitt entlang der Linie IV-IV aus Figur 5 entspricht;

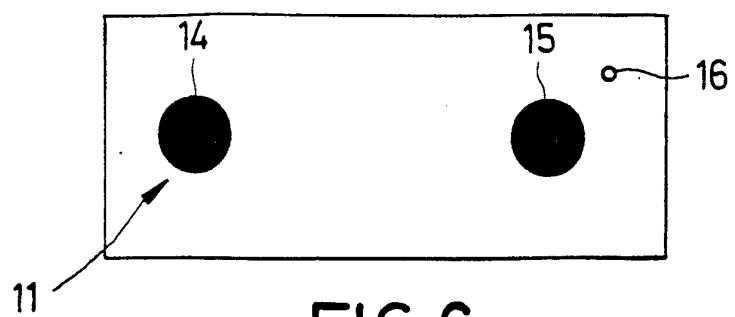

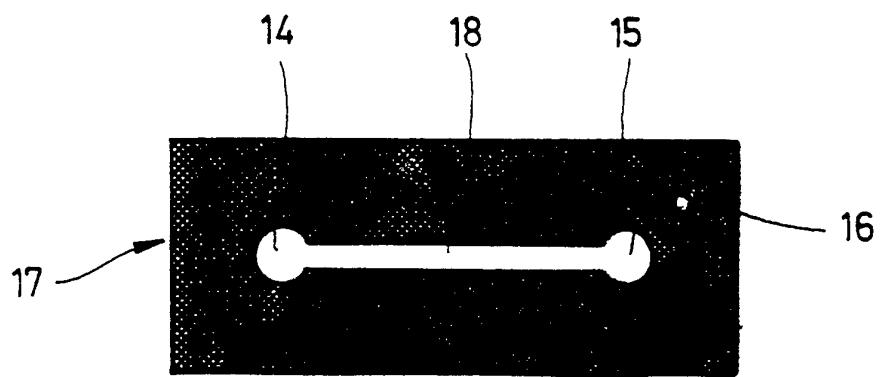

Fig.6 eine zweite Grundmaske;

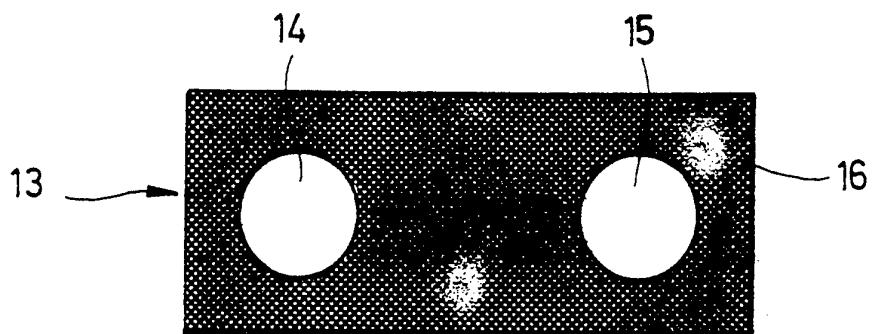

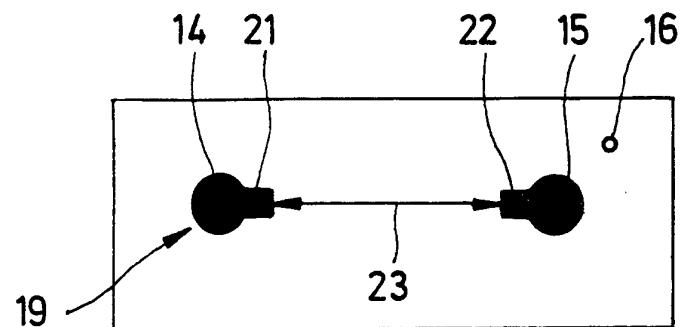

Fig.7 eine erste Hilfsmaske;

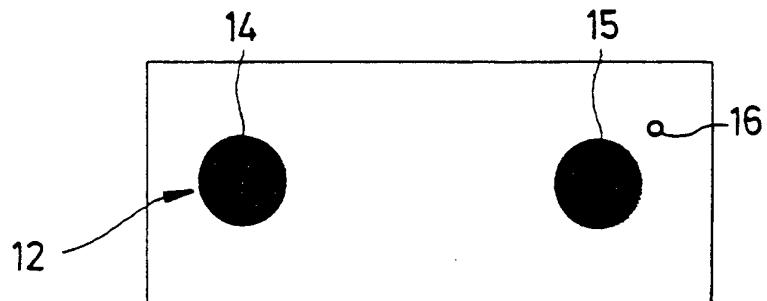

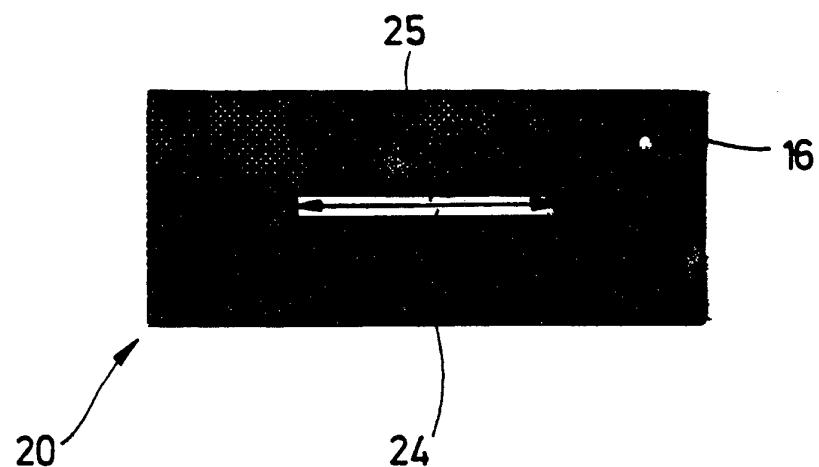

Fig.8 eine zweite Hilfsmaske;

Fig.9 eine erste Grundmaske;

Fig.10 eine erste Maske;

Fig.11 eine zweite Maske;

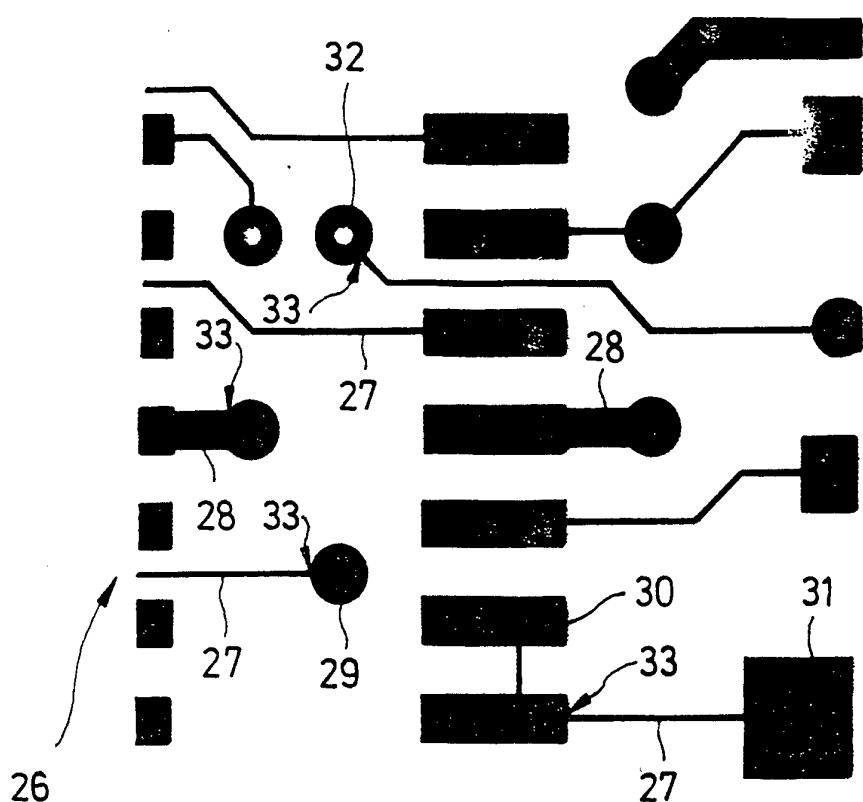

Fig.12 einen Ausschnitt einer auf einer Leiterplatte ausgebildeten Schaltung; und

Fig.13 einen weiteren Ausschnitt einer auf einer Leiterplatte ausgebildeten Schaltung mit "Teardrop".

In Figur 1 ist ein Längsschnitt durch eine Leiterplatte dargestellt. Von der Leiterplatte ist eine Seite zum Aufbringen von elektronischen Bauteilen sichtbar, wobei die dieser Seite gegenüberliegende Seite zur Vereinfachung nicht dargestellt ist. Das im folgenden geschilderte Verfahren ist in entsprechender Weise auf beiden Seiten der Leiterplatte durchführbar.

Die Leiterplatte ist im wesentlichen aus einem isolierenden Substrat 1 gebildet. Dieses Substrat kann ein gegebenenfalls Glasfaser enthaltendes Epoxidharz, Polyimid, PTFE, ein Metallkernträger mit elektrophoretisch aufgebrachter und eingearbeiteter keramische Isolierschicht oder dergleichen sein. Auf der Oberfläche des Substrats 1 ist eine Kupfermetallisierung 2 und eine erste Photoresistschicht 3 aufgetragen. Kupfermetallisierung 2 und erste Photoresistschicht 3 bedecken im wesentlichen die gesamte Oberfläche des Substrats 1.

Zur Bildung von Anschlußbereichen (Pads) 4 und Verbindungsbohrungen 5 wird die erste Photoresistschicht 3 durch eine entsprechende erste Maske belichtet und die belichteten Bereiche

dieser Schicht werden entfernt, wobei die Entfernung in üblicher Weise durch entsprechende chemische Lösungsmittel, Säuren, Plasmaätzen oder dergleichen erfolgt. In den Bereichen auf der Kupfermetallisierung 2, in denen die belichtete, erste Photoresistschicht 3 entfernt ist, wird später galvanisch eine Lötschicht aus PbSn aufgetragen. Zuerst wird die Verbindungsbohrung 5 eingestanzt oder gebohrt, siehe Figur 2.

Um mittels der Verbindungsbohrung 5 eine leitende Verbindung von auf beiden Seiten des Substrats 1 beziehungsweise der Leiterplatte angeordneten Schaltungen und Bauelementen herzustellen, wird innerhalb der Bohrung eine Kupfermetallisierung 2 aufgebracht, die mit den entsprechenden Kupfermetallisierungen auf den Oberflächen des Substrats 1 in Verbindung steht. Zusätzlich wird die Lötschicht 6 auf der Kupfermetallisierung 2 innerhalb der Verbindungsbohrung 3 aufgetragen, wobei sie zusätzlich die Bohrung auf der Oberfläche des Substrates 1 umrandet.

Nach dem galvanischen Auftragen der Lötschicht 6 im Bereich der Pads 4 und der Verbindungsbohrung 5 wird die restliche erste Photoresistschicht 3 entfernt und auf der gesamten Oberfläche der Leiterplatte eine zweite Photoresistschicht 7 aufgetragen, siehe Figur 3. Die zweite Photoresistschicht 7 kann auch innerhalb der Verbindungsbohrung 5 auf der Lötschicht 6 aufgetragen sein.

Mittels einer zweiten Maske wird die zweite Photoresistschicht 7 belichtet und insbesondere von den Lötschichten 6 von Pads 4 und Verbindungsbohrungen 5 entfernt. Die zweite Photoresistschicht 7 verbleibt zur Strukturierung von Leiterbahnen zwischen den Pads, zwischen zu verbindenden Verbindungsbohrungen 5 und zwischen zu verbindenden Pads 4 und Verbindungsbohrungen 5, siehe Figur 4. Darauffolgend wird die Kupfermetallisierung 2 in allen Bereichen auf der Oberfläche der Leiterplatte entfernt, in denen sie nicht von der zweiten Photoresistschicht 7 oder der Lötschicht 6 be-

deckt ist. Folglich verbleibt die Kupfermetallisierung unter den Pads, innerhalb der Verbindungsbohrung 5 und zur Bildung von Leiterbahnen unterhalb der verbliebenen zweiten Photoresistschicht 7. Schließlich wird auf der gesamten Oberfläche der Leiterplatte eine Schicht 8 aus Lötstopplack aufgetragen, wobei der Lötstopplack nicht die Lötschicht 6 im Bereich der Pads 4 und der Verbindungsbohrung 5 bedeckt, siehe Figur 4.

In Figur 5 ist eine Draufsicht auf einen Ausschnitt der nach den Figuren 1 bis 4 hergestellten Leiterplatte dargestellt. Figur 4 entspricht einem Schnitt entlang der Linie IV-IV, wobei in Figur 5 zur Vereinfachung die Schicht 8 aus Lötstopplack weggelassen wurde.

Die Pads 4 weisen eine im wesentlichen quadratische Form auf, wobei sie mit der Lötschicht 6 bedeckt sind. Zwischen den beiden dargestellten Pads verläuft auf dem Substrat 1 eine vom verbliebenen Rest der zweiten Photoresistschicht 7 überdeckte Kupfermetallisierung 2. Diese ist ebenfalls unterhalb der Lötschicht 6 zur Bildung der Pads und innerhalb der Verbindungsbohrung 5 angeordnet. Die zweite Photoresistschicht 7 ist mit ihren Enden 9 beabstandet von den Pads 4 ausgebildet. Unterhalb von Endstücken der zweiten Photoresistschicht 7 erstrecken sich in einem Überlappbereich 10 durch die Lötschicht 6 gebildete Anschlußstücke. Diese stehen von den im wesentlichen quadratischen Pads in Richtung der Leiterbahnen ab und decken zusammen mit der zweiten Photoresistschicht 7 die die Leiterbahnen bildende Kupfermetallisierung 2 ab, siehe Figur 4. Der Abstand der beiden aufeinanderzuweisenden Anschlußstücke der benachbarten Pads 4 ist geringer als der Abstand der Enden 9 der zweiten Photoresistschicht 7, so daß diese die Lötschicht 6 im Überlappbereich 10 überdeckt.

In analoger Weise ist zwischen der Verbindungsbohrung 5 und dem einen Pad 4 eine zweite Photoresistschicht 7 mit entsprechendem

Überlappbereich 10 zu durch die Lötschicht 6 gebildeten Anschlußstücken von Pad 4 und Verbindungsbohrung 5 aufgetragen.

Die Verbindungsbohrung 5 ist ringförmig auf dem Substrat 1 von einer Lötschicht 6 umgeben, wobei von dieser das Anschlußstück in Richtung Pad 4 absteht.

In den Figuren 6 bis 11 ist die Herstellung der ersten und zweiten Maske zur Verwendung bei dem erfindungsgemäßen Verfahren zur Herstellung einer Leiterplatte dargestellt. Zur Vereinfachung weist die auf den Masken dargestellte Schaltungsstruktur nur zwei voneinander beabstandete Pads 14 und 15 und eine zwischen diesen geradlinig verlaufende Leiterbahn 18 auf. Die Pads 14 und 15 sind im wesentlichen kreisförmig. Eine erste Grundmaske 17 mit der vereinfachten Schaltungsanordnung ist in Figur 9 dargestellt. Die erste Grundmaske 17 ist als Negativmaske ausgebildet. Zur genauen Ausrichtung relativ zu anderen Masken und zur Leiterplatte weist jede der in den Figuren 6 bis 11 dargestellten Maske ein Indexloch 16 an der gleichen Stelle auf.

In Figur 6 ist eine zweite Grundmaske 11 dargestellt, bei der nur die in der ersten Grundmaske 17 dargestellten Pads 14 und 15 vorhanden sind.

In Figur 7 ist eine erste Hilfsmaske 13 dargestellt, bei der die Pads 14 und 15 der zweiten Grundmaske 11 um einen ersten Vergrößerungsfaktor vergrößert dargestellt sind. Dabei ist zu beachten, daß Flächenschwerpunkte der Pads 14 und 15 bei beiden Masken 11 und 12 den gleichen Abstand aufweisen.

Die erste Hilfsmaske 13 ist eine Negativmaske, wobei durch diese Masken nur Bereiche außerhalb der Pads 14 und 15 belichtet werden.

In Figur 8 ist eine zweite Hilfsmaske 12 dargestellt, bei der die Pads 14 und 15 der zweiten Grundmaske 11 um einen zweiten Vergrößerungsfaktor vergrößert sind. Der zweite Vergrößerungsfaktor ist kleiner als der erste Vergrößerungsfaktor. Die zweite Hilfsmaske 12 ist als Positivmaske ausgebildet.

Werden die erste Hilfsmaske 13 und die erste Grundmaske 17 übereinander angeordnet und zur Herstellung einer weiteren Maske verwendet, so ergibt sich die in Figur 10 dargestellte erste Maske 19. Die erste Hilfsmaske 13 wird dabei so relativ zur ersten Grundmaske 17 angeordnet, daß die Flächenschwerpunkte der Pads 14 und 15, in diesem Fall die Mittelpunkte, übereinander angeordnet sind. Dadurch weist die erste Maske 19 in der Umgebung der Pads 14 und 15 Anschlußstücke 21 und 22 auf, die durch die Enden der Leiterbahn 18 aus Figur 9 gebildet werden, die innerhalb der Pads 14 und 15 der ersten Hilfsmaske 13 liegen.

Zur Herstellung der zweiten Maske 20 aus Figur 11 werden die zweite Hilfsmaske 12 und die erste Grundmaske 17 übereinander angeordnet. Wiederum sind die Flächenschwerpunkte der Pads 14 und 15 der zweiten Hilfsmaske 12 über beziehungsweise unterhalb der Flächenschwerpunkte der Pads 14 und 15 aus erster Grundmaske 17 angeordnet.

Da der erste Vergrößerungsfaktor zur Herstellung der zweiten Hilfsmaske 12 kleiner als der zweite Vergrößerungsfaktor zur Herstellung der ersten Hilfsmaske 13 ist, weisen die Pads 14 und 15 dieser beiden Masken unterschiedliche Radien auf. Entsprechend wird bei Überlagerung der zweiten Hilfsmaske mit der ersten Grundmaske 17 ein Leiterbahnverbindungsstück 24 erzeugt, dessen Länge 25 größer als ein Abstand 23, siehe Figur 10, der Anschlußstücke 21 und 22 ist. Folglich ergibt sich bei Überlagerung der ersten Maske 19 mit der zweiten Maske 20 ein Überlapp zwischen Leiterbahnverbindungsstück 24 und Anschlußstücken 21 und 22.

Die erste Maske 19 wird zum Belichten der ersten Photoresistschicht nach dem erfindungsgemäßen Verfahren verwendet. Da die erste Maske 19 eine Positivmaske ist, wird nach Belichtung der unbelichtete Teil der ersten Photoresistschicht entfernt, um auf den Pads 4, siehe Figur 2, die Lötschicht 6, siehe Figur 3, aufzutragen. Die zweite Maske 20 ist eine Negativmaske. Daher wird bei dem erfindungsgemäßen Verfahren zur Herstellung der Leiterplatte der unbelichtete Teil der zweiten Photoresistschicht entfernt, wodurch sich die Anordnung der zweiten Photoresistschicht 7 nach Figur 4 ergibt. Durch den Überlapp von Leiterbahnverbindungsstück 24 nach Figur 11 und der Anschlußstücke 21 und 22 nach Figur 10 ergeben sich die in Figur 4 mit "X" gekennzeichneten Überlappbereiche beziehungsweise die in Figur 5 durch "10" gekennzeichneten Überlappbereiche.

Die in den Figuren 10 und 11 dargestellten Masken 19 und 20 sind vereinfachte Prinzipdarstellungen der tatsächlich verwendeten Masken bei dem erfindungsgemäßen Verfahren.

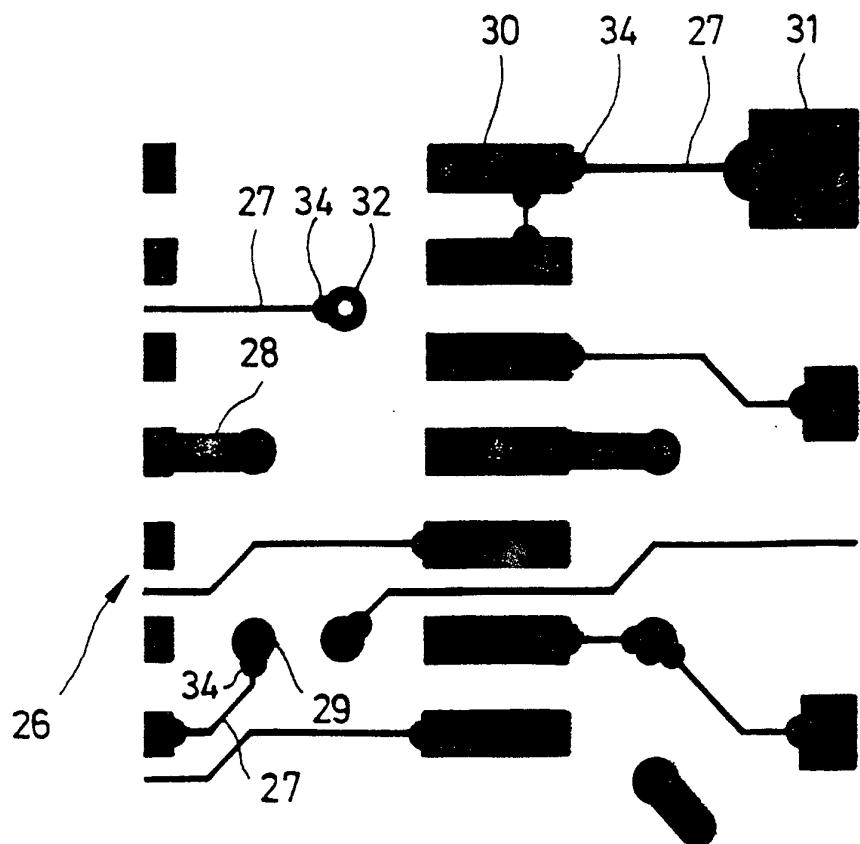

Ein komplexerer Schaltungsaufbau ist in den Figuren 12 und 13 dargestellt. Dieser wird in analoger Weise durch entsprechende erste und zweite Masken hergestellt.

In Figur 12 ist ein Ausschnitt 26 einer auf einer Leiterplatte angeordneten Schaltung dargestellt. Dieser umfaßt eine Vielzahl von Pads 29, 30 und 31. Die Pads 29 weisen einen kreisförmigen Querschnitt, die Pads 30 einen rechteckförmigen Querschnitt und die Pads 31 einen im wesentlichen quadratischen Querschnitt auf. Einige der kreisförmigen Pads 29 können beispielsweise mit einer Verbindungsbohrung ausgebildet sein, so daß sich eine Verbindungsbohrung 32 ergibt. Neben relativ feinen Leiterbahnen 27 sind grobere Leiterbahnen 28 ausgebildet. Jeweils im Kontaktbereich zwischen Leiterbahnen 27, 28 und Pads beziehungsweise Verbindungsbohrung 29, 30, 31 und 32 findet der in Figuren 4 und 5 dargestellte Überlapp von Lötschicht 6 und zweiter Photoresistschicht 7 statt.

In Figur 13 ist ein weiterer Ausschnitt 26 von einer auf der Leiterplatte dargestellten Schaltung dargestellt. Auch in diesem Fall sind entsprechende Leiterbahnen 27, 28 und Pads beziehungsweise Verbindungsbohrungen 29, 30, 31 und 32 ausgebildet. Zur Verbindung von den feinen Leiterbahnen 27 mit den Pads beziehungsweise Verbindungsbohrungen ist in deren Kontaktbereich, das heißt in dem Bereich, wo der Überlapp nach Figuren 4 und 5 stattfindet, ein sogenannter "Teardrop" angeordnet. Dieser weist eine im Vergleich zu den feinen Leiterbahnen größere Breite auf, wodurch ein entsprechender Überlapp von beispielsweise auf Pad 29 und "Teardrop" 34 aufgetragener Lötschicht mit einer auf der Leiterbahn 27 aufgetragenen zweiten Photoresistschicht erleichtert wird. Die Überlagerung von "Teardrop" und zweiter Photoresistschicht zur Strukturierung der Leiterbahnen zur korrekten Verbindung von Pads/Verbindungsbohrungen und Leiterbahnen ist in diesem Fall weniger kritisch als bei den in Figur 12 dargestellten feinen Leiterbahnen 27 und zugehörigen Pads ohne "Teardrop".

Gemäß der Erfindung ergibt sich zusammenfassend, daß durch die Überlagerung von Lötschicht und zweiter Photoresistschicht eine Unterbrechung zwischen Pads/Bohrungspunkten und Leiterbahnen beim Entfernen der nicht notwendigen Metallisierungsschicht von der Leiterplatte ausgeschlossen ist. Die Überlagerung wird durch Anordnung sogenannter "Teardrops" bei sehr dünnen Leiterbahnen erleichtert. Kleine Ungenauigkeiten beim Strukturieren der Leiterbahnen werden auf diese Weise toleriert.

Bei dem erfindungsgemäßen Verfahren sind mehrere aufwendige Verfahrensschritte der bekannte Herstellungsverfahren von Leiterplatten nicht mehr notwendig, wie Entfernen der Lötschicht von Leiterbahnen und Pads, das H.A.L.-Verfahren und alle damit verbundenen chemischen und mechanischen Behandlungen der Leiterplatte. Weiterhin ist die Lötschicht auf den Pad mit kontrollierter Schichtdicke und mit ebener Oberfläche auftragbar. Die bei dem H.A.L.-Verfahren zusätzlich verwendete flüssige Löt-

schicht zum Wiederauftragen der Lötschicht auf den Pads ist nicht mehr erforderlich, wodurch gleichzeitig die Umweltbelastungen durch Bleidämpfe, entsprechende Ätzelösungen und der gleichen wegfallen. Schließlich ist das erfindungsgemäße Verfahren im Vergleich zu dem mit dem H.A.L.-Verfahren arbeitenden Herstellungsverfahren erheblich kostengünstiger, da die teuren H.A.L.-Geräte nicht mehr notwendig sind.

## A N S P R Ü C H E

1. Verfahren zur Herstellung einer Leiterplatte mit einer ersten und eine zweiten Oberfläche, wobei wenigstens auf der ersten Oberfläche eine Vielzahl von Anschlußkontakten (Pads) (6; 29, 30, 31) zum Auflöten von elektronischen Bauelementen und eine Vielzahl von die Pads verbindenden Leiterbahnen (27, 28) aufgebracht wird,

**gekennzeichnet durch**

die folgenden Verfahrensschritte:

- i) Auftragen einer ersten Photoresistschicht (3) auf wenigstens einer ersten metallisierten Oberfläche (2) der Leiterplatte;

- ii) Belichten der ersten Photoresistschicht (3) mittels einer ersten Maske (19) und Entfernen von Bereichen der ersten Photoresistschicht (3) zum Strukturieren der Pads (4; 29, 30, 31);

- iii) Auftragen einer Lötschicht (6) auf die Pads und Entfernen der verbliebenen, ersten Photoresistschicht (3);

- iv) Auftragen einer zweiten Photoresistschicht (7) auf der ersten Oberfläche;

- v) Belichten der zweiten Photoresistschicht (7) mittels einer zweiten Maske (20) zum Strukturieren der Leiterbahnen, wobei auf den Leiterbahnen und zumindest teilweise auf den Pads die die Lötschicht (6) überlappende zweite Photoresistschicht (7) verbleibt;

- vi) Entfernen der freiliegenden Metallisierung (2) der Leiterplatte und Auftragen einer Lötstoppschicht

(8) auf der Leiterplatte außerhalb der Pads (4; 29, 30, 31).

2. Verfahren nach Anspruch 1,

**dadurch gekennzeichnet,**

daß die Pads (4; 29, 30, 31) im Schritt ii) mit im wesentlichen in Richtung der Leiterbahnen weisenden Anschlußstücken (10; 21, 22) strukturiert werden, wobei im Schritt v) die zweite Photoresistschicht (7) außer auf den Leiterbahnen wenigsteens teilweise auf den Anschlußstücken verbleibt.

3. Verfahren nach Anspruch 2,

**gekennzeichnet durch**

Strukturieren zusätzlicher Bohlungspunkte mit entsprechenden Anschlußstücken im Schritt ii), Bohren oder Stanzen von Verbindungsbohrungen (5, 32) zumindest in den Bohlungspunkten zur Verbindung beider Oberflächen der Leiterplatte und Auftragen von einer Metallisierung (2) zumindest innerhalb der Verbindungsbohrungen.

4. Verfahren nach einem der vorhergehenden Ansprüche,

**gekennzeichnet durch**

ein galvanisches Auftragen der Lötschicht (6) im Schritt iii).

5. Verfahren nach einem der vorangehenden Ansprüche,

**dadurch gekennzeichnet,**

daß in den Schritten ii) und v) als erste Maske (19) eine Positivmaske und als zweite Maske (20) eine Negativmaske verwendet wird, wobei die erste Photoresistschicht (3) außerhalb der Pads/Bohrungspunkte und zugehörigen Anschlußstücke und die zweite Photoresistschicht (7) auf den Leiterbahnen belichtet wird.

6. Verfahren nach wenigstens einem der vorangehenden Ansprüche,

**gekennzeichnet durch**

Aufschmelzen der Lötschicht (6) auf Pads mit Anschlußstücken und/oder Verbindungsbohrungen mit Anschlußstücken nach Schritt vi).

7. Verfahren nach Anspruch 6,

**dadurch gekennzeichnet,**

daß das Aufschmelzen durch Infrarotbestrahlung erfolgt.

8. Verfahren nach wenigstens einem der vorangehenden Ansprüche,

**dadurch gekennzeichnet,**

daß der Lötstopplack (8) fotografisch oder durch Siebdruck aufgetragen wird.

9. Verfahren nach wenigstens einem der vorangehenden Ansprüche,

**dadurch gekennzeichnet,**

daß die Strukturierung der Anschlußstücke (10, 21, 22) mit einer im Vergleich zu den Leiterbahnen größeren Breite im Schritt ii) erfolgt.

10. Verfahren nach wenigstens einem der vorangehenden Ansprüche,

**dadurch gekennzeichnet,**

daß die Metallisierung der Leiterplatte durch Auftragen einer Kupferschicht (2) erfolgt.

11. Verfahren nach wenigstens einem der vorangehenden Ansprüche,

**dadurch gekennzeichnet,**

daß eine PbSn-Schicht als Lötschicht (6) aufgetragen wird.

12. Verfahren zur Herstellung von Masken (19, 20) zur Belichtung von Photoresistschichten (3, 7) zur Verwendung bei dem Verfahren nach einem der vorangehenden Ansprüche,

**gekennzeichnet durch**

die folgenden Verfahrensschritte:

- a) Herstellen einer ersten Grundmaske (17) mit einem Gesamt-Lay-out aller auf einer Leiterplatte zu bildenden Pads (4; 14, 15, 29, 30, 31) und/oder Bohrungspunkte (5, 32) und/oder Leiterbahnen (18, 24, 27, 28);

- b) Herstellen einer zweiten Grundmaske (11) mit einem Lay-out zum Bilden von Pads und/oder Bohrungspunkten;

- c) Herstellen einer ersten Hilfsmaske (13) mit einer um einen ersten Vergrößerungsfaktor vergrößerten Darstellung von Pads und/oder Bohrungspunkten der ersten Hilfsmaske;

- d) Herstellen der ersten Maske (19) durch Überlagerung von erster Hilfsmaske (13) und erster Grundmaske (17);

- e) Herstellen einer zweiten Hilfsmaske (12) mit einer um einen im Vergleich zum ersten Vergrößerungsfaktor kleineren zweiten Vergrößerungsfaktor vergrößerten Darstellung von Pads und/oder Bohrungspunkten der zweiten Grundmaske (11);

- f) Herstellen der zweiten Maske (20) durch Überlagerung von zweiter Hilfsmaske (12) und erster Grundmaske (17).

13. Verfahren nach Anspruch 12,

**dadurch gekennzeichnet,**

daß bei Überlagerung von erster und zweiter Hilfsmaske (12,

13) mit der ersten Grundmaske (17) Flächenschwerpunkte von Pads und/oder Bohrungspunkten von Hilfsmasken (12, 13) und erster Grundmaske (17) übereinander liegen.

14. Verfahren nach Anspruch 12 oder 13,

**dadurch gekennzeichnet,**

daß der Entwurf von Grundmasken (11, 17) und Hilfsmasken (12, 13), Vergrößerung der Strukturen der ersten Grundmaske und die Überlagerung von erster und zweiter Hilfsmaske (12, 13) mit der ersten Grundmaske (17) durch ein CAD-Verfahren erfolgt.

15. Verfahren nach Anspruch 12 bis 14,

**dadurch gekennzeichnet,**

daß die erste Maske (19) an einer Verbindungsstelle von Leiterbahn und Pad und/oder Bohrungspunkt an diesen ein gegenüber der Leiterbahn verbreitertes Anschlußstück aufweist.

16. Leiterplatte mit auf wenigstens auf einer ersten Oberfläche angeordneten Pads (4, 29, 30, 31) und Leiterbahnen (27, 28) aus einem auf einem isolierenden Substrat (1) der Leiterplatte aufgetragenen Metall (2), mit zumindest auf den Pads aufgetragener Lötschicht (6) und mit einer auf der Leiterplatte außer den Pads aufgetragenen Lötstoppschicht (8)

**dadurch gekennzeichnet,**

daß in einem Kontaktbereich (10) von Pads (4, 29, 30, 31) und Leiterbahnen (27, 28) die Lötschicht (6) auf diesen aufgetragen ist.

17. Leiterplatte nach Anspruch 6,

**dadurch gekennzeichnet,**

daß der Kontaktbereich durch ein zur Verbindung von Pad und zu geordneter Leiterbahn ausgebildetes Anschlußstück (10, 21, 22, 34) gebildet ist, auf welchem die Lötschicht (6) und auf dieser zumindest teilweise die Photoresistschicht (7) aufgetragen ist.

18. Leiterplatte nach Anspruch 17,

**dadurch gekennzeichnet,**

daß das Anschlußstück (10, 21, 22, 34) von einem Endabschnitt der Leiterbahn (27, 28) gebildet ist.

19. Leiterplatte nach einem der Ansprüche 16 bis 18,

**dadurch gekennzeichnet,**

daß das Anschlußstück eine im Vergleich zur Leiterbahn größere Breite aufweist.

20. Leiterplatte nach einem der Ansprüche 16 bis 19,

**dadurch gekennzeichnet,**

daß die Photoresistschicht (7) im Vergleich zur Lötstoppschicht (8) in einem größeren Abstand vom Pad (4, 14, 15, 29, 30, 31) endet.

21. Leiterplatte mit wenigstens teilweise durch Leiterbahnen verbundenen Verbindungsbohrungen (5, 32) zur Verbindung von gegenüberliegenden Oberflächen der Leiterplatte nach einem der Ansprüche 16 bis 20,

**dadurch gekennzeichnet,**

daß wenigstens auf einer Innenfläche einer Verbindungsbohrung (5, 32) ein Metall (2) und die Lötschicht (6) aufgetragen sind und zumindest auf der ersten Oberfläche der Leiterplatte von der Verbindungsbohrung das Anschlußstück (10, 21, 22, 34) mit Lötschicht (6) und Photoresistschicht (7) absteht.

22. Leiterplatte nach einem der Ansprüche 15 bis 20,

**dadurch gekennzeichnet,**

daß die Lötschicht (6) aus PbSn und das Metall (2) Kupfer ist.

FIG.6

FIG.7

FIG.8

FIG.9

FIG.10

FIG.11

4 / 4

FIG.12

FIG.13

## INTERNATIONAL SEARCH REPORT

Int. Application No

PCT/EP 93/01004

| A. CLASSIFICATION OF SUBJECT MATTER |          |          |          |          |

|-------------------------------------|----------|----------|----------|----------|

| IPC 5                               | H05K3/24 | H05K3/06 | H05K3/34 | H05K3/40 |

|                                     | H05K3/00 |          |          | H05K3/42 |

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 5 H05K

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category | Citation of document, with indication, where appropriate, of the relevant passages                                                 | Relevant to claim No.             |

|----------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Y        | PATENT ABSTRACTS OF JAPAN<br>vol. 014, no. 320 (E-0950) 10 July 1990<br>& JP,A,02 105 597 (NEC CORP) 18 April 1990<br>see abstract | 1, 4, 10,<br>11                   |

| A        | ---                                                                                                                                | 3, 16, 20,<br>21                  |

| Y        | US,A,4 325 780 (SCHULZ, SR.) 20 April 1982<br>see column 4, line 22 - line 46; figures<br>11-13                                    | 1, 4, 10,<br>11                   |

| A        | ---                                                                                                                                | 3                                 |

| A        | GB,A,1 254 384 (STANDARD TELEPHONES AND<br>CABLES LTD) 24 November 1971<br>see the whole document                                  | 1, 3, 4,<br>10, 11,<br>16, 21, 22 |

|          | ---                                                                                                                                | -/-                               |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

## \* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*&\* document member of the same patent family

Date of the actual completion of the international search

10 December 1993

Date of mailing of the international search report

06.01.94

## Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentiaan 2

NL - 2280 HV Rijswijk

Tel. (+ 31-70) 340-2040, Tx. 31 651 epo nl,

Fax (+ 31-70) 340-3016

## Authorized officer

Mes, L

## INTERNATIONAL SEARCH REPORT

|                 |                    |

|-----------------|--------------------|

| Int.            | nal Application No |

| PCT/EP 93/01004 |                    |

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                      |                               |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Category                                             | Citation of document, with indication, where appropriate, of the relevant passages                                                                   | Relevant to claim No.         |

| A                                                    | PATENT ABSTRACTS OF JAPAN<br>vol. 015, no. 022 (E-1024) 18 January 1991<br>& JP,A,02 267 994 (HITACHI LTD) 1 November<br>1990<br>see abstract<br>--- | 1,3,4,<br>16,21               |

| A                                                    | EP,A,0 361 752 (AMERICAN TELEPHONE AND<br>TELEGRAPH COMPANY) 4 April 1990<br><br>see column 4, line 32 - line 47; figure 10<br>---                   | 1,2,4,<br>6-8,10,<br>11,17,22 |

| X                                                    |                                                                                                                                                      | 16                            |

| A                                                    | PATENT ABSTRACTS OF JAPAN<br>vol. 013, no. 416 (E-821) 14 September 1989<br>& JP,A,01 155 683 (IBIDEN CO LTD) 19 June<br>1989<br>see abstract<br>--- | 1,2,16,<br>17                 |

| A                                                    | DE,C,32 14 807 (TAMASIE) 6 October 1983<br><br>see the whole document<br>---                                                                         | 1,3,16,<br>21                 |

| A                                                    | US,A,4 571 072 (BOURBEAU, JR. ET AL.) 18<br>February 1986<br>see abstract; figures 1-3<br>-----                                                      | 12,14                         |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

Int. Application No

PCT/EP 93/01004

| Patent document cited in search report | Publication date | Patent family member(s) |                               |                                  | Publication date |

|----------------------------------------|------------------|-------------------------|-------------------------------|----------------------------------|------------------|

| US-A-4325780                           | 20-04-82         | NONE                    |                               |                                  |                  |

| GB-A-1254384                           | 24-11-71         | BE-A-<br>FR-A-          | 758490<br>2069036             | 05-05-71<br>03-09-71             |                  |

| EP-A-0361752                           | 04-04-90         | US-A-<br>CA-A-<br>JP-A- | 4978423<br>1301952<br>2122692 | 18-12-90<br>26-05-92<br>10-05-90 |                  |

| DE-C-3214807                           | 06-10-83         | NONE                    |                               |                                  |                  |

| US-A-4571072                           | 18-02-86         | NONE                    |                               |                                  |                  |

## INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/EP 93/01004

A. KLASIFIZIERUNG DES ANMELDUNGSGEGENSTANDES

IPK 5 H05K3/24 H05K3/06 H05K3/34 H05K3/40 H05K3/42

H05K3/00

Nach der Internationalen Patentklassifikation (IPK) oder nach der nationalen Klassifikation und der IPK

## B. RECHERCHIERTE GEBIETE

Recherchierte Mindestprüfstoff (Klassifikationsystem und Klassifikationssymbole)

IPK 5 H05K

Recherchierte aber nicht zum Mindestprüfstoff gehörende Veröffentlichungen, soweit diese unter die recherchierten Gebiete fallen

Während der internationalen Recherche konsultierte elektronische Datenbank (Name der Datenbank und evtl. verwendete Suchbegriffe)

## C. ALS WESENTLICH ANGESEHENE UNTERLAGEN

| Kategorie* | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile                                               | Betr. Anspruch Nr.                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Y          | PATENT ABSTRACTS OF JAPAN<br>vol. 014, no. 320 (E-0950) 10. Juli 1990<br>& JP,A,02 105 597 (NEC CORP) 18. April<br>1990<br>siehe Zusammenfassung | 1, 4, 10,<br>11                   |

| A          | ---                                                                                                                                              | 3, 16, 20,<br>21                  |

| Y          | US,A,4 325 780 (SCHULZ, SR.) 20. April<br>1982<br>siehe Spalte 4, Zeile 22 - Zeile 46;<br>Abbildungen 11-13                                      | 1, 4, 10,<br>11                   |

| A          | ---                                                                                                                                              | 3                                 |

| A          | GB,A,1 254 384 (STANDARD TELEPHONES AND<br>CABLES LTD) 24. November 1971<br><br>siehe das ganze Dokument<br>---                                  | 1, 3, 4,<br>10, 11,<br>16, 21, 22 |

|            | -/-                                                                                                                                              |                                   |

Weitere Veröffentlichungen sind der Fortsetzung von Feld C zu entnehmen

Siehe Anhang Patentfamilie