(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5266271号

(P5266271)

(45) 発行日 平成25年8月21日(2013.8.21)

(24) 登録日 平成25年5月10日(2013.5.10)

(51) Int.Cl.

G 11 C 11/407 (2006.01)

F 1

G 11 C 11/34 362 T

請求項の数 24 (全 20 頁)

(21) 出願番号 特願2010-76273 (P2010-76273)

(22) 出願日 平成22年3月29日 (2010.3.29)

(62) 分割の表示 特願2000-541688 (P2000-541688)

原出願日 平成11年4月1日 (1999.4.1)

(65) 公開番号 特開2010-176839 (P2010-176839A)

(43) 公開日 平成22年8月12日 (2010.8.12)

審査請求日 平成22年4月20日 (2010.4.20)

(31) 優先権主張番号 2,233,789

(32) 優先日 平成10年4月1日 (1998.4.1)

(33) 優先権主張国 カナダ(CA)

(31) 優先権主張番号 09/129,878

(32) 優先日 平成10年8月6日 (1998.8.6)

(33) 優先権主張国 米国(US)

(73) 特許権者 593138296

モーセッド・テクノロジーズ・インコーポ

レイテッド

M o s a i d T e c h n o l o g i e s

I n c o r p o r a t e d

カナダ国 ケイ2ケイ 2エックス1 オ

ンタリオ, オタワ, ハインズ・ロード 1

1, スイート 203

(74) 代理人 100107766

弁理士 伊東 忠重

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

最終頁に続く

(54) 【発明の名称】半導体メモリ非同期式パイプライン

## (57) 【特許請求の範囲】

## 【請求項 1】

アドレス可能なメモリ素子を有するメモリ、

該メモリから読み出したデータのうちのN個のビットを検知する複数の読み出し増幅器

該読み出し増幅器からのデータを受信し、それぞれN個のラッチを有するM個のラッチグループに構成され、同一のラッチグループに含まれる全てのラッチは該読み出し増幅器からの該データを同時にラッチする、複数のラッチ、

1つのラッチグループに含まれる全てのラッチを同時にイネーブルするカウンタ、

システム・クロック入力信号に同期した出力クロック信号を供給する遅延ロックループ及び

該出力クロック信号のエッジで前記複数のラッチの出力をラッチし、該システム・クロック入力信号のエッジに同期した出力データを供給する複数のデータ出力バッファ、

を有する同期式DRAM素子。

## 【請求項 2】

N = 32 である、

ことを特徴とする請求項1に記載の同期式DRAM素子。

## 【請求項 3】

M = 3 である、

ことを特徴とする請求項1に記載の同期式DRAM素子。

10

20

## 【請求項 4】

前記複数の出力バッファは、前記システム・クロック入力信号の立ち上がりエッジ及び立ち下がりエッジに同期した出力データを供給する、

ことを特徴とする請求項 1 に記載の同期式 D R A M 素子。

## 【請求項 5】

各前記ラッチグループは、前記システム・クロック入力信号の立ち上がりエッジに同期して出力されるべきデータを受信する  $N/2$  個のラッチを有するラッチグループと、前記システム・クロック入力信号の立ち下がりエッジに同期して出力されるべきデータを受信する  $N/2$  個のラッチを有するラッチグループと、を有する、

ことを特徴とする請求項 4 に記載の同期式 D R A M 素子。

10

## 【請求項 6】

$M = 6$  である、

ことを特徴とする請求項 5 に記載の同期式 D R A M 素子。

## 【請求項 7】

前記カウンタは 2 進カウンタである、

ことを特徴とする請求項 1 に記載の同期式 D R A M 素子。

## 【請求項 8】

前記 2 進カウンタは、前記複数のラッチにイネーブル信号を供給するためにデコードされる、

ことを特徴とする請求項 7 に記載の同期式 D R A M 素子。

20

## 【請求項 9】

前記出力クロック信号は、前記システム・クロック入力信号よりも位相が進んでいる、ことを特徴とする請求項 1 に記載の同期式 D R A M 素子。

## 【請求項 10】

各前記ラッチグループは、前記システム・クロック入力信号の複数のエッジに同期して前記出力バッファにより出力されるべきデータを受信する、

ことを特徴とする請求項 1 に記載の同期式 D R A M 素子。

## 【請求項 11】

各前記ラッチグループは、前記システム・クロック入力信号の 2 つのエッジに同期して前記出力バッファにより出力されるべきデータを受信する、

30

ことを特徴とする請求項 10 に記載の同期式 D R A M 素子。

## 【請求項 12】

各前記ラッチグループは、前記システム・クロック入力信号の立ち上がりエッジ及び立ち下がりエッジに同期して前記出力バッファにより出力されるべきデータを受信する、

ことを特徴とする請求項 11 に記載の同期式 D R A M 素子。

## 【請求項 13】

データ出力を供給する方法であって：

複数の読み出し増幅器を介して、アドレス可能なメモリ素子を有するメモリから読み出したデータのうちの  $N$  個のビットを検知する段階、

複数のラッチはそれぞれ  $N$  個のラッチを有する  $M$  個のラッチグループに構成され、同一のラッチグループに含まれる全てのラッチは該読み出し増幅器からの該データを同時にラッチし、該複数のラッチへのデータを受信する段階、

40

カウンタを介して、1 つのラッチグループに含まれる全てのラッチを同時にイネーブルする段階、

システム・クロック入力信号に同期した出力クロック信号を供給する段階、及び

該出力クロック信号のエッジで前記複数のラッチの出力をラッチする段階、及び

該システム・クロック入力信号のエッジに同期した出力データを供給する段階、

を有する方法。

## 【請求項 14】

$N = 32$  である、

50

ことを特徴とする請求項 1 3 に記載の方法。

【請求項 1 5】

$M = 3$  である、

ことを特徴とする請求項 1 3 に記載の方法。

【請求項 1 6】

前記出力データは、前記システム・クロック入力信号の立ち上がりエッジ及び立ち下がりエッジに同期する、

ことを特徴とする請求項 1 3 に記載の方法。

【請求項 1 7】

前記  $N$  個のラッチを有する  $M$  個のラッチグループのそれぞれは、前記システム・クロック入力信号の立ち上がりエッジに同期して出力されるべきデータを受信する  $N / 2$  個のラッチを有するラッチグループと、前記システム・クロック入力信号の立ち下がりエッジに同期して出力されるべきデータを受信する  $N / 2$  個のラッチを有するラッチグループと、を有する、

ことを特徴とする請求項 1 6 に記載の方法。

【請求項 1 8】

$M = 6$  である、

ことを特徴とする請求項 1 7 に記載の方法。

【請求項 1 9】

前記カウンタは 2 進カウンタである、

ことを特徴とする請求項 1 3 に記載の方法。

【請求項 2 0】

前記 2 進カウンタの出力をデコードして、前記複数のラッチにイネーブル信号を供給する段階、

を更に有する請求項 1 9 に記載の方法。

【請求項 2 1】

前記出力クロック信号は、前記システム・クロック入力信号よりも位相が進んでいる、

ことを特徴とする請求項 1 3 に記載の方法。

【請求項 2 2】

各前記ラッチグループで、前記システム・クロック入力信号の複数のエッジに同期して出力されるべきデータを受信する段階、

を更に有する請求項 1 3 に記載の方法。

【請求項 2 3】

各前記ラッチグループは、前記システム・クロック入力信号の 2 つのエッジに同期して出力されるべきデータを受信する、

ことを特徴とする請求項 2 2 に記載の方法。

【請求項 2 4】

各前記ラッチグループは、前記システム・クロック入力信号の立ち上がりエッジ及び立ち下がりエッジに同期して出力されるべきデータを受信する、

ことを特徴とする請求項 2 3 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体メモリ、より詳しくはダイナミックランダムアクセスメモリのパイプライン型データアクセスに関する。

【背景技術】

【0002】

従来の非パイプラインダイナミックランダムアクセスメモリ (DRAM) では、メモリへのあるいはメモリからのデータ転送は順次実行される。すなわち、読み取りまたは書き込み命令の一方が受信され、アドレスが利用可能になったとき、他の命令がメモリによっ

10

20

30

40

50

て受け入れられる前に、読み取りまたは書き込み命令によるデータ転送が全体として実行される。この結果、後続の命令は、現在のデータ転送が完了する時間だけ遅延される。

#### 【0003】

歴史的に、DRAMはプロセッサによって非同期に制御されてきた。これは、プロセッサがアドレスをDRAM入力に置き、ロードアドレス選択信号(/RAS)およびカラムアドレス選択信号(/CAS)ピンを用いてアドレスをストローブすることを意味する。アドレスは、必要な最小時間の長さの間保持される。この間、DRAMはメモリ内のアドレスされた位置にアクセスし、最大の遅延(アクセスタイム)後に、プロセッサからの新しいデータをメモリに書き込むか、あるいはプロセッサが読めるように出力にメモリからのデータを供給する。

10

#### 【0004】

この間、プロセッサは、DRAMがラインのプリチャージ、アドレスのデコードおよび同様の種々の内部機能を実行するのを待たなければならない。この結果「待ち状態」が生じ、この間、より高速のプロセッサはDRAMが応答するのを待たなければならず、これによってシステム全体の速度が遅くなる。

#### 【0005】

この問題に対する1つの解決方法はメモリ回路を同期化する、すなわちデータを保持できるDRAMに入出力ラッチを加えることである。入力ラッチは、アドレス、データおよび制御信号をDRAMの入力で記憶することができ、他のタスクのためにプロセッサを解放する。プリセットされた数のクロックサイクルの後に、読み取り用同期制御によってデータはDRAMの出力ラッチで利用可能になり、あるいは書き込み動作のためにメモリに書き込むことができる。

20

#### 【0006】

同期制御は、DRAMが、システムクロックの制御の下にプロセッサとDRAMそれ自身との間に転送された情報をラッチすることを意味する。このように、同期式DRAMの利点は、システムクロックが、メモリに設けなければならない唯一のタイミングエッジであることである。これによって、プリント回路基板周囲の多数のタイミングストロボの伝搬が低減あるいは除去される。

#### 【0007】

代わりに、DRAMは非同期にすることが可能である。例えば、ロードアドレスからデータアクセスまで60nsの遅延を有するDRAMが10nsクロックを有するシステムで使用されるとすれば、プロセッサはロードアドレスを加え、そして(/RAS)ピンでそれをストローブしている間、それを保持しなければならない。30ns後に、これにカラムアドレスが続き、このアドレスを有效地に保持し、そして(/CAS)ピンによってストロークしなければならない。次に、プロセッサは、30ns後にデータが出力に現われ、安定し、そして読み取られるのを待たなければならない。

30

#### 【0008】

他方、同期インターフェースによれば、プロセッサは、ローおよびカラムアドレス(および制御信号)を入力ラッチにロックし、そしてシステムクロックの制御の下でDRAMが読み取り動作を実行するのを待つ間に、他のタスクを実行することができる。DRAMの出力が6サイクル(60ns)後にクロックされる時、所望のデータは出力ラッチ内にある。

40

#### 【0009】

また同期式DRAMアーキテクチャは、アドレスをパイプライン化することによってDRAMの平均アクセスタイムを速めることも可能である。この場合、DRAMが以前のアドレスで操作している間に、プロセッサは次のアドレスを記憶するために入力ラッチを使用することができる。通常、アクセスすべきアドレスは、複数サイクル先行してプロセッサによって知られる。したがって、プロセッサはDRAMの入力アドレスラッチに第2のアドレスを送ることができ、このアドレスは、第1のアドレスがDRAMの次の処理段に移動するとすぐに利用可能である。これによって、DRAMへの次のアクセスを開始

50

する前にプロセッサが1完全アクセスサイクル待つ必要がなくなる。

【0010】

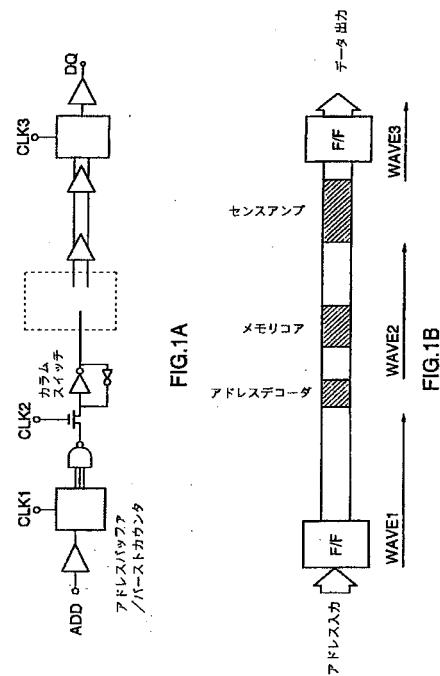

3段カラムアドレスパイプラインの例がFIG.1Aの概略図に示されている。カラムアドレスから出力への部分は3段パイプラインである。アドレスバッファは第1のラッチである。カラムスイッチは第2のラッチであり、そして出力バッファは第3のラッチである。したがって、カラムアクセスタイム固有の待ち時間はこれらの3つの段の間に分割される。

【0011】

パイプラインされる読み取りの動作は、次のように説明することが可能である。カラムアドレス(A1)は1つのクロックサイクルでアドレスバッファ内にクロックされ、そしてデコードされる。第2のクロックサイクルで、カラムスイッチは対応するデータ(D1)をセンス増幅器から読み取りバスに転送し、そしてカラムアドレス(A2)はアドレスバッファ内にクロックされる。第3のクロックでは、データ(D1)は出力バッファ内にクロックされ、(D2)は読み取りバスに転送され、そしてA3はカラムアドレスバッファ内にクロックされる。D1が出力に現われる時、D2とD3はD1の後のパイプラインにある。本発明の技術をより詳細に説明するために、Betty Princeによる「High Performance Memories」なる表題の本が参照される。

10

【0012】

SDRAM内のCASのラッチとデータバスのアベイラビリティとの間のクロックサイクルの数の遅延は、SDRAMの「CAS待ち時間」である。出力データが、カラムアドレスの到着に続くクロックの第2の前縁によって利用可能であるならば、装置は、2のCAS待ち時間を有すると説明される。同様に、データが第1の読み取り命令の到着に続くクロックの第3の前縁で利用可能であるならば、装置は、3の「CAS待ち時間」を有すると認識される。

20

【0013】

同期式DRAM(SDRAM)にはプログラム可能なCAS待ち時間がある。上述のように、クロックレート(CLK)に関係なく、CAS待ち時間は、読み取り命令が開始された後、どのクロックエッジでサイクルデータが利用可能であるかを決定する。プログラム可能なCAS待ち時間により、CAS待ち時間に影響を与えることなく、異なったシステムクロック周波数を有する異なったメモリシステムにおけるSDRAMの効率的な利用が可能になる。

30

【0014】

SDRAMデータバスを待ち時間段に分割する他の方法がある。ウェーブパイプラインがFIG.1Bに概略的に示されている。通常のクロック式パイプラインは、読み取り待ち時間が、パイプライン段の数を乗算した最も低速のパイプライン段の遅延(すなわち最長の遅延)に等しくなるという不都合を有する。読み取り待ち時間に影響を与えることなくより長いパイプライン段に適応可能であるように、調整されたクロックを有するクロック式パイプラインは、各パイプライン段に調整済みのクロック信号を使用する。より長いパイプライン段は、パイプライン段を開始するクロックよりも遅延されるクロックで終了される。より短いパイプライン段は、パイプライン段を終了するクロックよりも遅延されるクロックで開始される。この方法の不都合は、チップによってサポートされる各CAS待ち時間に対してクロックの異なった調整が必要とされることである。また、アーキテクチャの変更は待ち時間段の分割に大きな影響を及ぼす可能性があり、設計者は、待ち時間段の新しい分割を適応させるためにすべてのクロックの再調整を必要とする。

40

【0015】

さらに、余分の待ち時間またはチップ領域を加えることなく、待ち時間段を挿入することができる位置の数が制限される。多数の待ち時間段には、段を通して伝播する信号に必要とされる時間についてすべての待ち時間段が等しいわけではないという点で、不利益がある。他の厄介な問題は、チップが動作するようにプログラミングされるCAS待ち時間に応じて待ち時間段をイネーブルまたはディスエーブルする必要があるという点である。

50

## 【0016】

FIG. 1B のウェーブパイプラインでは、読み取りデータバス全体を通してデータのパルスが走る。ウェーブパイプラインは理想的なデータバスの長さに依存し、すなわち、すべてのデータバスが等しいと仮定する。しかし、メモリアレイのあるメモリセルから検索されたデータは、他のメモリセルから検索されたデータよりも本来的に速い。これは、主として、読み込みおよび読み出しデータバスの両方に関するメモリセルの物理的位置のためである。このように、チップから出力される前にデータを再同期しなければならない。このデータバススキュームは、ウェーブパイプライン装置で検索されたデータを確実に再同期することを難しくする。

## 【0017】

10

アドレス信号が、メモリアクセスタイムを超える 1 サイクルタイムを有するデータバスに加えられるならば、メモリから読み取られるデータはメモリコアの固有の遅延の間出力されない。換言すれば、ウェーブパイプライン技術では、メモリコア部分のクリティカルバスよりも短い期間がアドレス入力信号に加えられる。

## 【0018】

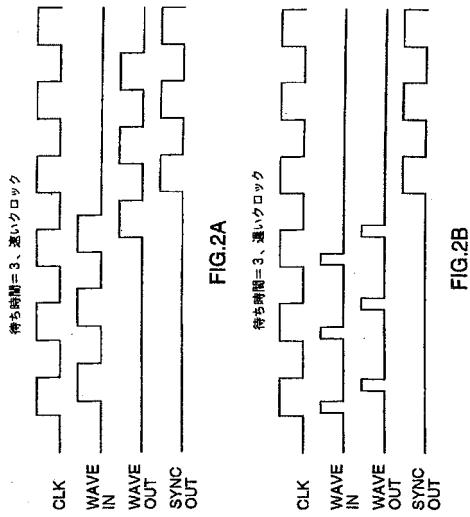

さらに、低速クロックを有する FIG. 2A と FIG. 2B に例示したように、データが必要になるまでウェーブパイプラインの出力データを記憶する必要がある。

【特許文献 1】米国特許第 5,655,105 号明細書

【特許文献 2】米国特許第 5,835,443 号明細書

20

【特許文献 3】米国特許第 6,014,339 号明細書

【特許文献 4】米国特許第 6,539,454 号明細書

【特許文献 5】米国特許第 5,294,842 号明細書

【特許文献 6】米国特許第 6,078,546 号明細書

【特許文献 7】米国特許第 4,658,354 号明細書

【特許文献 8】米国特許第 5,272,390 号明細書

【特許文献 9】米国特許第 5,402,388 号明細書

【特許文献 10】米国特許第 5,544,124 号明細書

【特許文献 11】米国特許第 5,550,784 号明細書

【特許文献 12】米国特許第 5,579,267 号明細書

【特許文献 13】米国特許第 5,703,815 号明細書

30

【特許文献 14】米国特許第 5,713,005 号明細書

【特許文献 15】米国特許第 5,784,705 号明細書

【特許文献 16】米国特許第 5,666,480 号明細書

【特許文献 17】米国特許第 RE35,934 号明細書

【特許文献 18】米国特許第 7,509,469B2 号明細書

【特許文献 19】米国特許第 5,781,499 号明細書

【特許文献 20】米国特許第 5,822,255 号明細書

【特許文献 21】米国特許第 5,978,884 号明細書

【特許文献 22】米国特許第 5,999,258 号明細書

【特許文献 23】米国特許第 5,796,673 号明細書

40

【特許文献 24】欧州特許第 0704848A2 号明細書

【特許文献 25】特開平 2-003177

【特許文献 26】特開平 8-096573

【特許文献 27】特開平 9-091955

【特許文献 28】特開平 9-139076

【特許文献 29】特開平 10-055668

【特許文献 30】特開平 10-188556

【特許文献 31】特開平 11-176158

【特許文献 32】米国特許第 5,812,489 号明細書

【特許文献 33】特開平 9-265777

50

- 【特許文献 34】米国特許第 5,631,871 号明細書

【特許文献 35】米国特許第 5,703,830 号明細書

【特許文献 36】米国特許第 5,412,615 号明細書

【特許文献 37】特開平 7-326190

【特許文献 38】米国特許出願第 2010-0232237 号明細書

【特許文献 39】米国特許第 6,483,770 号明細書

【特許文献 40】米国特許第 5,631,866 号明細書

【特許文献 41】特開平 6-203553

【特許文献 42】米国特許第 6,483,770 号明細書

【特許文献 43】米国特許第 5,844,858 号明細書

【特許文献 44】米国特許第 5,999,458 号明細書

【特許文献 45】米国特許第 6,209,071 号明細書

【特許文献 46】特開平 9-106671

【特許文献 47】米国特許第 6,178,492 号明細書

【特許文献 48】米国特許第 5,991,902 号明細書

【特許文献 49】米国特許第 5,954,435 号明細書

【特許文献 50】米国特許第 5,939,913 号明細書

- 【非特許文献 1】Mehrdad Heshami, et al., "A 250-MHz Skewed-Clock Pipelined Data Buffer," IEEE Journal of Solid-State Circuits, 31(3) : 376-383 (March 1998). 10

- 【非特許文献 2】Boemo, E. I., et al., "The Wave Pipeline Effect on LUT-Based FPGA Architectures," E.T.S.I. Telecommunication, 28740 Ciudad Universitaria, Madrid, Spain (date of publication not available) (6 pp). 20

- 【非特許文献 3】JDEC Solid State Technology Association, "JDEC Standard: DDR2 SDRAM Specification," JESD79-2E (Revision of JESD79-2D), April 2008. 30

- 【非特許文献 4】Takai, Y., et al., "250 Mbytes Synchronous DRAM Using a 3-Stage Pipeline Architecture," IEEE Journal of Solid-State Circuits, 29(4) : 426-431 (April 1994).

- 【発明の概要】

【発明が解決しようとする課題】

【0019】

このように、本発明は、現在の技術に関して説明した種々の不都合の少なくともあるものを緩和することを追求する。 40

- 【課題を解決するための手段】

【0020】

本発明によれば、(a)メモリコアと、(b)アドレス入力ポートと I/O データポートとの間に定められた読み取りバスと、

(c)各段が複数の非同期制御信号の対応する 1 つによって制御される、前記読み取りバスに配置された複数のパイプライン段と、

(d)前記非同期制御信号を発生するためのタイミング遅延素子と、(e)前記段の各々でデータをラッチするために、前記非同期制御信号に応答する前記複数のパイプライン段の各々に結合されるラッチであって、前記データが、前記システムクロックと無関係に各パイプライン段にラッチされる、ラッチと、を備えるパイプライン型 SDRAM が提供 50

される。

【0021】

本発明のさらなる面に従って、非同期制御信号はチップ内に生成され、そして異なった待ち時間段に最適化される。

【0022】

本発明のさらなる面は、システムクロックに無関係の段を提供し、これによって、適切な再同期出力によって支援することが可能な任意のCAS待ち時間において読み取りデータパスの実行が可能になる。

【0023】

本発明のさらなる面は、出力データをシステムクロックに同期させるための読み取りデータパスの端部に結合された同期回路を提供する。

【図面の簡単な説明】

【0024】

本発明のより良い理解が、次の図面と関連して以下の詳細な説明を参考にして得られるであろう。

【図1】FIG. 1Aは、従来のクロック式パイプライン型メモリ回路の概略図である。FIG. 1Bは、従来のウェーブパイプライン型メモリ回路の概略図である。

【図2】FIG. 2A及びFIG. 2Bは、それぞれ高速および低速クロック状態の下で走るCAS待ち時間 = 3のSDRAMのタイミング波形である。

【図3】FIG. 3は、本発明の一般化した実施形態の概略図である。

20

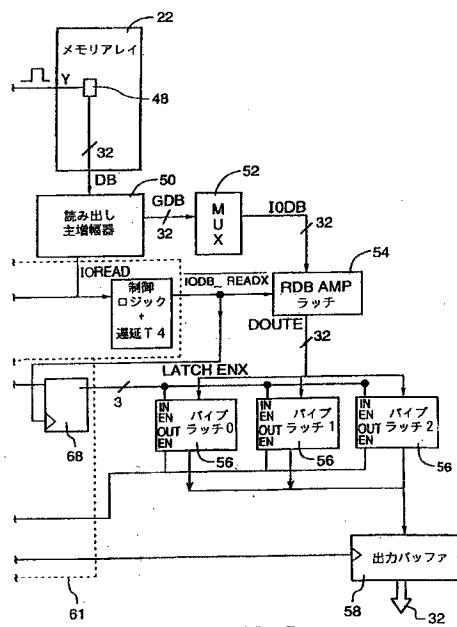

【図4】FIG. 4Aは、FIG. 3の一般化した実施形態のより詳細な概略図である。

【図5】FIG. 4Bは、FIG. 3の一般化した実施形態のより詳細な概略図である。

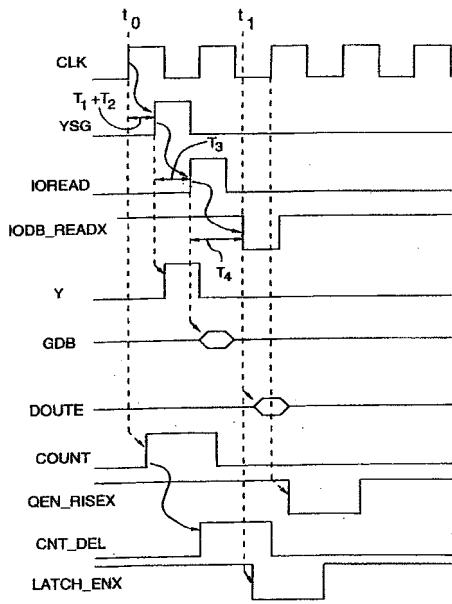

【図6】FIG. 5は、本発明の第1の実施形態によるタイミング波形図である。

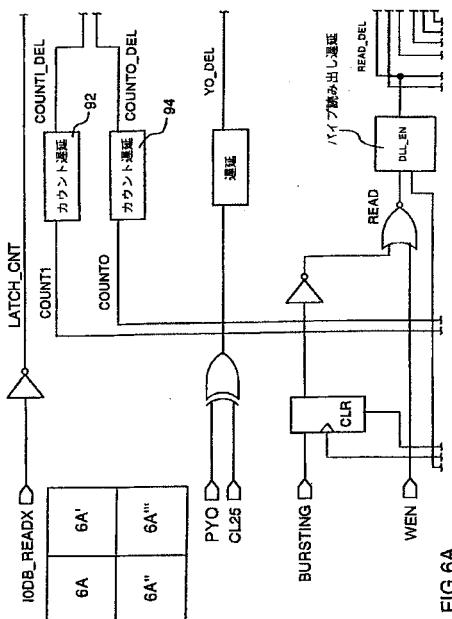

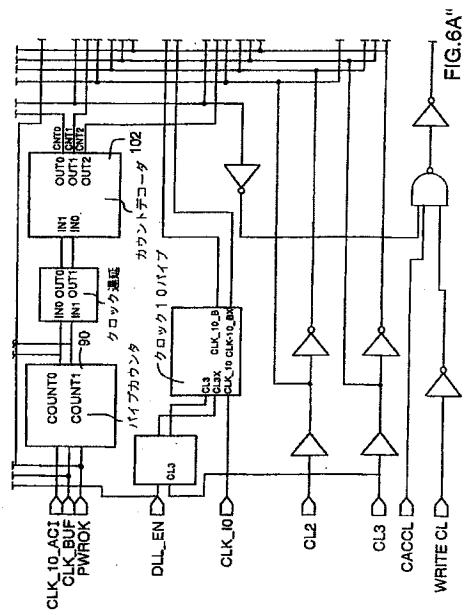

【図7】FIG. 6Aは、本発明の実施形態によるパイプ制御回路の詳細な回路図である。

。

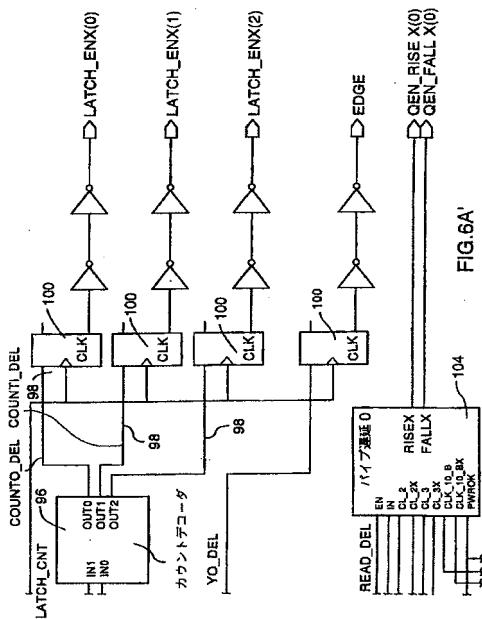

【図8】FIG. 6A'は、本発明の実施形態によるパイプ制御回路の詳細な回路図である。

【図9】FIG. 6A"は、本発明の実施形態によるパイプ制御回路の詳細な回路図である。

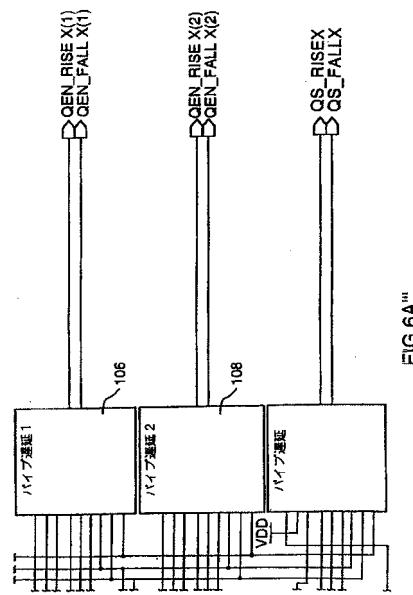

【図10】FIG. 6A'''は、本発明の実施形態によるパイプ制御回路の詳細な回路図である。

30

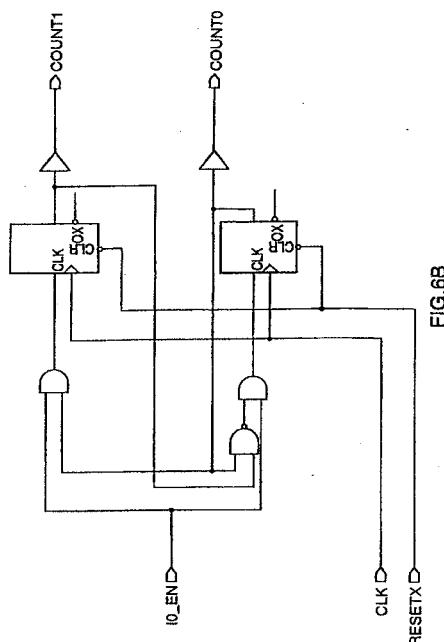

【図11】FIG. 6Bは、本発明の実施形態によるパイプ制御回路の詳細な回路図である。

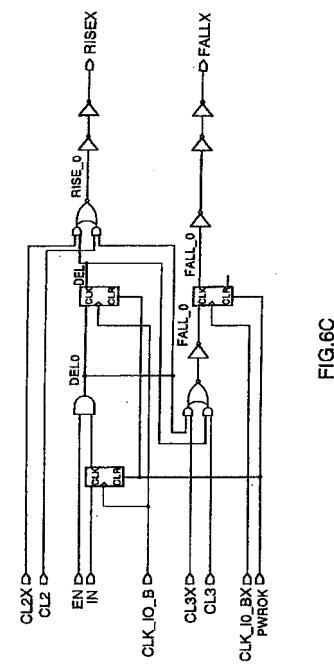

【図12】FIG. 6Cは、本発明の実施形態によるパイプ制御回路の詳細な回路図である。

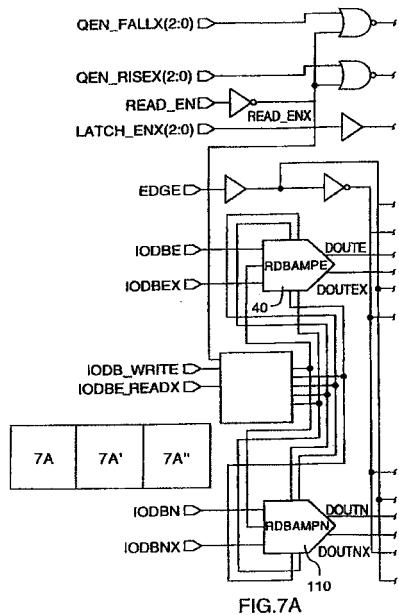

【図13】FIG. 7Aは、本発明の実施形態によるパイプラッヂとデータ出力ラッヂの詳細な回路図である。

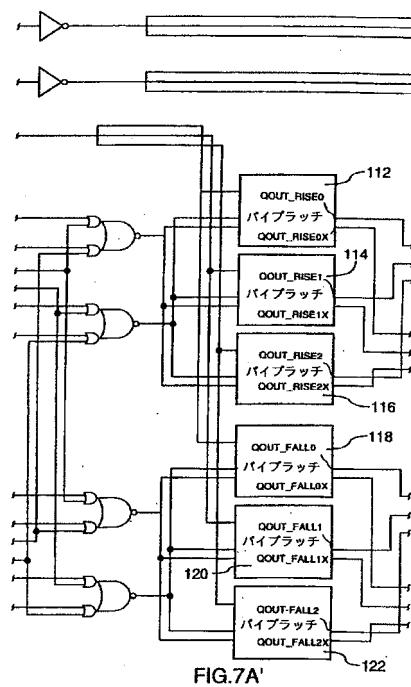

【図14】FIG. 7A'は、本発明の実施形態によるパイプラッヂとデータ出力ラッヂの詳細な回路図である。

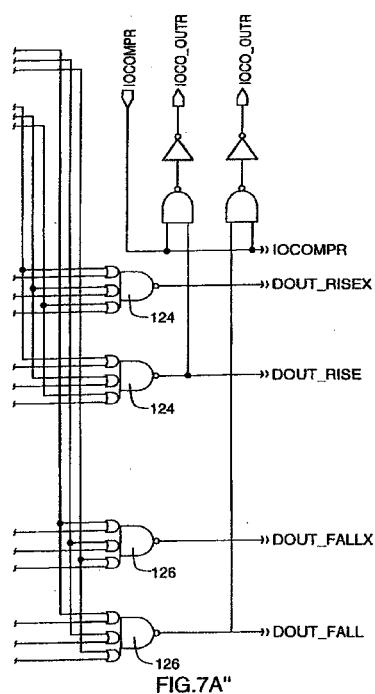

【図15】FIG. 7A"は、本発明の実施形態によるパイプラッヂとデータ出力ラッヂの詳細な回路図である。

40

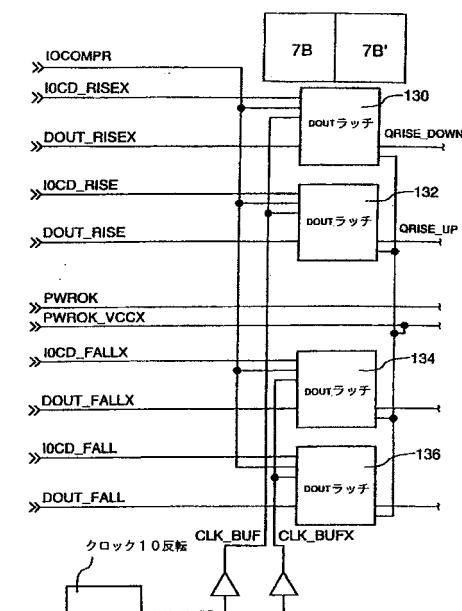

【図16】FIG. 7Bは、本発明の実施形態によるパイプラッヂとデータ出力ラッヂの詳細な回路図である。

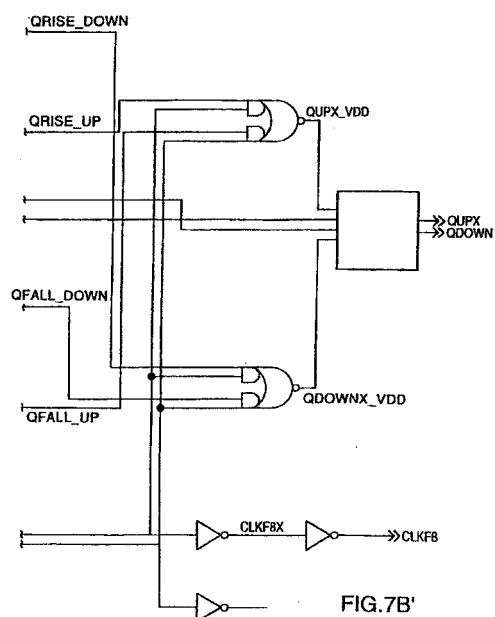

【図17】FIG. 7B'は、本発明の実施形態によるパイプラッヂとデータ出力ラッヂの詳細な回路図である。

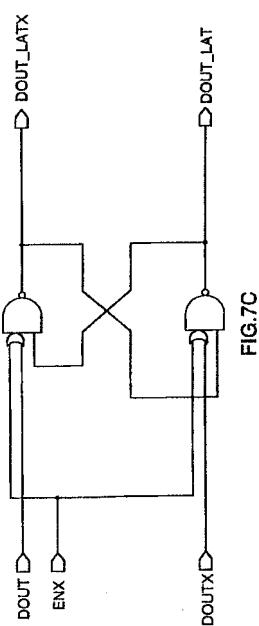

【図18】FIG. 7Cは、本発明の実施形態によるパイプラッヂとデータ出力ラッヂの詳細な回路図である。

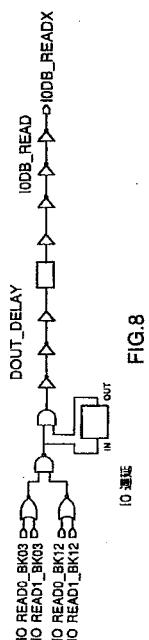

【図19】FIG. 8は、本発明の実施形態によるデータ出力制御回路の概略図である。

【発明を実施するための形態】

【0025】

50

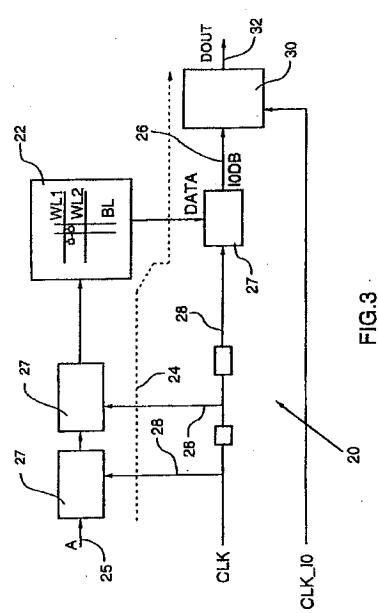

次の説明では、同様の数字は図の同様の要素を指し、そしてローにアサートした信号は対応する信号名に関連して、互いに置き換え可能な×または上線によって示される。次に FIG. 3 を参照すると、本発明の一般化した実施形態によるパイプライン型半導体メモリの概略図が概して数字 20 によって示されている。メモリは、アドレス入力ポート 25 とデータ出力 32 との間に画定された、読み取りバス 24 を有するコアメモリアレイ 22 を含む。読み取りバス 24 は複数の待ち時間段 27 に分解され、その各々はそれぞれの非同期制御信号 28 によってラッチされる。同期回路 30 は、読み取りバスの出力 32 のシステムクロック CLK にデータを再同期するために、読み取りバスの最後の待ち時間段に結合される。データは、アドレス入力 25 にアドレス信号 A を加えた後に、すなわちシステムの CAS 待ち時間に応じて、所定数のクロックサイクルだけシステムクロック CLK に同期される。各段がそれぞれの制御信号 28 によって制御される 3 つの主な待ち時間段への読み取りバス 24 の分割は、一般的に、本発明による非同期パイプライン装置を達成するためのクロック式およびウェーブパイプライン技術の組合せを例示し、前記装置は従来のウェーブパイプラインよりも小さなスキュームを示すが、クロック式パイプライン装置に必要とされるような各段の個々のクロックを調整する必要なしに、任意の CAS 待ち時間による動作を可能にする。FIG. 3 に関する説明は、以下に説明する詳細な回路の概略を示すために役立つ。

#### 【0026】

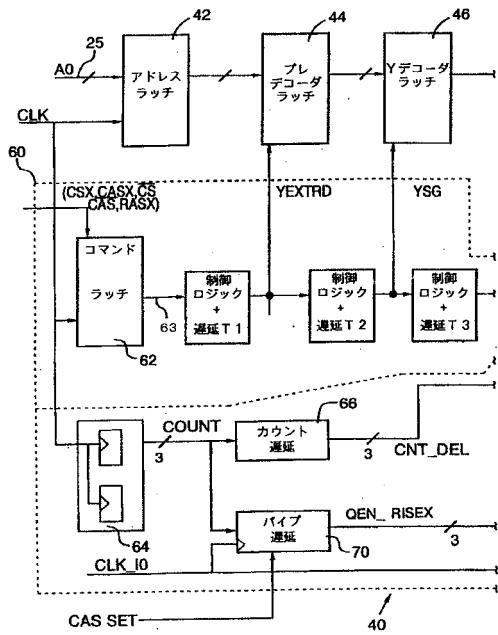

FIG. 4 A 及び 4 B を参照すると、FIG. 3 の一般化した実施形態の詳細な概略図が数字 40 によって示されている。FIG. 3 の待ち時間段 27 は、アドレス入力ポート 25 でアドレス信号 A<sub>i</sub> を受信するためのアドレス入力ラッチ 42 を含み、その出力はアドレスプリデコーダラッチ 44 に結合され、次にこのラッチはカラムアドレスデコーダラッチ 46 に接続される。カラムアドレスデコーダラッチ 46 はアドレス信号をデコードし、そしてメモリセルアレイ 22 の選択メモリセル 48 に結合される。カラムアドレスデコーダ 46 は、選択メモリセル 48 から読み出されたデータを検出するために関連のセンス增幅器（図示せず）を作動する。センス增幅器の出力はローカルデータバス DB を介して本実施形態では 32 ビット幅の読み取りメイン增幅器ブロック 50 に結合される。読み取りメイン增幅器 50 の出力はグローバルデータバス GDB に結合される。マルチプレクサ 52 は、GDB を I/O データバス IODB の上にマルチプレクスし、次に IODB は読み取りデータバス増幅器 RD BAMP ラッチブロック 54 に結合される。

#### 【0027】

FIG. 3 の同期回路 30 は、図 4 及び図 5 (FIG. 4 A 及び 4 B) に示すパイプラッヂ 56 と、出力バッファ 58 と、ブロック 61 によって示した制御回路とから構成される。より詳しくは、RD BAMP ラッチからの出力は、以下に説明するように、3 つのパイプ\_ラッヂ、パイプ\_ラッヂ 0、パイプ\_ラッヂ 1 およびパイプ\_ラッヂ 2 の入力に選択的に結合される。パイプラッヂからの出力は一緒に接続され、そして出力バッファ 58 の入力に結合される。

#### 【0028】

またメモリは、FIG. 4 A に示すようにシステムクロック CLK に結合されたクロック入力端子と、/RAS、/CAS、/CS のような命令信号を受信するための命令入力端子とを有する命令ラッヂ回路 62 を含む。命令ラッヂ 62 は第 1 の制御信号 63 を供給し、この信号は一連の制御ロジックと遅延素子 T1 から T4 とを通して実行される。遅延素子 T1、T2、T3、T4 の各々はそれぞれの遅延制御信号を生成し、これらの信号は、プリデコーダラッヂ 44、Y デコーダ 46、RMA50 および RD BAMP ラッヂ 54 の入力ラッヂ端子にそれぞれ送られる。これらの信号は、これらの回路用の個々の非同期制御信号として機能する。他方、アドレスラッヂ 42 のクロック入力はシステムクロック信号 CLK から直接導かれる。

#### 【0029】

FIG. 4 B に示す複数のパイプラッヂ、パイプ\_ラッヂ 0、パイプ\_ラッヂ 1 およびパイプ\_ラッヂ 2 の制御は、パイプラッヂ制御回路 61 によって行われる。各パイプラッヂ

10

20

30

40

50

チは、そのラッチ入力イネーブル端子に結合されたそれぞれのパイプラッティイネーブル信号、ラッチ<sub>enx(0)</sub>、ラッチ<sub>enx(1)</sub>およびラッチ<sub>enx(2)</sub>によって駆動される。パイプラッティイネーブル信号は、3つのカウント信号COUNTを生成するパイプカウンタ64(FIG.4A)から導かれる。パイプカウンタは、パイプラッチの総数に基づきそのカウントをリセットするフリーランニングカウンタである。システムクロックによって設定されたクロックカウントのプリセット数の後に、信号がパイプカウンタのクロック入力端子に結合される。パイプカウンタから出力されたCOUNT信号は、カウント遅延素子66を介してカウント同期ラッチ68(FIG.4B)に結合される。ラッチ68からの3つの出力は、適切なパイプラッチ56をクロックするためのパイプラッティイネーブル信号を供給する。ラッチ68のクロック入力イネーブル端子は、読み取りバスの待ち時間段の非同期制御信号に結合され、この場合、パイプラッチを確実に動作させるためのRDBAMP54の信号IODB\_READが適切な時間にラッチされる。

#### 【0030】

代わりに、データIODB\_READとラッチ68のCNT\_DEL信号とのより正確な同期を次のように達成することができる。

#### 【0031】

カウント遅延回路66はマルチ遅延段に分割することができ、前記各段はYSGまたはYEXTRDのような制御ロジックイネーブル信号を受信する。したがって、アドレス伝搬およびデータ検索とクロックカウント遅延との間のタイミング関係は、より密接に整合されるであろう。

#### 【0032】

さらに、FIG.4Aに示すようにパイプカウンタ64から出力されたCOUNTは、パイプラッチ出力イネーブル信号QEN\_RISEを生成するためのパイプ遅延素子70に接続され、この素子はパイプラッチ56のそれぞれの出力イネーブル端子に接続されている。DL\_Lにより生成され、そしてシステムクロックCLKをわずかにリードするCLK\_I\_O信号は、パイプ遅延と出力バッファ58の出力イネーブル端子に結合される。DL\_L(遅延ロックループ)は、CLK\_I\_Oが出力バッファをイネーブルし、データをシステムクロックエッジに適切に同期させるように保証する。

#### 【0033】

回路の動作は、FIG.5に示したタイミング図を参考にして次のように説明される。システムクロック信号CLKの時間t0で、アドレスラッチ42は外部アドレス信号Aiをラッチし、信号Aiは次にプリデコーダラッチ44に伝搬することができ、このラッチ44は、遅延素子T1によって設定された遅延T1の後にアドレスをラッチする。これらのアドレス信号は、T1とT2分CLKから遅れている信号YSGによってYデコーダ46でラッチされデコードされる。この時、適切なカラムが作動され、そしてデータがメモリセル48からカラムセンス増幅器に読み出され、次に、T1+T2+T3分CLKから遅延されるIORED信号によってRMA50にラッチされる。その後すぐに、データはグローバルデータバスGDBで利用可能である。RDBAMP54は、DOUTE信号を供給するために、時間t1で、T4分IOREDから遅れた信号IODB\_READによってラッチすることが可能である。

#### 【0034】

一般的に上述のように、これらの非同期制御信号はパイプライン段を制御するために使用される。これらの信号は、データがラッチ(通常ラッチ増幅器)に読み取られる時を制御する。ラッチに読み取られると、データは次の段に向かって伝搬することができる。各制御信号は、前の待ち時間段からの制御信号を遅延することによって生成される。第1段は外部クロックCLKによって開始される。次の段は、前の段からのデータを外部クロックから遅れた制御信号でラッチする。これらの遅延のうちのあるものは、読み取りが行われるべきかを制御するために使用される回路に固有のものであり、またあるものはタイミング遅延素子を使用して慎重に加えられるものであることが指摘できよう。これらの素子は、遅く動作するように設計され、そして追加の抵抗または容量素子を含むことが可能で

10

20

30

40

50

あるバッファから通常構成される。

【0035】

T1からT4の遅延は、外部クロックタイミングと無関係の特定のメモリに最適化することができる。これらのラッチの各々のための遅延は、これらのブロックの間の伝搬遅延に適応させるように選択される。このように、読み取りメイン増幅器ラッチに加えられるクロック信号は同期され、そしてメモリアレイ22の異なった領域から読み取りメイン増幅器50までのデータを検索する際の遅れに適応させるために、カラムデコーダラッチに加えられるクロック信号から遅延される。

【0036】

時間t1にRDBAMP54に一旦ラッチされたデータは、従来のウェーブパイプラインと同じように、メモリの出力32でシステムクロックCLKに再同期しなければならない。これは次のように達成される。パイプラッチ56は、高速データまたは低速クロックの場合にデータの記憶を可能にする。一般的に、必要とされるラッチの数は支援すべき待ち時間段の数と等しい。読み取りが実行される毎に、COUNT信号(1つがFIG.5に示されている)は、カウント遅延素子66によって非同期に遅延され、そして最後の段、この場合/IODB\_READ用の制御信号によってクロック同期ラッチ68にクロックされる。この時間遅延されたCOUNT信号は、RDBAMP54からのデータをラッチ56のどのラッチに記憶すべきかを決定する/LATCH\_ENXを生成する。さらに、COUNT信号もまた、チップがプログラミングされる現在のCAS待ち時間によって決定されるような適切な数のクロックサイクル分遅延される。FIG.5の/QEN\_RISEとして示したようなこのクロック遅延されたCOUNT信号は、ラッチ56のいずれが、データを出力バッファ58に出力するようにその出力をイネーブルしたかを制御する。COUNTが設定されると、カウント遅延回路66による遅延の後に、CNT\_DL信号が発生され、この信号はクロック同期ラッチ68内でIODB\_READ信号と結合されてLATCH\_ENX信号を生成する。QEN\_RISEに対するパイプ遅延回路の所定のクロック遅延がアサートされた後、ラッチからの出力が適切なクロックサイクルについてのデータを含むようになる。ラッチ56はFIG.0レジスタとして機能し、ラッチ56の組の1つへの第1のデータ入力は、ラッチの組から出力される第1のデータである。

【0037】

上記の説明から、読み取りバスのラッチがバスを非同期パイプラインの待ち時間段に分割することがわかる。チップアーキテクチャと最大動作周波数はこれらの段の数と配置とを決定する。一般的に、より高い動作周波数は多数のより短いパイプライン段を必要とする。段のデータバスの数を2倍にする、およびデータバスの間で交互に替えるなどの他の技術を使用することができる。例えば、センス増幅器からの読み取り出力は2つのデータバスの間で交互に替えられる。これはMossaidの特許第5,416,743号に開示されている。段の配置は、概して増幅器またはバッファの位置によって指定され、この位置は、広範囲領域の不利益を生じることなくラッチに転換することが可能である。分かりやすくするために、前および次の説明では、待ち時間段は、信号またはデータバスの遅延を導入する能力を有する任意の回路素子を指す。

【0038】

次にFIG.6からFIG.8を参照すると、FIG.4の一般化した実施例の詳細な形態が示されている。

【0039】

FIG.6A～6A'を参照する。FIG.6A～6A'はFIG.6Aの左上にある配置図に示すように配置されることにより1つの回路図を形成する。FIG.6Aのカウント遅延92、94はFIG.4Aのカウント遅延66に対応する。FIG.6A'及び6A'のパイプ遅延0～2は、FIG.4Aのパイプ遅延70に対応する。FIG.6A'のパイプカウンタ90、クロック遅延、カウントデコーダ102は、FIG.4Aのパイプカウンタ64に対応する。

10

20

20

30

40

50

## 【0040】

FIG. 4 A 及び 4 B のパイプ制御回路 6 1 は FIG. 6 A' のパイプカウンタ 9 0 (この詳細な概略図が FIG. 6 B に示されている) を含み、パイプカウンタ 9 0 はそのクロック入力端子 C L K の入力システムクロック周波数によって決定される 2 衍の 2 進カウント、COUNT 0 と COUNT 1 とを生成する。カウントラインの各々、COUNT 1 と COUNT 0 はそれぞれのカウント遅延素子 9 2 と 9 4 に接続している (FIG. 6 A)。遅延カウント信号は、FIG. 6 A' に示す 3 つのカウント遅延ライン 9 8、CNT 0\_DL、CNT 1\_DL、CNT 2\_DL の 1 つを作動するために入力 2 進カウントをデコードするカウントデコーダ 9 6 に接続している。これらの遅延カウントライン 9 8 の信号は FIG. 5 に示したように COUNT 信号に対応する。FIG. 5 では、すべての要素は、3 つのパイプラッチは例外として、単純化のために 3 つのコンポーネントの 1 つのみと共に示している。遅延 COUNT 信号 9 8 はそれぞれのクロックラッチ 1 0 0 の入力に結合され、その出力はバッファされ、そして FIG. 5 に参照されるそれぞれのラッチャイネーブル信号、LATCH\_ENX(0)、LATCH\_ENX(1)、LATCH\_EN(2) を供給する。これらのラッチ 1 0 0 のクロック入力端子は、インバータを介して最後の待ち時間段からの /I O D B \_ R E A D 非同期制御信号に結合される。

## 【0041】

FIG. 6 A' に示すように、パイプカウンタ 9 0 もまた、出力が第 2 のデコーダ 1 0 2 に接続され、同様にそれぞれのカウント信号 CNT 0、CNT 1、CNT 2 を供給する。これらはそれぞれの FIG. 6 A' に示すパイプ遅延要素 1 0 4、FIG. 6 A' に示すパイプ遅延要素 1 0 6、1 0 8 に結合される。パイプ遅延回路装置の詳細な回路図が FIG. 6 C に示されている。パイプ遅延の出力は C L K \_ I O 信号によって制御され、R I S E X 信号を生成する。FIG. 6 C の R I S E X 信号は FIG. 6 A' 及び 6 A' の Q E N \_ R I S E X (0) ~ (2) 信号、FIG. 5 の Q E N \_ R I S E X 信号、及び FIG. 4 A の Q E N \_ R I S E X 信号に対応する。FIG. 4 A 及び 4 B から分かるように、Q E N \_ R I S E X 信号はパイプラッチ 5 6 の出力ラッチャイネーブルに接続される。

## 【0042】

再び FIG. 6 C を参照すると、パイプ遅延回路装置は F A L L X 信号も生成する。F A L L X 信号は FIG. 6 A' 及び 6 A' の Q E N \_ F A L L X (0) ~ (2) 信号に対応する。対応する /Q E N \_ F A L L 信号はシステムクロックの立ち下がりエッジのために生成され、一方 /Q E N \_ R I S E はシステムクロックの立ち上がりエッジに対応する。

## 【0043】

FIG. 7 A ~ 7 A' と FIG. 7 B ~ B' を参照する。FIG. 7 A ~ 7 A' は FIG. 7 A の左下にある配置図に示すように配置されることにより 1 つの回路図を形成し、FIG. 4 B のパイプラッチ 5 6 の詳細な回路図を示す。FIG. 7 B ~ 7 B' は FIG. 7 B の右上にある配置図に示すように配置されることにより 1 つの回路図を形成し、FIG. 4 B の出力バッファ回路 5 8 の詳細な概略図を示す。また、FIG. 4 B に示されるようにパイプラッチ 5 6 は出力バッファ 5 8 に結合される。この結合は、FIG. 7 A' の各信号が FIG. 7 B の同様の名称を有する各信号に接続されることにより実現される。

## 【0044】

FIG. 7 A から理解できるように、I O D B データバスからのデータビット (I O D B N、I O D B N X) は R D B 増幅器 (R D B A M P N) 1 1 0 の入力で受信される。データがシステムクロックの立ち上がりと立ち下がりエッジの両方でクロックされるというダブルデータ速度 (D D R) のために、2 つの R D B A M P (4 0、1 1 0) がこの装置に示されている。

## 【0045】

10

20

30

40

50

FIG. 7A' に示されるように、FIG. 7A の各 RDBAMP (40, 110) に対応する 2 組のパイプラッチ 112, 114 及び 116 と 118, 120 及び 122 とが設けられる。図を簡略化するために FIG. 4B には、FIG. 4A のパイプ遅延 70 から QEN\_RISEX 信号を受けシステムクロックの立ち上がりエッジに応じて動作する 1 組のパイプラッチ、つまりパイプラッチ 0, 1 及び 2 (56) のみが示されている。

#### 【0046】

FIG. 7A の RDBAMP (40, 110) からの出力は、FIG. 7A' で OR 及び NOR ゲートを介して一連の 6 つのパイプラッチ 112 から 122 に接続される。DDR 装置のため、3 つの代わりに上述の 6 つのラッチ 112 ~ 122 が必要である。FIG. 7A' のパイプラッチ 112 から 122 は、FIG. 6A ~ 6A' の回路から導かれるそれぞれのラッティネーブル信号 LATC\_ENX (2) ~ (0) を入力として受信する (FIG. 7A)。これは、FIG. 4A 及び 4B のパイプカウンタ 64、カウント遅延 66 及びカウント同期ラッチ 68 により生成された LATC\_ENX 信号が FIG. 4B のパイプラッチ 56 へ入力されることに対応する。

10

#### 【0047】

FIG. 6A' 及び 6A' の各パイプ遅延 0 ~ 2 (104 ~ 108) が FIG. 6C に詳細に示されたようにシステムクロックの立ち上がりに対応する RISEX (FIG. 6A' 及び A' の QEN\_RISEX (0) ~ (2)) を生成し、FIG. 7A 及び 7A' に示すパイプラッチ 112 ~ 116 をシステムクロックの立ち上がりに応じて動作させる。また、各パイプ遅延 0 ~ 2 (104 ~ 108) はシステムクロックの立ち下がりに対応する FALLX (FIG. 6A' 及び A' の QEN\_FALLX (0) ~ (2)) も生成し、パイプラッチ 118 ~ 122 をシステムクロックの立ち下がりに応じて動作させる。

20

#### 【0048】

上部の 3 つのパイプラッチ 112 から 116 の出力は、FIG. 7A' で 3OR2NAND ゲート 124 の入力に接続される。同様に、下部の 3 つのラッチ 118 から 122 の出力は、3OR2NAND ゲート 126 に接続される。

#### 【0049】

/QEN\_RISE 信号 (FIG. 7A の QEN\_RISEX (2:0)) は、FIG. 7A' で 3OR2NAND ゲート 124 の入力に接続され、この出力は、イネーブルされた時、データを FIG. 7B に示した出力バッファの DOUT\_RISE、DOUT\_RISEX 入力に結合する。FIG. 7A からも理解できるように、システムクロック制御信号 E\_DGE は、データを上部の 3 つまたは下部の 3 つのラッチに導くために設けられ、これもまた DDR の特徴である。また、データバスの速度に対して速いシステムクロックのために、3OR2NAND ゲート 124 または 126 はすでにオンになり、よってパイプラッチから出力バッファまでのデータの通過を可能にする。代わりに低速クロックの場合、システムはデータを受信し、そしてクロックを待ち、よって 3OR2NAND ゲート 124 または 126 を利用する。

30

#### 【0050】

FIG. 7B に戻ると、FIG. 4B に示したようなデータ出力バッファ 58 はデータ出力ラッチ 130 から 136 を備える。データ出力ラッチ 130 から 136 の入力イネーブル端子は、正しいシステムクロックエッジに同期するための CLK\_I0 信号に結合される。システムクロックの立ち上がりに応じてパイプラッチ 112 ~ 116 から出力されたデータ DOUT\_RISEX、DOUT\_RISE (FIG. 7A') は、FIG. 7B でそれぞれデータ出力ラッチ 130、132 に入力され、CLK\_I0 信号から得られた CLK\_BUF に応じてデータ出力ラッチ 130、132 によりラッチされる。また、システムクロックの立ち下がりに応じてパイプラッチ 118 ~ 122 から出力されたデータ DOUT\_FALLX、DOUT\_FALL (FIG. 7A') は、FIG. 7B でそれぞれデータ出力ラッチ 134、136 に入力され、CLK\_I0 信号から得られた CLK\_BUF に応じてデータ出力ラッチ 134、136 によりラッチされる。パイプ

40

50

ラッチ 112 から 122 の詳細な回路装置が FIG. 7C に示されている。

【0051】

このように、本発明の実施形態はダブルデータ速度 (DDR) システムにも適用することができる。

【産業上の利用可能性】

【0052】

本発明は、高速および低速システムクロックの両方を容易に適応させることができるパイプライン型半導体メモリを実現するための柔軟な方法を提供することがわかる。さらに、柔軟な設計により、内部信号のより精密な整合のために読み取りバスのさらなる分割が可能になる。さらに、種々の CAS 待ち時間は、パイプ遅延素子 70 からの出力を単純に遅延して、データをクロックアウトする前に特定数のクロックサイクルを待つことによって適応可能である。

【0053】

特定の実施形態を参考にして本発明について説明してきたが、ここに添付した請求項で記述したように、本発明の精神と範囲から逸脱することなしにその種々の修正が当業者には明白であろう。

【符号の説明】

【0054】

|                         |                              |    |

|-------------------------|------------------------------|----|

| 20                      | メモリ                          | 20 |

| 22                      | コアメモリアレイ                     |    |

| 24                      | 読み取りバス                       |    |

| 27                      | 待ち時間段                        |    |

| 28                      | 非同期制御信号                      |    |

| 30                      | 同期回路                         |    |

| 32                      | 出力                           |    |

| 42                      | アドレス入力ラッチ                    |    |

| 44                      | アドレスプリデコーダラッチ                |    |

| 46                      | カラムアドレスデコーダ                  |    |

| 48                      | 選択メモリセル                      |    |

| 50                      | 読み取りメイン増幅器ブロック               | 30 |

| 52                      | マルチプレクサ                      |    |

| 54                      | 読み取りデータバス増幅器 (RDAMP) ラッチブロック |    |

| 56                      | パイプラッヂ                       |    |

| 58                      | 出力バッファ                       |    |

| 61                      | パイプ制御回路                      |    |

| 62                      | 命令ラッチ回路                      |    |

| 66                      | カウント遅延素子                     |    |

| 64                      | パイプカウンタ                      |    |

| 70                      | パイプ遅延素子                      |    |

| 90                      | パイプカウンタ                      | 40 |

| 92、94                   | カウント遅延素子                     |    |

| 96                      | カウントデコーダ                     |    |

| 98                      | カウント遅延ライン                    |    |

| 100                     | クロックラッチ                      |    |

| 102                     | デコーダ                         |    |

| 104、106、108             | パイプ遅延要素                      |    |

| 40、110                  | RDAMP                        |    |

| 112、114、116、118、120、122 | パイプラッヂ                       |    |

| 130、132、134、136         | データ出力ラッチ                     |    |

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【図5】

FIG.4B

【図6】

FIG.5

【図7】

FIG.6A

【図8】

FIG.6A'

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(72)発明者 メス、イアン

カナダ国 ケイ2ジー 6エス7、オンタリオ、ネピアン、エイボンモアクレセント24

審査官 堀田 和義

(56)参考文献 特開平9-106671(JP,A)

特開平9-91955(JP,A)

特開平11-176158(JP,A)

佐伯他, 2.5ns Clock Access 250MHz 256MSDRAM, 信学技報, Vol.96/No.225(SDM96 67-76), 21-

28

(58)調査した分野(Int.Cl., DB名)

G 11 C 11 / 407