## 특허청구의 범위

### 청구항 1

실리콘 산질화물 게이트 유전체 형성 방법으로서,

실리콘 산질화물 필름을 형성하기 위해서 플라즈마 질화 프로세스를 이용하여 유전체 필름 내측으로 질소를 도입시키는 단계;

700°C 내지 1100°C의 제 1 온도에서 1 mTorr 내지 100 mTorr의 제 1 부분압의 산소를 포함하는 불활성 대기를 포함하는 제 1 대기에서 상기 실리콘 산질화물 필름을 어닐링하는 단계;

900°C 내지 1100°C의 제 2 온도에서 0.1 Torr 내지 100 Torr의 제 2 부분압의 산소를 포함하는 제 2 대기에서 상기 실리콘 산질화물 필름을 어닐링하는 단계를 포함하며,

산소의 상기 제 2 부분압이 산소의 상기 제 1 부분압보다 큰

실리콘 산질화물 게이트 유전체 형성 방법.

### 청구항 2

삭제

### 청구항 3

삭제

### 청구항 4

제 1 항에 있어서,

상기 제 1 대기에서 상기 실리콘 산질화물 필름을 어닐링하는 단계는 30 초의 제 1 주기 동안 1050°C의 제 1 온도에서 15 mTorr의 제 1 부분압의 산소에서 이루어지며, 그리고

상기 제 2 대기에서 상기 실리콘 산질화물 필름을 어닐링하는 단계는 15초의 제 2 시간 주기 동안 1050°C의 제 2 온도에서 0.5 Torr의 제 2 부분압의 산소에서 이루어지는

실리콘 산질화물 게이트 유전체 형성 방법.

### 청구항 5

제 1 항에 있어서,

상기 제 2 대기에서 상기 실리콘 산질화물 필름을 어닐링하는 단계는, 산소 또는 산소 함유 가스로 상기 실리콘 산질화물 필름을 어닐링하는 단계를 포함하는

실리콘 산질화물 게이트 유전체 형성 방법.

### 청구항 6

제 1 항에 있어서,

상기 유전체 필름이 실리콘 이산화물인

실리콘 산질화물 게이트 유전체 형성 방법.

### 청구항 7

제 1 항에 있어서,

상기 유전체 필름 내측으로 도입되는 질소는 상기 실리콘 산질화물 게이트 유전체의 최상부 표면에서 발생하는 질소 농도 피크를 형성하는

실리콘 산질화물 게이트 유전체 형성 방법.

### 청구항 8

제 1 항에 있어서,

상기 유전체 필름 내측으로 도입되는 질소는 5%와 동일하거나 그보다 높은 질소 농도를 가지는 실리콘 산질화물 게이트 유전체 형성 방법.

### 청구항 9

실리콘 산질화물 게이트 유전체 형성 방법으로서,

실리콘 기판 상에 형성되는 실리콘 이산화물 필름을 포함하는 구조물을 제공하는 단계;

상기 실리콘 기판 상에 실리콘 산질화물 필름을 형성하기 위해서 질소 소오스를 포함하는 플라즈마에 상기 실리콘 기판 상에 형성되는 실리콘 이산화물 필름을 포함하는 구조물을 노출시키는 단계;

700°C 내지 1100°C의 온도에서 1 mTorr 내지 100 mTorr의 제 1 부분압의 산소를 포함하는 불활성 대기를 포함하는 제 1 대기에서 상기 실리콘 산질화물 필름을 어닐링하는 단계;

900°C 내지 1100°C의 온도에서 0.1 Torr 내지 100 Torr의 제 2 부분압의 산소를 포함하는 제 2 대기에서 상기 실리콘 산질화물 필름을 어닐링하는 단계; 및

상기 실리콘 산질화물 필름 상에 게이트 전극을 증착시키는 단계를 포함하며,

상기 제 2 부분압이 상기 제 1 부분압보다 큰

실리콘 산질화물 게이트 유전체 형성 방법.

### 청구항 10

삭제

### 청구항 11

제 9 항에 있어서,

상기 제 1 대기에서 상기 실리콘 산질화물 필름을 어닐링하는 단계는 30 초의 제 1 주기 동안 1050°C의 상기 제 1 온도에서 15 mTorr의 제 1 부분압의 산소에서 이루어지며, 그리고

상기 제 2 대기에서 상기 실리콘 산질화물 필름을 어닐링하는 단계는 15초의 제 2 시간 주기 동안 1050°C의 제 2 온도에서 0.5 Torr의 제 2 부분압의 산소에서 이루어지는

실리콘 산질화물 게이트 유전체 형성 방법.

### 청구항 12

제 9 항에 있어서,

상기 플라즈마에 상기 실리콘 기판 상에 형성되는 실리콘 이산화물 필름을 포함하는 구조물을 노출시키는 단계에서 도입되는 상기 질소는 5%와 동일하거나 그보다 높은 질소 농도를 가지는

실리콘 산질화물 게이트 유전체 형성 방법.

### 청구항 13

제 9 항에 있어서,

상기 제 1 대기에서 상기 실리콘 산질화물 필름을 어닐링하는 단계는 불활성 가스 또는 불활성 가스의 혼합물에서 상기 실리콘 산질화물 필름을 어닐링하는 단계를 포함하는

실리콘 산질화물 게이트 유전체 형성 방법.

#### 청구항 14

제 9 항에 있어서,

상기 제 2 부분압의 산소를 포함하는 제 2 대기에서 상기 실리콘 산질화물 필름을 어닐링하는 단계는 산소 또는 산소 함유 가스를 이용하여 상기 실리콘 산질화물 필름을 어닐링하는 단계를 포함하는

실리콘 산질화물 게이트 유전체 형성 방법.

#### 청구항 15

제 9 항에 있어서,

상기 실리콘 산질화물 게이트 유전체의 두께는 9Å과 동일하거나 그보다 작은

실리콘 산질화물 게이트 유전체 형성 방법.

#### 청구항 16

제 9 항에 있어서,

상기 게이트 전극은 폴리실리콘 필름, 비정질 실리콘 필름, 또는 금속 전극 중 어느 하나인

실리콘 산질화물 게이트 유전체 형성 방법.

#### 청구항 17

집적 프로세싱 시스템에서 실리콘 산질화물 게이트 유전체를 형성하는 방법으로서,

집적 프로세싱 시스템의 제 1 프로세싱 챔버 내측으로 실리콘을 포함하는 기판을 도입시키는 단계;

상기 실리콘 기판 상에 실리콘 이산화물 필름을 형성하는 단계;

상기 집적 프로세싱 시스템의 제 2 프로세싱 챔버에 상기 기판을 전달하는 단계;

질소 소오스를 포함하는 플라즈마에 상기 기판을 노출시키는 단계;

상기 집적 프로세싱 시스템의 제 3 프로세싱 챔버에 상기 기판을 전달하는 단계;

700°C 내지 1100°C의 온도에서 1 mTorr 내지 100 mTorr의 제 1 부분압의 산소를 포함하는 불활성 대기를 포함하는 제 1 대기에서 상기 기판을 어닐링하는 단계;

900°C 내지 1100°C의 온도에서 0.1 Torr 내지 100 Torr의 제 2 부분압의 산소를 포함하는 제 2 대기에서 상기 기판을 어닐링하는 단계를 포함하며,

상기 산소의 제 2 부분압이 상기 산소의 제 1 부분압보다 큰

집적 프로세싱 시스템에서 실리콘 산질화물 게이트 유전체 형성 방법.

#### 청구항 18

제 17 항에 있어서,

상기 집적 프로세싱 시스템의 화학 기상 증착(CVD) 프로세싱 챔버에 상기 기판을 전달하는 단계; 및

상기 기판 상에 폴리실리콘 층을 증착시키는 단계를 더 포함하는

집적 프로세싱 시스템에서 실리콘 산질화물 게이트 유전체 형성 방법.

#### 청구항 19

제 17 항에 있어서,

상기 기판을 제 2 플라즈마에 노출시킨 후, 상기 집적 프로세싱 시스템 외측의 화학 기상 증착(CVD) 프로세싱 챔버에 상기 기판을 전달하는 단계; 및

상기 기판상에 폴리실리콘을 증착시키는 단계를 더 포함하는

집적 프로세싱 시스템에서 실리콘 산질화물 게이트 유전체 형성 방법.

## 청구항 20

제 1 항에 있어서,

상기 플라즈마 질화 프로세스가 디커플링된 플라즈마 질화를 포함하는

실리콘 산질화물 게이트 유전체 형성 방법.

## 명세서

### 기술 분야

[0001]

본 발명의 실시예는 일반적으로 반도체 제조 분야에 관한 것이다. 보다 특히, 본 발명은 실리콘 산질화물 ( $\text{Si}_0\text{N}_y$ ) 게이트 유전체를 형성하는 방법 및 실리콘 산질화물 게이트 유전체를 플라즈마 질화 및 두 단계의 포스트 플라즈마 질화 어닐링(PNA) 프로세스를 이용하여 게이트 스택으로 집적시키는 방법에 관한 것이다.

### 배경기술

[0002]

집적 회로는 트랜지스터, 캐패시터 및 레지스터와 같은 기본 부품으로서 작용하는 사실상 수백만 개의 능동 및 수동 소자로 구성된다. 트랜지스터는 일반적으로 소오스, 드레인 및 게이트 스택을 포함한다. 게이트 스택은 (실리콘) 기판으로 이루어지며 이의 최상부는 유전체 성장되며(보통 실리콘 이산화물;  $\text{SiO}_2$ ) 그리고 (다결정 실리콘과 같은) 전극으로 캡핑(capped)된다.

[0003]

집적 회로 크기 및 이 상부의 트랜지스터 크기가 감소함에 따라, 트랜지스터의 속도를 증가시키기 위해서 요구되는 게이트 구동 전류가 증가된다. 게이트 정전용량이 증가함에 따라 구동 전류가 증가하고, 정전용량이 게이트 유전체 두께에 반비례하기 때문에, 유전체 두께가 감소하는 것이 구동 전류 증가의 하나의 방법이다.

[0004]

$\text{SiO}_2$  게이트 유전체의 두께를 20 Å 미만으로 감소시키려는 시도가 있어왔다. 그러나, 20 Å 미만의 얇은  $\text{SiO}_2$  게이트 유전체의 이용이 종종 게이트 성능 및 내구성에 바람직하지 않은 영향을 미치는 것을 발견했다. 예를 들어, 봉소 도핑된 게이트 전극으로부터의 봉소는 얇은  $\text{SiO}_2$  게이트 유전체를 통해 하부 실리콘 기판으로 침투할 수 있다. 또한 게이트 누출, 즉 터널링(tunneling)의 증가는 통상적이며, 얇은 유전체는 게이트에 의해 소비되는 전력 양을 증가시킨다. 얇은  $\text{SiO}_2$  게이트 유전체는 고온 캐리어 손상에 영향을 받기 쉬울 수 있으며, 여기서 유전체를 따라 이동하는 고 에너지 캐리어가 게이트를 손상 및 파괴시킬 수 있다. 얇은  $\text{SiO}_2$  게이트 유전체는 음전압 온도 불안정성(negative bias temperature instability; NBTI)에 영향을 받기 쉬울 수 있으며, 여기서 임계 전압 또는 구동 전류는 게이트의 작동에 따라 흐른다.

[0005]

결과적으로, 전류 누출 밀도를 감소시키기 위해서 충분히 두꺼운 물리적 두께로 이용될 수 있으며, 여전히 높은 게이트 정전용량을 제공하는 대안적인 게이트 유전체 재료가 필요하다. 이를 달성하기 위해서, 대안적인 게이트 유전체 재료가 실리콘 이산화물보다 높은 유전체 상수를 가져야만 한다. 통상적으로 이러한 대안적인 유전체 재료 중의 두께가 등가 산화물 두께(EOT)로 표현된다. 따라서, 특정 캐패시터의 대안적인 유전체 중의 EOT는, 이의 유전체 상수가 실리콘 이산화물의 유전체인 경우에 대안적인 유전체 중이 가질 수 있는 두께이다.

[0006]

얇은  $\text{SiO}_2$  게이트 유전체가  $\text{SiO}_x\text{N}_y$  게이트를 형성하기 위해서  $\text{SiO}_2$  층 내측으로 질소를 도입시키는데 있어 갖는 문제점을 해결하기 위해서 하나의 방법이 이용된다. 질소를  $\text{SiO}_2$  층으로 도입시키는 것은 게이트 유전체의 유전

체 상수를 상승시키며 하부 실리콘 기판으로 봉소 침투를 차단하여 보다 두꺼운 유전체 층의 이용을 허용한다.

[0007] 열적 성장 실리콘 산질화물은  $0.2 \mu\text{m}$ 에서  $0.13\mu\text{m}$ 까지의 소자 세대 수년 동안 게이트 유전체로서 이용되어 왔다. 소자 기술은  $0.2 \mu\text{m}$ 에서  $0.1\mu\text{m}$ 까지 향상되었으며,  $>25\text{\AA}$ 에서  $<12\text{\AA}$ 까지 얇아졌다. 봉소를 차단하고 게이트 누출을 감소시키기 위해서 필름 내의 질소의 양은  $25\text{\AA} \text{ SiO}_x\text{N}_y$  층에 있어 3%에서  $12\text{\AA} \text{ SiO}_x\text{N}_y$  층에 있어 5~10%로 증가되었다. 질소 산화물(NO) 및 질소 이산화물( $\text{N}_2\text{O}$ )이 산질화물 게이트 유전체를 성장시키는데 이용되는 경우에, 산질화물이 성장함에 따라 동시에 유전체 필름 내에 질소가 도입되며, 따라서 질소가 필름 내에 균일하게 분배된다. NO 또는  $\text{N}_2\text{O}$ 가 상승된 온도에서 현존하는  $\text{SiO}_2$  층을 어닐링함으로써 실리콘 산질화물을 형성하는데 이용된다면, 질소는 Si 기판/산화물 경계면에서 SiON을 성장시킴으로써 도입된다. 실리콘 산질화물을 형성하는 경우에 질소의 양(<2%)은 산질화물 게이트 유전체를 성장시키는데 이용되는 경우(4~5%) 보다 적다.

[0008] 보다 최근에, 플라즈마 질화(PN)는 게이트 산화물을 (상기 산화물 내측으로 질소를 도입시키기 위해서) 질화시키는데 이용되었다. 이러한 기술은 폴리 게이트/산화물 경계면에서 높은 질소 농도를 야기하며, 이는 산화물 유전체 내측으로의 봉소 침투를 방지한다. 동시에, 대량의 산화물 유전체는 플라즈마 질화 프로세스 중에 관련없는 질소로 약간 도핑되며, 이는 개시 산화물(starting oxide)에 걸쳐서 전기적 산화물 두께(EOT)를 감소시킨다. 이는 통상의 열 프로세스보다 높은 동일한 EOT에서 게이트 누출 감소를 달성시킨다. 양호한 채널 이동성 및 구동 전류(Idsat)를 유지하면서 EOT  $<12\text{\AA}$  범위에서 유전체를 스케일링=scaling하는 것은 산업 분야에서 시도되어 왔다.

[0009] 고온에서 실리콘 산질화물의 포스트 질화 어닐링(PNA)은 EOT 증가로, 채널 이동성을 위한 대용으로서 피크 트랜스컨덕턴스(transconductance)를 개선하는 방법으로서 도시되어 있다. 이러한 결과는 어플라이드 머티어리얼 아이엔씨(Applied Materials Inc.)에 양도된 " 저 EOT 플라즈마 질화 게이트 유전체에 대한 두 단계 포스트 질화 어닐링(Two-Step Post Nitridation Annealing For Lower EOT Plasma Nitrided Gate Dielectrics) "의 명칭으로 2004년 3월 4일 출원된 미국 특허 출원 공개 번호 제 2004/0175961 호에 기재되어 있으며, 이는 본 발명의 응용예와 상반되지 않는 범위에서 참조된다.

[0010] 낮은 압력 및 높은 온도에서,  $\text{SiO}_2$ 는  $\text{SiO}$ 로 분류될 것이며, 이는 피팅(pitting)이라 지칭되는 현상을 야기하는 실리콘 표면으로부터 탈착된다.

[0011] 따라서, 실리콘 일산화물 탈착의 문제를 간주하면서 개선된 이동성을 갖는 보다 얇은 EOT를 가지는 실리콘 산질화물 게이트 유전체를 증착시키기 위한 개선된 포스트 어닐링 방법이 필요하다.

### 발명의 상세한 설명

[0012] 본 발명의 실시예는 일반적으로  $\text{SiO}_x\text{N}_y$  게이트 유전체를 형성하는 방법을 제공한다. 본 발명의 방법은 실리콘 산질화물 필름을 형성하기 위해서 플라즈마 질화 프로세스를 이용하는 유전체 필름 내측으로 질소를 도입시키는 단계를 포함한다. 실리콘 산 질화물 필름은 두 단계 포스트 플라즈마 어닐링에 영향을 받는다. 제 1 단계는 제 1 온도에서 제 1 부분압의 산소를 포함하는 불활성 대기를 포함하는 제 1 대기에서 실리콘 산질화물 필름을 어닐링하는 단계를 포함한다. 제 2 단계는 제 2 온도에서 제 2 부분압의 산소를 포함하는 제 2 대기에서 실리콘 산질화물을 어닐링하는 단계를 포함하며, 상기 산소의 제 2 부분압은 산소의 제 1 부분압보다 크다. 제 1 실시예에서, 산소의 제 1 부분압은 약 1 mTorr 내지 100 mTorr이며, 산소의 제 2 부분압은 약 0.1 Torr 내지 100 Torr이다.

[0013] 다른 실시예에서, 게이트 전극은 두 단계 포스트 플라즈마 어닐링 후에 실리콘 산질화물 필름 상에 증착된다. 일 실시예에서, 게이트 전극은 폴리실리콘 필름을 포함한다. 다른 실시예에서, 게이트 전극은 비정질 실리콘 필름을 포함한다. 다른 실시예에서, 게이트 전극은 금속 전극을 포함한다.

[0014] 본 발명의 실시예는 집적 프로세싱 시스템 내에  $\text{SiO}_x\text{N}_y$  게이트 유전체를 형성하는 방법을 또한 제공한다. 실리콘 기판은 실리콘 이산화물 필름이 기판상에 형성되는 집적 프로세싱 챔버의 제 1 프로세싱 챔버 내측으로 도입된다. 기판은 기판이 질소 소오스를 포함하는 플라즈마에 노출되는 집적 프로세싱 시스템의 제 2 프로세싱 챔버에 전달된다. 기판은 기판이 두 단계 포스트 플라즈마 어닐링에 영향을 받는 집적 프로세싱 챔버의 제 3 프로세싱 챔버에 전달된다. 제 1 단계는 제 1 온도에서 제 1 부분압의 산소를 포함하는 불활성 대기를 포함하는 제 1 온도에서 실리콘 산질화물 필름을 어닐링하는 단계를 포함한다. 제 2 단계는 제 2 온도에서 제 2 부분압

의 산소를 포함하는 제 2 단계에서 실리콘 산질화물 필름을 어닐링하는 단계를 포함하며 산소의 제 1 부분압이 산소의 제 1 부분압 보다 크다. 다른 실시예에서, 플라즈마 질화 프로세스는 디커플링된 플라즈마 질화를 포함한다.

[0015] 다른 실시예에서,  $\text{SiO}_{x\text{N}_y}$  게이트 유전체는 실리콘 산화물 필름 내측으로 질소를 도입시키기 위해서  $\text{NH}_3$ 를 포함하는 대기에서 실리콘 기판 상에 실리콘 산화물 필름을 포함하는 구조물을 가열하는 단계 및 기판 상에  $\text{SiO}_{x\text{N}_y}$  게이트 유전체를 형성시키기 위해서 질소 소오스를 포함하는 플라즈마에 구조물을 노출시키는 단계를 포함하는 방법에 의해 형성된다.

[0016] 본 발명의 전술된 특징들을 보다 잘 이해하기 위해서, 간단하게 전술한 본 발명을 몇몇의 예가 첨부 도면에 도시되어 있는 실시예를 참조하여 보다 구체적으로 설명한다. 그러나, 첨부 도면은 본 발명의 전형적인 실시예만을 설명하며 따라서 본 발명의 범위를 제한하는 것은 아니며, 본 발명이 다른 동일한 효과의 실시예를 허용할 수 있다는 것을 주목해야 한다.

## 실시예

[0021] 본 발명의 실시예는 질소 플라즈마(또는 플라즈마 질화) 프로세스를 이용하여  $\text{SiON}$  또는  $\text{SiO}_{x\text{N}_y}$ 와 같은 질소를 포함하는 유전체를 형성하는 방법을 포함한다. 실리콘 산질화물은 두 단계 포스트 플라즈마 질화 어닐링 프로세스로 처리된다. 실시예는 실리콘 산질화물 필름의 질소 농도 프로파일 및 EOT의 제어를 고려한다.

[0022] 하기의 설명에서, 본 발명의 완전한 이해를 제공하기 위해서 설명, 다수의 구체적인 상세한 설명이 기재된다. 그러나, 당업자에게 본 발명은 이러한 구체적인 상세한 설명 없이 실행될 수 있음이 명백할 것이다. 다른 예에서, 구체적인 장치 구조 및 방법은 본 발명을 불명瞭하게 하지 않기 위해서 기재되지 않는다. 하기의 설명 및 도면은 본 발명을 설명하며 본 발명을 제한하도록 구성되는 것은 아니다.

[0023] 일 실시예에서, 디커플링된 플라즈마 질화(DPN)와 같은 플라즈마 질화 프로세스를 이용하는 실리콘 산질화물 유전체 필름을 형성하는 방법이 제공된다. 플라즈마 질화 후에, 실리콘 산질화물이 두 개의 단계 포스트 플라즈마 질화 어닐링(PNA) 프로세스에 영향을 받는다. 제 1 PNA 단계가 실리콘 산화물의 밀도를 높이기 위해서 미량의 산소와 결합하는 불활성제를 이용하여 수행된다. 제 2 PNA 단계가 질소 농도 프로파일을 수정하기 위해서 산화제로 수행된다. 두 단계 PNA 프로세스는 실리콘 산질화물의 표면 및 기판을 향해 질소를 이동시키며, 봉소를 보다 효율적으로 차단시킨다. 게다가, 질소의 농도 프로파일은 실리콘 산질화물의 표면에서 퍼크인 경향이 있다.

[0024] 다른 실시예에서, 트랜지스터와 같은 반도체 소자를 형성하기 위한 게이트 스택으로 두 개의 단계 PNA 프로세스에 의해 수반되는 플라즈마 질화 프로세스를 이용하여 형성되는 실리콘 산화물 필름을 집적시키는 방법이 제공된다.

[0025] 다른 실시예에서, 그 상부에 형성되는 실리콘 이산화물 필름을 가지는 기판은 실리콘 이산화물 필름을 실리콘 산질화물 필름으로 변환하도록 플라즈마 질화 프로세스로 처리된다. 일 실시예에서, 이용되는 플라즈마 질화 프로세스가 당업계에 공지된 디커플링된 플라즈마 질화(DPN)이다. DPN은 질소 프라즈마를 발생시키고 높은 레벨의 질소를 산화물 필름으로 도입시키기 위해서 유도 커플링을 이용하는 기술이다. DPN에서, 표면 필름, 예를 들어  $\text{SiO}_2$  필름은 실리콘 산질화물 필름을 형성하는  $\text{SiO}_2$  필름을 분열시키는 질소 이온과 충돌한다. 일 실시예에서, DPN은 약 5~20 mTorr 내지 10~20 mTorr의 범위의 압력을 갖는 챔버 내에서 수행되며, 플라즈마 압력은 200~800 와트이다. 질소 가스는 약 100~200 sccm 범위의 유동률로 챔버 내측으로 유동될 수 있다. 일 실시예에서, DPN은 약 5~15 kHz의 펄스 및 약 10~20 MHz의 펄스 무선 주파수 플라즈마를 이용한다. DPN 프로세스 매개변수는 챔버 크기 및 부피, 및 유전체 필름의 원하는 두께에 따라 수정될 수 있다.

[0026] 디커플링된 플라즈마 질화 챔버의 다른 상세한 설명이 본 발명의 범위와 일치하지 않는 범위에서 참조되며, 어플라이드 머티어리얼즈 아이엔씨에 양도된 "진폭 변조 무선 주파수 에너지를 이용한 게이트 유전체의 플라즈마 질화를 위한 방법 및 장치(Method And Apparatus For Plasma Nitridation Of Gate Dielectrics Using Amplitude Modulated Radio Frequency Energy)"의 명칭으로 미국 특허 출원 공개 번호 2004/0242021에 기재되어 있다. 적합한 DPN 챔버의 실시예는 캘리포니아 산타클라라에 소재하는 어플라이드 머티어리얼즈로부터 상용으로 입수 가능한 DPN Centura™을 포함한다.

- [0027] 일 실시예에서, 실리콘 산질화물 필름은 두번 어닐링된다. 제 1 어닐링 단계에서, 실리콘 산질화물은 질소 농도의 밀도를 높이기 위해서 어닐링된다. 제 1 어닐링 단계는 미량의 산소와 결합되는 N<sub>2</sub>, He, Ar, 또는 이의 조합과 같은 불활성 가스를 이용하여 불활성 대기에서 실행된다. 일 실시예에서, 제 1 어닐링 단계는 플라즈마 질화 프로세스 후에 즉시 실행된다. 일 실시예에서, 제 1 PNA 단계가 약 1mTorr 내지 50 Torr의 부분압과 같은 약 1mTorr 내지 약 100mTorr 범위의 부분압으로 미량의 산소를 갖는 약 100 mTorr 내지 약 800 Torr 범위의 압력으로 약 1 내지 120 초 동안 약 950°C 내지 1100°C의 온도와 같은 약 700°C 내지 약 1100°C 사이의 온도에서 수행된다. 다른 실시예에서, 미량의 산소가 약 1mTorr 내지 약 30mTorr 범위의 부분압을 가진다. 제 2 PNA 단계는 제 1 PNA 단계에 수반된다. 일 실시예에서, 제 1 PNA 단계 후에, 어닐링 대기는 O<sub>2</sub>, O<sub>2</sub>/N<sub>2</sub>, O<sub>2</sub>/Ar, O<sub>2</sub>/He, N<sub>2</sub>O, 또는 NO와 같은 산화제(또는 산소 함유제)를 포함하는 대기로 변경된다. 제 2 PNA 단계는 약 900°C 내지 1100°C 또는 약 1000°C 내지 1050°C의 온도에서 약 10 mTorr 내지 약 100 Torr 범위의 감소된 압력으로 실행된다. 제 2 PNA 단계는 약 1~120 초 동안 실행될 수 있다. 일 실시예에서, 제 2 PNA 단계의 온도, 시간 및 압력은 실리콘 산질화물의 EOT에서의 0.1Å 내지 2Å 증가를 달성하도록 제어된다.

- [0028] 일 실시예에서, 제 1 PNA 단계 및 제 2 PNA 단계는 급속 열 어닐링(RTA) 프로세스를 실행하도록 구성되는 단일 웨이퍼 급속 열 프로세싱(RTP) 챔버에서 수행된다. 어플라이드 머티어리얼즈 아이엔씨에 의해 제조된 XE, XE Plus 또는 Radiance와 같은 상용으로 입수 가능한 감압형(RTP) 챔버 하드웨어는 제 1 및 제 2 PNA 프로세스를 실행하도록 이용될 수 있다.

- [0029] 바람직하게, 본 명세서에 기재된 SiO<sub>x</sub>N<sub>y</sub> 게이트 유전체는 약 5 원자 퍼센트 질소를 포함하는 것으로 기재되어 있다. 일 실시예에서, SiO<sub>x</sub>N<sub>y</sub> 게이트 유전체는 약 5 원자 퍼센트 질소 내지 약 15 원자 퍼센트 질소를 포함한다.

- [0030] 구조물이 플라즈마에 노출되고 어닐링된 후에, 폴리실리콘 층, 비정질 실리콘 층, 또는 금속 층과 같은 게이트 전극이 게이트 스택을 완성시키기 위해서 SiO<sub>x</sub>N<sub>y</sub> 상에 증착될 수 있다.

- [0031] 집적되는 프로세싱 순서

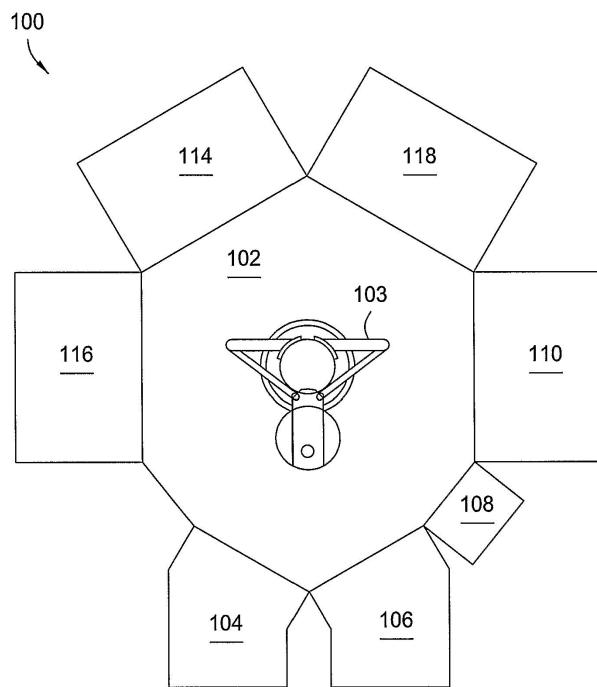

- [0032] 다른 실시예에서, SiO<sub>x</sub>N<sub>y</sub> 게이트 유전체는 집적되는 반도체 프로세싱 시스템과 같은 집적되는 프로세싱 시스템 내의 기판 상에 형성될 수 있으며, 이러한 방법에서 기판은 SiO<sub>x</sub>N<sub>y</sub> 게이트 유전체가 형성될 때까지 집적 프로세싱 시스템으로부터 제거되지 않는다. 이용될 수 있는 집적 프로세싱 시스템(100)의 실시예는 도 1에 도시된, 캘리포니아 산타 클라라에 소재하는 어플라이드 머티어리얼즈 아이엔씨로부터 입수 가능한 Gate Stack Centura® 시스템이다. 집적 프로세싱 시스템(100)은 중앙 전달 챔버(102), 전달 로봇(103), 로드 록(104, 106), 냉각 챔버(108), 증착 챔버(110), 플라즈마 프로세싱 챔버(114), 및 두 개의 급속 열 프로세싱(RTP) 챔버(116, 118)를 포함한다. 증착 챔버(110)는 당업계에 공지된 층 또는 필름을 형성하기 위해서 이용될 수 있는 통상의 화학 또는 물리 기상 증착일 수 있다. 일 실시예에서, CVD 프로세싱 챔버(110)는 어플라이드 머티어리얼즈로부터 입수 가능한 POLYgen 챔버와 같은 저압 화학 기상 증착 챔버(LPCVD)이다. RTP 챔버(116, 118)는 감압 또는 초저압(예를 들어, 약 10 Torr와 동일하거나 그 보다 작은)에서 급속 열 어닐링(RTA) 프로세스가 구동되는 챔버이다.

- [0033] 다른 실시예에서, 기판이 집적 프로세싱 시스템 내측으로 도입되며, 실리콘 산화물 필름, SiO<sub>x</sub>N<sub>y</sub> 게이트 유전체, 및 게이트 전극이 집적 프로세싱 시스템으로부터 기판을 제거하지 않은 챈 기판 상에 증착된다. 이러한 실시예는 도 1 및 도 2와 관련하여 아래에 기재될 것이다.

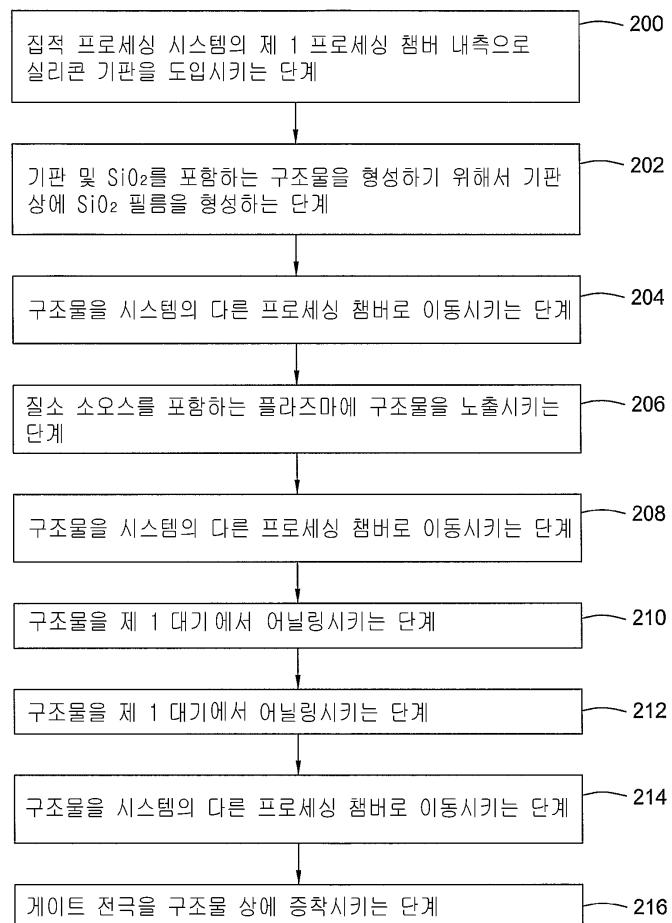

- [0034] SiO<sub>x</sub>N<sub>y</sub> 게이트 유전체가 집적 프로세싱 시스템에서 형성되는 실시예에 있어서 프로세싱 조건은 실리콘 산화물 필름 및 SiO<sub>x</sub>N<sub>y</sub> 게이트 유전체의 형성에 대해 전술된 프로세싱 조건과 동일하다. 실리콘 기판은 로드 록(104, 106)을 통해 집적 프로세싱 시스템(100) 내측으로 도입되며 RTP 챔버(116) 내에 위치되며, 여기서 실리콘 산화물 필름은 도 2의 단계(200 및 202)에 도시된 바와 같이 실리콘 기판 상에 형성된다. 기판 및 실리콘 산화물 필름을 포함하는 구조물은 플라즈마 프로세싱 챔버(114)에 전달되며, 여기서 질소 소오스를 포함하는 플라즈마에 노출되어 질소를 실리콘 산화물 필름으로 도입시키며, 단계 (204 및 206)에 도시된 바와 같이 SiO<sub>x</sub>N<sub>y</sub> 게이트 유전체를 형성한다. 구조물은 단계(210 및 212)에 도시된 바와 같이 어닐링되는 단계(208)에 도시된 바와 같은 RTP 챔버(116)에 전달된다. 구조물은 단계(214)에 도시된 바와 같이 CVD 프로세싱 챔버(110)에 전달되며, 폴리 실리콘 층 또는 비정질 실리콘 층과 같은 게이트 전극은 단계(216)에 도시된 바와 같이 구조물 상에 증착된다. 구조물은 로드 록(104, 106)을 통해 집적 프로세싱 시스템(100)으로부터 제거된다.

- [0035] 도 1 및 도 2와 관련하여 기재된 실시예에서, 실리콘 산화물 필름은 하나의 단계에서 RTP 챔버(116) 상에 형성되며, 구조물은 다음 단계에서 RTP 챔버(118) 내에서 어닐링된다. 대안적인 실시예에서, 단일 RTP 챔버는 실리콘 산화물 필름을 형성하고 또한 두 개의 단계 포스트 플라즈마 어닐링을 수행하도록 구성된다.

- [0036] 다른 실시예에서, 실리콘 기판 상에 실리콘 이산화물 필름을 포함하는 구조물은 질소를 실리콘 산화물 필름으로 도입시키기 위해서 집적 프로세싱 시스템의 제 1 프로세싱 챔버 내의  $\text{NH}_3$ 를 포함하는 대기에서 가열된다. 기판이 밀폐된 집적 프로세싱 시스템 내에서  $\text{NH}_3$ 를 포함하는 대기에 노출되기 때문에,  $\text{NH}_3$ 를 포함하는 대기에서 가열 중에 산소를 오염시키는 것이 구조물 내측으로 도입되지 않는다. 구조물은 제 2 프로세싱 챔버 내의 질소 소오스를 포함하는 플라즈마에 노출되며 집적 프로세싱 시스템의 제 2 프로세싱 챔버에 전달된다. 구조물을 플라즈마에 노출시킨 후에, 구조물은 집적 프로세싱 시스템의 제 3 프로세싱 챔버에 전달되며 제 3 프로세싱 챔버 내에서 어닐링된다.

- [0037] 질소를 포함하는 플라즈마를 갖는 구조물을 처리하기 전에  $\text{NH}_3$ 를 포함하는 대기 내의 구조물은 게이트 유전체와 하부 실리콘 기판 사이의 경계면을 평탄화시키며, 강화된 소자 성능 및 신뢰도를 야기하는 것으로 믿어진다. 구조물을 처리하는 플라즈마 이전에  $\text{NH}_3$ 를 포함하는 대기에 우선 구조물을 가열함으로써 약간 두꺼운 산화물 필름의 형성이 PMOS 소자의 성능 특징을 강화하는 것으로 믿어진다.

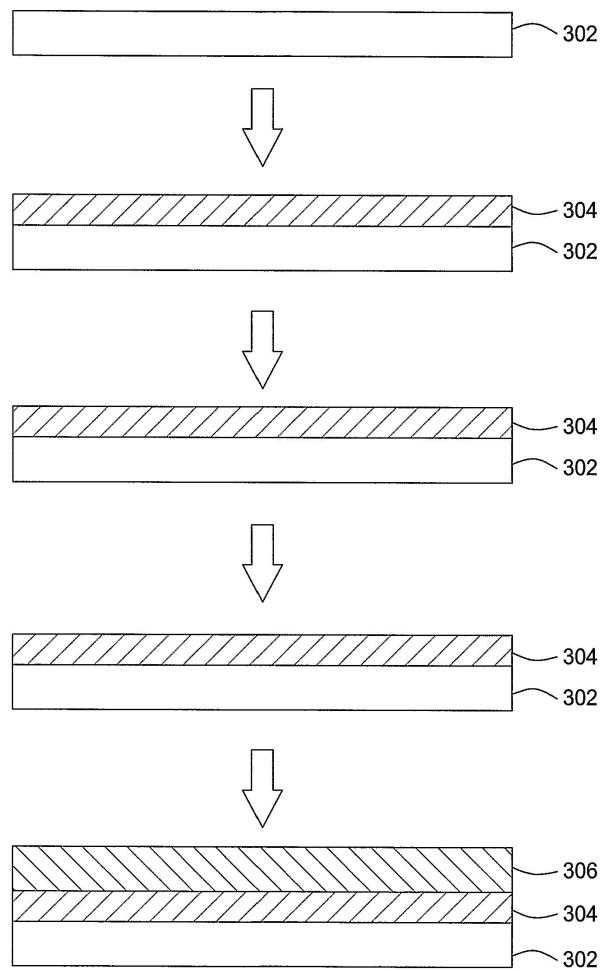

- [0038] 도 3은 본 발명의 실시예에 따라 게이트 스택을 형성하는 예시적 순서를 도시하고 있다. 기판(302)은 통상적으로 반도체 소자를 제조하는데 이용되는 단결정 실리콘 또는 반도체 웨이퍼일 수 있다. 일 실시예에서,  $\text{SiO}_2$  필름(304)은 약 4~15 Å의 물리적 두께를 가진다.

- [0039] 일 실시예에서,  $\text{SiO}_2$  필름(304)은 집적 프로세싱 시스템(100)(도 1)의 RTP 챔버(116)와 같은 감압형 RTP 챔버를 이용하여 성장된다.  $\text{SiO}_2$  필름(304)은 산소의 존재하에 산화되는 층을 형성하기 위해서 챔버에서 기판 표면을 급속하게 가열 및 건조시키기 위해서 램프를 이용하는 산화 프로세스인 급속 열 산화에 의해 형성된다. 실리콘 기판(또는 웨이퍼)의 급속 열 산화는  $\text{O}_2$ ,  $\text{O}_2+\text{N}_2$ ,  $\text{O}_2+\text{Ar}$ ,  $\text{N}_2\text{O}$ , 또는  $\text{N}_2\text{O}+\text{N}_2$  가스 혼합물의 존재와 함께 건조 프로세스 급속 열 산화를 이용하여 실행된다. 가스 또는 가스 혼합물은 약 1~5 slm의 총 유동률을 가질 수 있다. 이와 달리, 실리콘 기판의 급속 열 산화는 예를 들어, 1~13%  $\text{H}_2$ 를 갖는 약 1~5 slm의 총 유동률을 가지는,  $\text{O}_2+\text{H}_2$ ,  $\text{O}_2+\text{H}_2+\text{N}_2$  또는  $\text{N}_2\text{O}+\text{H}_2$ 의 존재 상태에서 인-시츄 증기 발전(In-Situ Steam Generation; ISSG)과 같은 습식 프로세스를 이용하여 실행된다. 일 실시예에서,  $\text{SiO}_2$  유전체 필름을 형성하기 위해서 이용되는 급속 열 산화 프로세스는 약 5~90 초 동안 약 0.5~50 Torr의 프로세싱 압력 및 약 750~1000°C의 프로세싱 온도에서 수행되어 약 4~15 Å 범위의 두께를 가지는  $\text{SiO}_2$  유전체 필름을 야기한다.

- [0040] 일 실시예에서,  $\text{SiO}_2$  필름(304)이 RTP 챔버(116)에서 형성된 후에, 기판(302)은 불활성(예를 들어,  $\text{N}_2$  또는  $\text{Ar}$ ) 대기 하에서 집적 프로세싱 시스템(100)의 DPN 챔버(114)에 전달되며, 전달 챔버 압력은 대략 플라즈마 질화 프로세스를 위해 동일한 압력을 가진다. 플라즈마 질화 프로세스는 실리콘 산질화물 필름(304)을 형성하기 위해서  $\text{SiO}_2$  필름(304) 내측으로 질소를 도입하고 질소 플라즈마에  $\text{SiO}_2$  필름(304)을 노출시킨다. 일 실시예에서, DPN 챔버(114)는  $\text{N}_2$ ,  $\text{He}$ , 또는  $\text{Ar}$ 과 같은 불활성 가스를 수용할 수 있는 감압형 유도 결합식 RF 플라즈마 반응기이다.

- [0041] 실리콘 산질화물 필름(304)은 RTP 챔버, 예를 들어, 집적 프로세싱 시스템(100)의 RTP 챔버(118) 내에서 두 단계 포스트 질화 어닐(PNA) 프로세스에 영향을 받는다. RTP 챔버(118)는 어플라이드 머티어리얼즈 반응기 XE, XE Plus, 또는 Radiance와 같은 감압형 챔버 반응기일 수 있다. PNA가 약 700°C와 동일하거나 그보다 높은 온도에서 질소 플라즈마 처리되는 필름(실리콘 산질화물 필름(304))의 밀도를 높이기 위해서 적당한(mild) 산화 대기(불활성 대기)에서 우선 발생하며, 이는 약 900°C와 동일하거나 그보다 높은 온도에서 산화 대기 내의 제 2 어닐링을 수반한다. 제 1 PNA 단계에 있어서, 미량의  $\text{O}_2$ 를 가지는 불활성 가스(예를 들어,  $\text{N}_2$  또는  $\text{Ar}$ )은 실리콘 산질화물 필름(304)의 밀도를 높이기 위해서 RTP 챔버 내측으로 유동된다. 제 1 실시예에서, 제 1 PNA는 실리콘 산 질화물 필름(304)을 가지는 기판을 약 5 Torr와 동일하거나 또는 그 미만의 총 압력에서 약 700 °C와 동일하거나 그보다 높은 적합한 어닐링 온도에서 가열하는 단계를 포함한다. 일 실시예에서, 약 1 slm의  $\text{N}_2$  가스와 같은 불활성 가스가 약 60~120 초 동안 RTP 챔버 내측으로 유동되며, 미량의 산소가 약 5 Torr의 압력 및

약 30 sccm의 유동률로 챔버 내측으로 유동된다. 제 1 PNA 다음에, RTP 챔버는 불활성 가스가 배출되며  $O_2$ 와 같은 산화 가스가 제 2 PNA를 위해 RTP 챔버 내측으로 유동된다. 온도는 약 900°C와 동일하거나 이보다 높은 온도로 변경될 수 있다. 산화 가스가 약 15 초 동안 약 1 slm 총 유동률로 RTP 챔버 내측으로 유동된다. 전술된 유동률은 특정 반응기 또는 프로세스 챔버 크기(예를 들어, 20 mm 반응기)만을 위한 실시예이다. 유동률은 부피 차이로 인해서 다른 크기 반응기를 위해 비례적으로 조절(증가 또는 감소)된다.

[0042] 일 실시예에서, 두 단계 PNA 프로세스 다음에, 실리콘 산 질화물 필름(304)이 폴리실리콘 필름(306)과 같은 전도성 층으로 캡핑된다. 폴리실리콘 필름(306)은 집적 프로세싱 시스템(100)의 증착 챔버(110)와 같은 증착 챔버 내에 형성될 수 있다(도 1). 폴리실리콘 대신에, 필름(306)이 비정질 실리콘 필름 또는 다른 적합한 전도성 재료일 수 있다. 또한, 티타늄, 티타늄 질화물, 탄탈, 탄탈 질화물, 텉스텐, 텉스텐 질화물, 및 다른 내화 재료 또는 다른 적합한 전극 재료와 같은 금속이 그 위에 증착될 수 있다. 증착 챔버(110)는 집적 프로세싱 시스템(100) 내측으로 도입될 수 있는 저압 화학 기상 증착 챔버(LPCVD)일 수 있다. 폴리실리콘 필름(306)의 형성 후에, 게이트 스택이 냉각 챔버(108)로 전달되며 그 후 추가의 프로세싱, 테스트, 또는 당업계에 공지된 다른 프로세스를 위해서 로드 록(104, 106)과 같은 저장 영역에 전달된다.

[0043] 게이트 유전체 필름 및 폴리실리콘 캡 필름을 포함하는 게이트 스택은 전술된 집적 프로세싱 시스템(100) 내측으로 필수적으로 도입되지 않는 몇몇 프로세싱 챔버 내에 형성될 수 있음을 인식해야 한다. 예를 들어,  $SiO_2$  필름이 하나의 챔버 내에 우선 형성될 수 있다.  $SiO_2$  필름은 플라즈마 질화 챔버 내에서 실리콘 산질화물로 전환될 수 있다. 실리콘 산질화물 챔버는 RTP 챔버를 이용하여 두 단계의 PNA 프로세스에서 어닐링된다. 폴리실리콘 필름은 동일한 RTP 챔버 내의  $SiON$  또는  $SiO_xN_y$  필름 위에 형성된다.

#### 포스트 어닐링되는 $SiO_xN_y$ 게이트 유전체의 성능

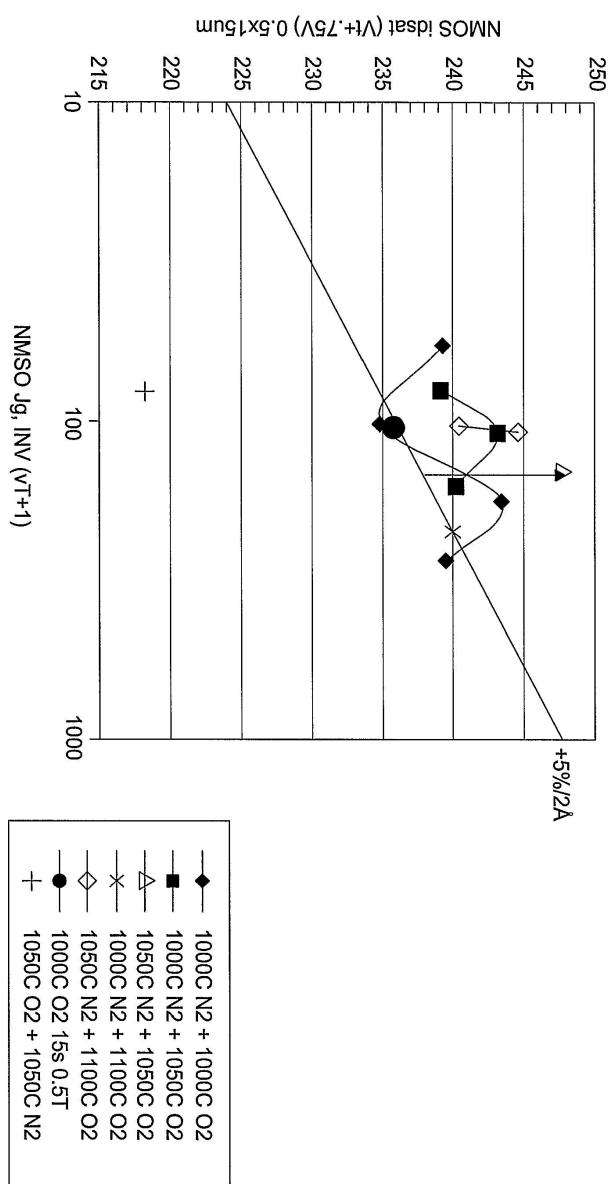

[0044] 도 4에 도시된 바와 같이, 실리콘 산질화물의 두 단계 포스트 어닐링의 제 1 단계에서 미량의 산소를 포함하는 것은 NMOS 게이트 누출에 대해 NMOS 구동 전류를 개선시킨다. 도 4에서, x-축선은 NMOS 게이트 누출을 나타내며, y 축선은 NMOS 구동 전류를 나타낸다. 예를 들어, 약 10 Å의  $SiO_2$  필름이 기본 산화물로 이용된다. 플라즈마 질화 후에, 다양한 포스트 어닐링 조건이 필름을 어닐링하는데 이용된다. 예를 들어, 질소 가스의 존재하에 산소의 15 mTorr 부분압에서 30초 동안 1000°C에서 어닐링하는 단계를 포함하는 제 1 단계는 10 Torr의 산소에서 15초 동안 1000°C에서의 제 2 단계를 수반한다. 다른 실시예에서, 질소 가스의 존재하에 산소의 15 mTorr에서 15초 동안 1000°C에서 어닐링하는 단계를 포함하는 제 1 단계는 1.5 Torr의 산소에서 15초 동안 1050°C에서의 제 2 단계를 수반한다. 다른 실시예에서, 질소 가스의 존재하에 산소의 15 mTorr에서 30초 동안 1050°C에서 어닐링하는 단계를 포함하는 제 1 단계는 0.5 Torr에서 15초 동안 1050°C에서의 제 2 단계를 수반한다. 다른 실시예에서, 질소 가스의 존재하에 산소의 0.015 mTorr에서 30초 동안 1000°C에서 어닐링하는 단계를 포함하는 제 1 단계는 0.05 Torr의 산소에서 5초 동안 1100°C에서의 제 2 단계를 수반한다. 도 1에 도시된 바와 같이, 제 1 단계에서 미량의 산소를 포함하는 두 단계 포스트 어닐링은 제 1 단계에서 미량의 산소 없이 두 단계 포스트 어닐링에 비해 NMOS Idast에서 4% 개선을 나타낸다.

[0045] 본 발명의 임의의 특정 이론에 제한하지 않고, 두 단계 포스트 플라즈마 어닐링의 제 1 단계에서 미량의 산소 첨가가, 유전체를 죽이시키고 손상시킬 수 있는  $SiO$  형성을 방지함이 믿어진다.

[0046] 전술된 내용은 본 발명의 실시예에만 제한되는 것은 아니며, 본 발명의 여타 다른 실시예가 본 발명의 기본 범위를 벗어나지 않고 고안될 수 있으며, 본 발명의 범위는 아래 청구범위에 의해 결정된다.

## 도면의 간단한 설명

[0017] 도 1은 집적 프로세싱 시스템의 개략적인 평면도이며,

[0018] 도 2는 본 발명의 일 실시예를 도시하는 흐름도이며,

[0019] 도 3은 본 발명의 실시예에 따라 게이트 스택을 형성하는 예시적인 순서를 도면이며,

[0020] 도 4는  $SiO_xN_y$  게이트 유전체를 포함하는 게이트 스택을 위한 NMOS 게이트 누출에 대해 네거티브 채널 금속 산화물 반도체(NMOS) 구동 전류를 도시하는 그래프이다.

도면

도면1

## 도면2

도면3

## 도면4