(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4768134号

(P4768134)

(45) 発行日 平成23年9月7日(2011.9.7)

(24) 登録日 平成23年6月24日(2011.6.24)

(51) Int.Cl.

F 1

G09G 3/28 (2006.01)

G09G 3/28

H

G09G 3/20 (2006.01)

G09G 3/20

622Q

G09G 3/20

624M

G09G 3/20

641E

請求項の数 3 (全 21 頁)

|           |                               |           |                                                        |

|-----------|-------------------------------|-----------|--------------------------------------------------------|

| (21) 出願番号 | 特願2001-12417 (P2001-12417)    | (73) 特許権者 | 599132708<br>日立プラズマディスプレイ株式会社<br>宮崎県東諸県郡国富町大字田尻1815番地1 |

| (22) 出願日  | 平成13年1月19日 (2001.1.19)        | (74) 代理人  | 100090273<br>弁理士 國分 孝悦                                 |

| (65) 公開番号 | 特開2002-215086 (P2002-215086A) | (72) 発明者  | 高森 孝宏<br>神奈川県川崎市高津区坂戸3丁目2番1号<br>富士通日立プラズマディスプレイ株式会社内   |

| (43) 公開日  | 平成14年7月31日 (2002.7.31)        | (72) 発明者  | 瀬戸口 典明<br>宮崎県東諸県郡国富町田尻1815 九州エフエイチピー株式会社内              |

| 審査請求日     | 平成19年12月3日 (2007.12.3)        |           |                                                        |

最終頁に続く

(54) 【発明の名称】 プラズマディスプレイ装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

維持放電期間において、隣接する2本の維持放電電極対の各々に正の電圧  $V_s / 2$  と負の電圧 ( $-V_s / 2$ ) とを交互に印加して表示セルにて表示放電を行うプラズマディスプレイ装置の駆動方法であって、

上記維持放電電極対の一方の電極に正の電圧  $V_s$  を印加し、上記維持放電電極対の他方の電極及び、上記表示セルを選択するためのアドレス電極にグランドレベルの電圧を印加する壁電荷形成工程と、

次いで、上記維持放電電極対の双方の電極に上記グランドレベルの電圧を印加し、上記アドレス電極に所定の正の電圧を印加する自己消去工程とを備え、

上記正の電圧  $V_s$  は、上記自己消去工程での上記アドレス電極への上記所定の正の電圧の印加により上記アドレス電極と上記維持放電電極対の一方の電極との間で自己消去放電が可能な壁電荷を、上記維持放電電極対間での放電により上記アドレス電極上及び上記維持放電電極対の一方の電極上に形成する電圧であることを特徴とするプラズマディスプレイ装置の駆動方法。

## 【請求項 2】

上記壁電荷形成工程は、上記維持放電電極対の一方の電極に上記正の電圧  $V_s$  を印加した後、上記維持放電電極対の他方の電極に上記正の電圧  $V_s$  を印加することを特徴とする請求項1記載のプラズマディスプレイ装置の駆動方法。

## 【請求項 3】

10

20

上記壁電荷形成工程と上記自己消去工程とは、リセット工程、アドレス工程および維持放電工程により構成されるサブフィールド間に設けたことを特徴とする請求項1又は2記載のプラズマディスプレイ装置の駆動方法。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、プラズマディスプレイ装置の駆動方法に関し、特に、3電極面放電型プラズマディスプレイ装置の駆動方法に用いて好適なものである。

**【0002】**

**【従来の技術】**

従来から、交流駆動型プラズマディスプレイパネル(Plasma Display Panel:PDP)は、自己発光型の表示装置であるため視認性が良く、薄型で大画面表示が可能であることから、CRTに代わる次世代の表示装置として注目されている。特に、面放電型PDPは、大画面化が可能なことから、高品位デジタル放送に対応した表示装置としての期待が高まっており、CRTを凌ぐ高画質化が要求されている。10

**【0003】**

交流駆動型PDPには、2本の電極で選択放電(アドレス放電)および維持放電を行う2電極型と、第3の電極を利用してアドレス放電を行う3電極型がある。また、上記3電極型においては、維持放電を行う第1の電極と第2の電極とが配置されている基板に第3の電極を形成する場合と、対向するもう1つの基板に当該第3の電極を形成する場合がある。20

**【0004】**

上記した各タイプのPDP装置は、何れも動作原理は同一であるので、以下では、維持放電を行う第1および第2の電極を第1の基板に設けるとともに、これとは別に、当該第1の基板と対向する第2の基板に第3の電極を設けたPDP装置についてその構成例を説明する。

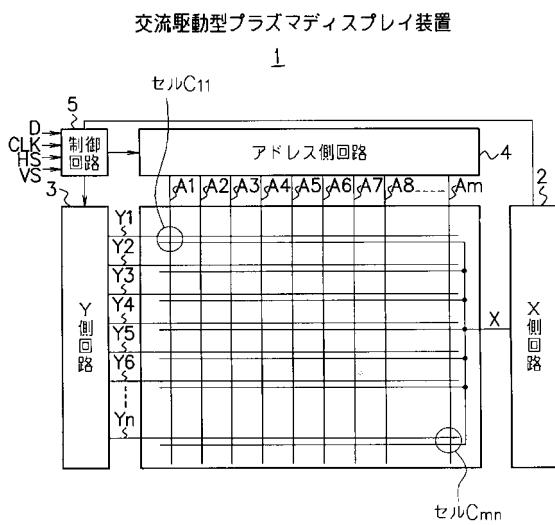

**【0005】**

図10は、交流駆動型PDP装置の全体構成を示す図である。図10において、交流駆動型PDP装置は、各セルが表示画像の1画素であるマトリックス状に配置された複数のセルを備えており、図10においてはm行n列のマトリックスに配置されたセルC<sub>m n</sub>からなる交流駆動型PDP装置を示している。また、交流駆動型PDPには、第1の基板に互いに平行な走査電極Y<sub>1</sub>～Y<sub>n</sub>および共通電極Xが設けられるとともに、上記第1の基板に対向する第2の基板にこれらの電極Y<sub>1</sub>～Y<sub>n</sub>、Xと直交する方向にアドレス電極A<sub>1</sub>～A<sub>m</sub>が設けられている。共通電極Xは、各走査電極Y<sub>1</sub>～Y<sub>n</sub>に対応してこれに接近して設けられ、一端が互いに共通に接続されている。30

**【0006】**

上記共通電極Xの共通端はX側回路2の出力端に接続され、各走査電極Y<sub>1</sub>～Y<sub>n</sub>はY側回路3の出力端に接続されている。また、アドレス電極A<sub>1</sub>～A<sub>m</sub>はアドレス側回路4の出力端に接続されている。X側回路2は放電を繰り返す回路から成り、Y側回路3は線順次走査する回路と放電を繰り返す回路とから成る。また、アドレス側回路4は、表示すべき列を選択する回路から成る。40

**【0007】**

これらのX側回路2、Y側回路3およびアドレス側回路4は、駆動制御回路5から供給される制御信号により制御される。すなわち、アドレス側回路4とY側回路3内の線順次走査する回路によりどこのセルを点灯させるかを決め、X側回路2およびY側回路3の放電を繰り返すことによって、PDPの表示動作を行う。

**【0008】**

制御回路5は、外部からの表示データD、表示データDの読み込みタイミングを示すクロックCLK、水平同期信号HSおよび垂直同期信号VSに基づいて上記制御信号を生成し、X側回路2、Y側回路3およびアドレス側回路4に供給する。50

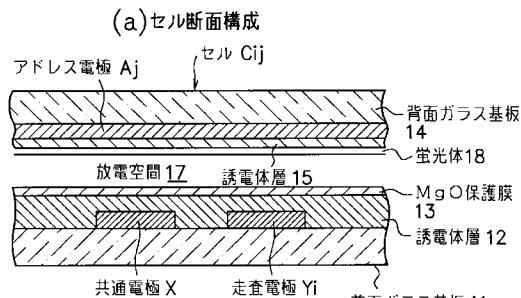

**【 0 0 0 9 】**

図11(a)は、1画素である第*i*行第*j*列のセルC<sub>*i**j*</sub>の断面構成を示す図である。図11(a)において、共通電極Xおよび走査電極Y<sub>*i*</sub>は、前面ガラス基板11上に形成されている。その上には、放電空間17に対し絶縁するための誘電体層12が被着されるとともに、更にその上にMgO(酸化マグネシウム)保護膜13が被着されている。

**【 0 0 1 0 】**

一方、アドレス電極A<sub>*j*</sub>は、前面ガラス基板11と対向して配置された背面ガラス基板14上に形成され、その上には誘電体層15が被着され、更にその上に蛍光体18が被着されている。MgO保護膜13と誘電体層15との間の放電空間17には、Ne+Xeペニンゲガス等が封入されている。

10

**【 0 0 1 1 】**

図11(b)は、交流駆動型PDPの維持放電を行うセルの容量について説明するための図である。図11(b)に示すように、交流駆動型PDPには、放電空間17、共通電極Xと走査電極Yとの間、および前面ガラス基板11にそれぞれ容量成分C<sub>a</sub>、C<sub>b</sub>、C<sub>c</sub>が存在し、これらの合計によって維持放電電極間のセル1つ当たりの容量C<sub>p cell</sub>が決まる(C<sub>p cell</sub>=C<sub>a</sub>+C<sub>b</sub>+C<sub>c</sub>)。全ての維持放電電極間のセルの容量C<sub>p cell</sub>の合計がパネル全体での維持放電を行うセルの容量である。

**【 0 0 1 2 】**

また、図11(c)は、交流駆動型PDPの発光について説明するための図である。図11(c)に示すように、リブ16の内面には、赤、青、緑色の蛍光体18がストライプ状に各色毎に配列、塗付されており、共通電極Xおよび走査電極Yの間の放電によって蛍光体18を励起して発光するようになっている。

20

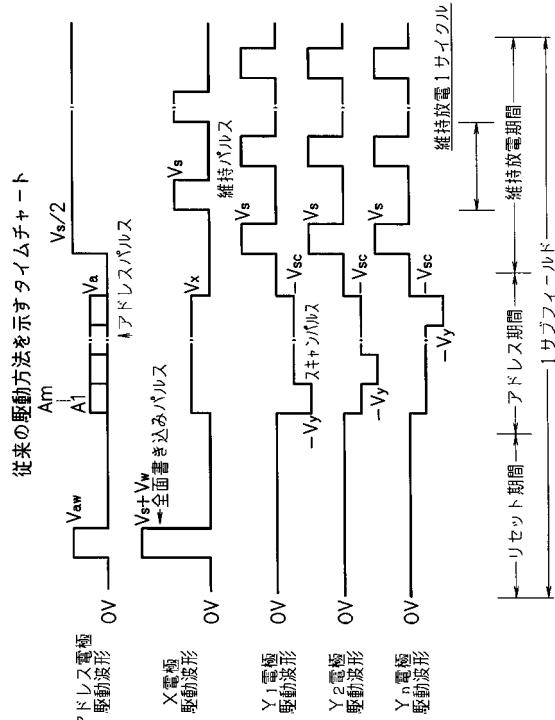

**【 0 0 1 3 】**

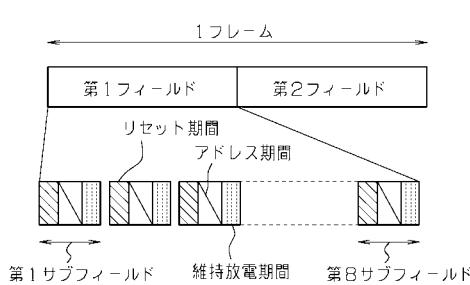

図12は、従来の交流駆動型PDPの駆動方法の一例を示すタイムチャートであり、いわゆる「アドレス/維持放電期間分離型・書き込みアドレス方式」のタイムチャートを示している。なお、図12に示すタイムチャートは、1フレームを構成する複数のサブフィールドのうちの1サブフィールド分を示しており、1つのサブフィールドは、全面書き込み期間および全面消去期間から成るリセット期間と、アドレス期間と、維持放電期間とに区分される。

**【 0 0 1 4 】**

30

リセット期間においては、まず全ての走査電極Y<sub>1</sub>~Y<sub>n</sub>がグランドレベル(0V)にされ、これと同時に共通電極Xに電圧V<sub>s</sub>+V<sub>w</sub>(約400V)から成る全面書き込みパルスが印加される。このときのアドレス電極A<sub>1</sub>~A<sub>m</sub>の電位は、全てV<sub>a w</sub>(約100V)である。この結果、以前の表示状態に関わらず、全表示ラインの全セルで放電が行われ、壁電荷が形成される。

**【 0 0 1 5 】**

次に、共通電極Xとアドレス電極A<sub>1</sub>~A<sub>m</sub>の電位が0Vとなることにより、全セルにおいて壁電荷自身の電圧が放電開始電圧を越えて放電が開始される。この放電では、電極間の電位差がないため、壁電荷が形成されることではなく、空間電荷は自己中和して放電が終息する。いわゆる自己消去放電である。この自己消去放電によって、パネル内の全セルの状態が壁電荷のない均一な状態となる。このリセット期間は、前のサブフィールドにおける各セルの点灯状態に関わらず全てのセルを同じ状態にする作用があり、これにより次のアドレス(書き込み)放電を安定して行うことができる。

40

**【 0 0 1 6 】**

次に、アドレス期間において、表示データに応じて各セルのON/OFFを行うために、線順次でアドレス放電が行われる。すなわち、まず第1表示ラインに相当する走査電極Y<sub>1</sub>に-V<sub>y</sub>レベル(約-150V)、他の表示ラインに相当する走査電極Y<sub>2</sub>~Y<sub>n</sub>に-V<sub>sc</sub>レベル(約-50V)の電圧が印加されるとともに、各アドレス電極A<sub>1</sub>~A<sub>m</sub>中の維持放電を起こすセル、すなわち点灯させるセルに対応するアドレス電極A<sub>j</sub>に、電圧V<sub>a</sub>(約50V)のアドレスパルスが選択的に印加される。

50

**【 0 0 1 7 】**

この結果、点灯させるセルのアドレス電極 A<sub>j</sub> と走査電極 Y<sub>1</sub>との間で放電が起こり、これをプライミング(種火)として、電圧 V<sub>X</sub>(約 50V)の共通電極 X と走査電極 Y<sub>1</sub>との放電に即移行する。これにより、選択セルの共通電極 X および走査電極 Y<sub>1</sub>の上の MgO 保護膜 13 面に、次の維持放電が可能な量の壁電荷が蓄積される。以下、他の表示ラインに相当する走査電極 Y<sub>2</sub> ~ Y<sub>n</sub>についても同様に、選択セルの走査電極には -V<sub>y</sub> レベルの電圧が順次印加され、非選択セルの残りの走査電極には -V<sub>s c</sub> レベルの電圧が印加されることにより、全表示ラインにおいて新たな表示データの書き込みが行われる。

**【 0 0 1 8 】**

その後、維持放電期間になると、走査電極 Y<sub>1</sub> ~ Y<sub>n</sub> と共通電極 X とに電圧 V<sub>s</sub>(約 200V)から成る維持パルスが交互に印加されて維持放電が行われ、1 サブフィールドの映像表示が行われる。なお、「アドレス / 維持放電期間分離型・書き込みアドレス方式」においては、この維持放電期間の長短、つまり維持パルスの回数によって、映像の輝度が決定される。

**【 0 0 1 9 】**

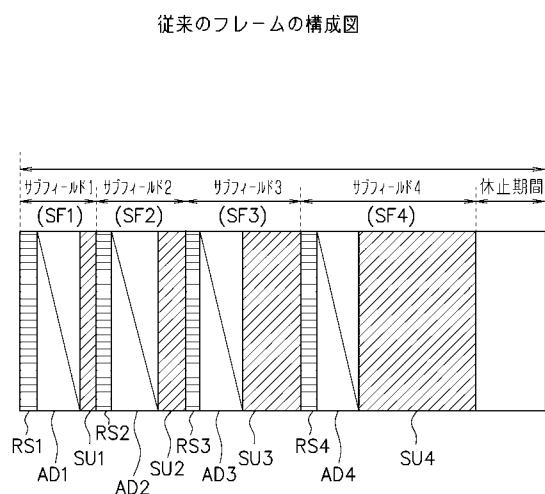

図 13 は、従来の 1 フレームの構成例を示す図である。なお、図 13 においては、多階調表示の一例として 16 階調表示を行う場合の 1 フレームの構成を示している。

**【 0 0 2 0 】**

図 13において、1 フレームは 4 つのサブフィールド S F 1、S F 2、S F 3、S F 4 で構成される。また、サブフィールド S F 1 ~ S F 4 は、それぞれリセット期間 R S 1 ~ R S 4、アドレス期間 A D 1 ~ A D 4 および維持放電期間 S U 1 ~ S U 4 からなり、各サブフィールド S F 1 ~ S F 4 のリセット期間 R S 1 ~ R S 4、アドレス期間 A D 1 ~ A D 4 はそれぞれ同じ長さの期間である。

**【 0 0 2 1 】**

また、維持放電期間 S U 1 ~ S U 4 の長さは、S U 1 : S U 2 : S U 3 : S U 4 = 1 : 2 : 4 : 8 である。したがって、上記サブフィールド S F 1 ~ S F 4 の中からセルを点灯させるサブフィールドを選択することにより、0 ~ 15までの 16 段階の輝度で階調表示できる。なお、休止期間は、駆動波形を出力しない期間である。

**【 0 0 2 2 】**

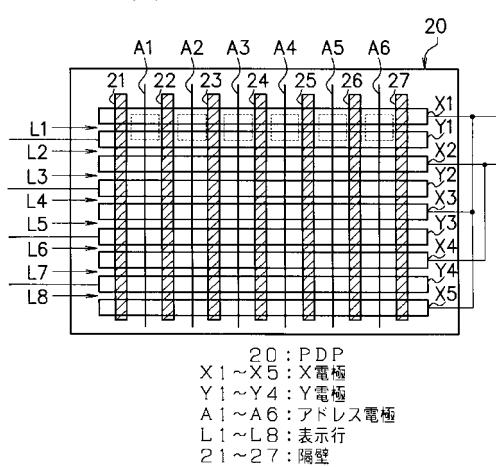

図 14 は、面放電型 PDP の構成を示す図であり、すべての維持放電電極(X 電極および Y 電極)間で放電させ表示を行うプラズマディスプレイの構成を示すものである。

**【 0 0 2 3 】**

図 14(a) は、面放電型 PDP の概略構成図である。面放電型 PDP 20 は、一方の基板上に互いに平行に配置された X 電極 X<sub>1</sub> ~ X<sub>5</sub>、Y 電極 Y<sub>1</sub> ~ Y<sub>4</sub> と他方の基板上に形成され上記 X 電極 X<sub>1</sub> ~ X<sub>5</sub> および Y 電極 Y<sub>1</sub> ~ Y<sub>4</sub> に直交するように形成されたアドレス電極 A<sub>1</sub> ~ A<sub>6</sub> とを備えている。また、面放電型 PDP 20 には、上記アドレス電極 A<sub>1</sub> ~ A<sub>6</sub> に平行に配置された放電空間を仕切るための隔壁 21 ~ 27 が形成されている。

**【 0 0 2 4 】**

そして、上記面放電型 PDP 20 においては、X 電極 X<sub>1</sub> ~ X<sub>5</sub> と Y 電極 Y<sub>1</sub> ~ Y<sub>4</sub> とが隣接し、さらにアドレス電極 A<sub>1</sub> ~ A<sub>6</sub> が直交する領域にセルが形成され、図 14(a) に示すように表示行 L<sub>1</sub> ~ L<sub>8</sub>、すなわち維持放電電極(X 電極および Y 電極)間で表示することができる。

**【 0 0 2 5 】**

図 14(b) は、面放電型 PDP の断面図であり、X 電極および Y 電極に直交し、アドレス電極に平行な断面を示したものである。図 14(b) において、28 はアドレス電極が形成される背面基板であり、29 は X 電極および Y 電極が形成される前面基板である。上述したように、面放電型 PDP においては、X 電極と Y 電極とが隣接し、さらにアドレス電極 A<sub>1</sub> ~ A<sub>6</sub> が直交する領域にセルが形成され、図 14(b) に示すように領域 D<sub>1</sub> ~ D<sub>3</sub> において放電が行われる。すなわち、全ての維持放電電極(X 電極および Y 電極)間で放電させ表示を行う。

10

20

30

40

50

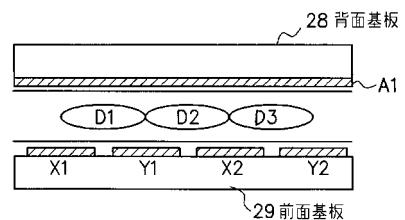

**【 0 0 2 6 】**

図15は、面放電型PDPのフレームの構成例を示す図である。なお、図15においては、全ての維持放電電極(X電極およびY電極)間で放電させ表示を行う場合のフレーム構成を示している。

**【 0 0 2 7 】**

図15において、1フレームは第1フィールドおよび第2フィールドで構成され、例えば、第1フィールドでは奇数番目の表示行において表示を行い、第2フィールドでは偶数番目の表示行において表示を行うことで、1画面の表示を行う。また、第1フィールドおよび第2フィールドは、それぞれが複数(例えば、8個)のサブフィールドにより構成される。なお、各サブフィールドは、図13に示した従来のフレーム構成と同様なので説明は省略する。10

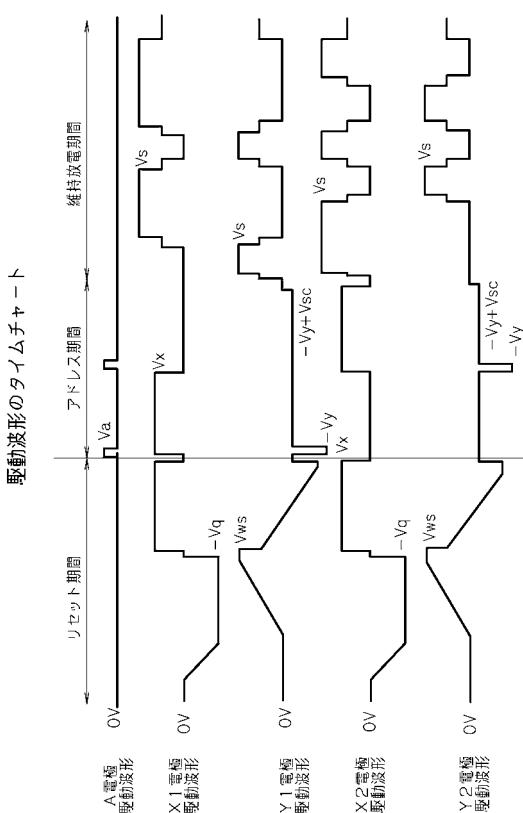

**【 0 0 2 8 】**

図16は、面放電型PDPの駆動波形の一例を示すタイムチャートである。図16においては、X電極 $X_i$ とY電極 $Y_i$ ( $i$ は任意の整数)との間ににおいて放電し表示を行う第1フィールドにおける駆動波形を示し、第1フィールドを構成する複数のサブフィールドのうちの1サブフィールド分を示している。1つのサブフィールドは、全面書き込み期間および全面消去期間から成るリセット期間と、アドレス期間と、維持放電期間とに区分される。

**【 0 0 2 9 】**

また、図16においては、任意のアドレス電極AとX電極 $X_1$ 、 $X_2$ とY電極 $Y_1$ 、 $Y_2$ との駆動波形について示す。なお、他のX電極およびY電極は、それぞれ(X電極 $X_3$ 、Y電極 $Y_3$ 、X電極 $X_4$ 、Y電極 $Y_4$ )、(X電極 $X_5$ 、Y電極 $Y_5$ 、X電極 $X_6$ 、Y電極 $Y_6$ )、…、のように2つのX電極と2つのY電極とが1組となり、図16に示す駆動波形と同様の波形で駆動される。20

**【 0 0 3 0 】**

リセット期間においては、まずX電極 $X_1$ 、 $X_2$ に電圧(- $V_q$ )が印加され、Y電極 $Y_1$ 、 $Y_2$ に、電圧 $V_{ws}$ が印加される。これにより、以前の表示状態に拘わらず、全表示ラインの全セルで放電が行われ、壁電荷が形成される。また、このとき、Y電極 $Y_1$ 、 $Y_2$ に印加される電圧は、時間の経過とともに連続的に変化するような波形(以下、「鈍波」と称す。)で印加される。このような鈍波を印加すると、鈍波の立ち上がり中に放電電圧に達したセルから順次放電が行われるため、実質的に各セルには、最適電圧(放電開始電圧にほぼ等しい電圧)が印加されたことになる。30

**【 0 0 3 1 】**

次に、X電極 $X_1$ 、 $X_2$ には電圧 $V_x$ が印加され、Y電極 $Y_1$ 、 $Y_2$ には到達電圧が電圧(- $V_y$ )の鈍波が印加される。これにより、全セルにおいて壁電荷自身の電圧が放電開始電圧を越えて放電が開始される。このときも鈍波の印加によって微弱放電が行われ、蓄積されていた壁電荷が一部を除いて消去される。

**【 0 0 3 2 】**

次に、アドレス期間においては、表示データに応じて各セルのON/OFFを行うために、線順次でアドレス放電が行われる。上記アドレス期間は前半部分と後半部分の2つに区分され、アドレス期間の前半部分では奇数番目のY電極に対してアドレス放電が行われ、アドレス期間の後半部分では偶数番目のY電極に対してアドレス放電が行われる。40

**【 0 0 3 3 】**

このアドレス期間においては、アドレス放電を行うために選択されたY電極には電圧(- $V_y$ )が印加され、その他のY電極には電圧(- $V_y + V_{sc}$ )が印加されるとともに、維持放電を起こすセル、すなわち点灯させるセルに対応するアドレス電極Aには、電圧 $V_a$ のアドレスパルスが選択的に印加される。この結果、点灯させるセルのアドレス電極AとY電極との間で放電が起り、これをプライミング(種火)として、電圧 $V_x$ のX電極とY電極との放電に移行し、維持放電が可能な量の壁電荷が蓄積される。

**【 0 0 3 4 】**

10

20

30

40

50

なお、図16においては、Y電極Y1、Y2でのアドレス放電のみ示しているが、アドレス期間の前半部分ではY電極Y1、Y3、Y5、…の順に順次選択されてアドレス放電が行われ、アドレス期間の後半部分ではY電極Y2、Y4、Y6、…の順に順次選択されてアドレス放電が行われる。

#### 【0035】

その後、維持放電期間においては、X電極とY電極とに適当なタイミングで電圧Vsの維持パルスが交互に印加されて維持放電が行われ、1サブフィールドの映像表示が行われる。

#### 【0036】

しかしながら、上述した駆動方法により面放電型PDPを駆動する場合には、上記図16に示すタイムチャートに従った駆動電圧を各電極に印加しなければならず、面放電型PDPの駆動装置を構成する各素子には、大きな耐圧を備える素子を用いなければならなかつた。例えば、上記図16に示す維持パルスVsをX電極、Y電極に印加する回路では、上記維持パルス電圧分の非常に大きな耐圧を備える素子を、当該回路を構成する素子に用いなければならなかつた。

#### 【0037】

上記問題を解決する方法の一つとして、面放電型PDPの維持放電電極間で放電を行う際に、一方の電極には正の電圧を印加し、他方の電極には負の電圧を印加することで、消費電力を増加させることなく電極間の電位差を利用して電極間の放電を行う面放電型PDPの駆動方法が提案されている。

10

20

#### 【0038】

図17は、維持放電電極間で放電を行う際に、電極間の電位差を利用して電極間で放電を行う面放電型PDPの駆動波形の一例を示すタイムチャートである。なお、図17において、リセット期間およびアドレス期間においては、図16に示すタイムチャートと各電極間に印加する電圧値のみが異なるだけで、X電極およびY電極の電位関係は同じである。

20

#### 【0039】

維持放電期間においては、X電極およびY電極にはそれぞれ電圧(-Vs/2)から電圧Vs/2の範囲の電圧が印加される。さらに、一方の電極に正の電圧Vs/2を印加している場合には、他方の電極には負の電圧(-Vs/2)を印加することで、X電極とY電極間との電位差が上記図16に示す維持パルス電圧Vs分の電位差となり維持放電電極(X電極とY電極)間で維持放電が行われる。

30

#### 【0040】

このように、維持放電期間において、図17に示す駆動波形に従い、一方の電極には正の電圧を印加して、他方の電極には負の電圧を印加することで、維持放電電極(X電極とY電極)間に上記図16に示す維持パルスVsに相当する電位差を発生させることができ、上記図16に示す駆動波形に従い面放電型PDPを駆動する場合と比較して、駆動装置を構成する各素子の耐圧を小さくすることができる。

30

#### 【0041】

##### 【発明が解決しようとする課題】

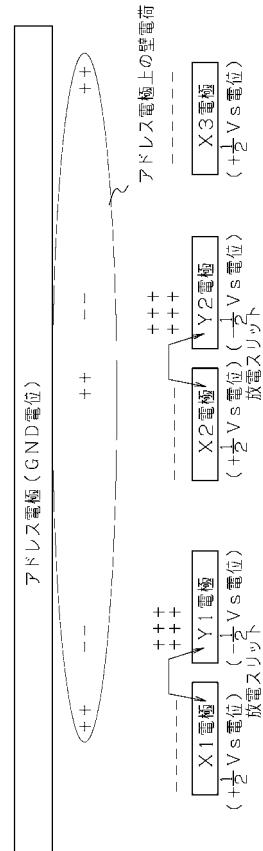

しかしながら、上記図17に示す駆動波形に従って、X電極およびY電極に電圧を印加するようにした場合には、図18に示すように維持放電期間終了後にアドレス電極A上に壁電荷が残留する。

40

図18は、維持放電期間終了後に各電極(アドレス電極、X電極およびY電極)に形成されている壁電荷を示す図である。なお、図18は、維持放電期間の最後の維持パルスとして、X電極には電圧Vs/2が印加され、Y電極には電圧(-Vs/2)が印加された場合に、各電極に形成されている壁電荷を示している。

#### 【0042】

図18に示すように、維持放電期間の最後に電圧Vs/2が印加されたX電極には、マイナスの壁電荷が形成され、電圧(-Vs/2)が印加されたY電極には、プラスの壁電荷が形成されている。また、GND電位であるアドレス電極のX電極に対応する部分にはブ

50

ラスの壁電荷が形成され、Y電極に対応する部分にはマイナスの壁電荷が形成されている。

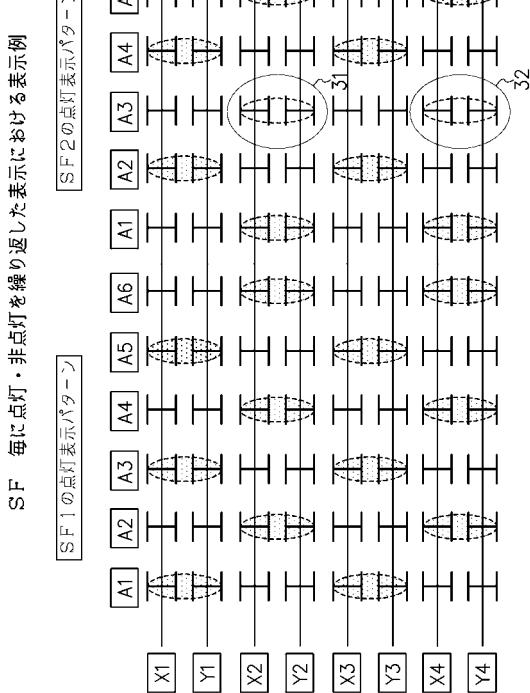

#### 【0043】

このように、維持放電期間終了後に、アドレス電極上に壁電荷が形成されてしまうと、次のサブフィールドにおいて、アドレッシングする（点灯させるセルを選択する）際、隣接セルのアドレス電極、X電極およびY電極に逆極性の電荷が形成され、さらに次のサブフィールドにおいて、アドレッシングする際、表示データに従いアドレスパルスV<sub>a</sub>をアドレス電極に印加したとしても、その残留電荷によりアドレス電極とY電極との間の電位差が放電電圧に到達せず、アドレス電極とY電極との間でのアドレス放電が行われないことがあった。例えば、図19に示すようにサブフィールド毎に点灯と非点灯とを繰り返す場合には、サブフィールドSF2において本来点灯すべきセル31、32が点灯しないことがあった。10

#### 【0044】

また、逆に維持放電期間終了後にアドレス電極上に壁電荷が残留することで、アドレスパルスV<sub>a</sub>をアドレス電極に印加しなくとも、アドレス電極とY電極との間の電位差が放電電圧に到達してしまい、本来点灯させないアドレス電極とY電極との間でのアドレス放電が行われてしまうことがあった。

#### 【0045】

すなわち、維持放電期間終了後にアドレス電極上に壁電荷が残留することで、アドレス期間において点灯させるセルを選択する（アドレッシング）際に、表示データに従って正確に点灯させるセルを選択することができず、PDPの駆動マージンを劣化させたり、表示品位を劣化させたりしてしまうという問題があった。20

#### 【0046】

本発明は、このような問題を解決するために成されたものであり、表示データに従い点灯させるセルを正確に選択し、プラズマディスプレイ装置の駆動マージンや表示品位の劣化を抑制することができるようすることを目的とする。

#### 【0047】

##### 【課題を解決するための手段】

本発明のプラズマディスプレイ装置の駆動方法は、維持放電期間において、隣接する2つの維持放電電極対の各々に正の電圧V<sub>s</sub>/2と負の電圧(-V<sub>s</sub>/2)とを交互に印加して表示セルにて表示放電を行うプラズマディスプレイ装置の駆動方法であって、上記維持放電電極対の一方の電極に正の電圧V<sub>s</sub>を印加し、上記維持放電電極対の他方の電極及び、上記表示セルを選択するためのアドレス電極にグランドレベルの電圧を印加する壁電荷形成工程と、次いで、上記維持放電電極対の双方の電極に上記グランドレベルの電圧を印加し、上記アドレス電極に所定の正の電圧を印加する自己消去工程とを備え、上記正の電圧V<sub>s</sub>は、上記自己消去工程での上記アドレス電極への上記所定の正の電圧の印加により上記アドレス電極と上記維持放電電極対の一方の電極との間で自己消去放電が可能な壁電荷を、上記維持放電電極対間での放電により上記アドレス電極上及び上記維持放電電極対の一方の電極上に形成することを特徴とする。30

#### 【0048】

上記技術手段によれば、維持放電期間における維持放電電極間での維持放電によりアドレス電極上に形成された壁電荷が壁電荷形成工程および自己消去工程での放電により除去され、維持放電により残留した壁電荷の影響を受けずに、表示データに従い点灯させるセルを正確に選択することができるようになる。40

#### 【0049】

##### 【発明の実施の形態】

以下に、本発明の実施形態を図面に基づいて説明する。

なお、以下に示す実施形態は、例えば図14に示す面放電型PDPを備えた図10に示すような交流駆動型のPDP装置に適用することが可能である。

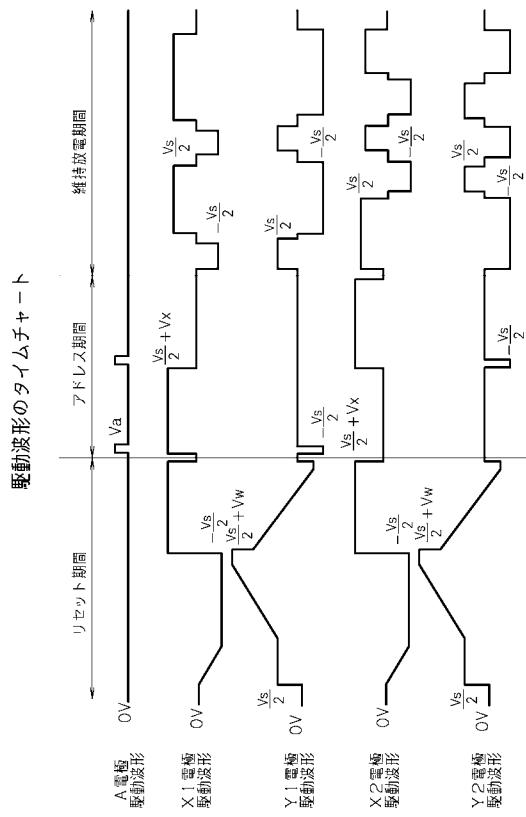

また、以下に示す実施形態による交流駆動型PDPの駆動波形の一例を示すタイムチャート50

トでは、任意のアドレス電極 A と X 電極 X 1、X 2 と Y 電極 Y 1、Y 2 との駆動波形について示しているが、他の X 電極および Y 電極は、それぞれ ( X 電極 X 3、Y 電極 Y 3、X 電極 X 4、Y 電極 Y 4 )、( X 電極 X 5、Y 電極 Y 5、X 電極 X 6、Y 電極 Y 6 )、...、のように 2 つの X 電極と 2 つの Y 電極とが 1 組となり、X 電極 X 1、X 2 と Y 電極 Y 1、Y 2 と同様の波形で駆動される。

#### 【 0 0 5 0 】

( 第 1 の実施形態 )

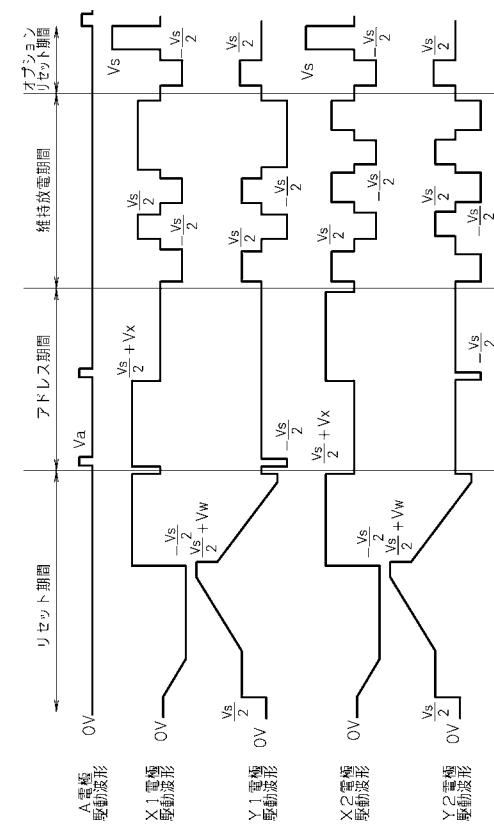

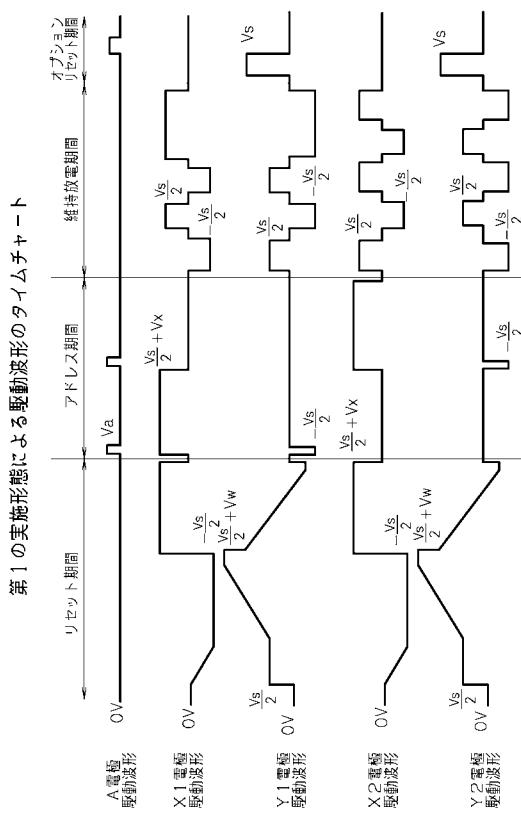

図 1 は、第 1 の実施形態による交流駆動型 PDP の駆動波形の一例を示すタイムチャートである。

また、図 1 においては、X 電極 X i と Y 電極 Y i ( i は任意の整数 ) との間に放電し表示を行う第 1 フィールドにおける駆動波形を示し、第 1 フィールドを構成する複数のサブフィールドのうちの 1 サブフィールド分を示している。1 つのサブフィールドは、全面書き込み期間および全面消去期間から成るリセット期間と、アドレス期間と、維持放電期間と、オプションリセット期間に区分される。

#### 【 0 0 5 1 】

リセット期間においては、まず X 電極 X 1、X 2 に電圧 ( - V s / 2 ) を印加する。また、Y 電極 Y 1、Y 2 にはまず電圧 V s / 2 を印加し、次に電圧 ( V s / 2 + V w ) の鈍波を印加する。これにより、以前の表示状態に関わらず、全表示ラインの全セルで放電が行われ、壁電荷が形成される ( 全面書き込み )。このような鈍波を印加することで、鈍波の立ち上がり中に放電電圧に達したセルから順次放電が行われ、実質的に各セルには最適電圧 ( 放電開始電圧にほぼ等しい電圧 ) が印加されたことになる。

#### 【 0 0 5 2 】

次に、X 電極 X 1、X 2 には電圧 ( V s / 2 + V x ) を印加し、Y 電極 Y 1、Y 2 には到達電圧が負の電圧の鈍波を印加する。これにより、全セルにおいて壁電荷自身の電圧が放電開始電圧を越えて放電が開始される ( 全面消去 )。このときも鈍波の印加によって微弱放電が行われ、蓄積されていた壁電荷が一部を除いて消去される。

#### 【 0 0 5 3 】

次に、アドレス期間においては、表示データに応じて各セルの ON / OFF を行うために、線順次でアドレス放電が行われる。上記アドレス期間は前半部分と後半部分の 2 つに区分され、アドレス期間の前半部分では奇数番目の Y 電極に対してアドレス放電が行われ、アドレス期間の後半部分では偶数番目の Y 電極に対してアドレス放電が行われる。また、アドレス期間の前半部分では、維持放電期間において奇数番目の Y 電極と放電を行う奇数番目の X 電極には電圧 ( V s / 2 + V x ) を印加し、アドレス期間の後半部分では維持放電期間において偶数番目の Y 電極と放電を行う偶数番目の X 電極には電圧 ( V s / 2 + V x ) を印加する。

#### 【 0 0 5 4 】

このアドレス期間においては、アドレス放電を行うために選択された Y 電極には電圧 ( - V s / 2 ) を印加し、その他の Y 電極はグランドレベル ( 0 V ) にされるとともに、維持放電を起こすセル、すなわち点灯させるセルに対応するアドレス電極 A には、電圧 V a のアドレスパルスを選択的に印加する。この結果、点灯させるセルのアドレス電極 A と Y 電極との間で放電が起こり、これをプライミング ( 種火 ) として、電圧 ( V s / 2 + V x ) の X 電極と Y 電極との放電に移行し、維持放電が可能な量の壁電荷が蓄積される。

#### 【 0 0 5 5 】

なお、図 1 においては、Y 電極 Y 1、Y 2 でのアドレス放電のみ示しているが、アドレス期間の前半部分では Y 電極 Y 1、Y 3、Y 5、... の順に順次選択されてアドレス放電が行われ、アドレス期間の後半部分では Y 電極 Y 2、Y 4、Y 6、... の順に順次選択されてアドレス放電が行われる。

#### 【 0 0 5 6 】

その後、維持放電期間においては、維持放電電極 ( X 電極および Y 電極 ) に、正の電圧 V s / 2 と負の電圧 ( - V s / 2 ) とを交互に印加していく。このとき、X 電極および Y 電

10

20

30

40

50

極のそれぞれに印加する電圧は、互いに極性が反転するように印加する。つまり、X電極に正の電圧 $V_s / 2$ を印加している場合には、Y電極には負の電圧( $-V_s / 2$ )を印加する。これにより、X電極とY電極との電位差が、X電極とY電極との間で放電を行う維持パルス電圧 $V_s$ 分の電位差となり維持放電電極(X電極とY電極)間で維持放電が行われる。

#### 【0057】

次に、オプションリセット期間においては、まずX電極X1、X2に電圧( $-V_s / 2$ )を印加し、Y電極Y1、Y2には電圧 $V_s / 2$ を印加する。次に、X電極X1、X2およびY電極Y1、Y2の双方をグランドレベルした後、X電極X1、X2に維持パルス電圧の2倍の電圧 $V_s$ を印加する。これにより、X電極X1、X2とY電極Y1、Y2とで放電を行う。この間、アドレス電極Aはグランドレベルに保たれる。

10

その後、X電極X1、X2をグランドレベル(0V)にするとともに、アドレス電極Aに電圧 $V_a$ のパルスを印加する。これにより、アドレス電極AとX電極X1、X2とで自己消去放電を行う。なお、このとき、Y電極Y1、Y2はグランドレベルである。

#### 【0058】

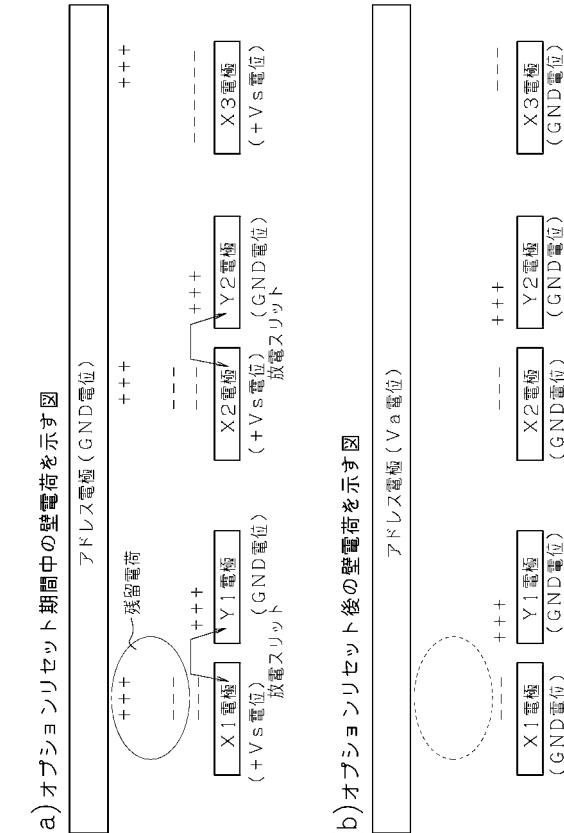

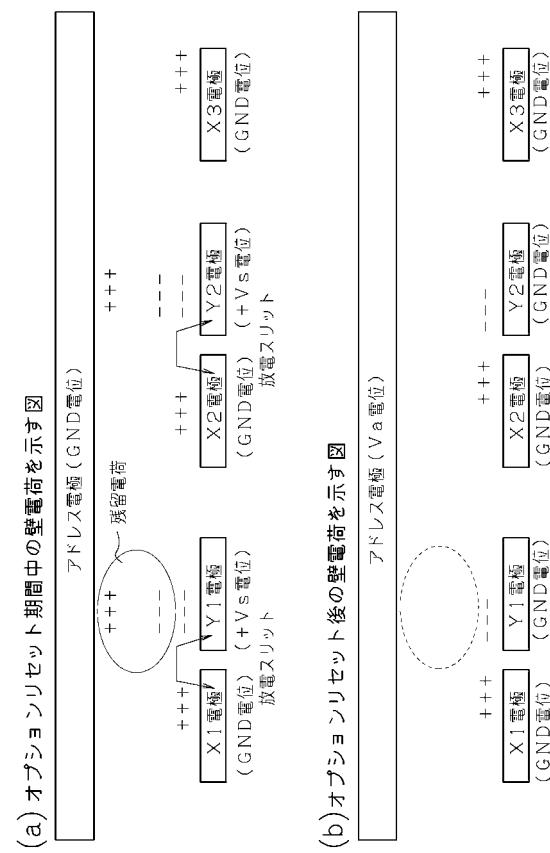

図2は、上記図1に示すオプションリセット期間において、各電極(アドレス電極、X電極およびY電極)に形成されている壁電荷について説明するための図である。

#### 【0059】

図2(a)は、オプションリセット期間において、X電極に維持パルス電圧の2倍の電圧 $V_s$ を印加したときの各電極(アドレス電極、X電極およびY電極)に形成される壁電荷について示している。図2(a)に示すように、維持パルス電圧の2倍の電圧 $V_s$ をX電極X1、X2、X3を印加することで、X電極 $X_i$ とグランドレベル(0V)であるY電極 $i$ ( $i$ は任意の整数)との間で放電が行われ、X電極X1、X2、X3にはマイナスの壁電荷が形成され、Y電極Y1、Y2にはプラスの壁電荷が形成される。また、グランドレベル(0V)であるアドレス電極は、上記X電極X1、X2、X3に対して陰極となり、アドレス電極のX電極X1、X2、X3に対応する部分にはプラスの壁電荷が形成される。

20

#### 【0060】

図2(b)は、図2(a)に示すように各電極に壁電荷が形成されている状態で、アドレス電極に電圧 $V_a$ のパルスを印加したときの各電極に形成される壁電荷について示した図である。アドレス電極に電圧 $V_a$ のパルスを印加すると、アドレス電極とX電極X1、X2、X3との間で自己消去放電が行われる。つまり、アドレス電極およびX電極X1、X2、X3上の壁電荷が中和され、残留していた壁電荷が除去される。その結果、図2(b)に示すように、X電極X1、X2、X3にはマイナスの壁電荷の一部が残り、アドレス電極上のプラスの壁電荷は除去される。

30

#### 【0061】

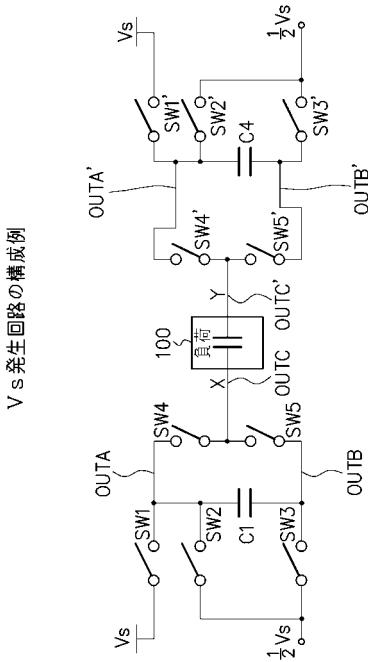

図3は、上記図1に示した駆動波形のオプションリセット期間において、X電極X1、X2に維持パルス電圧の2倍の電圧 $V_s$ を印加するための $V_s$ 発生回路の回路構成例である。

。

図3において、負荷100は、1つのX電極と1つのY電極との間に形成されている維持放電電極間のセルの合計の容量C p c e l lである。また、負荷100には、X電極およびY電極が形成されている。

40

#### 【0062】

X電極側では、スイッチSW1、SW2は、図示しない電源から供給される電圧 $V_s$ の電源ラインと、電圧 $V_s / 2$ の電源ラインとの間に直列に接続される。上記2つのスイッチSW1、SW2の相互接続点にはコンデンサC1の一方の端子が接続され、このコンデンサC1の他方の端子と電圧 $V_s / 2$ の電源ラインとの間には、スイッチSW3が接続される。

#### 【0063】

また、スイッチSW4、SW5は、上記コンデンサC1の両端に直列に接続され、上記S

50

W4は第1の信号ラインOUTAを介して、コンデンサC1の上記一方の端子に接続され、上記SW5は第2の信号ラインOUTBを介して、コンデンサC1の上記他方の端子に接続される。そして、これら2つのスイッチSW4およびSW5の相互接続点には、出力ラインOUTCを介して負荷100のX電極が接続されている。

なお、Y電極側の構成については、X電極側の構成と同じであるので、説明は省略する。

#### 【0064】

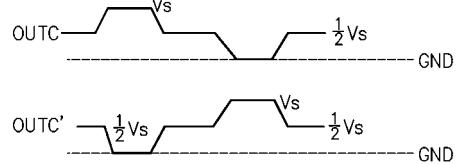

図4は、上記図3に示したVs発生回路のタイムチャートである。

図4において、まずX電極側の2つのスイッチSW1、SW3がONとなり、残りのスイッチSW2、SW4、SW5はOFFとなると、第1の信号ラインOUTAの電圧は、図示しない電源よりスイッチSW1を介して与えられる電圧レベルVsとなる。このとき、SW1とSW3との間に接続されたコンデンサC1には、図示しない電源にそれぞれ接続されたスイッチSW1とスイッチSW3との電位差(Vs/2)に応じた電荷が蓄積される。その後、スイッチSW4がONとなるとともに、Y電極側のスイッチSW4'、SW2'がONとなることにより、第1の信号ラインOUTAの電圧Vsが出力ラインOUTCを介して負荷100のX電極に印加され、X電極とY電極との間に電圧Vsが印加される。

10

#### 【0065】

次に、スイッチSW4がOFFとなって、電圧を印加する際の電流経路が遮断された後、スイッチSW5がパルス状にONとなることにより、出力ラインOUTCの電圧が、スイッチSW3および第2の信号ラインOUTB'を介して図示しない電源より与えられる電圧レベル(Vs/2)となる。次に、スイッチSW2がON、残り4つのスイッチSW1、SW3、SW4、SW5がOFFとされた後、スイッチSW4がパルス状にONとなる。このスイッチSW4がONとなることにより、X電極に対し、Y電極側に電圧を印加するときの電流経路となる。

20

#### 【0066】

次に、スイッチSW2をONに維持したまま、スイッチSW5がONとなる。このとき、第1の信号ラインOUTAには図示しない電源からスイッチSW1を介して電源電圧が供給されないので、その電圧はVs/2となる。一方、第2の信号ラインOUTBに関しては、スイッチSW2がONとなって第1の信号ラインOUTAが接地されることにより、第2の信号ラインOUTBの電圧は、コンデンサC1に蓄積されている電荷に応じた電圧(Vs/2)分だけVs/2から下がったグランドレベル(0V)となる。

30

#### 【0067】

このとき、スイッチSW5がONとなっているので、出力ラインOUTCを介して第2の信号ラインOUTBと接続されている負荷100のX電極側の電位はグランドレベルとなる。その際、走査電極Y側のスイッチSW3'、SW4'はONである。

次に、スイッチSW2、SW4がONとなり、残りのスイッチSW1、SW3、SW5はOFFとなる。これにより、出力ラインOUTCの電圧がVs/2になる。

30

#### 【0068】

図5は、第1の実施形態による交流駆動型PDPの駆動波形の他の一例を示すタイムチャートである。この図5に示す駆動波形のタイムチャートは、上記図1に示した駆動波形のタイムチャートにおいては、オプションリセット期間において、X電極X1、X2に維持パルス電圧の2倍の電圧Vsを印加していたものを、X電極X1、X2をグランドレベルにして、Y電極Y1、Y2に維持パルス電圧の2倍の電圧Vsを印加するようにした駆動波形のタイムチャートである。

40

#### 【0069】

また、図5においては、図1と同様に第1フィールドにおける駆動波形を示し、第1フィールドを構成する複数のサブフィールドのうちの1サブフィールド分を示している。1つのサブフィールドは、全面書き込み期間および全面消去期間から成るリセット期間と、アドレス期間と、維持放電期間と、オプションリセット期間に区分される。

#### 【0070】

50

なお、図5において、リセット期間、アドレス期間および維持放電期間の駆動波形は、図1に示した駆動波形と同じであるので、重複する説明は省略する。

#### 【0071】

オプションリセット期間においては、まずX電極X1、X2およびY電極Y1、Y2の双方をグランドレベルする。その後、Y電極Y1、Y2に維持パルス電圧の2倍の電圧Vsを印加する。これにより、X電極X1、X2とY電極Y1、Y2とで放電を行う。この間、アドレス電極Aはグランドレベルに保たれる。

#### 【0072】

次に、Y電極Y1、Y2をグランドレベル(0V)にするとともに、アドレス電極Aに電圧Vaのパルスを印加する。これにより、アドレス電極AとY電極Y1、Y2とで自己消去放電を行う。なお、このとき、X電極X1、X2はグランドレベルである。

10

#### 【0073】

図6は、上記図5に示すオプションリセット期間において、各電極(アドレス電極、X電極およびY電極)に形成されている壁電荷について説明するための図である。

図6(a)は、オプションリセット期間において、Y電極に維持パルス電圧の2倍の電圧Vsを印加したときの各電極に形成される壁電荷について示している。図6(a)に示すように、維持パルス電圧の2倍の電圧VsをY電極Y1、Y2を印加することにより、グランドレベル(0V)であるX電極XiとY電極i(iは任意の整数)との間で放電が行われ、X電極X1、X2、X3にはプラスの壁電荷が形成され、Y電極Y1、Y2にはマイナスの壁電荷が形成される。また、グランドレベル(0V)であるアドレス電極は、上記Y電極Y1、Y2に対して陰極となり、アドレス電極のY電極Y1、Y2に対応する部分にはプラスの壁電荷が形成される。

20

#### 【0074】

図6(b)は、図6(a)に示すように各電極に壁電荷が形成されている状態で、アドレス電極に電圧Vaのパルスを印加したときの各電極に形成される壁電荷について示した図である。アドレス電極に電圧Vaのパルスを印加すると、アドレス電極とY電極Y1、Y2との間で自己消去放電が行われる。つまり、アドレス電極およびY電極Y1、Y2上の壁電荷が中和され、残っていた壁電荷が除去される。その結果、図6(b)に示すように、Y電極Y1、Y2にはマイナスの壁電荷の一部が残り、アドレス電極上のプラスの壁電荷は除去される。

30

#### 【0075】

以上、詳しく説明したように第1の実施形態によれば、各サブフィールドの維持放電期間後に、維持放電電極の何れか一方の電極に維持パルスの2倍の電圧Vsを印加することにより行われる維持放電電極間での放電により、電圧Vaのパルスにてアドレス電極と維持放電電極の何れか一方の電極とで自己消去放電が可能な壁電荷を、アドレス電極上に形成する。その後、アドレス電極Aに電圧Vaのパルスを印加することで、アドレス電極と維持放電電極の何れか一方の電極とで自己消去放電を行い、アドレス電極上に形成された壁電荷を除去する。

#### 【0076】

これにより、維持放電期間の維持放電によりアドレス電極上に形成される壁電荷を除去した状態で、アドレス期間において表示データに従い点灯させるセルを正確に選択することができ、プラズマディスプレイ装置の駆動マージンや表示品位の劣化を抑制することができる。

40

#### 【0077】

##### (第2の実施形態)

次に、本発明の第2の実施形態について説明する。

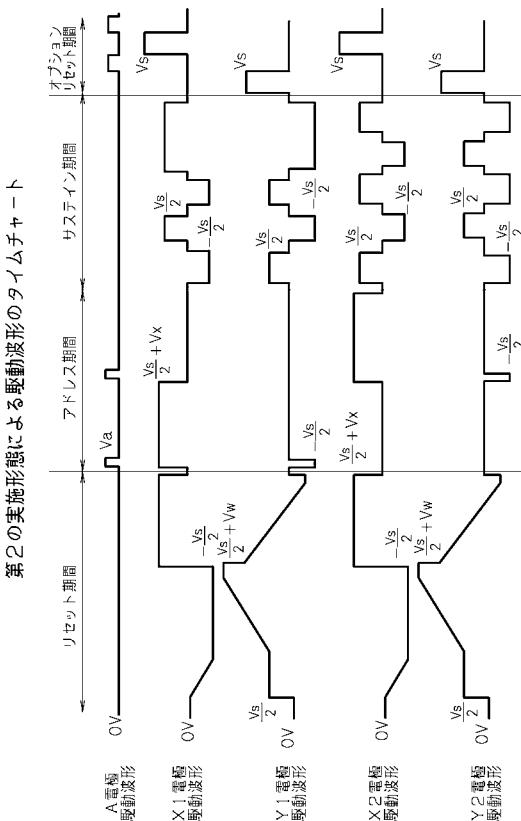

図7は、第2の実施形態による交流駆動型PDPの駆動波形の一例を示すタイムチャートである。第2の実施形態による駆動波形のタイムチャートは、オプションリセット期間において、第1の実施形態ではX電極またはY電極の何れかに維持パルス電圧の2倍の電圧Vsを印加するようにしていたものを、X電極およびY電極の双方にタイミングをずらし

50

て、それぞれ維持パルス電圧の2倍の電圧 $V_s$ を印加するようにしたものである。

**【0078】**

また、図7においては、第1フィールドにおける駆動波形を示し、第1フィールドを構成する複数のサブフィールドのうちの1サブフィールド分を示しており、1つのサブフィールドは、全面書き込み期間および全面消去期間から成るリセット期間と、アドレス期間と、維持放電期間と、オプションリセット期間に区分される。

**【0079】**

なお、図7において、リセット期間、アドレス期間および維持放電期間の駆動波形は、図1に示した駆動波形と同じであるので、重複する説明は省略する。

**【0080】**

オプションリセット期間においては、まずX電極X1、X2およびY電極Y1、Y2の双方をグランドレベルする。その後、Y電極Y1、Y2に維持パルス電圧の2倍の電圧 $V_s$ を印加する。これにより、X電極X1、X2とY電極Y1、Y2とで放電を行う。この間、アドレス電極Aはグランドレベルに保たれる。

**【0081】**

次に、Y電極Y1、Y2をグランドレベル(0V)にするとともに、アドレス電極Aに電圧 $V_a$ のパルスを印加する。これにより、アドレス電極AとY電極Y1、Y2とで自己消去放電を行う。なお、このとき、X電極X1、X2はグランドレベルである。

**【0082】**

その後、アドレス電極Aをグランドレベルにして、X電極X1、X2に維持パルス電圧の2倍の電圧 $V_s$ を印加した後、Y電極Y1、Y2をグランドレベル(0V)にするとともに、アドレス電極Aに電圧 $V_a$ のパルスを印加する。これにより、X電極X1、X2とY電極Y1、Y2との放電に引き続き、アドレス電極AとX電極X1、X2とで自己消去放電を行う。

**【0083】**

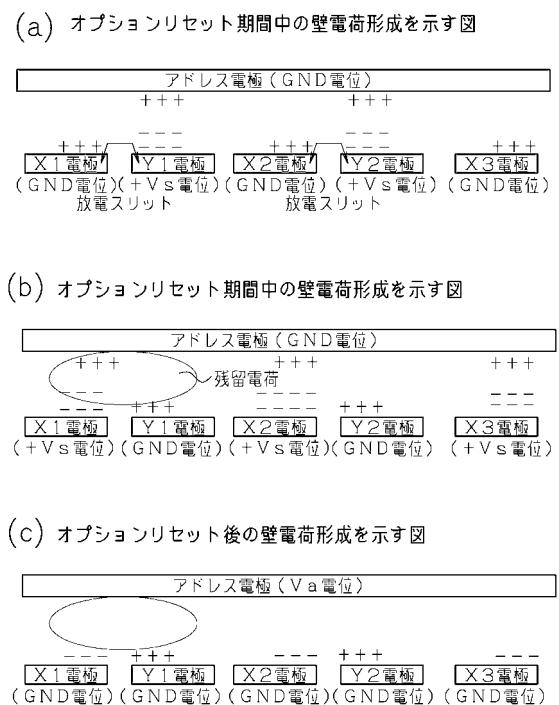

図8は、上記図7に示すオプションリセット期間において、各電極(アドレス電極、X電極およびY電極)に形成されている壁電荷について説明するための図である。

図8(a)は、オプションリセット期間において、Y電極に維持パルス電圧の2倍の電圧 $V_s$ を印加したときの各電極に形成される壁電荷について示している。図8(a)に示すように、維持パルス電圧の2倍の電圧 $V_s$ をY電極Y1、Y2に印加することで、グランドレベル(0V)であるX電極 $X_i$ とY電極 $i$ ( $i$ は任意の整数)との間で放電が行われ、X電極X1、X2、X3にはプラスの壁電荷が形成され、Y電極Y1、Y2にはマイナスの壁電荷が形成される。また、グランドレベル(0V)であるアドレス電極は、上記Y電極Y1、Y2に対して陰極となり、アドレス電極のY電極Y1、Y2に対応する部分にはプラスの壁電荷が形成される。

**【0084】**

図8(b)は、図8(a)に示すように各電極に壁電荷が形成されている状態で、アドレス電極に電圧 $V_a$ のパルスを印加しY電極上に形成された壁電荷を除去した後、X電極に維持パルス電圧の2倍の電圧 $V_s$ を印加したときの各電極に形成される壁電荷について示している。図8(b)に示すように、維持パルス電圧の2倍の電圧 $V_s$ をX電極X1、X2、X3に印加することで、X電極 $X_i$ とグランドレベル(0V)であるY電極 $i$ ( $i$ は任意の整数)との間で放電が行われ、X電極X1、X2、X3にはマイナスの壁電荷が形成され、Y電極Y1、Y2にはプラスの壁電荷が形成される。また、グランドレベル(0V)であるアドレス電極は、上記X電極X1、X2、X3に対して陰極となり、アドレス電極のX電極X1、X2、X3に対応する部分にはプラスの壁電荷が形成される。

**【0085】**

図8(c)は、図8(b)に示すように各電極に壁電荷が形成されている状態で、アドレス電極に電圧 $V_a$ のパルスを印加したときの各電極に形成される壁電荷について示した図である。アドレス電極に電圧 $V_a$ のパルスを印加すると、アドレス電極とX電極X1、X2、X3との間で自己消去放電が行われる。つまり、アドレス電極およびX電極X1、X2、X3との間に

10

20

30

40

50

2、X 3 上の壁電荷が中和され、残留していた壁電荷が除去される。その結果、図 8 ( c ) に示すように、X 電極 X 1、X 2、X 3 にはマイナスの壁電荷の一部が残り、アドレス電極上のプラスの壁電荷は除去される。

#### 【 0 0 8 6 】

以上、説明したように第 2 の実施形態によれば、各サブフィールドの維持放電期間後に、維持放電電極の何れか一方の電極に維持パルスの 2 倍の電圧  $V_s$  を印加した後、さらに他方の電極に維持パルスの 2 倍の電圧  $V_s$  を印加することにより、電圧  $V_a$  のパルスにてアドレス電極と維持放電電極の何れか一方の電極とで自己消去放電が可能な壁電荷を、維持放電電極間の維持放電によりアドレス電極上に形成する。その後、アドレス電極 A に電圧  $V_a$  のパルスを印加することで、アドレス電極と上記他方の電極とで自己消去放電を行い、アドレス電極上に形成された壁電荷を除去する。10

#### 【 0 0 8 7 】

これにより、維持放電期間の維持放電によりアドレス電極上に形成される壁電荷を除去した状態で、アドレス期間において表示データに従い点灯させるセルを正確に選択することができ、プラズマディスプレイ装置の駆動マージンや表示品位の劣化を抑制することができる。

#### 【 0 0 8 8 】

また、維持放電電極の何れか一方の電極に維持パルスの 2 倍の電圧  $V_s$  を印加した後、さらに他方の電極に維持パルスの 2 倍の電圧  $V_s$  を印加するようにしたので、維持放電期間での最後の維持パルスの印加状態に関係なく、確実にアドレス電極上に形成される壁電荷を除去することができる。20

#### 【 0 0 8 9 】

なお、上述した第 2 の実施形態においては、オプションリセット期間において Y 電極 Y 1、Y 2 に維持パルス電圧の 2 倍の電圧  $V_s$  を印加した後、X 電極 X 1、X 2 に電圧  $V_s$  を印加するようにしているが、X 電極 X 1、X 2 に維持パルス電圧の 2 倍の電圧  $V_s$  を印加した後、Y 電極 Y 1、Y 2 に電圧  $V_s$  を印加するようにしても良い。

#### 【 0 0 9 0 】

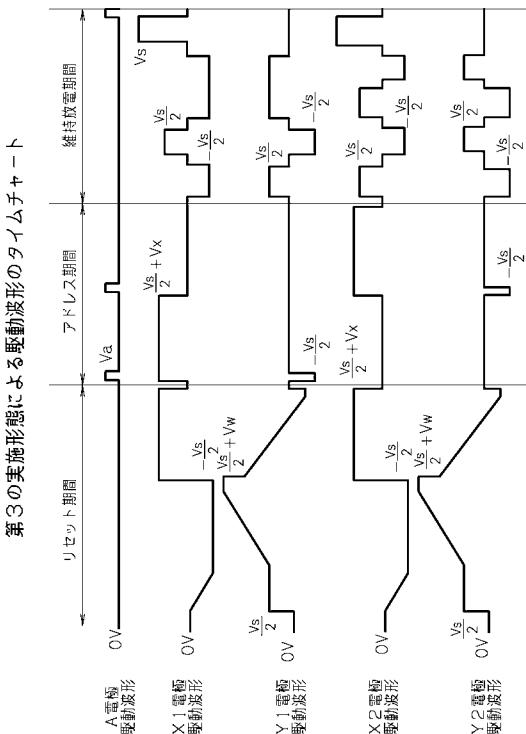

##### ( 第 3 の実施形態 )

次に、本発明の第 3 の実施形態について説明する。

図 9 は、第 3 の実施形態による交流駆動型 PDP の駆動波形の一例を示すタイムチャートである。第 3 の実施形態による駆動波形のタイムチャートは、第 1 の実施形態では、オプションリセット期間において X 電極または Y 電極の何れかに維持パルス電圧の 2 倍の電圧  $V_s$  を印加するようになっていたものを、維持放電期間中の最後に印加する維持パルスを 2 倍の電圧  $V_s$  に置き換え、維持放電電極に印加するようにしたものである。30

#### 【 0 0 9 1 】

また、図 9においては、第 1 フィールドにおける駆動波形を示し、第 1 フィールドを構成する複数のサブフィールドのうちの 1 サブフィールド分を示しており、1 つのサブフィールドは、全面書き込み期間および全面消去期間から成るリセット期間と、アドレス期間と、維持放電期間に区分される。

#### 【 0 0 9 2 】

なお、図 9において、リセット期間、アドレス期間の駆動波形は、図 1 に示した駆動波形と同じであるので、重複する説明は省略する。40

#### 【 0 0 9 3 】

維持放電期間においては、維持放電電極 ( X 電極および Y 電極 ) に、正の電圧  $V_s / 2$  と負の電圧 ( -  $V_s / 2$  ) とを交互に印加していく。このとき、X 電極および Y 電極のそれぞれに印加する電圧は、互いに極性が反転するように印加する。つまり、X 電極に正の電圧  $V_s / 2$  を印加している場合には、Y 電極には負の電圧 ( -  $V_s / 2$  ) を印加する。これにより、X 電極と Y 電極との電位差が、X 電極と Y 電極との間で放電を行う維持パルス電圧  $V_s$  分の電位差となり維持放電電極 ( X 電極と Y 電極 ) 間で維持放電が行われる。

#### 【 0 0 9 4 】

さらに、本実施形態では、維持放電期間において、最後の維持パルスを印加する際、維持放電電極（X電極およびY電極）の一方の電極には維持パルス電圧の2倍の電圧 $V_s$ を印加し、他方の電極はグランドレベル（0V）にする。なお、図9は、X電極X1、X2に維持パルス電圧の2倍の電圧 $V_s$ を印加した場合を示している。これにより、X電極X1、X2とY電極Y1、Y2とで放電を行う。

#### 【0095】

その後、維持放電電極（X電極およびY電極）の双方の電極をグランドレベル（0V）にするとともに、アドレス電極Aに電圧 $V_a$ のパルスを印加する。これにより、アドレス電極AとX電極X1、X2とで自己消去放電を行う。なお、このとき、Y電極Y1、Y2はグランドレベルである。

10

#### 【0096】

以上、説明したように第3の実施形態によれば、維持放電期間中の最後に印加する維持パルスを2倍の電圧 $V_s$ に置き換えて印加することにより、電圧 $V_a$ のパルスにてアドレス電極と維持放電電極の何れか一方の電極とで自己消去放電が可能な壁電荷を、維持放電電極間の維持放電によりアドレス電極上に形成する。その後、アドレス電極Aに電圧 $V_a$ のパルスを印加することで、アドレス電極と上記他方の電極とで自己消去放電を行い、アドレス電極上に形成された壁電荷を除去する。

#### 【0097】

これにより、維持放電期間中にアドレス電極上に形成される壁電荷を維持放電期間中の最後に印加した維持パルスにより除去することができる、アドレス電極上に壁電荷がない状態で、アドレス期間において表示データに従い点灯させるセルを正確に選択することができ、プラズマディスプレイ装置の駆動マージンや表示品位の劣化を抑制することができる。

20

#### 【0098】

また、維持放電期間中の最後に印加する維持パルスを2倍の電圧 $V_s$ に置き換えて印加するようにしたので、フィールドやサブフィールドの構成を変えることなく、確実にアドレス電極上に形成される壁電荷を除去することができる。

#### 【0099】

なお、上述した第1および第2の実施形態においては、1つのサブフィールドは、リセット期間と、アドレス期間と、維持放電期間と、オプションリセット期間に区分されるものとしたが、1つのサブフィールドを、リセット期間と、アドレス期間と、維持放電期間に区分して、サブフィールド間にオプションリセット期間を設けるようにしても良い。また、上述した第1および第2の実施形態においては、サブフィールド内の維持放電期間後にオプションリセット期間を設けていたが、サブフィールド内のリセット期間前にオプションリセット期間を設けるようにしても良い。

30

#### 【0100】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化のほんの一例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。

40

#### 【0101】

#### 【発明の効果】

本発明によれば、表示セルを選択するためのアドレス電極上に維持放電期間における維持放電電極間での維持放電により形成された壁電荷が壁電荷形成工程および自己消去工程での放電により除去され、維持放電により形成された壁電荷の影響を受けずに、表示データに従い点灯させるセルを正確に選択することができ、プラズマディスプレイ装置の駆動マージンや表示品位の劣化を抑制することができる。

#### 【図面の簡単な説明】

【図1】第1の実施形態による交流駆動型PDPの駆動波形の一例を示すタイムチャートである。

50

【図2】オプションリセット期間において、各電極に形成されている壁電荷について説明するための図である。

【図3】Vs発生回路の回路構成例を示す図である。

【図4】Vs発生回路のタイムチャートである。

【図5】第1の実施形態による交流駆動型PDPの駆動波形の他の一例を示すタイムチャートである。

【図6】オプションリセット期間において、各電極に形成されている壁電荷について説明するための図である。

【図7】第2の実施形態による交流駆動型PDPの駆動波形の一例を示すタイムチャートである。

【図8】オプションリセット期間において、各電極（アドレス電極、X電極およびY電極）に形成されている壁電荷について説明するための図である。

【図9】第3の実施形態による交流駆動型PDPの駆動波形の一例を示すタイムチャートである。

【図10】交流駆動型PDP装置の全体構成を示す図である。

【図11】1画素である第i行第j列のセルC<sub>ij</sub>の断面構成を示す図である。

【図12】従来の交流駆動型PDPの駆動方法の一例を示すタイムチャートである。

【図13】従来の1フレームの構成例を示す図である。

【図14】面放電型PDPの構成を示す図である。

【図15】面放電型PDPのフレームの構成例を示す図である。

【図16】面放電型PDPの駆動波形の一例を示すタイムチャートである。

【図17】面放電型PDPの駆動波形の一例を示すタイムチャートである。

【図18】維持放電期間終了後に各電極に形成されている壁電荷を示す図である。

【図19】サブフィールド毎に点灯・非点灯を繰り返した表示における表示例を示す図である。

#### 【符号の説明】

1、20 PDP

2 X側回路

3 Y側回路

4 アドレス側回路

5 制御回路

100 負荷

SW1～SW5、SW1'～SW5' スイッチ

OUTA 第1の信号ライン

OUTB 第2の信号ライン

OUTA' 第3の信号ライン

OUTB' 第4の信号ライン

10

20

30

【図 1】

【図 3】

【図 2】

【図 4】

V<sub>s</sub>発生回路のタイムチャート

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【 図 1 1 】

【図12】

【図 1 3】

【図 1 4】

(a) 両放電型PDPの概略構成図

(b) 両放電型PDPの断面図

【図 1 5】

両放電型PDPのフレームの構成図

【図 1 6】

【図 17】

【図 18】

【図 19】

---

フロントページの続き

(72)発明者 伊藤 英司

神奈川県川崎市高津区坂戸3丁目2番1号 富士通日立プラズマディスプレイ株式会社内

(72)発明者 岸 智勝

神奈川県川崎市高津区坂戸3丁目2番1号 富士通日立プラズマディスプレイ株式会社内

審査官 小川 浩史

(56)参考文献 特開平11-312470(JP,A)

特開平11-133913(JP,A)

特開平10-274955(JP,A)

特開2000-122602(JP,A)

特開2000-306516(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/20-3/38